# Engineered substrates with embedded strain relief for stretchable thin-film electronics

## THÈSE Nº 6798 (2015)

PRÉSENTÉE LE 6 NOVEMBRE 2015

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR CHAIRE FONDATION BERTARELLI DE TECHNOLOGIE NEUROPROSTHÉTIQUE PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

#### Alessia ROMEO

acceptée sur proposition du jury:

Prof. H. Shea, président du jury Prof. S. Lacour, directrice de thèse Prof. A. R. Studart, rapporteur Prof. J. P. Conde, rapporteur Prof. J. Brugger, rapporteur

## **Abstract**

Stretchable electronics are integrated circuitry that can reversibly expand and relax while retaining their functionality. This emerging technology has great potential in unconventional electronic application areas, especially in biomedical sector. To attain stretchability, new class of substrates, based on highly elastic polymers, have to be used. The resulting stretchable circuits are hybrid systems, combining *hard* functional materials on *soft* substrates. However, manufacturing of stretchable electronics sets new challenges due to significantly different material properties between the stretchable substrates and electronic devices, and, therefore, optimized mechanical architectures are required.

In this thesis a simple and robust approach to design and manufacture stretchable substrate for stretchable electronic applications is reported. The proposed solution is based on engineered stretchable substrates with embedded strain relief. The substrate is engineered by embedding stiff platfroms within a soft elastomer. Since the platforms are significantly stiffer than the surrounding silicone matrix, the stiff regions distributed across the substrate allow for large global strains with local areas that remain un-strained. These local, un-strained regions act as non-stretchable areas on the plain top surface of the elastomer, which can host brittle devices and protect them from exceeding their fracture strain. Optimization of the platforms geometry and layout, as well as, grading of the mechanical compliance at the rigid-to-soft transition zones have been performed to adjust the strain distribution on the top surface. Associated design rules to produce stretchable circuits based on experimental as well as modeling data are presented.

This innovative approach is compatible with conventional, additive thin-film processing. Direct integration of metal oxide thin film transistors onto the planar but mechanically engineered heterogeneous elastic substrate is demonstrated. IGZO TFTs interconnected with stretchable metallization spanning across the rigid platform were manufactured directly on the non deformable elastomer regions, using standard, dry and low temperature processing. IGZO TFT could sustained applied tensile strain up to 20% without electrical degradation and mechanical fracture.

Elastomeric substrates with engineered strain relief are, thus, a promising solution to carry reliable and durable stretchable electronics.

Additionally, concurrent mechanical and structural photopatterning in photosensitive elastomer was discovered.

To date, photosensitive elastomers have mainly been implemented in soft lithography or to locally modulate the elasticity. This thesis demonstrates that shape and stiffness can be

engineered in a single elastomeric membrane using simple UV exposure through standard photolithography mask. Modulating the UV dose defines mechanical stiffness gradient within the elastomer as well as topography across the elastomer surface. This process eliminates lithography wet development step therefore offers a new technique to silicone microstructuring, allowing for mold and development free 3D patterning of microfluidic channels. Therefore, single-step photopatterning of photosensitve elastomers enables for rapid prototyping approach for soft MEMS, microfluidics and stretchable electronic.

**Keywords**: stretchable electronics, mechanical patterning, thin film transistor (TFT), IGZO, photosensitive elastomer.

## **Sintesi**

L'elettronica estensibile permette ai circuiti elettronici di espandersi e rilassarsi senza che il loro funzionamento venga. Questa nuova tecnologia possiede un grande potenziale per applicazioni in aree non convenzionali dell'elettronica, ad esempio, nel settore biomedicale. Per rendere un circuito elettrico estensibile è necessario l'utilizzo di una nuova classe di substrati, basata su polimeri altamente elastici. I circuiti estensibili che ne derivano sono sistemi ibridi, che combinano materiali funzionali, tipicamente rigidi, con substrati deformabili. Di conseguenza, la produzione di elettronica estensibile richiede nuove sfide dovute alla grande differenza tra le proprietá meccaniche dei materiali utilizzati per i substrati estensibili ed i dispositivi elettronici. Pertanto é perció necessaria un'ottimizzazione dell'architettura meccanica.

In questa tesi viene presentato un nuovo approccio per progettare e realizzare un substrato elastico che possa essere utilizzato per realizzare circuiti estensibili. La soluzione proposta è basata su un substrato estensibile con strain relief integrato. Il substrato è stato progettato integrando piattaforme rigide all'interno di una matrice elastica. Dato che le piattaforme sono significativamente più rigide rispetto alla matrice elastica che le circonda, all'allungamento del substrato, alcune zone in corrispondenza delle piattaforme rimangono non-deformate. Queste regioni rigide formano delle aree non estensibili sulla superficie superiore dell'elastomero, le quali sono idonee ad ospitare i dispositivi elettronici, impedendo che questi vengano deformati fino alla rottura. Per migliorare la distribuzione della deformazione sulla superficie superiore del substrato, sono state eseguite sia l'ottimizzazione della geometria e del layout delle piattaforme, sia la modulazione della rigidità in corrispondenza delle zone di transizione tra le regioni rigide e quelle elastiche. In questo studio, si definiscono le regole per la progettazione e la realizzazione di circuiti estensibili, basate sia sui risultati sperimentali, sia sui dati di modellazione.

Questo approccio innovativo è compatibile con le tecniche convenzionali di lavorazione a film sottile. Si dimostra l'integrazione diretta di *thin film transistors*, basati su ossido di metallo, sul substrato elastico ingegnerizzato. IGZO TFTs, interconnessi con metallizzazioni elastiche, sono stati fabbricati direttamente sulle regioni non deformabili del substrato, utilizzando tecniche di fabbricazione standard a bassa temperatura. E'stato dimostrato che IGZO TFT puó sostenere deformazioni fino al 20 % senza alcun deterioramento delle sue prestazioni elettriche né frattura meccanica.

Il substrato elastomerico, con *strain relief* integrato, offre, perció , una soluzione promettente per sviluppare circuiti estensibili affidabili e durevoli.

$E'inoltre presentato il \ photopatterning \ simultaneo, \ meccanico e \ strutturale, \ degli \ elastomeri fotosensibili.$

Fino ad oggi, gli elastomeri fotosensibili sono stati usati principalmente in soft photolithography o per modulare a localmente il livello di elasticità. Questa tesi dimostra che sia la forma sia la rigidità possono essere progettati in un'unica membrana elastomerica semplicemente con l'esposizione ai raggi UV tramite una maschera fotolitografica standard. Modulando la dose UV è possibile definire un gradiente di rigidità meccanica all'interno dell'elastomero, cosícome la topografia della superficie dello stesso. Questo processo elimina lo step di sviluppo in soluzione, tipico della fotolitografia, offrendo quindi una nuova tecnica per il microstructuring del silicone e consentendo lo sviluppo di patterns 3D per la formazione di canali microfluidici. Pertanto, il single-step photopatterning degli elastomeri fotosensibili consente un nuovo approccio per la prototipazione rapida di soft MEMS, microfluidica ed elettronica estensibile.

**Parole chiave**: elettronica estensibile, patterning meccanico, transistori a film sottile (TFT), IGZO, elastomeri fotosensibili.

# Acknowledgements

It has been a long, but fortunately not lone journey towards the degree of Ph.D. It took more than four years to complete it and a fair amount of initiative, dedication and perseverance. This would not have been possible without the support and encouragement that I received along the way from a number of great people.

I would first like to thank my advisor, Professor Stéphanie Lacour for providing me with the opportunity to be part of the Laboratory of Soft Bioelctronic Interfaces (LSBI). She patiently supported and encouraged my work throughout my PhD. From her, I learned how to think and plan independently, how to handle stressful situations. I believe these skills will continue to be tremendously helpful after my graduation from EPFL.

I would like to thank the members of the jury, who read through my manuscript and provided me with solid feedback. I thank Prof. Herbet Shea, president of the jury and head of the Microsystem for Space Technologies Laboratory at EPFL, Prof. André R. Studart head of the Complex Materials group at ETHZ and Prof. Joao Pedro Conde from the Department of Bioengineering at the University of Lisbon. A special thank goes to Prof. Jugger Brugger, head of the Microsystems Laboratory 1 at EPFL, who took the time to personally discuss some points of the manuscript.

I would like to thank Prof. Zhingang Suo and Qihan Liu from the Mechanics of Materials and Structures Group at Harvard University, for their help in thin film mechanics. Their contributions to micromechanics modelling were very helpful to complete a part of my research.

It would be unthinkable to finish any device batch without the help of the staff of the EPFL Center of MicroNanoTechnology (CMi), who I thank for their precious support with the cleanroom equipment. They have been exceptionally responsive and ready to help.

My thanks go out to present and past members of the entire LSBI for their friendliness and daily presence, which created a pleasant working environment. To Amèlie, Arthur, Hadrien, Cedric, Kate, Huge, Tom, Sandra, Frèdèric, Nicolas, Laurent, Kristie, Anna and Yi-lin, with whom I shared scientific discussions, coffee/lunch breaks and lab outings. A particular thanks go to Aaron Gerratt and Ivan Minev. The discussions with them on various aspects of the project have been helpful and inspiring. I would also like to thank Tero Kulmala. Even if for a short period, it was great working together on the transistors. Many thanks go to Swati

Gupta.In the last year, she has always been willing to discuss the experimental results and answer my questions. A special thank goes to Alba de Luca, for her sense of humor and the emotional support she gave me in the final part of my PhD. More than a colleague she has been a friend.

Furthermore, I would like to thank Marco, Pietro ed Enrica for having played at my jury members asking me a lot of interesting questions and giving me important feedbacks. A special thank goes to Marco Letizia, who fully support me over these four years. I am truly grateful for sharing his experience and his time with me, for soothing away many anxieties in my graduate and private life and to be such a great friend.

I would also like to thank all my friends who made my life outside of EPFL extraordinary, full of great days and nights in and around Lausanne. A special thank go to Alberto for being more than just flatmates but also a friend; to Giulia for her delicious dinners; to Marta for her guidance over these years; to Carlo for his enthusiasm, his support and the interesting social and political discussions; to Erica for the runs, the hiking, the chats and the rest... I would also like to thanks the fellows from ITALaus, with whom we organized so many successful events, and to all the team mates of Sfigatos, with whom we had such a great time playing and winning the EPFL volleyball tournament.

Thanks to my "evergreen" friends from Minervino: Ciccio, Stefania, Salvatore, Antonio, Sara, Rosalba e Carmine, that made me laugh almost everyday over these years, even at hundreds km of distance. I also would like to thank my historical friends from Milan: Giulia, Andrea Gabriele, Patato and Federica for being always part of my life.

My greatest thanks goes to my family. To my parents for their unconditional support and trust they have put in me. I would like to dedicate this work to them. To my sister, who was always there for me, for her priceless understanding, advices and love. To Giosué for cheering me up with his crazy stories and his delightful company.

And finally, I would like to thank my beloved Alessio, for his support, patience and encouragement he gave me in the last part of this intense experience. Thank you Ale for being beside me because you are able to bring out the best in me.

# **Table of Contents**

| Li | List of Figures xv |         |                                                          |   |     |

|----|--------------------|---------|----------------------------------------------------------|---|-----|

| Li | st of              | Tables  |                                                          | X | vii |

| 1  | Intro              | oductio | on                                                       |   | 1   |

|    | 1.1                | Motiv   | ration                                                   |   | 1   |

|    |                    | 1.1.1   | Stretchable electronics                                  |   | 2   |

|    |                    | 1.1.2   | TFTs on Stretchable Substrates                           |   | 7   |

|    | 1.2                | Objec   | etives                                                   |   | 9   |

|    | 1.3                | Thesis  | s outline                                                |   | 10  |

|    | Refe               | erences |                                                          |   | 11  |

| 2  | Eng                | ineered | Stretchable Substrate with Embedded Strain Relief        |   | 17  |

|    | 2.1                | Pixell  | ated Layout                                              |   | 18  |

|    |                    | 2.1.1   | Mechanics                                                |   | 19  |

|    |                    | 2.1.2   | Substrate Materials Selection                            |   | 24  |

|    |                    | 2.1.3   | Mechanical Requirements                                  |   | 26  |

|    | 2.2                | Stiff F | Platform Geometry Optimization                           |   | 28  |

|    |                    | 2.2.1   | Finite Element Modeling                                  |   | 28  |

|    |                    | 2.2.2   | Experimental: Materials and Methods                      |   | 32  |

|    |                    | 2.2.3   | Experimental Results and Discussion                      |   | 35  |

|    |                    | 2.2.4   | Conclusions                                              |   | 41  |

|    | 2.3                | Greys   | cale-photolitography for Top Surface Strain Optimization |   | 42  |

|    |                    | 2.3.1   | Greyscale photolitography                                |   | 42  |

|    |                    | 2.3.2   | Materials and methods                                    |   | 43  |

|    |                    | 2.3.3   | Results and Discussion                                   |   | 48  |

|    |                    | 2.3.4   | Conclusions                                              |   | 52  |

|    | 2.4                | Optin   | nized Engineered Substrate Layout                        |   | 53  |

|    |                    | 2.4.1   | Materials and Methods                                    |   | 53  |

|    |                    | 2.4.2   | Results and Discussion                                   |   | 54  |

Table of Contents

|   |      | 2.4.3   | Conclusions                                                         | 56  |

|---|------|---------|---------------------------------------------------------------------|-----|

|   | 2.5  | Concl   | usions                                                              | 57  |

|   | Refe | erences |                                                                     | 59  |

| 3 | Stre | tchable | e metal oxide thin-film transistor                                  | 63  |

|   | 3.1  | Introd  | luction                                                             | 64  |

|   |      | 3.1.1   | Thin film transistor                                                | 65  |

|   |      | 3.1.2   | Consideration for deposition and patterning room temperature TFTs   |     |

|   |      |         | materials                                                           | 68  |

|   |      | 3.1.3   | Stretchable metal oxide TFTs                                        | 73  |

|   | 3.2  | Mater   | ials and methods                                                    | 74  |

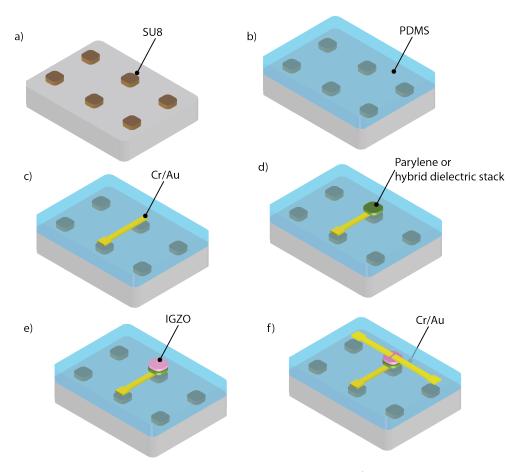

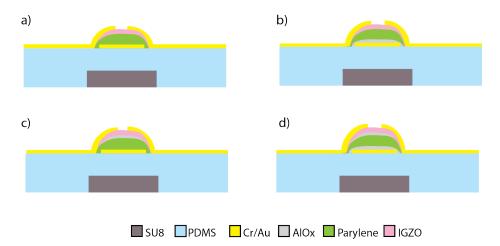

|   |      | 3.2.1   | Fabrication Process                                                 | 74  |

|   |      | 3.2.2   | Dielectric structure                                                | 75  |

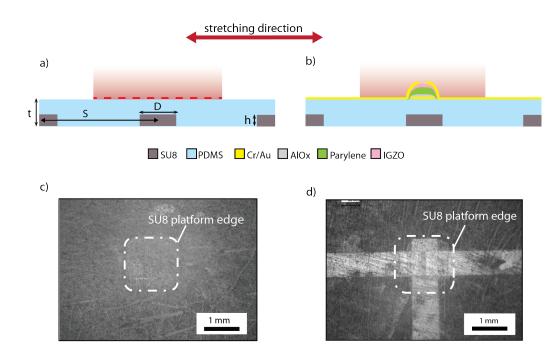

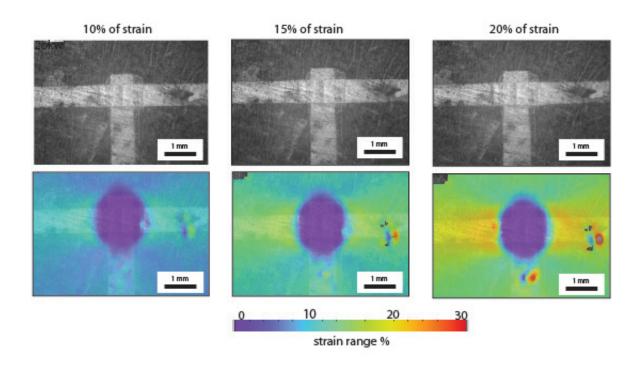

|   |      | 3.2.3   | Characterization of substrate mechanics                             | 76  |

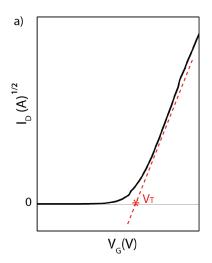

|   |      | 3.2.4   | TFT Electrical characterization                                     | 77  |

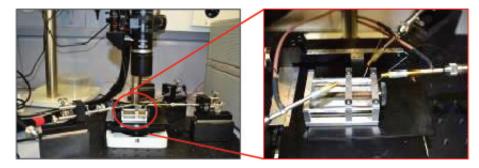

|   |      | 3.2.5   | TFT Electro-mechanical characterization                             | 79  |

|   | 3.3  | Result  | ts and discussions                                                  | 79  |

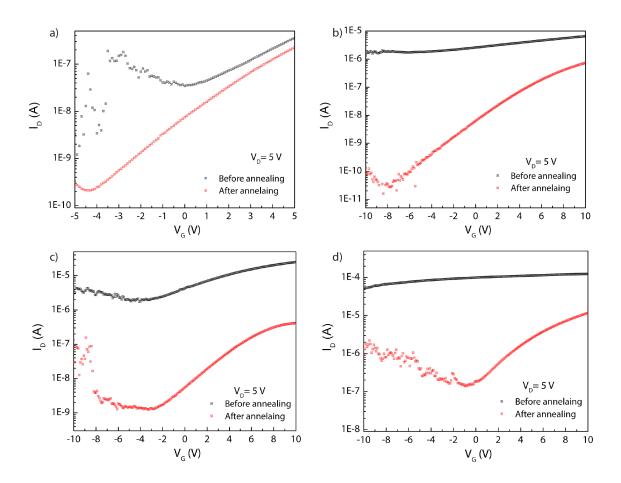

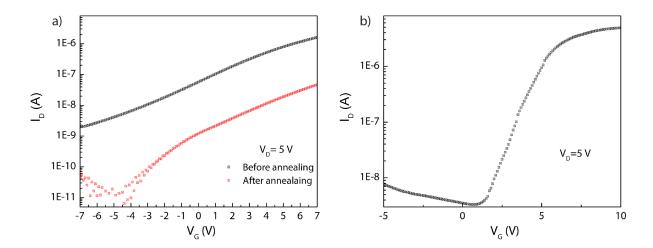

|   |      | 3.3.1   | Dielectric film(s) structure                                        | 80  |

|   |      | 3.3.2   | Substrate mechanical characterization                               | 83  |

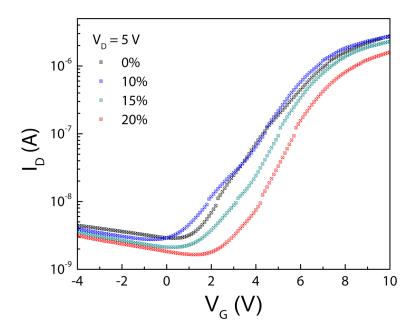

|   |      | 3.3.3   | TFT electro-mechanical characterization                             | 84  |

|   | 3.4  | Concl   | usions                                                              | 88  |

|   | Refe | erences |                                                                     | 90  |

|   |      |         |                                                                     |     |

| 4 |      |         | photopatterning of elastic modulus and structures in photosensitive |     |

|   |      |         | stomers                                                             | 97  |

|   | 4.1  | Introd  | luction                                                             |     |

|   |      | 4.1.1   | PDMS Microstructuirng                                               |     |

|   |      | 4.1.2   | Positive P-PDMS elasticity photopatterning                          |     |

|   |      | 4.1.3   | Single-step photopatterning                                         | 102 |

|   | 4.2  | Mater   | ials and methods                                                    | 102 |

|   |      | 4.2.1   | P-PDMS preparation                                                  |     |

|   |      | 4.2.2   | Young's modulus characterization                                    | 104 |

|   | 4.3  | Result  | ts and discussions                                                  | 106 |

|   |      | 4.3.1   | Young's modulus characterization                                    | 106 |

|   |      | 4.3.2   | Top surface microstructuring                                        | 107 |

|   |      | 4.3.3   | Stiffness characterization                                          | 110 |

|   |      | 4.3.4   | Microchannels                                                       | 112 |

Table of Contents xi

|     | 4.4 Conclusion         |     |

|-----|------------------------|-----|

| 5   | Conclusion and outlook | 119 |

|     | 5.1 Conclusion         | 119 |

|     | 5.2 Outlook            | 121 |

| Lis | ist of Acronyms        | 124 |

| Sc  | cientific achievements | 125 |

| C.  | urriculum Vitae        | 126 |

# **List of Figures**

| Four examples of stretchable electronics are presented                                     | 3                                                                                                  |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| The wide range of Young's modulus of different types of materials used for                 |                                                                                                    |

| stretchable electronics                                                                    | 4                                                                                                  |

| Stress-strain behavior of brittle, ductile and elastic materials                           | 4                                                                                                  |

| Concept of stretchable electronics with wavy and open mesh layout of a 100                 |                                                                                                    |

| nm thick silicon membrane                                                                  | 5                                                                                                  |

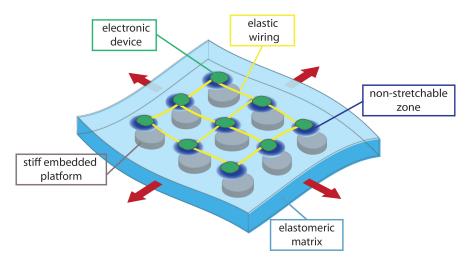

| Concept of pixellated architecture for stretchable electronics                             | 5                                                                                                  |

| Different relief patterns of stretchable thin gold interconnects                           | 6                                                                                                  |

| Thin gold film deposited onto PDMS substrate: the gold ligaments percolate                 |                                                                                                    |

| between the micron-size microcracks                                                        | 7                                                                                                  |

| Thin film transistor fabricated directly onto elastomeric substrate                        | 8                                                                                                  |

| Concept of pixellated architecture for stretchable electronic                              | 18                                                                                                 |

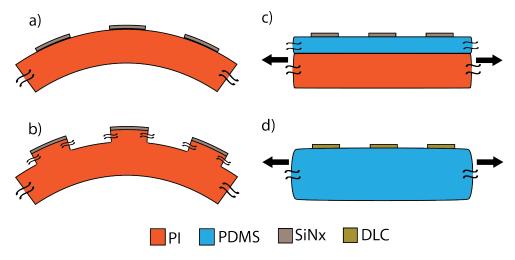

| Schematic of different substrate structures with thin superficial stiff islands $$ . $$    | 20                                                                                                 |

| Schematic of different substrate structures with embedded local stiffness $\ .\ .\ .$ .    | 22                                                                                                 |

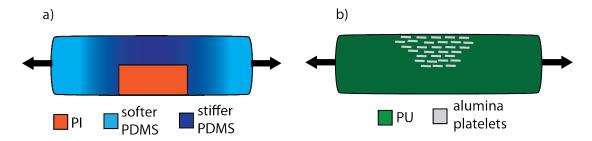

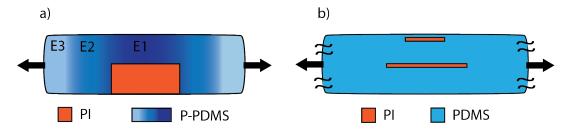

| Schematic of different substrate structures with Smooth strain gradient across             |                                                                                                    |

| interconnects                                                                              | 23                                                                                                 |

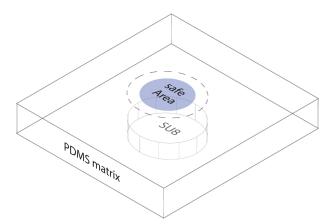

| Engineered substrate schematic                                                             | 26                                                                                                 |

| Safe area schematic                                                                        | 27                                                                                                 |

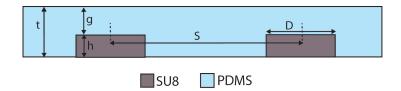

| Schematic cross sectional view of the substrate and geometrical parameters $$ . $$         | 28                                                                                                 |

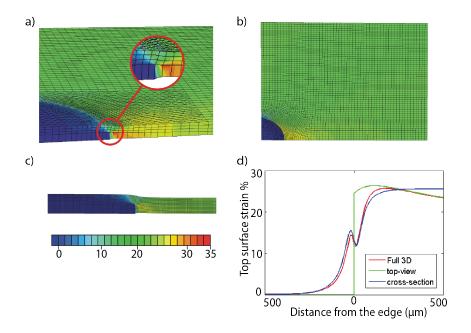

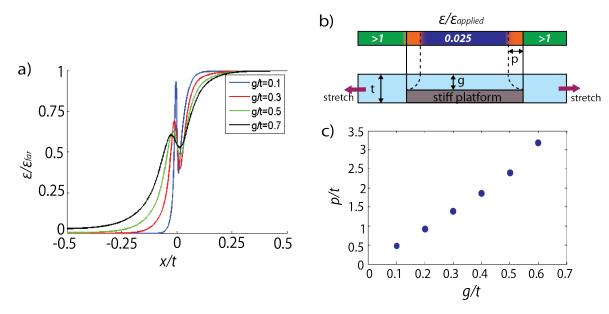

| Computed strain distribution trough FEM of the engineered substarte $\dots$                | 29                                                                                                 |

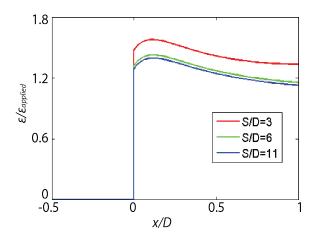

| $f_{global}$ surface strain profile calculations at different $S/D$ ratios, when $g/t=0.5$ |                                                                                                    |

| ratio and $\varepsilon_{applied} = 20\%$                                                   | 31                                                                                                 |

| Local-scale                                                                                | 32                                                                                                 |

| Global and local scale design                                                              | 33                                                                                                 |

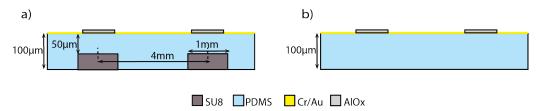

| Cross sectional view of brittle 150 nm thick $AlO_x$ disks and interconnected with         |                                                                                                    |

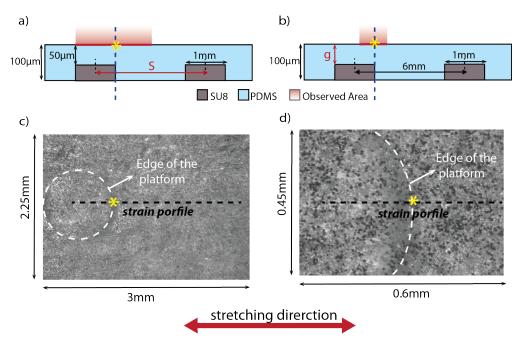

| elastic $Au$ wiring                                                                        | 34                                                                                                 |

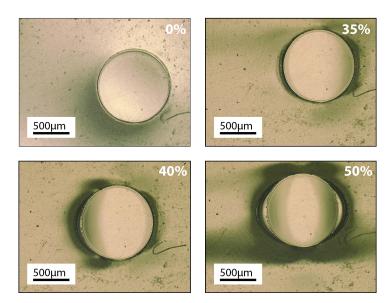

| Delamination test: optical images of the bottom surface of the engineered sub-             |                                                                                                    |

| strate taken at different applied strain 0%, 35%, 40% and 50% $$                           | 36                                                                                                 |

|                                                                                            | The wide range of Young's modulus of different types of materials used for stretchable electronics |

xiv List of Figures

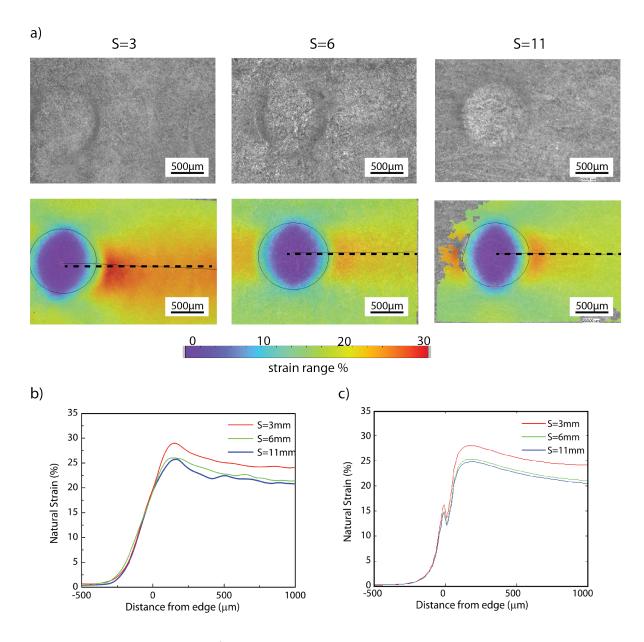

| 2.14 | Global strain                                                                        |

|------|--------------------------------------------------------------------------------------|

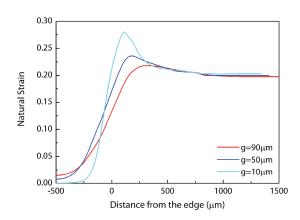

| 2.15 | Experimental strain profile of the engineered substrate with different $g$           |

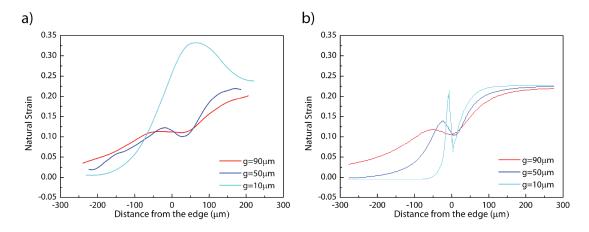

| 2.16 | Local strain:strain profile of engineered substrate                                  |

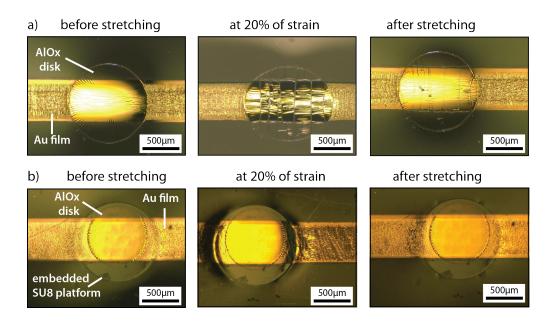

| 2.17 | Stretchable alumina disks on engineered elastomeric substrate                        |

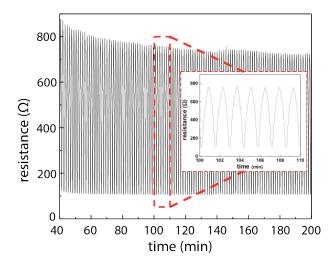

| 2.18 | Electrical resistance as a function of time                                          |

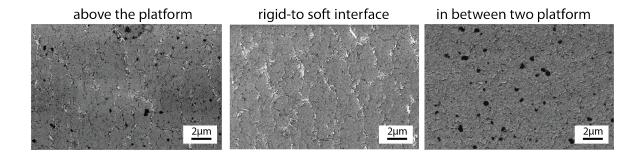

| 2.19 | EM picture of the microcracked thin gold interconnect                                |

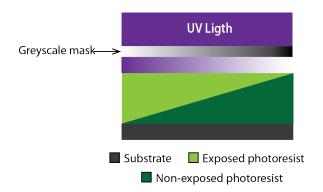

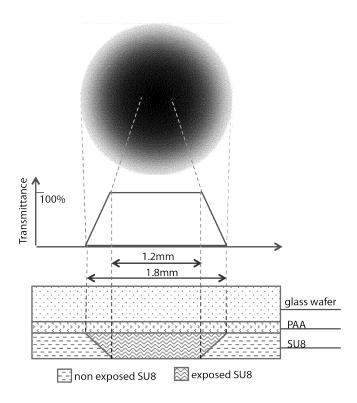

| 2.20 | The gray-scale optical mask controls the UV light intensity across the wafer         |

|      | using a single exposur                                                               |

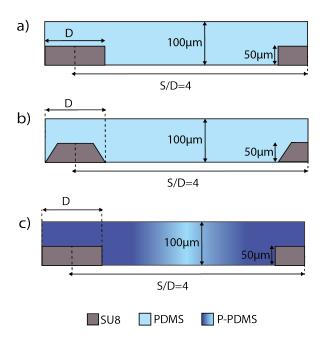

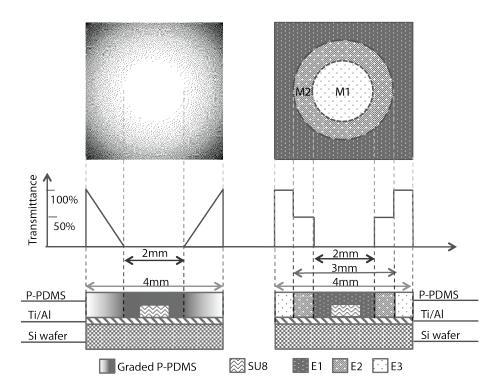

| 2.21 | Schematic cross sections of three different engineered substrates                    |

| 2.22 | Schematic vertical patterning of SU8                                                 |

| 2.23 | Schematic of stiffness patterning of P-PDMS                                          |

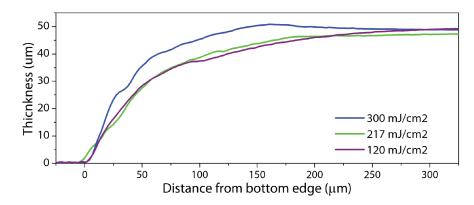

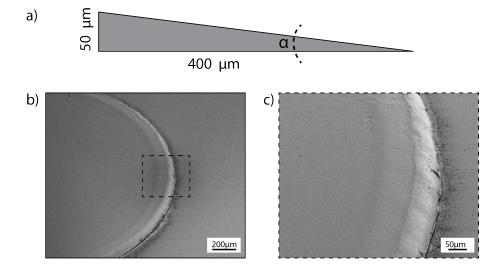

| 2.24 | Sloped side-wall profiles of truncated SU8 cones platforms patterned with pix-       |

|      | elated greyscale mask at different exposure energies                                 |

| 2.25 | Side-wall edge undercut                                                              |

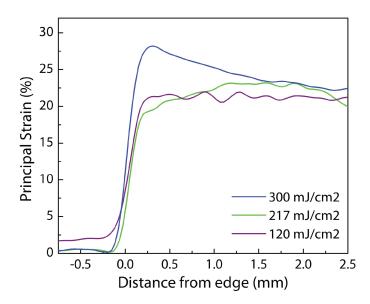

| 2.26 | Strain profiles taken along the x-axis from the center of the SU8 platform and       |

|      | as function of the total UV exposure energy                                          |

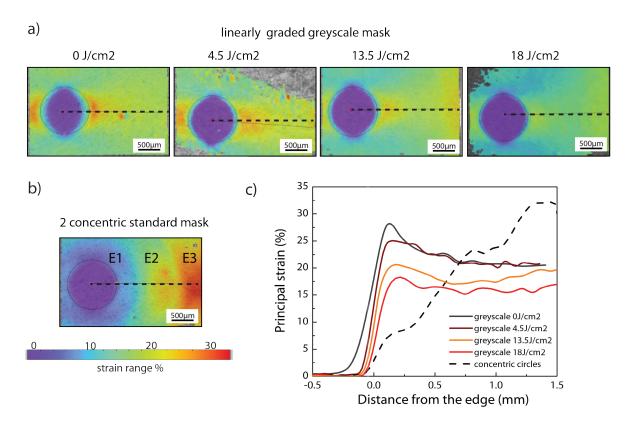

| 2.27 | Surface strain experimental measurement                                              |

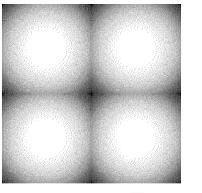

| 2.28 | Greyscale mask pattern (inverted) used to linearly patter the P-PDMS around          |

|      | 4 platforms                                                                          |

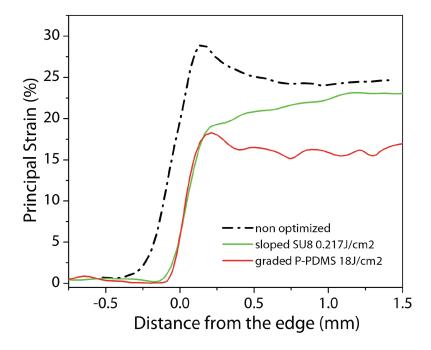

| 2.29 | Strain profiles for each of the three substrate designs                              |

| 2.30 | Engineered stretchable substrates with optimized layout                              |

| 2.31 | Surface strain experimental measurement of stretched engineered substrates $$ . $$ . |

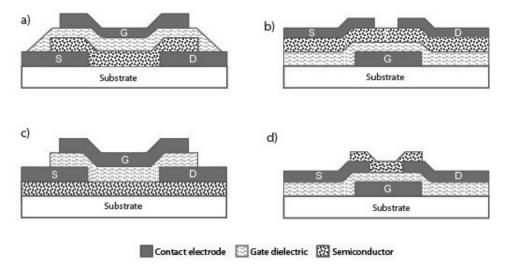

| 3.1  | Four thin-film transistor structures                                                 |

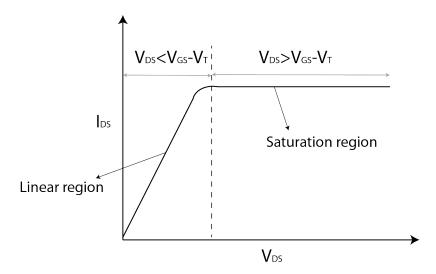

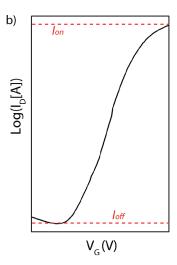

| 3.2  | Relation of drain-source current versus voltage                                      |

| 3.3  | Schematic illustration of a stretchable a-IGZO TFT                                   |

| 3.4  | Schematic cross section of the four gate dielectric structure                        |

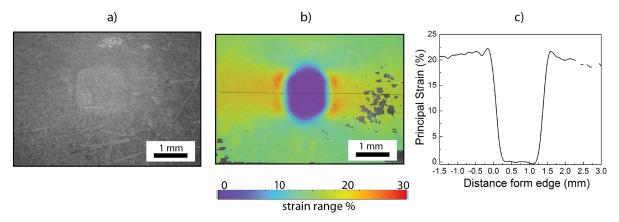

| 3.5  | Top surface strain characterization of the two sets of samples                       |

| 3.6  | TFT performance parameters extrapolation                                             |

| 3.7  | TFT electromechanical characterization setup                                         |

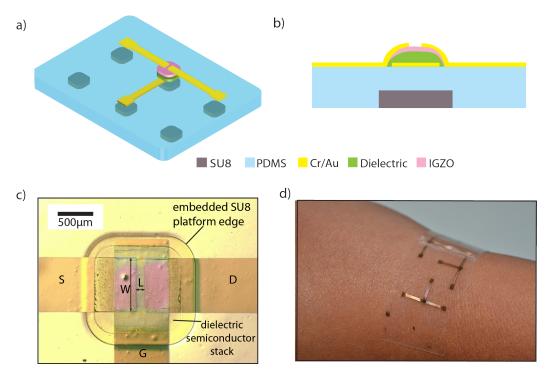

| 3.8  | IGZO TFT fabricated on top of the engineered substrate                               |

| 3.9  | Transfer characteristic of IGZO TFTs before and after annealing $\ \ldots \ \ldots$  |

| 3.10 | Top surface strain distribution on the engineered substrate without the TFT stack    |

| 3.11 | Top surface strain distribution on the engineered substrate with the TFT stack       |

|      | Transfer characteristic of soft a-IGZO TFT                                           |

List of Figures xv

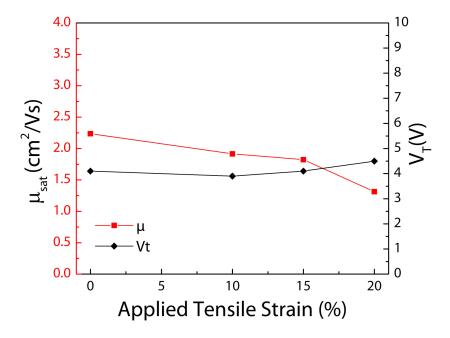

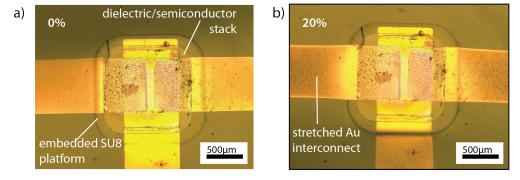

| 3.13        | Transfer characteristics under stretching recorded at $0\%$ , $10\%,15\%$ and $20\%$                                                                       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | of strain, when $V_{DS} = 5 \text{ V.} \dots 86$                                                                                                           |

| 3.14        | Saturation mobility, on the left, and threshold voltage, on the right, as function                                                                         |

|             | of the applied strain                                                                                                                                      |

| 3.15        | Optical picture of the free standing TFT at: (a) $0\%$ of strain and (b) $20\%$ of                                                                         |

|             | strain                                                                                                                                                     |

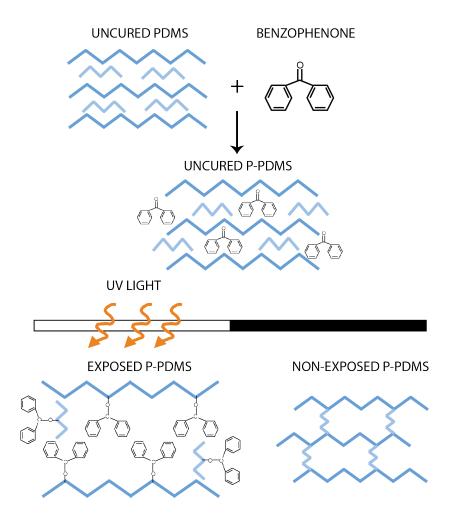

| 4.1         | Schematic representation of positive P-PDMS under UV light exposure 100                                                                                    |

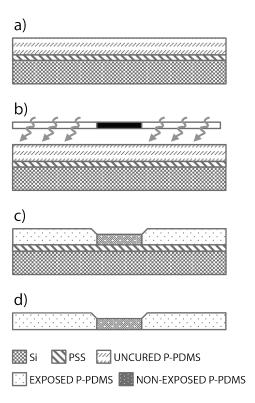

| 4.2         | Schematic diagram showing the different step of P-PDMS preparatio 103                                                                                      |

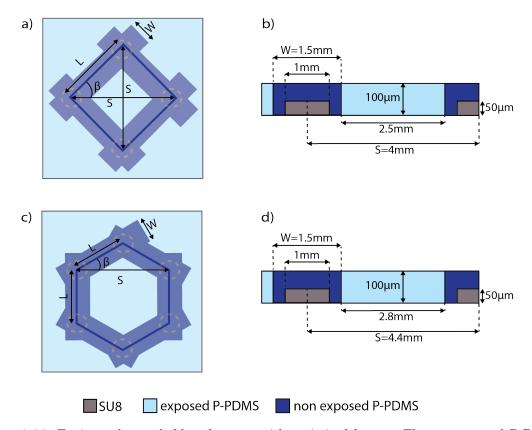

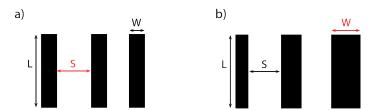

| 4.3         | Schematic of the stripe non exposed patterns                                                                                                               |

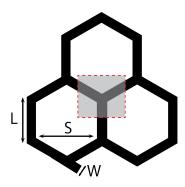

| 4.4         | Schematic of the hexagonal non-exposed pattern L=5 mm, W= 1 mm, S = ;                                                                                      |

|             | the red zone highlights the selected area for strain mapping                                                                                               |

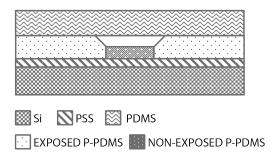

| 4.5         | Schematic cross-section of a P-PDMS microchannel                                                                                                           |

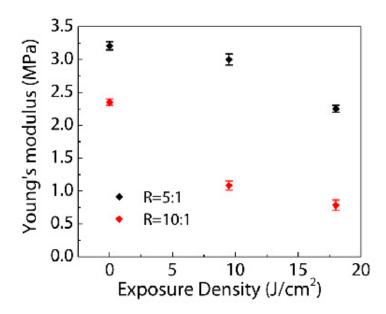

| 4.6         | Tensile Young's modulus of P-PDMS as a function of UV exposure density for                                                                                 |

|             | two initial prepolymer:<br>curing agent ratio $R$ (10:1 and 5:1)                                                                                           |

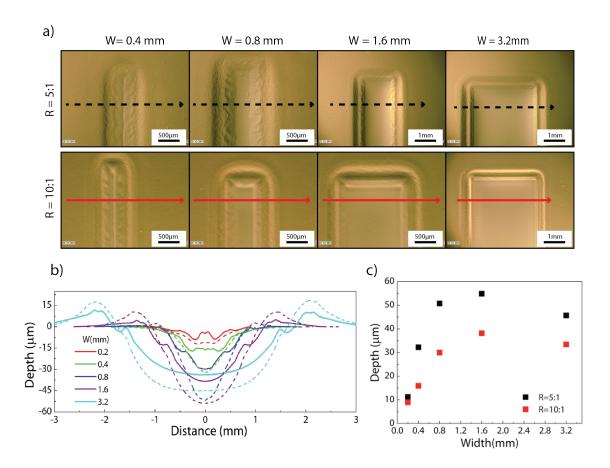

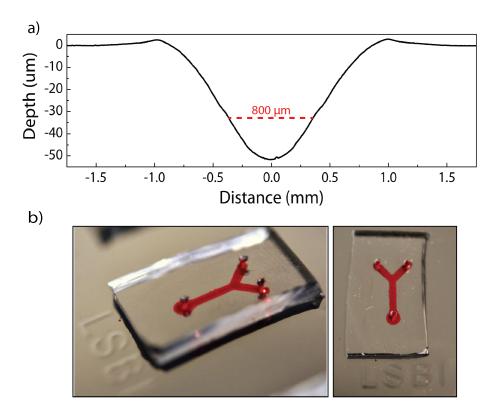

| 4.7         | Channel profiles as function of the width W $\dots \dots $ |

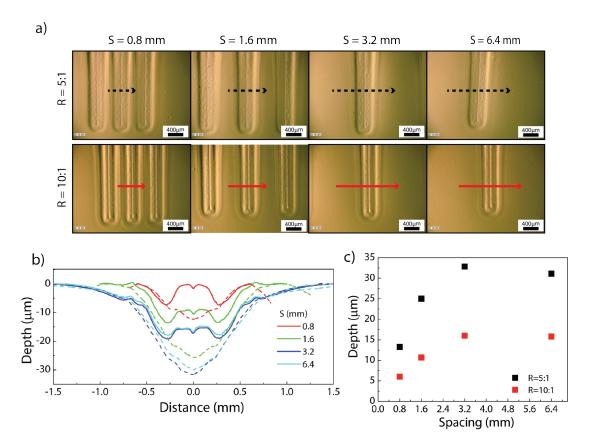

| 4.8         | Channel profiles as function of the spacing S                                                                                                              |

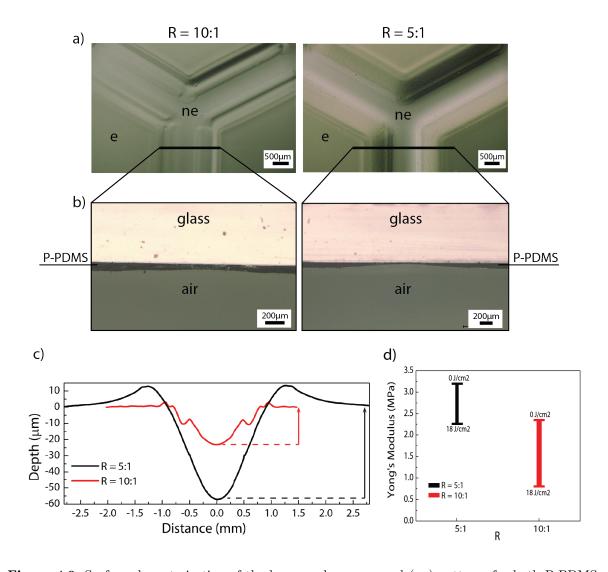

| 4.9         | Surface characterization of the hexagonal non-exposed $(ne)$ patterns 110                                                                                  |

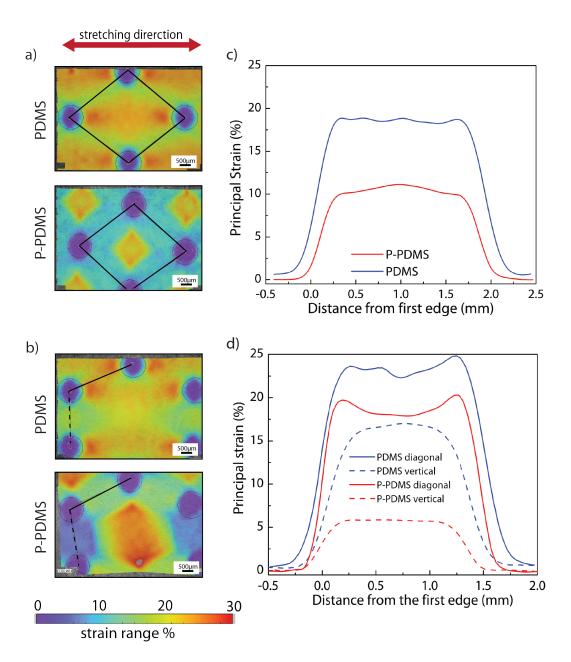

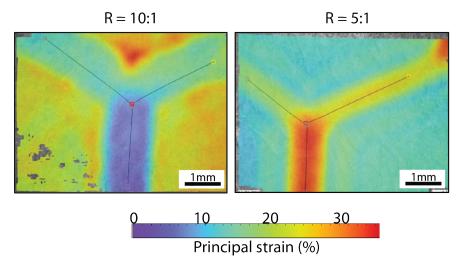

| 4.10        | Surface strain maps (principal strain) for both P-PDMS ratios                                                                                              |

| <i>4</i> 11 | Fabrication of microfluidic channel                                                                                                                        |

# **List of Tables**

| 2.1 | Young's modulus of substrate materials considered in Fig. 2.2                                              | 21 |

|-----|------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Thermo-mechanical properties of engineered substrate materials, where E is                                 |    |

|     | the Youn's modulus, CTE is the coefficient of thermal expansion and $\lambda$ is the thermal conductivity. | 25 |

| 3.1 | Parylene-C properties [62]                                                                                 | 71 |

## 1 Introduction

This chapter gives the motivation and a brief overview on the state of the art on stretchable electronics. The objectives and the outline of this thesis are separately described.

#### 1.1 Motivation

Stretchable electronics are integrated circuitry that can reversibly expand and relax while maintaining their functionality. Stretchability ensures the electronic circuits can conform curved and complex shaped objects and comply to the elastic surfaces that expand and relax. Stretchable devices provide interesting opportunities, particularly in biomedical applications, where shape adaptability is a highly desirable feature, enabling for example skin like circuits for health care monitoring.

These applications are hardly achievable with conventional planar, rigid and brittle siliconbased electronic circuits. Therefore, there is currently a strong tendency integrate circuits on elastic carriers. While the semiconducting devices do not stretch, substrate and electrical interconnects take up the applied deformation.

Stretchability can be introduced into electronic systems by the use of suitable stretchable substrate materials, hosting rigid electronic components interconnected with elastic wiring. The resulting stretchable systems are therefore hybrids of soft and hard materials, which mechanical and thermal properties differ by several orders of magnitude. The realization of stretchable electronics is still a challenge since the integration of brittle and fragile device materials with elastomeric substrates is limited among others by two main critical issues: (i) electronic device materials are brittle and typically fracture at 1-2% tensile strain, and (ii) maximum working temperature imposed by the soft substrate is limited to  $< 150^{\circ}$ C.

In order to integrate such disparate materials, it is essential to carefully select the device materials and associated processing techniques, and derive reliable circuits's mechanical architectures ensuring the most fragile elements are strain-free.

#### 1.1.1 Stretchable electronics

Conventional electronic circuits are constructed on planar, rigid substrates, (e.g. silicon). Although they exhibit remarkable electronic performance and stability, they possess poor mechanical robustness. They may face limitations when placed in environments that are dominated by stretchable or three-dimensional structures, including those within the human body. Recent studies have led to the development of a new class of electronics with improved mechanical features. A first way to convey mechanical compliance to electronic circuit was the development of flexible electronics, which enables electronic devices to be bendable, rollable and even wearable. Electronics could be made flexible by patterning thin film device materials onto freestanding flexible substrate [1]. Fabrication of flexible electronics is nowadays well established in the research and the industrial communities.

However, the ability to be bent is not enough to satisfy compliance needs, for devices that intimately integrate with the human body [2–7]. Stretchable electronics is a relatively new field, emerging from flexible electronics. Imagine an electronic skin, that senses like a real skin and needs to be applied conformally on a prosthetic arm. As the arm moves, the system is subjected to various levels of strain. For example, the skin wrapped over the elbow stretchs and relaxes many times to  $\sim 15\%$  strain [8]. This requirement is impossible to meet with designs that offer only bendability. Stretchability demands that the circuits have the capacity to absorb large levels of strain (>1%) and often multiaxial deformations without fracture or significant degradation in their electronic properties.

#### **Applications**

Stretchable electronics offer exciting opportunities in the biomedical field.

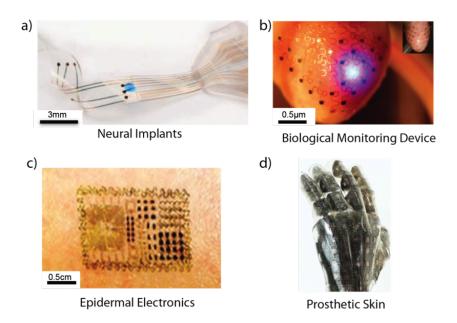

Stretchable electronics would allow electronic circuits to be "perfectly" attached to any organ in the body and monitor or assist its functions for health monitoring or treatment. Stretchable microelectrode arrays (SMEA) that conform complex surfaces or operate in mechanically active environments have been produced [9-12]. Figure 1 highlights some of the recent developments in stretchable electronics for body interfaces. Figure 1.1a displays a stretchable neural implants, called electronic dura matter, because its mechanical properties match those of natural dura matter. The proposed solution embeds interconnects, electrodes and chemotrode, and was implemented to deliver electrochemical spinal neuromodulation that restored locomotion after paralyzing spinal cord injury. [6] . Stretchable electronics have also been used for biological monitoring devices. Deformable arrays of multifunctional sensors and electronic components were developed to monitor the function of the beating heart (Fig. 1.1b) [13, 14]. Also, tattoo-like epidermal electronic systems, extremely thin and perfectly conformable, were mounted onto the surface of the skin to record electrical activity produced by the heart, brain, and skeletal muscles (Fig. 1.1c) [15]. Electronic eye which is able adjust thickness of lens was developed [16, 17]. Moreover, stretchable sensing systems which mimic the mechanical properties and tactile and temperature sensing properties of human skin

Section 1.1: Motivation 3

Figure 1.1: Four examples of stretchable electronics are presented: a) stretchable neural implants embedding electrods and chemotrode for spinal cord stimulation, e-dura, the image is adopted from Minev et al. [6]; b) 3D deformable membrane for spatiotemporal cardiac measurements and stimulation across the entire epicardium, the image is adopted from Xu et al. [13]; c) epidermal electronic for electrophysiological characterizatelectronic ion of human skin, the image is taken from Kim et al. [15]; d) electronic artificial skin or E-skin, where organic devices are used to read out pressure images from the sensors, the image is taken from Someya et al. [24]

have been attracting significant interest, as shown in figure 1.1d [8, 18–22]. Electronic skin (e-skin) are crucial property for future generation robots or to produce prosthetic limbs that would "feel "like the natural limb [23, 24].

#### **Fabrication Strategies**

If stretchability of electronic circuits opens to a new class of applications, an important associated challenge is the manufacturing of stretchable electronic devices.

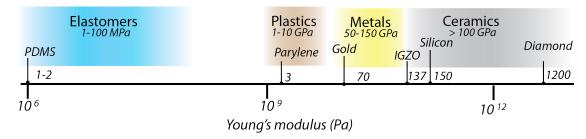

Stretchable electronics are hybrid systems, combining mechanically disparate, soft and hard, materials within a single structure [25]. Figure 1.2 illustrate the rage of Young's modulus of the materials employed in stretchable electronics. In most cases, the carrier substrate is an elastic or viscoelastic polymer, e.g., silicones or polyurethanes, characterized by low elastic modulus (E< 10 MPa), large ductility (elongation at break> 100%), Poisson's ratio  $\nu$  close to 0.5, and thickness in the 10  $\mu m$  to 1 mm range. By contrast, electronic device materials, used either in thin-film or thinned forms, are stiff (elastic modulus in the GPa range), brittle

**Figure 1.2:** The wide range of Young's modulus of different types of materials used for stretchable electronics.

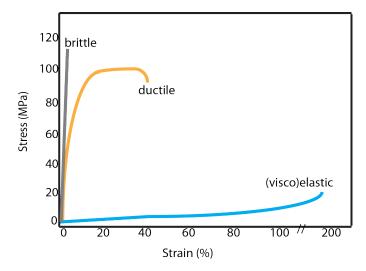

Figure 1.3: Stress-strain behavior of brittle, ductile and elastic materials.

(fracture strain < 5%), and thin (thickness $< 1\mu m$ ) [26]. Figure 1.3 illustrates three types of stress-strain behavior of respectively a brittle (e.g. Silicon), ductile (e.g. metals) and elastic (e.g. silicone) materials. The integration of these materials onto elastic substrates to implement stretchable devices is a primary challenge and requires a carefully mechanical design.

To overcome this mechanical mismatch, different strategies have been proposed, where mechanics meets geometry to enable large, reversible deformation of the structure.

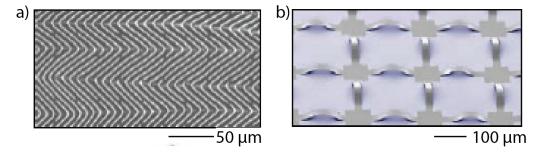

A first approach relies on a wavy layout. Thin-film devices are prepared on sacrificial substrate and then transferred on a prestretch elastomer. Upon releasing of the strain, the films relax into a strain-induced wavy geometry (Fig.1.4a) that enables the stretchable system to sustain strain to up the initial prestretch [29–32]. However, this technique limits the stretchability of the circuit to a predefined direction.

A related strategy is to pattern the substrate to enable the film to flex out of the plane of the strain. Instead of adhering completely on top of the elastomeric substrate, the circuits Section 1.1: Motivation 5

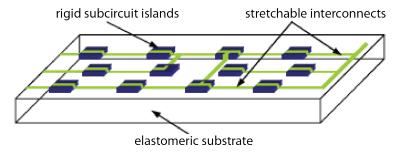

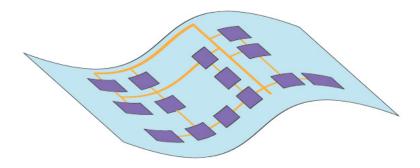

are patterned in an open mesh layouts and locally bonded to the prestretched stretchable matrix, as shown in figure 1.4b. When the pre-strain is released the "not-attached" areas form out-of-plane but controlled buckling that can more effectively accommodate macroscopic strain [16, 33, 34]. The functional devices are deposited on non-wavy (non-stretchable) islands to ensure reliable electromechanical performance. The out-of-plane buckling structure interconnects the functional islands and accommodates the deformation. "pick-and-place" steps to transfer the devices onto the pre-strained substrate are required to achieve such complex layouts. This open mesh layout is based on the pixellated architecture, commonly used for stretchable electronics. Figure 1.5 shows a schematic of the pixellated macroscopic structure [35–37]. Here, the "pixels" or nodes are made of hard materials for device placement and distributed on the surface of an elastomeric substrate and interconnected with elastic wiring. When the stretchable system is deformed, the soft elastomeric substrate, together with the elastic interconnects, support the mechanically rigid nodes and isolates them from the applied macroscopic strain. This prevents fragile device materials from exposure to deformation exceeding their fracture strain, while ensuring the circuit deforms.

Figure 1.4: Concept of stretchable electronics with wavy and open mesh layout of a 100 nm thick silicon membrane: a) stretchable thin silicon membrane configured in a wavy shape and bonded to a piece of rubber; b) stretchable thin silicon membrane patterned into a mesh geometry and geometry and bonded to a rubber substrate only at square pads located between arc shaped bridge structures. The images are adopted from Rogers et al. [27].

Figure 1.5: Concept of pixellated architecture for stretchable electronics. Rigid subcircuit islands are distributed on an elastomeric substrate. The cells are interconnected with stretchable metallization. The image is adopted from Lacour et al. [28].

#### Stretchable Interconnects

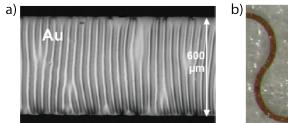

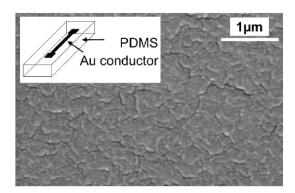

Since the stretchable conductors have to withstand most of the deformations, a reliable design is essential to avoid losing electrical performance and structural integrity. Different materials have been employed to produce highly stretchable interconnects, such as conductive polymer composites [41–43], carbon based materials [31, 44–46], liquid metal [47], metal nanowires [48, 49], nanoparticles [50, 51] and thin metal films [38, 39, 52]. Among these, stretchable metallization based on thin gold films on rubbery substrate has received significant interest and research efforts. It was demonstrated that thin gold films well attached on polymeric substrates are more resistant to tensile strain than free standing films, since strain is delocalized over the whole area [53, 54]. Combining this ability with proper strain relief patterns produces highly stretchable metallization bonded to elastomeric substrates. Technologies based on wavy layout [38, 55] and coplanar [39, 56], or off-plane [40] meandering structures, have been adopted to provide strain relief within the interconnects. Figure 1.6 gives an examples of the three different strategies. However, they are difficult to fabricate, requiring complicated layout and process flow.

In 2005 by Lacour et al.proposed an alternative strategies who ere the strain relief patterns are embedded in thin metal film omitting the need of complex layouts [57]. The authors demonstrated that thin gold films, deposited by evaporation onto silicone substrates, support an unique micro-cracked topography (Fig. 1.7) that allows films to stretch up to and beyond 20% tensile strain, for repeated cycles, without electrical failure [58]. The strain-induced cracks are formed in the continuous thin film of the deposited metal while maintaining a

Figure 1.6: Different relief patterns of stretchable thin gold interconnects. a) wavy layout: built-in waves are observed in gold conductor patterned on relaxed PDMS. The wavelength is  $25\mu m$ , the image is adopted from Lacour et al. [38]. b) coplanar meandering structure: horseshoe metal interconnects embedded into PDMS matrix, the image is adopted from Gonzalez et al. [39]. c) off-plane meandering structure: noncoplanar conductors bridges with serpentine layouts, the image is adopted form Kim et al. [40].

Section 1.1: Motivation 7

**Figure 1.7:** Thin gold film deposited onto PDMS substrate: the gold ligaments percolate between the micron-size microcracks. The inset illustrates the schematic of a gold conductor on PDMS. The image is adopted from Lacour et al. [57].

percolating pathway which ensure the reversible elasticity of the gold film. Rational control of the crack formation process can improve the stretchability to values as large as 100% in gold films [59, 60]. Microcracked thin gold film, thus offer a simple and straightforward method for stretchable interconnects, forgoing complex layout and fabrication process.

#### 1.1.2 TFTs on Stretchable Substrates

Beside stretchable electrical interconnections, thin film transistors (TFTs) are the basic element for electronic circuits. Several advanced stretchable organic and inorganic TFTs with elastic conductors, prepared using pixellated design, have recently been demonstrated [2, 4, 18].

One of the common fabrication approaches to produce stretchable electronics is based on the transfer techniques, where the soft elastomeric polymer is introduced only after all the high-temperature fabrication steps have been completed. Here active device materials are first deposited and patterned on a rigid or plastic substrate, using standard high-temperature fabrication steps. The substrate is then machined into a thin mesh defining the rigid nodes, and subsequently transferred onto the elastic matrix [9, 13, 16, 30, 52, 61]. These approaches allow for stretchable circuits with good electronic performance and stability, however, it requires complex, multi-step, multi-carrier processing.

An alternative way to implement stretchable circuits is to fabricate the thin film devices directly on the elastic substrates by planar and standard cleanroom methods. Fabricating functional devices directly on elastomeric substrates brings unique challenges such as compatibility with microfabrication process, patterning resolution and reproducibility. In particular, two technological challenges need to be overcome: (i) the limitation on the maximum process temperature due to the polymeric nature of the substrate, and (ii) the chemical stability of the substrate. Organic and inorganic TFTs, using respectively pentacene and amorphous silicon

drain

island

and scalability.

Figure 1.8: Thin film transistor fabricated directly onto elastomeric substrate: a) pentacene TFT onto engineered PDMS substrate, the image is adopted from Graz et al. [37]; b) amorphous silicon TFT onto PDMS substrate with rigid  $SiN_x$  subcircuit islands, the image is adopted from Lacour et al. [28]

as active layer (Fig. 1.8), were directly manufactured onto silicone substrates using only low temperature deposition techniques and dry patterning process are required. Both kinds of transistors performed similarly to their counterparts on, flexible, plastic foil, [28, 37]. Despite the limitations imposed by the polymeric substrate, this fabrication technique based on direct integration of micro-electronic devices onto elastomeric substrates enables to simplify the manufacturing process and devices layout, thereby, promises low cost manufacturing

### 1.2 Objectives

The aim of this project is to develop a planar but mechanically engineered heterogeneous elastic substrate compatible with direct fabrication of thin film devices.

A first objective is to develop a simple and robust approach for designing and manufacturing versatile elastic substrates for stretchable electronic applications.

Engineered substrate with built-in strain relief is proposed as compliant yet reliable substrate to host stretchable circuitry. First the geometry and density of the embedded platforms are optimized to maximize the stiff region and minimize the far field strain. A simulation by finite element method (FEM) predicts the mechanical behavior of the engineered substrates. Associated design rules based on experimental as well as modeling data are presented. Then greyscale photolitography is implemented to smooth out the strain concentration at the stiff-to-soft interface. Last, new geometrical layout is presented to further decrease the strain along the interconnects. Compatibility of the proposed engineered substrate with standard, additive thin-film processing is also demonstrated.

The second objective is to fabricate metal oxide based TFTs on the engineered stretchable substrate. IGZO TFT with organic dielectric layer are manufactured directly on top of the soft polymeric substrate. Different dielectric structures are tested in order to achieve a robust transistor-like behavior. Further, the electrical performance is measured under tensile strain to validate the design of the stretchable electronic devices.

In addition concurrent photopatterning of elastic modulus and structures in photosensitive silicone elastomers has been discovered and studied.

The aim is to simultaneously patterning the topography and elasticity of positive photopatternable PDMS, P-PDMS, solely by dry UV light irradiation, avoiding any wet chemistry. First the elastic modulus of the photosensitive elastomer is evaluated as function of UV light energy density. Then P-PDMS patternability against feature, size and spacing is investigated. Next the combined topographical and mechanical patterning of P-PDMS is explored to investigate the resulting stiffness of the photosesitive elastomer. Microfluidic devices are fabricated through the proposed technique and demonstrate a interesting application of the single-step photopatterning of P-PDMS.

#### 1.3 Thesis outline

This thesis is organized in four chapters.

After this introduction, the following first three chapters are structured in four main sections: (i) *introduction*, where more precise theory and state of the art of the discussed topic are presented, (ii) *materials and methods*, (ii) *results and discussion*, and (iv) *conclusions*. The last chapter summarizes the key findings of the thesis and give an outlook on the future work.

Chapter 2 focuses on the mechanical optimization of the engineered substrate. This chapter presents a particular structure, composed by a general introduction on the available stretchable substrate strategies, followed by multiple *introduction-materials and methods-results and discussion-conclusion* structures.

The first section introduces the engineered stretchable substrate with embedded strain relief. In particular it focus on the optimization of the embedded platforms geometry, thickness and spacing, to increase the stiff area to host the electronic devices and to decrease the strain along the interconnects. Modeling and experimental data are compared to produce design rules of the engineered substrate.

The second section aims to reduce the peak of strain concentration at the edge of the embedded platforms and to maximize the stiff area without affecting the spatial resolution. Pixelated greyscale mask are employed to grade the large mechanical mismatch at the stiff-to-soft interface, by grading the mechanical compliance of the elastomeric matrix or by sloping the side wall of the embedded platforms.

The last section presents additional designs to further reduce the along the elastic wiring interconnecting adjacent devices. The proposed designs are based on hexagonal and rhomboidal layouts of the embedded platforms together with a mechanically patterned elastomeric matrix.

Chapter 3 reports on fabrication and electro-mechanical characterization of rigid IGZO TFTs on the engineered stretchable substrates. The active devices are patterned directly on the pre-defined, rigid regions of the elastomeric substrate, and interconnected with stretchable metallization spanning across the rigid platforms. Brittle transistors, with different dielectric hybrid stack, are electrically characterized before and after annealing. An IGZO TFT on the engineered substrate is monitored under tensile strain.

Chapter 4 introduces a single-step photopatterning of positive P-PDMS membrane. The chapter illustrates how both mechanical and topographical patterning of the elastomeric film can be achieved simultaneously and without any wet development step. The ability to concurrently photopatterning the elastic modulus and relief structures in P-PDMS film is investigated. Then, proof of concept designs using the photosensitive elastomer in microfluidics are presented.

Finally, Chapter 5 summarizes the key results obtained in the thesis. An overall conclusion and an outlook for future objectives are presented.

References 11

#### References

[1] C. I. and W. S., "Overview of Flexible Electronics Technology" in Flexible Electronics, Springer, Ed., London, 2009.

- [2] T. Sekitani and T. Someya, "Stretchable organic integrated circuits for large-area electronic skin surfaces," *MRS Bulletin*, vol. 37, no. 03, pp. 236–245, Mar. 2012. [Online]. Available:

- [3] D.-H. Kim, N. Lu, R. Ghaffari, and J. a. Rogers, "Inorganic semiconductor nanomaterials for flexible and stretchable bio-integrated electronics," *NPG Asia Materials*, vol. 4, no. 4, p. e15, Apr. 2012. [Online]. Available:

- [4] D.-H. Kim, N. Lu, Y. Huang, and J. A. Rogers, "Materials for stretchable electronics in bioinspired and biointegrated devices," *MRS Bulletin*, vol. 37, pp. 226–235, 2012.

- [5] M. Kaltenbrunner, T. Sekitani, J. Reeder, T. Yokota, K. Kuribara, T. Tokuhara, I. Graz, S. Bauer-gogonea, S. Bauer, T. Someya, M. Drack, and R. Schwo, "An ultra-lightweight design for imperceptible plastic electronics."

- [6] I. R. Minev, P. Musienko, a. Hirsch, Q. Barraud, N. Wenger, E. M. Moraud, J. Gandar, M. Capogrosso, T. Milekovic, L. Asboth, R. F. Torres, N. Vachicouras, Q. Liu, N. Pavlova, S. Duis, a. Larmagnac, J. Voros, S. Micera, Z. Suo, G. Courtine, and S. P. Lacour, "Electronic dura mater for long-term multimodal neural interfaces," *Science*, vol. 347, no. 6218, pp. 159–163, 2015. [Online]. Available:

- [7] J.-H. Ahn and J. H. Je, "Stretchable electronics: materials, architectures and integrations," *Journal of Physics D: Applied Physics*, vol. 45, no. 10, p. 103001, Mar. 2012. [Online]. Available:

- [8] S. Wagner, "Electronic skin: architecture and components," *Physica E: Low-dimensional Systems and Nanostructures*, vol. 25, no. 2-3, pp. 326–334, Nov. 2004. [Online]. Available:

- [9] J. Viventi, D.-H. Kim, J. D. Moss, Y.-S. Kim, J. a. Blanco, N. Annetta, A. Hicks, J. Xiao, Y. Huang, D. J. Callans, J. a. Rogers, and B. Litt, "A conformal, bio-interfaced class of silicon electronics for mapping cardiac electrophysiology." *Sci. Transl. Med.*, vol. 2, no. 24, p. 24ra22, Mar. 2010. [Online]. Available:

- [10] C. Tsay, S. P. Lacour, S. Wagner, and B. M. Iii, "Architecture, Fabrication, and Properties of Stretchable Micro-electrode Arrays," *Electrical Engineering*, pp. 1169–1172, 2005.

- [11] Z. Yu, C. Tsay, S. P. Lacour, S. Wagner, and B. Morrison, "Stretchable microelectrode arrays-a tool for discovering mechanisms of functional deficits underlying traumatic brain injury and interfacing neurons with neuroprosthetics." *IEEE Engineering in Medicine and Biology Society. Conference*, vol. Suppl, pp. 6732–5, Jan. 2006. [Online]. Available:

[12] S. Khoshfetrat Pakazad, a. M. Savov, a. van de Stolpe, S. Braam, B. van Meer, and R. Dekker, "A stretchable Micro-Electrode Array for in vitro electrophysiology," 2011 IEEE 24th International Conference on Micro Electro Mechanical Systems, pp. 829–832, Jan. 2011. [Online]. Available:

- [13] L. Xu, S. R. Gutbrod, A. P. Bonifas, Y. Su, M. S. Sulkin, N. Lu, H.-J. Chung, K.-I. Jang, Z. Liu, M. Ying, C. Lu, R. C. Webb, J.-S. Kim, J. I. Laughner, H. Cheng, Y. Liu, A. Ameen, J.-W. Jeong, G.-T. Kim, Y. Huang, I. R. Efimov, and J. a. Rogers, "3D multifunctional integumentary membranes for spatiotemporal cardiac measurements and stimulation across the entire epicardium," *Nature Communications*, vol. 5, pp. 1–10, Feb. 2014. [Online]. Available:

- [14] D.-H. Kim, N. Lu, R. Ghaffari, Y.-S. Kim, S. P. Lee, L. Xu, J. Wu, R.-H. Kim, J. Song, Z. Liu, J. Viventi, B. de Graff, B. Elolampi, M. Mansour, M. J. Slepian, S. Hwang, J. D. Moss, B. L. S, and J. A. Rogers, "Materials for multifunctional balloon catheters with capabilities in cardiac electrophysiological mapping and ablation therapy," *Nature Materials*, no. 10, pp. 316–323, 2011. [Online]. Available:

- [15] D.-H. Kim, N. Lu, R. Ma, Y.-S. Kim, R.-H. Kim, S. Wang, J. Wu, S. M. Won, H. Tao, A. Islam, K. J. Yu, T.-i. Kim, R. Chowdhury, M. Ying, L. Xu, M. Li, H.-J. Chung, H. Keum, M. McCormick, P. Liu, Y.-W. Zhang, F. G. Omenetto, Y. Huang, T. Coleman, and J. a. Rogers, "Epidermal electronics." Science (New York, N.Y.), vol. 333, no. 6044, pp. 838–43, Aug. 2011. [Online]. Available:

- [16] H. C. Ko, M. P. Stoykovich, J. Song, V. Malyarchuk, W. M. Choi, C.-J. Yu, J. B. Geddes, J. Xiao, S. Wang, Y. Huang, and J. a. Rogers, "A hemispherical electronic eye camera based on compressible silicon optoelectronics." *Nature*, vol. 454, no. 7205, pp. 748–753, 2008.

- [17] I. Jung, J. Xiao, V. Malyarchuk, C. Lu, M. Li, Z. Liu, J. Yoon, Y. Huang, and J. a. Rogers, "Dynamically tunable hemispherical electronic eye camera system with adjustable zoom capability." Proceedings of the National Academy of Sciences of the United States of America, vol. 108, no. 5, pp. 1788–1793, 2011.

- [18] A. Chortos and Z. Bao, "Skin-inspired electronic devices," *Materials Today*, vol. 00, no. 00, Jun. 2014. [Online]. Available:

- [19] D. J. Lipomi and Z. Bao, "Stretchable, elastic materials and devices for solar energy conversion," *Energy & Environmental Science*, vol. 4, no. 9, p. 3314, 2011. [Online]. Available:

- [20] A. P. Gerratt, H. O. Michaud, and P. Stéphanie, "[SOM]Elastomeric Electronic Skin for Prosthetic Tactile Sensation," Advanced Functional Materials, vol. 25, 2015.

- [21] D. Son, J. Lee, S. Qiao, R. Ghaffari, J. Kim, J. E. Lee, C. Song, S. J. Kim, D. J. Lee, S. W. Jun, S. Yang, M. Park, J. Shin, K. Do, M. Lee, K. Kang, C. S. Hwang, N. Lu, T. Hyeon, and D.-H. Kim, "Multifunctional wearable devices for diagnosis

References 13

- and therapy of movement disorders," *Nature Nanotechnology*, no. March, Mar. 2014. [Online]. Available:

- [22] L. Pan, A. Chortos, G. Yu, Y. Wang, S. Isaacson, R. Allen, Y. Shi, R. Dauskardt, and Z. Bao, "An ultra-sensitive resistive pressure sensor based on hollow-sphere microstructure induced elasticity in conducting polymer film." *Nature communications*, vol. 5, p. 3002, Jan. 2014. [Online]. Available:

- [23] S. P. Lacour, I. Graz, D. Cotton, S. Bauer, and S. Wagner, "Elastic components for prosthetic skin." Conference proceedings: ... Annual International Conference of the IEEE Engineering in Medicine and Biology Society. IEEE Engineering in Medicine and Biology Society. Conference, vol. 2011, pp. 8373-6, Jan. 2011. [Online]. Available:

- [24] T. Someya, T. Sekitani, and T. Agency, "Exploratory Research for Advanced Technology (ERATO), Japan Science and Technology Agency BIONIC SKINS USING FLEXIBLE ORGANIC DEVICES," pp. 68–71, 2014.

- [25] T. Someya, Stretchable electronics, Wiley-VCH, Ed., Weinheim, Germany, 2013.

- [26] Z. Suo, "Fracture in Thin Films," Encyclopedia of Materials Science and Technology, pp. 1–17, 2001. [Online]. Available:

- [27] J. A. Rogers, T. Someya, and Y. Huang, "Materials and mechanics for stretchable electronics." *Science (New York, N.Y.)*, vol. 327, no. 5973, pp. 1603–7, Mar. 2010. [Online]. Available:

- [28] S. P. Lacour and S. Wagner, "Thin Film Transistor Circuits Integrated onto Elastomeric Substrates for Elastically Stretchable Electronics," Film, vol. 00, no. c, pp. 20–23, 2005.

- [29] J. Song, H. Jiang, W. M. Choi, D. Y. Khang, Y. Huang, and J. a. Rogers, "An analytical study of two-dimensional buckling of thin films on compliant substrates," *Journal of Applied Physics*, vol. 103, no. 1, p. 014303, 2008. [Online]. Available:

- [30] K. Park, D.-K. Lee, B.-S. Kim, H. Jeon, N.-E. Lee, D. Whang, H.-J. Lee, Y. J. Kim, and J.-H. Ahn, "Stretchable, Transparent Zinc Oxide Thin Film Transistors," *Advanced Functional Materials*, vol. 20, no. 20, pp. 3577–3582, Oct. 2010. [Online]. Available:

- [31] M. Shin, J. H. Song, G.-H. Lim, B. Lim, J.-J. Park, and U. Jeong, "Highly Stretchable Polymer Transistors Consisting Entirely of Stretchable Device Components," *Advanced Materials*, pp. n/a-n/a, Mar. 2014. [Online]. Available:

- [32] H. Wu, S. Kustra, E. M. Gates, and C. J. Bettinger, "Topographic substrates as strain relief features in stretchable organic thin film transistors," *Organic Electronics*, vol. 14, no. 6, pp. 1636–1642, Jun. 2013. [Online]. Available:

- [33] J. a. Rogers, "Materials for semiconductor devices that can bend, fold, twist, and stretch," MRS Bulletin, vol. 39, no. 06, pp. 549–556, Jun. 2014. [Online]. Available:

- [34] D.-H. Kim, Y.-S. Kim, J. Wu, Z. Liu, J. Song, H.-S. Kim, Y. Y. Huang, K.-C. Hwang, and J. a. Rogers, "Ultrathin Silicon Circuits With Strain-Isolation Layers and Mesh Layouts for High-Performance Electronics on Fabric, Vinyl, Leather, and Paper," Advanced Materials, vol. 21, no. 36, pp. 3703–3707, Sep. 2009. [Online]. Available:

- [35] S. Wagner, S. P. Lacour, J. Jones, P.-h. I. Hsu, J. C. Sturm, T. Li, and Z. Suo, "Electronic skin: architecture and components," *Physica E: Low-dimensional Systems and Nanostructures*, vol. 25, no. 2-3, pp. 326–334, Nov. 2004. [Online]. Available:

- [36] T. Someya, T. Sekitani, S. Iba, Y. Kato, H. Kawaguchi, and T. Sakurai, "A large-area, flexible pressure sensor matrix with organic field-effect transistors for artificial skin applications," PNAS, vol. 101, no. 27, pp. 9966–9970, 2004.

- [37] I. M. Graz, D. P. J. Cotton, A. Robinson, and S. P. Lacour, "Silicone substrate with in situ strain relief for stretchable thin-film transistors," *Applied Physics Letters*, vol. 98, no. 12, p. 124101, 2011. [Online]. Available:

- [38] P. Lacour, J. Jones, and P.-h. I. Hsu, "Electronic skin: architecture and components," vol. 25, pp. 326–334, 2004.

- [39] M. Gonzalez, F. Axisa, M. Bulcke, D. Brosteaux, B. Vandevelde, and J. Vanfleteren, "Design of metal interconnects for stretchable electronic circuits," *Microelectronics Reliability*, vol. 48, no. 6, pp. 825–832, Jun. 2008. [Online]. Available:

- [40] D.-H. Kim, J. Song, W. M. Choi, H.-S. Kim, R.-H. Kim, Z. Liu, Y. Y. Huang, K.-C. Hwang, Y.-w. Zhang, and J. a. Rogers, "Materials and noncoplanar mesh designs for integrated circuits with linear elastic responses to extreme mechanical deformations." Proceedings of the National Academy of Sciences of the United States of America, vol. 105, no. 48, pp. 18675–80, Dec. 2008. [Online]. Available:

- [41] M. Vosgueritchian, D. J. Lipomi, and Z. Bao, "Highly Conductive and Transparent PEDOT:PSS Films with a Fluorosurfactant for Stretchable and Flexible Transparent Electrodes," *Advanced Functional Materials*, vol. 22, no. 2, pp. 421–428, Jan. 2012. [Online]. Available:

- [42] Z. Xiong and C. Liu, "Optimization of inkjet printed PEDOT:PSS thin films through annealing processes," *Organic Electronics: physics, materials, applications*, vol. 13, no. 9, pp. 1532–1540, 2012. [Online]. Available:

- [43] J. Lessing, S. a. Morin, C. Keplinger, A. S. Tayi, and G. M. Whitesides, "Stretchable Conductive Composites Based on Metal Wools for Use as Electrical Vias in Soft Devices," *Advanced Functional Materials*, pp. n/a–n/a, Jan. 2015. [Online]. Available:

- [44] Y. Ohno, "Frontiers of Graphene and Carbon Nanotubes," pp. 269–283, 2015. [Online]. Available:

References 15

[45] Z. Chen, W. Ren, L. Gao, B. Liu, S. Pei, and H.-M. Cheng, "Three-dimensional flexible and conductive interconnected graphene networks grown by chemical vapour deposition." *Nat. Mater.*, vol. 10, no. 6, pp. 424–428, Jun. 2011. [Online]. Available:

- [46] S. Tuukkanen, M. Hoikkanen, M. Poikelispää, M. Honkanen, T. Vuorinen, M. Kakkonen, J. Vuorinen, and D. Lupo, "Stretching of solution processed carbon nanotube and graphene nanocomposite films on rubber substrates," Synthetic Metals, vol. 191, pp. 28–35, May 2014. [Online]. Available:

- [47] R. K. Kramer, C. Majidi, and R. J. Wood, "Wearable tactile keypad with stretchable artificial skin," 2011 IEEE International Conference on Robotics and Automation, pp. 1103–1107, May 2011. [Online]. Available:

- [48] H. O. U. Yuqun, M. O. Lixin, Z. Qingbin, and L. I. Luhai, "Synthesis of Silver Nanowires and Its Application on Stretchable Conductor b," vol. 731, pp. 593–596, 2015.

- [49] P. Lee, J. Lee, H. Lee, J. Yeo, S. Hong, K. H. Nam, D. Lee, S. S. Lee, and S. H. Ko, "Highly stretchable and highly conductive metal electrode by very long metal nanowire percolation network." *Advanced materials (Deerfield Beach, Fla.)*, vol. 24, no. 25, pp. 3326–32, Jul. 2012. [Online]. Available:

- [50] M. Park, J. Im, M. Shin, Y. Min, J. Park, H. Cho, S. Park, M.-B. Shim, S. Jeon, D.-Y. Chung, J. Bae, J. Park, U. Jeong, and K. Kim, "Highly stretchable electric circuits from a composite material of silver nanoparticles and elastomeric fibres." *Nature nanotechnology*, vol. 7, no. 12, pp. 803–809, Nov. 2012. [Online]. Available:

- [51] G. Corbelli, C. Ghisleri, M. Marelli, P. Milani, and L. Ravagnan, "Highly Deformable Nanostructured Elastomeric Electrodes With Improving Conductivity Upon Cyclical Stretching," *Advanced Materials*, pp. n/a–n/a, Aug. 2011. [Online]. Available:

- [52] D.-H. Kim, Y.-S. Kim, J. Amsden, B. Panilaitis, D. L. Kaplan, F. G. Omenetto, M. R. Zakin, and J. a. Rogers, "Silicon electronics on silk as a path to bioresorbable, implantable devices." Applied physics letters, vol. 95, no. 13, p. 133701, Sep. 2009. [Online]. Available:

- [53] T. Li, Z. Huang, Z. Suo, S. P. Lacour, and S. Wagner, "Stretchability of thin metal films on elastomer substrates," *Applied Physics Letters*, vol. 85, no. 16, p. 3435, 2004. [Online]. Available:

- [54] Y. Xiang, T. Li, Z. Suo, and J. J. Vlassak, "High ductility of a metal film adherent on a polymer substrate," *Applied Physics Letters*, vol. 87, no. 16, pp. 1–3, 2005.

- [55] L. Yu, P.-J. Alet, G. Picardi, and P. Roca i Cabarrocas, "An In-Plane Solid-Liquid-Solid Growth Mode for Self-Avoiding Lateral Silicon Nanowires," *Physical Review Letters*, vol. 102, no. 12, pp. 2–5, Mar. 2009. [Online]. Available:

- [56] D. Brosteaux, F. Axisa, M. Gonzalez, and J. Vanfleteren, "Design and Fabrication of Elastic Interconnections for Stretchable Electronic Circuits," *Electron Device Letters*, *IEEE*, vol. 28, no. 7, pp. 552–554, 2007.

- [57] S. P. Lacour, D. Chan, S. Wagner, T. Li, and Z. Suo, "Mechanisms of reversible stretchability of thin metal films on elastomeric substrates," *Applied Physics Letters*, vol. 88, no. 20, p. 204103, 2006. [Online]. Available:

- [58] I. M. Graz, D. P. J. Cotton, and S. P. Lacour, "Extended cyclic uniaxial loading of stretchable gold thin-films on elastomeric substrates," *Applied Physics Letters*, vol. 94, no. 7, p. 071902, 2009. [Online]. Available:

- [59] N. Lambricht, T. Pardoen, and S. Yunus, "Giant stretchability of thin gold films on rough elastomeric substrates," *Acta Materialia*, pp. 1–8, Nov. 2012. [Online]. Available:

- [60] —, "Giant stretchability of thin gold films on rough elastomeric substrates," *Acta Materialia*, vol. 61, no. 2, pp. 540–547, 2013. [Online]. Available:

- [61] R. M. Erb, K. H. Cherenack, R. E. Stahel, R. Libanori, T. Kinkeldei, N. Münzenrieder, G. Tröster, and A. R. Studart, "Locally Reinforced Polymer-Based Composites for Elastic Electronics." ACS applied materials & interfaces, Jun. 2012. [Online]. Available:

# 2 Engineered Stretchable Substrate with Embedded Strain Relief \*†

#### Contents

| Pixella | ted Layout                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1.1   | Mechanics                                                                                                                                                             |

| 2.1.2   | Substrate Materials Selection                                                                                                                                         |

| 2.1.3   | Mechanical Requirements                                                                                                                                               |

| Stiff P | latform Geometry Optimization                                                                                                                                         |

| 2.2.1   | Finite Element Modeling                                                                                                                                               |

| 2.2.2   | Experimental: Materials and Methods                                                                                                                                   |

| 2.2.3   | Experimental Results and Discussion                                                                                                                                   |

| 2.2.4   | Conclusions                                                                                                                                                           |

| Greysc  | ale-photolitography for Top Surface Strain Optimization                                                                                                               |

| 2.3.1   | Greyscale photolitography                                                                                                                                             |

| 2.3.2   | Materials and methods                                                                                                                                                 |

| 2.3.3   | Results and Discussion                                                                                                                                                |

| 2.3.4   | Conclusions                                                                                                                                                           |

| Optim   | ized Engineered Substrate Layout                                                                                                                                      |

| 2.4.1   | Materials and Methods                                                                                                                                                 |

| 2.4.2   | Results and Discussion                                                                                                                                                |

| 2.4.3   | Conclusions                                                                                                                                                           |

| Conclu  | sions                                                                                                                                                                 |

| rences  |                                                                                                                                                                       |

|         | 2.1.1<br>2.1.2<br>2.1.3<br>Stiff Pl<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Greysc<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>Optimi<br>2.4.1<br>2.4.2<br>2.4.3<br>Conclus |

<sup>\*</sup>A. Romeo, Q. Liu, Z. Suo, S.P. Lacour, "Elastomeric substrates with embedded stiff platforms for stretchable electronics ," *Applied Physics Letters*, April 2013.

<sup>&</sup>lt;sup>†</sup>A. Romeo, Y. Hofmeister, S.P. Lacour, "Implementing MEMS technology for soft, (bio)electronics interfaces," proc. of SPIE DSS, Baltimore, USA, May 2014

#### 2.1 Pixellated Layout

Stretchable electronics are integrated circuitry that can reversibly expand and relax while maintaining their functionalities. This cannot be achieved with the hard, planar integrated circuits that exist today. Stretchability can be introduced into electronic systems by the use of suitable stretchable substrate materials, electrical interconnections and active electronic components. Therefore stretchable system are mostly hybrids of soft and hard materials that span more than 12 orders of magnitude in elastic modulus [1].

The main challenge to implement stretchable electronics is how to integrate fragile electronic device materials with compliant elastomeric substrates. Device material are brittle and crack at strains of a few tenths of percent [2] while the rubbery substrate can be repeatedly deformed with different strain levels on objects with arbitrary shapes. Thus, to enable large deformation, while keeping brittle materials intact, it is highly desirable to reduce the applied mechanical strain in such device structure on deformable substrates. One possible solution is the implementation of a pixellated matrix of rigid platform interconnected with elastic wiring (Fig2.1) [3–5]. The rigid platform are designed to host fragile device materials, preventing them from exceeding their critical fracture strain, while the exposed substrate together with the interconnects accommodate most of the deformation.

**Figure 2.1:** Concept of pixellated architecture for stretchable electronic. Stiff cell which host electronics devices is replicated many times and interconnected with elastic wiring.

In order to achieve electro-mechanical stability for this architecture the following mechanical conditions must be fulfilled [6].

• the stiffness of the platforms should be high enough to assure the strain within the device stack remains below the materials fracture strain i.e. < 1%. Defining the stiffness as the product between the Young's modulus E and the thickness t of a material it necessary that:

$$E_{platform} \cdot t_{platform} \gg E_{substrate} \cdot t_{substrate}$$

(2.1)

• the strain profile along the interconnects running from the stiff platform to the soft matrix should be as smooth as possible. There is an abrupt transition of material properties at the stiff/soft interfaces, which cause strain localization at the interface of the islands

Mechanics and materials of the pixellated substrate will be analysed in the following subsections.

### 2.1.1 Mechanics

Two different strategies based on the pixellated architecture will be presented in the following paragraphs. The first one implements thin-film stiff islands deposited on top of the deformable substrate, the other relies on rigid thick platforms embedded in the elastomeric membrane.

#### Thin superficial stiff islands

One approach is to pattern directly onto thick (ranging from tens  $\mu m$  to 1mm) polymeric substrate, thin (few hundreds nm) rigid platforms which work as functional non stretchable islands and can host active electronic devices. To guarantee the architecture function, appropriate island material must be chosen in order to fulfill the following conditions

- according to the equation 2.1, since the substrate is thicker than the stiff platforms, for those to be stiffer than the substrate, they should have a Young's modulus much larger than the substrate one:

- the stiff platform materials need to be deposited with standard thin-film techniques at low temperature process in order to be compatible with organic substrates