### Polarity Control at Runtime: from Circuit Concept to Device Fabrication

THÈSE Nº 6821 (2015)

PRÉSENTÉE LE 23 OCTOBRE 2015 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI) PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

### Michele DE MARCHI

acceptée sur proposition du jury:

Prof. C. Guiducci, présidente du jury Prof. G. De Micheli, directeur de thèse Prof. S. Mitra, rapporteur Dr W. Weber, rapporteur Prof. Y. Leblebici, rapporteur

## Acknowledgements

The first and warmest thank you goes to my supervisor, Prof. Giovanni De Micheli, in art *nanni*, for his trust, advice and support throughout the development of this five-year PhD endeavor. The experimental device work presented in this thesis required a great deal of resources, freedom to explore, and patience to produce successes and results. Having these granted at all times is no obvious thing, and I am deeply grateful to nanni for providing them without question.

I want to thank my thesis jury: the president Prof. Guiducci, Prof. Subhasish Mitra, Dr. Walter Weber and Prof. Yusuf Leblebici, for accepting to read my thesis, evaluating it and providing interesting insights and questions.

I want to express my deepest gratitude to Pierre-Emmanuel, for firmly and smartly counteracting my pessimism, while listening and guiding without boundaries. The resulting balance has proven most fructful for my research.

Thank you to Haykel and Davide, for setting me on track with my research, and teaching me a lot of very complicated cleanroom tricks. Thank you to Prof. Yusuf Leblebici, for his support and advice along my research path.

I want to thank the technical-psychological support entourage, who filled all the gaps, beaurocratic, logistic, infrastructural: Christina, Anil, Rodolphe and Marie. Thank you for answering all the questions, and providing support beyond reason.

No university has a cooler cleanroom, nor a better microscopy facility (besides when electron guns blow up). The difference, though, is not made by the machines. Thank you Zdenek, Kevin, Samuel, Cyrille, Joffrey, Didier, Anthony and all the CMi staff for your constant availability and support. A thanks to Duncan, Marco, Danièle, Colette and Emad for helping me scratch the surface of the art of transmission electron microscopy.

A PhD is carried out in a Lab, and a Lab whose people make up the loudest table of the cafeteria is an amazing environment where to grow, share ideas and challenges. Thanks to Jacopo, Irene, Andrea, Alena, Camilla, Federico, Antonio, Ciprian, Vasilis, Somayyeh, Gözen, Sara, Cristina, Shashi, Julien, Jian, Luca, Sandro, Wenqi, Hu, Ismael, Jaume, Mitty, Maxime, Lucia, and Francesca for making my life in LSI unforgettable. Working with you has been a gift and a honor. Thanks also to Matteo, Anna, Ludovica, Ivan, Lucian, Pablo, Egle, Alberto, Oleg, Roberto, Sophie and Massimo, who shared work, life and sport discussions making these five years go way beyond pure academic research.

A warm hug to Stefy, for supporting me in this *thesis writing* year, and driving together with me to the most legendary of Europe's (and US!) climbing destinations.

#### Acknowledgements

I conclude with a thank you to my family, for their unconditional support, and the most important of the teachings, that learning is the basis for happiness, that it is a right, that learning deserves attention, effort and care because it is the only way to a better world.

### Abstract

Semiconductor device research for digital circuit design is currently facing increasing challenges to enhance miniaturization and performance. A huge economic push and the interest in novel applications are stimulating the development of new pathways to overcome physical limitations affecting conventional CMOS technology.

Here, we propose a novel Schottky barrier device concept based on electrostatic polarity control. Specifically, this device can behave as p- or n-type by simply changing an electric input bias. This device combines *More-than-Moore* and *Beyond CMOS* elements to create an efficient technology with a viable path to *Very Large Scale Integration* (VLSI). This thesis proposes a device/circuit/architecture co-optimization methodology, where aspects of device technology to logic circuit and system design are considered.

At device level, a full CMOS compatible fabrication process is presented. In particular, devices are demonstrated using vertically stacked, top-down fabricated silicon nanowires with gate-all-around electrode geometry. Source and drain contacts are implemented using nickel silicide to provide quasi-symmetric conduction of either electrons or holes, depending on the mode of operation. Electrical measurements confirm excellent performance, showing  $I_{\rm on}/I_{\rm off} > 10^7$  and subthreshold slopes approaching the thermal limit,  $SS \approx 60 \,\mathrm{mV/dec}$  ( $\approx 63 \,\mathrm{mV/dec}$ ) for n(p)-type operation in the same physical device. Moreover, the shown devices behave as p-type for a polarization bias (polarity gate voltage,  $V_{\rm pg}$ ) of 0 V, and n-type for a  $V_{\rm pg} \approx 1 V$ , confirming their compatibility with multi-level static logic circuit design.

At logic gate level, two- and four-transistor logic gates are fabricated and tested. In particular, the first fully functional, two-transistor XOR logic gate is demonstrated through electrical characterization, confirming that polarity control can enable more compact logic gate design with respect to conventional CMOS. Furthermore, we show for the first time fabricated four-transistors logic gates that can be reconfigured as NAND or XOR only depending on their external connectivity. In this case, logic gates with full swing output range are experimentally demonstrated. Finally, single device and mixed-mode TCAD simulation results show that lower  $V_{\rm th}$  and more optimized polarization ranges can be expected in scaled devices implementing strain or high- $\kappa$  technologies.

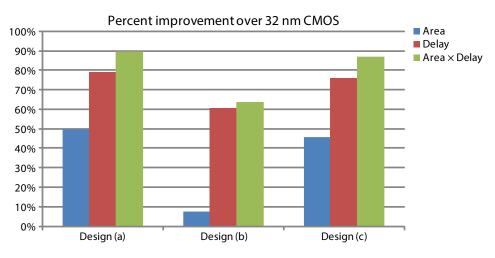

At circuit and system level, a full semi-custom logic circuit design tool flow was defined and configured. Using this flow, novel logic libraries based on standard cells or regular gate fabrics were compared with standard CMOS. In this respect, results were shown in comparison to CMOS, including a 40% normalized area-delay product reduction for the analyzed standard cell libraries, and improvements of over 2× in terms of normalized delay for regular *Controlled*

#### Abstract

*Polarity* (CP)-based cells in the context of Structured ASICs. These results, in turn, confirm the interest in further developing and optimizing CP devices, as promising candidates for future digital circuit technology.

Key words: nanotechnology, emerging technologies, silicon nanowires, Schottky barrier, logic design, multi-level synthesis, gate-all-around, polarity control, beyond CMOS, XOR, device fabrication.

## Sommario

L'attuale ricerca sul progetto di circuiti digitali sta incontrando crescenti difficoltà nel tentativo di migliorare prestazioni e miniaturizzazione dei moderni dispositivi a semiconduttore. Una fortissima spinta economica e l'interesse in nuove applicazioni stanno stimolando lo sviluppo verso nuove direzioni di ricerca per superare le limitazioni fisiche che caratterizzano la tecnologia CMOS standard.

In questa tesi consideriamo un nuovo concetto di dispositivo, basato sul controllo elettrostatico della polarità, che consiste in un dispositivo a barriera Schottky che si può configurare elettostaticamente per operare come *tipo n* o *p*. Questo dispositivo combina elementi *Morethan-Moore* e *Beyond CMOS* per creare una tecnologia efficiente e con una visione pratica per l'integrazione su larga scala (*Very Large Scale Integration* o VLSI). Qui, proponiamo una metodologia di co-ottimizzazione tra i livelli di dispositivo/circuito/architettura, dove consideriamo aspetti che vanno dalla tecnologia dei dispositivi, al design di circuiti e sistemi.

A livello di dispositivo, presentiamo un processo di fabbricazione completo e compatibile con i processi CMOS standard. In particolare, dimostriamo dispositivi che utilizzano canali composti da nanofili (*nanowire*) di silicio impilati, fabbricati con una metodologia *top-down* e circondati da elettrodi *gate-all-around* per ottenere un'elettrostatica ottimale. I contatti di *Source* e *Drain* sono implementati usando siliciuro di nichel per garantire una conduzione quasi simmetrica di elettroni o lacune a seconda della modalità di conduzione selezionata. Le misure elettriche confermano prestazioni eccellenti, dimostrando  $I_{on}/I_{off} > 10^7$  e *subthreshold slope* vicine al limite termico  $SS \approx 60 \text{ mV/dec}$  e  $\approx 63 \text{ mV/dec}$  rispettivamente nelle modalità *tipo n* e *p*. Inoltre, i dispositivi fabbricati possono essere polarizzati a *tipo p* per polarizzazioni del gate di polarità (*polarity gate voltage*,  $V_{pg}$ ) di 0 V e *tipo n* per  $V_{pg} \approx 1$  V, confermando la loro compatibilità con la sintesi di circuiti logici con porte logiche connesse in cascata.

A livello di porta logica, abbiamo fabbricato e collaudato porte composte da due e quattro transistor. In particolare, presentiamo la prima porta logica di tipo XOR composta da soli due transistor, confermando che il controllo della polarità permette il progetto di porte logiche più compatte rispetto alla tecnologia CMOS standard. In aggiunta, mostriamo per la prima volta porte logiche composte da quattro transistor che possono essere configurate come NAND o XOR solo modificando le loro connessioni esterne. In questo caso, porte logiche con output *full-swing* sono state dimostrate sperimentalmente. Infine, presentiamo delle simulazioni effettuate utilizzando TCAD che indicano che una riduzione della tensione di soglia nonché condizioni di polarizzazione ottimizzate possono essere ottenute utilizzando dispositivi più miniaturizzati e utilizzando tecnologie come *strain* o dielettrici *high-* $\kappa$ .

#### Sommario

A livello di circuito e sistema, abbiamo definito e configurato un flusso di progetto software *semi-custom* per il design di circuiti in modo automatizzato. Utilizzando questo strumento, abbiamo confrontato delle innovative librerie logiche basate su *standard cell* o matrici regolari di porte logiche con le porte CMOS standard. In particolare, abbiamo ottenuto una riduzione del 40% in termini di prodotto *area-delay* per le librerie di *standard cell* analizzate, e miglio-ramenti di oltre 2× in termini di *delay* normalizzato nel contesto delle tecnologie *Structured ASIC*. Questi risultati, in definitiva, confermano l'interesse nel continuare lo sviluppo e l'ottimizzazione dei dispositivi con controllo elettrostatico della polarità, affermandoli come ottimi candidati per l'evoluzione delle future tecnologie digitali.

Key words: nanotecnologie, tecnologie emergenti, nanofili di silicio, barriera Schottky, progetto logico, sintesi logica, gate-all-around, controllo elettrostatico della polarità, beyond CMOS, XOR, fabbricazione di dispositivi.

## Résumé

Des nos jours, la recherche dans le domaine des circuits numériques est confrontée à des difficultés croissantes dans la tentative d'améliorer les performances et la miniaturisation des dispositifs à semi-conducteur modernes. Une énorme pression économique et l'intérêt pour de nouvelles applications sont en train de stimuler le développement de nouvelles directions de recherche capable de surmonter les limitations physiques qui contraignent la technologie CMOS conventionnelle.

Dans cette thèse, nous considérons un nouveau concept de dispositif, basé sur le contrôle électrostatique de polarité, qui se compose d'un transistor à barrière de Schottky qui peut être configuré pour opérer comme un type n ou p. Ce dispositif combine des éléments Morethen-Moore et Beyond CMOS pour créer une technologie efficace et crédible pour l'intégration à grande échelle (Very Large Scale Integration, ou VLSI). Ici, nous proposons une méthodologie de co-optimisation aux niveaux dispositif/circuit/architecture, où nous adressons des questions partant de la technologie du dispositif, jusqu'à la conception de circuits et systèmes. Au niveau du dispositif, nous présentons un procédé de fabrication complet et compatible avec les procédés de fabrication standards CMOS. En particulier, nous démontrons des dispositifs qui utilisent un canal composé de nanofils de silicium empilés, fabriqué avec une méthodologie top-down et entouré par une grille enrobante afin d'obtenir un contrôle électrostatique optimal. Les contacts de source et de drain sont fabriqués en utilisant du siliciure de nickel afin d'assurer une conduction quasi-symétrique des électrons ou des trous en fonction du mode de conduction sélectionné. Les mesures électriques confirment une excellente performance, montrant un rapport  $I_{on}/I_{off} > 10^7$  et une pente sous le seuil près de la limite thermique, de  $\approx 60 \,\text{mV/dec}$  et  $\approx 63 \,\text{mV/dec}$  respectivement pour le type *n* et le type *p*. De plus, les dispositifs fabriqués peuvent être polarisés comme type p pour une polarisation de la grille de polarité (*polarity gate voltage*, Vpg) de 0 V et comme type *n* pour  $V_{pg} \approx 1$  V, confirmant leur compatibilité avec la réalisation des circuits logiques avec des portes logiques connectés en cascade.

Au niveau portes logiques, nous avons fabriqué et testé des portes composées de deux et quatre transistors. En particulier, nous présentons la première porte logique XOR constituée de seulement deux transistors, confirmant que le contrôle de polarité permet la conception de portes logiques plus compactes par rapport à la technologie CMOS conventionnelle. De plus, nous montrons pour la première fois des portes logiques composées de quatre transistors qui peuvent être configurées comme NAND ou XOR uniquement en modifiant leurs connexions externes. Dans ce cas, des portes logiques avec sortie pleine-échelle ont été démontrées

#### Sommario

expérimentalement. Enfin, nous présentons des simulations TCAD qui indiquent qu'une réduction de la tension de seuil ainsi que des conditions de polarisation optimisées peuvent être obtenues en utilisant des dispositifs plus miniaturisés ainsi qu'utilisant des technologies telles que la contrainte ou des isolants de grille à forte permittivité.

Au niveau circuit et système, nous avons défini et configuré un flot d'outils de conception de projet logiciel de type *semi-custom* pour la conception de circuits de manière automatisée. Grâce à cet outil, nous avons comparé des librairies logiques innovantes basées sur des cellules standards ou des matrices régulières de portes logiques avec des portes CMOS standards. En particulier, nous avons obtenu une réduction de 40% en termes de produit surface délai pour les librairies de cellules standards analysées, et des améliorations de plus de 2× en termes de délai normalisé dans le contexte des technologies de circuits ASIC structurés. Ces résultats, finalement, confirment l'intérêt de poursuivre le développement et l'optimisation des dispositifs avec contrôle électrostatique de polarité, les affirmant comme d'excellents candidats pour le développement des technologies numériques du futur.

Mots clefs : nanotechnologies, technologies émergentes, nanofils de silicium, barrière de Schottky, projet numérique, synthèse numerique, gate-all-around, contrôle électrostatique de polarité, beyond CMOS, XOR, fabrication de dispositifs.

| Ao | cknow | wledgements                                                         | i    |

|----|-------|---------------------------------------------------------------------|------|

| Al | bstra | ct (English/Italiano)                                               | iii  |

| Li | st of | figures                                                             | xiii |

| Li | st of | tables x                                                            | xvii |

| Li | st of | acronyms                                                            | xxix |

| 1  | Intr  | oduction                                                            | 1    |

|    | 1.1   | Industrial and research innovation                                  | 2    |

|    |       | 1.1.1 Emerging research technologies                                | 2    |

|    |       | 1.1.2 The ITRS roadmap: Beyond-CMOS and More-than-Moore             | 4    |

|    | 1.2   | The controlled polarity silicon nanowire FET                        | 5    |

|    | 1.3   | A wider perspective: device/circuit/architecture interactions       | 7    |

|    | 1.4   | Prior art                                                           | 8    |

|    | 1.5   | Research objectives and contributions                               | 9    |

|    |       | 1.5.1 Device design and fabrication                                 | 11   |

|    |       | 1.5.2 Two and four-transistor XOR demonstration                     | 11   |

|    |       | 1.5.3 Large logic circuit level benchmarking                        | 12   |

|    | 1.6   | Thesis organization                                                 | 12   |

| 2  | In-l  | Field Controlled Polarity SB FET                                    | 15   |

|    | 2.1   | Polarity control functionality                                      | 15   |

|    |       | 2.1.1 Generalities                                                  | 16   |

|    |       | 2.1.2 Ambipolarity as an added degree of freedom                    | 17   |

|    |       | 2.1.3 Embedded binate operation                                     | 18   |

|    | 2.2   |                                                                     | 19   |

|    |       | 2.2.1 Ambipolar FET implementing a single transistor XOR logic gate | 19   |

|    |       | 2.2.2 Electrostatic polarity control demonstration in a CNTFET      | 21   |

|    |       | 2.2.3 Voltage-selectable top-down SiNW FET                          | 22   |

|    |       | 2.2.4 SiNWFET with two independent $\Omega$ gate electrodes         | 22   |

|    | 2.3   | The proposed CP Schottky barrier nanowire FET device                | 23   |

|    |       | 2.3.1 Device requirements                                           | 23   |

|   |      | 2.3.2    | Schottky barrier FET technology                                                                                | 25 |

|---|------|----------|----------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.3.3    | CP SiNWFET geometry and switching mechanism                                                                    | 28 |

|   | 2.4  | Devic    | e measurements                                                                                                 | 30 |

|   |      | 2.4.1    | Measurement setup                                                                                              | 30 |

|   |      | 2.4.2    | Polarity control demonstration                                                                                 | 30 |

|   |      | 2.4.3    | Subthreshold slope and $I_{on}/I_{off}$ performance $\ldots \ldots \ldots \ldots \ldots \ldots$                | 31 |

|   |      | 2.4.4    | $I_d - V_d$ characteristics                                                                                    | 35 |

|   | 2.5  | TCAD     | simulations                                                                                                    | 35 |

|   |      | 2.5.1    | $I_d - V_d$ characteristics                                                                                    | 36 |

|   |      | 2.5.2    | $I_d - V_{cg}$ vs. $I_d - V_{pg}$ switching behavior $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 37 |

|   |      | 2.5.3    | Optimized device model and simulations                                                                         | 38 |

|   | 2.6  | Chapt    | ter summary and contributions                                                                                  | 40 |

| 3 | Dev  | ice Fab  | prication                                                                                                      | 43 |

| - | 3.1  |          | NWFET structure motivation                                                                                     | 43 |

|   | 3.2  |          | wire fabrication                                                                                               | 45 |

|   |      | 3.2.1    | Top-down methodologies                                                                                         | 46 |

|   |      | 3.2.2    | Bottom-up methodologies                                                                                        | 48 |

|   | 3.3  |          | Ill CP SiNWFET process flow                                                                                    | 50 |

|   |      | 3.3.1    | Substrate choice for device isolation                                                                          | 51 |

|   |      | 3.3.2    | EBL alignment markers definition – Phases 1–2                                                                  | 52 |

|   |      | 3.3.3    | Nanowire mask – Phase 3                                                                                        | 53 |

|   |      | 3.3.4    | Nanowires DRIE etching – Phase 4                                                                               | 56 |

|   |      | 3.3.5    | Polarity gate stack deposition and lithography – Phases 5–6                                                    | 57 |

|   |      | 3.3.6    | Polarity gate etching – Phase 7                                                                                | 59 |

|   |      | 3.3.7    | Control gate deposition, lithography and etching – Phases 8–10                                                 | 61 |

|   |      | 3.3.8    | Nitride spacer process – Phase 11                                                                              | 63 |

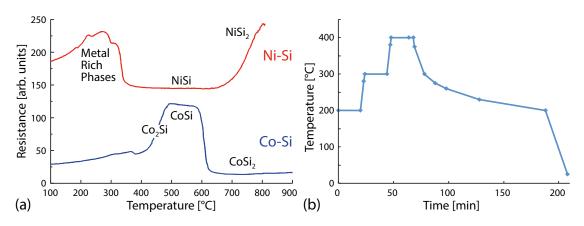

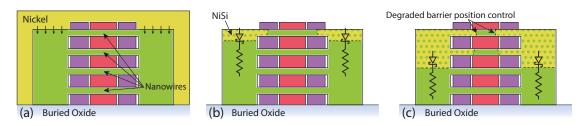

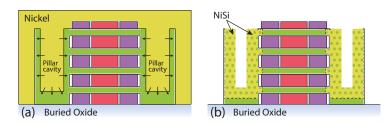

|   |      | 3.3.9    | Nickel silicide formation – Phase 12                                                                           | 64 |

|   | 3.4  | Chapt    | ter summary and contributions                                                                                  | 64 |

| 4 | Pola | arity co | ontrol based logic gates                                                                                       | 73 |

| - | 4.1  | •        | ty control for logic gate design                                                                               | 73 |

|   |      |          | One-transistor controlled polarity pseudo-logic gate                                                           | 74 |

|   |      |          | From pseudo-logic to complementary pass-transistor logic gates                                                 | 75 |

|   | 4.2  |          | of-the-art                                                                                                     | 76 |

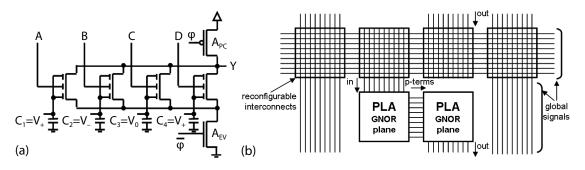

|   |      | 4.2.1    | Dopant independent CMOS for reconfigurable logic applications                                                  | 76 |

|   |      | 4.2.2    | Single NW configurable logic gates                                                                             | 77 |

|   | 4.3  | CP Sil   | WWFET one and two-transistor circuit measurements                                                              | 79 |

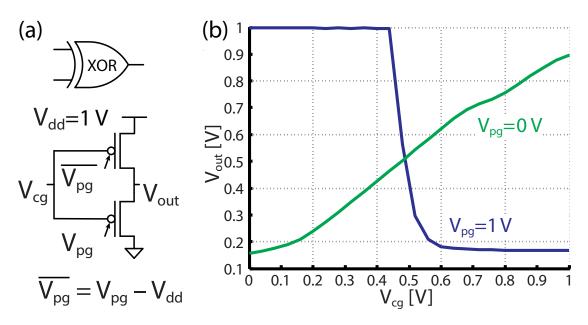

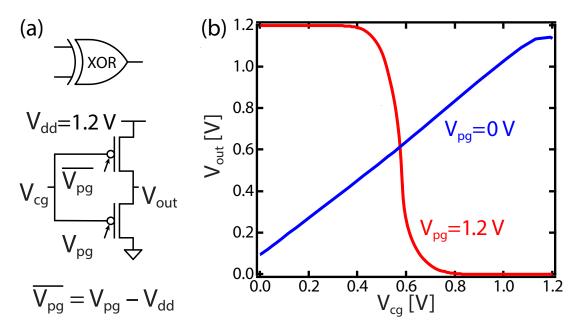

|   |      | 4.3.1    | Single CP SiNWFET embedded as a pseudo-logic XOR gate                                                          | 79 |

|   |      | 4.3.2    | Two-transistor configurable inverter                                                                           | 80 |

|   |      | 4.3.3    | Two-transistor XOR operation                                                                                   | 81 |

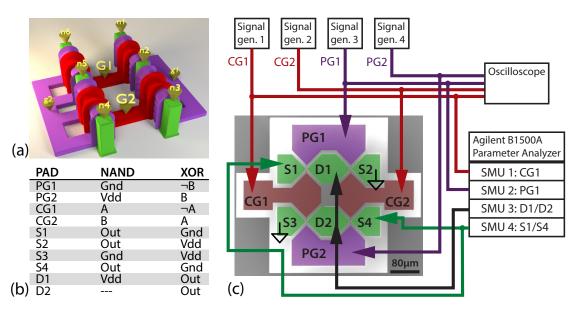

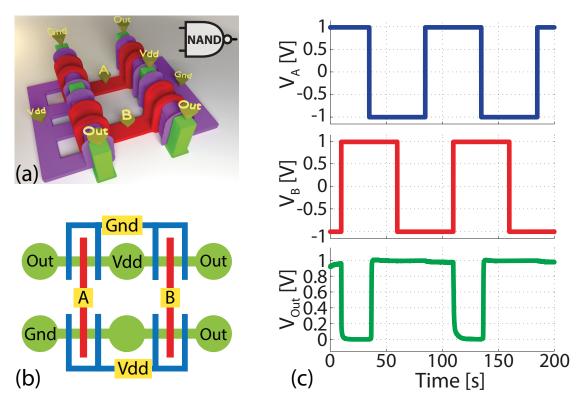

|   | 4.4  |          | abricated four-transistor logic gates                                                                          | 83 |

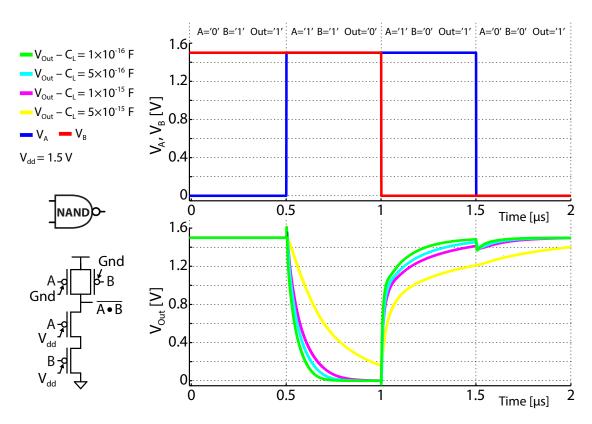

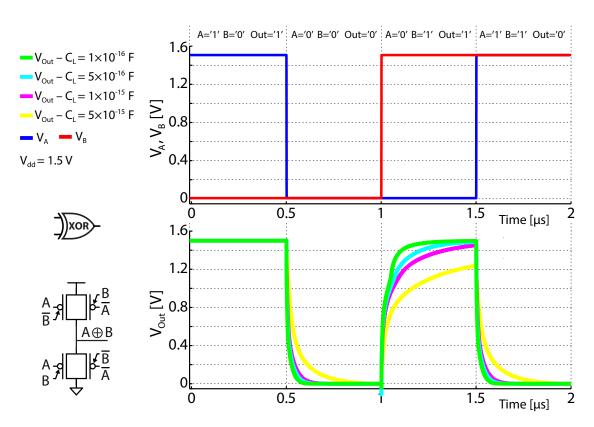

|   | 4.5  |          | rmance investigation through simulations                                                                       | 85 |

|   |      | 4.5.1    | Four-transistor logic gate mixed-mode simulations              | 86  |

|---|------|----------|----------------------------------------------------------------|-----|

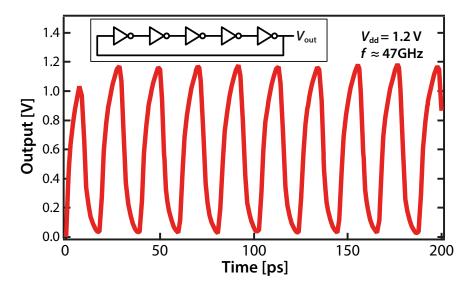

|   |      | 4.5.2    | Ring oscillator performance                                    | 88  |

|   | 4.6  | Chapt    | er summary and contributions                                   | 89  |

| 5 | Pola | arity co | ontrol in logic circuit design                                 | 91  |

|   | 5.1  | Backg    | round                                                          | 92  |

|   | 5.2  | State-   | of-the-art                                                     | 94  |

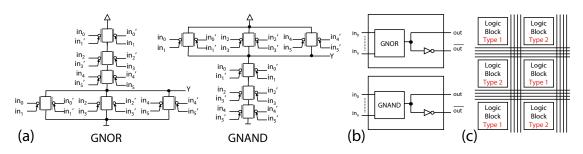

|   |      | 5.2.1    | Circuit design using reconfigurable dynamic logic gates        | 94  |

|   |      | 5.2.2    | Dynamic Generalized NAND/NOR PLA design                        | 95  |

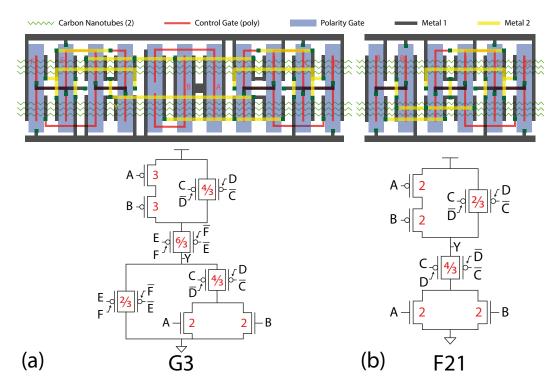

|   |      | 5.2.3    | Polarity control based static logic design                     | 96  |

|   | 5.3  | Static   | logic circuit design with CP devices                           | 97  |

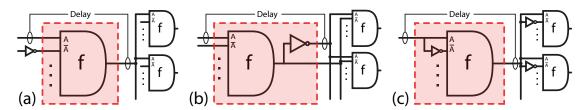

|   |      | 5.3.1    | Signal-polarity-aware design                                   | 98  |

|   |      | 5.3.2    | Logic gates for regular fabrics                                | 99  |

|   | 5.4  | Simula   | ation results                                                  | 101 |

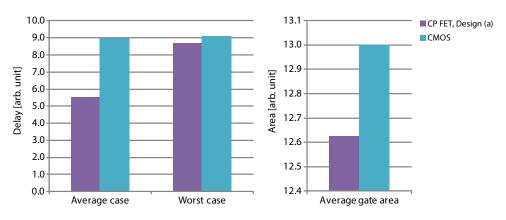

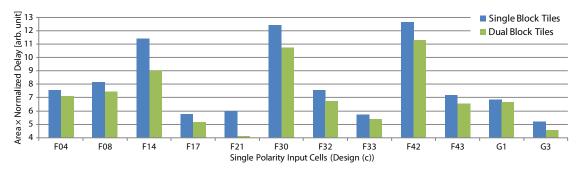

|   |      | 5.4.1    | Characterization of individual logic gates                     | 101 |

|   |      | 5.4.2    | Full logic library characterization                            | 103 |

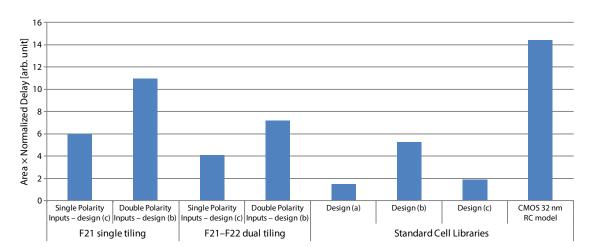

|   |      | 5.4.3    | Characterization of configurable gates                         | 104 |

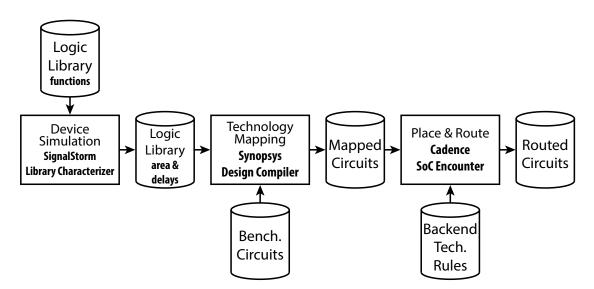

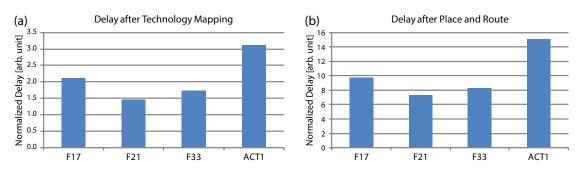

|   | 5.5  | Place    | and route process flow for regular fabric evaluation           | 107 |

|   |      | 5.5.1    | Evaluation results                                             | 108 |

|   | 5.6  | Perspe   | ectives for device/circuit co-optimization                     | 109 |

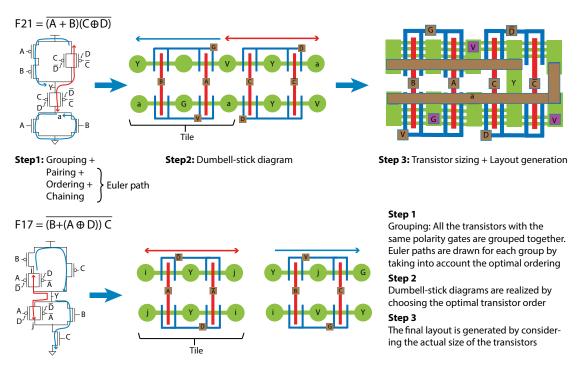

|   |      | 5.6.1    | Sea-of-Tiles as paradigm for physical regular fabric synthesis | 109 |

|   |      | 5.6.2    | Further developments and outlook                               | 111 |

|   | 5.7  | Chapt    | er summary and contributions                                   | 112 |

| 6 | Dev  | ice Opt  | timization                                                     | 115 |

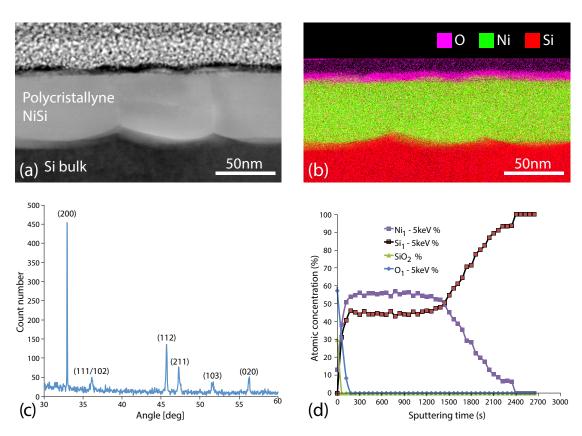

|   | 6.1  | Nickel   | l silicide technology                                          | 115 |

|   |      | 6.1.1    | Nickel deposition methods                                      | 117 |

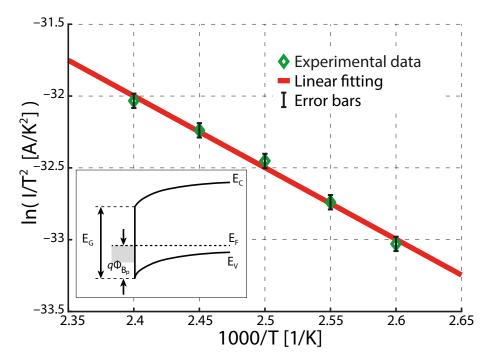

|   | 6.2  | Silicid  | le characterization                                            | 119 |

|   |      | 6.2.1    | Material characterization                                      | 119 |

|   |      | 6.2.2    | Schottky barrier height extraction                             | 119 |

|   | 6.3  | S/D ad   | ccess resistance reduction                                     | 121 |

|   | 6.4  | Wet co   | onformal NiSi deposition                                       | 123 |

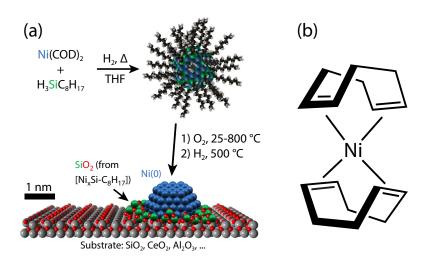

|   |      | 6.4.1    | Nickel silicide deposition in wet chemical conditions          | 125 |

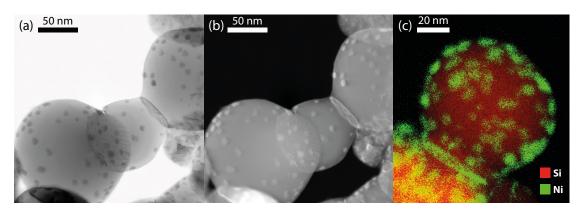

|   |      | 6.4.2    | Ni deposition on Si nanoparticles                              | 126 |

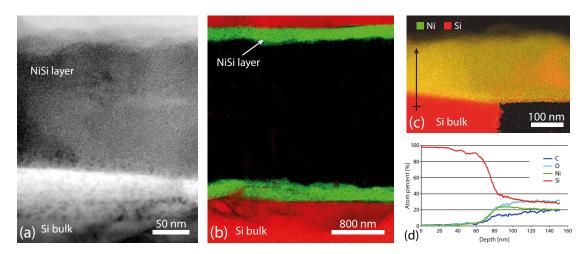

|   |      | 6.4.3    | Deposition on Si bulk substrate                                | 126 |

|   |      | 6.4.4    | Diode process flow                                             | 127 |

|   | 6.5  | Chapt    | er summary and contributions                                   | 128 |

| 7 | Con  | clusio   | ns and outlook                                                 | 135 |

|   | 7.1  | Summ     | nary of contributions                                          | 136 |

|   |      | 7.1.1    | Device fabrication and characterization                        | 136 |

|   |      | 7.1.2    | Reconfigurable logic gate demonstration                        | 137 |

|   |      | 7.1.3    | Device and logic gate simulations                              | 137 |

|                                                                                     | Curric |       |                           | 155 |

|-------------------------------------------------------------------------------------|--------|-------|---------------------------|-----|

|                                                                                     |        |       | •                         |     |

| 7.2.1Catalyst for extended research directions1397.2.2Future research directions140 | 7.2    | Outlo | ok and future research    | 139 |

| •                                                                                   |        | 7.1.5 | Technology refinements    | 139 |

| 7.2.1 Catalyst for extended research directions                                     |        | 7.1.4 | System level benchmarking | 138 |

## **List of Figures**

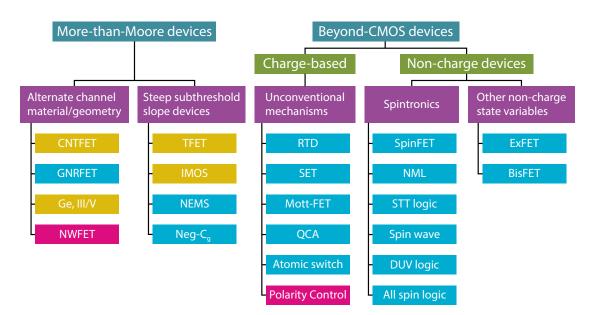

| 1.1 | Emerging device universe, categorized as <i>More-than-Moore</i> and <i>Beyond CMOS</i> . |

|-----|------------------------------------------------------------------------------------------|

|     | The devices are generally sorted from the more conventional (left) to more               |

|     | exotic structures, based on non-charge mechanisms. Beyond CMOS devices                   |

|     | enable degrees of freedom and architectures not achievable using conventional            |

|     | CMOS. As a general trade-off, while some devices have been demonstrated and              |

|     | thoroughly characterized (CNTFET, TFET), the more exotic devices are also the            |

|     | most difficult to implement, and devices such as the BisFET [7] are still at a very      |

|     | early research stage. We highlighted in fuchsia the features of the device we will       |

|     | present in the remainder of this thesis. In addition, technologies highlighted in        |

|     | yellow are directly compatible with our device concept. Image adapted from An            |

|     | Chen, IEDM 2012                                                                          |

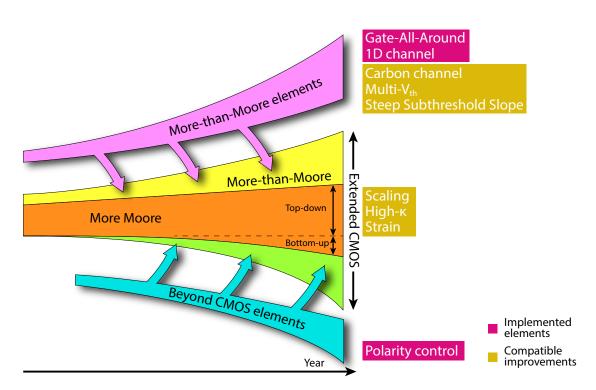

- 1.2 Relationship between technology-defining domains as described in the ITRS ERD chapter. Specifically, the *More Moore* roadmap brings to the extension of conventional CMOS by means of *More-than-Moore* elements, integrating new materials and structures, without enhancing the CMOS paradigm at a higher level, and *Beyond CMOS* elements, adding functional degrees of freedom beyond the capabilities of conventional CMOS. Image adapted from [17].

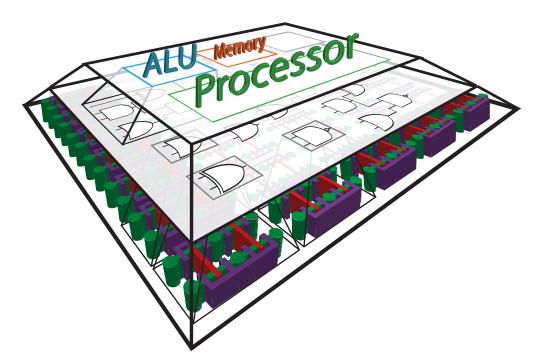

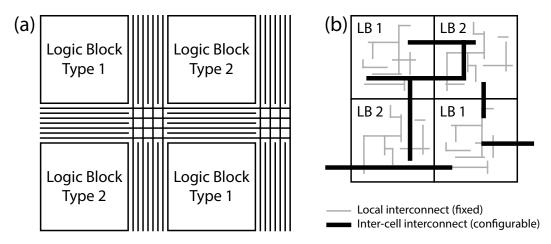

- 1.4 Conceptual representation of a regular sea-of-wires. Tiles are configured to realize logic functions that are part of a complex system such as a processor. . . 8

7

3

4

#### **List of Figures**

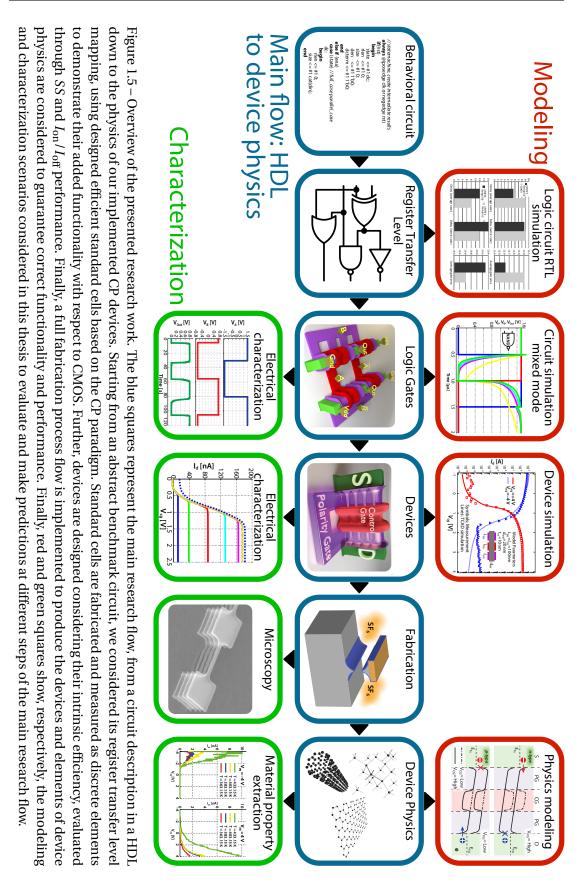

| 1.5 | Overview of the presented research work. The blue squares represent the main                   |

|-----|------------------------------------------------------------------------------------------------|

|     | research flow, from a circuit description in a HDL down to the physics of our                  |

|     | implemented CP devices. Starting from an abstract benchmark circuit, we con-                   |

|     | sidered its register transfer level mapping, using designed efficient standard                 |

|     | cells based on the CP paradigm. Standard cells are fabricated and measured                     |

|     | as discrete elements to demonstrate their added functionality with respect to                  |

|     | CMOS. Further, devices are designed considering their intrinsic efficiency, eval-              |

|     | uated through SS and $I_{\rm on}/I_{\rm off}$ performance. Finally, a full fabrication process |

|     | flow is implemented to produce the devices and elements of device physics are                  |

|     | considered to guarantee correct functionality and performance. Finally, red and                |

|     | green squares show, respectively, the modeling and characterization scenarios                  |

|     | considered in this thesis to evaluate and make predictions at different steps of               |

|     | the main research flow                                                                         |

|     |                                                                                                |

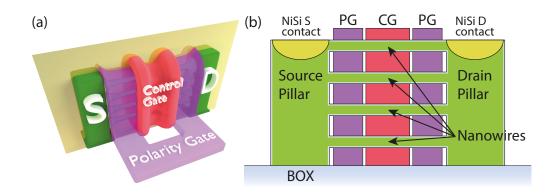

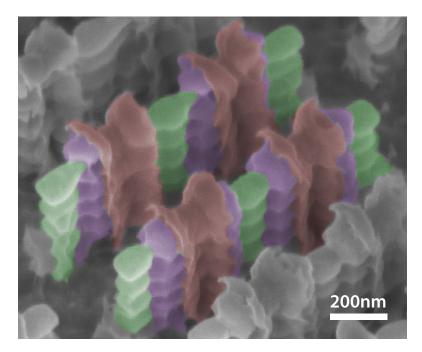

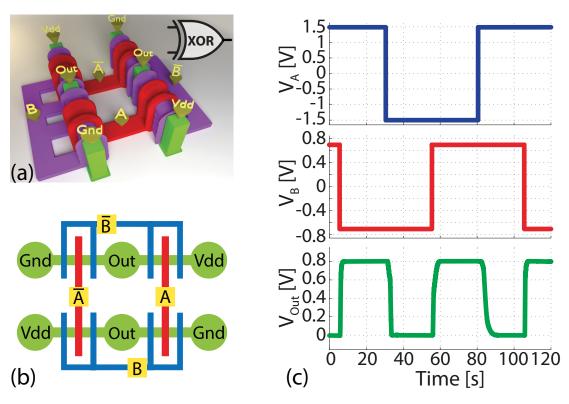

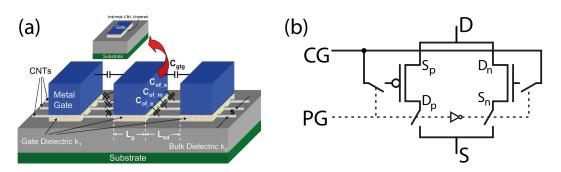

2.1 3D conceptual view of the proposed device. Source/Drain pillars supporting a vertical stack of nanowires are shown in green. The Gate-All-Around polarity gate, covering the side regions of the channel is shown in violet, while the central control gate is shown in red. The model is shown in proportion to the actual fabricated device dimensions.

10

16

17

18

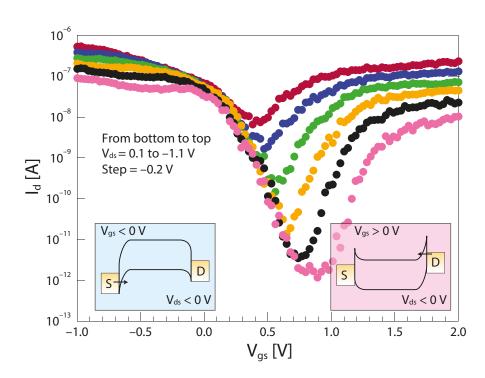

- 2.2 Typical strongly ambipolar device  $I_d-V_{gs}$  characteristic. The characteristics show a superposition of n-type and p-type conduction. The characteristics are quasi symmetric around a minimum  $I_d$  value. The shift of the minimum  $I_d$  to the left for increasing  $V_d$  biases is due to the fact that the dominating barrier for carrier injection in the channel changes from the source to the drain side along the characteristics. Therefore, when the barrier is at the source side (light blue inset), the device behaves as a p-type device, and the  $V_d$  has no influence on the source side barrier. When the  $V_{gs}$  is at high bias, however, the dominating barrier is at the drain side, and  $V_d$  has a strong influence on the barrier and thus the  $I_d$ . Image adapted from [9].

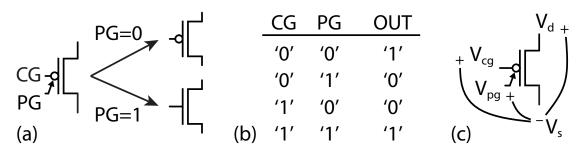

- 2.3 (a) CP FET circuit symbol, with the used polarization convention. (b) Conceptual single device truth table, with inputs following the convention: high  $V_{pg-s}$  or  $V_{cg-s}$  equals '1'; low  $V_{pg-s}$  or  $V_{cg-s}$  equals '0'. Equivalently, for the output, a high  $I_{ds}$  equals '1' and a low  $I_{ds}$  equals '0', as if the device was connected as pull-down network in a pseudo-logic gate (see Section 4.1). (c) Definitions of the used bias voltages. Unless otherwise stated, all voltages are defined with reference to  $V_s$ . Due to the inherent polarization symmetry provided by this device, the source is defined as the electrode at the lowest voltage between the two channel access contacts.

xiv

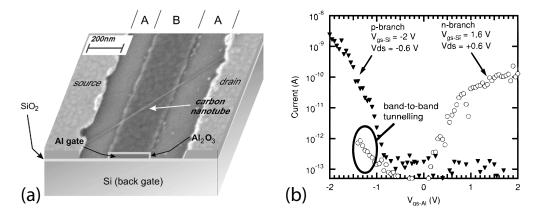

| 2.5  | (a) Composite image of the device proposed in [29]. A CNT is laid between two Ti S/D contacts. The substrate is isolated with 10 nm of SiO <sub>2</sub> and acts as back gate, while a second Al gate acts along the center section of the device channel. (b) Measured device subthreshold $I_d$ – $V_{gs}$ characteristics for high and low $V_{bg}$ , showing n-type and p-type behavior. Good suppression of ambipolar                                                                                                                                |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

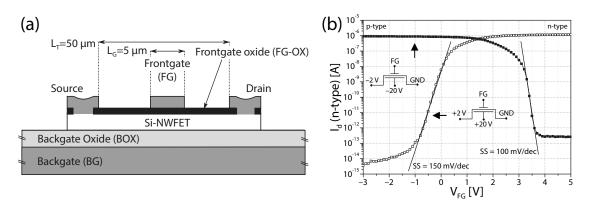

| 2.6  | conduction is shown. Image adapted from [29]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

|      | from [48, 51]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 |

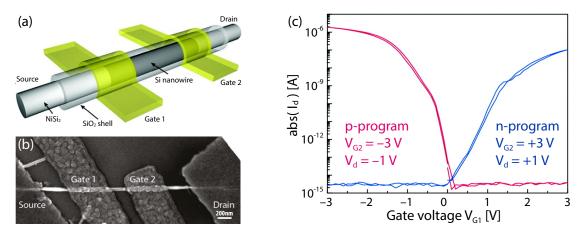

| 2.7  | (a) 3D conceptual view of the device proposed in [52], with two $\Omega$ -gate structures deposited on top of a bottom-up fabricated nanowire channel, in proximity of S and D metal electrodes. (b) SEM micrograph of a fabricated device and (c) $I_d$ - $V_{G1}$ transfer characteristics for the p-type ( $V_{G2} = -3 \text{ V}$ ) and n-type ( $V_{G2} = +3 \text{ V}$ ) polarizations. Note that the two characteristics are obtained for opposite $V_d$ polarizations of respectively $-1 \text{ V}$ and $+1 \text{ V}$ . Image adapted from [52] | 23 |

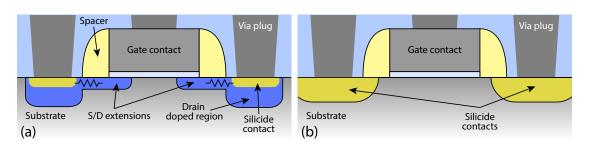

| 2.8  | (a) Conceptual cross section of a conventional bulk MOSFET structure. A complex series of lithographically masked dopant implantation/activation process steps are required to produce the S/D contacts. For simplicity, dopant wells and more advanced techniques such as halo regions are not shown in the picture. In (b), the greatly simplified silicided contact process is shown.                                                                                                                                                                  | 26 |

| 2.9  | (a) Position of the vertical device cross section. (b) Corresponding conceptual cross section of the device, showing the green S/D pillars sustaining a vertical stack of silicon Nanowires, with GAA PG structures in proximity of S/D electrodes and CG positioned at the middle of the channel.                                                                                                                                                                                                                                                        | 27 |

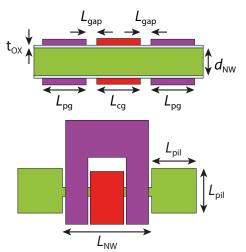

| 2.10 | Schematic view of the dimensions of Table 2.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

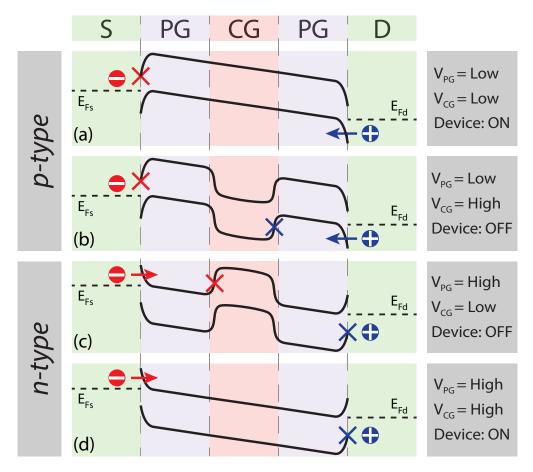

| 2.11 | Conceptual band diagrams for the controlled polarity SB FET device. Four cases are shown, describing the four combinations of high / low bias for the polarity gate and control gate of the device. Electron paths are shown with red arrows / crosses, hole paths are shown with blue arrows / crosses. Following the                                                                                                                                                                                                                                    |    |

|      | convention of Figure 2.3, the device is shown to embed the XOR functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29 |

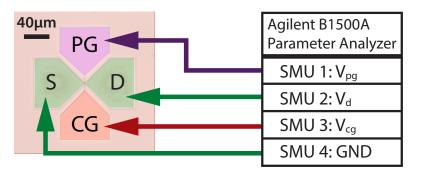

| 2.12 | Single device measurement setup. The measurements are performed landing four probes on large ( $\approx 80 \times 80 \mu$ m) pads fabricated as extensions of the pillars                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 0.10 | or gate electrodes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

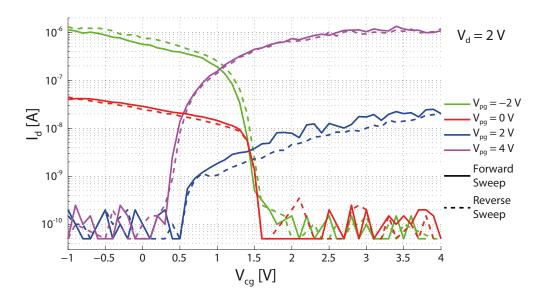

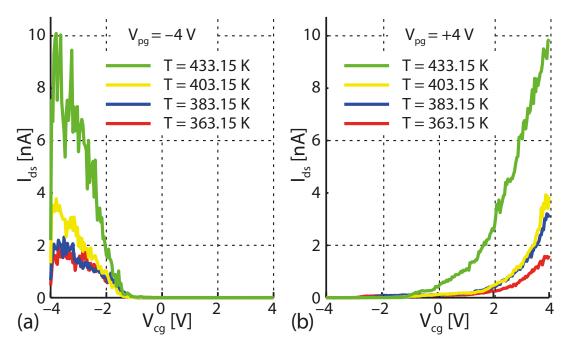

| 2.13 | Measured $I_d$ - $V_{cg}$ device transfer characteristic for various $V_{pg}$ bias voltages, at $V_d = 2$ V. The device behaves as a conventional semiconductor to semiconductor thermionic barrier with respect to $V_{cg}$ , due to the electrostatic doping effect imposed on the channel regions in proximity of S/D by the PG. The device is shown to be p-type up to $V_{pg} = 0$ V, and switch to n-type for $V_{pg} > 0$ V. Forward                                                                                                               |    |

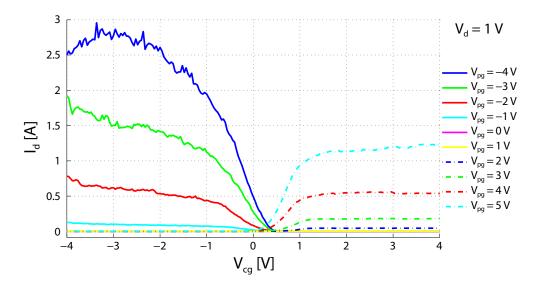

|      | (solid lines) and reverse (dashed lines) sweeps of $V_{cg}$ are shown, demonstrating the absence of relevant hysteresis effects during device operation                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

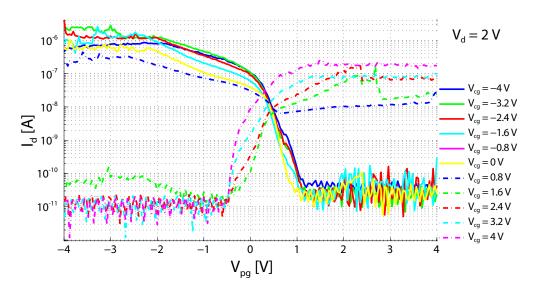

| 2.14 Measured $I_d-V_{pg}$ device transfer characteristic for various $V_{cg}$ bias voltages, at $V_d = 2$ V. The device is shown to switch between p-type and n-type with a crossing of the characteristics around $V_{pg} = 0.5$ V. At strong polarizations, the plots show the tri-slope behavior typical of SB FET switching. Note that the device is in the on state for $V_{pg} = V_{cg} = 0$ V (yellow line), as expected for correct logic circuit design compatibility.                                                                                                                                                                                                                                                                                                                                                               | 32 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

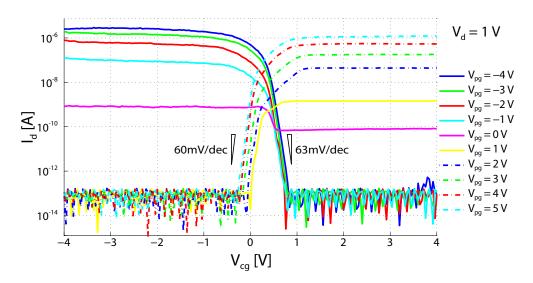

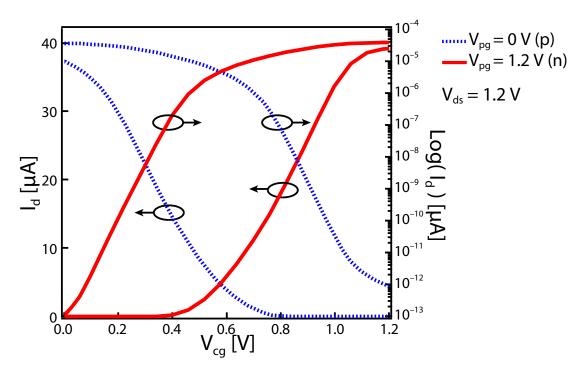

| 2.15 Measured $I_d-V_{cg}$ device transfer characteristic for various $V_{pg}$ bias voltages, at $V_d = 1, V$ . Subthreshold slopes are highlighted for the p-type and n-type characteristics. The values are shown for the case $V_{pg} = 4 \text{ V}$ , with $SS \approx 60 \text{ mV/dec}$ and for $V_{pg} = -4 \text{ V}$ , with $SS \approx 63 \text{ mV/dec}$ . $I_{on}/I_{off}$ performance reaches $10^8$ for $V_{pg} = -4 \text{ V}$ and $3.5 \times 10^7$ for $V_{pg} = 5 \text{ V}$ in the same physical device. Note that $I_{off}$ measurements are limited by our instrument bottom current range                                                                                                                                                                                                                                | 32 |

| 2.16 Linear $I_d$ – $V_{cg}$ characteristics corresponding to the semi-log plot of Figure 2.15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

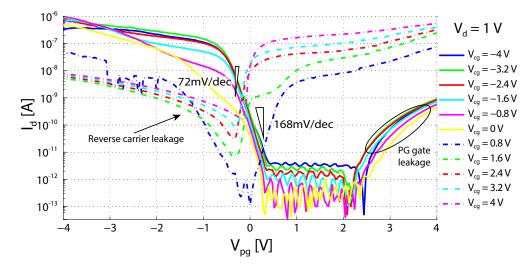

| 2.17 Measured $I_d$ – $V_{pg}$ device transfer characteristic for various $V_{cg}$ bias voltages, at $V_d = 1, V$ . Subthreshold slopes are highlighted for the p-type and n-type characteristics. The values are shown for the case $V_{cg} = 4 V$ , with $SS \approx 72 \text{ mV/dec}$ and for $V_{pg} = -1.6 V$ , with $SS \approx 168 \text{ mV/dec}$ . $I_{on}/I_{off}$ performance reaches $10^6$ for $V_{pg} = -0.8 V$ and $7.5 \times 10^5$ for $V_{pg} = 0.8 V$ in the same physical device. Note that in this device, for negative $V_{pg}$ voltages, the CG does not efficiently suppress reverse leakage of holes from the drain electrode. At the same time, the characteristics for negative $V_{cg}$ (solid lines) show strong leakage for high $V_{pg}$ voltages. This is due to the appearance of parasitic PG gate leakage. | 33 |

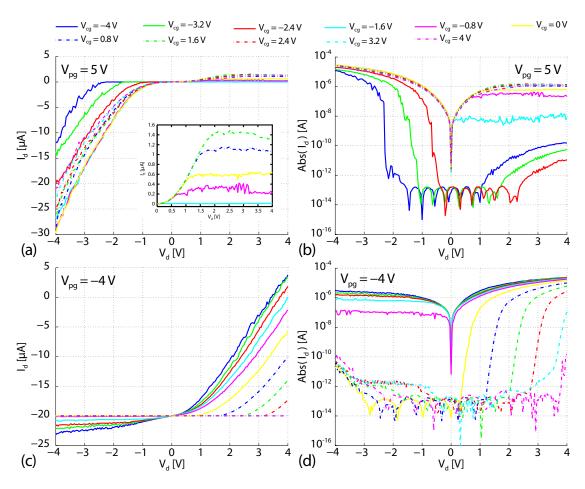

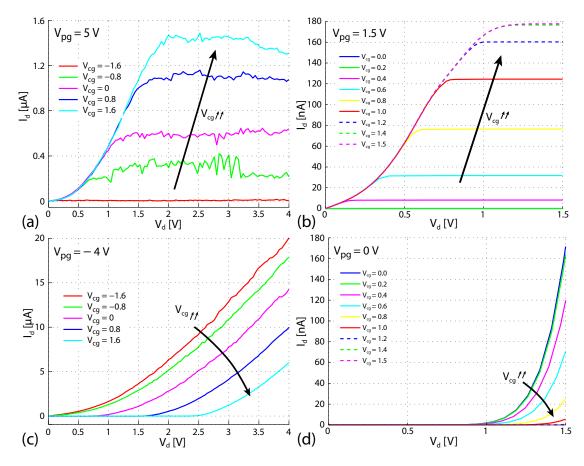

| 2.18 $I_d-V_d$ device output characteristics all measured in the same physical device<br>at various $V_{cg}$ polarizations, ranging from $V_{cg} = -4$ V to $+4$ V. (a) Linear $I_d-V_d$<br>for a strong n-type polarization, setting $V_{pg} = 5$ V. The inset shows a zoom-in<br>for positive $V_d$ values. (b) Semi-log plot of the same data. (c) Linear $I_d-V_d$ for a<br>strong p-type polarization, setting $V_{pg} = -4$ V and (c) semi-log plot of the same<br>data                                                                                                                                                                                                                                                                                                                                                                  | 34 |

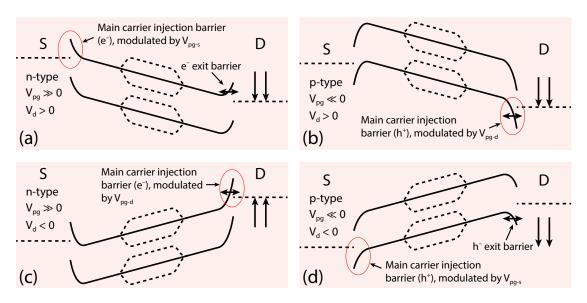

| 2.19 Conceptual band diagrams describing the cases of Figure 2.18. (a) and (c): n-type cases, for $V_{pg} \gg 0$ V (see Figure 2.18(a)); (b) and (d): p-type cases, for $V_{pg} \ll 0$ V (see Figure 2.18(c)). The main carrier injection barrier is highlighted with a red circle, while a $\leftrightarrow$ symbol shows the barrier most strongly modulated by $V_{pg}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36 |

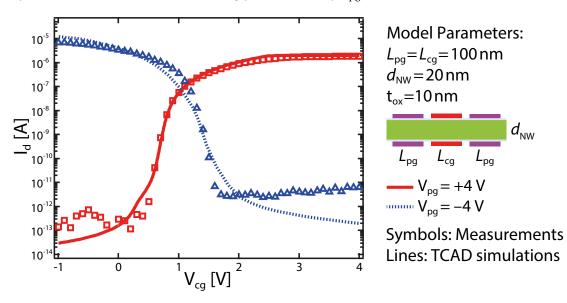

| 2.20 Basic TCAD model fitting for the SiNW device. The model is built considering a single nanowire device channel, with dimensions adapted from the fabricated device parameters, with gated regions of 100 nm in length, nanowire diameter of 20 nm and relaxed gate oxide thickness of 10 nm. In the plot, measured (symbols) and simulated (solid lines) characteristics show good overlap, with the fabricated device presenting quite high reverse leakage in the region for $V_{cg} \gg 0$ V due to the very strong $V_{pg} = -4$ V polarization. Image adapted from [64].                                                                                                                                                                                                                                                              | 36 |

| 2.21 | Comparison of measured $I_d-V_d$ device output characteristics with simulated characteristics using the basic TCAD device model described in Figure 2.20.<br>(a) Measured $I_d-V_d$ for $V_{pg} = 5 V$ (strong n-type polarization) and (b) simulated characteristics for the n-type polarization. (c) Measured $I_d-V_d$ for $V_{pg} = -4 V$ (p-type) and (d) simulated characteristics for the p-type polarization. Qualitatively similar behavior is observed, with a sublinear region at very low $V_d$ , typical for SB devices [65]. | 37 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

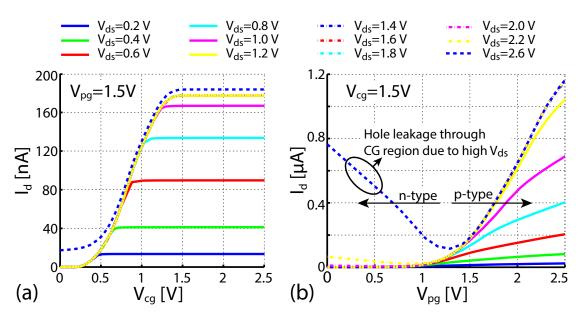

| 2.22 | Simulated $I_d-V_g$ plots at different $V_{ds}$ . (a) $I_d-V_{cg}$ characteristics and (b) $I_d-V_{pg}$ characteristics. Due to the asymmetry in geometry, different threshold voltages are expected in the two characteristics. Image adapted from [66].                                                                                                                                                                                                                                                                                  | 38 |

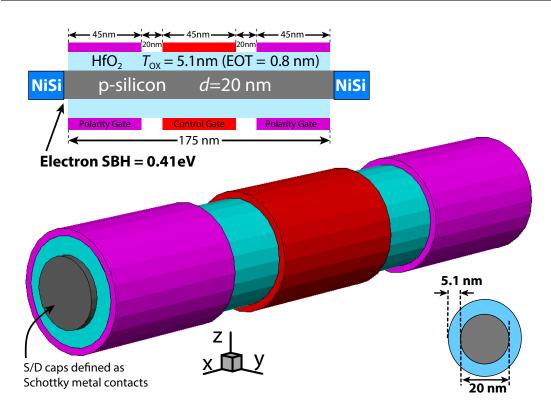

| 2.23 | Structure of the optimized controlled polarity SiNW device structure with three, 45 nm-long gate regions. High- $\kappa$ gate dielectric and metal gate with mid-gap work function are introduced to evaluate device performance after tuning of dimensions and materials. Schottky barrier height $q\Phi_{\rm Bp}$ for electrons is fixed at 0.41 eV at bothS and D electrodes. Image adapted from [64].                                                                                                                                  | 39 |

| 2.24 | $I_{\rm d}-V_{\rm cg}$ characteristics of the optimized device as predicted by TCAD simulation. Symmetric characteristics for n-type (blue curves) and p-type (red curves) polarizations are observed, respectively, bat $V_{\rm pg} = 1.2$ V and $V_{\rm pg} = 0$ V. For both polarizations, linear (left axis) and logarithmic (right axis) plots are shown                                                                                                                                                                              | 40 |

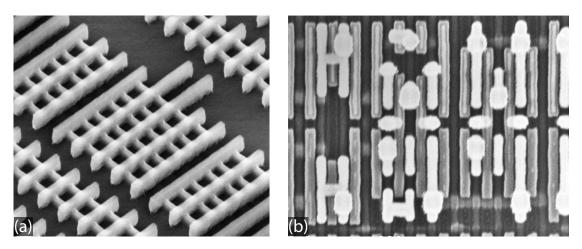

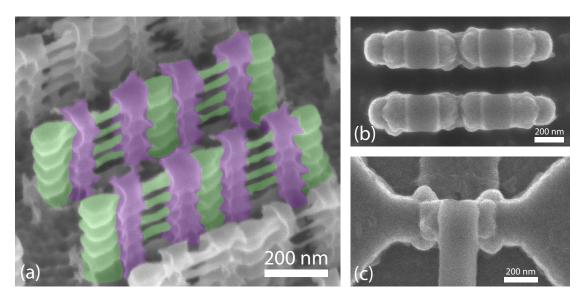

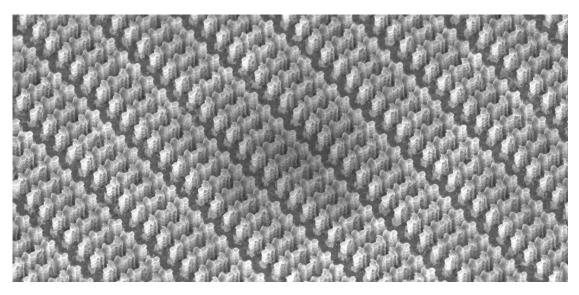

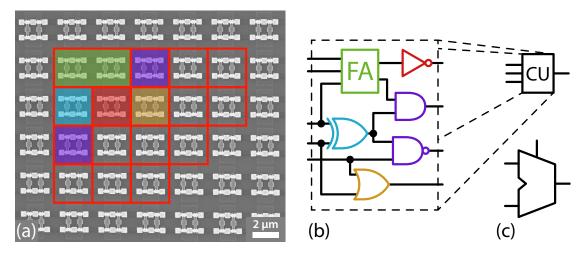

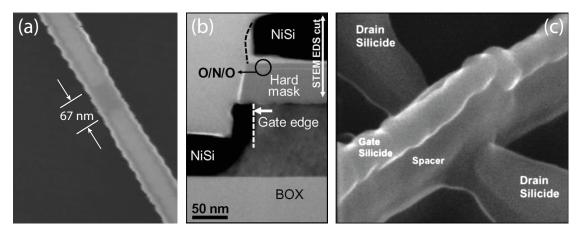

| 3.1  | Tilted SEM micrograph of a fabricated four-transistor tile. False colors show the nanowire stack sustaining pillars (green), with Polarity (violet) and Control gates (red) wrapped around the NW channel.                                                                                                                                                                                                                                                                                                                                 | 44 |

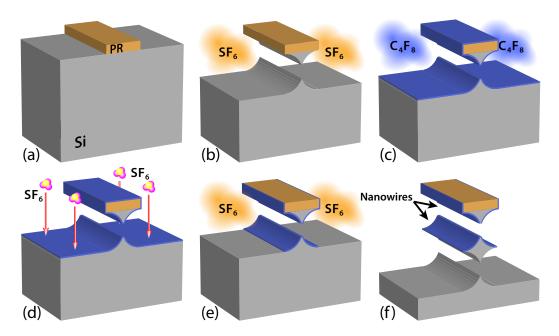

| 3.2  | Deep Reactive Ion Etching applied to nanowire fabrication. (a) a photoresist mask is applied on crystalline silicon; (b) physical/chemical $SF_6$ etching is applied, creating an undercut below the mask pattern; (c) conformal thin passivation is applied using $C_4F_8$ gas; (d) the vertically accessible surface passivation is readily removed by the partly anisotropic $SF_6$ etching; (e) finally, a new undercut is produced by chemical etching by the $SF_6$ , leading to (f) a new nanowire                                  | 47 |

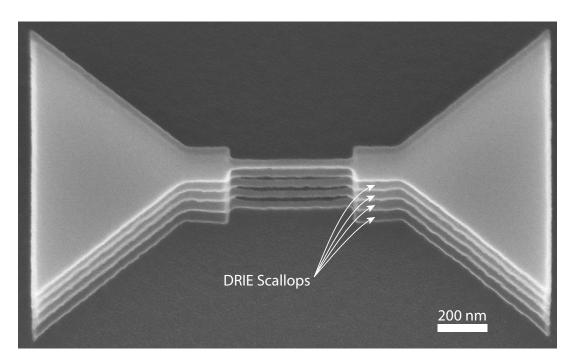

| 3.3  | SEM micrograph of a structure etched using DRIE on a silicon bulk wafer. Scal-<br>loping due to the cycling nature of the etching is visible on the sidewalls. The                                                                                                                                                                                                                                                                                                                                                                         |    |

number of scallops typically indicates the number of etching cycles, although the first isotropic etching step may not result in a visible groove, due to the

surface imperfections, including native oxide, require a breakthrough time. ... 48

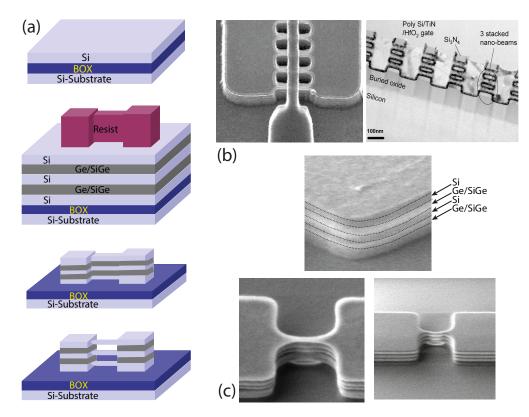

| 3.4 | (a) Process flow for Si/SiGe superlattice stacked nanowire fabrication (image adapted from [72]). (b) SEM micrograph and TEM cross section of fabricated densely packed crystalline silicon nano-beams, including conformal HfO <sub>2</sub> and polysilicon GAA electrodes (images adapted from [73]). (c) Etched sidewall of a Si/SiGe epitaxial superlattice, with highlighted layers grown on the BOX of an SOI substrate. In the bottom-left image, the wire structures appearing after SiGe wet etch and in the bottom-right image, the nanowires being released and reduced in diameter after self-limiting oxidation and oxide removal. Images adapted from [72].                                                                                                                                                                                                             | 49 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

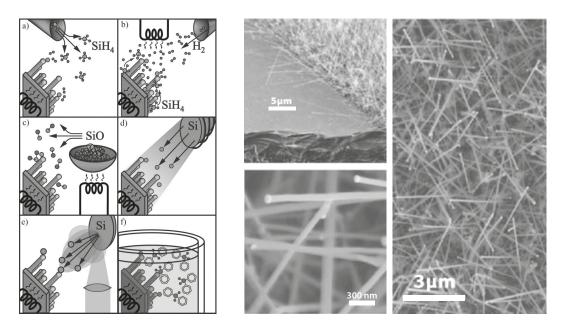

| 3.5 | (Left side) Schematics of experimental setups for silicon nanowire growth. a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45 |

|     | CVD, b) annealing in reactive atmosphere, c) evaporation of SiO, d) MBE, e) laser<br>ablation, and f) solution-based growth. Image adapted from [76]. (Right side)<br>SEM micrographs of grown nanowires on a substrate. The wires are randomly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | distributed and oriented, however, smooth sidewalls and large length to width ratios can be attained using bottom-up growth methodologies [82]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 |

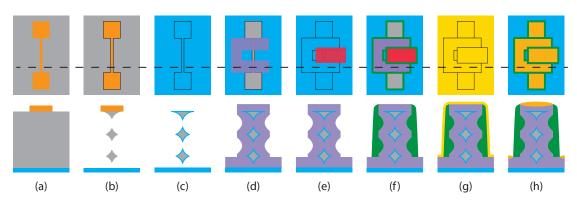

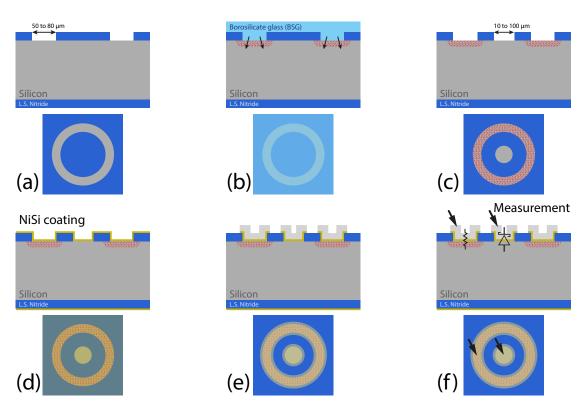

| 3.6 | Vertically stacked CP NW process flow conceptual overview. (a-h) Top and cross section views of the main fabrication process steps. (a) The nanowires are patterned by EBL on an SOI substrate with two larger areas at the sides which will form the sustaining pillars (Phase 3); (b) the nanowires are created in a single DRIE (BOSCH) procedure (Phase 4); (c) dry gate oxide is formed by on the nanowires and (d) conformal gate polysilicon is deposited around the nanowires and patterned by EBL (Phases 5–7); (e) a second oxidation and polysilicon deposition is performed. The control gate (red) is patterned by EBL self-aligned to the polarity gate (violet) (Phases 8–10). Finally, (f) low-stress SiN spacers are formed to isolate the structures (Phase 11), (g) nickel is blanket-deposited on all the wafer surface and (h) annealing is performed to produce | 50 |

|     | NiSi S/D and gate contacts, after which excess metallic Ni is removed by wet etching (Phase 12).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51 |

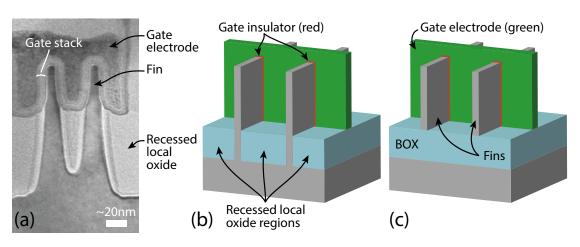

| 3.7 | <ul> <li>(a) State-of-the-art 14 nm technology node FinFET device cross section from Intel, fabricated on a bulk Si substrate and isolated using recessed local oxide regions that leave only the top, thin fin tip exposed. Image adapted from [3].</li> <li>(b) Conceptual 3D view of the local recessed oxide isolation on bulk substrates. In this process, after etching the fins, an oxide is deposited on the whole wafer surface and fills the gaps between the fins. Subsequently, CMP is performed to planarize the oxide and blanket oxide etching is performed to etchback the oxide until the fin tips are exposed. (c) The simpler SOI FinFET structures, with BOX isolation. In this case, a single etching of the device layer is sufficient to obtain isolated fins of controlled height</li></ul>                                                                   | 52 |

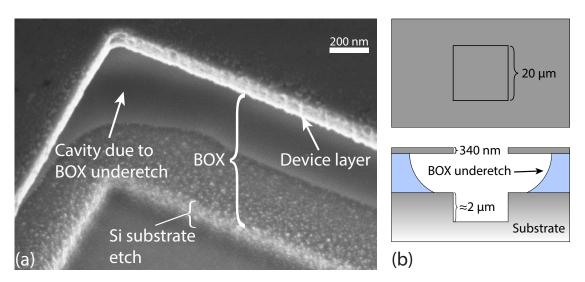

| 3.8 | (a) Tilted SEM view (35°tilt) of an etched EBL alignment marker in an SOI sub-<br>strate with 2 µm BOX thickness. (b) Concentual ten view and cross section of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | strate, with $2\mu$ m BOX thickness. (b) Conceptual top-view and cross section of the marker after dry etching of the device layer, BHF wet etching of the BOX and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|     | further dry etching of the Si substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53 |

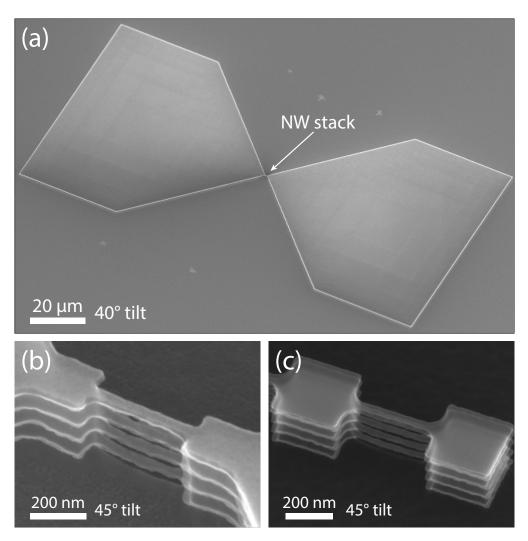

| 3.9 (a) Tilted SEM view of a DRIE-etched nanowire stack with large contact areas for landing probe station needles. (b) Close-up on the device nanowire stack for the large-contact device (50% pattern area fill) and (c) a nanowire stack with small sustaining pillars. In this last case the pattern is much more sparse, and typically lower LER can be obtained in this case.                                                                                                                                                                                                                                                                                                                                                                                                               | 54 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

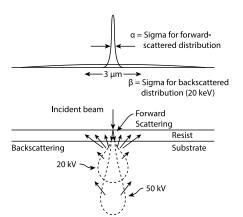

| 3.10 Forward and Backscattered electron influence area for a typical semiconducting substrate coated with a thin PR layer. Image adapted from [85]5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55 |

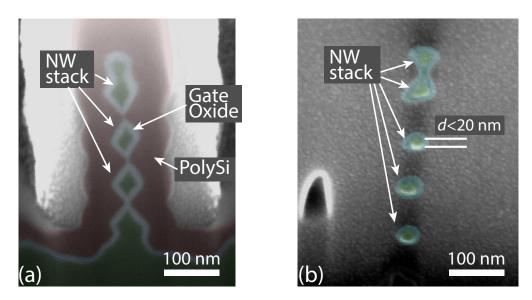

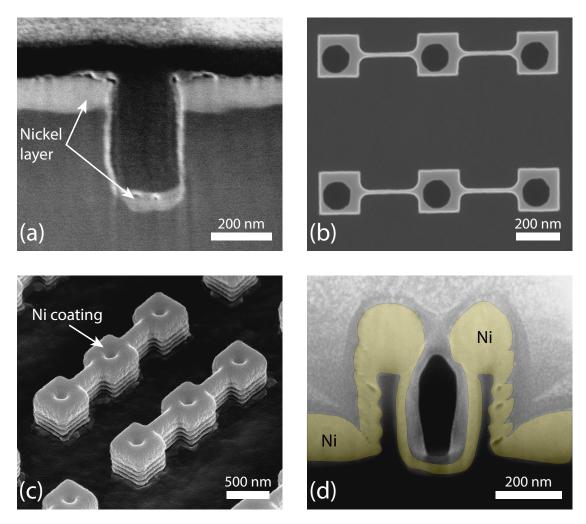

| 3.11 SEM/FIB cross-section views of fabricated nanowire stacks, showing (a) the<br>nanowire stack with 8 nm gate oxide and 50 nm thick conformal polysilicon GAA<br>structure, and (b) an optimized nanowire stack with nanowires of $d < 20$ nm<br>diameter, surrounded by a $\approx$ 5 nm gate oxide. Image adapted from [64] 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57 |

| <ul> <li>3.12 (a) SEM micrograph showing the effect of destructive notching on DRIE-etched structures on an SOI substrate. Due to the charging of the BOX surface, the device layer structures are damaged and detached completely from the BOX. Shifted and collapsed pillars can be observed. (b) Structures etched with a less aggressive DRIE recipe. In this case, no notching and detachment of the structures is observed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                      | 58 |

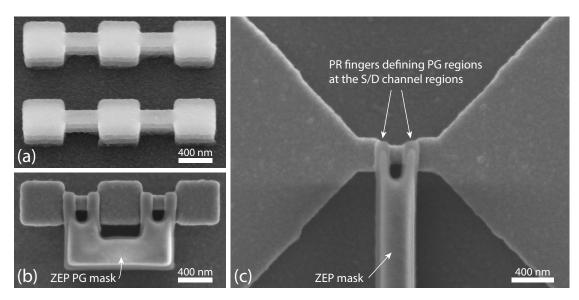

| <ul> <li>3.13 (a) Tilted (40°) SEM view of a nanowire stack after oxidation and deposition of 50 nm conformal LPCVD polysilicon layer (Phase 5). (b) The same nanowire stack tilted at 40° after potoresist coating, e-beam exposure and PR development. (c) The PG mask for the design with large pads. The PG fingers covering the side channel regions are visible, as well as the elongated PG mask leading to the PG large contact pad (not visible in the figure)</li></ul>                                                                                                                                                                                                                                                                                                                 | 60 |

| <ul> <li>3.14 (a) Tilted SEM view with false colors of the nanowire stacks after deposition and etching of the PG structures (Phase 7), showing the PG 100 nm long gate sections (violet) in contact with S/D sustaining pillars (green). Image adapted from [64].</li> <li>(b) Self-aligned CG ZEP520 PR mask for the small pillar devices: the mask is patterned with an overlap to the underlying PG electrodes. (c) CG mask for the large pillar devices for measurement: in this case the CG structure extends away from the device to form a large contact pad.</li> </ul>                                                                                                                                                                                                                  | 61 |

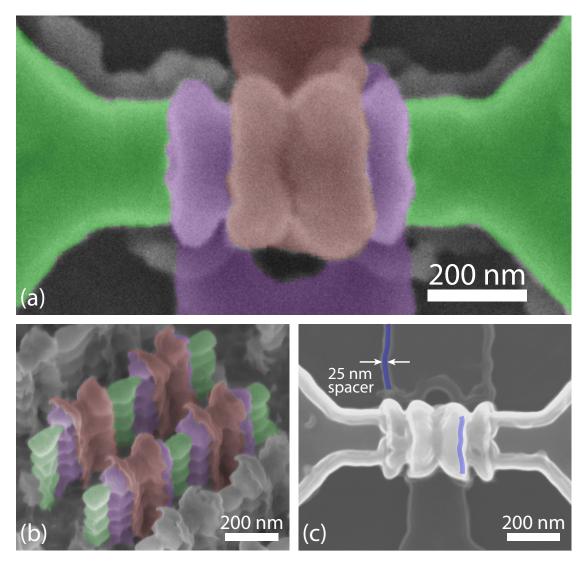

| 3.15 (a) SEM micrograph with false colors of a large-contact pad device with patterned CG and PG electrodes. (b) Tilted SEM view of an array of completed devices. The structures are colored following the convention of Figure 2.1, with green S/D pillars, violet PG and red CG electrodes. (c) A large-contact pad device after definition of the L.S. SiN spacer. The spacer is visible in correspondence of all the vertical step features. In order to facilitate the interpretation of this image, the spacer is highlighted in blue in two regions of the device, one along the PG polysilicon extension (top) and the other between CG and PG electrodes at the top of the nanowire stack (center of the image). The other regions are left without color overlay for improved clarity. | 62 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

#### List of Figures

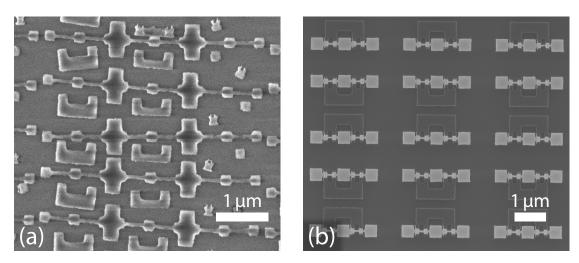

| 3.16 | Tilted SEM micrograph of a fabricated dense device array on bulk substrate. The transistors are grouped in four-transistor tiles, with $1.5 \times 0.9 \mu\text{m}$ size, for a density of $\approx 3 \times 10^8$ transistors/cm <sup>2</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

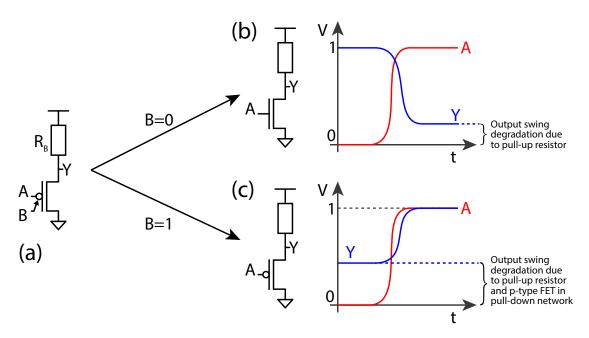

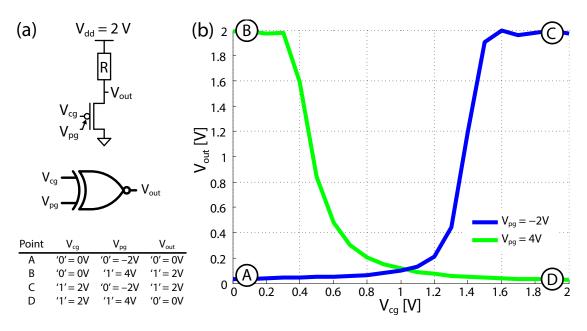

| 4.1  | CP FET based pseudo-logic one-transistor gate. When the polarity control gate is driven to logic '0', the transistor becomes n-type and the gate becomes an inverter; if the control gate has value '1', the transistor becomes p-type and the output follows the input value. On the right, qualitative $V_{in}-V_{out}$ characteristics are shown.                                                                                                                                                                                                                                                                                                                                              | 74 |

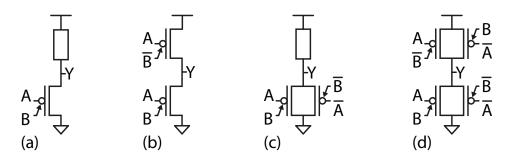

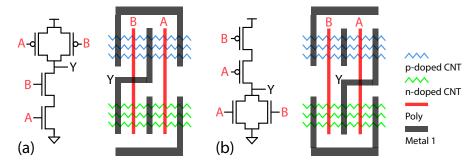

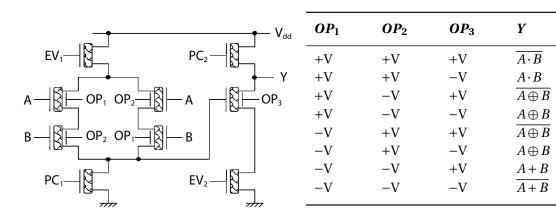

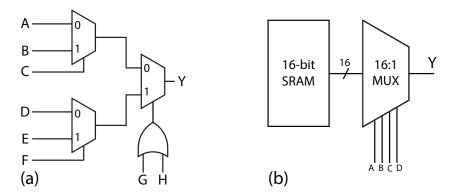

| 4.2  | CP FET static logic families; (a) pass transistor pseudo-logic, (b) pass transistor complementary logic, (c) transmission gate pseudo-logic and (d) transmission gate complementary logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76 |

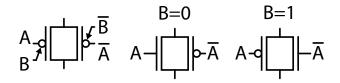

| 4.3  | CP based transmission gate structure. At any time, at least one transistor in the structure transfers a strong logic signal, i.e., at any time one transistor is polarized as n-type and the other is polarized as p-type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76 |

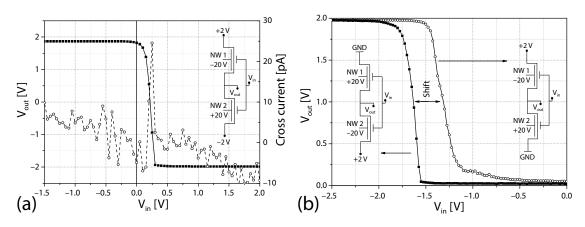

| 4.4  | Switching characteristics (solid symbols) of a CMOS inverter circuit fabricated<br>using CMOS NW FETs by applying the appropriate voltages at the back gates<br>(schematic shown as inset). (b) Two traces of the switching characteristics of the<br>voltage selectable CMOS inverter illustrate the versatile programming capability<br>of the NW devices. Filled symbols represent NW FET 1 working as p-fet and NW<br>FET 2 as n-fet. Interchanging back-gate bias and supply voltage polarity, the<br>transistor types are swapped and again a CMOS inverter characteristic (open<br>symbols) is observed. Image adapted from [48]                                                           | 77 |

| 4.5  | Reconfigurable inverter circuit on a single wire, separated to create two tran-<br>sistors as described in [47]. (a) Conceptual configuration setup for the shown<br>measured characteristics. (b) SEM tilted view with false colors highlighting S/D<br>contacts and $\Omega$ gate electrodes for the fabricated two-transistor circuit. (c) Con-<br>figured inverter transfer characteristic showing switching at $V_{dd}/2$ with steep<br>switching slope and full swing output voltage range. Significant current only<br>flows during switching demonstrating the complementary function. (d) Time<br>domain measured sweeps, showing correct inverter operation. Image adapted<br>from [47] | 70 |

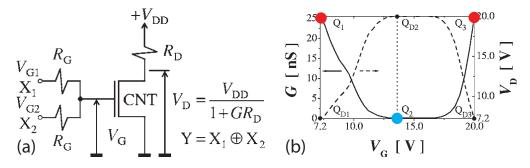

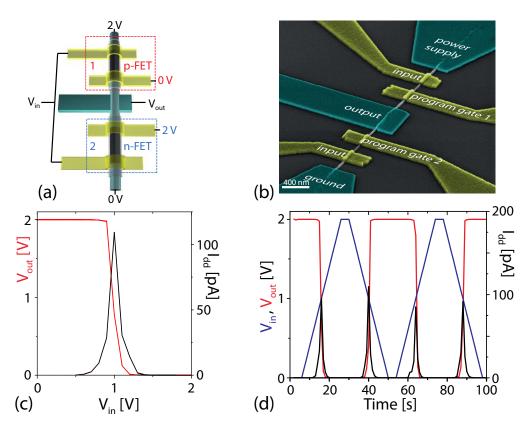

| 4.6  | from [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78 |

|      | transistor. Image adapted from [64]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80 |

| 4.7  | Measured inverter characteristic (b) obtained by connecting two transistors as in<br>the logic gate circuit (a) The polarity gates are biased so as to obtain a CMOS-like<br>inverter, with a p-type transistor in the pull-up network and a n-type transistor |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | in the pull-down network. Image adapted from [64].                                                                                                                                                                                                             | 81 |

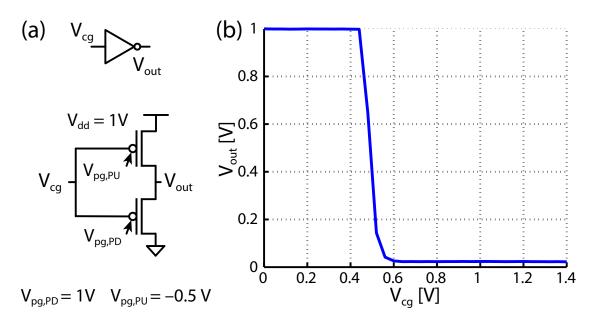

| 4.8  | Output characteristic of a two-transistor complementary XOR logic gate. Similar                                                                                                                                                                                |    |

|      | to a two-transistor non-inverting gate, the buffer characteristic is degraded due                                                                                                                                                                              |    |

|      | to the presence of weakly polarized n-type FET in the pull-up network and                                                                                                                                                                                      |    |