### Tunnel Field Effect Transistors: from Steep-Slope Electronic Switches to Energy Efficient Logic Applications

THÈSE Nº 6802 (2015)

PRÉSENTÉE LE 9 OCTOBRE 2015 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES DISPOSITIFS NANOÉLECTRONIQUES PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

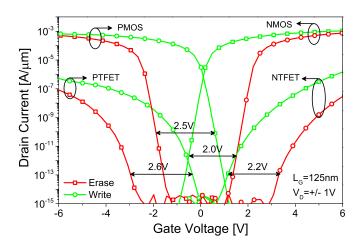

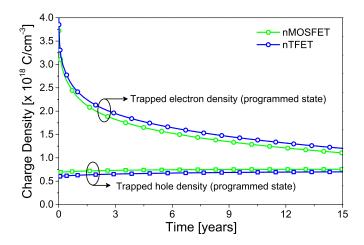

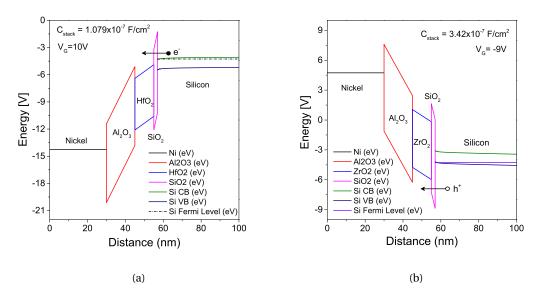

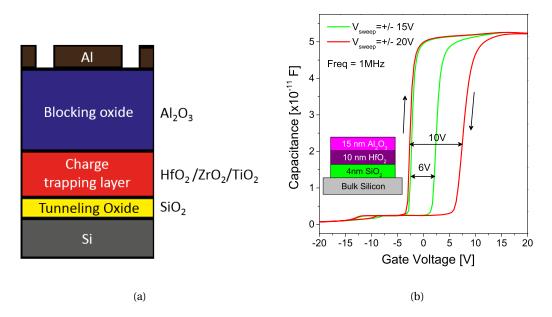

PAR

Arnab BISWAS

acceptée sur proposition du jury:

Prof. M. Kayal, président du jury Prof. M. A. lonescu, directeur de thèse Prof. L. Selmi, rapporteur Prof. E. Pop, rapporteur Dr J. M. Sallese, rapporteur

In a conflict between the heart and the brain, follow your heart. — Swami Vivekananda

Dedicated to my father and mother...

## Acknowledgements

This thesis marks an end to an amazing journey of more than four years filled with wonderful and exciting experiences. This thesis has been written during my stay as a PhD student at the Ecole Polytechnique Fédérale de Lausanne(EPFL), and I would like to express my gratitude to all the people who supported me scientifically and emotionally in this journey.

First of all, I would like to express my deep appreciation for my thesis advisor, Prof. Adrian M. Ionescu, for his willingness to take me into his research group and for the wonderful opportunity he gave me to work on this very interesting topic. Thanks to his support, encouragement and constant discussions, my motivation for the project has always been very strong, also in the most difficult of times.

I would like to acknowledge the members of the jury for having accepted to review my PhD thesis, for the valuable feedback on my work and their time to disseminate it: Prof. Eric Pop from the Stanford University(USA), Prof. Luca Selmi from University of Udine(Italy), Dr. Jean-Michel Sallese from EPFL and Prof. Maher Kayal, president of the jury, from EPFL.

Special thanks to all scientific partners I have had the pleasure to interact with within the STEEPER and E2SWITCH European projects. Thank you for the useful discussion and brainstorming during the meetings on this challenging subject: IUNET, IBM Zurich, CEA Leti, IMEC Leuven, Cambridge CMOS sensors, FZJ Research Center Jülich and ETH Zurich.

I am also grateful to Luca De Michielis for his continuous help and support throughout my PhD. His knowledge in simulations and the insightful discussions that we have had on device physics, have been a great aid in writing this thesis. I also thank Livio for supervising my masters thesis in Nanolab and introducing me to the world of Tunnel FETs. I thank all my past and present Nanolab colleagues Erick, Mariazel, Ali, Clara, Cem, Jose, Francesco, Maneesha, Nilay, Sara, Ji, Seb, Alex, Giovanni, Donatello, Jyotshna, Anupama, Mohammad, Nenad, Matthieu and Montse for all the good times over the years.

I also want to thank Dr. Wladek Grabinsky and Dr. Antonios Bazigos, for all their help throughout my PhD, specially in setting up the characterization related projects. Thanks to all the engineers in CMI, EPFL who trained me in various equipments used in the fabrication process and for their help in solving problems related to clean room processing.

The awesome-twosome Nanolab secretaries Isabelle and Karin were always there to help with any bureaucratic formality. Thank you for all your help and kindness. I also would like to thank the doctoral secretaries Marie and Lucie for their help during the beginning and towards the end of my PhD. Thanks also to Joseph, Roland, Marc, Raymond and Cedric for all the administrative help on the IT infrastructures.

A special thanks to my colleagues Hoel and Elizabeth with whom I have spent my formative years in Nanolab and shared a special bond. We even called ourselves as the "three muske-teers". I will miss all the fun we had together specially during the conference trips. Special thanks to my best pals in town Wolfgang, Emanuele and Pankaj for being part of my journey through these years. Along with Francesco(Chicco) and Erick they have been like brothers to me. I will definitely miss all the good times over lunch, coffee time discussions and countless Friday and Saturday nights. My time in Nanolab would not have been the same without all the fun and camaraderie we have shared over the years. I will forever cherish the great times we had together.

Special thanks to fellow Bengalis and my good friends in campus Soumya(Bob) and Namrata. It was always cool hanging out with you guys in mother tongue goodness. I also would like to thank my officemates Nilay and Cem with whom I shared my office space ELB343 in Nanolab. Their friendship and support created an exceptional working environment. A special thanks goes to all my friends who made my stay in Lausanne so special and enjoyable: Gabriele, Clemens, Pietro, Enver, Oguz, Charly, Francesco(Chicco), Chloé, Annie, Massimo, Gianrocco, Loris, Rammohan, Anurag, Bakul, Aamani, Czuee, Chhavi and the list goes on.

I also acknowledge the help of all my master project and semester project students whose thesis work was directly or indirectly supervised by me during the course of my PhD: Saurabh, Francesco, Maneesha and Riccardo.

I would like to express my deepest appreciation for Irene who have hosted me in Lausanne for more than four years. Your love and kindness made me forget how far away from home I really was.

Last but not the least, there are no words to describe my gratitude towards my family for their unconditional love, inspiration and encouragement: my father, mother, sister and brother-inlaw. They have been a pillar of support guiding me through thick and thin of times.

Lausanne, 27th July 2015

Arnab Biswas

### Abstract

At the heart of the microelectronic revolution is the complimentary-metal-oxide semiconductor(CMOS) technology. Scaling of the MOSFET is governed by the need of higher speeds and package density. The main reason to make transistors smaller is to pack more and more devices in a given chip area. It is also expected that smaller transistors switch faster. Upon further decreasing the MOSFET device dimensions, the leakage current of the MOSFET increases,while the supply voltage can no longer be scaled down, both of which result in increased power consumption. By lowering  $V_{DD}$  from 500mV to 250mV while preserving the effective voltage, the leakage power has been shown to increase unacceptably by a factor of 275 in a 45-nm bulk CMOS technology. Another way of reducing the voltage supply without performance loss is to increase the turn-on steepness, which means decreasing the average sub-threshold swing,  $SS_{avg}$ , over 3 or 4 decades of current. Therefore, devices with a steep *SS*, called steep-slope switches, are expected to enable  $V_{DD}$  scaling.

The primary aim of this work has been the investigation of one such steep-slope switch: the Tunnel Field Effect Transistor, starting from a compact modelling perspective to its possible applications. We discuss the basic working principle of Tunnel FET and the main differences of a Tunnel FET with respect to a conventional MOSFET are pointed out and explained. We study in detail the band-to-band tunneling model in detail with reference to the Landauer's formulation and Kane's model. An overview of the all the band-to-band tunneling models available in commercial TCAD simulators are presented. A TCAD based simulation study is done to understand the main device characteristics. The importance of Miller effect specifically to Tunnel FETs and its impact on circuit behaviour is also discussed. We propose a new structure to mitigate this effect on the circuit performance of the Tunnel FET.

We developed a compact DC/AC model for the double gate Tunnel FET, which is capable of describing the I-V and C-V characteristics in all regimes of operation. The model takes in to account ambipolarity, drain side breakdown and all tunneling related physics. An indirect temperature dependence is also added to the model to study the temperature independent behaviour of tunneling. The model was further implemented in a Verilog-A based circuit simulator. Following calibration to experimental results of Silicon and strained-Silicon TFETs, the model has been also used to benchmark against a 28nm FDSOI CMOS node for digital and analog applications. Typical analog FOMs showed the benefits of a TFET over CMOS particularly in the low operating power regime. The circuits built with Tunnel FETs also showed interesting temperature behaviour which was superior to the compared CMOS node.

In the same work, we also explore and propose solutions for using TFETs for low power memory applications. Both volatile and non-volatile memory concepts are investigated and explored. The application of a Tunnel FET as a capacitor-less memory has been experimentally demonstrated for the first time, which opens a new field of applications for TFETs. We propose a new Tunnel FET based non-volatile memory concept, which uses vertical line tunneling to boost the memory operation and validated with simulations. We also developed process flows for the new structures for future realization in the clean room in EPFL.

**Key words:** Physics of semiconductor devices; modeling and simulation; Tunnel FET, bandto-band tunneling; compact model; Verilog-A; TCAD simulation; steep sub-threshold slope switches; analytical compact model; circuit and device level benchmarking; characterization; capacitor-less DRAM; SONOS; non-volatile memory.

## Résumé

Au cœur de la révolution microélectronique est la technologie offerte métal oxyde semiconducteur (CMOS). Mise à l'échelle du MOSFET est régie par la nécessité de vitesses plus élevées et de la densité de l'emballage. La principale raison à réaliser des transistors plus petits est d'emballer plus en plus d'appareils dans une zone de la puce donnée. Il est également prévu que les petits transistors commutent rapidement. Lors de diminuer encore les dimensions du dispositif MOSFET, le courant de fuite du transistor MOSFET augmente, tandis que la tension d'alimentation ne peut plus être réduite, à la fois de l'augmentation qui se traduit par une consommation de courant. En abaissant  $V_{DD}$  de 500mV à 250mV, de la préservation de la tension tandis que efficace, la puissance de fuite a été démontré que l'augmentation inacceptable par un facteur de 275 dans une technologie CMOS en vrac de 45 nm. Une autre façon de réduire la tension d'alimentation sans perte de performance est d'augmenter le tour sur la pente, ce qui signifie diminuer le swing moyenne sous-seuil,  $SS_{avg}$ , sur 3 ou 4 décennies de courant. Par conséquent, les appareils dotés d'une pente raide *SS*, appelés commutateurs forte pente, sont attendus pour permettre  $V_{DD}$  mise à l'échelle.

Ces travaux de recherche ont porté sur les transistors à effet de champ, à effet tunnel (Tunnel FET or TFET) et à homo-jonction partant d'une perspective de modélisation compacte jusqu'à leurs applications possibles. En premier lieu, une étude basée sur une simulation TCAD est effectuée pour comprendre les caractéristiques principales du dispositif. Le principe de fonctionnement de base du Tunnel FET est abordé. Les principales différences d'un Tunnel FET par rapport à un MOSFET classique sont mises en exergue et expliquées. Le modèle de l'effet tunnel bande à bande a été étudié en détail en référence à la formule de Landauer et au modèle de Kane. Un aperçu de l'ensemble des modèles d'effet tunnel bande à bande disponibles dans les simulateurs commerciaux TCAD est présenté. L'importance de l'effet Miller en particulier pour les Tunnel FETs et son impact sur le comportement des circuits sont également traités.

Un modèle DC/AC compact, capable de décrire les caractéristiques I-V et C-V dans tous les régimes de fonctionnement a été développé. Le modèle prend en compte l'ambipolarité et toute la physique relative à l'effet tunnel. Une dépendance à la température est également ajoutée au modèle pour étudier le comportement indépendant de la température de l'effet tunnel. Le modèle a en outre été implémenté dans un simulateur de circuit en Verilog-A. Après étalonnage sur les résultats expérimentaux de TFETs sur silicium et silicium contraint, le modèle a également été utilisé comme référence pour comparaison avec un nœud CMOS FDSOI 28nm pour des applications numériques et analogiques. Les facteurs de mérite analogiques

typiques ont démontré les avantages du TFET par rapport au CMOS, en particulier dans le régime de fonctionnement à faible puissance. Les circuits construits avec des Tunnel FETs ont également montré un comportement avec la température intéressant et supérieur au nœud CMOS comparé.

Dans cette recherche, nous explorons et proposons aussi des solutions pour l'utilisation des TFETs pour des applications de mémoire à faible puissance. Les deux concepts de mémoire volatile et non-volatile sont examinés et explorés. L'utilisation d'un Tunnel FET comme mémoire sans condensateur a été démontrée expérimentalement pour la première fois, ouvrant un nouveau champ d'applications pour les TFETs. Un nouveau concept de mémoire non volatile basée sur des TFETs et qui utilise un effet tunnel en ligne verticale pour améliorer le fonctionnement de la mémoire a été proposé et validé avec des simulations. De nouveaux concepts de dispositifs ont été proposés et leurs procédés de fabrication sont développés pour une réalisation future dans la salle blanche de l'EPFL.

**Mots clefs :** Physique des semiconducteurs ; modélisation et simulation ; Tunnel FET ; effet tunnel bande à bande ; modèle compact ; Verilog-A ; simulation TCAD ; commutateurs à pente sous seuil abrupte ; modèle analytique compact ; analyse comparative de dispositifs et circuits ; caractérisation ; mémoire vive dynamique (DRAM) sans condensateur ; SONOS ; mémoire non-volatile.

## Zusammenfassung

Im Herzen des mikroelektronischen Umdrehung der komplementäre Metall-Oxid-Halbleiter (CMOS) -Technologie. Skalierung des MOSFET wird durch den Bedarf an höherer Geschwindigkeit und Packungsdichte bestimmt. Der Hauptgrund Transistoren kleiner zu machen ist, mehr und mehr Vorrichtungen in einer gegebenen Chipfläche zu verpacken. Es wird auch erwartet, dass kleinere Transistoren schneller schalten. Bei weiterer Verringerung der MOSFET Geräteabmessungen, den Leckstrom des MOSFET ansteigt, während die Versorgungsspannung nicht mehr verkleinert werden kann, die beide zu einem erhöhten Energieverbrauch. Durch die Absenkung  $V_{DD}$  von 500mV bis 250mV und gleichzeitig die effektive Spannung hat die Leckleistung wurde gezeigt, dass unannehmbar um einen Faktor von 275 in einem 45-nm-CMOS-Technologie Schütt erhöhen. Ein anderer Weg zum Reduzieren der Versorgungsspannung, ohne Leistungsverlust ist, um die Einschalt-Steilheit, die die durchschnittliche Unterschwellenschwenkverringerungseinrichtung zu erhöhen,  $SS_{avg}$ , mehr als 3 oder 4 Jahrzehnten Strom. Daher Geräte mit einem steilen *SS*, genannt Steillagen-Schalter, wird erwartet, dass  $V_{DD}$  Skalierung zu ermöglichen.

Das Ziel dieser Arbeit war die Untersuchung von Homoübergangs-Tunnel-Feldeffekt transistoren (TFET) ausgehend von der Perspektive einer kompakten Modellierung bis hin zu möglichen Anwendungen. Zu Beginn wurde eine TCAD basierte Simulationsstudie durchgeführt, um die wichtigsten Geräteeigenschaften zu verstehen. Das grundlegende Arbeitsprinzip eines Tunnel-FET wird diskutiert. Die Hauptunterschiede eines Tunnel-FET gegenüber eines herkömmlichen MOSFET werden aufgezeigt und die Unterschiede werden erläutert. Das Band-zu-Band-Tunnelmodell wurde im Detail mit Bezug auf die Landauer Formulierung und das Kanes Modell untersucht. Es wird eine Übersicht aller Band-zu-Band-Tunnelmodelle verfügbar in kommerziellen TCAD Simulatoren vorgestellt. Die Bedeutung des Miller-Effekts speziell für Tunnel-FETs und seine Auswirkung auf das Schaltungsverhalten wird ebenfalls diskutiert.

Eine kompaktes DC/AC-Modell wurde entwickelt, welches in der Lage ist, die Beschreibung der I-V und C-V Eigenschaften in allen Betriebsbereichen zu beschreiben. Das Modell berücksichtigt Ambipolarität, Abbau der Abflussseite und die gesamte tunnelbezogenen Physik. Außerdem wurde zu dem Modell eine Temperaturabhängigkeit hinzugefügt, um das temperaturunabhängige Verhalten des Tunnelns zu untersuchen. Zusätzlich wurde das Modell in einen Verilog-A basierten Schaltungssimulator implementiert. Nach der Kalibrierung mit experimentellen Ergebnissen von Silicon und Strained-Silicon-TFETs wurde das Modell ebenfalls als Benchmark gegen einen 28-nm-CMOS FDSOI Knoten für digitale und analoge Anwendungen verwendet. Typische analoge FOMs zeigten die Vorteile eines TFET gegenüber CMOS insbesondere im niedrigen Betriebsleistungsbereich. Die mit Tunnel-FETs aufgebauten Schaltungen zeigten außerdem ein interessantes Temperaturverhalten, welches im Vergleich zum CMOS Knoten überlegen war.

In der gleichen Arbeit untersuchen wir auch die Verwendung von TFETs für niedrige Stromspeicheranwendungen und bieten Lösungsvorschläge an . Sowohl flüchtige als auch nichtflüchtige Speicherkonzepte wurden untersucht und erforscht. Die Anwendung eines Tunnel-FET als kondensatorloser Speicher wurde experimentell zum ersten Mal gezeigt, was neue Anwendungsbereiche für TFETs eröffnet. Ein neues TFET basierendes nicht-flüchtiges Speicherkonzept, welches vertikales Linientunneln verwendet, um den Speichervorgang zu steigern, wurde vorgeschlagen und mit Simulationen validiert. Neue Gerätekonzepte wurden vorgeschlagen und Prozessabläufe für dieselben wurden für die zukünftige Realisierung im Reinraum des EPFL entwickelt.

**Stichwörter:** Physik der halbleiterbauelemente; modellierung und simulation; Tunnel-FET; Band-zu-Band-Tunneling; kompaktes modell; Verilog-A; TCAD simulation; steiler unter-schwellenknotenschalter; analytischen Kompakt modell; Schaltungs-und Geräteebenen Benchmarking; Charakterisierung; kondensatorlose DRAM; SONOS; nicht-flüchtiger Speicher.

## Contents

| Ack  | cnov   | ledgements                                                           | i     |

|------|--------|----------------------------------------------------------------------|-------|

| Abs  | strac  | t (English/Français/Deutsch)                                         | iii   |

| List | t of f | igures                                                               | xiii  |

| List | t of 1 | ables                                                                | xxiii |

| Acr  | ony    | ms                                                                   | XXV   |

| 1    | Intr   | oduction                                                             | 1     |

|      | 1.1    | The microelectronic revolution                                       | . 1   |

|      | 1.2    | Evolution of nano-electronics                                        | . 2   |

|      | 1.3    | The scaling problem                                                  | . 3   |

|      |        | 1.3.1 Challenges in MOSFET scaling                                   | . 4   |

|      |        | 1.3.2 Beyond CMOS devices: an alternative ?                          | . 6   |

|      | 1.4    | Thesis overview                                                      | . 8   |

| 2 '  | Tun    | nel FET                                                              | 11    |

| :    | 2.1    | Band to band tunneling                                               | . 11  |

|      |        | 2.1.1 Tunneling theory                                               | . 13  |

| :    | 2.2    | Overview of Simulation tools available                               | . 15  |

|      |        | 2.2.1 Sentaurus Local Tunneling model                                | . 16  |

|      |        | 2.2.2 Sentaurus Dynamic non-Local Tunneling model                    | . 17  |

|      |        | 2.2.3 Silvaco non-Local Tunneling model                              | . 20  |

|      | 2.3    | Basic working principle of a TFET                                    | . 22  |

|      |        | 2.3.1 Point tunneling Tunnel FET                                     |       |

|      |        | 2.3.2 Line tunneling device                                          |       |

|      |        | 2.3.3 Temperature dependence                                         |       |

| 2    | 2.4    | FD-SOI Tunnel FET simulation and fitting to measurements             |       |

|      |        | 2.4.1 Calibration Methodology                                        |       |

|      |        | 2.4.2 Crystal orientation dependent tunneling generation rate        |       |

|      | 2.5    | Miller effect                                                        |       |

|      |        | 2.5.1 Miller effect in Tunnel FETs                                   |       |

|      |        | 2.5.2 Proposed new structure to mitigate Miller effect in Tunnel FET | . 34  |

### Contents

|   | 2.6 | Sumn      | nary                                                    | 37        |

|---|-----|-----------|---------------------------------------------------------|-----------|

| 3 | Con | npact r   | nodelling of Tunnel FET                                 | 39        |

|   | 3.1 | Overv     | iew                                                     | 39        |

|   | 3.2 | DC m      | odel version 1 (non-local)                              | 40        |

|   |     | 3.2.1     | Model Description                                       | 40        |

|   |     | 3.2.2     | Model Evaluation                                        | 45        |

|   | 3.3 | DC m      | odel version 2 (local)                                  | 48        |

|   |     | 3.3.1     | Model Description                                       | 49        |

|   |     | 3.3.2     | Surface potential                                       | 49        |

|   |     | 3.3.3     | Tunnelling path estimation                              | 50        |

|   |     | 3.3.4     | Tunneling current calculation                           | 53        |

|   |     | 3.3.5     | Comparison with simulations                             | 53        |

|   | 3.4 | Charg     | e model of a DG-TFET                                    | 56        |

|   |     | 3.4.1     | CV measurements on FD-SOI TFETs from LETI               | 57        |

|   |     | 3.4.2     | Suitability of 100-0 (drain/source) charge distribution | 57        |

|   |     | 3.4.3     | Description of charge model of a DG-TFET                | 58        |

|   |     | 3.4.4     | Comparison with TCAD simulation                         | 59        |

|   | 3.5 | Verilo    | g-A implementation of full compact model                | 60        |

|   |     | 3.5.1     | Single stage inverter                                   | 62        |

|   |     | 3.5.2     | 2-bit half adder                                        | 63        |

|   |     | 3.5.3     | 15 stage ring oscillator                                | 64        |

|   | 3.6 | Mode      | l calibration and benchmarking study                    | 65        |

|   |     | 3.6.1     | Description of fabricated devices                       | 67        |

|   |     | 3.6.2     | 28nm FDSOI CMOS design kit                              | 67        |

|   |     | 3.6.3     | Calibration with experimental results                   | 68        |

|   |     | 3.6.4     | Device level analog benchmarking                        | 69        |

|   |     | 3.6.5     | Circuit level analog benchmarking                       | 74        |

|   | 3.7 | Sumn      | nary                                                    | 78        |

|   | T   | 1 1 1 1 1 |                                                         | =0        |

| 4 |     |           | Ts based Volatile Memories                              | <b>79</b> |

|   | 4.1 | •         | should TFETs be used as a memory                        | 79        |

|   | 4.2 |           | as a volatile memory: Capacitorless memory introduction | 81        |

|   | 4.3 |           | Tunnel FET as 1T/0C DRAM                                | 84        |

|   |     | 4.3.1     | Principle of Operation                                  | 85        |

|   |     | 4.3.2     | Proposed Programming Scheme                             | 86        |

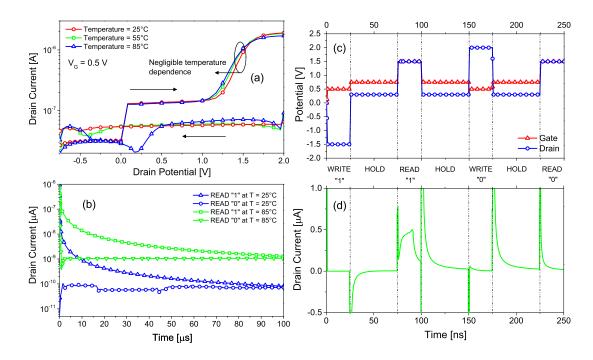

|   |     | 4.3.3     | Experimental Results                                    | 88        |

|   |     | 4.3.4     | Temperature Dependence                                  | 89        |

|   |     | 4.3.5     | Transient Measurements                                  | 89        |

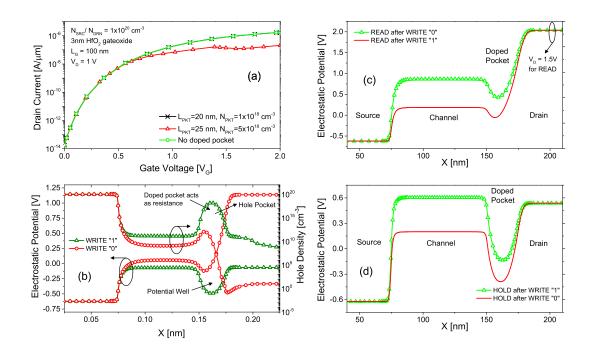

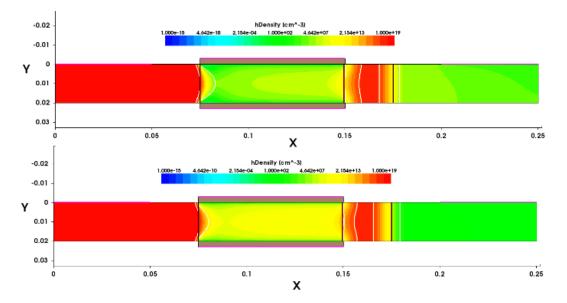

|   | 4.4 | -         | d pocket device simulations                             | 96        |

|   |     | 4.4.1     | Principle of operation                                  | 96        |

|   |     | 4.4.2     | DRAM operation                                          | 98        |

|   | 4.5 | Sumn      | nary                                                    | 100       |

| 5  | Tun                 | nel FE   | Γ based Non Volatile Memories              | 101 |  |

|----|---------------------|----------|--------------------------------------------|-----|--|

|    | 5.1                 | Flash    | Memory                                     | 101 |  |

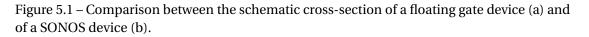

|    |                     | 5.1.1    | Working Principle                          | 102 |  |

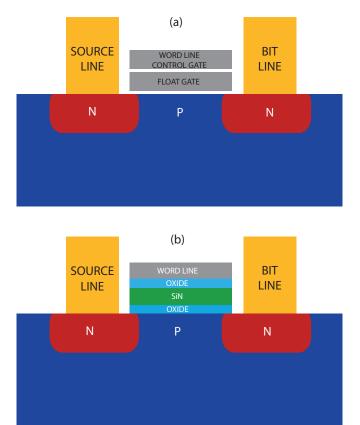

|    |                     | 5.1.2    | Floating gate vs. SONOS                    | 104 |  |

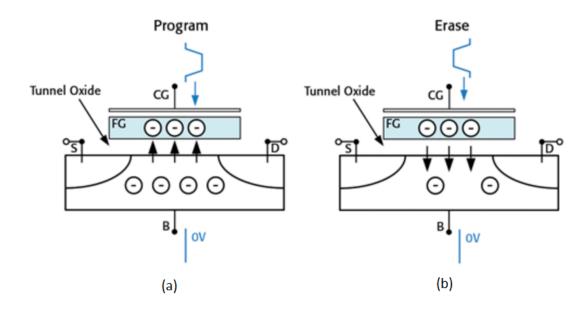

|    |                     | 5.1.3    | State of the art                           | 105 |  |

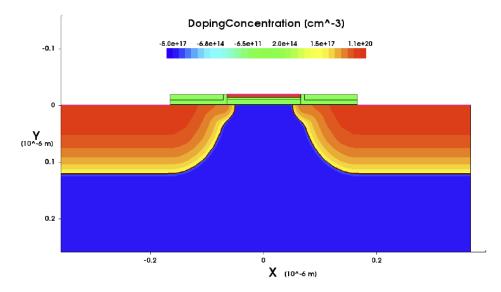

|    | 5.2                 | Simul    | ation methodology                          | 107 |  |

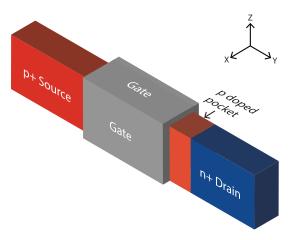

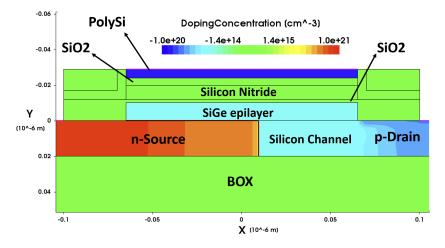

|    |                     | 5.2.1    | Vertical p-type TFET architecture          | 111 |  |

|    | 5.3                 | Vertic   | al TFET non-volatile memory device         | 113 |  |

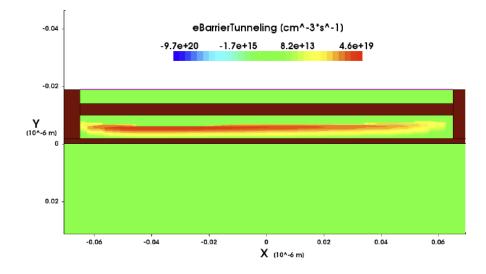

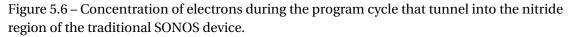

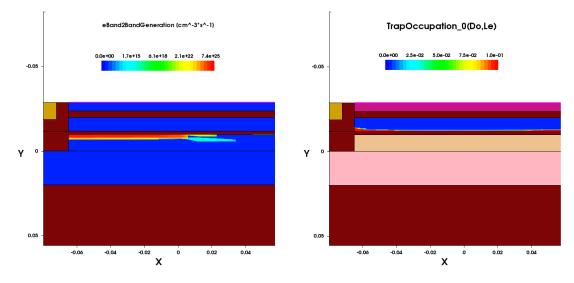

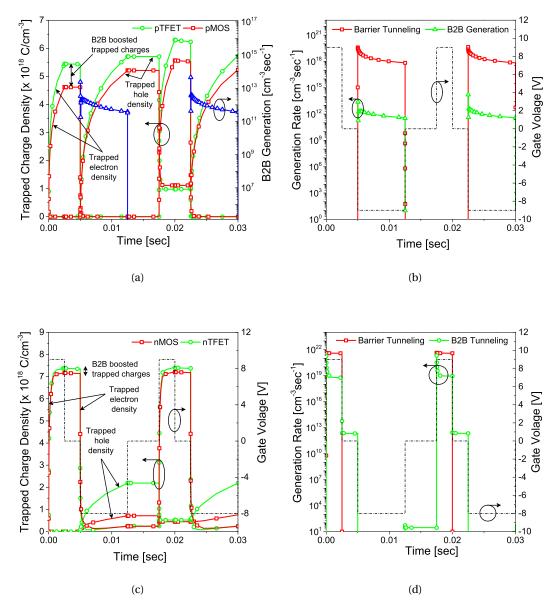

|    |                     | 5.3.1    | Simulation of memory operation             | 114 |  |

|    |                     | 5.3.2    | Simulation of Retention characteristics    | 116 |  |

|    | 5.4                 | Fabric   | cation of TFET non-volatile memory         | 117 |  |

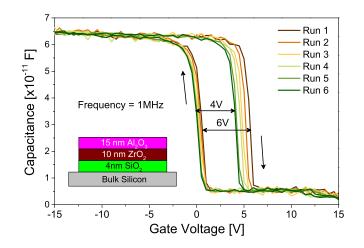

|    |                     | 5.4.1    | Evaluation of gate-oxide stacks            | 118 |  |

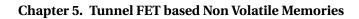

|    |                     | 5.4.2    | Process flow                               | 120 |  |

|    |                     | 5.4.3    | Results obtained                           | 122 |  |

|    | 5.5                 | Sumn     | nary                                       | 122 |  |

| 6  | Con                 | clusio   | ns                                         | 127 |  |

|    | 6.1                 | Futur    | e perspectives                             | 128 |  |

| A  | Calo                | culatio  | n of parameters in section 2.4             | 131 |  |

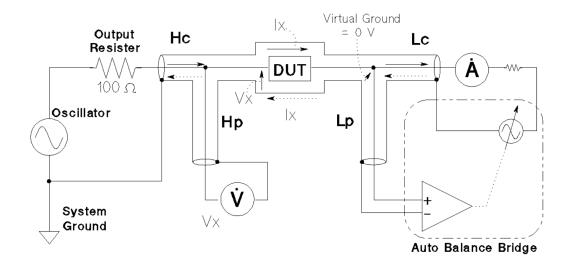

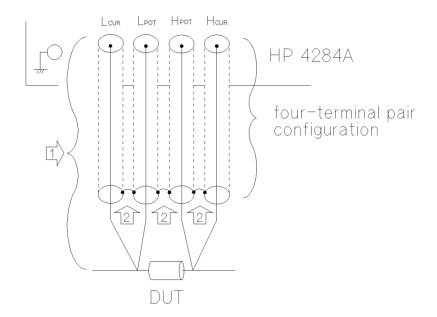

| B  | Сар                 | acitan   | ce measurements                            | 133 |  |

|    | B.1                 | Notes    | on trans-capacitance measurements in a FET | 135 |  |

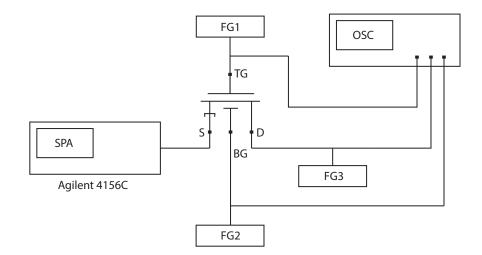

| С  | Puls                | sed me   | asurement details                          | 137 |  |

| Bi | bliog               | graphy   |                                            | 148 |  |

| M  | y Puł               | olicatio | ns                                         | 149 |  |

| Сι | Curriculum Vitae 15 |          |                                            |     |  |

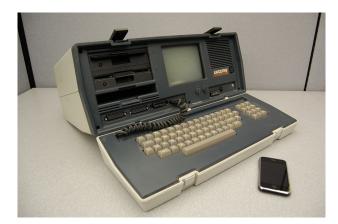

| 1.1        | Evolution of microelectronic technology: An Osborne Executive portable com-<br>puter, from 1982 with a Zilog Z80 4MHz CPU, and a 2007 Apple iPhone with a<br>412MHz ARM11 CPU; the Executive weighs 100 times as much, has nearly 500<br>times as much volume, cost approximately 10 times as much (adjusted for infla- |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | tion), and has about 1/100th the clock frequency of the smart-phone. [source wikipedia]                                                                                                                                                                                                                                 | 1  |

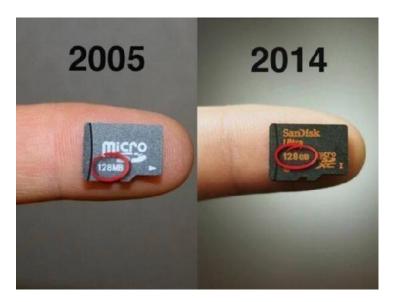

| 1.2        | Evolution of memory technology from 2005 to 2014. Over a span of 9 years the                                                                                                                                                                                                                                            |    |

|            | capacity of a micro SD card has increased by a factor of 1024. [source Wikipedia]                                                                                                                                                                                                                                       | 3  |

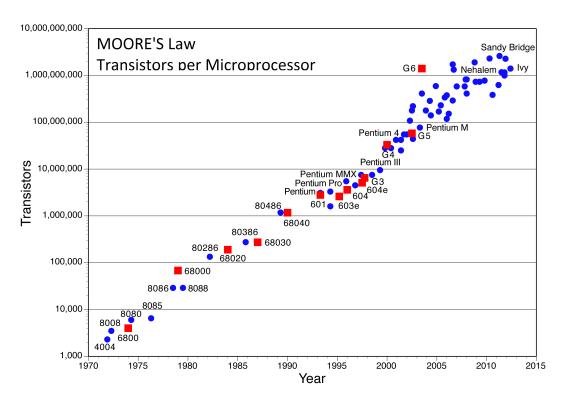

| 1.3        | Plot of CPU transistor counts against dates of introduction; the line corresponds to exponential growth with transistor count doubling every two years. [source                                                                                                                                                         |    |

|            | wikipedia]                                                                                                                                                                                                                                                                                                              | 4  |

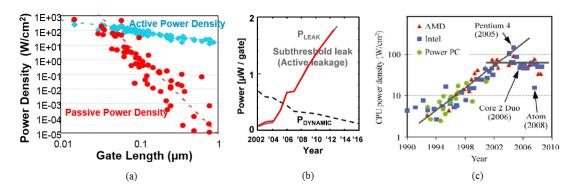

| 1.4        | (a)Power consumption trends with gate length scaling (b) comparison of dy-<br>namic and leakage power trend over the years. [courtesy IBM coorp.] and (c)<br>Near-exponential increase of CPU power density in recent decades has flattened                                                                             |    |

|            | with the introduction of multi-core CPUs [4]                                                                                                                                                                                                                                                                            | 5  |

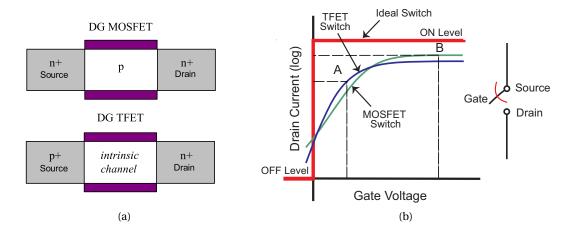

| 1.5        | (a)Comparison of an n-type double gate MOSFET and Tunnel FET schematic.<br>The different source doping is to be noted. (b)Qualitative comparison of a<br>conventional MOSFET (green) and a Tunnel FET (blue), which has a steep off–on                                                                                  |    |

|            | transition and the lowest <i>I</i> <sub>OFF</sub>                                                                                                                                                                                                                                                                       | 7  |

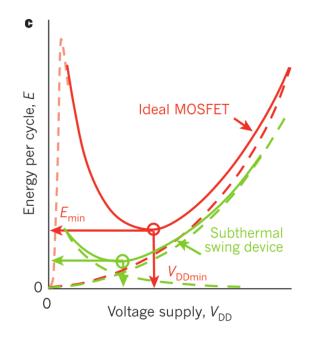

| 1.6        | Comparison of the minimum switching energy, $E_{min}$ , and the corresponding voltage supply, $VDD_{min}$ , for a subthermal swing device (S < 60 mV decade <sup>-1</sup> , green curve) and the ideal MOSFET (S = 60 mV decade <sup>-1</sup> , red) at the same                                                        |    |

|            | $I_{ON}/I_{OFF}$ . (source [5])                                                                                                                                                                                                                                                                                         | 8  |

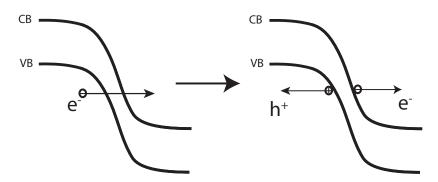

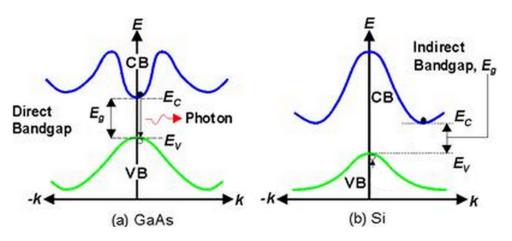

| 2.1<br>2.2 | Generation of an electron and hole pair as a result of band-to-band tunneling.<br>Direct and indirect semiconductor band structure (a)GaAs (direct) (b)Silicon                                                                                                                                                          | 11 |

|            | (indirect) [7]                                                                                                                                                                                                                                                                                                          | 12 |

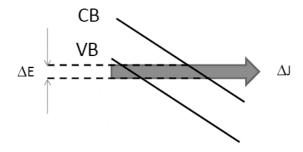

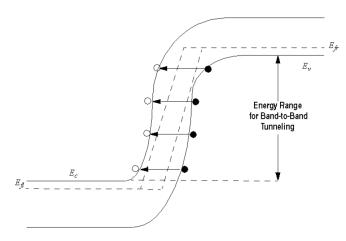

| 2.3        | Schematic showing energy window and $\Delta J$ (current) [9]                                                                                                                                                                                                                                                            | 13 |

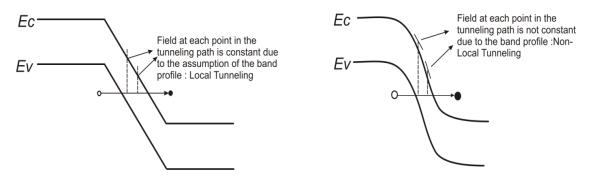

| 2.4        | Schematic showing the difference between local (left) and non-local tunneling                                                                                                                                                                                                                                           |    |

| 2.5        | model                                                                                                                                                                                                                                                                                                                   | 15 |

|            | to default.                                                                                                                                                                                                                                                                                                             | 17 |

|            |                                                                                                                                                                                                                                                                                                                         |    |

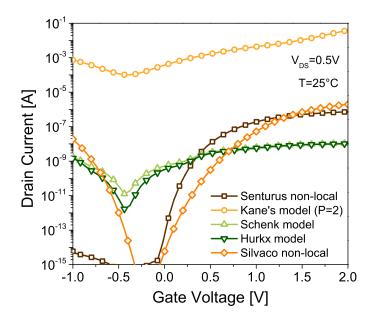

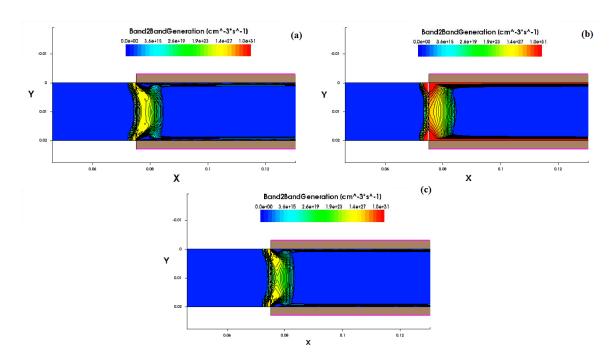

| 2.6  | Comparison of generation rates in local and nonlocal models in Sentaurus (a)<br>Schenk model (b) Kane's model (P=2) (c) Hurkx model                                                                                                                                                                                                     | 18 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

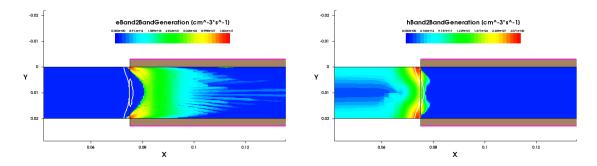

| 2.7  | Comparison of electron and hole generation rates in the dynamic nonlocal model in Sentaurus.                                                                                                                                                                                                                                            | 19 |

| 2.8  | Schematic of non-local band to band tunneling in reverse bias in Silvaco Atlas. [12]                                                                                                                                                                                                                                                    |    |

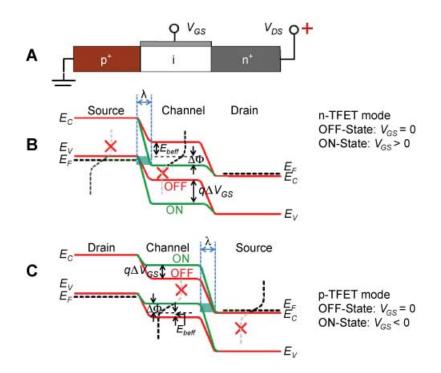

| 2.9  | (a)Schematic of a Tunnel FET with ntype biasing applied (b) nTFET mode with<br>both OFF and ON conditions shown (b) pTFET mode with both OFF and ON                                                                                                                                                                                     | 21 |

|      | conditions shown. [20]                                                                                                                                                                                                                                                                                                                  | 23 |

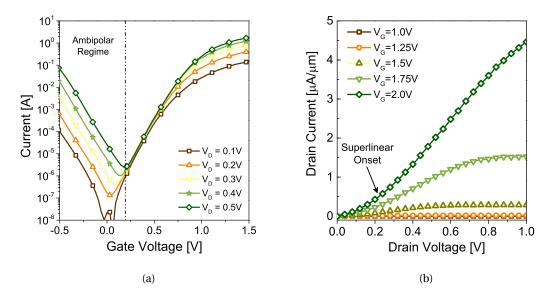

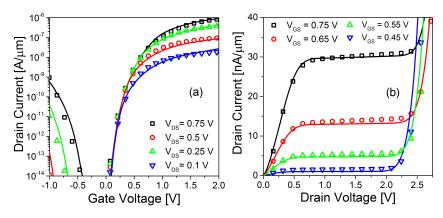

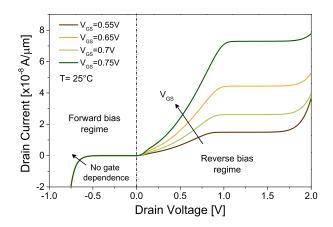

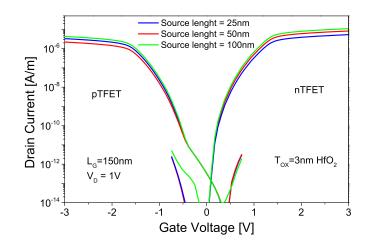

| 2.10 | Measured (a)transfer and (b)output characteristics of an all Silcon nanowire<br>n-type Tunnel FET on fully depleted SOI wafers at room temperature. The am-<br>bipolarity and superlinear onset which are typical to Tunnel FETs are highlighted.                                                                                       |    |

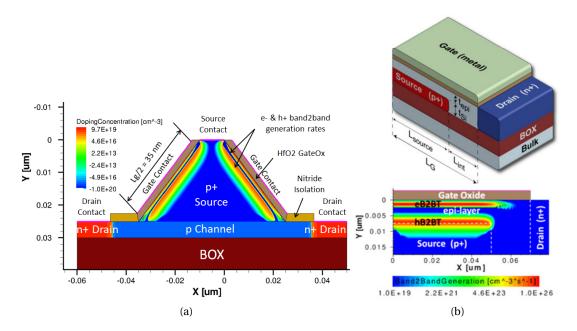

| 2.11 | Examples of line tunneling structures (a) [29] (b) [30] where the primary tun-<br>neling mechanism is oriented to the direction of the gate electric field. The<br>band-to-band generation is spread over a linear fashion, resembling a line,                                                                                          |    |

|      | hence the name line tunneling.                                                                                                                                                                                                                                                                                                          | 26 |

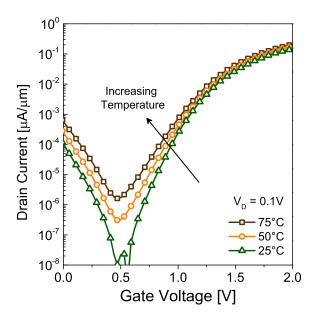

|      | Measured transfer characteristic of a all Silcon nanowire n-type Tunnel FET on fully depleted SOI wafers at elevated temperatures. [36]                                                                                                                                                                                                 | 27 |

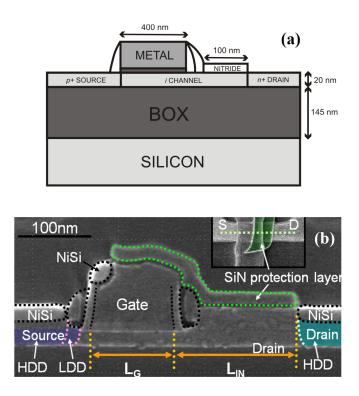

| 2.13 | (a) Basic structure and dimensions of TFET devices simulated. (b) SEM image showing the fabricated SOI TFET device. Inset shows the top view.[23]                                                                                                                                                                                       | 28 |

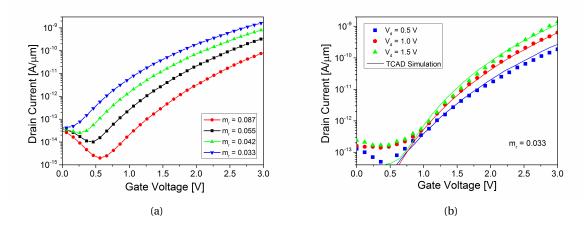

| 2.14 | (a)Impact of reduced mass on tunneling current shown for different value of<br>reduced masses including the theoretical mass and the default mass extracted<br>from default parameters and (b) Simulated and measured transfer character-<br>istics. Symbols indicate experimental data and solid lines the corresponding<br>simulation | 29 |

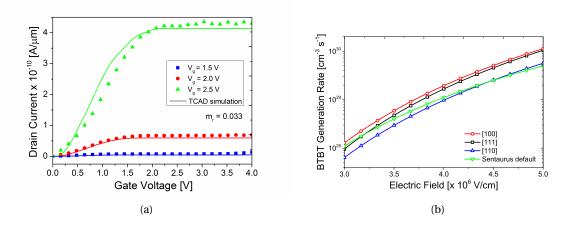

| 2.15 | (a) Simulated and measured output characteristics. Symbols indicate measured data and solid lines the corresponding simulation and (b) Variation of band-to-band generation rate as a function of uniform electric field with different crystallographic directions.                                                                    | 31 |

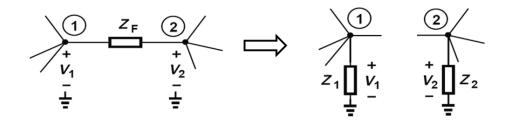

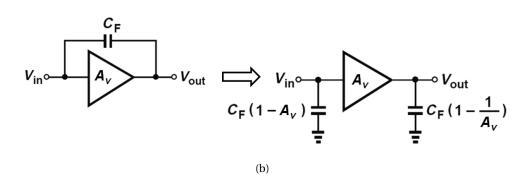

| 2.16 | (a) Amplifier with voltage gain $-A$ , with an impedance Z connected from input to output and (b) Amplifier with feedback capacitor $C_C$ .                                                                                                                                                                                             | 32 |

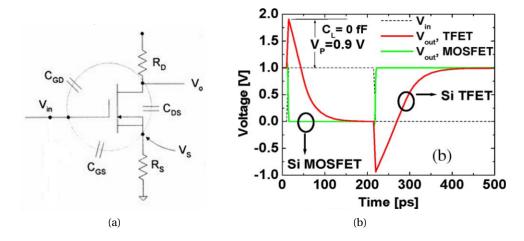

| 2.17 | (a) A simple MOS transistor circuit showing the main capacitance components<br>and (b) Transient response characteristics of silicon TFET and MOSFET based                                                                                                                                                                              |    |

| 2.18 | inverters. [41]                                                                                                                                                                                                                                                                                                                         | 33 |

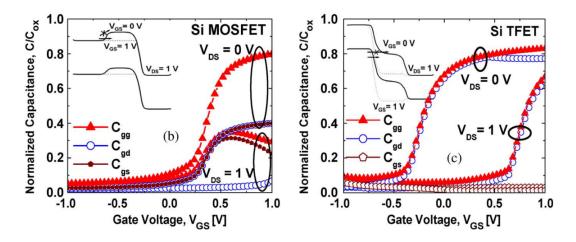

| 2.10 | and gate-to-drain $(C_{gd})$ capacitances as a function of gate-to-source voltage $V_{GS}$<br>for (a) Si MOSFET and (b) Si TFET [41]                                                                                                                                                                                                    | 34 |

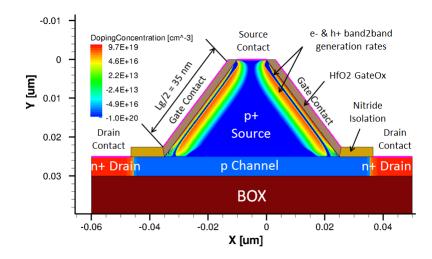

| 2.19 | Proposed structure with $T_{Si} = 5nm$ , $L_{g,eff} = 50nm$ . Gate work-function is $3.9eV$ .                                                                                                                                                                                                                                           |    |

|      | $N_{A,source} = 10^{20} cm^{-3}$ ; $N_{D,drain} = 10^{20} cm^{-3}$ while $N_{A,channel} = 10^{18} cm^{-3}$ . 2.5 <i>nm</i> of $HfO_2$ are used as gate-oxide; $t_{BOX} = 10nm$ ; $t_{bulk} = 1\mu m$ and the effective                                                                                                                  |    |

|      | Gate length $L_{g,eff} = 50 nm$ .                                                                                                                                                                                                                                                                                                       | 35 |

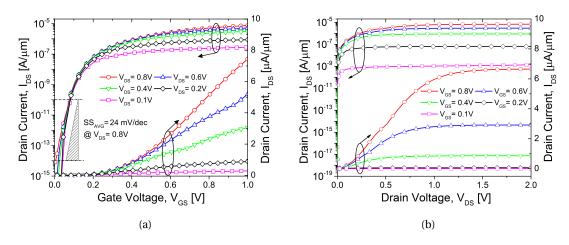

| 2.20 | Transfer (a) and output (b) characteristics of the proposed new structure                                                                                                                                                                                                                                                               | 35 |

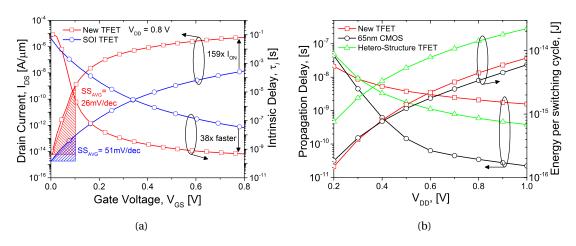

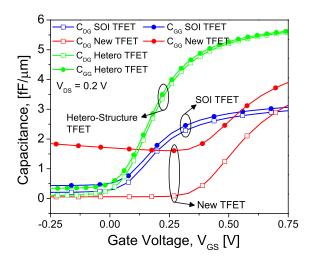

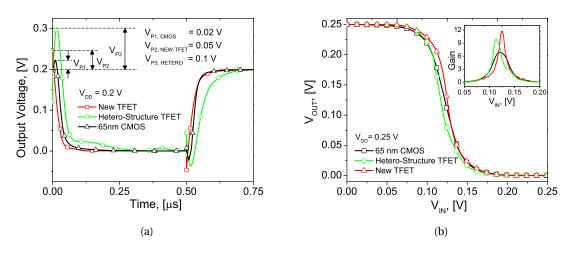

| <ul> <li>2.22 Capacitance-Voltage characteristics showing the drain-to-gate(<i>C<sub>DG</sub></i>) and gate(<i>C<sub>GG</sub></i>) capacitances as a function of <i>V<sub>GS</sub></i></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.21 | (a)Transfer characteristics comparison of the proposed new structure with a SOI TFET. Improved $I_{ON}$ , better SS and faster device speed (Intrinsic delay = CV/I) is observed. (b)Variation of propagation delay and energy per switching cycle with supply voltage. The proposed TFET becomes comparable to CMOS at $V_{DD} = 0.3V$ and lower. | 36 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| figuration for an input period of $1\mu s$ . (b)Voltage transfer characteristics of the three technologies reported in Fig. 2.20 & 2.23(a). Inset shows the inverter Gain $= dV_{OUT}/dV_{IN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.22 | Capacitance-Voltage characteristics showing the drain-to-gate $(C_{DG})$ and gate $(C_{GG})$                                                                                                                                                                                                                                                       | 37 |

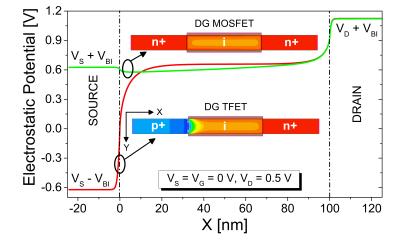

| and an n-type DG-TFET(red) with the same device parameters except the source<br>doping (n+/p+). Inset shows the electron density of the two devices at the given<br>bias. The cross sections are taken 1 <i>nm</i> below the gateoxide-Silicon channel<br>interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.23 | figuration for an input period of $1\mu s$ . (b)Voltage transfer characteristics of the three technologies reported in Fig. 2.20 & 2.23(a). Inset shows the inverter Gain                                                                                                                                                                          | 38 |

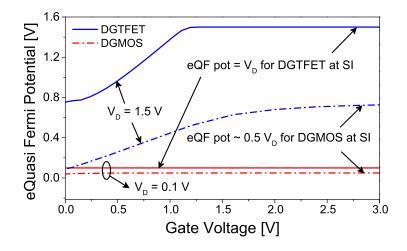

| at two different $V_D$ . The TFET electron quasi Fermi level stays at $-qV_D$ for<br>almost the entire gate bias range. The cross sections are taken $1 nm$ below the<br>gateoxide-Silicon channel interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.1  | and an n-type DG-TFET(red) with the same device parameters except the source doping $(n+/p+)$ . Inset shows the electron density of the two devices at the given bias. The cross sections are taken $1nm$ below the gateoxide-Silicon channel                                                                                                      | 40 |

| resent TCAD simulations. Dotted lines indicate results from eqn.3.2. Symbols<br>refer to eqn.3.3. Bottom: Simulated electron density with Fermi and Maxwell-<br>Boltzmann (MB) statistics for different $V_D$ (b) and gate dielectric materials (c).<br>The cross sections are taken just below the gateoxide-Silicon channel interface. 42<br>3.4 Lateral potential profile of the channel in a DG-TFET at the surface (a) at weak<br>inversion (b) at strong inversion. Lines indicate the model and symbols TCAD<br>simulations. The cross sections are taken just below the gateoxide-Silicon chan-<br>nel interface. $V_G = 0, 0.25, 0.5, 0.75, 1V \dots 44$<br>3.5 Two dimensional electrostatic potential solution of a double gate Tunnel FET<br>Inm below the gateoxide- channel interface from the conformal mapping tech-<br>nique | 3.2  | at two different $V_D$ . The TFET electron quasi Fermi level stays at $-qV_D$ for almost the entire gate bias range. The cross sections are taken $1nm$ below the                                                                                                                                                                                  | 41 |

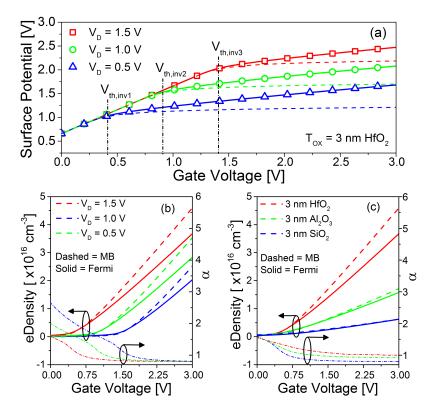

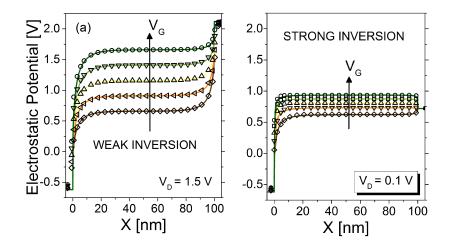

| <ul> <li>inversion (b) at strong inversion. Lines indicate the model and symbols TCAD simulations. The cross sections are taken just below the gateoxide-Silicon channel interface. V<sub>G</sub> = 0, 0.25, 0.5, 0.75, 1V</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.3  | resent TCAD simulations. Dotted lines indicate results from eqn.3.2. Symbols refer to eqn.3.3. Bottom: Simulated electron density with Fermi and Maxwell-Boltzmann (MB) statistics for different $V_D$ (b) and gate dielectric materials (c).                                                                                                      | 42 |

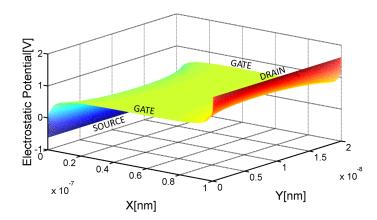

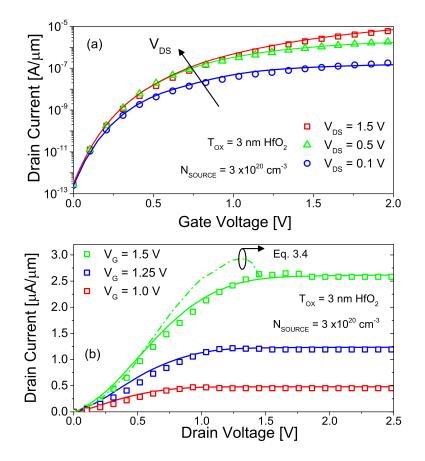

| <ul> <li>1nm below the gateoxide- channel interface from the conformal mapping technique.</li> <li>3.6 (a) Transfer characteristics with different V<sub>D</sub> and (b) output characteristics at different V<sub>G</sub>. The dotted lines in the output characteristics show the curve with eqn.3.4. Rest of the plot uses eqn.3.5 with the transition function from eqn.3.8.</li> <li>3.7 (a) Transfer characteristics with varying gate dielectric constant. α = 0.8 for HfO<sub>2</sub>, 0.92 for Al<sub>2</sub>O<sub>3</sub> and 1 for SiO<sub>2</sub> gate dielectric. (b) Transfer characteristics with varying source doping level. Low doping curves were corrected according</li> </ul>                                                                                                                                           | 3.4  | inversion (b) at strong inversion. Lines indicate the model and symbols TCAD simulations. The cross sections are taken just below the gateoxide-Silicon chan-                                                                                                                                                                                      | 44 |

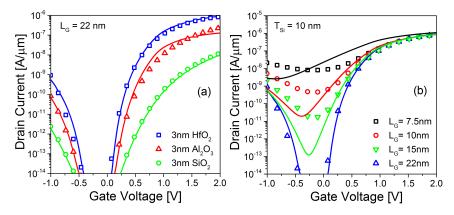

| <ul> <li>different V<sub>G</sub>. The dotted lines in the output characteristics show the curve with eqn.3.4. Rest of the plot uses eqn.3.5 with the transition function from eqn.3.8 .</li> <li>3.7 (a) Transfer characteristics with varying gate dielectric constant. α = 0.8 for <i>HfO</i><sub>2</sub>, 0.92 for <i>Al</i><sub>2</sub><i>O</i><sub>3</sub> and 1 for <i>SiO</i><sub>2</sub> gate dielectric. (b) Transfer characteristics with varying source doping level. Low doping curves were corrected according</li> </ul>                                                                                                                                                                                                                                                                                                        | 3.5  | 1nm below the gateoxide- channel interface from the conformal mapping tech-                                                                                                                                                                                                                                                                        | 45 |

| $HfO_2$ , 0.92 for $Al_2O_3$ and 1 for $SiO_2$ gate dielectric. (b) Transfer characteristics with varying source doping level. Low doping curves were corrected according                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.6  | different $V_G$ . The dotted lines in the output characteristics show the curve with                                                                                                                                                                                                                                                               | 46 |

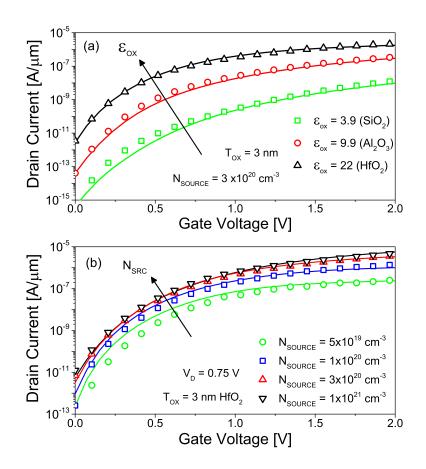

| to table 3.1. $L_g = 22nm$ , $t_{Si} = 10nm$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.7  | $HfO_2$ , 0.92 for $Al_2O_3$ and 1 for $SiO_2$ gate dielectric. (b) Transfer characteristics with varying source doping level. Low doping curves were corrected according                                                                                                                                                                          |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | to table 3.1. $L_g = 22nm$ , $t_{Si} = 10nm$                                                                                                                                                                                                                                                                                                       | 47 |

| List | of Figures | ; |

|------|------------|---|

|------|------------|---|

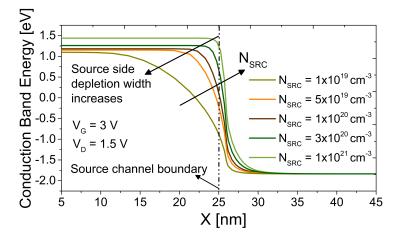

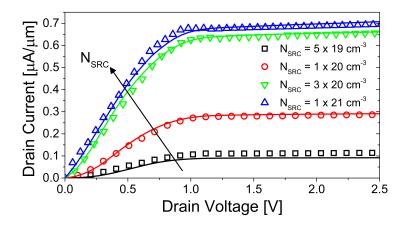

| 3.8  | Conduction band energy profile at the source channel boundary for different source doping levels. The source depletion width increases with decreasing                                                                                                              |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | source doping                                                                                                                                                                                                                                                       | 48 |

|      | function of eqn.3.8 is used here.                                                                                                                                                                                                                                   | 49 |

| 3.10 | (a) Cross section of the device under study with typical dimensions marked<br>(b) lateral potential profile of the channel in a DG-TFET at the oxide-Silicon<br>interface at strong inversion for $V_{GS}$ = 0,0.25,0.5,0.75,1V. Lines indicate the model           |    |

|      | and symbols TCAD simulation in all relevant plots.                                                                                                                                                                                                                  | 50 |

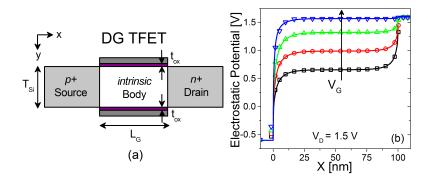

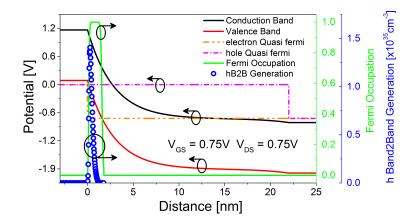

| 3.11 | The operating regimes of a TFET: ON state with $V_{DS} = V_{GS} = V_{DD}$ , where supply voltage $V_{DD} = 0.75V$                                                                                                                                                   | 51 |

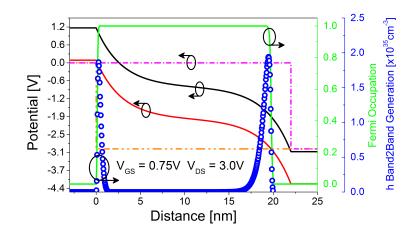

| 3.12 | The operating regimes of a TFET: Ambipolar state with $V_{DS} = V_{DD}$ and $V_{GS} =$                                                                                                                                                                              |    |

|      | $-V_{DD}$ , where supply voltage $V_{DD} = 0.75V$                                                                                                                                                                                                                   | 51 |

| 3.13 | The operating regimes of a TFET: Breakdown state with $V_{DS} = V_{DD}$ and $V_{GS} =$                                                                                                                                                                              |    |

|      | $V_{DD}$ , where supply voltage $V_{DD} = 0.75V$                                                                                                                                                                                                                    | 52 |

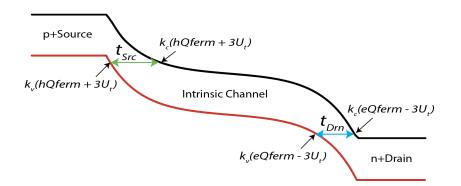

| 3.14 | Schematic showing the location of the two tunnelling paths considered. The                                                                                                                                                                                          |    |

|      | breakdown state biasing is used here to show both the tunnelling paths.                                                                                                                                                                                             | 52 |

| 3.15 | (a) Transfer characteristics for different $V_{DS}$ (b) Output characteristics for differ-                                                                                                                                                                          |    |

|      | ent $V_{GS}$ .                                                                                                                                                                                                                                                      | 54 |

| 3.16 | (a) Transfer curves with three different gate oxide material. (b) Transfer curves with gate length scaling with other parameters constant                                                                                                                           | 54 |

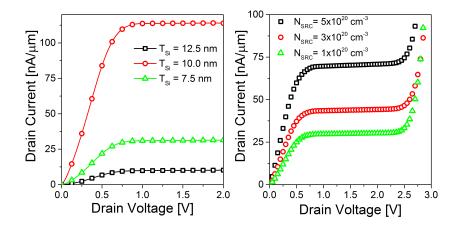

| 3.17 | (a) Transfer curves with three different body thickness. (b) Transfer curves with                                                                                                                                                                                   |    |

|      | source doping variation.                                                                                                                                                                                                                                            | 55 |

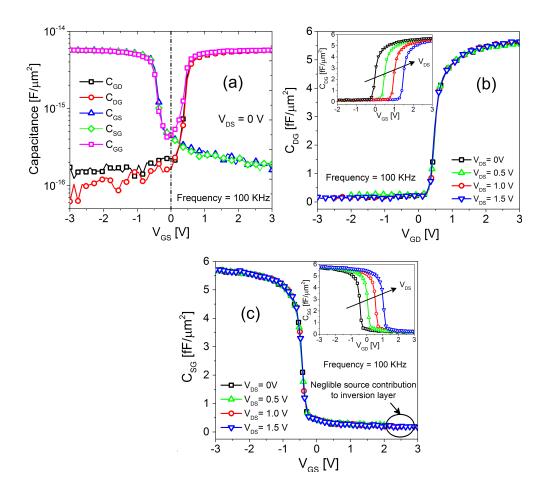

| 3.18 | (a) Measured $C_{GS}$ , $C_{GD}$ and $C_{GG}$ with respect to $V_{GS}$ . Perfect symmetry is observed highlighting the ambipolar nature of TFETs. (b) Measured Gate-Drain capacitance for different $V_{DS}$ . Inset shows measured $C_{GD}$ curves with respect to |    |

|      | $V_{GS}$ . (c) Measured Gate-Source capacitance for different $V_{DS}$ . Source contribu-                                                                                                                                                                           |    |

|      | tion to inversion electrons is negligible even at $V_{DS} = 1.5V$ with device turned                                                                                                                                                                                |    |

|      | ON. Inset shows measured $C_{GS}$ curves with respect to $V_{GD}$ . Fully depleted SOI                                                                                                                                                                              |    |

|      | TFET with $L_G = 200 nm$ , $t_{Si} = 21 nm$ and 6 nm $SiO_2$ dielectric                                                                                                                                                                                             | 56 |

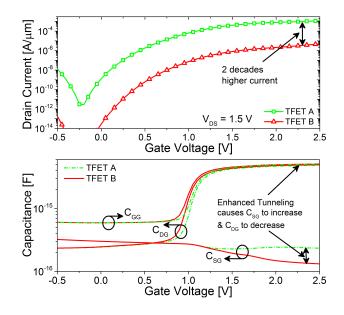

| 3.19 | (top) TFET A simulated with artificially enhanced tunnelling injection to have 2                                                                                                                                                                                    |    |

|      | order of magnitude more current than TFET B. (bottom) TFET A shows a slightly                                                                                                                                                                                       |    |

|      | higher $C_{SG}$ and slightly lower $C_{DG}$ compared to TFET B. $C_{SG}$ remains negligible                                                                                                                                                                         |    |

|      | compared to $C_{DG}$ in TFET A, verifying that tunnelling has little or negligible                                                                                                                                                                                  |    |

|      | influence in the charge distribution of a TFET.                                                                                                                                                                                                                     | 58 |

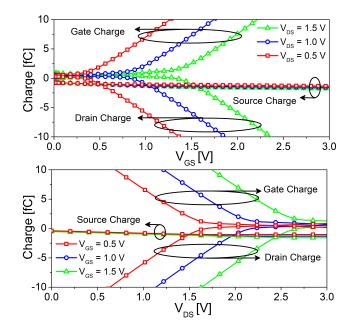

| 3.20 | Modelled gate, drain and source charges of an n-type double gate tunnel FET                                                                                                                                                                                         |    |

|      | (top) as a function of gate-source voltage and (bottom) as a function of drain-                                                                                                                                                                                     |    |

|      | source voltage                                                                                                                                                                                                                                                      | 59 |

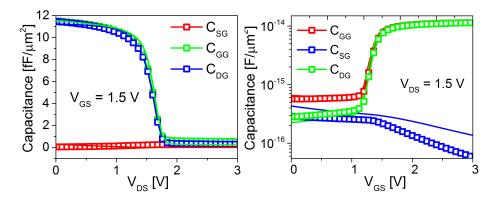

| 3.21 | $C_{GG}$ , $C_{SG}$ and $C_{DG}$ with respect to drain-source voltage at $V_{GS} = 1.5V$ (left) and gate-source voltage at $V_{DS} = 1.5V$ (right) computed by the simplified model and                                                                             |    |

|      | comparison with TCAD simulations. Symbols indicate simulations and solid                                                                                                                                                                                            |    |

|      | lines indicate model for all relevant figures                                                                                                                                                                                                                       | 60 |

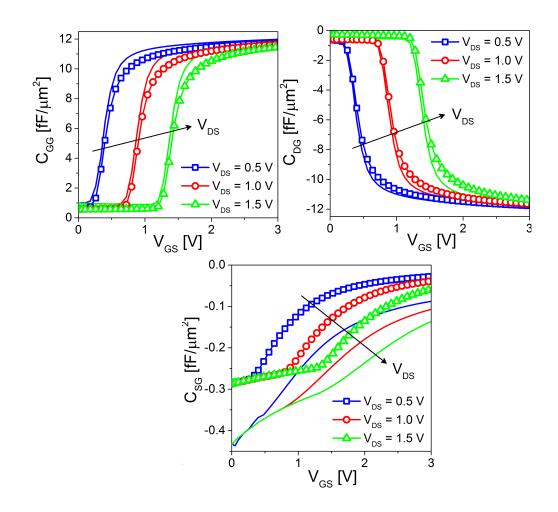

| 3.22 | Modelled $C_{GG}$ , $C_{SG}$ and $C_{DG}$ curves with respect to $V_{GS}$ for three different drain voltages and comparison with TCAD simulations. Modelled $C_{SG}$ curves with | 01 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | respect to $V_{GS}$ although do not show a good match, predicts the trend correctly                                                                                              | 61 |

| 3.23 | Modelled output characteristic of a n type TFET showing both positive and                                                                                                        |    |

|      | negative drain voltages. Note the forward biased drain current has not gate                                                                                                      |    |

|      | dependence                                                                                                                                                                       | 62 |

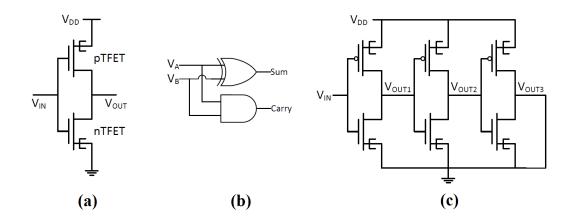

| 3.24 | Schematics of circuits simulated (a) single stage inverter (b) 2-bit half adder (c)                                                                                              |    |

|      | A ring oscillator (3 stage shown here)                                                                                                                                           | 63 |

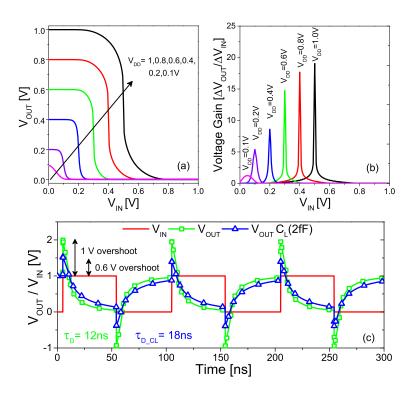

| 3.25 | (a) VTC of a TFET based single stage inverter with $V_{DD}$ 0.1V to 1V. (b) Voltage                                                                                              |    |

|      | gain of the inverter for the same $V_{DD}$ range. Inset shows the simulated single                                                                                               |    |

|      | stage inverter. (c) Transient response of a single stage TFET inverter at $V_{DD}$ =1V                                                                                           |    |

|      | with $C_L$ =0fF and $C_L$ =2fF.                                                                                                                                                  | 64 |

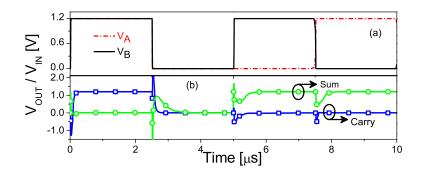

| 3.26 | All-Silicon 22nm TFET based 2-bit half adder with $V_{DD}$ =1.2V (a) the two input                                                                                               |    |

|      | signals $V_A$ and $V_B$ (inset shows the schematic of the simulated 2-bit half adder)                                                                                            |    |

|      | (b) the sum and carry output signals.                                                                                                                                            | 65 |

| 3 27 | (a) All-Silicon 22nm TFET based 15 stage ring oscillator output for $V_{DD}$ =1V. A                                                                                              | 00 |

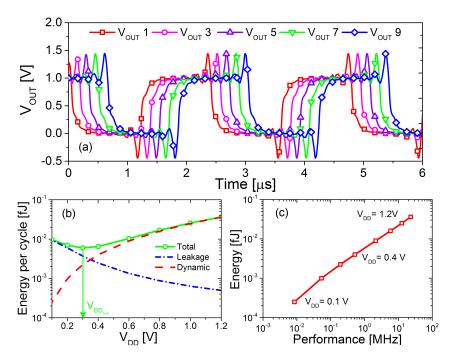

| 0.21 | delay of $\tau_D$ =79.4ns is observed. (b) Leakage, dynamic and total energy with $V_{DD}$                                                                                       |    |

|      | scaling (c) Switching energy-performance comparison. $\dots \dots \dots \dots \dots \dots$                                                                                       | 66 |

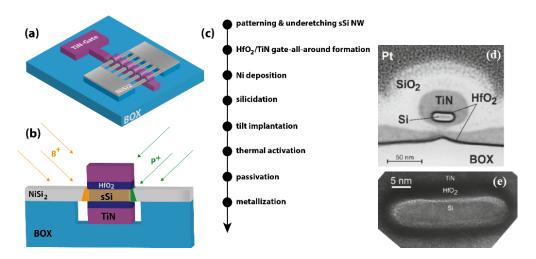

| 2 20 | (a) Schematic of the fabricated sSi NW TFET with $TiN/HfO_2$ gate stack (b)                                                                                                      | 00 |

| 3.28 |                                                                                                                                                                                  |    |

|      | Highly doped $n$ + and $p$ + pockets at the silicide edges are formed after a low                                                                                                |    |

|      | temperature anneal (c) sSi NW TFET fabrication process using tilted $B$ + and $P$ –                                                                                              |    |

|      | ion implants into epitaxial $NiSi_2$ S/D contacts. (d) SEM image of single sSi NW                                                                                                |    |

|      | TFET after fabrication. (e) SEM cross section along the NW showing the gate                                                                                                      | 0= |

|      | oxide and metal layers. [43]                                                                                                                                                     | 67 |

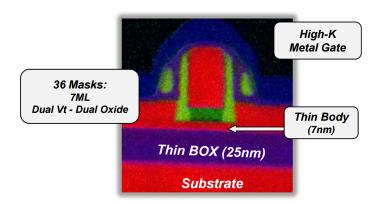

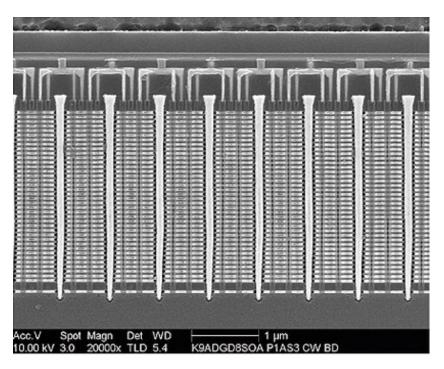

| 3.29 | SEM cross section along the NW showing the gate oxide and metal layers. [image                                                                                                   |    |

|      | courtesy: ST-Microelectronics]                                                                                                                                                   | 68 |

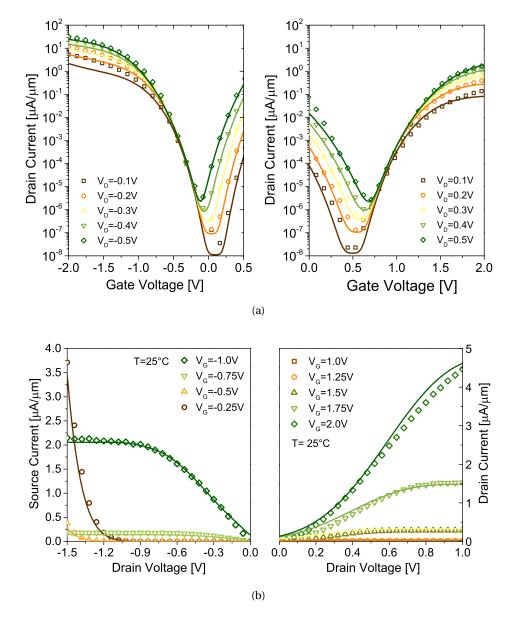

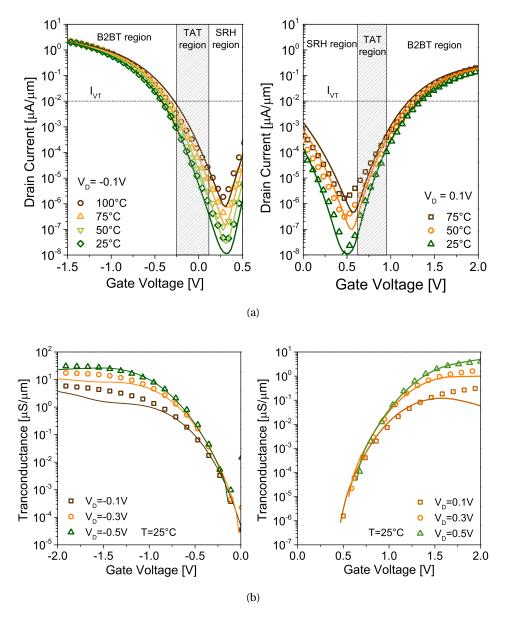

| 3.30 | (a) Measured transfer characteristics and calibrated model at different $V_{DS}$ of the                                                                                          |    |

|      | fabricated sSi NW TFET for (left) p-type and (right) n-type TFET (b) Measured                                                                                                    |    |

|      | output characteristics and calibrated model at different $V_{GS}$ for (left) p-type                                                                                              |    |

|      | (right) n-type TFET at room temperature. (Symbol: measurement, lines: model)                                                                                                     | 70 |

| 3.31 | (a) Measured transfer characteristics with temperature (25°C to 100°C) with                                                                                                      |    |

|      | calibrated model; achieved $I_{ON}$ is $20\mu A/\mu m$ and $2\mu A/\mu m$ for p- and n-type                                                                                      |    |

|      | sSi homo-junction NW TFET at $V_{GS} = 1.5V$ and min point swings, $SS_{pt} \approx$                                                                                             |    |

|      | 70-100mV/dec at room temperature and $I_{OFF} < 1 - 10nA/\mu m$ . (b)Measured                                                                                                    |    |

|      | transconductance and calibrated model at $ V_{DS}  = 0.1V$ with respect to tem-                                                                                                  |    |

|      | perature for p type (left) and n type (right) TFET. (Symbol: measurement, lines:                                                                                                 |    |

|      | model)                                                                                                                                                                           | 71 |

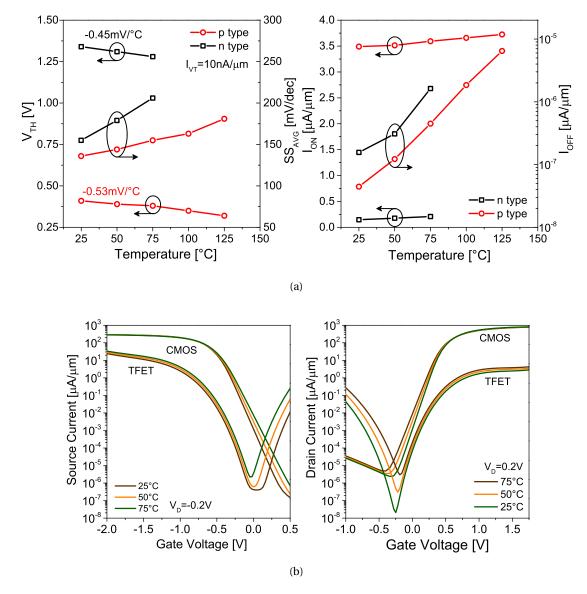

| 3.32 | (a)(Left) experimentally extracted $V_{TH}$ and average sub-threshold swing, $SS_{AVG}$ ,                                                                                        |    |

|      | (over 4 decades of current) dependences, and, (right) $I_{ON}$ and $I_{OFF}$ dependences                                                                                         |    |

|      | on temperature, from 25°C to 125°C. (b)Transfer characteristics of 28nm CMOS                                                                                                     |    |

|      | (calibrated simulation) and TFET (calibrated model) overlapped with respect to                                                                                                   |    |

|      | temperature                                                                                                                                                                      | 72 |

|      |                                                                                                                                                                                  |    |

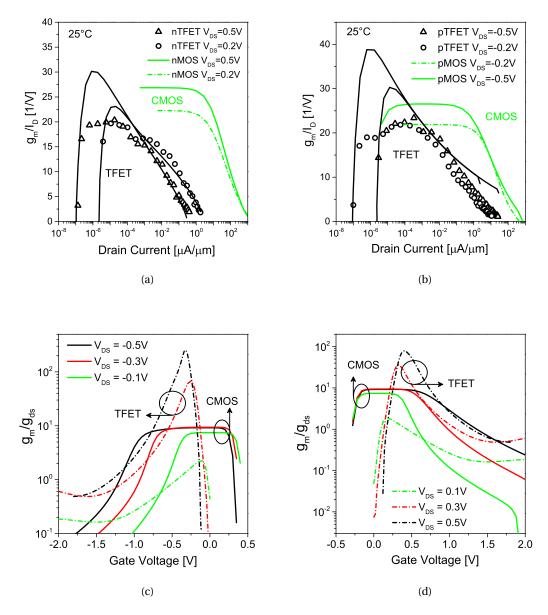

| 3.33 | (a)Transconductance per unit drain current for p type (left) and n type (right) with respect to VDS. (b)Intrinsic gain vs. gate voltage for p type (left) and n type (right). The calibrated model is used for the TFET plots.                                                                                                                                                                                                                                 | 73 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

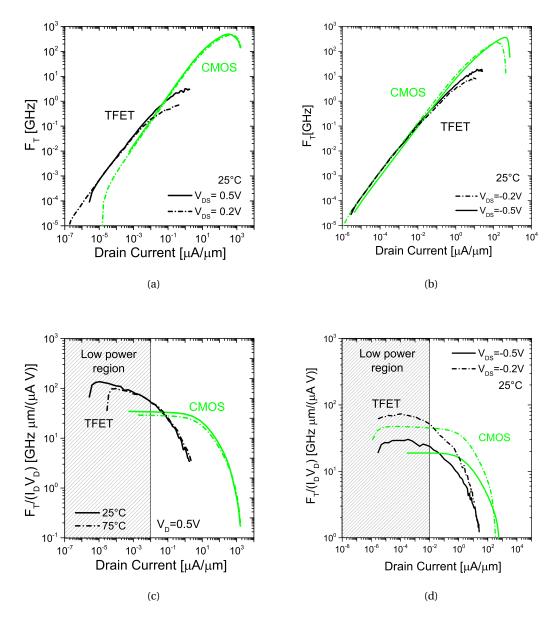

| 3.34 | (a)Measured (TFET) current gain cut-off frequency Vs current per unit width for p type (left) and n type (right) TFET (b)Measured (TFET) unity gain frequency per unit power vs. current per unit width for p type (left) and n type (right) TFET.                                                                                                                                                                                                             | 74 |

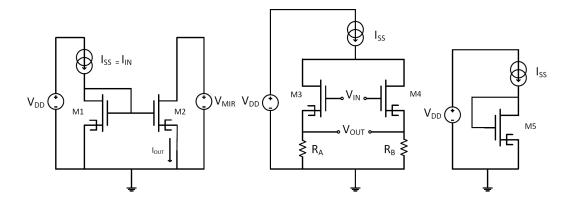

| 3.35 | Schematics of investigated analog cells: (a) current mirror circuit (b) differential pair circuit and (c) a diode connected transistor circuit.                                                                                                                                                                                                                                                                                                                | 75 |

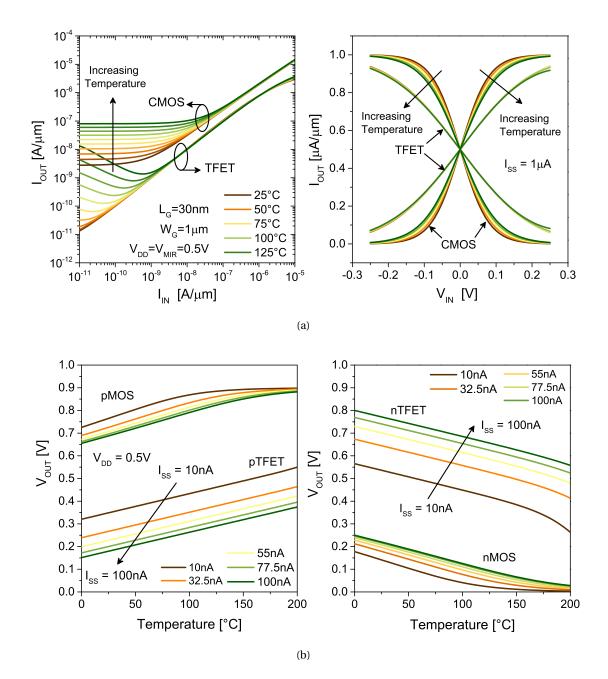

| 3.36 | (a) TFET vs. CMOS current mirror: $I_{OUT}/I_{IN}$ for temperature 25°C to 125°C (left)<br>Differential pair output current as a function of temperature (25°C to 125°C) for<br>both nTFET and nMOS (right) (b) Temperature dependence of $V_{OUT}$ with $I_{SS}$<br>as parameter; CMOS vs TFET for a diode connected circuit. TFET embodiment<br>shows excellent linearity versus temperature, suggesting possible use a highly<br>linear temperature sensor. | 76 |

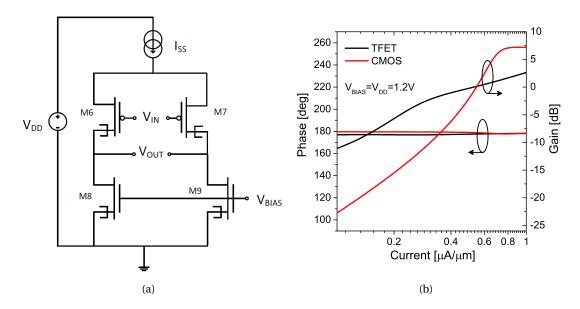

| 3.37 | (left) Schematic of TFET differential stage circuit with an active load and (Right) gain (in dB) versus current, for CMOS and TFET and (right) showing the phase and the gain versus input current. The gain drops by 30 dB for the CMOS at room temperature.                                                                                                                                                                                                  | 77 |

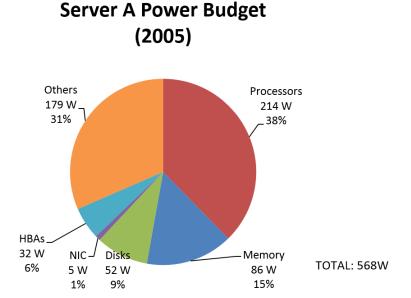

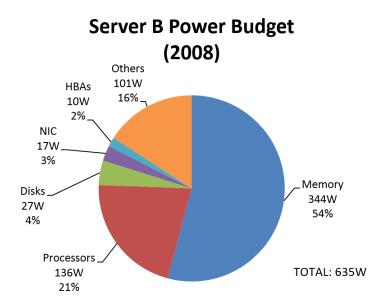

| 4.1  | Component power distribution, 2005 two-socket dual-core server.[84]                                                                                                                                                                                                                                                                                                                                                                                            | 80 |

| 4.2  | Component power distribution, 2008 four-socket quad-core server.[84]                                                                                                                                                                                                                                                                                                                                                                                           | 81 |

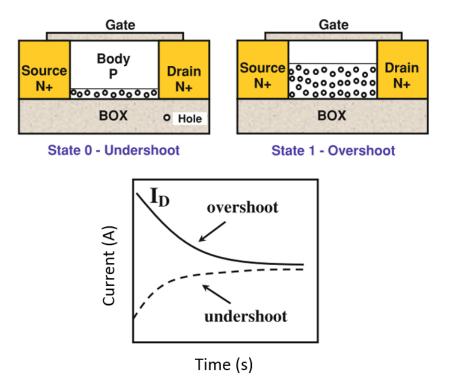

| 4.3  | Schematic cross-section of a partially depleted (PD) SOI nMOSFET used as<br>a 1T-DRAM memory cell and the corresponding current transient for 0 state<br>(undershoot) and 1 state (overshoot) resulting from the lack or excess of majority<br>carriers (holes), respectively. Image courtesy [88]                                                                                                                                                             | 82 |

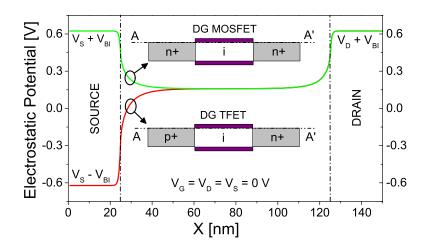

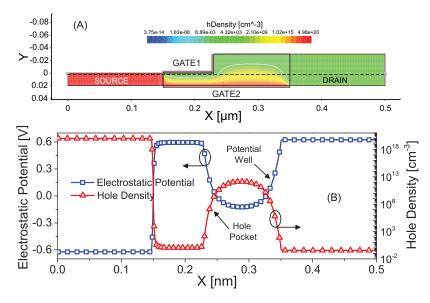

| 4.4  | Simulated potential profile at 1 nm below the gate-oxide/channel interface for both DG-MOSFET and DG-TFET.                                                                                                                                                                                                                                                                                                                                                     | 83 |

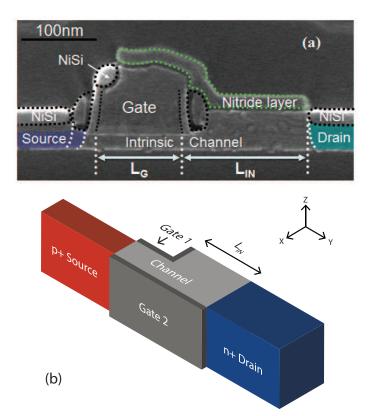

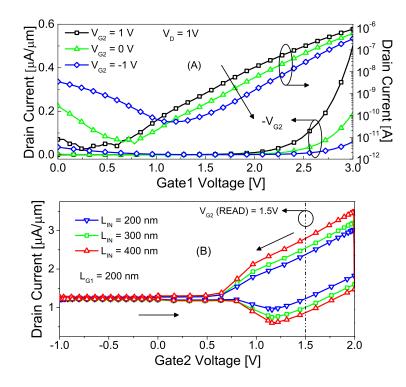

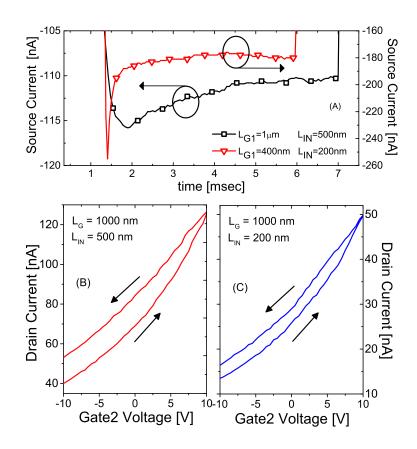

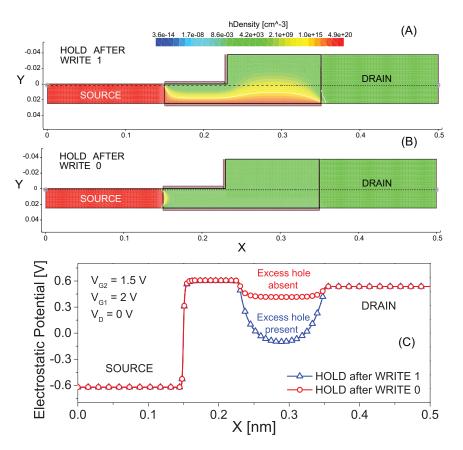

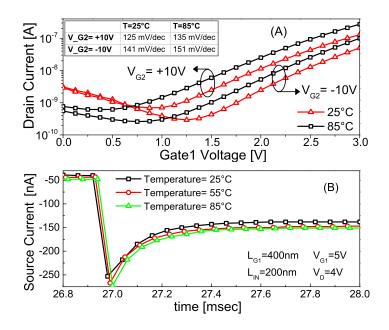

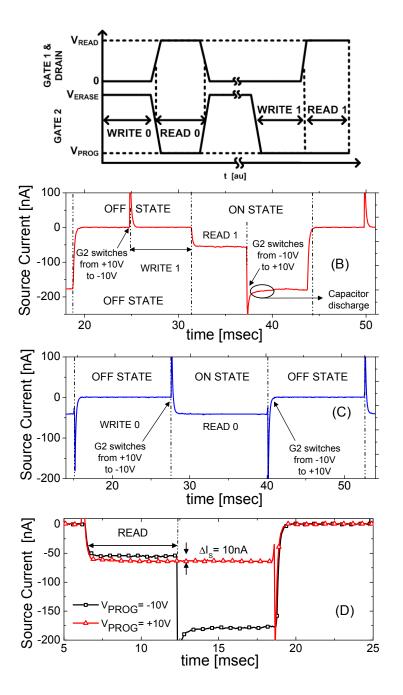

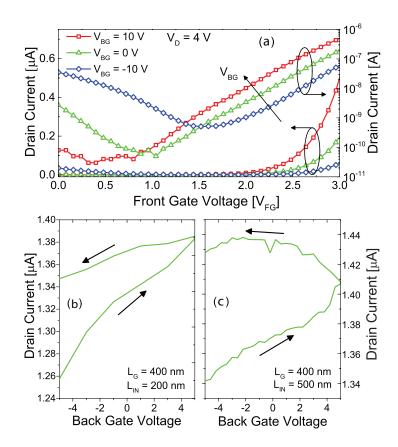

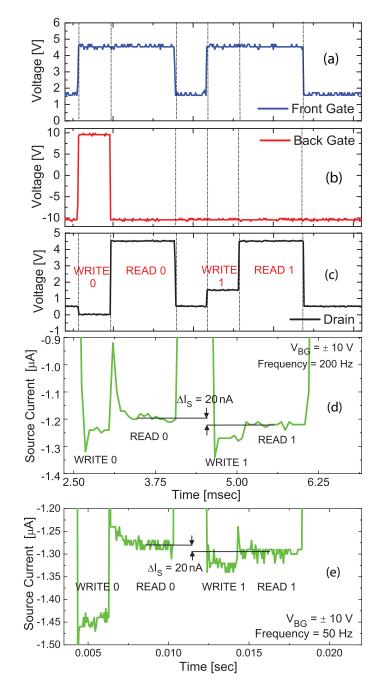

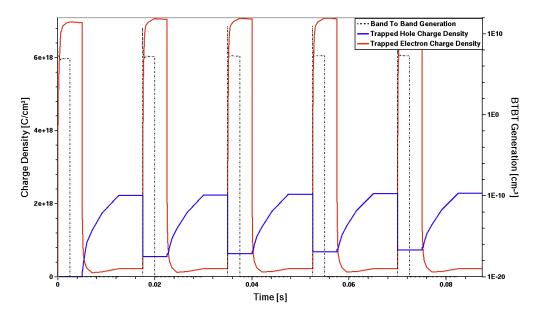

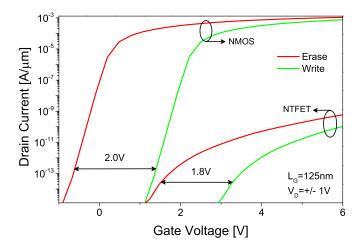

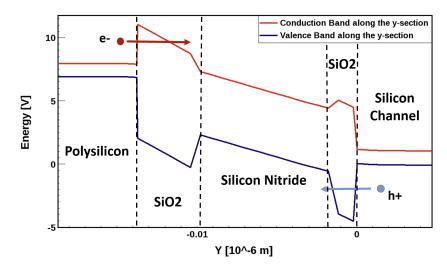

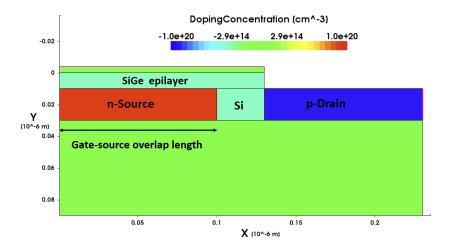

| 4.5  | (a) SEM image of a fabricated FD-SOI Tunnel FET showing the top gate partially covering the channel [23]. (b) Independent gate FinFET device structure for TFET based capacitorless DRAM.                                                                                                                                                                                                                                                                      | 84 |