### Multi-Gigabyte On-Chip DRAM Caches for Servers

### THÈSE Nº 6631 (2015)

#### PRÉSENTÉE LE 15 SEPTEMBRE 2015

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DE SYSTÈMES PARALLÈLES PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Djordje JEVDJIC

acceptée sur proposition du jury:

Prof. C. Koch, président du jury Prof. B. Falsafi, directeur de thèse Prof. G. Loh, rapporteur Prof. . H.-H. S. Lee, rapporteur Prof. E. Bugnion, rapporteur

# Acknowledgements

This thesis has been a long and dynamic journey, which I certainly would not be able to complete alone. I would like to spend a few words to express my enormous gratitude to some of the people who, directly or indirectly, helped me make this thesis happen.

First and foremost, I owe my biggest gratitude to my advisor and my friend, Babak Falsafi. I thank Babak for believing in me, for giving me the level of independence that I needed, for always having great and nonjudgmental understanding for every problem I encountered, for understanding and tolerating my disobedient personality, for supporting me in my numerous extracurricular activities, for teaching me so many things about computer science, and, most importantly, for shaping my views and being a great role model regarding those things in life that matter the most.

I was very fortunate to have the most highly regarded experts in my thesis committee. I thank Edouard Bugnion, Hsien-Hsin Sean Lee and Gabriel Loh for being part of my thesis, for giving me constructive feedback on my research, for shaping the direction of the thesis, and, most importantly, for giving me a hard time at the thesis proposal exam and thesis defense.

The past six years of my PhD life were tough, yet wonderful and full of memorable moments, thanks to my closest collaborators and friends, and my currently *youngest* academic siblings: Cansu Kaynak, Stavros Volos, and Onur Koçberber. The four of us started the PhD program together, worked together, shared offices together, coauthored many papers together, spent sleepless nights together, ate together, partied together, travelled together, skied together, and ended our PhD trip together. Their presence, support and help were instrumental in making this thesis happen. Thank you guys!

I spent only one year less in the PARSA lab with Javier Picorel *Obando*. I owe him many thanks for many different things, but if I had to be specific, I would have to thank Javier for two important things: first, for taking the risk to be the first student I've had a chance to supervise. And second, for volunteering to drive that van full of PARSA members around the French Alps under heavy snow. Thank you, Javier!

<sup>&</sup>lt;sup>1</sup>Sorted by the graduation date, not by sex

I don't have enough words to express my gratitude to the rest of the members, current or past, of the PARSA lab at EPFL, for their huge contributions to my professional and social well-being during my PhD. Listing all those contributions would take a separate book. But I cannot miss my opportunity to thank Sotiria Fytraki for filling the air of PARSA offices with her melodic Cretan accent. I will always remember Almutaz Adileh and Pejman Lotfi-Kamran for the fun we had on our frequent trips to exotic European countries for the EuroCloud project meetings.<sup>2</sup>. I'm truly grateful to Alexandros Daglis for organizing the trip to Las Vegas after ASPLOS'14 and for taking us to Stratosphere. I greatly thank Mohammad Alisafaee for referring me to some of the best black comedies. I thank Michael Ferdman and Alisa Yurovski for organizing the best tea parties, and Boris Grot and Gaya Khachatryan-Grot for being amazing hosts in Edinburgh. Thank you Effi Georgala, Stanko Novaković, Nooshin Mirzadeh, Georgios Psaropoulos, Mario Drumond, and Dmitri Ustiugov for all the moments, either fun or busy, that we shared together. Thank you Stéphanie Baillargues and Rodolphe Buret for always providing great administrative and technical help. Last, but not least, I thank monsieur Damien Hilloulin for translating the abstract of this thesis into French.

PhD is only the last step in my formal education. I owe enormous gratitude to my closest friends and collaborators, Andrijana Svorcan, Ivan Kuraj, Ana Romandić, Katarina Maksimović, Marija Popović, Una Aksentijević, Slavko Perišić, Đorđe Vuksanović, Viktor Vilotijević, among many others, for being great friends and supporting me throughout my long education in Serbia and Switzerland.

I owe special thanks to my lifelong friend, Darko Petrović. Darko and I were classmates since the kindergarten, then later in the elementary school, also during our undergraduate studies at the University of Belgrade, and finally during our PhD at EPFL. Occasionally, we were neighbors too. I thank Darko, his wife Ivana and their adorable daughter Iva, for being great friends and great neighbors during my entire stay in Switzerland.

For some of the most cheerful moments during my stay in Switzerland, I owe very special thanks to choir Fa7, in which I spent three wonderfull years singing jazz and gospel throughout the country. Thank you Jacqueline Savoyant, for sharing your positive energy, for encouraging me to sing solo, and trusting me on sometimes quite demanding but always beautiful and powerful solo tunes. Thank you Sylvie Füllemann and Olivier Nicole, singing with you every Tuesday was pure joy. Thank you Aurélie Burnier (I will never forget singing *Do you know what it means to miss New Orleans* with you), Vimi Gobin, Thaddeus Castillo, and Coralie Wenger Bonny for so many fun moments outside the choir. Thank you all Fa7 members for

<sup>&</sup>lt;sup>2</sup>I will certainly not forget Pejman's and mine long layover in Amsterdam

accepting me genuinely and warmly into your choir, despite my poor French skills. Thank you for encouraging me to speak French and for helping me learn it. The time I spent with you gave me such an invaluable insight into the Swiss culture and the real Swiss spirit, and made my whole stay in Switzerland much more enjoyable.

Finally, I owe special thanks to Marko Milanović and Nemanja Kostić, for being my very best friends and helping me survive my PhD journey.

My family has always played an important role in my private and professional life. I'm eternally thankful to my grandparents, Vera and Dušan Žunić, Milosava and Mijailo Jevđić, for all the great moments I spent with them in their village, for all the healthy, fresh and delicious food I ate with them. I thank my grandad Mijajlo for teaching me very early that being different and thinking against the odds is something one should be proud of. I thank my uncles, Zoran Jevđić, Jovica Jevđić, Predrag Žunić, my aunts, Vesna Bjekić, Snežana Mitrić, Milica Radović, my first cousins, Jovana Jevđić, Milan Jevđić, Nikola Žunić, Stefan Žunić, Milutin Jevđić, Joviša Jevđić, Mirjana Radović and Miloš Radović being part of my dearest childhood memories and for their unconditional support. I thank my dear friend, Desimir Krupiniković, for being there for me and my family when it mattered the most.

Above all, I thank my parents, Dobrinka Jevđić and Vidoje Jevđić, and my brother Aleksandar Jevđić, for their endless love and support throughout my whole life.

Lausanne, July 22nd 2015

### **Abstract**

While DRAM latency has long been recognized as a major bottleneck in servers, DRAM bandwidth is emerging as an important bottleneck as server processors shift to many-core architectures to allow for sustainable throughput improvements. The rapid expansion of the digital universe, increasingly stored in memory, rapidly pushes the need for higher DRAM density as well.

Emerging die-stacked DRAM technology dramatically improves the three major DRAM properties: latency, bandwidth and density. Recent advancements in die-stacking technology made it possible to integrate a sizeable amount of DRAM directly on top of the processor. While the feasible on-chip DRAM capacities are insufficient to satisfy the memory needs of modern servers, architecting on-chip DRAM as a high-capacity low-latency high-bandwidth cache has the potential to provide significant reduction both in off-chip memory traffic and in average memory access latency.

We make the observation that high-capacity on-chip DRAM caches expose abundant spatial locality present in server applications and a modest amount of temporal data reuse. As a consequence, DRAM caches that manage and fetch data at a coarser granularity, e.g., in 2KB pages, exhibit overall superior properties compared to caches that do fine-grain management using 64B blocks. These properties include substantially higher hit rates, smaller tag storage, higher energy efficiency and set-associativity. Unfortunately, naïve employment of page-based caches results in excessive data overfetch and capacity waste, as some of the fetched and allocated blocks are never accessed prior to their eviction. We demonstrate that if the cache is organized in pages, then page footprints — i.e., the set of blocks that are touched while the page is in the cache — are highly predictable using well-established code-correlation techniques. Accurately predicting access patterns within a page can eliminate most of the bandwidth overhead and capacity waste that page-based caches suffer from.

Key words: die-stacked DRAM, 3D integration, caches, memory bandwidth, memory latency, servers

### Résumé

Tandis que la latence des mémoires DRAM est depuis longtemps reconnue comme un goulet d'étranglement pour les serveurs, la bande passante devient elle aussi limitante à mesure que les processeurs intègrent de plus en plus de cœurs d'exécution dans l'objectif d'augmenter les capacités de traitement. L'expansion rapide de l'univers digital, de plus en plus placé en mémoire, fait apparaître la nécessité de mémoires DRAM à plus grandes densités.

La technologie émergente de mémoires DRAM à dies empilés améliore les trois caractéristiques déterminantes de la DRAM : la latence, la bande passante et la densité. Les récents progrès dans l'empilement des dies rend possible d'intégrer des capacités importantes de DRAM directement sur le processeur. Tandis que la quantité de mémoire DRAM qu'il est possible d'intégrer sur une puce est à l'heure actuelle insuffisante pour satisfaire les besoins en mémoire des serveurs modernes, utiliser de la mémoire DRAM sur les puces comme un cache de grande capacité, à faible latence et grande bande passante a le potentiel de permettre une réduction significative du trafic mémoire externe et de réduire la latence mémoire en moyenne.

Nous faisons l'observation que les structures de caches locales de grandes capacités exposent la localité spatiale abondante des données présente dans les applications serveurs ainsi qu'un modeste degré de réutilisation temporel des données. Par conséquent, les caches DRAM qui gèrent et récupèrent les données à une granularité plus grossière, par exemple par pages de 2ko, présentent de meilleures caractéristiques que des structures de caches utilisant une gestion plus fine. Ces caractéristiques incluent de meilleurs taux d'utilisation, des étiquettes à stocker plus petites, une meilleure efficacité énergétique ainsi que la set-associativity. Cependant, l'utilisation naïve de tels caches reposant sur l'utilisation de pages amène à un préchargement excessif de données et à une perte de capacité étant donné que certains des blocs chargés et alloués ne sont pas utilisés avant leur éviction. Nous montrons que si le cache est organisé par pages, les motifs d'accès — i.e., l'ensemble des blocs accédés quand la page est dans le cache — sont hautement prévisibles en utilisant des techniques éprouvées de code-correlation. Prédire de manière précise les motifs d'accès au sein d'une même page permet d'éliminer une grande partie de l'augmentation du besoin en bande passante et aussi la perte en capacité dont les

### Résumé

caches reposant sur l'utilisation de pages souffrent.

Mots clefs : mémoires DRAM à dies empilés, l'integration 3D, cache, bande passante mémoire, latence mémoire, serveurs

# Contents

| Ac | knov  | wledge  | ments                            | i    |

|----|-------|---------|----------------------------------|------|

| Ał | ostra | ct      |                                  | v    |

| Li | st of | figures |                                  | xiii |

| Li | st of | tables  |                                  | xvii |

| 1  | Intr  | oducti  | ion                              | 1    |

|    | 1.1   | DRAN    | M Caches and Server Applications | . 3  |

|    | 1.2   | Footp   | orint Cache                      | . 4  |

|    | 1.3   | Scalal  | ble DRAM Caches                  | . 5  |

|    | 1.4   | Impro   | oving DRAM Cache Efficiency      | . 6  |

|    | 1.5   | Thesi   | s Statement and Contributions    | . 8  |

| 2  | DRA   | AM Cad  | ches and Server Applications     | 11   |

|    | 2.1   | Backg   | ground and Motivation            | . 12 |

|    |       | 2.1.1   | DRAM Cache Design Objectives     | . 14 |

|    |       | 2.1.2   | Block-Based Caches               | . 15 |

|    |       | 2.1.3   | Page-Based Caches                | . 16 |

|    |       | 2.1.4   | Summary                          | . 18 |

|    | 2.2   | Spatia  | al and Temporal Characterization | . 18 |

|    |       | 2.2.1   | Methodology                      | . 18 |

|    |       | 2.2.2   | Temporal Behavior                | . 18 |

|    |       | 2.2.3   | Spatial Behavior                 | . 19 |

|    |       | 2.2.4   | Block-Based vs. Page-Based       | . 21 |

| 3  | Foo   | tprint  | Cache                            | 25   |

|    | 3.1   | Footp   | orint Cache                      | . 25 |

|    |       | 3.1.1   | Footprint Prediction             | . 26 |

### **Contents**

|   |      | 3.1.2    | Capacity Optimization                     | 27 |

|---|------|----------|-------------------------------------------|----|

|   | 3.2  | Footpr   | int Cache Design                          | 28 |

|   |      | 3.2.1    | Footprint Cache Tag Array                 | 28 |

|   |      | 3.2.2    | Prediction History                        | 29 |

|   |      | 3.2.3    | Footprint Generation                      | 30 |

|   |      | 3.2.4    | Capacity Optimization                     | 30 |

|   | 3.3  | Metho    | dology                                    | 31 |

|   |      | 3.3.1    | Baseline System                           | 31 |

|   |      | 3.3.2    | DRAM Cache Organizations                  | 32 |

|   |      | 3.3.3    | Workloads                                 | 34 |

|   |      | 3.3.4    | Simulation Infrastructure                 | 35 |

|   | 3.4  | Results  | 8                                         | 35 |

|   |      | 3.4.1    | Spatial Characterization                  | 35 |

|   |      | 3.4.2    | Coverage and Off-Chip Bandwidth           | 36 |

|   |      | 3.4.3    | Performance                               | 38 |

|   |      | 3.4.4    | Sensitivity to Page Size and History Size | 39 |

|   |      | 3.4.5    | Impact of Capacity Optimization           | 40 |

|   |      | 3.4.6    | Energy Implications                       | 40 |

|   |      | 3.4.7    | Other Page-Based Proposals                | 42 |

|   | 3.5  | Discus   | sion                                      | 43 |

|   |      | 3.5.1    | Footprint Cache and Coherence             | 43 |

|   |      | 3.5.2    | Knowledge and Transfer of PC              | 43 |

|   |      | 3.5.3    | SRAM Area Overhead                        | 45 |

|   |      | 3.5.4    | Other Processor Architectures             | 46 |

|   |      | 3.5.5    | Cache Capacity                            | 46 |

|   |      | 3.5.6    | Footprint Cache in Non-3D Systems         | 47 |

|   | 3.6  | Conclu   | ısion                                     | 47 |

| 4 | Scal | lable DI | RAM caches                                | 49 |

|   | 4.1  | Block-   | Based Caches with DRAM-Based Tags         | 51 |

|   | 4.2  | Unisor   | n Cache                                   | 53 |

|   |      | 4.2.1    | Alternative Approaches                    | 60 |

|   |      |          | Summary and Comparisons                   | 62 |

|   | 4.3  |          | dology                                    | 63 |

|   |      |          | Simulation Infrastructure                 | 63 |

|   |      |          | Baseline System Configuration             | 63 |

|   |      | 4.3.3 DRAM Cache Organizations                           | 64  |

|---|------|----------------------------------------------------------|-----|

|   |      | 4.3.4 Workloads                                          | 65  |

|   | 4.4  | Evaluation                                               | 65  |

|   |      | 4.4.1 Predictor Accuracy                                 | 65  |

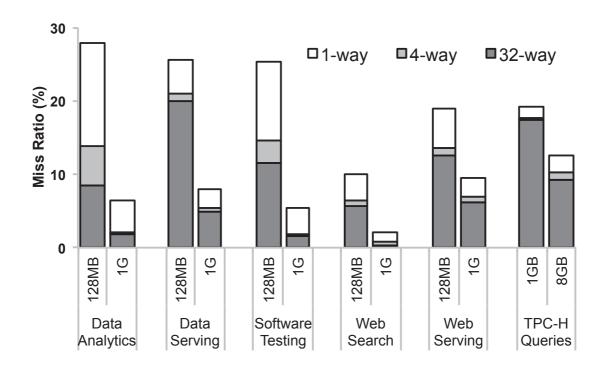

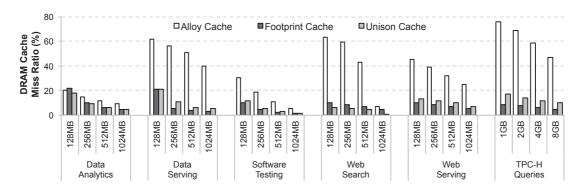

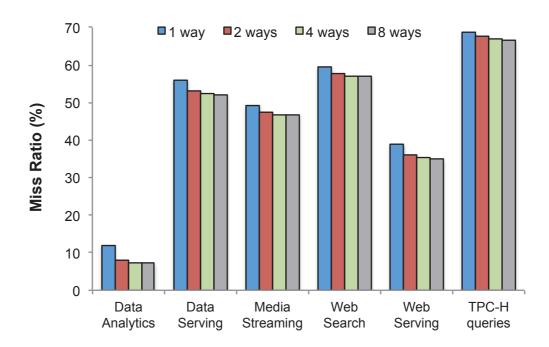

|   |      | 4.4.2 Miss Ratio                                         | 67  |

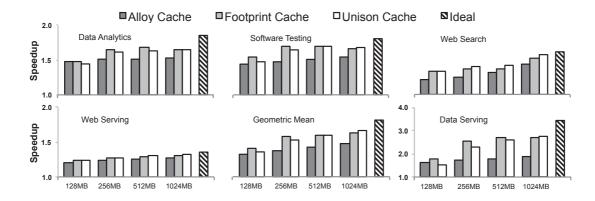

|   |      | 4.4.3 Performance                                        | 69  |

|   |      | 4.4.4 Energy Considerations                              | 70  |

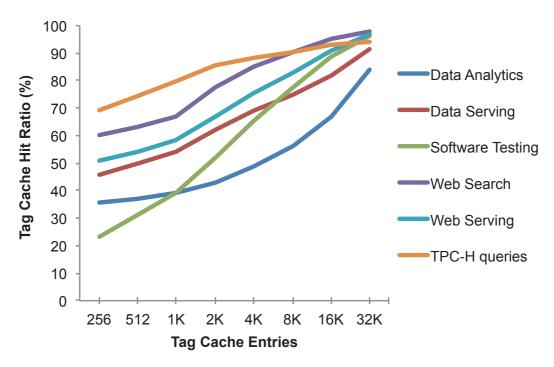

|   | 4.5  | Tag Cache                                                | 70  |

|   |      | 4.5.1 Tag Cache vs. Miss Predictor                       | 73  |

|   | 4.6  | Efficient Footprint Tracking through Sampling            | 74  |

|   | 4.7  | Page Alignment                                           | 76  |

|   |      | 4.7.1 Effects of Misalignments                           | 76  |

|   |      | 4.7.2 Mitigating Page Alignment Problems in Unison Cache | 77  |

|   | 4.8  | Unison Cache in the Context of Near-Memory Acceleration  | 80  |

|   | 4.9  | Summary                                                  | 82  |

| 5 | Res  | search Directions for Improving DRAM Cache Efficiency    | 83  |

|   | 5.1  | Increasing the Associativity in DRAM Caches              | 84  |

|   |      | 5.1.1 Associativity in Block-Based DRAM Caches           | 84  |

|   |      | 5.1.2 Associativity in Page-Based DRAM Caches            | 87  |

|   | 5.2  | Cache Insertion and Promotion Policies                   | 89  |

|   |      | 5.2.1 Promotion upon Evictions                           | 92  |

|   |      | 5.2.2 Summary                                            | 93  |

|   | 5.3  | Cache Bypassing                                          | 93  |

|   |      | 5.3.1 Random Cache Bypassing                             | 95  |

|   |      | 5.3.2 PC-Based Cache Bypassing                           | 97  |

|   |      | 5.3.3 Cache Bypassing in Page-Based Designs              | 103 |

|   | 5.4  | Dead-Block and Dead-Page Prediction                      | 103 |

|   |      | 5.4.1 Quantitative Comparison                            | 105 |

|   | 5.5  | Prefetching                                              | 107 |

| 6 | Rela | ated Work 1                                              | .09 |

|   | 6.1  | Die-Stacked DRAM                                         | 109 |

|   | 6.2  | Spatial Prefetchers                                      | 110 |

|   | 6.3  | Cache Bypassing                                          | 111 |

|   | 6.4  | Way Prediction                                           | 111 |

### **Contents**

|    | 6.5 Dead-Block Prediction | 112 |  |

|----|---------------------------|-----|--|

| 7  | Conclusions               | 113 |  |

| Bi | Bibliography              |     |  |

| Cı | ırriculum Vitae           | 125 |  |

# **List of Figures**

| 2.1 | Opportunity for performance improvement with high-bandwidth and low-latency       |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | die-stacked DRAM                                                                  | 13 |

| 2.2 | A DRAM die stacked on top of the logic die architected as a block-based cache.    |    |

|     | One tag entry corresponds to one data block                                       | 15 |

| 2.3 | A DRAM die stacked on top of the logic die architected as a page-based cache.     |    |

|     | Only the useful blocks (accessed by the cores) are shown in the figure. One tag   |    |

|     | entry corresponds to one page                                                     | 17 |

| 2.4 | Miss ratio of a block-based cache design for TPC-H database queries on a ma-      |    |

|     | chine with 128GB of main memory.                                                  | 20 |

| 2.5 | Miss ratio of a block-based cache design for TPC-H database queries on a ma-      |    |

|     | chine with 128GB of main memory as compared to a mix of SPEC2006 INT              |    |

|     | applications)                                                                     | 21 |

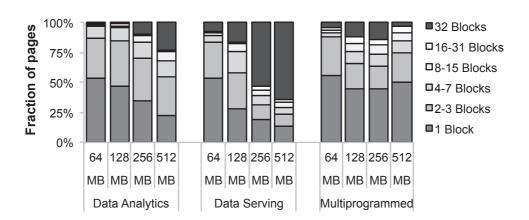

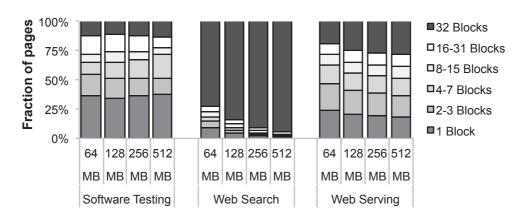

| 2.6 | Page density as a function of cache size for Data Analytics, Data Serving and the |    |

|     | Multiprogrammed workloads                                                         | 22 |

| 2.7 | Page density as a function of cache size for Software Testing, Web Search, and    |    |

|     | Web Serving                                                                       | 22 |

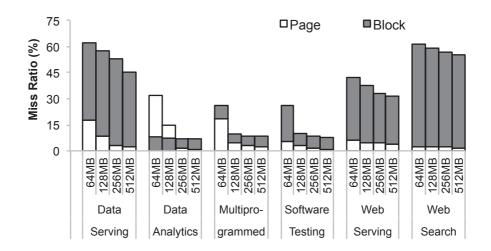

| 2.8 | Miss ratio in block-based and page-based DRAM cache designs                       | 23 |

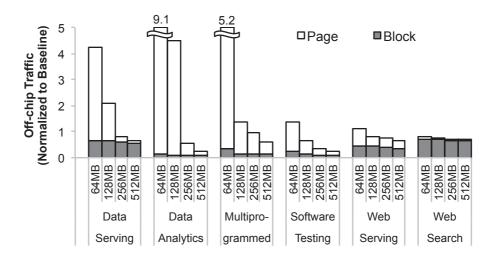

| 2.9 | Off-chip traffic in block-based and page-based DRAM cache designs normalized      |    |

|     | to the baseline system without a DRAM cache                                       | 23 |

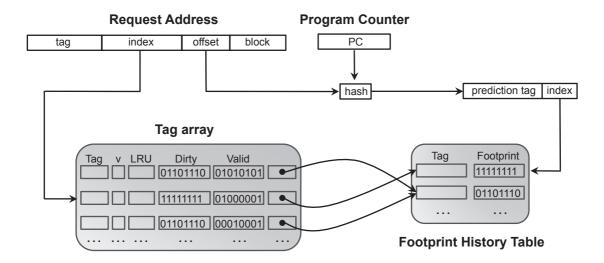

| 3.1 | Footprint Cache tag array and Footprint History Table (FHT)                       | 28 |

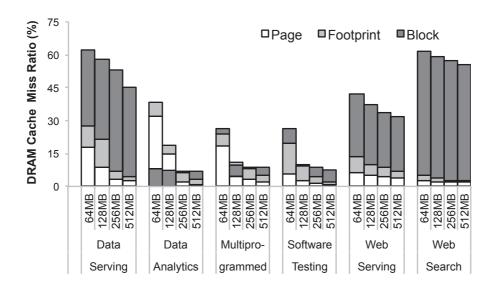

| 3.2 | Miss ratio of Block-based, Footprint, and Page-based cache organizations, nor-    |    |

|     | malized to a baseline system without a DRAM cache                                 | 36 |

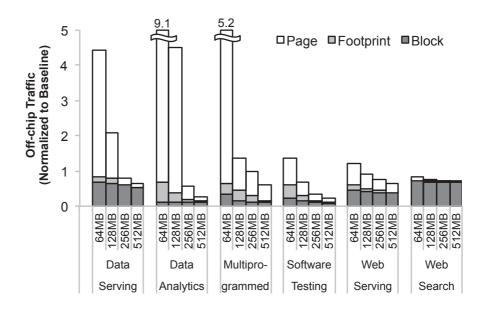

| 3.3 | Off-chip bandwidth requirements of Block-based, Footprint, and Page-based         |    |

|     | cache organizations, normalized to a baseline system without a DRAM cache. $$ .   | 37 |

| 3.4 | Performance improvement of various designs over the baseline system for the       |    |

|     | Data Analytics and Multiprogrammed workloads                                      | 38 |

### **List of Figures**

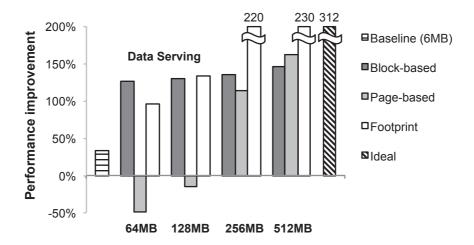

| 3.5  | Performance improvement of various designs over the baseline system for Data       |    |

|------|------------------------------------------------------------------------------------|----|

|      | Serving                                                                            | 39 |

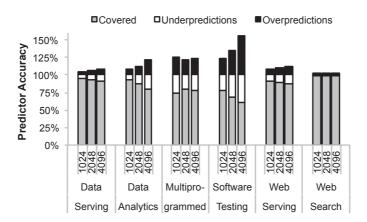

| 3.6  | Predictor accuracy sensitivity to the page size, for a 256MB cache with 16K FHT    |    |

|      | entries                                                                            | 40 |

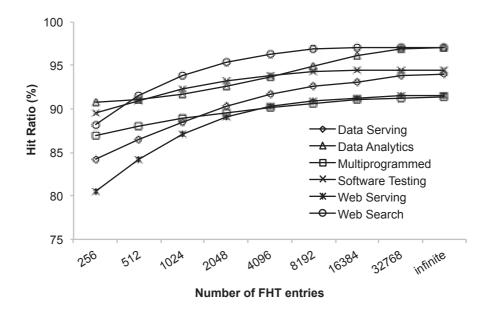

| 3.7  | Hit ratio sensitivity to the history size. The DRAM cache capacity is 256MB and    |    |

|      | the page size is 2KB                                                               | 41 |

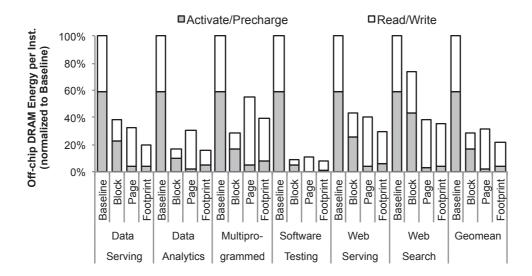

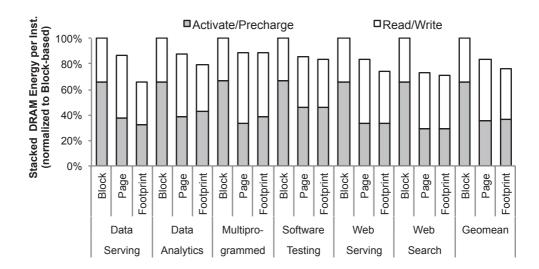

| 3.8  | Off-chip DRAM dynamic energy per instruction normalized to the baseline system.    | 42 |

| 3.9  | Stacked DRAM dynamic energy per instruction normalized to the block-based          |    |

|      | design                                                                             | 43 |

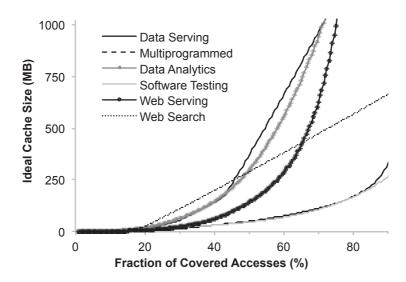

| 3.10 | Minimum size of an ideal cache needed to cover a given fraction of cache accesses. | 44 |

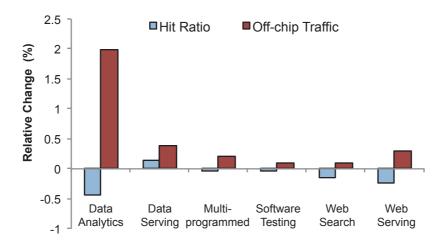

| 3.11 | Relative change in hit ratio and off-chip traffic for a 256MB Footprint Cache with |    |

|      | 1KB pages using a tagless history table, normalized to the design with complete    |    |

|      | tags                                                                               | 46 |

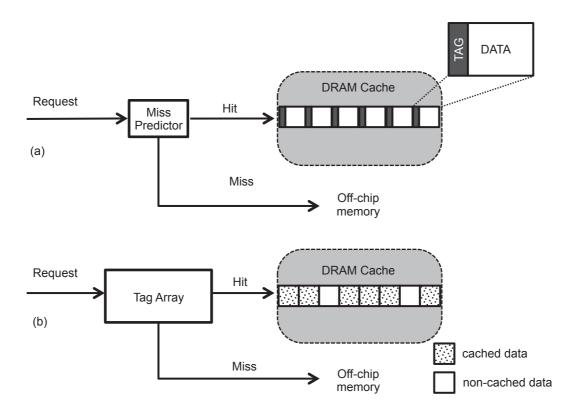

| 4.1  | Overview of the (a) Alloy Cache and (b) Footprint Cache designs                    | 52 |

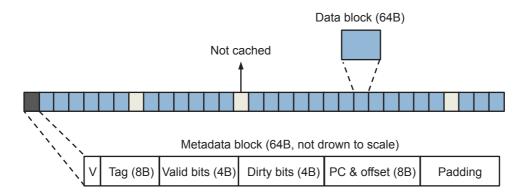

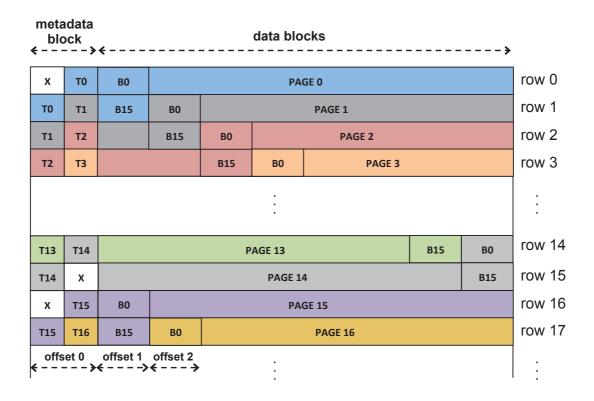

| 4.2  | DRAM row content in Unison Cache (not drawn to scale)                              | 54 |

| 4.3  | DRAM row organization in the Unison Cache design                                   | 56 |

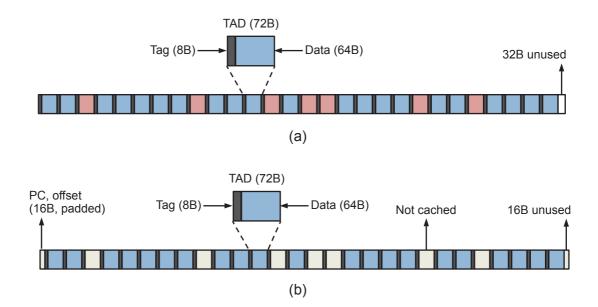

| 4.4  | DRAM row organizations for (a) block-based cache with footprint prediction,        |    |

|      | and (b) page-based cache with tagged blocks.                                       | 59 |

| 4.5  | Unison Cache's miss ratio as a function of associativity                           | 67 |

| 4.6  | Miss ratio comparison of Alloy Cache, Footprint Cache, and Unison Cache            | 68 |

| 4.7  | Performance comparison of Alloy, Footprint, and Unison Caches. Note the            |    |

|      | difference in scale for Data Serving.                                              | 68 |

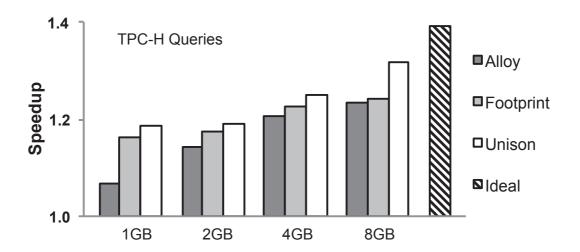

| 4.8  | Performance comparison for TPC-H queries                                           | 70 |

| 4.9  | Tag cache hit ratio as a function of the number of tag cache entries. Each entry   |    |

|      | corresponds to one cache set (four 1KB pages) and requires 40B of storage          | 72 |

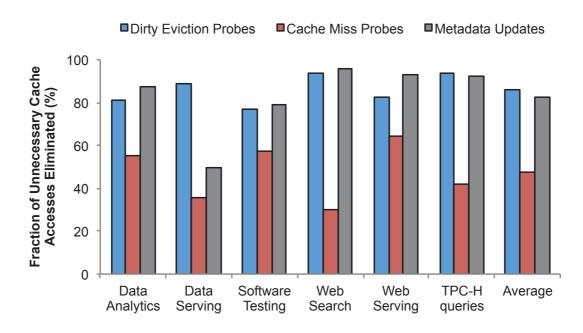

| 4.10 | Cache accesses eliminated by a practical tag cache with a three-cycle access       |    |

|      | latency. The figure shows the fraction of unnecessary probes upon dirty evictions  |    |

|      | and cache misses that are eliminated, as well as the fraction of LRU/metadata      |    |

|      | updates upon cache hits that can be coalesced. The cache capacity is 256MB         |    |

|      | (2GB for TPC-H queries)                                                            | 73 |

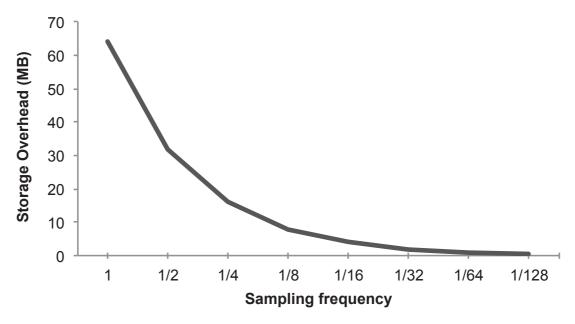

| 4.11 | Storage required for PC & offset pairs for an 8GB cache with 1KB pages             | 75 |

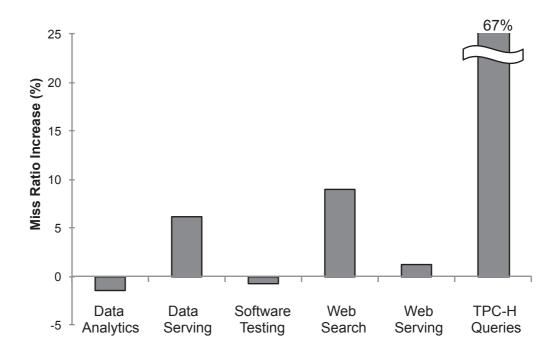

| 4.12 | 2 Increase in miss ratio due to misaligned pages.                                  | 77 |

| 4.13 | 3 Alternative data layout with 1KB pages                                           | 78 |

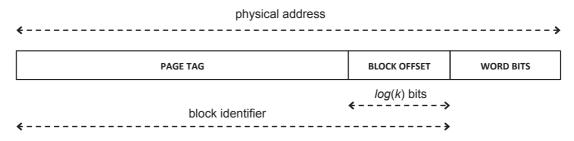

| 4.14 | Physical address bits                                                              | 79 |

| 5.1 | Miss ratio as a function of associativity for a 256MB block-based cache (2GB for TPC-H queries)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2 | Way prediction accuracy as a function of associativity for a 256MB block-based cache (2GB for TPC-H queries)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86 |

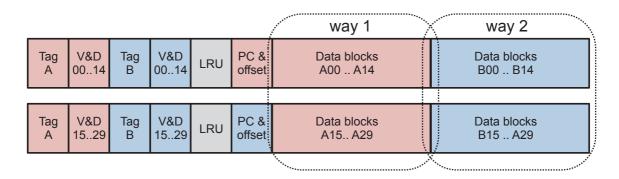

| 5.3 | The layout in DRAM of a single cache set in a two-way associative cache with 2KB pages and 2KB DRAM rows. Each cache set consists of two DRAM rows, and each way spans both rows                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88 |

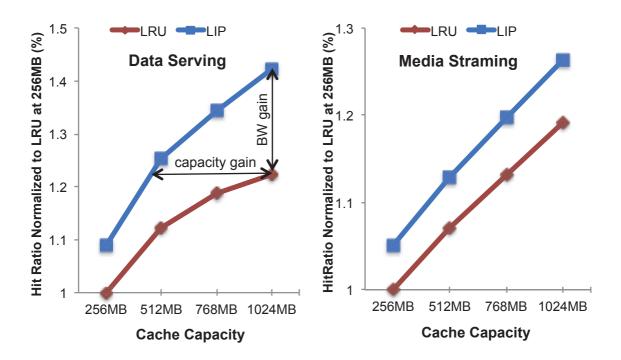

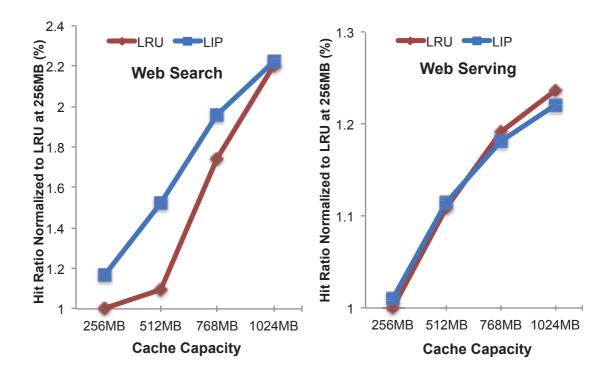

| 5.4 | Hit ratio in a four-way associative block-based DRAM cache with the traditional LRU policy and MRU Insertion (LRU) and with LRU Insertion (LIP) for Data Serving (left) and Media Streaming (right). Note the difference in the scale. Increase in hit ratio is directly proportional to the off-chip bandwidth savings (vertical dimension). The horizontal distance in the figure directly corresponds to the difference in effective capacity between the designs                                                                                                                                                | 90 |

| 5.5 | Hit ratio in a four-way associative block-based DRAM cache with the traditional LRU policy and MRU Insertion (LRU) and with LRU Insertion (LIP) for Web Search (left) and Web Serving (right). Note the difference in scale. Increase in hit ratio is directly proportional to the off-chip bandwidth savings (vertical dimension). The horizontal distance in the figure directly corresponds to the difference in effective capacity between the designs. The point in the figure on the right at which the curves cross each other is a starting point after which a block is more likely to be reused than not. | 91 |

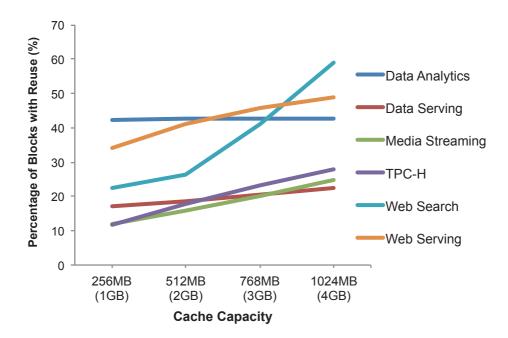

| 5.6 | Fraction of evicted blocks that were reused before their eviction for various cache sizes. The cache is organized as direct-mapped block-based cache. The cache size for CloudSuite applications is between 256MB-1024MB, whereas for TPC-H queries the cache size is between 1GB and 4GB. The reuse of all blocks that flow in and out of the cache on average ranges between 23% for the smallest cache size, and 37% for the largest cache size                                                                                                                                                                  | 94 |

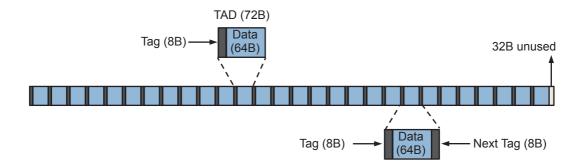

| 5.7 | DRAM row layout in Alloy Cache and BEAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95 |

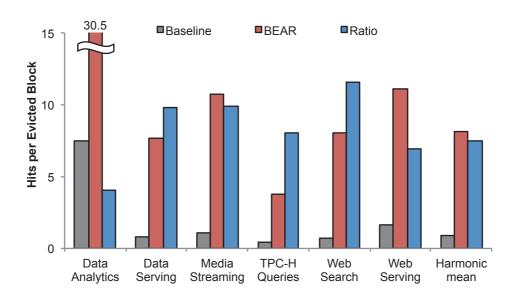

| 5.8 | Average number of accesses per block with (BEAR) and without (Baseline) random bypassing for a 256MB cache (2GB for TPC-H Queries), and the ratio between the two                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 96 |

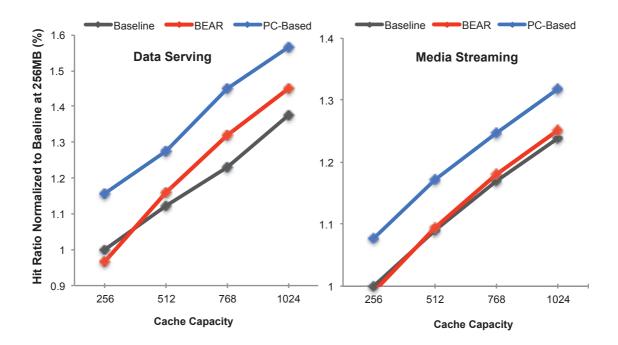

| 5.9  | Hit ratio of a direct-mapped Alloy Cache (baseline), Alloy Cache with random            |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | cache bypassing (BEAR) and PC-based bypassing for Data Serving (left) and               |     |

|      | Media Streaming (right), normalized to the baseline design at 256MB. Note the           |     |

|      | difference in the scale. Increase in hit ratio is directly proportional to the off-chip |     |

|      | bandwidth savings (vertical dimension). The horizontal distance in the figure           |     |

|      | directly corresponds to the difference in effective capacity between the designs        | 100 |

| 5.10 | Hit ratio of a direct-mapped Alloy Cache (baseline), Alloy Cache with random            |     |

|      | block bypassing (BEAR), and PC-based bypassing for Web Search (left) and Web            |     |

|      | Serving (right), normalized to the baseline design at 256MB. Note the difference        |     |

|      | in the scale. The horizontal distance in the figure directly corresponds to the         |     |

|      | difference in effective capacity between the designs                                    | 101 |

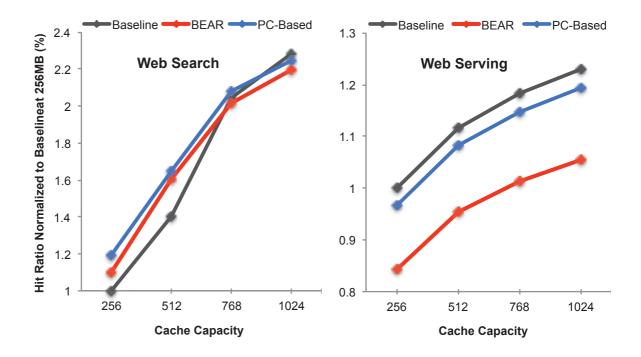

| 5.11 | Hit ratio of a direct-mapped Alloy Cache (baseline), Alloy Cache with random            |     |

|      | block bypassing (BEAR), and PC-based bypassing for Data Analytics, normalized           |     |

|      | to the baseline design at 256MB (left) and TPC-H queries, normalized to the 1GB         |     |

|      | baseline (right). Note the difference in the scale. The horizontal distance in the      |     |

|      | figure directly corresponds to the difference in effective capacity between the         |     |

|      | designs                                                                                 | 102 |

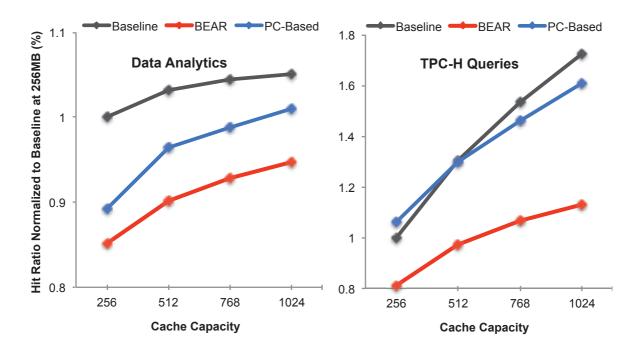

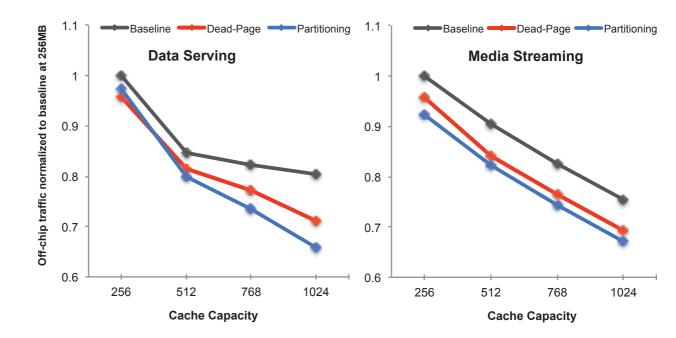

| 5.12 | Off-chip traffic in Data Serving and Media Streaming in the baseline four-way           |     |

|      | Unison Cache, Unison Cache with counter-based dead-page prediction and                  |     |

|      | Unison Cache with cache partitioning. The results are normalized to the off-chip        |     |

|      | traffic of the baseline design at 256MB. The horizontal distance in the figure          |     |

|      | directly corresponds to the difference in effective capacity between the designs.       | 105 |

# **List of Tables**

| 2.1 | Comparison of block-based and page-based designs                                  | 17 |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | Architectural system parameters                                                   | 19 |

| 3.1 | Block state encoding                                                              | 30 |

| 3.2 | Architectural system parameters                                                   | 32 |

| 3.3 | Footprint Cache parameters                                                        | 33 |

| 3.4 | Block-based cache parameters                                                      | 33 |

| 3.5 | Page-based cache parameters                                                       | 33 |

|     |                                                                                   |    |

| 4.1 | Comparison of Alloy Cache (AC), Footprint Cache (FC), and Unison Cache (UC).      | 51 |

| 4.2 | Comparison of key characteristics of different DRAM cache schemes                 | 60 |

| 4.3 | Architectural system parameters                                                   | 64 |

| 4.4 | Footprint Cache parameters                                                        | 64 |

| 4.5 | Accuracy of various predictors: Miss Predictor (MP) in Alloy Cache, and Footprint |    |

|     | Predictor (FP) in Footprint Cache and Unison Cache, and Way Predictor (WP) in     |    |

|     | Unison Cache for a 1GB cache (8GB for TPC-H queries)                              | 66 |

## 1 Introduction

Computer systems are among the worst affected by the ongoing energy crisis. For many decades the advancements in semiconductor technology have regularly provided exponential increase in computing power within a constant power budget. The technology advancements have recently started reaching the limits of physics, making it impossible to gain more in computing without investing more energy. Unfortunately, the overall energy budget allocated to computing is already prohibitively high, while the demand for computing is increasing exponentially as a consequence of data explosion and the constant emergence of new IT-based services. Most of those services are hosted in massive datacenters, whose space and energy footprints are constantly increasing. Minimizing the energy footprint and maximizing the compute and storage density are therefore the highest priority goals for datacenter operators, with substantial global impact. Efforts toward these goals must not, however, sacrifice the quality of these services, which is vital to their economic success.

Maximizing the compute density while minimizing the energy footprint mandates a dramatic increase in throughput per server chip with each technology generation at a reduced energy cost. With the slowdown both in Dennard Scaling and of Moore's law, server chips are resorting to larger numbers of increasingly less complex cores and specialized accelerators to support big data processing, while maintaining a practical power envelope and transistor budget. The resulting highly parallel processor organizations greatly benefit datacenter server workloads, which exhibit abundant request-level parallelism. This growth in core count, however, ultimately drives server processor designs into a memory bandwidth wall due to poor pin count scalability. Emerging many-core server chips with hundreds of cores are already able to utilize and even exceed their bandwidth budgets [21, 50], hitting the bandwidth wall before the power wall [21], and making the memory bandwidth a scarce resource.

### **Chapter 1. Introduction**

The strict response latency requirements of IT-based services put enormous pressure on storage systems in datacenters. The dramatic increase in the amount of data mandates the use of high-density storage systems and devices. The high density and low access latency requirements are in a direct conflict. To meet both requirements, datacenter operators must keep massive amounts of frequently accessed data in main memory, which increasingly acts as a DRAM-based data cache. It is thus common for a today's server to accommodate hundreds of gigabytes of main memory per processor chip. Unfortunately, the need for high memory capacity puts further pressure on memory bandwidth. To be able to attach hundreds of gigabytes of DRAM to a single chip, multiple DRAM modules must be connected to every DRAM channel. Sharing a DRAM channel by multiple DRAM modules requires lowering the frequency of the channel, directly reducing its bandwidth and creating a fast-track to the bandwidth wall.

Die-stacked DRAM has been advocated as a promising technology to break the memory bandwidth wall and improve memory latency and density. It delivers several times more internal bandwidth compared to off-chip memory due to dense on-chip TSV buses, as well as lower access latency due to the reduction in physical distances enabled by die stacking. Recent advancements in die-stacking technologies have made it possible to tightly integrate a sizeable amount of DRAM in the same package as the processor. Having die-stacked DRAM on the chip or in the package could virtually eliminate the memory bandwidth wall by exposing all of its internal bandwidth at lower access latency. The latency advantage that die-stacked on-chip DRAM provides over conventional off-chip DRAM is particularly important in server applications, which are known to be memory-bound and suffer from low memory-level parallelism [1, 12].

Technological constraints, however, limit the on-chip stacked DRAM capacity to levels that are orders of magnitude lower than what modern server applications demand. It is impossible to fit all the main memory distributed across multiple multi-chip DRAM modules onto a single processor chip. Such a constraint forces the architects to use the on-chip stacked DRAM as a hardware-managed cache or as a software-managed cache or scratchpad. Managing die-stacked DRAM in software is a preferable option in custom designs where hardware and software evolve together, such as embedded systems. In contrast, deep, diverse and rapidly changing software stacks in server systems rely on general-purpose processors and operating systems, mandating non-intrusive hardware-based solutions.

This thesis investigates the use of on-chip die-stacked DRAM as a hardware-managed cache in processor chips for datacenters with the purpose of reducing memory traffic on the processor

side and improving memory latency. We provide a detailed characterization of real-world server software stacks with respect to DRAM caches in order to gain the critical insights that will lead us to appropriate cache designs. We demonstrate the potential of die-stacked DRAM caches to reduce memory traffic and improve memory latency in server systems, and propose effective, scalable and energy-efficient designs that realize that potential.

### 1.1 DRAM Caches and Server Applications

Our key observation is that server applications exhibit abundant spatial locality that becomes visible in high-capacity caches, such as on-chip DRAM caches. The reason behind the abundance of spatial locality is in the nature of server applications, which typically manipulate large objects or streams of data. The reason why this locality becomes apparent in DRAM caches is related to the long residency of objects at this level of the memory hierarchy: the longer an object stays in the cache, the more of it eventually becomes accessed by the processor.

While spatial locality in DRAM caches is abundant, temporal locality is scarce. Most of the temporal data reuse that happens within a short amount of time, e.g., within a single request, is filtered by L1 caches and is rarely seen in lower levels of the cache hierarchy. Data reuse seen in DRAM caches typically happens across independent requests and highly depends on object popularity distributions, also known as data skew; the more skewed the application data is, the more reuse takes place. As the cache size increases, the residency of objects in the cache increases and so does the probability of their reuse. Practical on-chip DRAM sizes, unfortunately, can capture only 1-2% of the hundreds of gigabytes stored in off-chip DRAM, which is typically not enough to capture the working set comprising the most frequently accessed data even under high skew.

The abundance of spatial locality and the paucity of temporal locality suggest that DRAM caches may benefit from large cache lines. DRAM caches that organize and fetch data in spatial regions of several kilobytes (e.g., 4KB pages) take advantage of the spatial locality and exhibit an order of magnitude lower miss rate compared to caches that manage data in conventional 64B blocks [18, 29, 30, 41]. We refer to such designs as *page-based caches*. Managing data at such coarse granularity also results in a commensurate reduction in tag space, which enables the placement of tags in SRAM for moderately sized caches. Unfortunately, the excessive data overfetch caused by accesses to sparse pages may substantially increase the off-chip traffic and offset any bandwidth benefits provided by caching.

Cache designs that employ conventional 64B blocks [46, 47, 48, 55], and which we refer to as

block-based caches, utilize the available off-chip bandwidth much more efficiently, but see an order of magnitude more misses compared to their page-based counterparts. Although some of the gap in miss rates between the designs could be bridged through prefetching, existing implementation of block-based designs do not provide efficient support for it. Because block-based caches do the bookkeeping at the level of individual blocks, they require prohibitively large tag space that cannot be stored in SRAM even for the smallest DRAM cache sizes and therefore store the tag array in the stacked DRAM. Storing tags in DRAM either significantly increases the cache access latency [46, 47, 48] or completely disables cache associativity in block-based designs [55], enforcing a direct-mapped organization. While the direct-mapped organization *per se* does not harm block-based DRAM caches due to the large number of sets, it does not support many standard cache optimization techniques that rely on associativity. In contrast to page-based caches, block-based designs efficiently utilize the available cache capacity, because they do not suffer from fragmentation. However, limited temporal locality implies that on-chip DRAM caches are less sensitive to small capacity variations; techniques that suboptimally use cache capacity will therefore not necessarily perform suboptimally.

### 1.2 Footprint Cache

Block-based and page-based designs show complementary properties. On one hand, block-based designs are much more efficient in using cache capacity and off-chip bandwidth, but suffer from low hit rates. Their tag array is huge and must be stored in DRAM at the cost of either high latency or associativity. On the other hand, page-based caches provide high hit rates and small and arbitrarily associative SRAM-based tag storage. However, they severely misuse the precious off-chip bandwidth resources, and as such are not a feasible option.

Our goal is to preserve the properties of page-based designs, but without the unnecessary traffic and with better capacity management. Toward that goal, we propose Footprint Cache, which is a sectored cache organization that separates the cache allocation unit from the fetch unit. Upon a cache miss, Footprint Cache allocates a page, but fetches only those 64-byte blocks within the page that are predicted to be useful in future. In doing so, Footprint Cache eliminates the unnecessary off-chip and on-chip traffic stemming from the movement of unused data.

To mitigate the poor capacity management in page-based designs, Footprint Cache identifies pages that have the fewest useful blocks and show neither spatial nor temporal reuse, and does not allocate entries in the cache for such pages. It instead fetches 64-byte blocks from

such pages, one by one and only on demand, and forwards them to the requestor, bypassing the cache. Such pages account for a significant fraction of all pages that are fetched and make the biggest contribution to the capacity waste.

Footprint Cache mitigates most of the bandwidth and capacity problems of page-based designs and manages to get the best of the page-based and block-based designs. The key to Footprint Cache's success is its *fooprint predictor*, a simple hardware structure that estimates the spatial *footprint* of each page — i.e., the exact set of blocks that will be demanded during the page's on-chip residency. To design an effective footprint predictor, we rely on the observation that the majority of huge server datasets are accessed by a limited number of code fragments that have repetitive and predictable behavior and result in recurring access patterns. Our footprint predictor fully relies on the correlation between the code and spatial locality [62] to predict access patterns within each page, which are then used to reduce both the bandwidth and the capacity waste in page-based designs. Furthermore, by fetching and evicting all useful data in a page at once, Footprint Cache significantly reduces the number of row activations in off-chip DRAM and saves a substantial amount of its dynamic power.

#### 1.3 Scalable DRAM Caches

What allows Footprint Cache to store its tags in SRAM is its page-based organization, which minimizes the storage required for the tags. It is best suited for caches in the range of several hundred megabytes. However, as the technology rapidly enables multi-gigabyte stacked DRAM capacities, even page-based tags will quickly consume too much SRAM to be practical. To illustrate, 8GB of stacked DRAM organized in 4KB pages would need 16MB of SRAM in the best case, which is in the order of today's last-level cache sizes. This storage drastically increases if the cache uses sub-blocking to optimize for off-chip bandwidth, as Footprint Cache does. Furthermore, while the stacked DRAM provides a huge increase in bandwidth compared to conventional DDR channels, the *latency* of the die-stacked DRAM is not substantially better. If a DRAM cache architecture requires accessing the stacked-DRAM or a multi-megabyte SRAM table for tag lookups, then that could add several tens of cycles to the overall cache latency, offsetting any latency advantage of the stacked DRAM technology.

To overcome Footprint Cache's scalability limitation, we introduce a novel set-associative page-based DRAM cache design, called Unison Cache, which carefully incorporates the tag metadata directly into the stacked DRAM to enable scalability to arbitrary stacked-DRAM capacities. Unison Cache stores each cache set in a DRAM row, placing page tags at the beginning of

each DRAM row, followed by the corresponding data blocks. To support associativity without serializing tag and data accesses, Unison Cache employs a simple address-based way predictor, which is, thanks to the spatial locality and large page size, highly accurate. Upon a cache request, provided that the way prediction is correct, the exact location of the requested block can be correctly determined. Although every data block is physically separated from its tag within the DRAM row, the positions of both the tag and the data block are known in advance, so the tag and data accesses can be fully overlapped, removing the tag lookup latency from the critical path.

### 1.4 Improving DRAM Cache Efficiency

The main motivation behind the research on DRAM caches is the reduction in traffic between the processor and the memory. DRAM caches provide a traffic reduction on the processor side solely through reuse of locally stored copies of data within high capacity on-chip DRAM. What makes the reuse possible is data skew; certain types of data, such as metadata, are more frequently accessed than others; certain objects also happen to be more popular than others. Despite their high capacity, practical DRAM cache sizes are still two orders of magnitude smaller than the off-chip main memory in the subsequent level of the hierarchy and as such cannot accommodate the hot data structures for the majority of applications [28]. As a result, the amount of temporal reuse in on-chip DRAM caches is fairly low [8, 29].

The underlying mechanism through which capacity-constrained caches exploit reuse is associativity, which stands for the number of slots into which a new cache entry can be inserted. Associativity enables control over the placement of data in the cache and over their promotion through recency lists that aim to rank the possible victim options according to the likelihood of their reuse. Unfortunately, practical DRAM cache implementations provide either no associativity at all [8, 55] or very limited associativity [18, 28, 55], which severely limits the cache's ability to identify and keep reusable data in the cache.

The abundance of spatial locality and the lack of either temporal reuse or mechanisms to exploit it may lead to cache thrashing. In page-based designs, pages with high spatial locality typically show less temporal reuse and occupy space in the cache for a long time, but are often not useful after they are completely scanned. In block-based designs, most of the data that is inserted into the cache is *dead upon arrival* [8, 29]. It is therefore important to provide DRAM caches with mechanisms that would on one hand minimize the cache space and cache bandwidth resources allocated to data that is not reused, and on the other hand exploit the

existing and encourage more reuse among data that are prone to it, and therefore improve the overall cache efficiency.

In this thesis we revisit some of the traditional techniques for improving cache efficiency in the context of DRAM caches. We demonstrate that they are either ineffective or not directly applicable to DRAM caches. We recognize the problems associated with applying those techniques to DRAM caches and propose new research directions that have the potential to improve cache efficiency. The techniques we consider include:

- Increasing associativity, which is a trivial technique to reduce the number of conflict misses and support reuse. Increasing associativity in SRAM caches is expensive from the power perspective, but in DRAM caches has different benefits and cost implications. Increasing associativity in block-based DRAM caches provides minimal benefit in terms of hit rates, but enables a variety of cache optimization techniques that rely on associativity. Unfortunately, increasing associativity in block-based DRAM caches is not practical as it implies a commensurate increase in die-stacked DRAM bandwidth. On the contrary, we find that associativity is vital to performance of page-based DRAM caches and for which we propose techniques to support arbitrarily high associativity.

- Cache bypassing, which aims to identify non-reusable cache blocks and avoid storing them in the cache to prevent cache pollution. Cache bypassing avoids pollution in block-based DRAM caches, but existing block-based DRAM solution lack support for it, as they cannot identify non-reusable data in a practical way. Instead, bypassing of randomly selected cache blocks could be used not to improve the hit ratio, but to trade it for a reduction in cache activity [8]. We demonstrate that PC-based prediction techniques have the potential to more accurately identify non-reusable blocks, and we propose an efficient method for their integration into block-based DRAM caches. Our method relies on sampling and incurs no cost related to storage, bandwidth or latency. Unlike block-based caches, page-based DRAM caches can more easily identify non-reusable data. However, we show that applying cache bypassing to page-based DRAM caches may do more harm than good, as it reduces the number of cache hits and severely undermines the opportunity for energy savings in off-chip DRAM.

- Improved policies for cache insertion, promotion and replacement. We demonstrate that the fundamental cache replacement optimizations [56] are applicable neither to block-based nor to page-based DRAM caches. Namely, such techniques fundamentally rely on associativity, whereas state-of-the-art block-based DRAM caches are direct-

mapped [8, 55]. Page-based caches confuse the optimization techniques by promoting a whole page, i.e., by giving it a recently accessed status upon accesses to different blocks within the same page. While such situations happen due to page reuse — i.e., due to spatial locality — the effective temporal data reuse does not happen. The optimization techniques will therefore confuse spatial locality for temporal and promote the page in question, penalizing pages that do exhibit temporal reuse.

- Dead-block prediction. There has been a large body of research trying to mitigate the cache pollution problem in SRAM caches through dead-block prediction [35, 23, 36, 40, 44]. We show that while dead-block prediction can be accurately performed in block-based DRAM caches, the lack of cache associativity severely limits its usability. In contrast, we show that PC-based *dead-page prediction* could almost double the effective page-based cache capacity for certain applications, while leveraging existing Unison Cache's metadata structures to perform predictions.

- Prefetching. Page-based designs implicitly rely on spatial prefetching to boost their hit

ratio. Although prefetching could significantly benefit block-based designs as well, we

show that the lack of centralized information about the presence of neighboring blocks

in the cache severely limits the applicability of spatial prefetchers in block-based DRAM

caches. Further research on effective prefetchers for block-based DRAM caches is highly

encouraged.

#### 1.5 Thesis Statement and Contributions

The thesis statement reads as follows:

Effective and efficient on-chip DRAM cache designs for servers must leverage the abundant spatial locality in server applications and must do so in a bandwidth- and capacity-efficient manner.

Using analytic models, trace-driven and cycle-accurate full-system simulation of modern, real-world server workloads, this thesis demonstrates that:

High capacity on-chip DRAM caches expose abundant spatial locality of server applications and their modest temporal locality. As a consequence, DRAM caches that manage and fetch data at a coarser granularity exhibit overall superior properties compared to caches that do fine-grain management. These properties include higher hit rates, smaller tag storage, and higher energy efficiency. However, their naïve employment results in excessive data overfetch and capacity waste that can offsets any benefits of DRAM caches.

- If the cache is organized as page-based, page footprints i.e., the set of blocks that are touched while the page is in the cache are highly predictable using well-established code-correlation techniques [62]. Predicting page footprints can eliminate most of the bandwidth overhead and capacity waste that page-based caches suffer from.

- Fetching whole page footprints at once and writing them back together to the main memory greatly improves the energy efficiency in off-chip DRAM by reducing the number of DRAM row activations by an order of magnitude as compared to fetching the same set of blocks separately.

- Unlike block-based caches, page-based caches need a modest amount of associativity

to avoid frequent conflicts. Associativity can be efficiently implemented, even in caches

with DRAM-based tags through way prediction, which is highly accurate for and only

for page-based designs. We demonstrate an efficient implementation of arbitrarily high

associativity for page-based designs.

- It is possible to build a scalable, associative, low-latency page-based cache design with DRAM-based tags that achieves high hit rates and high bandwidth efficiency.

- Although associativity is not crucial for the baseline cache performance in block-based DRAM caches, its absence disables many standard cache optimization techniques that block-based caches could otherwise greatly benefit from.

- There is a significant correlation between the code and temporal data reuse. In the absence of associativity, block-based DRAM caches could leverage this correlation and perform PC-based cache bypassing not only to reduce the cache activity but also to increase the hit rate. We demonstrate an efficient implementation of cache bypassing with only 16KB of SRAM storage and without bandwidth, latency or storage costs in the die-stacked DRAM. Page-based caches can leverage the correlation between the code and data reuse to employ dead-page prediction and increase cache efficiency.

This thesis covers the DRAM cache design space in single-socket setups. While our findings are equally applicable to multi-socket setups, providing efficient support for cache coherence between multiple sockets equipped with multi-gigabyte DRAM caches is out of the scope of this thesis and is an important research topic for future work.

### Chapter 1. Introduction

While this thesis is focused on die-stacked DRAM, the major conclusions of the thesis are not bound to any specific technology and may apply to other materials, such as PCM, STT-RAM or other MRAM technologies, with different performance, energy and durability implications.

The rest of the thesis is organized as follows. In Chapter 2 we study the behavior of real-world server applications in the context of DRAM caches and provide critial insights that will lead us to effective designs. In Chapter 4.2 we look at highly associative DRAM cache designs that keep the precise presence information about the cache content in SRAM, and propose Footprint Cache, a design that leverages spatial locality in a bandwidth-efficient way. Chapter 4 proposes a Unison Cache, an effective DRAM cache solution that scales to multi-gigabyte capacities thanks to its DRAM-based tags. In Chapter 5 we study various techniques that aim to improve cache efficiency and propose further research directions toward that goal. Chapter 6 presents the relevant related work, and Chapter 7 concludes the thesis.

# 2 DRAM Caches and Server Applications

Die-stacked DRAM has been advocated as a promising technology to break the memory bandwidth wall and improve memory latency and density. It delivers several times more internal bandwidth compared to off-chip memory due to dense on-chip TSV buses, as well as lower access latency due to reduction in physical distances enabled by die stacking. Recent advances in die-stacking technologies have made it possible to tightly integrate a sizeable amount of DRAM in the same chip as the processor. Having die-stacked DRAM on the chip could virtually eliminate the memory bandwidth wall by exposing all of its internal bandwidth at lower access latency. The latency advantage that die-stacked on-chip DRAM provides over conventional off-chip DRAM is particularly important in server applications, which are known for being memory-bound [1, 12].

Technological constraints, however, limit the on-chip stacked DRAM capacity to levels that are orders of magnitude lower than what modern server applications demand. It is impossible to fit all the main memory distributed across multiple multi-chip DRAM modules onto a single processor chip. Such a constraint forces the architects to use the on-chip stacked DRAM as a hardware-managed cache or as a software-managed cache or scratchpad. Managing die-stacked DRAM in software is a preferable option in custom designs where hardware and software evolve together, such as embedded systems. In contrast, deep, diverse and rapidly changing software stacks in server systems rely on general-purpose processors and operating systems, mandating non-intrusive hardware-based solutions.

In this chapter we investigate the use of on-chip die-stacked DRAM as a hardware-managed cache in processor chips for datacenters with the purpose of reducing memory traffic on the processor side and improving memory latency. We demonstrate the potential of die-stacked DRAM caches to reduce memory traffic and improve memory latency in server systems, and

we look at different trade-offs in DRAM cache designs that are specific to server settings.

### 2.1 Background and Motivation

With the slowdown in Dennard Scaling server chips are resorting to larger numbers of lean cores to maintain a practical power envelope. Scale-out server workloads benefit from such many-core processor organizations, which enable high throughput thanks to the abundant parallelism in these workloads. The growth in core count, however, ultimately drives designs into a memory bandwidth wall due to poor pin count scalability. Emerging many-core chips with hundreds of cores are already able to utilize and even exceed their bandwidth budgets [21, 34, 50], hitting the bandwidth wall before the power wall [50].

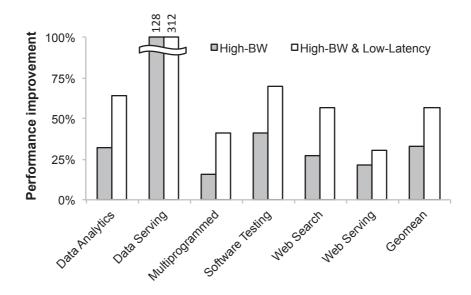

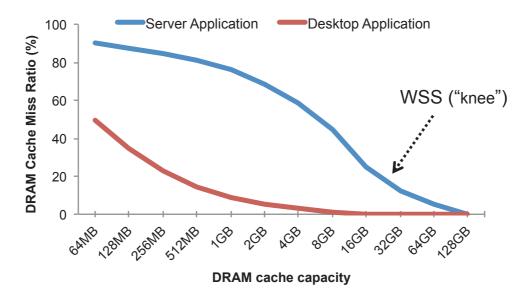

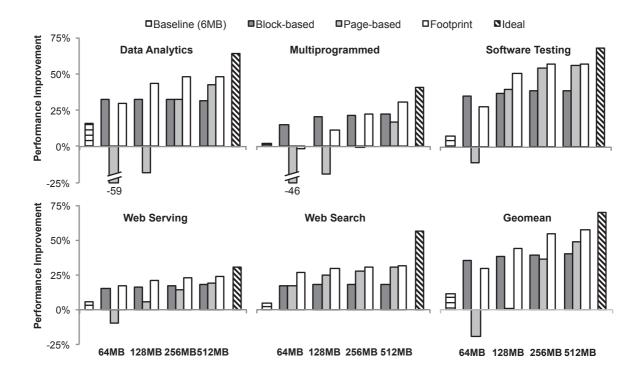

Recent research advocates using die-stacked DRAM to break the memory bandwidth wall and improve memory latency [21, 25, 30, 34, 43, 45, 46, 48]. Figure 2.1 assesses the opportunity of the technology to boost performance of scale-out server and multiprogrammed Desktop workloads from two aspects: bandwidth and latency (details on the experimental methodology are explained in Section 2.2.1). The first set of bars shows performance improvement for a many-core server system [50] with the main memory fully integrated on the chip using die stacking, providing 8x the bandwidth of the 2D baseline. The second set of bars shows performance improvement of the same high-bandwidth system, but with halved DRAM latency [48]. We see that both bandwidth and latency play a vital role in achieving high performance, which implies that future designs must exploit both opportunities given by the technology.

Technological constraints, however, limit the stacked DRAM capacity to levels that are far lower than what modern server workloads demand [48]. While today's servers need tens to hundreds of gigabytes of DRAM each, the projections for die-stacked DRAM capacity vary between hundreds of megabytes to several gigabytes. Thus, most proposals for die stacking advocate using the stacked DRAM as a cache [30, 46, 48]. Unfortunately, the inherent limitations of DRAM cache designs prevent them from achieving the full potential of the technology, depicted in Figure 2.1. Firstly, DRAM caches, regardless of their organization, require significant tag storage due to their large capacity, whose lookup necessarily adds extra latency to the critical path. Secondly, the limited capacity of the stacked DRAM limits the level of concurrency it can provide, despite the virtually unlimited TSV bandwidth. The stacked DRAM is orders of magnitude smaller than the off-chip DRAM, and, thus, experiences frequent bank conflicts and lower availability. In contrast to off-chip main memory systems

Figure 2.1 – Opportunity for performance improvement with high-bandwidth and low-latency die-stacked DRAM.

with hundreds of gigabytes of DRAM that provide more bandwidth than the memory channels can sustain, the bandwidth to the DRAM cache is restricted by the parallelism in the stacked DRAM itself, and not by the interface. Therefore, stacked DRAM caches fall short of fully leveraging the abundant on-chip bandwidth enabled by dense TSV buses. Cache designs must be aware of this limitation, and optimize for the stacked DRAM locality to allow for higher concurrency and availability.

Despite their capacity, DRAM caches may exhibit high miss ratios, with each miss being satisfied from the off-chip memory at full off-chip latency. This behavior is caused by the low reuse of the data in lower-level caches [20], in contrast to L1 caches, where data are frequently reused and where most of the temporal locality is exploited. This phenomenon is further exacerbated by vast datasets of scale-out workloads [12], which do not form any well-defined working sets within the cache sizes of interest. Besides their latency penalty, misses inherently result in DRAM cache evictions. We find that, for scale-out workloads, these are mostly dirty evictions, because data reside in the cache for long enough to become modified by dirty evictions from the upper-level caches. Dirty evictions consume additional off-chip and on-chip TSV bandwidth, affecting the stacked DRAM availability as well (the data have to be read from the stacked DRAM and written back to the off-chip DRAM). The same holds for cache fills that follow the misses. The bandwidth overhead caused by secondary cache traffic — e.g., evictions, fills, probes — is sometimes referred to as *bandwidth bloat* [8].

### 2.1.1 DRAM Cache Design Objectives

DRAM cache designs fall short of leveraging the benefits that die stacking technology provides. In this section we present a set of objectives and guidelines for designing effective DRAM caches aiming to bridge the gap between die-stacked main memory and die-stacked caches:

- Fast tag lookup. Because tag lookups are on the critical path of all requests coming to the cache, tag lookup latency must be minimized. While this statement holds for all cache designs that serialize tag and data lookups, it gains more importance in the context of DRAM caches, due to their tag array size.

- Small tag storage. The total storage dedicated to tags or other metadata should be minimal, as it does not directly contribute to better system performance, but does incur high storage cost.

- Low off-chip traffic. While cache misses are responsible for most of the off-chip bandwidth overhead, various cache features can adversely impact off-chip bandwidth even further. Examples include the use of large cache blocks that saturate off-chip bandwidth and the use of predictors for miss speculation. Reduction in off-chip traffic is the main driver for 3D-stacked DRAM adoption, and as such should be among the top priority goals.

- The stacked DRAM bandwidth overhead caused by secondary cache traffic i.e., evictions, fills, probes, replacement policy metadata updates —should be minimized.

- High hit ratio is crucial to leveraging both the bandwidth and the latency advantages of the die-stacking technology, demonstrated by Figure reffig:motivation.

- Low hit and miss latency. To achieve the benefits depicted in Figure 2.1, DRAM caches must optimize for both hit and miss latency. Internal details of the cache organization should neither penalize hit latency nor postpone miss serving.

- High DRAM access locality. Accesses to DRAM structures experience unpredictable

latency, highly dependent on the locality of references, availability, address-mapping

schemes, row-buffer management policy, and access scheduling. To minimize the

stacked DRAM and off-chip DRAM access latencies and energy per access, cache designs

must take of all these parameters into account.

- Efficient capacity management. Allocation of space for data that are never used should be avoided. The problem is severe in page-based designs, which suffer from internal

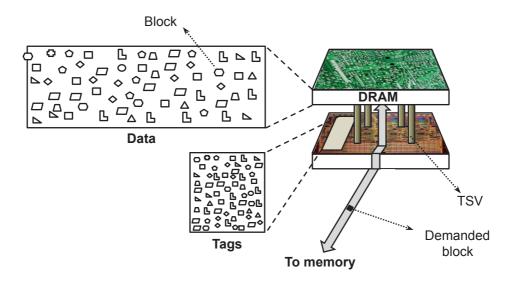

Figure 2.2 – A DRAM die stacked on top of the logic die architected as a block-based cache. One tag entry corresponds to one data block.

fragmentation.

Unfortunately, many of the aforementioned requirements are mutually conflicting, which makes the design process more challenging. To better understand such challenges, we focus on two main DRAM cache design classes that achieve different goals.

## 2.1.2 Block-Based Caches

On-chip caches have traditionally been designed to primarily exploit temporal locality, and to make the best use of their limited capacity. Trade-offs between the effective cache capacity, temporal and spatial locality resulted in 16- to 128-byte cache blocks, 64- byte being the most common block size employed today. Such a design is illustrated in Figure 2.2. For large DRAM caches, 64-byte blocks would require huge tag storage, as illustrated in Figure 2.2, which is infeasible to build in SRAM, thereby forcing the tags to be embedded in DRAM [30, 46, 48]. Embedding tags in DRAM, however, results either in multiple DRAM accesses per cache request — and, consequently, in substantially higher hit and miss latencies [46] — or in the absence of associativity.

Intelligent co-location of data with the corresponding tags in the same DRAM row [46] accompanied with optimized access scheduling, as done in Loh & Hill cache, [48], obviates the need for multiple DRAM accesses per request. However, this optimization only partially reduces

the high hit latency, because of the need for several operations to be performed within the DRAM row-buffer. Furthermore, the co-location of tags and data may in such a way mandates particular data placement policies that diminish DRAM locality. It also requires a way to determine the presence of a block in the cache prior to accessing the tags, as well as additional multi-megabyte storage for that purpose (not shown in Figure 2.2), whose access latency is on the critical path.

A more recent block-based cache design, called Alloy Cache [55], provides an architecture that completely avoids any large SRAM-based tag arrays, and overall provides low latencies on cache hits. Alloy Cache is organized as direct-mapped to avoid searching for the correct way throughout the DRAM-based tags and co-locates each data block with its tags, reading it together with the data block in a single access. However, these advantages come at the cost of relatively low cache hit rates, which are further penalized by the cache's direct-mapped organization, and high miss penalty. To avoid DRAM cache lookups on cache misses, Alloy Cache employs a miss predictor, sending cache requests to main memory speculatively, if a miss is predicted. However, because the miss predictor is imperfect, it can be relied upon for coherence or aggressive prefetching.

Regardless of their tag architecture, block-based designs fall short of exploiting abundant spatial locality. Instead, they focus on limited temporal locality, experiencing high miss ratios, thus frequently exposing full off-chip latency to incoming requests. However, due to the small fetch unit and the efficient management of cache capacity, block-based designs minimize off-chip traffic, making them a favorable option for high-throughput servers.

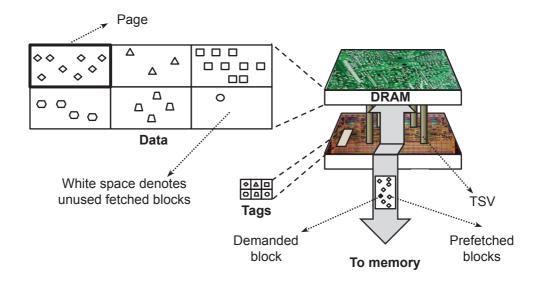

## 2.1.3 Page-Based Caches

Increasing the block size allows for a proportionate reduction in tag storage. The use of larger allocation/fetch units (e.g., 1-8KB) makes the placement of tags in SRAM feasible at an acceptable storage overhead [18, 29, 30]. We call such units *pages* and the corresponding designs *page-based* designs.

The large fetch unit allows for maximum DRAM access efficiency, fully exploiting locality in both off-chip and stacked DRAM. For instance, a single DRAM row opening is needed per off-chip DRAM fetch, eviction, or stacked DRAM fill, for a whole page, assuming that the page size does not exceed the DRAM row size. While large DRAM caches exhibit limited temporal locality, they show significant spatial locality, which can be easily leveraged by large fetch units, as illustrated in Figure 2.3, providing an order of magnitude more hits compared to a block-based

Figure 2.3 – A DRAM die stacked on top of the logic die architected as a page-based cache. Only the useful blocks (accessed by the cores) are shown in the figure. One tag entry corresponds to one page.

|                               | Block-based – Loh & Hill | Block-based – Alloy | Page-based |

|-------------------------------|--------------------------|---------------------|------------|

| Small and fast tag storage    | Х                        | ×                   | ✓          |

| Low off-chip traffic          | ✓                        | ✓                   | X          |

| High hit rate                 | Х                        | ×                   | ✓          |

| Low hit latency               | Х                        | ✓                   | ✓          |

| Associativity                 | ✓                        | ×                   | ✓          |

| High DRAM locality            | Х                        | ✓                   | ✓          |

| Efficient capacity management | ✓                        | ✓                   | X          |

Table 2.1 – Comparison of block-based and page-based designs.

cache of the same size [25, 30]. Cache hits are critical to exploiting the latency advantages of die-stacked DRAM and page-based caches provide them at lower latency. Unfortunately, many of the cached pages contain data that are not used prior to the page eviction, resulting in excessive data overfetch [30] and capacity waste. As a result, page-based caches tend to increase the off-chip traffic of the baseline system without a DRAM cache by up to an order of magnitude in the worst case, which negates a key benefit of die-stacked DRAM caches.

## **2.1.4 Summary**

Table 4.1 provides a comparison between the two designs with respect to the most important features. The block-based and page-based designs show complementary, yet mutually exclusive, characteristics.

## 2.2 Spatial and Temporal Characterization

In this section we characterize server applications by studying their behavior in large-scale DRAM caches

## 2.2.1 Methodology

To study the behavior of DRAM caches in server settings we use CloudSuite workloads [9], including Data Analytics, Data Serving, Software Testing, Web Search, and Web Serving. For comparison, we also include a mix of SPEC2006 Integer benchmarks as a representative of desktop applications. Because the datasets of CloudSuite benchmarks are slightly scaled down to allow for practical full-system simulation, we also include one unscaled server application, which is a modern column-oriented database, MonetDB, running a set of TPC-H queries on a server with 128GB of main memory. We evaluate the applications while running on one pod of a scale-out server chip [50]. The simulation parameters are given in Table 2.2.

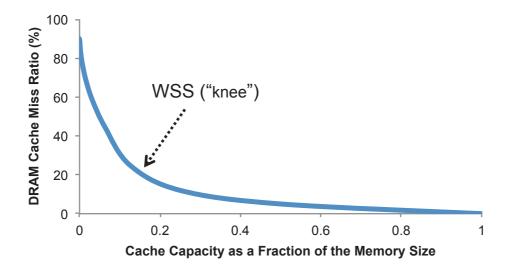

### 2.2.2 Temporal Behavior

To study the temporal behavior of DRAM caches, we look at the miss ratio of block-based designs that use no prefetching. Because block-based designs do not leverage spatial locality, any observed cache hits come solely from temporal data reuse. Figure 2.4 shows the miss ratio of a block-based design for TPC-H queries running on a 16-core machine with 128GB of memory. The cache capacity varied on the *x*-axis is shown as a ratio between the cache capacity and the main memory size. We see that the working set size (WSS), which is between 10% and 15% of the dataset, is well beyond the reach of practical DRAM caches, which could accommodate up to a few gigabytes in the best case. As a result, the temporal reuse seen in DRAM caches is limited. Note that in server applications the temporal reuse observed in L1 caches typically comes from reuse within a single server request. This kind of reuse is typically fully filtered by SRAM caches and is not visible at the DRAM cache level. In contrast, the reuse in DRAM caches is likely to happen accross different server requests and is a result of

| Technology                                                               | 20nm, 0.85V, 3GHz                       |

|--------------------------------------------------------------------------|-----------------------------------------|

| CMP Organization                                                         | 16-core Scale-Out Processor pod         |

| Core                                                                     | ARM Cortex-A15-like, 3-way OoO @3GHz    |

| L1-I/D caches                                                            | 64KB, split, 64B blocks                 |

|                                                                          | 2-cycle load-to-use latency             |

| L2 cache per pod                                                         | 4MB, unified, 16-way, 64B blocks,       |

|                                                                          | 4 banks, 13-cycle hit latency           |