# A mixed-signal computer architecture and its application to power system problems

THÈSE Nº 6613 (2015)

PRÉSENTÉE LE 4 SEPTEMBRE 2015 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR GROUPE KAYAL PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

#### Theodoros KYRIAKIDIS

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Prof. M. Kayal, Dr S.-R. Cherkaoui, directeurs de thèse Prof. T. Van Cutsem, rapporteur Prof. A. Hatzopoulos, rapporteur Prof. M. Paolone, rapporteur

Ἐν ἀρχῆ ῆν ὁ Λόγος. — Ἰω. ἀ 1

To my family.

## Acknowledgements

First of all I would like to thank my supervisors Maher Kayal and Rachid Cherkaoui. They gave me the opportunity to conduct my research "the old way", in the sense of providing me with suggestions and tips along the way rather constraining me to a fixed target. It is this kind of freedom that allows the investigation of "crazy ideas" and it is due to them that this work has been enabled.

I would like to equally thank the professor Thierry Van Cutsem of the University of Liège and his group for their exemplary hospitality during my spell with them in Liège. Particular mention goes to dear friend and colleague Petros Aristidou for all our fruitful discussions and his invaluable help.

A big part of what you read in this manuscript is done in collaboration with colleagues of my lab and elsewhere. Sometimes collaboration was so tight that is is really difficult to say who has really contributed what. I would like to specially mention Guillaume Lanz, Denis Sallin and Georgios Lilis. Each one with his deep dedication to his field, and each one always willing to share and help.

Apart from the above, there is a number of people that have contributed their bit in the scientific part of this work. It being a discussion over a coffee, a review of a paper, a coding idea, or some useful small-talk over a pint of beer, to you all people, I am grateful.

I would also like to thank all the people who have made my days here in Switzerland happy and cheerful: my office-, flat-, and team-mates, and all my amazing Greek and Swiss friends.

I would finally like to thank my family, for their constant support and for the happiness they bring to my life.

Lausanne, 04 Juin 2015

Θ. Κ.

### Abstract

Radical changes are taking place in the landscape of modern power systems. This massive shift in the way the system is designed and operated has been termed the advent of the "smart grid". One of its implications is a strong market pull for faster power system analysis computing. This work concerns in particular transient simulation, which is one of the most demanding power system analyses. This refers to the imitation of the operation of the real-world system over time, for time scales that cover the majority of slow electromechanical transient phenomena. The general mathematical formulation of the simulation problem includes a set of non-linear differential algebraic equations (DAEs).

In the algebraic part of this set, heavy linear algebra computations are included, which are related to the admittance matrix of the topology. These computations are a critical factor to the overall performance of a transient simulator.

This work proposes the use of analog electronic computing as a means of exceeding the performance barriers of conventional digital computers for the linear algebra operations. Analog computing is integrated in the frame of a power system transient simulator yielding significant computational performance benefits to the latter. Two hybrid, analog and digital computers are presented.

The first prototype has been implemented using reconfigurable hardware. In its core, analog computing is used for linear algebra operations, while pipelined digital resources on a field programmable gate array (FPGA) handle all remaining computations. The properties of the analog hardware are thoroughly examined, with special attention to accuracy and timing. The application of the platform to the transient analysis of power system dynamics showed a speedup of two orders of magnitude against conventional software solutions.

The second prototype is proposed as a future conceptual architecture that would overcome the limitations of the already implemented hardware, while retaining its virtues. The design space of this future architecture has been thoroughly explored, with the help of a software emulator. For one possible suggested implementation, speedups of two orders of magnitude against software solvers have been observed for the linear algebra operations.

Key words: [**Computing**]: analog computing, pipeline processing, field programmable gate arrays, reconfigurable computing, computer accelerator architectures, high performance computing; [**Power systems**]: power system simulations, power system analysis computing, power system dynamics; [**Mathematics**]: linear algebra - *linear systems*, numerical analysis - *numerical simulation, numerical linear algebra*;

### Résumé

Des changements radicaux prennent place dans les systèmes électriques modernes. Ces changements massifs dans la façon dont le système est conçu et exploité correspondent à l'avènement du "smart grid". L'une des conséquences est le besoin d'outils d'analyse du système plus rapides.

Ce travail concerne en particulier une analyse très exigeante, la simulation transitoire. Ceci se rapporte à l'imitation de l'opération du système réel, pour des échelles de temps qui couvrent la majorité des phénomènes transitoires électromécaniques lents. La formulation mathématique générale du problème comprend un ensemble d'équations algébriques différentielles non-linéaires (DAE).

Dans la partie algébrique de cet ensemble, de lourds calculs d'algèbre linéaire prennent place, qui sont liés à la matrice d'admittance de la topologie. Ces calculs sont un facteur critique de la performance globale d'un simulateur transitoire.

Ce travail propose l'utilisation des calculs analogiques comme un moyen de dépasser les barrières de performance des ordinateurs numériques classiques pour les opérations d'algèbre linéaire. Le calcul analogique est intégré dans le cadre d'un simulateur transitoire et apporte d'importants avantages en termes de performances. Deux ordinateurs hybrides, analogique et numérique, sont présentés.

Le premier prototype a été mis en œuvre en utilisant ressources reconfigurables. Dans son cœur, le calcul analogique est utilisé pour des opérations d'algèbre linéaire, tandis que les ressources numériques sur un Field Programmable Gate Array (FPGA) gèrent tous les calculs restants. Les propriétés du matériel analogique sont examinées. Une attention particulière est portée à la précision et au timing. L'application de la plate-forme à l'analyse transitoire de la dynamique du réseau électrique a montré une accélération de deux ordres de grandeur par rapport à des solutions logicielles classiques.

Le deuxième prototype est proposé comme une future architecture conceptuelle qui permettrait de surmonter les limitations du matériel déjà mis en œuvre, tout en conservant ses vertus. L'espace de conception de cette future architecture a été explorée à fond, avec l'aide d'un émulateur en logiciel. Pour une mise en œuvre suggérée, accélérations de deux ordres de grandeur contre logiciels classiques ont été observées pour les opérations d'algèbre linéaire.

Mots clefs : [**Informatique**] : calcul analogique, traitement en pipeline, circuit logique programmable, computing reconfigurable, architectures d'ordinateur de l'accélérateur, calcul haute performance ; [**Réseau électrique**] : simulations du réseau électrique, informatique

#### Acknowledgements

de l'analyse du réseau électrique, dynamique du réseau électrique; [**Mathématiques**] : algèbre linéaire - *systèmes linéaires*, analyse numérique - *simulation numérique, algèbre linéaire numérique*;

## Περίληψη

Ριζικές αλλαγές λαμβάνουν χώρα στον τομέα των σύγχρονων συστημάτων ηλεκτρικής ενέργειας (ΣΗΕ). Αυτή η μετάβαση στον τρόπο με τον οποίο το σύστημα σχεδιάζεται και λειτουργείται αποκαλείται η έλευση του 'έξυπνου δικτύου'. Ένα από τα επακόλουθα της είναι η ανάγκη για ταχύτερους υπολογιστές ανάλυσης ΣΗΕ.

Αυτή η εργασία επικεντρώνεται σε μια ιδιαίτερη απαιτητική ανάλυση, την προσομοίωση ΣΗΕ. Αυτό αναφέρεται στην πιστή αναπαράσταση της λειτουργίας του συστήματος για σταθερές χρόνου που καλύπτουν την πλειονότητα των ηλεκτρομηχανικών μεταβατικών φαινομένων στο σύστημα. Η γενική μαθηματική διατύπωση του προβλήματος της προσομοίωσης περιλαμβάνει ένα σύνολο μη γραμμικών διαφορικών-αλγεβρικών εξισώσεων (ΔΑΕ).

Στο αλγεβρικό μέρος αυτού του συνόλου περιλαμβάνονται πολλοί και απαιτητικοί υπολογισμοί γραμμικής άλγεβρα. Αυτοί σχετίζονται με τον πίνακα αγωγιμοτήτων της τοπολογίας και είναι κρίσιμοι για την συνολική απόδοση ενός προσομοιωτή μεταβατικών φαινομένων ΣΗΕ.

Σε αυτή την εργασία προτείνεται η χρήση αναλογικών αρχιτεκτονικών ως μέσο υπέρβασης των περιορισμών των συμβατικών ψηφιακών υπολογιστών όσον αφορά ιδιαίτερα τους υπολογισμούς γραμμικής άλγεβρας. Οι αναλογικοί υπολογισμοί ενσωματώνονται στην ροή του προσομοιωτή μεταβατικών φαινομένων αποφέροντας σημαντικά ωφέλη στην απόδοση του. Δύο υβριδικοί υπολογιστές παρουσιάζονται.

Ο πρώτος αφορά ένα πρωτότυπο το οποίο έχει κατασκευαστεί σε επαναδιαμορφώσιμο υλικό. Στον πυρήνα του αναλογικοί υπολογισμοί χρησιμοποιούνται για την γραμμική άλγεβρα, ενώ σωληνομένοι επεξεργαστές έχουν προγραμματιστεί σε μια συστοιχία επιτόπια προγραμματιζομένων πυλών (ΦΠΓΑ) για τους υπόλοιπους υπολογισμούς. Οι ιδιότητες του αναλογικού τμήματος εξετάζονται διεξοδικά, με ιδιαίτερη έμφαση στην ακρίβεια και τον χρονισμό. Η εφαρμογή της πλατφορμας στην προσομοίωση ΣΗΕ έδειξε μια επιτάχυνση δύο τάξεων μεγέθους σε σχέση με συμβατικό ψηφιακό λογισμικό.

Ένα δεύτερο πρωτότυπο προτείνεται ως μελλοντική αρχιτεκτονική η οποία θα μπορέσει να διατηρήσει τις αρετές του υπάρχοντος πρωτοτύπου, αλλά και ταυτόχρονα να ξεπεράσει τους περιορισμούς του. Ένας εξομοιωτής υλοποιήθηκε σε λογισμικό με σκοπό την ανάλυση και την βελτιστοποίηση του σχεδιασμού. Για την τελικά προτεινόμενη διαμόρφωση, επιτάχυνση δύο τάξεων μεγέθους επιτεύχθηκε για τους υπολογισμούς γραμμικής άλγεβρας σε σχέση με συμβατικό ψηφιακό λογισμικό.

Λέξεις κλειδιά: Πληροφορική: αναλογική πληροφορική, σωληνωμένη επεξεργασία, συστοιχία

#### Acknowledgements

επιτόπια προγραμματιζόμενων πυλών, επαναδιαμορφώσιμοι υπολογιστές, αρχιτεκτονικές επιταχυντών υλικού υπολογιστές υψηλών επιδόσεων<sup>.</sup> Συστήματα ηλεκτρικής ενέργειας (ΣΗΕ): προσομοίωση ΣΗΕ, υπολογιστές ανάλυσης ΣΗΕ, δυναμική ΣΗΕ<sup>.</sup> Μαθηματικά: γραμμική άλγεβρα - γραμμικά συστήματα, αριθμητική ανάλυση - αριθμητική ολοκλήρωση, αριθμητική γραμμική άλγεβρα<sup>.</sup>

# Contents

| Ac | knov   | vledgements                                                  | i    |

|----|--------|--------------------------------------------------------------|------|

| Ał | ostra  | ct (en/fr/el)                                                | iii  |

| Li | st of: | figures                                                      | xiii |

| Li | st of  | tables                                                       | xvii |

| In | trod   | uction                                                       | 1    |

| 1  | Мос    | lern power system landscape                                  | 5    |

|    | 1.1    | Current architecture                                         | 6    |

|    |        | 1.1.1 The need for change                                    | 13   |

|    | 1.2    | Future architecture: the Smart Grid                          | 14   |

|    |        | 1.2.1 Distributed energy resources                           | 16   |

|    |        | 1.2.2 Aggregations                                           | 17   |

|    | 1.3    | The effect of the smart grid on analysis tools               | 18   |

| 2  | Pow    | er system simulation, linear algebra and computing platforms | 21   |

|    | 2.1    | Simulation                                                   | 22   |

|    |        | 2.1.1 Mathematical formulation of simulation problems        | 23   |

|    | 2.2    | Linear algebra in power systems                              | 24   |

|    |        | 2.2.1 Algorithms and implementations                         | 24   |

|    |        | 2.2.2 Coherence between the algorithm and the platform       | 26   |

|    | 2.3    | Dedicated platforms                                          | 28   |

|    |        | 2.3.1 SIMD                                                   | 28   |

|    |        | 2.3.2 Multi-core                                             | 28   |

|    |        | 2.3.3 Heterogeneous computing                                | 30   |

|    |        | 2.3.4 GPU                                                    | 30   |

|    |        | 2.3.5 FPGA                                                   | 31   |

|    |        | 2.3.6 DSP                                                    | 32   |

|    |        | 2.3.7 ASIC and VLSI                                          | 32   |

|    |        | 2.3.8 Conventional computing and its limitations             | 33   |

|    |        | 2.3.9 Unconventional computing                               | 33   |

|    | 2.4    | Analog electronic computers                                  | 34   |

#### Contents

|   |          | 2.4.1          | In linear algebra                    | 35           |

|---|----------|----------------|--------------------------------------|--------------|

|   |          | 2.4.2          | In power systems computing           | 36           |

|   |          | 2.4.3          | Evaluation criteria                  | 37           |

|   | 2.5      | Outlo          | ok                                   | 38           |

| • | <b>D</b> |                |                                      |              |

| 3 |          |                | edicated mixed signal solver         | 41           |

|   | 3.1      |                | vare                                 | 42           |

|   |          | 3.1.1          | 01                                   | 45           |

|   |          | 3.1.2          | Digital part                         | 55           |

|   | 0.0      | 3.1.3          | Timing                               | 61           |

|   | 3.2      |                | are                                  | 62           |

|   |          | 3.2.1          | Backend                              | 62           |

|   |          | 3.2.2          | Frontend                             | 65           |

|   | 3.3      |                | uracy                                | 66           |

|   |          | 3.3.1          | Analog inaccuracy                    | 66           |

|   |          | 3.3.2          | Digital inaccuracy                   | 80           |

|   |          | 3.3.3          | Effect on the mathematical operation | 82           |

|   |          | 3.3.4          | Calibration                          | 84           |

|   | 3.4      |                | ts                                   | 86           |

|   |          | 3.4.1          | Linear system solving                | 86           |

|   |          | 3.4.2          | Sample radial and meshed topologies  | 91           |

|   |          | 3.4.3          | Transient simulation                 | 95           |

|   |          | 3.4.4          |                                      | 101          |

|   |          | 3.4.5          | 0 0                                  | 103          |

|   |          | 3.4.6          | 1 0                                  | 107          |

|   | 3.5      | Concl          |                                      | 108          |

|   |          | 3.5.1          | 1                                    | 108          |

|   |          | 3.5.2          | Limitations                          | 111          |

| 4 | Con      | cent fi        | iture solver                         | 113          |

| - |          | -              |                                      | 115          |

|   | 4.2      |                | n methodology                        |              |

|   | 1.2      | 4.2.1          |                                      | 120          |

|   |          | 4.2.2          |                                      | 120          |

|   |          |                | -                                    | 124          |

|   | 4.3      |                |                                      | 123          |

|   | 1.5      | 4.3.1          |                                      | 131          |

|   |          | 4.3.2          |                                      | 131          |

|   |          | 4.3.3          |                                      | 132          |

|   |          | 4.3.3<br>4.3.4 |                                      | $135 \\ 135$ |

|   |          | 4.3.4<br>4.3.5 |                                      | $135 \\ 136$ |

|   |          | 4.3.5<br>4.3.6 |                                      | $130 \\ 138$ |

|   |          |                |                                      |              |

|   |          | 4.3.7          | Timing                               | 139          |

#### Contents

|    | 4.4                | Numerical results                          | 140 |  |

|----|--------------------|--------------------------------------------|-----|--|

|    |                    | 4.4.1 Selection of mapping ratios          | 140 |  |

|    |                    | 4.4.2 Linear system solving                | 141 |  |

|    |                    | 4.4.3 Integration into the RAMSES flow     | 151 |  |

|    | 4.5                | Conclusions                                | 160 |  |

| 5  | Con                | clusions                                   | 161 |  |

|    | 5.1                | Future work                                | 162 |  |

|    |                    | 5.1.1 On the existing solver               | 162 |  |

|    |                    | 5.1.2 On the conceptual future solver      | 163 |  |

|    | 5.2                | Final discussion                           | 165 |  |

| A  | Test               | power system topologies                    | 167 |  |

| B  | Con                | nmon modeling assumptions in power systems | 171 |  |

|    | B.1                | Phasor representation                      | 171 |  |

|    | B.2                | Balance in electrical quantities           | 174 |  |

|    | B.3                | Symmetry in the network                    | 177 |  |

|    | B.4                | Power considerations                       | 179 |  |

|    | B.5                | Per-unit representation                    | 182 |  |

| С  | Nun                | nerical integration                        | 189 |  |

|    | C.1                | Explicit and implicit methods              | 189 |  |

|    | C.2                | Numerical properties of methods            | 190 |  |

|    |                    | C.2.1 Convergence                          | 191 |  |

|    |                    | C.2.2 Order                                | 191 |  |

|    |                    | C.2.3 Stability                            | 191 |  |

|    | C.3                | Truncation error                           | 192 |  |

| Bi | Bibliography       |                                            |     |  |

| Cu | Curriculum Vitae 2 |                                            |     |  |

# List of Figures

| 1.1  | A schematic of the traditional structure of a power system [1]                                | 6  |

|------|-----------------------------------------------------------------------------------------------|----|

| 1.2  | The power system as a black box                                                               | 8  |

| 1.3  | The operation cycle of a stakeholder                                                          | 8  |

| 1.4  | The effect of a faster operation cycle for a stakeholder                                      | 9  |

| 1.5  | Building blocks of an Energy Management System (EMS) of a utility operator .                  | 9  |

| 1.6  | The concept of DER aggregation                                                                | 18 |

| 2.1  | Power system dynamic simulation domains for different time scales - adapted                   |    |

|      | from [2, 3]                                                                                   | 22 |

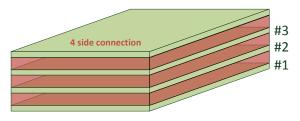

| 3.1  | Overview of the multi-platform system                                                         | 42 |

| 3.2  | Levels of the multi-platform system                                                           | 42 |

| 3.3  | Photo of the multi-platform system                                                            | 43 |

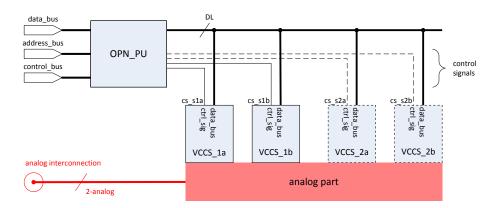

| 3.4  | Overview of the existing mixed-signal computer [4].                                           | 44 |

| 3.5  | Partitioned solution scheme for power system simulation equations                             | 44 |

| 3.6  | Generalized $\pi$ model of a generic power system branch $\ldots \ldots \ldots \ldots \ldots$ | 46 |

| 3.7  | The complex two-port network for a branch connecting buses $f$ and $t$ and the                |    |

|      | effect it has on the building of the <i>Y</i> matrix                                          | 48 |

| 3.8  | The complex one-port network for a shunt element on bus <i>s</i> and the effect it has        |    |

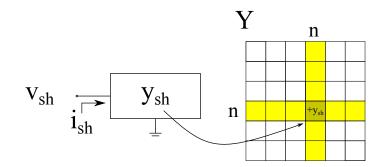

|      | on the building of the <i>Y</i> matrix                                                        | 49 |

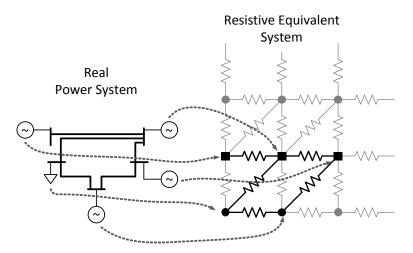

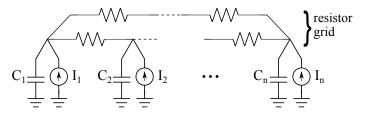

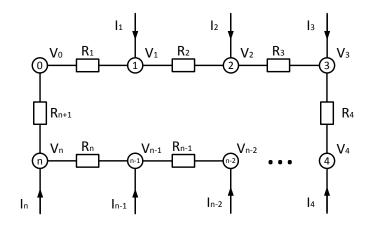

| 3.9  | Power system topological mapping into an electronic resistor network equivalent.              | 50 |

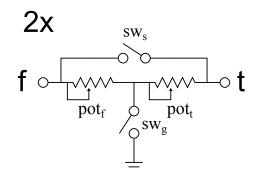

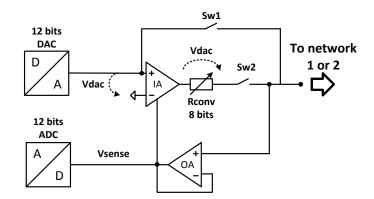

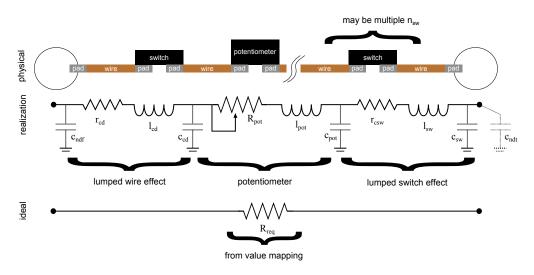

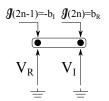

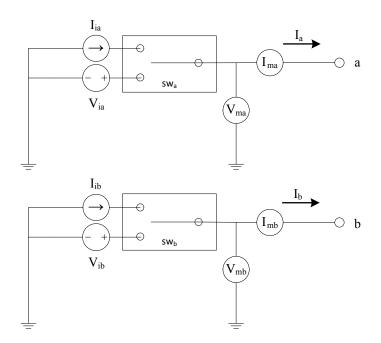

| 3.10 | Schematic of an electrical branch of the existing FPPNS                                       | 51 |

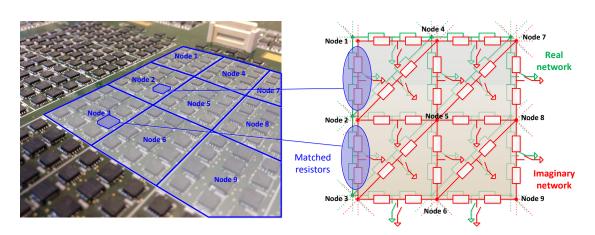

|      | Detail of the implementation of a slice of the FPPNS using discrete electronics               | 52 |

| 3.12 | A stack of four FPPNS slices                                                                  | 52 |

|      | Synoptical schematic of a node of the FPPNS                                                   | 53 |

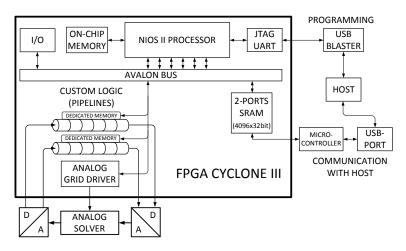

| 3.14 | Configuration of the digital part of the existing computer prototype (Altera                  |    |

|      | Cyclone III FPGA).                                                                            | 56 |

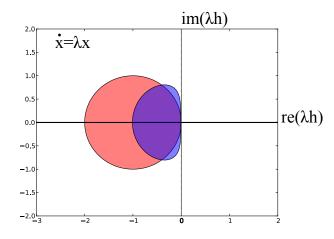

| 3.15 | Stability region of the Forward Euler method and the 2-step Adams-Bashforth                   |    |

|      | method                                                                                        | 57 |

| 3.16 | Pipelined versions of the FE and the AB2 algorithms                                           | 58 |

| 3.17 | Datapath of the synthesized pipeline for generators that are modeled with the                 |    |

|      | classical generator model of (3.30) using the FE integration scheme of (3.28) $$ .            | 60 |

| 3.18 | The USB controller and the shared RAM that is interfaced to the FPGA                          | 60 |

|      |                                                                                               |    |

#### List of Figures

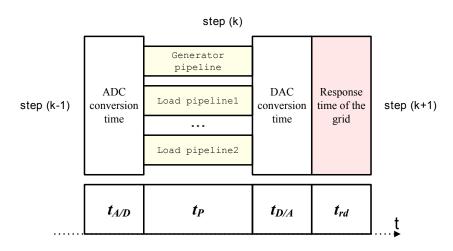

| 3.19 Schematic diagram of the timing break up of the operations of the FPPNS for       |     |

|----------------------------------------------------------------------------------------|-----|

| one simulation step                                                                    | 61  |

| 3.20 Diagram of the timing break up of a computing pipeline                            | 62  |

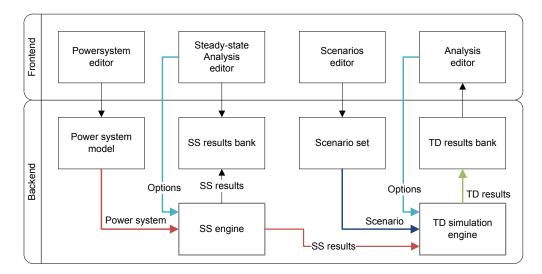

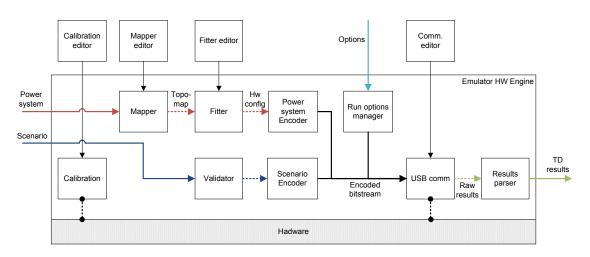

| 3.21 Architecture overview of elab-tsaot                                               | 63  |

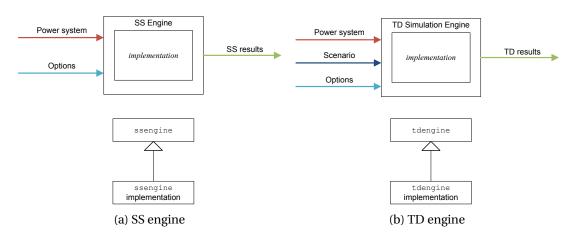

| 3.22 Interface design pattern for the SS and TD engines                                | 63  |

| 3.23 Hardware Abstraction Layer (HAL) of the dedicated hardware                        | 64  |

| 3.24 The model-view-controller (MVC) software architectural pattern used to imple-     |     |

| ment the frontend of elab-tsaot                                                        | 66  |

| 3.25 Physical and schematic representation of parasitics for an electrical branch that |     |

| contains a potentiometer                                                               | 70  |

| 3.26 Schematic representation of the resulting electrical circuit taking into account  |     |

| the node parasitic capacitances                                                        | 77  |

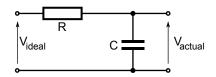

| 3.27 An RC circuit in which R and C are in series.                                     | 79  |

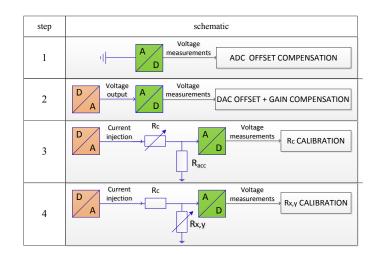

| 3.28 Calibration procedure                                                             | 84  |

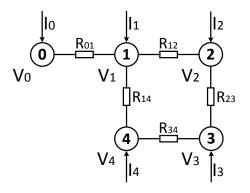

| 3.29 Sample topology with 5 electrical branches and 5 electrical nodes                 | 86  |

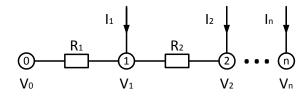

| 3.30 Sample radial topology                                                            | 91  |

| 3.31 Sample meshed topology                                                            | 93  |

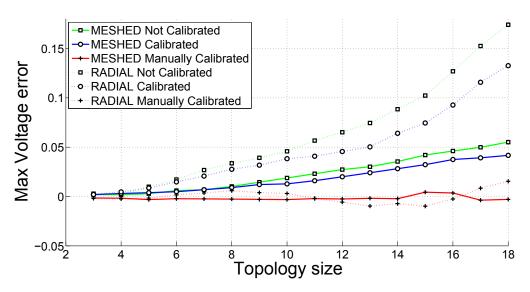

| 3.32 Maximum absolute voltage error for radial and meshed topologies of increasing     |     |

| size                                                                                   | 94  |

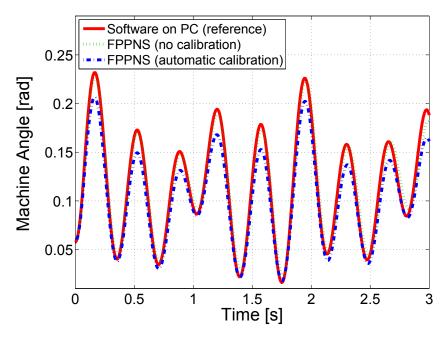

| 3.33 Rotor angle oscillations of generator #3 of the 18-bus topology using different   |     |

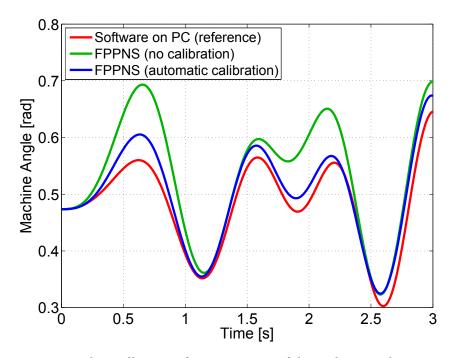

| simulators                                                                             | 96  |

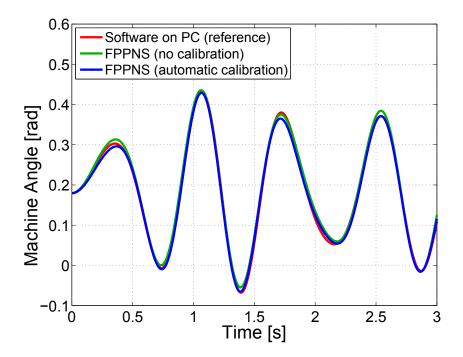

| 3.34 Rotor angle oscillations of generator #11 of the 59-bus topology using different  |     |

| simulators                                                                             | 97  |

| 3.35 Rotor angle oscillations of generator #54 of the 59-bus topology using different  |     |

| simulators                                                                             | 97  |

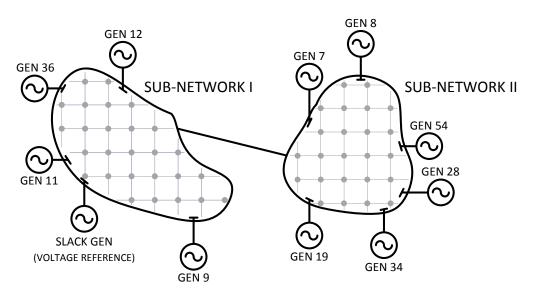

| 3.36 Reduced schematic of the 59-bus test case                                         | 98  |

| 3.37 Timing breakup of computation time for transient simulation of the 18-bus $$      | 100 |

| 3.38 Screenshot of the Analysis editor of the elab-tsaot visualizing results for a     |     |

| n-1 branch contingency analysis on an 18-bus system                                    | 102 |

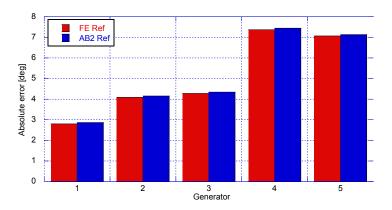

| 3.39 Minimal time-step FPPNS error compared to PC software simulation reference        |     |

| for the 18-bus test system                                                             | 103 |

| 3.40 FPPNS error due to digital imprecision for different time steps for the 18-bus    |     |

| test system                                                                            | 104 |

| 3.41 FE instability while AB2 succeeds in retaining the stability of the numerical     |     |

| solution                                                                               | 104 |

| 3.42 CCT for branches #4, #10, #30 of the 18-bus system with varying timesteps using   |     |

| FE & AB2                                                                               | 106 |

| 3.43 CCT for branch #30 of the 18-bus system with varying timesteps using FE & AB2,    |     |

| in a calibrated and an non-calibrated FPPNS environment                                | 106 |

| 3.44 Internal angle of generator #4 after a transient event in the 18-bus case, for    |     |

| different ADC waiting times.                                                           | 107 |

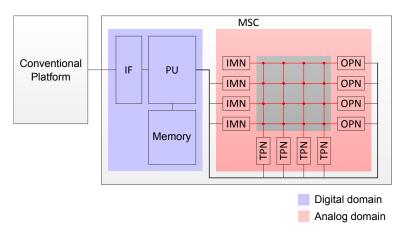

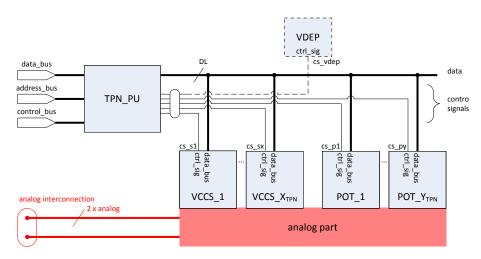

| 4.1  | A schematic overview of the proposed mixed-signal computer (MSC) $\ldots \ldots$                     | 114 |

|------|------------------------------------------------------------------------------------------------------|-----|

| 4.2  | The flow of the RAMSES transient simulator with the linear algebra operation                         |     |

|      | identified in red                                                                                    | 118 |

| 4.3  | The two-port, four-pole network (2 poles per port) defined for a branch by (4.8)                     |     |

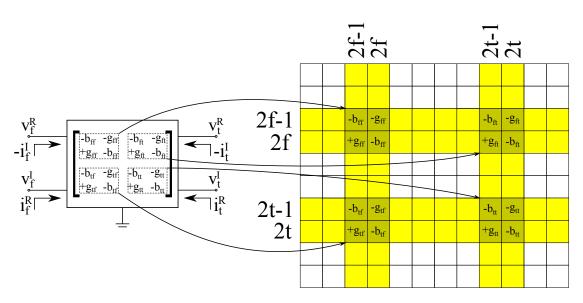

|      | and the effect it has on the building of the $\mathscr{Y}$                                           | 120 |

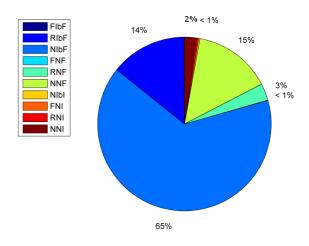

| 4.4  | Empirical pie chart of occurances of branch types for several typical power                          |     |

|      | systems with sizes ranging between 3-15k buses                                                       | 121 |

| 4.5  | The one-port, two-pole network (2 poles per port) defined for a shunt element                        |     |

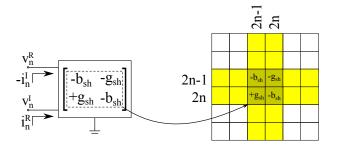

|      | by (4.9) and the effect it has on the building of the $\mathscr{Y}$                                  | 122 |

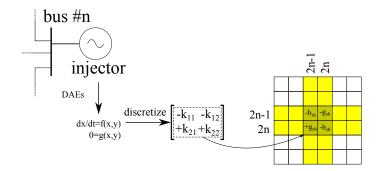

| 4.6  | The 2 × 2 diagonal correction that arises from the dynamic behavior of an injector                   |     |

|      | and the effect it has in the augmenting of $\mathscr{Y}$ to $\tilde{\mathscr{Y}}$                    | 123 |

| 4.7  | An equivalent of a power system bus that follows the real decomposition, the                         |     |

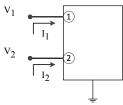

|      | ordering and the sign convention for the MSC                                                         | 123 |

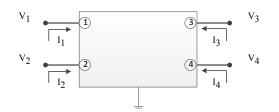

| 4.8  | An outline of an electrical two-port network used to map a power system branch                       | 124 |

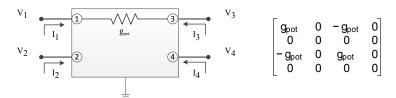

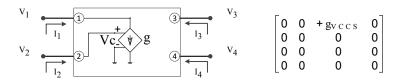

| 4.9  | Examples of the effect of the TPN building blocks (potentiometers and VCCS) to                       |     |

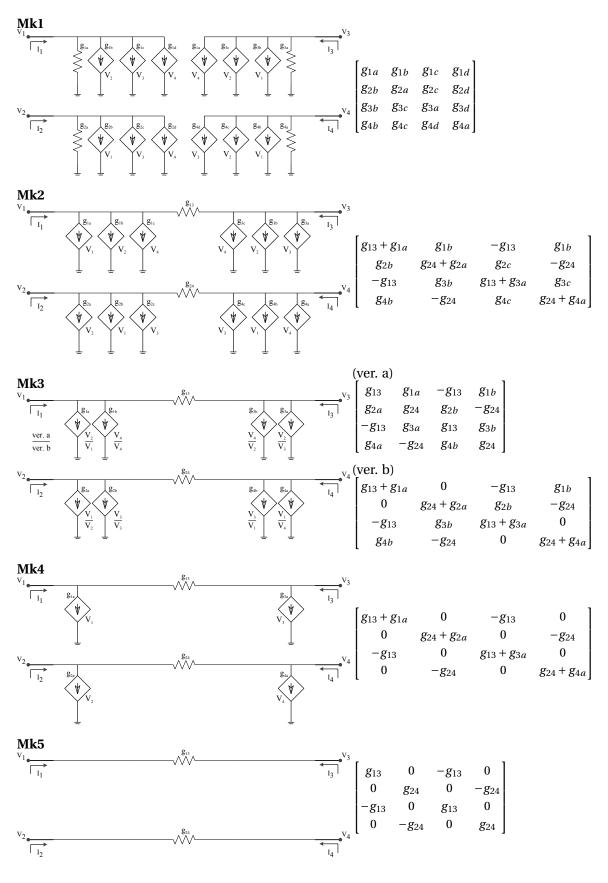

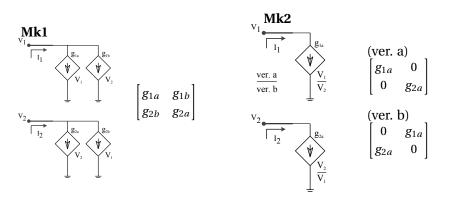

|      | the g-parameters matrix of the TPN                                                                   | 125 |

| 4.10 | Schematic of the digital part of a TPN                                                               | 127 |

| 4.11 | An outline of an electrical one-port network used to map a power system shunt                        |     |

|      | element or a diagonal correction                                                                     | 128 |

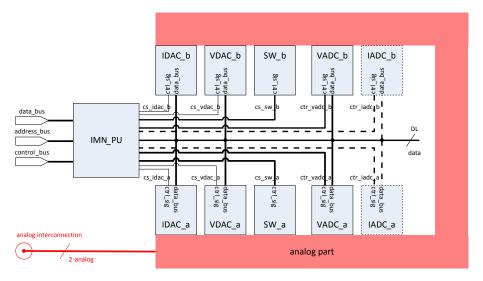

| 4.12 | Schematic of the digital part of an OPN                                                              | 129 |

| 4.13 | Synoptical diagram of an injection and measurement node of the MSC                                   | 130 |

| 4.14 | Schematic of the digital part of an IMN                                                              | 130 |

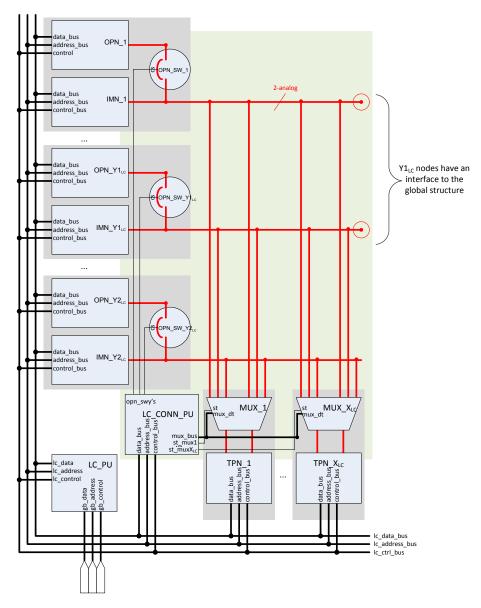

| 4.15 | Schematic of a local cell (LC) of the MSC                                                            | 133 |

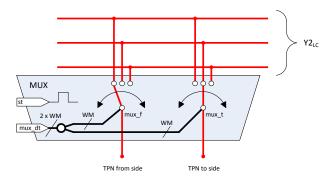

| 4.16 | Connectivity detail and simplified schematic of a TPN connection multiplexer                         |     |

|      | (MUX)                                                                                                | 133 |

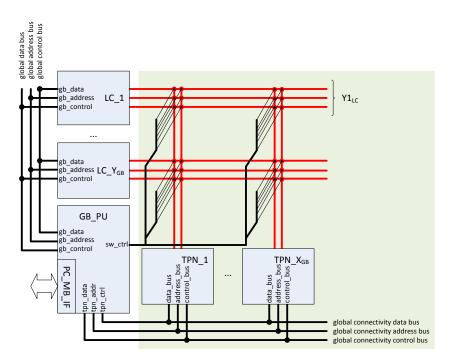

| 4.17 | Global view of the digital architecture of the MSC                                                   | 134 |

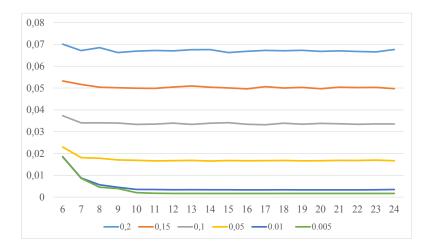

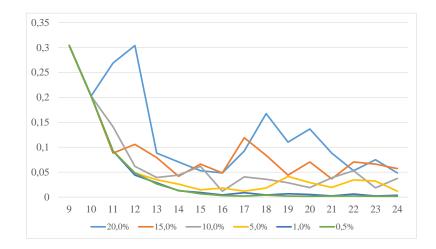

| 4.18 | Relative $\infty$ -norm errors that are introduced in the electronic equivalent of the $\Gamma$      |     |

|      | matrix                                                                                               | 142 |

| 4.19 | Relative $\infty$ -norm errors that are introduced in the electronic equivalent of the               |     |

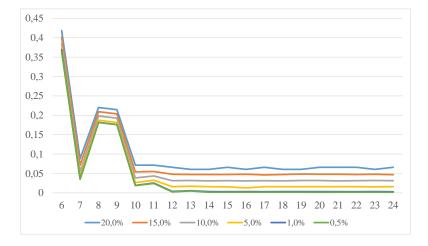

|      | $\Gamma^{-1}$ matrix                                                                                 | 142 |

| 4.20 | Relative $\infty$ -norm errors that are introduced in the electronic equivalent of the $\mathcal I$  |     |

|      | vector                                                                                               | 143 |

| 4.21 | Relative $\infty$ -norm errors that are introduced in the electronic equivalent of the $\mathscr{I}$ |     |

|      | vector; dynamic scaling of the current mapping ratio $\rho_I$ is followed as per (4.36)              | 144 |

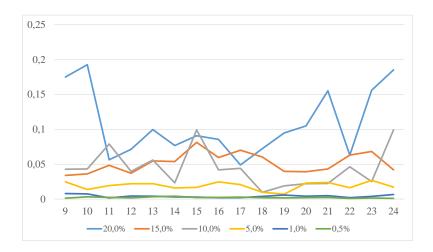

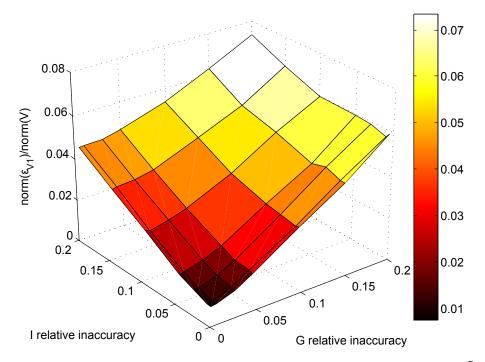

| 4.22 | Relative $\infty$ -norm errors that are introduced to the voltage solution $\tilde{V}$ due to        |     |

|      | conductance and current inaccuracies of the MSC $\ldots \ldots \ldots \ldots \ldots \ldots$          | 145 |

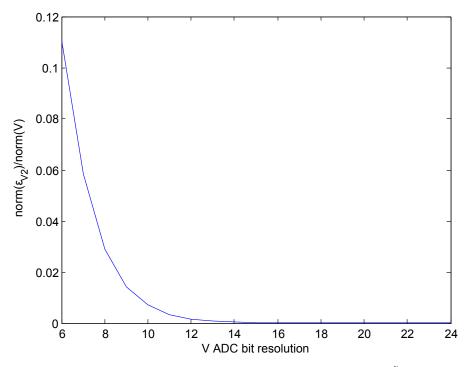

| 4.23 | Relative $\infty$ -norm errors introduced to the voltage solution $\tilde{V}'$ due to the quanti-    |     |

|      | zation of the voltage ADC of the IMNs                                                                | 146 |

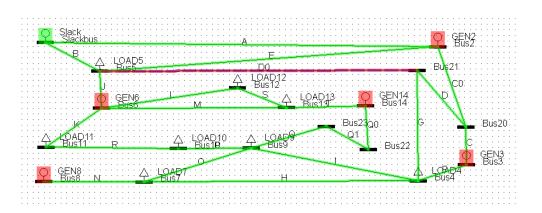

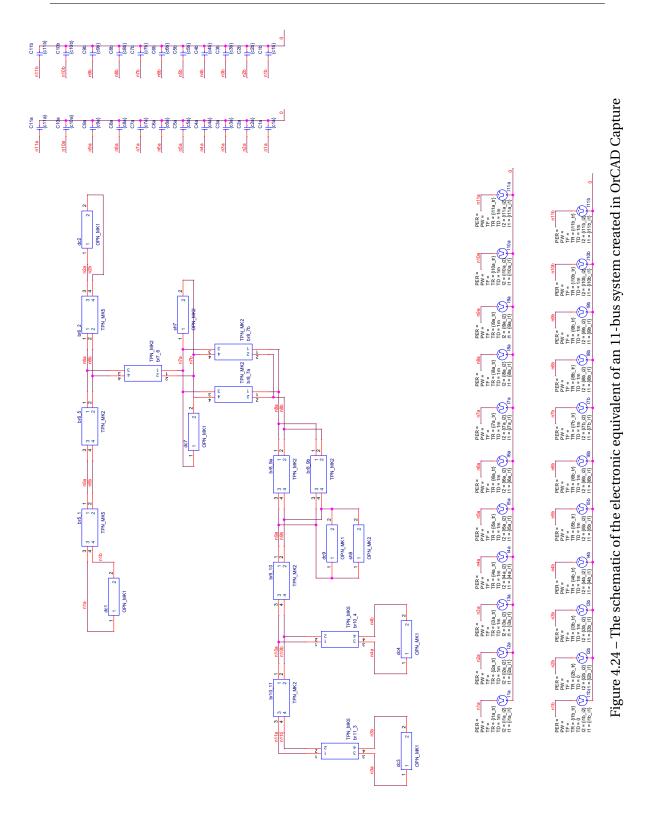

| 4.24 | The schematic of the electronic equivalent of an 11-bus system created in OrCAD                      |     |

|      | Capture                                                                                              | 147 |

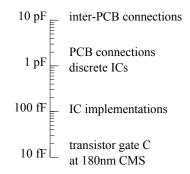

| 4.25 | Thumb-rule diagram for the order of magnitude of parasitic capacitances on                           |     |

|      | different electronic design paradigms                                                                | 148 |

#### List of Figures

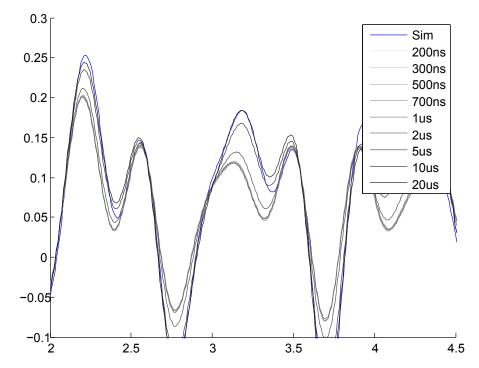

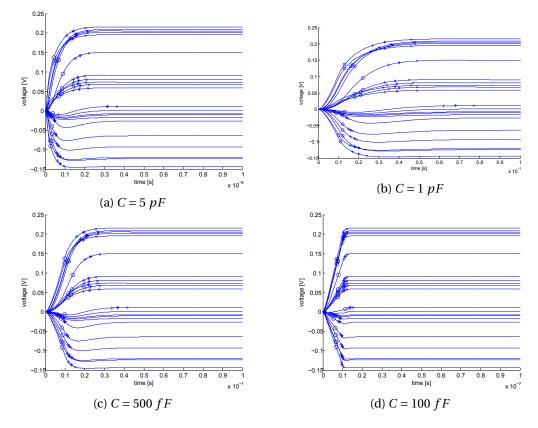

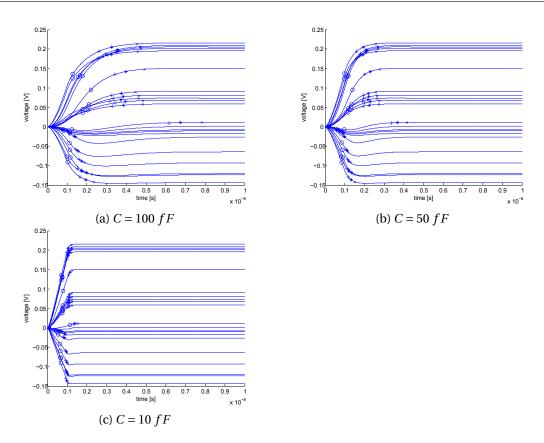

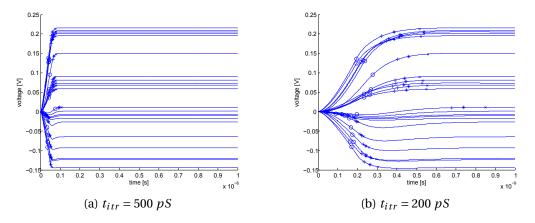

| 4.26 | Transients of the node of voltages of the MSC-mapping of the 11-bus system                                                                                          |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | using a current source slew rate of $t_{itr} = 10 \ ns \ \dots \ \dots \ \dots \ \dots \ \dots$                                                                     | 149  |

| 4.27 | Transients of the node of voltages of the MSC-mapping of the 11-bus system                                                                                          |      |

|      | using a current source slew rate of $t_{itr} = 1 \ ns \dots $ | 150  |

| 4.28 | Transients of the node of voltages of the MSC-mapping of the 11-bus system                                                                                          |      |

|      | assuming uniform parasitic capacitances of $C = 10 fF$                                                                                                              | 150  |

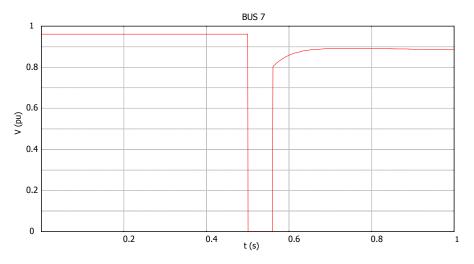

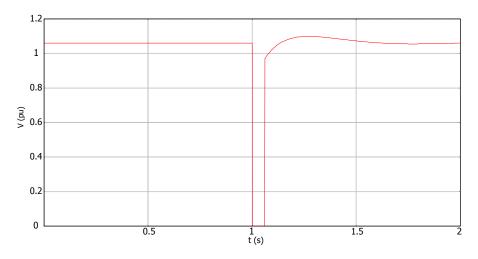

| 4.29 | Voltage of bus #7 of the 11-bus system after a 60 ms $3{\text -}\phi$ fault on the same bus $% \phi$ .                                                              | 152  |

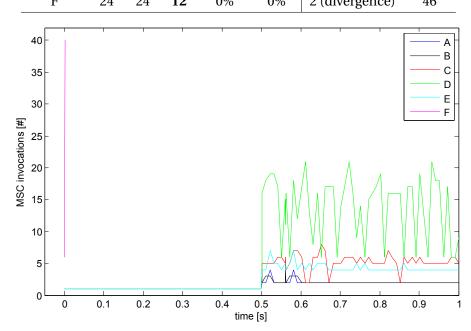

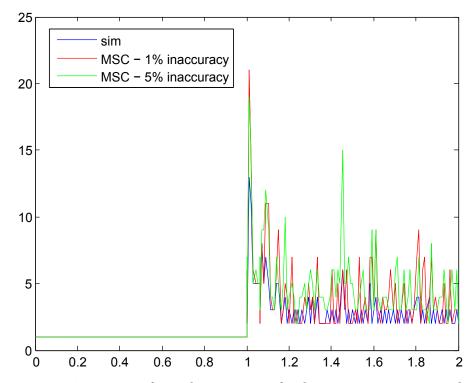

| 4.30 | MSC invocations for each time instant for the transient scenario on the 11-bus                                                                                      |      |

|      | system                                                                                                                                                              | 153  |

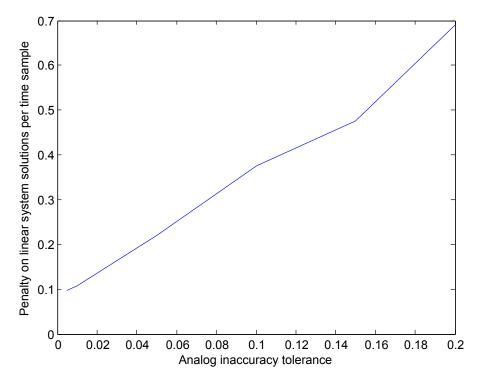

| 4.31 | Average penalty on the number of Newton (internal) iterations for one time                                                                                          |      |

|      | (external) iteration                                                                                                                                                | 154  |

| 4.32 | Voltage of bus #4072 of the 77-bus system after a 60 ms $3-\phi$ fault on the same bus                                                                              | 5156 |

| 4.33 | MSC invocations for each time instant for the transient scenario on the 77-bus                                                                                      |      |

|      | system                                                                                                                                                              | 157  |

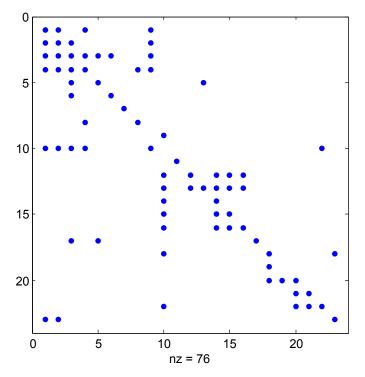

| 5.1  | Most generic sparsity pattern of the $A_i$ matrix of injectors                                                                                                      | 164  |

## List of Tables

| 1.1 | Operations in power systems 10                                                        |

|-----|---------------------------------------------------------------------------------------|

| 1.2 | Smart grid technologies 15                                                            |

| 1.3 | Benefits of distributed generation 17                                                 |

| 2.1 | Abstraction layers of power system computing                                          |

| 2.2 | Linear algebra libraries in power system research and applications                    |

| 2.3 | Analogies between flow networks, power systems, and analog electronic networks 36     |

| 3.1 | Time domain and Laplace domain    77                                                  |

| 3.2 | Stages of inaccuracy of linear operations performed by the mixed-signal computer 82   |

| 3.3 | 59-bus test case maximum absolute rotor angle deviation for TSA 98                    |

| 3.4 | Speed comparison between different engines for the TD simulation of the 18-bus        |

|     | system                                                                                |

| 3.5 | Timing break-up between PC, USB communication and the FPPNS for a tran-               |

|     | sient stability operation 101                                                         |

| 3.6 | Timing results summary for the n-1 branch contingency analysis 101                    |

| 3.7 | Timing results summary for the CCT analysis 102                                       |

| 3.8 | n-1 branch contingency results for different integration algorithms and time steps105 |

| 3.9 | Characterization of the existing platform 109                                         |

| 4.1 | Comparison of the roles of different platforms and domains in the FPPNS and           |

|     | the MSC 115                                                                           |

| 4.2 | Different models for different parts of the branch model of Fig. 3.6 122              |

| 4.3 | TPN modifications and their ability to represent branch types 125                     |

| 4.4 | TPN modifications, their complexity and their primary usage for branch type           |

|     | representation                                                                        |

| 4.5 | Interface between the RAMSES software and the MSC platform                            |

| 4.6 | Empirical settling times for different parasitic capacitances and current sources     |

|     | slew rates                                                                            |

| 4.7 | Free design parameters of the MSC and their effect in the operation 151               |

| 4.8 | Test cases to validate the design guidelines of table 4.7                             |

| 4.9 | Effect of analog inaccuracy to the average penalty on Newton iterations with          |

|     | respect to the bit resolution of the current injections 155                           |

|     |                                                                                       |

#### List of Tables

| 4.10 | Effect of analog inaccuracy to the average penalty on Newton iterations with          |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | respect to the bit resolution of the voltage measurements                             | 155 |

| 4.11 | Effect of analog inaccuracy to the average penalty on Newton iterations with          |     |

|      | respect to the bit resolution the reconfigurable conductances                         | 155 |

|      |                                                                                       |     |

| A.I  | General overview of systems to be examined                                            | 168 |

| A.2  | General linear algebraic properties of the admittance matrix <i>Y</i> of power system |     |

|      |                                                                                       |     |

### Introduction

The purpose of this work is to create *a computing platform, dedicated to power system simulation.* First of all it is important to understand, *why* such a platform is necessary. In order to understand this motivation, an overview of modern power system and its stakeholders is given in chapter 1. The operations that are performed by the stakeholders are described and their time intensity is assessed. The environment is shifting however, with radical changes being imminent, in what has been termed as the advent of the "smart grid". The triggers of this change are presented and the premises of this new future state of the grid are shown. It is partly this change, that calls for faster power system analysis tools.

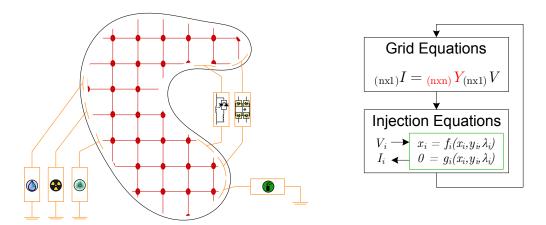

Equally important is to see *what* is expected by a power system analysis platform. Special focus is given to simulation of the dynamics of the power system, since this is the major focus of this work. Through modeling of the power system components, each analysis is associated with a mathematical formulation. The latter is handled by algorithms dedicated to it. The algorithms are concerned with *how* the problem is solved. They are the ones to be executed on the hardware computing platforms, i.e. *where* the problem is solved. This logical chain and the coherence that is necessary between its components is the focus of the first part of chapter 2.

In this course it will become evident, that linear algebra has a central position in power system computations. This is related to the interconnected nature of the system under study, which results in large matrix-vector relations between the quantities of interest, e.g. voltage, currents, and admittances. Linear algebra qualifies as one of the most challenging scientific computing domains for conventional digital computing. The state of the art of conventional digital platforms with favorable computing characteristics for linear algebra & power system applications is reviewed in the second part chapter 2. As an alternative to conventional digital computing the analog electronic paradigm is presented, which is the main focus of the next chapters of this work. Both analog electronic networks and power system topologies are *flow networks*, and this underlying affinity makes analog electronic computing particularly pertinent to power system problems.

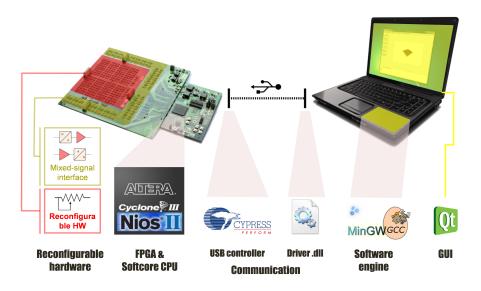

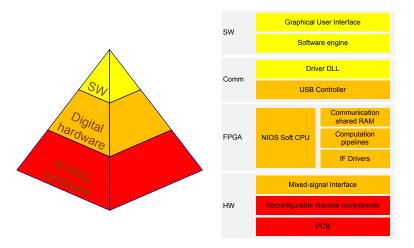

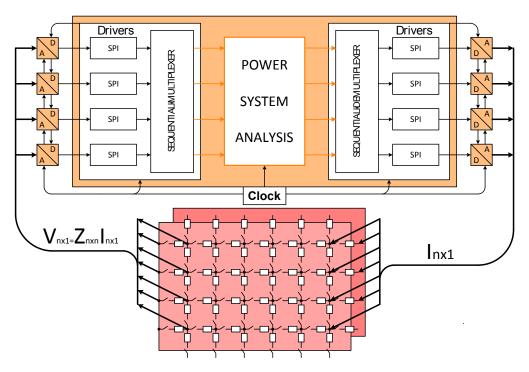

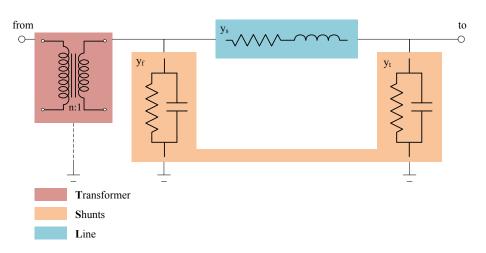

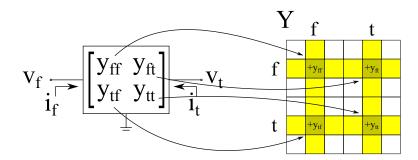

Chapter 3 presents a hardware platform that is dedicated to the transient simulation of power systems. The platform, termed Field Programmable Power System Network (FPPNS), has an analog and a digital part. The analog part handles the linear algebra operations, and

#### List of Tables

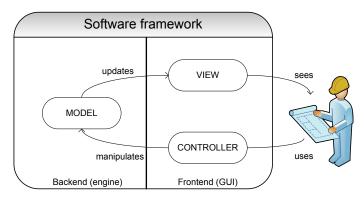

the digital one the solution of the differential algebraic equations that describe the dynamic behavior of the components of the system. A USB connection is used to connect the FPPNS to a conventional PC. On the PC side a co-designed software application has been created. It acts as a user interface as well as a wrapper of the functionality of the dedicated hardware. The mathematical properties of the FPPNS are thoroughly examined in the chapter. The inaccuracies of the hardware are examined and their effect on the final results provided by the FPPNS is shown. The system is evaluated across nine different criteria, and a comparison with related state-of the art is conducted.

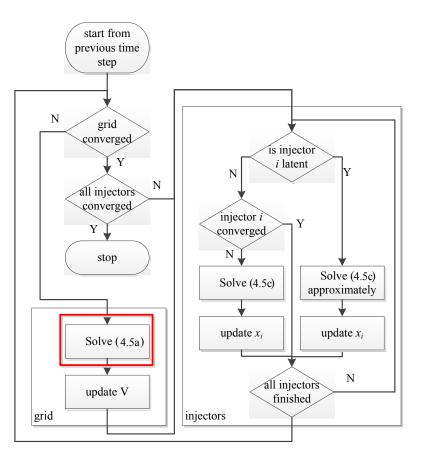

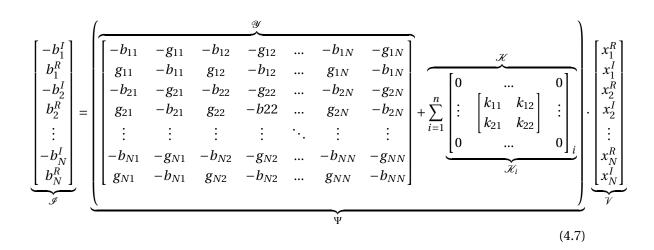

Despite the favorable performance characteristics of the realized platform, certain limitations have been identified. Hence, chapter 4 introduces a concept design for a future generation of a mixed-signal computer that overcomes most of the limitations of the current prototype. The new design is again mixed signal, analog and digital and is termed Mixed Signal Computer (MSC). An a priori design objective was to integrate the MSC into the flow of the transient simulator RAMSES [5, 6]. A software emulator of the proposed hardware platform has been created. With the help of the emulator a thorough exploration of the design space of MSC parameters has been conducted. The effect of individual parameters to the overall accuracy of the results has been examined and related design guidelines have been proposed. One suggested implementation has been successfully utilized in the RAMSES flow to simulate small and medium sized systems. For the linear algebra operations, speedups of four orders of magnitude have been achieved. This translates to respectable overall speedups of the simulation. Finally, conclusions and future perspectives of this work are given in chapter 5.

This work lies in the cross-field of three distinct and vast domains: power systems, electronics, and computing. An exhaustive presentation of every encountered topic is not realistically feasible and is out of the scope of this manuscript. When required, the reader is referred to related literature. Where additional insight on peripheral topics has been deemed useful, dedicated appendices have been included.

#### **Contributions of this work**

Hereunder the major original contributions of this work are listed.

- A detailed **list of operations and analyses in the modern power system environment** has been compiled.

- An overview of the emerging **future of the power system**, termed the "smart grid" has been presented.

- The critical **role of linear algebra operations in power system computations** has been identified and related literature has been reviewed.

- The importance of the coherence between the underlying platform and the algorithm

that is executed has been highlighted. In view of this observation, a literature review on hardware platforms that are dedicated to linear algebra operations has been compiled.

- The **limitations of conventional digital electronic hardware** are noted and analog computing is proposed as an alternative. The state of analog computing is given, again with a particular focus on power system applications.

- A set of plausible **evaluation criteria for analog computers** is drafted. These criteria are used to evaluate the main results of this work.

- A hardware prototype dedicated to the analysis of power systems has been created. The system spans along a conventional host PC and a dedicated hardware platform.

- On the PC side, dedicated software has been written. It acts as a user interface and it exposes the functionality of the dedicated hardware to any programming language through an API.

- The dedicated hardware consists of an analog and a digital part which is synthesized on reconfigurable hardware. The *author did not take part in the actual implementation* of the platform. He participated in the **design of the system and the determination of its specifications**, especially on the digital and the communication interface side.

- The **mathematical properties of the analog part** of the platform have been detailed. The accuracy of the actual implementation has been thoroughly studied.

- An investigation has been conducted on the **effect of numerical integration** on the quality of the final results of the dedicated hardware.

- The **timing properties of the analog part** of the hardware have been investigated and an aggregate simplified model has been proposed.

- The limitations of the proposed design are exposed.

- A **conceptual future solver** that overcomes the limitations of the existing prototype has been proposed, termed Mixed Signal Computer (MSC). It is again hybrid (analog-digital) and dedicated to power system simulation. A major design goal has been to integrate the proposed hardware in the flow of the RAMSES [5, 6] power system transient simulator software.

- The mathematical properties of the MSC are presented. An analysis of the accuracy and the timing of the operations is in the same vein as in the case of the existing realized prototype.

- A fully parameterizable software emulator of the MSC has been created. It has been used to get results on the application of the MSC in atomic linear algebra operations, as well as on its integration into the RAMSES flow. Based on these results an **exploration of the design space** has been conducted and design guidelines are proposed.

### 1 Modern power system landscape

In this chapter an overview of the architecture of the power system is given. Its traditional structure is presented alongside a brief description of the stakeholders that participate in its design, planning and everyday operation. A list of operations of the stakeholders is compiled and characterized for their time intensity.

The traditional way to operate the grid is changing. Reasons that call for that change will be highlighted. The prospective evolution of the grid into the future is what is often called the "smart-grid". Premises of it will be postulated and the side-effect it has to power system analysis tools will be shown.

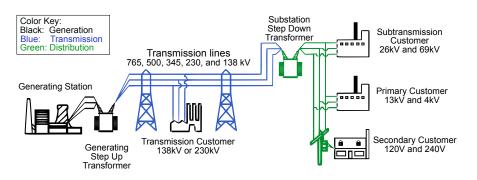

Figure 1.1 – A schematic of the traditional structure of a power system [1]

#### **1.1 Current architecture**

The power system has been named the "largest man-made machine ever". It can be defined as a complex socio-economic-technical system, featuring strong interrelation between societal needs and expectations, market operations and technical infrastructure. Electricity is conceivably the most multipurpose energy carrier in our modern global economy, and it is therefore primarily linked to human and economic development. Electricity growth has overtaken that of any other fuel, leading to ever-increasing shares in the overall mix. This trend is expected to continue throughout the following decades, with large parts of the world population in developing countries appealing to be connected to power grids [7].

Electrical power systems have been traditionally designed and operated taking energy from high-voltage levels, and distributing it to lower voltage level networks. There are large generation units connected to transmission networks. In these networks there is a bulk transport of electricity, with central coordination of control. Demands are passive and uncontrollable, connected to distribution networks. Distribution systems are also passive and, in the lower levels of voltage, radial in operation. They are designed to accept power from transmission systems and distribute to customers, generally with unidirectional flows [8]. Such a system is depicted in Fig. 1.1.

It is made up of many geographically dispersed components and it can exhibit global change almost instantaneously as a result of local actions. Actions are exerted on the components of the system by the *stakeholders*. As a stakeholder we consider anyone that is in interaction with the power system, i.e. that is affected by it or that can affect the system through his actions. It is out of the scope of this work to present a thorough stakeholder analysis of the power system. Instead the following sample entities are defined indicatively for the facilitation of the analysis that follows. These entities have arisen after the liberalization and the unbundling of the top-down monopolies in power system operators. They are the conceptual players in the power system world that have an interest/utility in fulfilling their objectives. These objectives may be financial profit, or simply the utility of serving their need for electricity.

ISO refers to the Independent System Operator. ISOs coordinate, control and monitor the

operation of the system in a given region. In some regions around the world the ISO also has market authorities.

- **GENCO** stands for Generation Company, i.e. a company engaged solely in producing electivity, normally by owing or maintaining energy production facilities (e.g generators).

- **TRANSCO** stands for Transmission Company, as understood in the market sense, i.e. a company which owns or maintains energy transmission facilities and the business object of which is the transmission of energy.

- **DISCO** stands for Distribution Company, i.e. a theoretical (or real) company which owns or maintains energy distribution facilities and the business object of which is the distribution of energy from the transmission level of the grid to the *End users*

- **End users** are the final consumers of electricity, residential, commercial or industrial. As it will be explained in sections that follow, there is a recent trend that the end users also feed electricity back into the grid.

The above definitions of the ISO, the GENCO, the TRANSCO and the DISCO are only indicative and always depend on the local power system governance and regulatory scheme. Often the boundaries between their responsibilities are blurred.

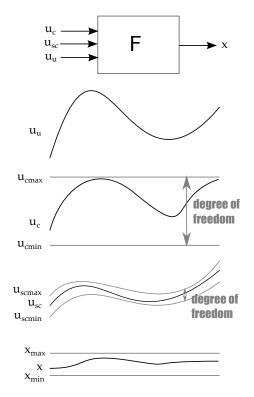

The aim of the stakeholders is to drive the system in a way that generates the most utility to them. Utility can be monetary or anything relevant, e.g. proper functioning of the grid within its technical limits for some ISOs. An illustrating abstraction can be introduced that is drawn from general system theory. For each stakeholder, the power system can be viewed as a black box  $\mathscr{F}$  that has two kind of inputs: the *uncontrollable* inputs that the stakeholder cannot control  $u_u$ , and the ones that can be controlled, termed *controllable*  $u_c$  and *semi-controllable* inputs  $u_{sc}$ . The former are termed controllable because the stakeholder has a large degree of freedom on them  $[u_{cmin} - u_{cmax}]$ , and the latter are termed semi-controllable because the degree of freedom on them  $[u_{scmin} - u_{scmax}]$  is smaller. The goal of each stakeholder is to manipulate the controllable and the semi-controllable inputs so as to keep some system "state" variable *x* within some "good operation limits"  $[x_{min} - x_{max}]$ . These state variables (e.g. voltage magnitudes, angles, power flows, prices) are different for each stakeholder and they are all subject to equality and inequality constraints, to ensure proper operation of the system. This concept is illustrated in Fig. 1.2.

The way each stakeholder acts on the system is as follows.

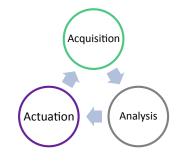

- Acquisition is the phase where the stakeholder collects data on the system, i.e. "measures" variables of interest to him.

- **Analysis** is the phase where the stakeholder runs his "computation routines" in order to determine his actions.

Figure 1.2 – The power system as a black box

**Actuation** is the feedback of the stakeholder back to the grid, in terms of values for the controllable and the semi-controllable variables.

The above cycle is executed repeatedly, in what is here called the *stakeholder operation cycle*, shown in Fig. 1.3.

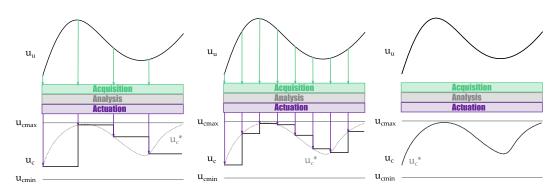

The faster the stakeholder cycle, the better the ideal *x* curve is approximated as shown in Fig. 1.4. In the ideal case where all acquisition, analysis and actuation phases were instantaneous, the *x* curve would be as close to the ideal one as possible. It is therefore to the interest of the stakeholder to improve the speed of every element of the cycle of his operation cycle.

Figure 1.3 – The operation cycle of a stakeholder

Figure 1.4 - The effect of a faster operation cycle for a stakeholder

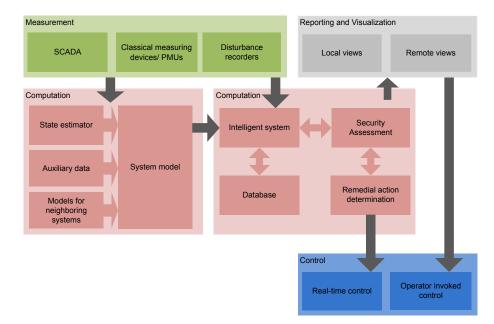

Figure 1.5 - Building blocks of an Energy Management System (EMS) of a utility operator

For utility operators, these operations are performed in computer-aided environments called energy management systems (EMS). EMSs have been present since the era of vertical integration in power systems. EMSs are a point of monitoring, control and optimization for a part of a grid. For that to be enabled, an EMS employs a wide range of supervisory control and data acquisition (SCADA) functionality. Such a system is shown schematically in Fig. 1.5; color coding from Fig. 1.3 has been retained.

Table 1.1 provides a non-exhaustive list of operations commonly executed in the frame of a modern power system. Column "Level" refers to the level of the power system, as in table 1.2.

| Operation                                                                       | Algorithms                                                                                 | Software & Equipment<br>involved | Level   | Stakeholders                     | Time<br>intensity |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------|---------|----------------------------------|-------------------|

| Economical feasibility studies (equip-<br>ment sizing)                          | Operational research                                                                       |                                  | GTD     | ISO, GENCO,<br>TRANSCO,          | -                 |

| Torritorian anticonterior                                                       | linn) chadten/coincurce activitiend                                                        |                                  | F       | DISCO                            | -                 |

| rransmission expansion, Opuma<br>compensation device/capacitor                  | rreuction scenarios/ methous, (Avair-<br>able Transfer Capability (ATC) meth-              |                                  | -       | IRAINOCO                         | -                 |

| placement<br>Power flow analysis                                                | ods), VAR optimization methods<br>Power flow algorithms, network reduc-<br>tion algorithms |                                  | *       | ISO                              | 23                |

| Static Security Assessment (SSA), con-                                          | N-1/N-P contingency analysis                                                               |                                  | *       | ISO, GENCO,                      | 2                 |

| tingency analysis, emergency switch-<br>ing plans                               |                                                                                            |                                  |         | TRANSCO,<br>DISCO                |                   |

| Protective device coordination/sizing,                                          | Short circuit analysis (ANSI C37/IEC                                                       | Distance/protection re-          | *       | ISO, GENCO,                      |                   |

| Distance relaying configuration, Reclo-<br>sure synchronization                 | (60609                                                                                     | lays                             |         | TRANSCO,<br>DISCO, 1-2           |                   |

| Voltage stability analysis                                                      | Continuation power flow (CPF) meth-<br>ods, Bifurcation analysis                           |                                  | *       | ISO                              | 2                 |

| Power quality/Harmonic (distortion)<br>analysis                                 | Fourier analysis                                                                           |                                  | 11<br>L | ISO, TRANSCO,<br>DISCO           | 2                 |

| Small-signal Stability analysis, Power<br>System Stabilized (PSS) configuration | Eigenvalue algorithms, sensitivity<br>analysis                                             |                                  | Г       | ISO, TRANSCO,<br>DISCO           | 1-2               |

| Dynamic Security Assessment (DSA)                                               | Time domain (TD) simulation (ms scale), Symmetrical components the-<br>ory                 |                                  | Œ       | ISO, TRANSCO,<br>DISCO           | 2                 |

| Electo-Magnetic Transients analysis<br>(EMT), Lightning protection              | Time domain (TD) simulation (sub-ms scale)                                                 | EMTP                             | Π       | ISO, TRANSCO,<br>DISCO           | 2                 |

| Reliability assessment                                                          | Probabilistic methods, Index based<br>quantification                                       |                                  | *       | ISO, GENCO,<br>TRANSCO,<br>DISCO | 0                 |

Table 1.1 - Operations in power systems

| Optimization, Unit Commitment                                                    | Unit commitment algorithms, Op-<br>timal Power (OPF) algorithms, -<br>emmisions/security constrained |                                                                                    | *   | ISO, GENCO,<br>TRANSCO,<br>DISCO | n   |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|----------------------------------|-----|

| Market decision making/bidding                                                   | Market simulation                                                                                    | Market agents                                                                      | *   | ISO, GENCO, End<br>users         | 4   |

| Load forecasting                                                                 | Statistical methods, Intelligent systems (ANN, etc.)                                                 |                                                                                    | U   | (TRANSCO),<br>DISCO, End         | 3-4 |

| Price/Load forecasting                                                           | Artificial intelligence, neural networks,<br>times series analysis                                   | Microgrid controllers,<br>market agents                                            | *   | *                                | 3-4 |

| State Estimation, Monitoring/Situa-<br>tional awareness (engineering diag-       | WLS, Kalman filters                                                                                  | SCADA, Wide Area<br>Measurement Systems                                            | TDC | TRANSCO,<br>DISCO                | 3-5 |

| Active power flow and frequency con-<br>trol. Power electronic interface control | AGC & FACTs configuration                                                                            | (warne)<br>Prime movers (speed<br>governing)                                       | QI  | TRANSCO,<br>DISCO                | J.  |

| Smart metering                                                                   |                                                                                                      | Smart meters                                                                       | U   | DISCO, End users                 | 4   |

| Intelligent load shedding                                                        |                                                                                                      | Breakers, substations                                                              | DC  | DISCO, End users                 | 5   |

| Home/Building automation                                                         |                                                                                                      | Distributed electronics                                                            | U   | (DISCO), End                     | 4-5 |

|                                                                                  |                                                                                                      | (sensors, actuators,<br>comm_infrastructure)                                       |     | users                            |     |

| Transmission/distribution line design                                            | Line parameter estimation                                                                            |                                                                                    | TD  | TRANSCO,<br>DISCO                | 1   |

| Reactive power flow and voltage con-                                             | Reactive compensation techniques,                                                                    | Tap changing/ULTC                                                                  | Π   | TRANSCO,                         | 4-5 |

| trol                                                                             | AVR configuration                                                                                    | transformers,<br>shunt/series capac-<br>itor banks/reactors,<br>static var systems |     | DISCO                            |     |

| Sub-synchronous resonance analysis                                               |                                                                                                      | Prime movers and re-<br>lated controls                                             | GT  | GENCO, ISO                       | 1-2 |

| Controlled islanding schemes, Black<br>start planning, System restoration        |                                                                                                      |                                                                                    | GT  | ISO                              | 1   |

11

| 1                              |        | 1                       |                 |

|--------------------------------|--------|-------------------------|-----------------|

| TRANSCO,                       | DISCO  | End users               |                 |

| đī                             |        | Compensation device/- C | capacitor banks |

| Time-domain simulation (sub-ms | scale) |                         |                 |

| Insulation coordination        |        | Power factor correction |                 |

12

The column "Time intensity" refers to how tight are the time margins for the operation to be finished. Increasing number denote tighter requirements.

- **1: planning/design operations** These analyses are often performed only once, in a planning/design phase, hence, they have no practical time constraints.

- **2: periodic offline operations** These are analyses that are executed once per day/week. They are performed more than once, but their periodicity is so infrequent that poses almost no practical limits to their execution.

- **3: periodic online operations** <sup>1</sup> These are analyses that executed once per a tighter time frame than the above, e.g. in the execution frame of a "measurement data acquisition state estimation analysis" cycle of an Energy Management System in a system operator (15 minutes). Or in the bidding-clearing time frame of an energy exchange (5 minutes).

- **4: real-time operations** <sup>1</sup> These operations refer to operations that are performed continuously, i.e. that are subject to some real-time constraints.

- **5: hard real-time operations** In these case of real-time operations the constraints are "hard", in the sense that if they are not met, some part of the expected functionality in the system will fail. These task are the most demanding tasks from a computing point of view.

#### 1.1.1 The need for change

It is now widely accepted that changes to the aforementioned traditional architecture are necessary. Among others, factors contributing to this reshaping are the following [10].

- Different governance frame: liberalization, shift from vertical monopolies to deregulated markets.

- Consumer consciousness, power "ethics", e.g. consider post-Fukushima declining support for nuclear.

- Aging infrastructure: early post-WWII.

- Increase in demand quantity beyond expectation, e.g. demand doubled since '60s.

- Changes in demand nature: changing peak hours, load patterns, increased quality-ofservice demands, differentiated products.

<sup>&</sup>lt;sup>1</sup>It is useful to note a distinction raised in [9], between the terms *online* and *real-time* when used in the power system domain. Online refers to the results of the analysis tool being available to the SCADA/EMS of the operator, while real-time refers to the results of the analysis being ready within a time frame that is deemed "real-time" for the specific application.

- Advances in technology: storage, distributed generation, smart metering.

- · Climate change and related political/public opinion pressures.

As very significant investments will be required to simply renew this infrastructure (\$6.9 trillion capital investment spanning 15 to 25 years reported in [11]), the most efficient way forward is to incorporate innovative technologies and solutions when planning and executing this renewal [12].

#### 1.2 Future architecture: the Smart Grid

The term *smart grid* is used interchangeably to denote a plethora of emerging technologies in the field of power systems. It would be more precise to refer to the smart grid as *the grid of the future*, but for conventionality the use of the term is retained throughout this work. Two underlying conceptual points of the smart grid are its *de-centralization* and the existence of *localized intelligence*.

History and organizational analysis suggest that a centralized point of control comes in the way of rapid scaling of value creating activities, often becoming the bottleneck limiting evolution of ideas and novelty of executions [13]. Furthermore, a bottom-line premise of the smart grid is to be self-healing. This implies some sort of underlying distributed control of the system with individual components as independent intelligent agents. These agents would compete and cooperate to achieve global optimization [14].

A complex socio-technical system featuring similar requirements is the internet. And as Robert Metcalfe urges, *it is of utmost importance to mine the history of the internet, to learn from that experience, and to find the correct lenses to look at the smart grid problem* [15]. The genius in the internet is in its flexibility and versatility. For the smart grid to follow the success story of the internet, it needs to endorse this versatile design and encourage innovative participation from all stakeholders.

For that the following premises are set [13]: The smart grid is the future evolution of the power system that:

- will meet all our energy demands (not just current electricity demand),

- will be powered almost totally by renewable resources,

- will operate all its components at their maximum allowable capacity,

- command and control intelligence will be pervasively distributed and sub-second responsive, and

- will be able to self heal.

| Tech                                                             | Level <sup>1</sup> |  |  |

|------------------------------------------------------------------|--------------------|--|--|

| Substation automation                                            | TD                 |  |  |

| Distribution automation                                          | TD                 |  |  |

| Phasor measurement                                               | GTD                |  |  |

| Smart metering                                                   | С                  |  |  |

| Smart appliances                                                 | С                  |  |  |

| Home automation                                                  | С                  |  |  |

| Demand response                                                  | С                  |  |  |

| Electric vehicles                                                | GC                 |  |  |

| Energy storage                                                   | GC                 |  |  |

| Distributed generation                                           | G                  |  |  |

| Renewable sources                                                | G                  |  |  |

| Communication infrastructure                                     | GTDC               |  |  |

| DER aggregation schemes                                          | GTDC               |  |  |

| <sup>1</sup> G: Generation; T: Transmission; D: Distribution; C: |                    |  |  |

Table 1.2 – Smart grid technologies

<sup>1</sup> G: Generation; T: Transmission; D: Distribution; C: Consumption

The definition of smart grid can also depend on local conditions; different countries can have very different starting points for the progress towards smart grid. Deployment of smart grid technologies will occur over a long period of time, adding successive layers of functionality and capability onto existing equipments and systems.

Technology is the key consideration and it can be defined by certain technical characteristics: e.g. predictive, integrated, interactive, optimized, flexible, accessible, reliable, economic, and secure. Broadly speaking, three major technological domains of the smart grid are distributed intelligence, communication technologies, and automated control systems [16]. So far, research has been focusing on all three of them. Among others, impressive work has been carried out in technologies such as: substation automation, distribution automation, phasor measurement (PMU), smart metering, smart appliances, home automation, demand response, electric vehicles (PHEV), energy storage, distributed generation, renewable sources, communication infrastructure, DER aggregation schemes, etc. Scrutiny of the aforementioned is out of the scope of this paper. Table 1.2 summarizes them according to which level of the power system they pertain to: Generation, Transmission, Distribution or Consumption.

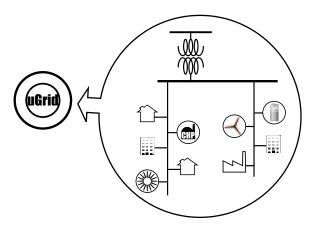

The next section presents recent advances in the field of distributed energy resources (DER) that seem to be greatly contributing to shifting the power system paradigm away from the prevalent centralized production scheme. The vehicle through which DER are to impact the structure of the power system is DER aggregations, reviewed in section 1.2.2.

#### 1.2.1 Distributed energy resources

Perhaps the most heavily researched field in smart-grid related technologies is distributed energy resources (DER). DER include distributed generation (DG), responsive loads and storage systems alike. Smart grid advances regarding the loads mainly focus on their responsiveness (see table 1.2). Storage systems would add to the flexibility of the system, providing the ability to shift energy consumption/production in time. Distributed generation is the sector that has received the most attention of the three and seems to have the greatest potential.

There is an ongoing debate on the definition of the distributed generation. To the author's opinion, the most apt definition has been given in [17]: DG is defined as an electric power source connected directly to the distribution network or on the customer side of the meter. Recent developments in DG include the following [18].

- Improvement of the efficiency of solar cells up to 20-24%.

- Increase in the capacity of wind generators from few kW up to several MW.

- Development of micro-, bio- and multi-fuel-CHPs (combined heat and power) plants to replace the conventional ones.

- Development of fuel cell technologies.

- Increase of efficiency and capacity of storage devices.

- Introduction of new renewable energy resources as tidal generators, small hydro generators, etc.

Reference [19] provides a comprehensive insight on DG technologies and their respective status quo.

The projected benefits of increased DG penetration seem to be in accord with the concept of sustainable development. This becomes clear once the benefits of DG are categorized in four domains as shown in table 1.3 [20, 8].

For completeness sake, it should be noted that high-degree penetration of DG into the bulk grid can also have adverse effects. These mostly relate to the technical operation of the system [8], including inversion in the energy flow, difficulties in voltage control and in management of reactive power. Also, despite the professed positive impact on reliability, it has been argued that there can also be a negative impact due to the non-dispatchable nature of some types of generation, such as intermittent solar panels, wind turbines, tidal generators, etc. Furthermore, the unpredictability implied by dependance on weather conditions for those generation units would require additional conventional standby capacity.

Up to now, DER have been used to displace energy from conventional generating plants but not to displace their capacity as they are not visible to system operators [23]. However, it is

| Domain        | Benefit                                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technical     | increase overall system efficiency e.g. CHP, bypass 'con-<br>gestion' in existing transmission grids, avoid transmis-<br>sion losses, provide network support or ancillary services,<br>increase flexibility, continuity and reliability of supply,<br>positive effect on transient stability [21] |

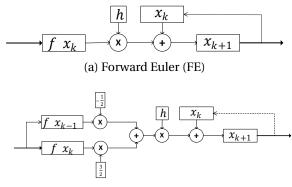

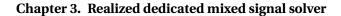

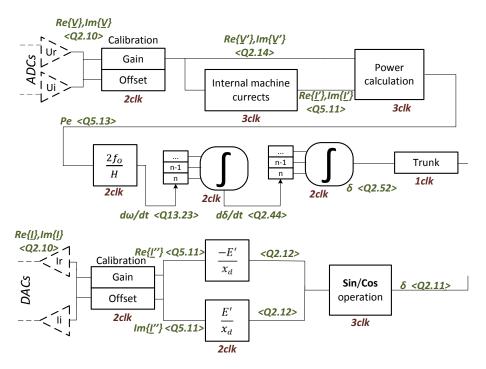

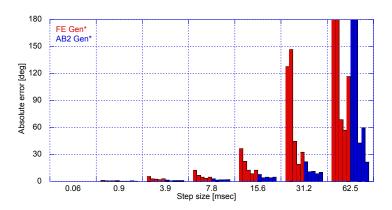

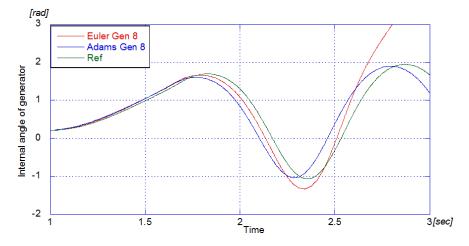

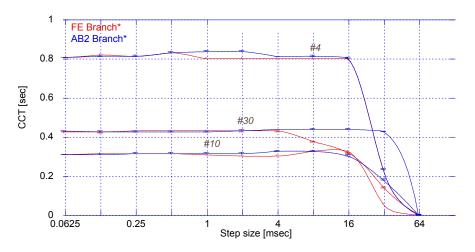

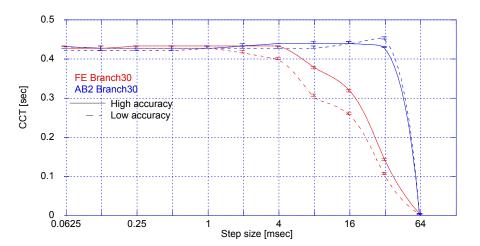

| Social [22]   | enable power equity, diversification of energy sources to<br>enhance energy security, support for competition policy,<br>improved utilization of local resources, local job creation                                                                                                               |