## Assessment of pseudo-bilayer structures in the heterogate germanium electron-hole bilayer tunnel field-effect transistor

J. L. Padilla, C. Alper, C. Medina-Bailón, F. Gámiz, and A. M. Ionescu

Citation: Applied Physics Letters 106, 262102 (2015); doi: 10.1063/1.4923467

View online: http://dx.doi.org/10.1063/1.4923467

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/106/26?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Response to "Comment on 'Assessment of field-induced quantum confinement in heterogate germanium electron–hole bilayer tunnel field-effect transistor" [Appl. Phys. Lett. 106, 026102 (2015)]

Appl. Phys. Lett. 106, 026103 (2015); 10.1063/1.4905866

Comment on "Assessment of field-induced quantum confinement in heterogate germanium electron-hole bilayer tunnel field-effect transistor" [Appl. Phys. Lett. 105, 082108 (2014)]

Appl. Phys. Lett. 106, 026102 (2015); 10.1063/1.4905865

Assessment of field-induced quantum confinement in heterogate germanium electron-hole bilayer tunnel field-effect transistor

Appl. Phys. Lett. 105, 082108 (2014); 10.1063/1.4894088

Tensile strained Ge tunnel field-effect transistors: k·p material modeling and numerical device simulation J. Appl. Phys. **115**, 044505 (2014); 10.1063/1.4862806

A model determining optimal doping concentration and material's band gap of tunnel field-effect transistors Appl. Phys. Lett. **100**, 193509 (2012); 10.1063/1.4714544

## Assessment of pseudo-bilayer structures in the heterogate germanium electron-hole bilayer tunnel field-effect transistor

J. L. Padilla, 1,a) C. Alper, 1 C. Medina-Bailón, 2 F. Gámiz, 2 and A. M. Ionescu 1

<sup>1</sup>Nanoelectronic Devices Laboratory, École Polytechnique Fédérale de Lausanne, Lausanne CH-1015, Switzerland

<sup>2</sup>Departamento de Electrónica y Tecnología de los Computadores, Universidad de Granada, Avda. Fuentenueva s/n, 18071 Granada, Spain

(Received 18 March 2015; accepted 20 June 2015; published online 30 June 2015)

We investigate the effect of pseudo-bilayer configurations at low operating voltages ( $\leq 0.5 \, \mathrm{V}$ ) in the heterogate germanium electron-hole bilayer tunnel field-effect transistor (HG-EHBTFET) compared to the traditional bilayer structures of EHBTFETs arising from semiclassical simulations where the inversion layers for electrons and holes featured very symmetric profiles with similar concentration levels at the ON-state. Pseudo-bilayer layouts are attained by inducing a certain asymmetry between the top and the bottom gates so that even though the hole inversion layer is formed at the bottom of the channel, the top gate voltage remains below the required value to trigger the formation of the inversion layer for electrons. Resulting benefits from this setup are improved electrostatic control on the channel, enhanced gate-to-gate efficiency, and higher  $I_{\rm ON}$  levels. Furthermore, pseudo-bilayer configurations alleviate the difficulties derived from confining very high opposite carrier concentrations in very thin structures. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4923467]

Extensive research has been devoted in the last years to explore more efficient configurations based on tunnel field-effect transistors (TFETs) in order to make this type of devices become a feasible alternative to conventional MOSFETs for sub-0.5 V operating voltages.  $^{1-3}$  Their strongest point is the remarkable steepness of point and average subthreshold swings,  $SS_{pt}$  and  $SS_{av}$ , respectively, that they may feature below the  $60\,\mathrm{mV/dec}$  thermal limit due to band-to-band tunneling (BTBT) injection mechanisms.  $^{4,5}$  However, TFETs have been repeatedly reported to suffer from low ON-currents compared to their MOSFET counterparts.

At early stages of development, it was found that the orientation of BTBT phenomena was important in order to allow the gate a better control over them. Simulation results and some recent experimental evidences indicate that the optimal scenario is attained when the tunneling direction and the gate-induced electric field are arranged to be aligned. Taking this into account, electron-hole bilayer TFETs (EHBTFETs) were proposed to exploit the benefits of dimensionality for BTBT between 2-D electron and hole gases. Later on, a heterogate structure for the EHBTFET (HG-EHBTFET) was introduced in order to avoid parasitic lateral BTBT processes. Nevertheless, quantization of conduction and valence bands due to field-induced confinement led to reduced  $I_{\rm ON}$  values for TFETs in general, and for EHBTFETs, in particular.  $I_{\rm A}^{13,17}$

In this letter, we show that a certain asymmetry between top and bottom gates delays the appearance of the electron inversion layer at the top of the channel thus giving rise to a pseudo-bilayer configuration that can be preserved for low operating voltages (we take  $V_{\rm TG} = V_{\rm DD} = 0.2, 0.3, 0.4$  and 0.5 V). We demonstrate that for a chosen top gate operating

voltage (bottom gate voltage,  $V_{\rm BG}$ , will be used to induce the asymmetric setup), there exists an optimized degree of asymmetry which minimizes the shortest tunneling distance,  $d_{\rm tunn}$ , at  $V_{\rm TG} = V_{\rm DD}$ . The use of pseudo-bilayer configurations keeps the energy subbands for electrons unpinned and enhances the gate-to-gate efficiency as defined in Ref. 18. A similar suggestion pointing to the direction of minimizing electron quantum capacitance while maximizing hole quantum capacitance was done in Ref. 19.

The HG-EHBTFET depicted in Fig. 1 features a source p<sup>+</sup> region (10<sup>20</sup> atoms/cm<sup>3</sup>), intrinsic channel region with central overlap and side underlap regions (1015 atoms/cm3), and drain  $n^+$  region (10<sup>20</sup> atoms/cm<sup>3</sup>). The body thickness,  $t_{body}$ , is chosen to be 10 nm. Top and bottom gate dielectrics are 3 nm-thick HfO<sub>2</sub> layers. Drain bias will be set at 0.3 V throughout this work and  $V_{\rm BG}$  initially set to 0 V. The different asymmetric configurations will be induced by gradual negative values of  $V_{\rm BG}$ . Optimized workfunctions for avoiding parasitic lateral BTBT<sup>13</sup> and for fixing subband alignment at very low  $V_{TG}$ (namely, we choose  $V_{\rm TG,align}$  to be 0.04 V in our study) are chosen as  $\phi_{tg,ol}=3.06\,\mathrm{eV},\ \phi_{tg,ul}=4.25\,\mathrm{eV},\ \phi_{bg,ul}=4.40\,\mathrm{eV},$ and  $\phi_{\rm bg,ol} = 5.05\,{\rm eV}$  at  $V_{\rm BG} = 0\,{\rm V}$ . For these values, the top gate voltage at which the electron inversion layer is formed,  $V_{\rm inv}$ , calculated as done in Ref. 20, turns out to be  $V_{\rm inv}$  $(V_{\rm BG} = 0 \, \rm V) = 0.05 \, \rm V$ . As we want the onset of vertical BTBT to remain fixed at the same  $V_{TG}$  value (0.04 V), and given that variations in the electron and hole subband alignment will be produced by applying gradual negative  $V_{\rm BG}$  values,  $\phi_{\rm tg,ol}$  will be readjusted in every case to guarantee that  $V_{\text{TG,align}}$  occurs at 0.04 V. The rest of the workfunctions will be kept constant throughout our study. Notice that a fixed  $V_{TG,align}$  value implies that the overdrive voltage will be raised as we increase  $V_{\rm TG}$ .

The quantization direction is along the [100] crystal orientation of Ge. Along this direction, the *L* electron valleys

a)Electronic mail: jose.padilladelatorre@epfl.ch

FIG. 1. (a) Schematic cross-section (not to scale) of Ge HG-EHBTFET considered in this work. The heterogate structure is introduced in both top and bottom gates. (b) Band profile along the vertical  $\overline{AB}$  segment with vertical BTBT allowed between the first energy subband for heavy holes,  $E_{hh1}$ , and that for electrons,  $E_{e1}$ .  $E_{ov}$  stands for the energy overlap once alignment has been surpassed.

are fourfold degenerate with quantization effective mass  $m_y = 0.12m_0$  and transverse effective masses  $m_x = 0.15m_0$  and  $m_z = 0.58m_0$ . For the  $\Gamma$  valley, effective masses for heavy holes, light holes, and electrons are  $m_{hh} = 0.33m_0$ ,  $m_{lh} = 0.044m_0$ , and  $m_e = m_{lh}$ , respectively.

The simulation setup accounting for quantum confinement was carefully described in Ref. 13 and is based on a TCAD hybrid integration that combines the most recent versions of the two most widely used simulators: Silvaco ATLAS (v.5.20.2.R)<sup>21</sup> and Synopsys Sentaurus (v.2014.09).<sup>22</sup> Similar approaches have been very recently used in the literature.<sup>23</sup>

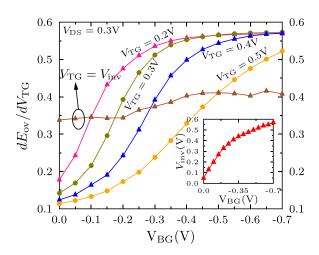

For analyzing Fig. 2 (and later on Fig. 3), three premises need to be clearly stated: (i) bottom gate sweeps must be understood not as conventional rampings, but rather as a comparison between multiple potential scenarios, each of which is characterized by a  $V_{\rm BG}$  value (and its associated  $\phi_{\rm tg,ol}$ ); (ii) along each curve where  $V_{\rm TG} = V_{\rm DD}$ , the only voltage that we vary is  $V_{\rm BG}$ ; and (iii) given the dependence of  $V_{\rm inv}$  with  $V_{\rm BG}$  (see inset) at a fixed drain bias (recall that we take  $V_{\rm DS} = 0.3$  V throughout all the paper), it is obvious that along the curve  $V_{\rm TG} = V_{\rm inv}$ , both  $V_{\rm BG}$  and  $V_{\rm TG}$  vary.

Taking this into account, we observe that when no asymmetry is induced, i.e.,  $V_{\rm BG} = 0 \, \rm V$ , efficiency remains extremely low ( $\leq 0.18$ ) for all the curves corresponding to  $V_{\rm TG} = V_{\rm DD}$ ; and jumping from one  $V_{\rm DD}$  to another at  $V_{\rm BG} = 0 \, \rm V$  has little impact on it. This is due to the fact that

FIG. 2. Gate-to-gate efficiency controlling the energy overlap between first energy subbands as defined in Ref. 18, at fixed  $V_{\rm DS} = 0.3$  V. For each  $V_{\rm TG}$ , efficiency increases as we induce stronger asymmetries saturating at  $dE_{\rm ov}/dV_{\rm TG} = 0.57$ . The inset shows the growing behavior of  $V_{\rm inv}$  for increasing asymmetric configurations.

for  $V_{BG} = 0 \text{ V}$ ,  $V_{inv}$  is 0.05 V (see inset) and, therefore, all the curves with  $V_{TG}$  fixed to  $V_{DD}$  verify that they stand for situations where  $V_{\mathrm{TG}}$  is above  $V_{\mathrm{inv}}$ . In other words, this implies that for  $V_{BG} = 0 \text{ V}$ , the inversion layer for electrons is formed in all cases, the energy subbands pinned and, thus, the gate efficiency severely degraded. As we increase the asymmetry between both gates (making  $V_{BG}$  gradually more negative), so does the gate efficiency go up because  $V_{\rm inv}$  is raised (again, see inset). It is straightforward to understand that for a given  $V_{BG}$ , the further we keep  $V_{TG}$  below  $V_{inv}$  the higher the efficiency that we obtain. For example, let us focus on  $V_{BG} = -0.2 \,\text{V}$ , which provides  $V_{inv} = 0.33 \,\text{V}$ . Observe that, in that case, for  $V_{\rm DD}$  values of 0.4 and 0.5 V (i.e.,  $V_{\rm DD} > V_{\rm inv}$ ) their corresponding curves feature efficiencies of 0.24 and 0.17, respectively. However, for  $V_{\rm DD} = 0.2$ and 0.3 V, we have that  $V_{\rm DD} < V_{\rm inv}$  and, consequently, for those curves, the electron inversion layer is not formed yet and the subbands remain unpinned. For these  $V_{\rm DD}$  values, we report efficiencies of 0.48 and 0.4, respectively. Moreover, we notice that for very strong asymmetric configurations, gate efficiency tends to saturate to a value of 0.57. Impact of quantum confinement on limiting gate-to-gate efficiencies below 1 has been discussed in Ref. 18 and more recently in Ref. 19.

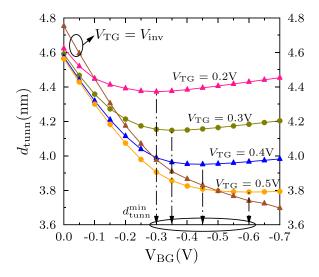

Once we established that growing asymmetric layouts feature increasing efficiencies for low operating voltages,

FIG. 3. Dependence of minimum vertical BTBT distances,  $d_{\rm tunn}$ , on  $V_{\rm BG}$  for  $V_{\rm TG} = V_{\rm DD} = 0.2$ , 0.3, 0.4, and 0.5 V.  $V_{\rm DS}$  is fixed to 0.3 V in all cases. For each top gate bias, there exists an optimized value of  $V_{\rm BG}$  that minimizes  $d_{\rm tunn}$ . Notice that all  $d_{\rm tunn}^{\rm min}$  verify that  $V_{\rm TG} < V_{\rm inv}$ .

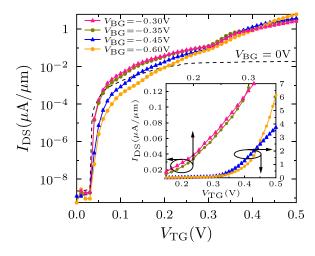

FIG. 4.  $I_{\rm DS}-V_{\rm TG}$  curves for every operating voltage corresponding to the different optimized  $V_{\rm BG}$  values. Switching behavior is gradually degraded for increasing degrees of asymmetry. Dashed line stands for the transfer characteristic when no bottom bias is applied.  $V_{\rm DS}$  is fixed to 0.3 V.

one important question arises: is there a privileged degree of asymmetry for a given  $V_{TG} = V_{DD}$  so that its minimum tunneling distance could be optimized? The answer turns out to be positive and indeed a favored asymmetric setup can be found for a chosen  $V_{\rm DD}$ . In Fig. 3, we show the evolution of  $d_{\text{tunn}}$  as we increase (in negative terms)  $V_{\text{BG}}$ . Notice how for each fixed value of  $V_{TG}$ ,  $d_{tunn}$  presents a minimum which, in turn, matches with an asymmetric configuration where  $V_{TG}$ lies below  $V_{\rm inv}$ . This means that the optimized asymmetries correspond to configurations of the HG-EHBTFET where, instead of a mostly symmetric electron-hole bilayer structure, electron concentrations at the top of the channel are reduced giving rise to a more properly named pseudo-bilayer structure. Notice that the increasing behavior of  $d_{tunn}$ observed at the right side of Fig. 3 is due to the switching from triangular band profiles to more rounded ones taking place at the bottom of the channel as a result of the hole strong inversion induced by high  $|V_{BG}|$  values.

The transfer characteristics for  $V_{\rm DD} = 0.2$ , 0.3, 0.4, and 0.5 V at the optimized bottom biases of Fig. 3 are shown in Fig. 4. In each case,  $V_{\rm BG}$  could be absorbed into the corresponding bottom gate workfunctions,  $\phi_{\rm bg,ul}$  and  $\phi_{\rm bg,ol}$ , so that its value could be readjusted to 0 V. For the sake of comparison, we have also included the transfer characteristic when no asymmetry is applied showing that considerably lower current levels are attained in that case.

Table I summarizes the optimized setup for each  $V_{\rm DD}$ . Electron and hole concentrations correspond to the maximum densities obtained along the  $\overline{AB}$  cut of Fig. 1(a). It can be noted that, consistently, the closer  $V_{\rm TG}$  is to its

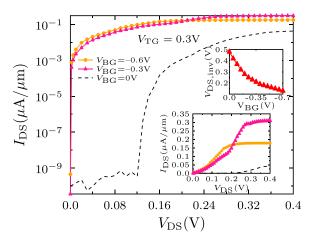

FIG. 5.  $I_{\rm DS}-V_{\rm DS}$  curves at fixed  $V_{\rm TG}=0.3\,\rm V$  for the configurations corresponding to  $V_{\rm BG}=0,\,-0.3$ , and  $-0.6\,\rm V$ . Bottom inset illustrates the transition between superlinear regime and saturation, whereas top inset shows the values of  $V_{\rm DS}$  at which the electron inversion layer is formed.

corresponding  $V_{\rm inv}$ , the higher the maximum electron concentration proves to be. In any case, for  $V_{\rm TG} = V_{\rm DD} = 0.5~\rm V$ , the maximum concentration for electrons remains still more than one decade below that for holes.  ${\rm SS}_{\rm pt}$  is calculated at  $V_{\rm TG,align}$ ; and  ${\rm SS}_{\rm av}$  is taken from  $V_{\rm TG,align}$  to  $V_{\rm TG} = V_{\rm DD}$ . Notice that these SS values have been obtained assuming perfectly sharp band edges and not accounting for a potential finite DOS distribution extending into the forbidden gap. More realistic treatments taking this into account would be expected to degrade to a certain extent the values shown in Table I.

Finally, for the sake of completeness, it is interesting to show the impact of some of these asymmetries on the output characteristics of the device. In Fig. 5, we depict the aspect of the  $I_{DS} - V_{DS}$  curves for the layouts with  $V_{BG} = 0$ , -0.3and  $-0.6\,\mathrm{V}$  corresponding, respectively, to the nonoptimized case and to the cases described by the first and last rows of Table I. All the curves were obtained taking  $V_{\rm TG} = 0.3$  V. For the two cases with  $V_{\rm BG} = -0.3$  and -0.6 V, the curves indicate that subband alignment had been already attained for  $V_{DS} = 0 \text{ V}$ ; whereas for  $V_{BG} = 0 \text{ V}$ , subbands align at  $V_{\rm DS} = 0.12 \, \rm V$ . Inspecting the shape of the curves in linear scale (see bottom inset), we confirm the expected transition between a superlinear regime and a saturation region.<sup>24</sup> Top inset displays the behavior of the drain voltage required to form the electron inversion layer,  $V_{DS,inv}$ , as a function of  $V_{\rm BG}$ . Both trends, the one shown in the top inset of Fig. 5 and that reported in the inset of Fig. 2, are consistent. The reason is simple. If the formation of the electron inversion layer depends on the voltage difference between the top gate and the drain; then, whatever the impact that a

TABLE I. Optimized bottom gate biases and resulting values for  $V_{\rm TG} = V_{\rm DD} = 0.2, 0.3, 0.4, \text{ and } 0.5 \text{ V}$  with  $V_{\rm TG,align} = 0.04 \text{ V}$  in the Ge HG-EHBTFET.

| $V_{\mathrm{DD}}\left(\mathbf{V}\right)$ | $V_{\mathrm{BG}}\left(\mathbf{V}\right)$ | $\phi_{ m tg,ol}({ m eV})$ | $V_{\mathrm{inv}}\left(\mathbf{V}\right)$ | $d_{\mathrm{tunn}}^{\mathrm{min}}(\mathrm{nm})$ | Electron concentration (cm <sup>-3</sup> ) | Hole concentration (cm <sup>-3</sup> ) | SS <sub>pt</sub> (mV/dec) | SS <sub>av</sub> (mV/dec) |

|------------------------------------------|------------------------------------------|----------------------------|-------------------------------------------|-------------------------------------------------|--------------------------------------------|----------------------------------------|---------------------------|---------------------------|

| 0.2                                      | -0.3                                     | 3.30                       | 0.41                                      | 4.37                                            | $1.613 \times 10^{16}$                     | $8.159 \times 10^{18}$                 | 2.57                      | 26.83                     |

| 0.3                                      | -0.35                                    | 3.32                       | 0.44                                      | 4.15                                            | $1.071 \times 10^{17}$                     | $1.065 \times 10^{19}$                 | 2.58                      | 36.27                     |

| 0.4                                      | -0.45                                    | 3.35                       | 0.48                                      | 3.95                                            | $4.433 \times 10^{17}$                     | $2.036 \times 10^{19}$                 | 4.80                      | 44.86                     |

| 0.5                                      | -0.60                                    | 3.39                       | 0.54                                      | 3.79                                            | $1.284 \times 10^{18}$                     | $4.002 \times 10^{19}$                 | 5.45                      | 49.89                     |

negative ramping of  $V_{\rm BG}$  may have on one of these electrodes for triggering the formation of the inversion layer, it will entail the opposite effect on the other, provided that each time we keep fixed the bias of the electrode not being analyzed.

In this work, we have shown that for low operating voltages in the heterogate germanium electron-hole bilayer tunnel field-effect transistor, there exists an optimal asymmetric configuration that: (i) enhances the gate electrostatic control over the channel, keeping the gate efficiency very high (close to the saturation value) for the whole  $V_{\rm TG}$  ramping and (ii) minimizes the lowest tunneling distance at the ON-state. We have demonstrated that these optimized asymmetric layouts feature pseudo-bilayer structures of electrons and holes in which the maximum electron concentrations turn out to be around two decades lower than their hole counterparts. The effect of these optimized asymmetries on the output characteristics of the device has been also elucidated.

The research leading to these results has received funding from the European Community's Seventh Framework Programme under Grant Agreement No. 619509 (Project E2-Switch). Jose L. Padilla acknowledges a postdoctoral fellowship from the Ramón Areces Foundation.

- R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, IEEE Tech. Dig. -Int. Electron Devices Meet. **2011**, 33.6.1–33.6.4.

- <sup>6</sup>L. De Michielis, L. Lattanzio, P. Palestri, L. Selmi, and A. M. Ionescu, in *Proceedings of 69th Annual IEEE Device Research Conference* (2011), pp. 111–112.

- <sup>7</sup>Y. Lu, G. Zhou, R. Li, Q. Liu, Q. Zhang, T. Vasen, S. D. Chae, T. Kosel, M. Wistey, H. Xing, A. Seabaugh, and P. Fay, IEEE Electron Device Lett. 33, 655 (2012).

- <sup>8</sup>I. A. Fischer, A. S. M. Bakibillah, M. Golve, D. Hahnel, H. Isemann, A. Kottantharayil, M. Oehme, and J. Schulze, IEEE Electron Device Lett. **34**, 154 (2013).

- <sup>9</sup>K.-H. Kao, A. S. Verhulst, W. G. Vandenberghe, B. Sorée, G. Groeseneken, and K. D. Meyer, IEEE Trans. Electron Devices **59**, 292 (2012).

- <sup>10</sup>M. Schmidt, A. Schäfer, R. A. Minamisawa, D. Buca, S. Trellenkamp, J. M. Hartmann, Q. T. Zhao, and S. Mantl, IEEE Electron Device Lett. 35, 699 (2014).

- <sup>11</sup>S. Agarwal and E. Yablonovitch, in *Proceedings of 69th Annual IEEE Device Research Conference* (2011), pp. 199–200.

- <sup>12</sup>L. Lattanzio, L. De Michielis, and A. M. Ionescu, IEEE Electron Device Lett. 33, 167 (2012).

- <sup>13</sup>J. L. Padilla, C. Alper, F. Gamiz, and A. M. Ionescu, Appl. Phys. Lett. 105, 082108 (2014).

- <sup>14</sup>W. Vandenberghe, B. Soree, W. Magnus, G. Groeseneken, and M. Fischetti, Appl. Phys. Lett. 98, 143503 (2011).

- <sup>15</sup>J. L. Padilla, F. Gamiz, and A. Godoy, IEEE Electron Device Lett. 33, 1342 (2012).

- <sup>16</sup>A. M. Walke, A. S. Verhulst, A. Vandooren, D. Verreck, E. Simoen, V. R. Rao, G. Groeseneken, N. Collaert, and A. V. Y. Thean, IEEE Trans. Electron Devices 60, 4057 (2013).

- <sup>17</sup>C. Alper, L. Lattanzio, L. De Michielis, P. Palestri, L. Selmi, and A. Ionescu, IEEE Trans. Electron Devices 60, 2754 (2013).

- <sup>18</sup>J. T. Teherani, S. Agarwal, E. Yablonovitch, J. L. Hoyt, and D. A. Antoniadis, IEEE Electron Device Lett. 34, 298 (2013).

- <sup>19</sup>S. Agarwal, J. T. Teherani, J. L. Hoyt, D. A. Antoniadis, and E. Yablonovitch, IEEE Trans. Electron Devices 61, 1599 (2014).

- <sup>20</sup>J. L. Padilla, F. Gamiz, and A. Godoy, IEEE Trans. Electron Devices 59, 3205 (2012).

- <sup>21</sup>Silvaco, ATLAS Users Manual (November 2014).

- <sup>22</sup>Synopsys, Sentaurus Device Tool Manual (September 2014).

- <sup>23</sup>G. B. Beneventi, E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, IEEE Trans. Electron Devices 62, 44 (2015).

- <sup>24</sup>L. De Michielis, L. Lattanzio, and A. M. Ionescu, IEEE Electron Device Lett. 33, 1523 (2012).

<sup>&</sup>lt;sup>1</sup>A. C. Seabaugh and Q. Zhang, Proc. IEEE **98**, 2095 (2010).

<sup>&</sup>lt;sup>2</sup>T. Nirschl, P.-F. Wang, C. Webe, J. Sedlmeir, R. Heinrich, R. Kakoschke, K. Schrufer, J. Holz, C. Pacha, T. Schulz, M. Ostermayr, A. Olbrich, G. Georgakos, E. Ruderer, W. Hansch, and D. Schmitt-Landsiedel, IEEE Tech. Dig. -Int. Electron Devices Meet. 2004, 195–198.

<sup>&</sup>lt;sup>3</sup>R. Asra, M. Shrivastava, K. V. R. M. Murali, R. K. Pandey, H. Gossner, and V. R. Rao, IEEE Trans. Electron Devices **58**, 1855 (2011).

<sup>&</sup>lt;sup>4</sup>R. Gandhi, Z. Chen, N. Singh, K. Banerjee, and S. Lee, IEEE Electron Device Lett. **32**, 437 (2011).

<sup>&</sup>lt;sup>5</sup>G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P. Oakey,