### Analysis and optimization of dynamic dataflow programs

THÈSE Nº 6663 (2015)

PRÉSENTÉE LE 8 JUIN 2015 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR GROUPE SCI STI MM PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

#### Simone CASALE BRUNET

acceptée sur proposition du jury:

Dr J.-M. Vesin, président du jury Dr M. Mattavelli, directeur de thèse Prof. J. Castrillon, rapporteur Prof. N. Zufferey, rapporteur Prof. A. P. Burg, rapporteur

#### This thesis is dedicated to the loving memory of my younger brother Edo

Multas per gentes et multa per aequora uectus Advenio has miseras, frater, ad inferias, Vt te postremo donarem munere mortis Et mutam nequiquam adloquerer cinerem, Quandoquidem fortuna mihi tete abstulit ipsum, Heu miser indigne frater adempte mihi. Nunc tamen interea haec, prisco quae more parentum Tradita sunt tristi munere ad inferias, Accipe fraterno multum manantia fletu Atque in perpetuum, frater, aue atque uale. — Catullus (Carmi, CI. Ad inferias)

## Acknowledgements

First of all, I would like to express my deepest sense of gratitude to my supervisor, Dr. Marco Mattavelli, who offered his continuous advice and encouragement throughout the course of this thesis.

I would also like to express my very sincere gratitude to Dr. Jorn W. Janneck, from the Lund University, for his support and systematic guidance to this thesis. Special thanks to Prof. Massimo Canale, from the Politecnico di Torino, who encouraged me to pursue the vision to become a PhD.

The work presented in this thesis was partly supported by the Fonds National Suisse pour la Recherche Scientifique under grant 200021.138214. This support is gratefully acknowledged.

I am thankful to all lab colleagues. A very special thanks to Endri Bezati for his precious friendship and technical assistance to my project. I also take this opportunity to express my gratitude to my friends Christian and Nicoletta, Giacomo, Aurora and Tia, Lucianone, Marco, Martina, Rinaldo and Jenny, Renato and Sandra.

A very special and warm thanks with my profound gratitude to Jessica, who loved and supported me during the writing of my dissertation. She made me feel like everything was possible and incredible. I love you  $\infty^{\infty}$  Principessinadellafavolapiùbella  $\heartsuit$

I thank my parents, Patrizia and Andrea, who have always given me the strength and wisdom to be sincere in my work, for setting high moral standards and supporting me through their hard work, and for their unselfish love and affection.

Lausanne, 8 May 2015

Simone Casale Brunet

### Abstract

All computing platforms, from mobile to supercomputers, are becoming more and more heterogeneous and massively parallel. While they can provide higher power efficiency and computation throughput, effective and confident use of these systems always requires knowledge about low-level programming. The average time necessary to develop and optimize a design on heterogeneous platforms is higher and higher compared to typical homogeneous systems. Dataflow models of computation (MoC) are quickly becoming the common practice in heterogeneous systems development. In domains such as signal processing and multimedia communication, dataflow MoCs have become accepted as standard. However, the shift from a sequential and architecture-specific MoC to a dataflow MoC still uncovers several programming and development challenges. The Cal Actor Language (CAL) is a recently-specified dataflow and actor-based language capable of concisely expressing complex and general purpose parallel applications. However, design tools supporting this language are generally not adequate to fully exploit its features and expressiveness power. In fact, they generally restrict its MoC in order to reduce the design space exploration (DSE) effort. The objective of this thesis is to provide a DSE methodology where all the features of CAL and dynamic dataflow MoCs can be exploited in a more general and effective manner. This dissertation illustrates a novel profiling, analysis and performance estimation methodology for the DSE of dynamic dataflow programs. The main research contributions of this thesis are: the formalization of a graph-based representation of the program execution called an execution trace graph (ETG); the formalization of a systematic methodology for profiling generic dynamic dataflow programs through their code interpretation; the formalization of a complete DSE methodology for dynamic dataflow programs in order to efficiently identify close-to-optimal design points according to various and tailored performance merit functions. In particular, the following design space optimization problems for dynamic dataflow programs are addressed: the analysis of the hotspots and the algorithmic bottlenecks of a parallel program; the bounding and optimization of the buffer size configuration for complex designs; the dynamic power dissipation minimization of programs implemented in multi-clock domain architecture. Furthermore, theoretical concepts like the design space critical path and the potential speedup of a dataflow application have been defined and revisited, respectively. The thesis also presents a DSE framework developed in order to demonstrate the effectiveness of this design methodology.

Key words: dynamic dataflow, design space exploration, heterogeneous computing, CAL

## Résumé

De nos jours, des mobiles aux super-ordinateurs, toutes les plates-formes informatiques deviennent de plus en plus hétérogènes et massivement parallèles ce qui les rend très efficaces en termes de puissance et de calcul. Pour obtenir une très bonne utilisation de ces systèmes, il est nécessaire d'avoir toujours plus de connaissances de programmation bas niveau. De plus, le temps moyen nécessaire pour développer et optimiser ce type de système est de plus en plus élevé par rapport aux systèmes typiquement séquentiels. Les modèles de calcul flux de données deviennent rapidement la pratique la plus courante dans le développement des systèmes hétérogènes. Dans des domaines, tels que le traitement du signal et le multimédia, ces modèles de calcul flux de données sont devenus un standard largement accepté. Cependant, le passage d'une méthode séquentielle et spécifique à l'architecture à une méthode flux de données, montre que plusieurs défis de programmation et de développement sont encore à découvrir. Pour répondre à ce passage, un langage de programmation flux de données, récemment spécifié, a été développé. Ce langage, appelé Cal Actor Language (CAL), est capable d'exprimer de manière concise des applications parallèles complexes avec un formalisme simple et générique. Malgré cela, les outils de conception basés sur ce langage ne sont généralement pas suffisants pour exploiter entièrement toutes ses caractéristiques, surtout sa puissance d'expression. En général, les outils actuellement disponibles limitent énormément son modèle de calcul afin de réduire l'effort de l'exploration de l'espace de conception. L'objectif de cette thèse est donc de fournir une méthodologie d'exploration de l'espace de conception où toutes les fonctionnalités du CAL et de son modèle de calcul peuvent être exploitées d'une manière plus générale et plus efficace. Elle démontre aussi une nouvelle méthodologie d'estimation et d'analyse des performances pour les applications flux de données dynamiques. Les principales contributions à la recherche de cette thèse sont: la formalisation d'une représentation de l'exécution du programme basée sur la théorie des graphes et appelée "graphe de trace d'exécution"; la formalisation d'une méthodologie systématique pour le profilage des programmes flux de données dynamiques génériques à travers l'interprétation de haut niveau de leur code source; la formalisation d'une méthodologie complète de l'exploration de l'espace de conception pour des programmes flux de données dynamiques. En outre, les problèmes d'optimisation de l'espace de conception du design pour les programmes flux de données dynamiques abordés sont: l'analyse des goulets d'étranglement algorithmiques d'un programme; la sélection et l'optimisation de la configuration de la taille de mémoire pour des applications complexes; la minimisation de la dissipation de puissance dynamique des programmes mis en œuvre dans une architec-

#### Résumé

ture multi-horloges. De plus, les concepts théoriques comme l'espace du chemin critique et l'accélération potentielle d'une application flux de données ont été respectivement définis et revisités. La thèse présente, également, un logiciel d'exploration de l'espace de conception développé afin de démontrer l'efficacité de cette méthode.

Mots clefs: flux de données, exploration de l'espace du design, computation parallèle, platesformes hétérogènes, CAL

| Acknowledgements |          |                                                                                               |  |  |  |

|------------------|----------|-----------------------------------------------------------------------------------------------|--|--|--|

| Ab               | Abstract |                                                                                               |  |  |  |

| Ré               | ésum     | é v                                                                                           |  |  |  |

| Li               | stof     | symbols xiii                                                                                  |  |  |  |

| Li               | st of t  | figures xix                                                                                   |  |  |  |

| Li               | st of    | tables xxiii                                                                                  |  |  |  |

| Li               | st of ]  | listings xxv                                                                                  |  |  |  |

| Li               | stof     | algorithms xxvii                                                                              |  |  |  |

| 1                | Intr     | oduction 1                                                                                    |  |  |  |

|                  | 1.1      | Heterogeneous systems development   1                                                         |  |  |  |

|                  |          | 1.1.1       Requirements for effective design development       3                             |  |  |  |

|                  |          | 1.1.2 Models of computation       3                                                           |  |  |  |

|                  |          | 1.1.2       Notes of computation       3         1.1.3       Design space exploration       4 |  |  |  |

|                  | 1.2      | Motivation of this thesis                                                                     |  |  |  |

|                  | 1.2      | System development design flow                                                                |  |  |  |

|                  | 1.3      | Research contributions of this thesis                                                         |  |  |  |

|                  | 1.4      | Thesis organization   9                                                                       |  |  |  |

| _                |          |                                                                                               |  |  |  |

| 2                | Dat      | aflow programming 11                                                                          |  |  |  |

|                  | 2.1      | Dataflow programs                                                                             |  |  |  |

|                  |          | 2.1.1         Kahn process networks         12                                                |  |  |  |

|                  |          | 2.1.2Dataflow process networks13                                                              |  |  |  |

|                  |          | 2.1.3 Actor transition systems                                                                |  |  |  |

|                  | 2.2      | Dataflow paradigm16                                                                           |  |  |  |

|                  |          | 2.2.1 Modular programming                                                                     |  |  |  |

|                  |          | 2.2.2 Parallelism flavors         16                                                          |  |  |  |

|                  | 2.3      | Dataflow classes                                                                              |  |  |  |

2.3.1 Static dataflow programs .....

18

|   |            | 2.3.2          | Cyclo-static dataflow programs                  | 21        |

|---|------------|----------------|-------------------------------------------------|-----------|

|   |            | 2.3.3          | Dynamic dataflow programs                       | 22        |

|   | 2.4        | Code i         | interpretation and generation                   | 22        |

|   |            | 2.4.1          | Abstract syntax tree                            | 23        |

|   |            | 2.4.2          | Intermediate representation                     | 23        |

|   |            | 2.4.3          | Control flow graph                              | 23        |

|   | 2.5        | The Ca         | al Actor Language                               | 24        |

|   |            | 2.5.1          | CAL program                                     | 25        |

|   |            | 2.5.2          | Execution model                                 | 25        |

|   |            | 2.5.3          | CAL syntax and semantics                        | 26        |

|   |            | 2.5.4          | An example of a CAL program                     | 30        |

|   |            | 2.5.5          | RVC-CAL                                         | 32        |

|   |            | 2.5.6          | Compiler infrastructure                         | 32        |

|   | 2.6        | Concl          | usions                                          | 33        |

| n | Dread      | 6lina C        |                                                 | 35        |

| 3 | <b>Pro</b> | -              | AL programs<br>classification                   | <b>35</b> |

|   | 3.2        |                | analysis                                        | 35<br>36  |

|   | 3.2        | 3.2.1          | Source lines of code                            | 36        |

|   |            | 3.2.1          |                                                 | 30<br>37  |

|   |            | 3.2.2<br>3.2.3 | Operators count                                 | 37<br>37  |

|   |            | 3.2.3<br>3.2.4 | Halstead metrics                                | 39        |

|   | 3.3        |                |                                                 | 39<br>40  |

|   | 3.3        |                | dependent analysis                              |           |

|   |            | 3.3.1          | Computational load                              | 41        |

|   | 2.4        | 3.3.2          | Data-transfers and storage load                 | 41<br>42  |

|   | 3.4        | Conci          | usions                                          | 42        |

| 4 | Exp        | loring         | the design space of dataflow programs           | 43        |

|   | 4.1        | Ortho          | gonalization of concerns                        | 43        |

|   |            | 4.1.1          | Model of computation                            | 44        |

|   |            | 4.1.2          | Model of architecture                           | 44        |

|   |            | 4.1.3          | Mapping                                         | 45        |

|   | 4.2        | The de         | esign space of a dataflow program               | 45        |

|   |            | 4.2.1          | Design space and design points                  | 46        |

|   |            | 4.2.2          | Exploration methods                             | 48        |

|   |            | 4.2.3          | Performance estimation                          | 49        |

|   | 4.3        | Relate         | d work                                          | 49        |

|   | 4.4        | Advan          | ces in design space exploration of CAL programs | 54        |

|   |            | 4.4.1          | Space for improvement                           | 54        |

|   |            | 4.4.2          | New requirements                                | 54        |

|   | 4.5        | Concl          | usions                                          | 55        |

| 5 | Exe | ution trace graph 57                                                                                             |

|---|-----|------------------------------------------------------------------------------------------------------------------|

|   | 5.1 | Geometry of execution                                                                                            |

|   |     | 5.1.1 Partially-ordered space 57                                                                                 |

|   |     | 5.1.2 Execution trace                                                                                            |

|   |     | 5.1.3 Execution trace space                                                                                      |

|   | 5.2 | Execution trace graph 59                                                                                         |

|   |     | 5.2.1 Firings                                                                                                    |

|   |     | 5.2.2 Dependencies                                                                                               |

|   |     | 5.2.3 Example of an execution trace graph                                                                        |

|   | 5.3 | $Properties  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    |

|   |     | 5.3.1 Topological order $\ldots$ 66                                                                              |

|   |     | 5.3.2 Mapping independence $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $66$ |

|   |     | 5.3.3 Untimed                                                                                                    |

|   |     | 5.3.4 Maximum parallelism                                                                                        |

|   |     | 5.3.5 Data dependent                                                                                             |

|   |     | 5.3.6 Modeling a dynamic program execution                                                                       |

|   | 5.4 | Timed execution trace graph    74                                                                                |

|   |     | 5.4.1 Firing weight                                                                                              |

|   |     | 5.4.2 Dependency weight                                                                                          |

|   | 5.5 | Transformations                                                                                                  |

|   |     | 5.5.1 Firing expansion                                                                                           |

|   |     | 5.5.2 Dependency amalgamation                                                                                    |

|   |     | 5.5.3 Event-driven system representation                                                                         |

|   | 5.6 | Conclusions                                                                                                      |

| 6 | TUI | NUS: a design space exploration environment for CAL programs 85                                                  |

|   | 6.1 | Design flow features and capabilities    85                                                                      |

|   |     | 6.1.1 Profiler                                                                                                   |

|   |     | 6.1.2 Execution trace graph post-mortem scheduling and analysis 86                                               |

|   | 6.2 | High-level models                                                                                                |

|   |     | 6.2.1 CAL dataflow program                                                                                       |

|   |     | 6.2.2 Architecture and constraints                                                                               |

|   |     | 6.2.3 Execution trace graph                                                                                      |

|   |     | 6.2.4 Profiling information                                                                                      |

|   | 6.3 | Integration with third-party CAL dataflow environments                                                           |

|   | 6.4 | Conclusions                                                                                                      |

| 7 | Pro | ling CAL programs with TURNUS 105                                                                                |

|   | 7.1 | Advances in profiling CAL programs                                                                               |

|   | 7.2 | Data collection                                                                                                  |

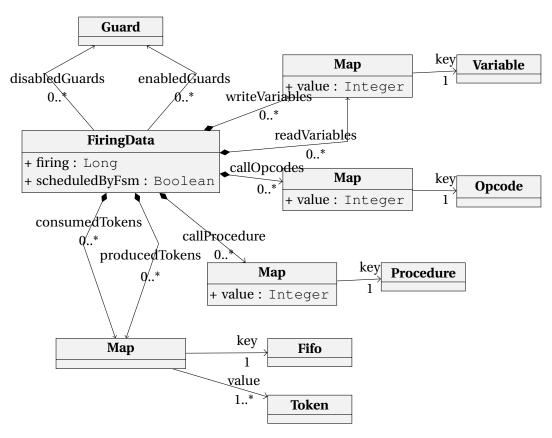

|   |     | 7.2.1 Firing data                                                                                                |

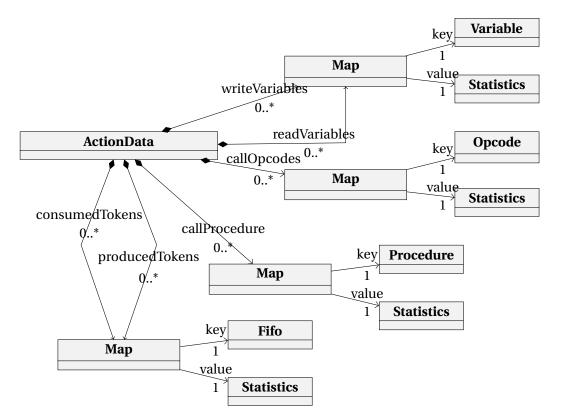

|   |     | 7.2.2 Action data                                                                                                |

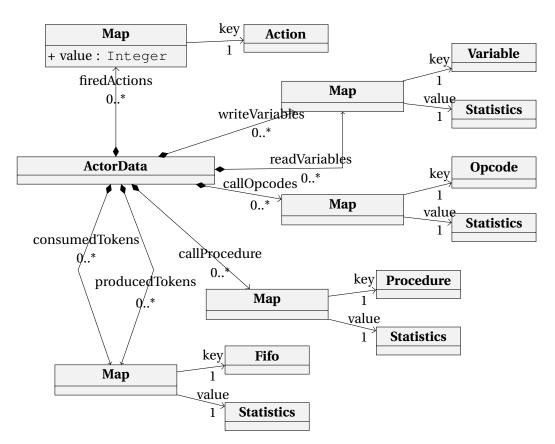

|   |     | 7.2.3 Actor data                                                                                                 |

|   |     | 7.2.4 Buffer data                                                          | 12 |

|---|-----|----------------------------------------------------------------------------|----|

|   |     | 7.2.5 Statistical data                                                     | 14 |

|   |     | 7.2.6 Profiled token                                                       | 14 |

|   | 7.3 | Building of the execution trace graph 1                                    | 15 |

|   | 7.4 | Application programming interface 1                                        | 16 |

|   | 7.5 | Conclusions                                                                | 17 |

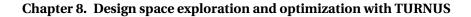

| 8 | Des | gn space exploration and optimization with TURNUS 11                       | 19 |

|   | 8.1 | Performance estimation                                                     | 19 |

|   |     | 8.1.1 Post-mortem scheduler models                                         | 20 |

|   |     | 8.1.2 Execution trace graph post-mortem scheduling                         | 23 |

|   |     | 8.1.3 Execution statistics                                                 | 26 |

|   |     | 8.1.4 Analysis of a collection of execution trace graphs 12                | 26 |

|   | 8.2 | Design space critical path                                                 | 26 |

|   |     | 8.2.1 Critical path length                                                 | 27 |

|   |     | 8.2.2 Algorithmic critical path                                            | 31 |

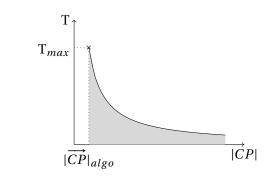

|   |     | 8.2.3 Throughput and design space critical path                            | 32 |

|   |     | 8.2.4 Potential speedup                                                    | 32 |

|   | 8.3 | Hotspot analysis                                                           | 35 |

|   |     | 8.3.1 Critical actions ranking 13                                          | 35 |

|   |     | 8.3.2 Impact analysis                                                      | 36 |

|   | 8.4 | Buffer size dimensioning 13                                                | 38 |

|   |     | 8.4.1 Related work                                                         | 38 |

|   |     | 8.4.2 Deadlock and feasible regions 13                                     | 39 |

|   |     | 8.4.3 Minimization by the use of a model predictive control approach 13    | 39 |

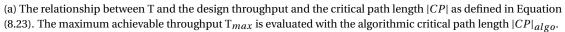

|   |     | 8.4.4 Optimization by the exploration of the design space critical path 14 | 42 |

|   | 8.5 | Dynamic power dissipation minimization 14                                  | 45 |

|   |     | 8.5.1 Related work                                                         | 47 |

|   |     | 8.5.2 Multi-clock domain partitioning                                      | 48 |

|   |     | 8.5.3 Linear programming formulation 14                                    | 48 |

|   |     | 8.5.4 Heuristic approach                                                   | 49 |

|   | 8.6 | Conclusions                                                                | 50 |

| 9 | Exp | erimental results 15                                                       | 53 |

|   | 9.1 | Design cases                                                               | 53 |

|   |     | 9.1.1 JPEG decoder                                                         | 53 |

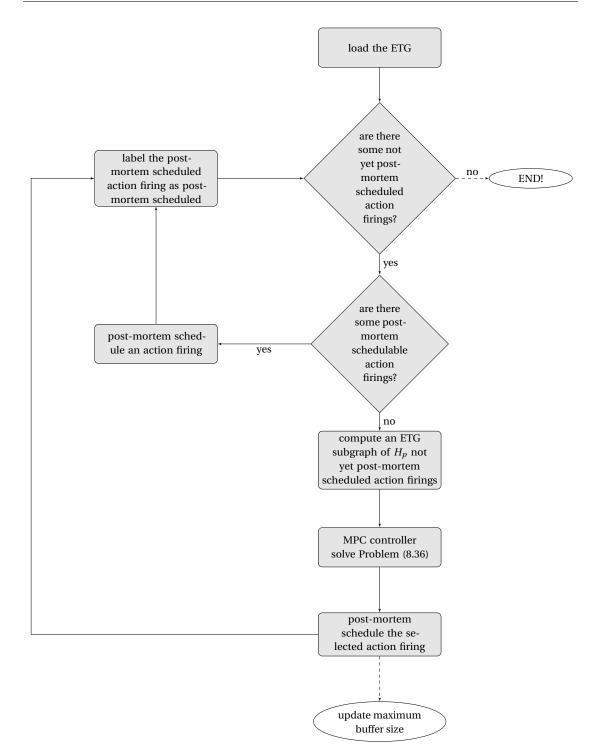

|   |     | 9.1.2 MPEG4-SP decoder                                                     | 54 |

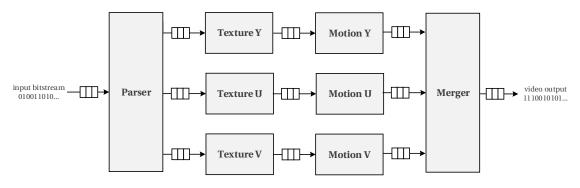

|   |     | 9.1.3 MPEG-HEVC decoder 1                                                  | 54 |

|   | 9.2 | CAL source code static and dynamic profiling 15                            | 54 |

|   |     |                                                                            | 55 |

|   |     | 9.2.2 Memory requirements and utilization                                  | 56 |

|   |     |                                                                            | 57 |

|   |     | 9.2.4 Initial design-refactoring directions                                | 57 |

|                | 9.3  | Design refactoring                                    | 161 |

|----------------|------|-------------------------------------------------------|-----|

|                |      | 9.3.1 Critical action ranking                         | 162 |

|                |      | 9.3.2 Impact analysis                                 | 163 |

|                | 9.4  | Bounded buffer size configuration                     | 164 |

|                | 9.5  | Buffer size optimization                              | 167 |

|                | 9.6  | Dynamic power dissipation minimization                | 169 |

|                | 9.7  | Conclusions                                           | 171 |

| 10             | Con  | clusions                                              | 173 |

|                | 10.1 | Future work                                           | 176 |

| A              | Disc | crete event system and simulation                     | 179 |

|                | A.1  | Petri nets                                            | 179 |

|                |      | A.1.1 State                                           | 180 |

|                |      | A.1.2 Transition firing                               | 180 |

|                | A.2  | Discrete event system specification                   | 181 |

|                |      | A.2.1 The atomic model                                | 181 |

| B              | Мос  | lel predictive control                                | 183 |

| С              | A CA | AL esoteric example                                   | 185 |

|                | C.1  | A Chef chocolate cake                                 | 185 |

|                | C.2  | From a sequential to a dataflow program specification | 187 |

|                | C.3  | The first CAL chocolate cake                          | 188 |

|                | C.4  | A dynamic refrigerator                                | 191 |

|                | C.5  | Design space exploration of a kitchen                 | 193 |

| Bibliography 2 |      |                                                       |     |

#### **Curriculum Vitae**

# List of Symbols

#### Acronyms

| AAM  | Algorithm architecture adequation matching |

|------|--------------------------------------------|

| ACP  | Algorithmic critical path                  |

| API  | Application programming interface          |

| ASIC | Application-specific integrated circuit    |

| ATM  | Actor transition system                    |

| CAL  | Cal Actor Language                         |

| CIF  | Common interchange format                  |

| СР   | Critical path                              |

| CPL  | Critical path length                       |

| CSDF | Cyclo-static dataflow program              |

| DAG  | Directed acyclic graph                     |

| DCT  | Discrete cosine transform                  |

| DDF  | Dynamic dataflow program                   |

| DPN  | Dataflow process network                   |

| DSCP | Design space critical path                 |

| DSE  | Design space exploration                   |

| ETG  | Execution trace graph                      |

| FID  | Firing identifier                          |

| FIFO | First in, first out                        |

| FNL  | Functional unit network language           |

|      |                                            |

| FPGA  | Field-programmable gate array                    |

|-------|--------------------------------------------------|

| GALS  | Globally asynchronous locally synchronous        |

| HEVC  | High efficiency video coding                     |

| HW    | Hardware                                         |

| IDCT  | Inverse DCT                                      |

| ILP   | Integer linear programming                       |

| IQ    | Inverse quantization                             |

| JPEG  | Joint photographic experts group                 |

| KPN   | Kahn process network                             |

| LP    | Linear programming                               |

| LTS   | Labeled transition systems                       |

| LUB   | Least upper bound                                |

| MCD   | Multiple-clock domain                            |

| MoA   | Model of architecture                            |

| MoC   | Model of computation                             |

| MPC   | Model predictive control                         |

| MPEG  | Moving picture experts group                     |

| MPSoC | Multiprocessor system on chip                    |

| NPM   | Native programming model                         |

| Orcc  | Open RVC-CAL compiler infrastructure             |

| PAPI  | Performance application programming interface    |

| PAPS  | Periodic admissible parallel schedule            |

| PASS  | Periodic admissible sequential schedule          |

| PiMM  | Parameterized and interfaced dataflow meta-model |

| PN    | Petri net                                        |

| QCIF  | Quarter CIF                                      |

| RMC   | Reconfigurable media coding                      |

| :     |                                                  |

xiv

- RTL Register-transfer level

- RVC Reconfigurable video coding

- S-LAM System-level architecture model

- SDF Static or synchronous dataflow program

- SoC System on chip

- SP Simple profile

- SW Software

- TETG Timed execution trace graph

- UML Unified modeling language

- VHDL VHSIC hardware description language

- VHSIC Very high speed integrated circuit

- VLSI Very large scale integration

- XDF XML dataflow format

- XML Extensible markup language

#### Operators

- [.]' The matrix transpose operator

- argmax(.) The argument of the maximum operator

- argmin(.) The argument of the minimum operator

- The amalgamation operator

- |.| The cardinality operator

- $||.||_n$  The n-norm operator

- $| \rightarrow |$  The directed path length operator

- max(.) The maximum value operator

- min(.) The minimum value operator

- $\oplus$  The concatenation operator

- $\rightarrow$  The directed path operator

- *E*[.] The expected value operator

| Var(.)                           | The variance operator                                                           |

|----------------------------------|---------------------------------------------------------------------------------|

| Variables                        |                                                                                 |

| $(X, \leq)$                      | A partially-ordered space, also called po-space                                 |

| (X, dX)                          | A directed topological space, also called d-space                               |

| $\beta \in C_{\beta}$            | A buffer size configuration                                                     |

| η                                | Action execution index                                                          |

| $\kappa \in K$                   | The CAL actor-classes                                                           |

| $\lambda \in \Lambda$            | The CAL action                                                                  |

| Λ                                | The set of CAL actions                                                          |

| $\Lambda_{CP} \subseteq \Lambda$ | The set of actions that have at least one action firing along the critical path |

| $ \overrightarrow{CP} $          | The critical path length                                                        |

| Î                                | The estimated design throughput                                                 |

| S( <i>n</i> )                    | The speedup of a program when executed in $n$ processing elements               |

| Т                                | The design throughput                                                           |

| $\mu$                            | Dependency kind                                                                 |

| $\overrightarrow{1} = [0,1]$     | The closed and directed unit interval                                           |

| $\overrightarrow{CP}$            | The critical path                                                               |

| $\overrightarrow{CP}_{algo}$     | The algorithmic critical path                                                   |

| $\overrightarrow{p}$             | A directed path, also called d-path                                             |

| $\perp$                          | The empty sequence                                                              |

| $\rho \in C_{\rho}$              | A partitioning configuration                                                    |

| $\sigma \in C_\sigma$            | A scheduling configuration                                                      |

| Θ                                | The set clock-accurate profiling information                                    |

| $a \in A$                        | The CAL actor                                                                   |

| Α                                | The set of CAL actors                                                           |

| $A_{CP} \subseteq A$             | The set of actors that have at least one action firing along the critical path  |

| В                                | The set of buffers of a dataflow program                                        |

| xvi                              |                                                                                 |

| $b_i \in B$ The i-th buffer of a dataflow program |

|---------------------------------------------------|

|---------------------------------------------------|

| $C_{\beta}$ | The set of buffer size configurations  |

|-------------|----------------------------------------|

| $\sim_D$    | The set of stanet since configurations |

- $C_{\rho}$  The set of partitioning configurations

- $C_{\sigma}$  The set of scheduling configurations

- D The ETG dependencies set

- *d* Dependency direction

- *D* The set of amalgamated dependencies

- $D_c \subseteq D$  The critical dependencies set

- $D_f \subseteq D$  The finite state machine dependencies set

- $D_g \subseteq D$  The guard dependencies set

- $D_p \subseteq D$  The port dependencies set

- $D_t \subseteq D$  The tokens dependencies set

- $D_v \subseteq D$  The internal variables dependencies set

- $D_{CP} \subseteq D_c$  The dependencies set along the critical path

- E(X, dX) The execution trace space

- $e_n^{\bullet} \in D^{\bullet}$  The n-th amalgamated dependency

$e_n = (s_i, s_j) \in D$  The n-th dependency of the ETG, with  $s_i$  and  $s_j$  source and target firings

G(PU, ME, L) The platform architecture model

- G(V, E) A generic graph with V and E the sets of vertexes and edges

- *K* The set of CAL actor-classes

$K_{CP} \subseteq K$  The set of actor-classes that have at least one action firing along the critical path

- *L* The set of links available on the architecture

- $l_i \in L$  The i-th link (i.e. interconnection between a processing element and a medium)

- *M* The set of mapping point

- *ME* The set of media of an architecture

- $me_i \in ME$  The i-th medium

*P* The set of Petri net places

| $p_i \in P$              | The i-th of Petri place                                             |

|--------------------------|---------------------------------------------------------------------|

| $P_{oldsymbol{arphi}^-}$ | The set of fictive Petri net places                                 |

| PU                       | The set of processing elements of an architecture                   |

| $pu_i \in PU$            | The i-th processing element                                         |

| S                        | The ETG action firings set                                          |

| $S_c \subseteq S$        | The critical action firings set                                     |

| $s_i \in S$              | The i-th firing of the ETG                                          |

| $S_{CP} \subseteq S_c$   | The action firings set along the critical path                      |

| Т                        | The set of Petri net transitions                                    |

| $t_i \in T$              | The i-th of Petri transition                                        |

| $w(s_i)$                 | Execution time (or time weight) required by action firing $s_i$     |

| $w(s_i,s_j)$             | Execution time (or time weight) required by dependency $(s_i, s_j)$ |

# List of Figures

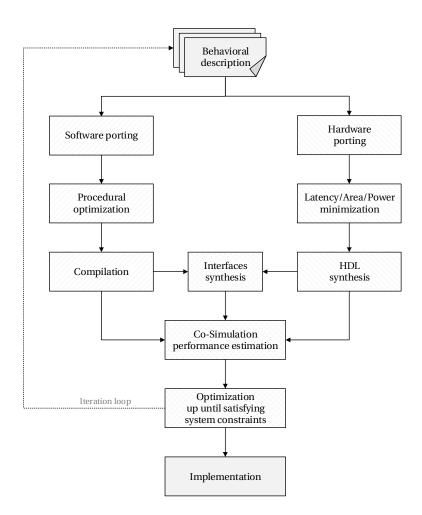

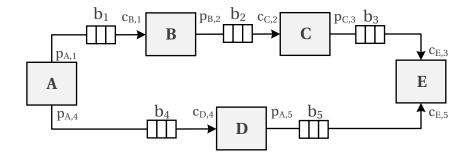

| 1.1  | Simplified typical design flow of a heterogeneous hardware and software system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

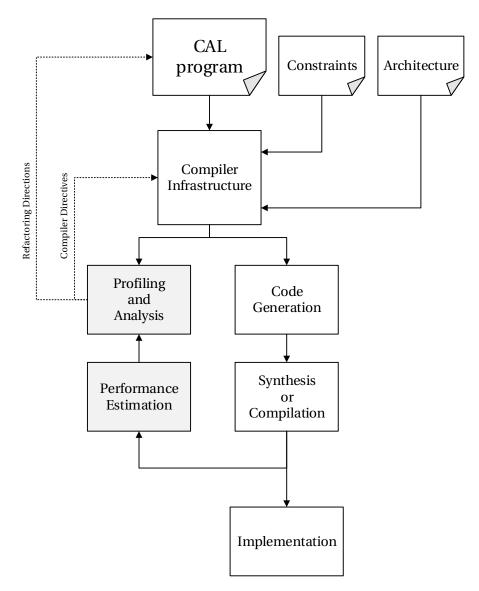

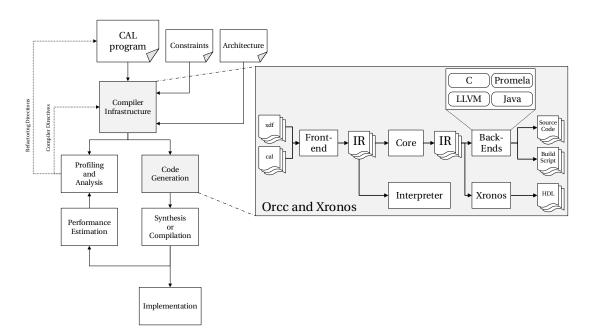

| 1.2  | Heterogeneous system development design flow for CAL dataflow programs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7  |

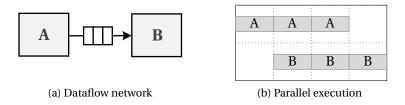

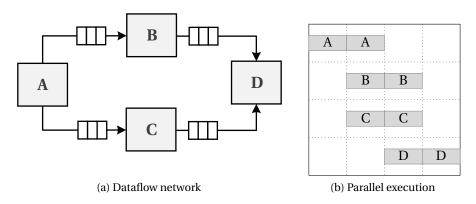

| 2.1  | Pipeline parallelism.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17 |

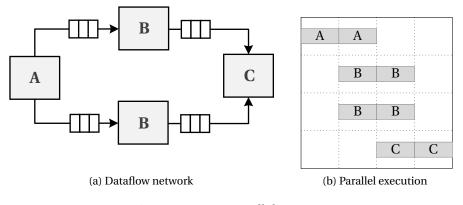

| 2.2  | Task parallelism.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17 |

| 2.3  | Data parallelism.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18 |

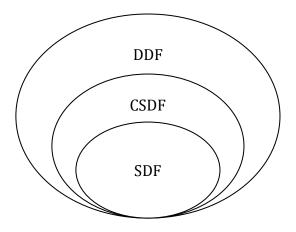

| 2.4  | Dataflow MoCs classes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18 |

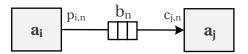

| 2.5  | A dataflow graph with two actors, $a_i$ and $a_j$ , connected through the buffer $b_n$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|      | $p_{i,n}$ defines the number of tokens produced on $b_n$ during each firing of $a_i$ . $c_{j,n}$ defines the number of tokens consumed from $b_n$ during each firing of $a_j$                                                                                                                                                                                                                                                                                                                                                                       | 19 |

| 2.6  | Dataflow graph example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

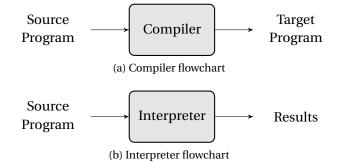

| 2.7  | Code compiler and interpreter flowcharts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 |

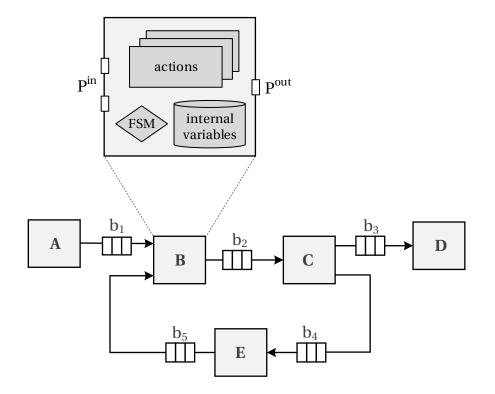

| 2.8  | CAL network and actors structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24 |

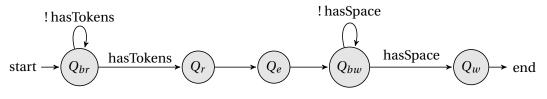

| 2.9  | Action execution model according to Equation 5.10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26 |

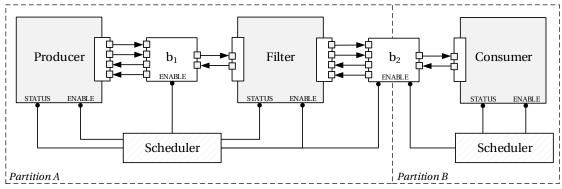

| 2.10 | Basic dataflow program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30 |

| 2.11 | The RVC-CAL compiler and Xronos infrastructure integrated in the design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | presented in Figure 1.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33 |

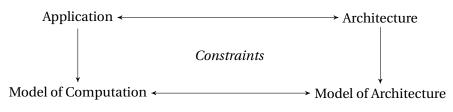

| 4.1  | Mapping from an application to an architecture. Constraints represent the                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | feasible regions of the design space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45 |

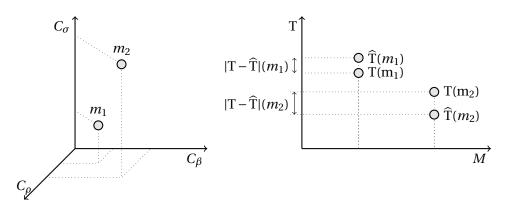

| 4.2  | The design space $M = C_{\rho} \times C_{\sigma} \times C_{\beta} = \{m_1, m_2,, m_{n_M}\}$ and the corresponding performance $T(m)$ and estimated performance $\hat{T}(m)$ .                                                                                                                                                                                                                                                                                                                                                                       | 46 |

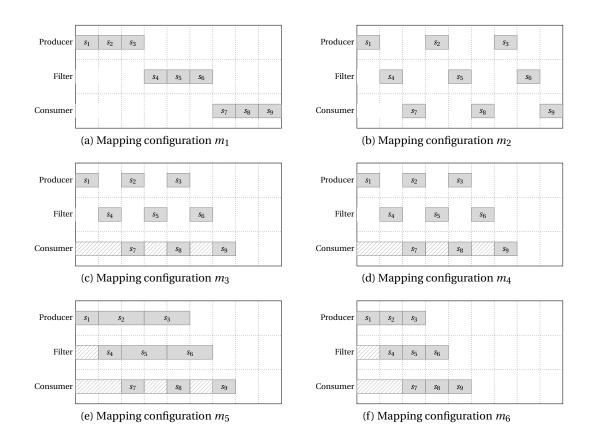

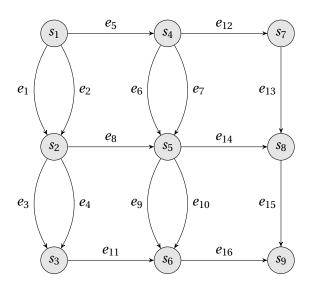

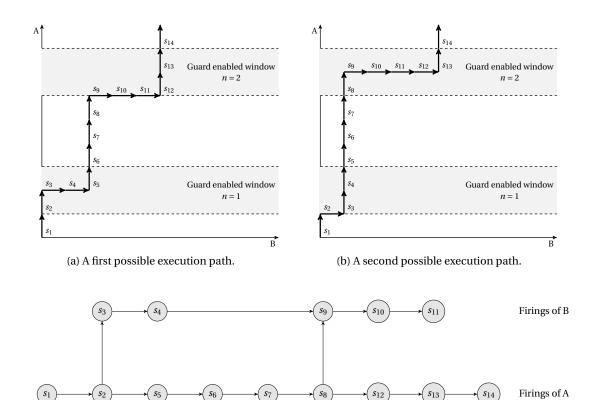

| 4.3  | Platform independent simulation of the CAL network depicted in Fig. 2.10 with the mapping configurations described in Table 4.1. The execution of each action is supposed to take at least one (abstract) clock cycle (when there are no blocking output buffers), the overhead introduced by the action selection and buffer access overheads are both neglected. In gray the actor execution with the corresponding action firing. In striped-gray the actor execution is postponed due to the unavailability of a token (i.e. blocking reading). | 47 |

| 5.1  | Execution space in $\mathbb{R}^2$ of two actors A and B mapped on two processing units $pu_1$ and $pu_2$ , respectively. The dashed arrow represents a possible execution path of the program.                                                                                                                                                                                                                                                                                                                                                      | 58 |

#### List of Figures

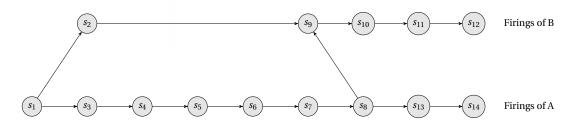

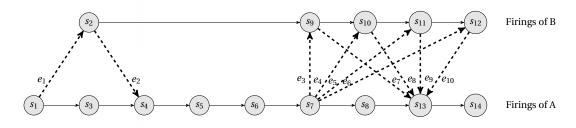

| 5.2  | Execution trace graph obtained after the execution of the CAL program de-<br>scribed in Section 2.5.4. The firing set <i>S</i> is summarized in Table 2.2, and the  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3  | dependencies set <i>D</i> is summarized in Table 5.2                                                                                                                |

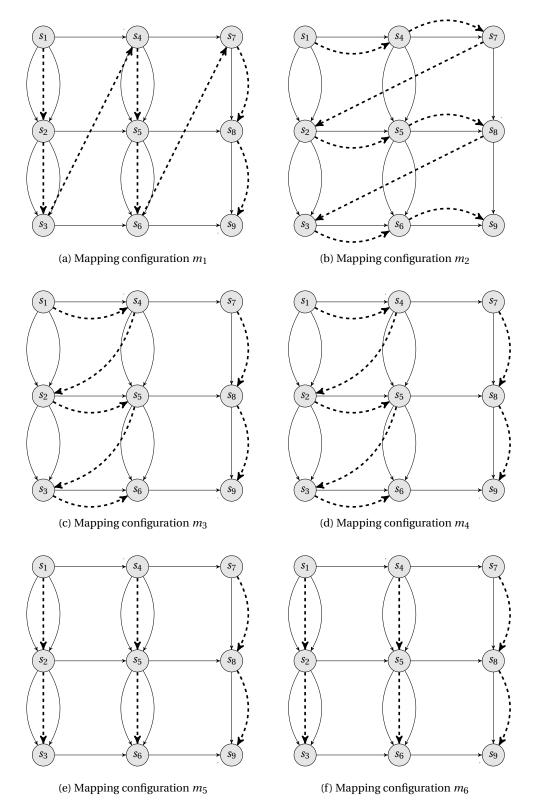

| 5.4  | defined within the mapping configurations described in Table 4.1                                                                                                    |

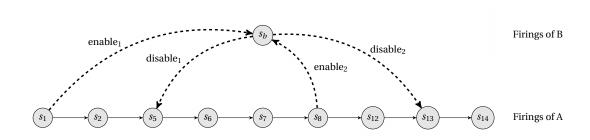

|      | the guard enable and disable dependencies                                                                                                                           |

| 5.5  | Guard enable and disable dependencies couples that model the guard enable windows $n = 1$ and $n = 2$ depicted in Figure 5.4. The firing $s_b$ represents a generic |

|      | firing of the action B.                                                                                                                                             |

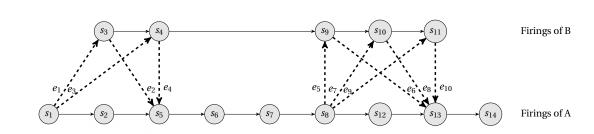

| 5.6  | The ETGs related to the execution paths depicted in Figure 5.4a and Figure                                                                                          |

|      | 5.4b where for each firing of $\ensuremath{\mathbb{B}}$ a couple of guard enable and disable has been                                                               |

|      | considered in order to model the guard enabled windows $n = 1$ and $n = 2$ 75                                                                                       |

| 5.7  | Firings expansion of an execution trace graph                                                                                                                       |

| 5.8  | Amalgamation of the execution trace graph illustrated in Figure 5.2 79                                                                                              |

| 5.9  | Petri net obtained from the execution trace graph depicted in Figure 5.2 82                                                                                         |

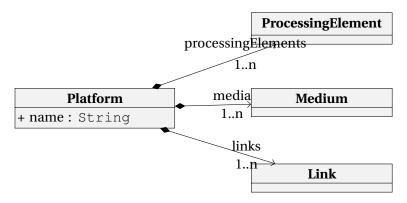

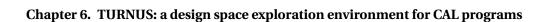

| 6.1  | TURNUS design flow.   87                                                                                                                                            |

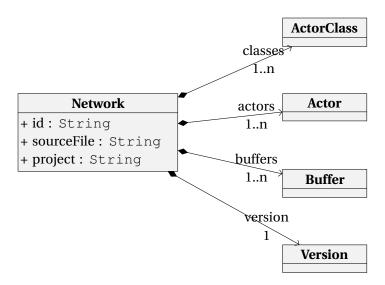

| 6.2  | The Network object                                                                                                                                                  |

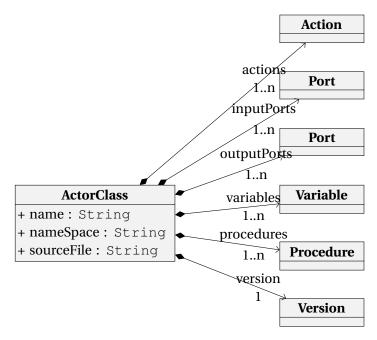

| 6.3  | The ActorClass object 90                                                                                                                                            |

| 6.4  | The Actor object                                                                                                                                                    |

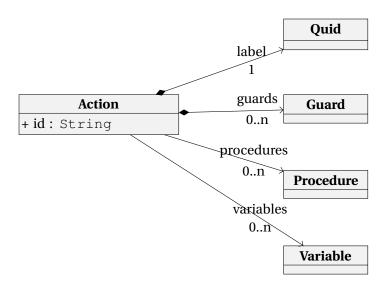

| 6.5  | The Action object                                                                                                                                                   |

| 6.6  | The Quid object                                                                                                                                                     |

| 6.7  | The Procedure object. 92                                                                                                                                            |

| 6.8  | The Variable object                                                                                                                                                 |

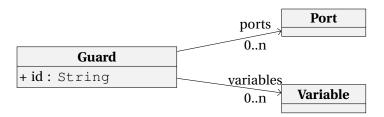

| 6.9  | The Guard object                                                                                                                                                    |

| 6.10 | The Port object                                                                                                                                                     |

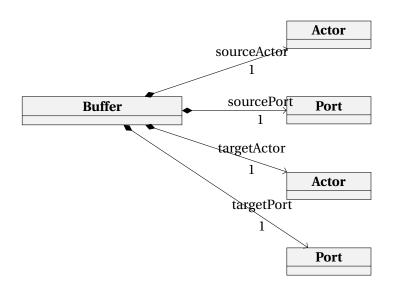

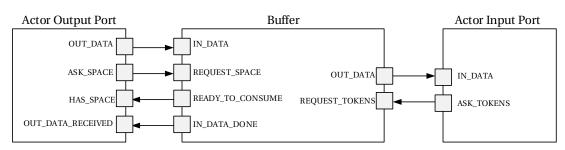

| 6.11 | The Buffer object                                                                                                                                                   |

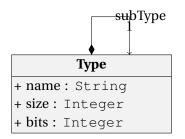

| 6.12 | The Type object                                                                                                                                                     |

| 6.13 | The Version object                                                                                                                                                  |

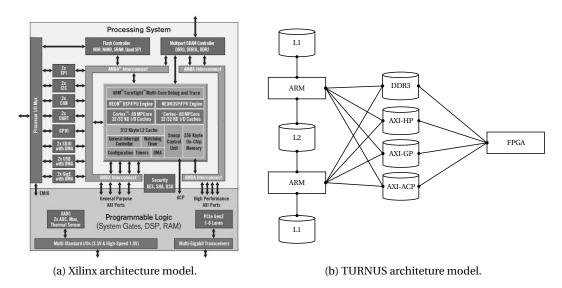

| 6.14 | Xilinx Zynq-7 ZC702 evaluation-board architecture model                                                                                                             |

| 6.15 | The Platform object                                                                                                                                                 |

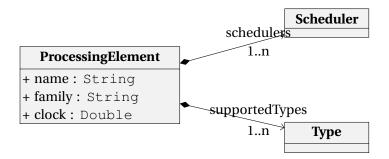

|      | The ProcessingElement object                                                                                                                                        |

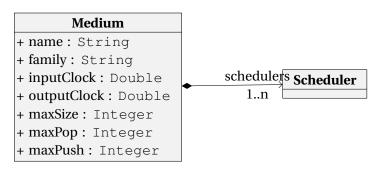

| 6.17 | The Medium object 98                                                                                                                                                |

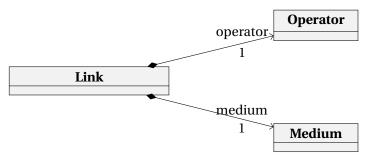

|      | The Link object                                                                                                                                                     |

|      | The Scheduler object 99                                                                                                                                             |

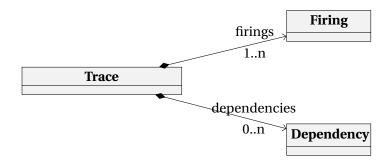

| 6.20 | The Trace object                                                                                                                                                    |

| 6.21 | The Firing object 100                                                                                                                                               |

| 6.22 | The Dependency object 10                                                                                                                                            |

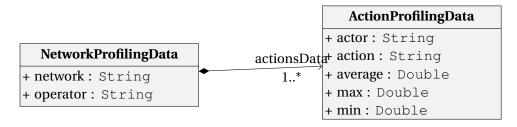

| 6.23 | The NetworkProfilingData and ActionProfilingData objects 102                                                                                                        |

#### List of Figures

| 6.24 | The open RVC-CAL compiler (Orcc) and Xronos infrastructure integrated in the           |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | TURNUS design flow.                                                                    | 104 |

|      |                                                                                        |     |

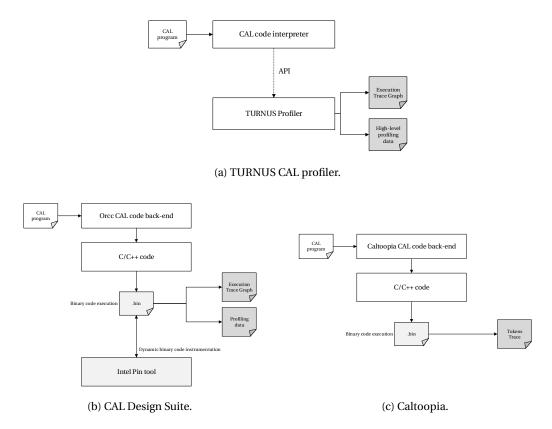

| 7.1  | CAL profilers design flow.                                                             | 106 |

| 7.2  | The FiringData object.                                                                 | 109 |

| 7.3  | The ActionData object.                                                                 | 110 |

| 7.4  | The ActorData object.                                                                  | 112 |

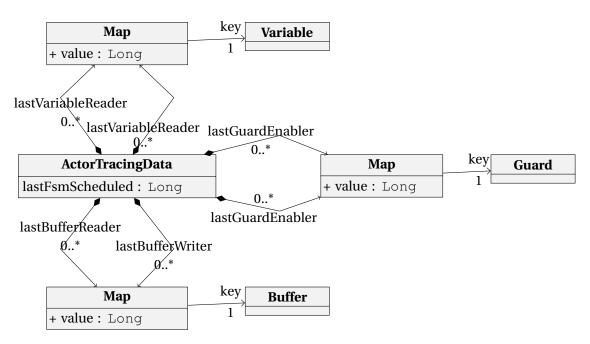

| 7.5  | The ActorTracingData object.                                                           | 113 |

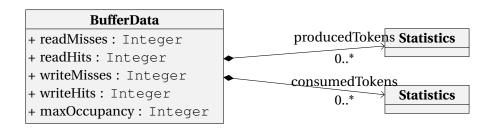

| 7.6  | The BufferData object.                                                                 | 113 |

| 7.7  | The Statistics object                                                                  | 114 |

| 7.8  | The Token object.                                                                      | 114 |

| 8.1  | Execution trace graph post-mortem scheduler: simulation models.                        | 121 |

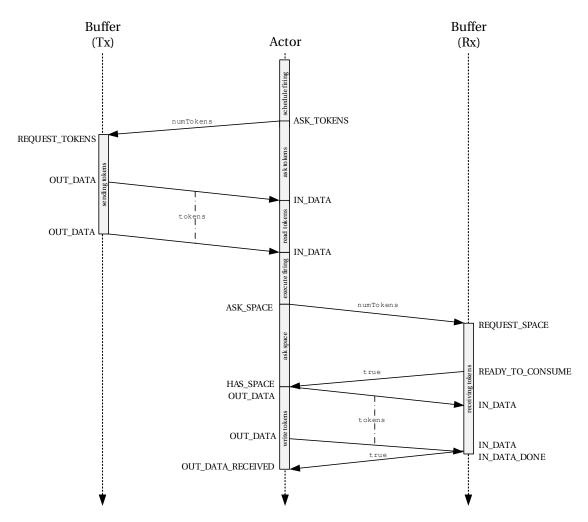

| 8.2  | Sequence diagram for the DEVS atomic implementation of an actor.                       | 124 |

| 8.3  | Design space critical path.                                                            | 133 |

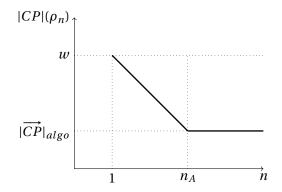

| 8.4  | Critical path length linear model $ CP (\rho_n)$                                       | 134 |

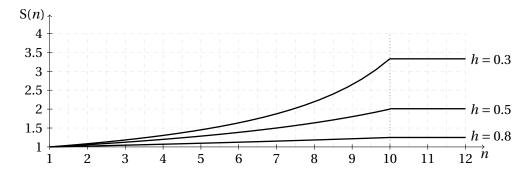

| 8.5  | Theoretical speedup $S(n)$ defined in Equation (8.27) for different values of $h =$    |     |

|      | $ CP _{algo}/w \in [0,1]$ when $n_A = 10.$                                             | 135 |

| 8.6  | Example of impact analysis for three actions $\lambda_1$ , $\lambda_2$ and $\lambda_3$ | 138 |

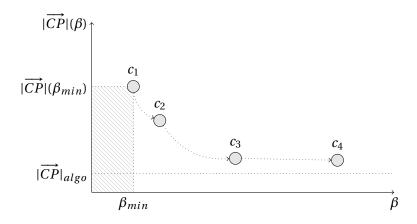

| 8.7  | Critical path design space given different buffer size configurations.                 | 139 |

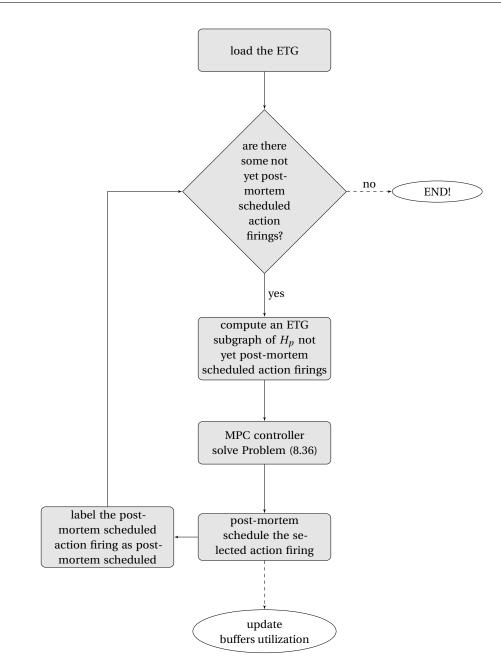

| 8.8  | Bounded buffer scheduling with deadlock avoidance approach.                            | 143 |

| 8.9  | Bounded buffer scheduling with deadlock recovery approach.                             | 144 |

|      |                                                                                        |     |

| 9.1  | JPEG decoder                                                                           | 154 |

| 9.2  | MPEG4-SP decoder.                                                                      | 154 |

| 9.3  | HEVC decoder.                                                                          | 155 |

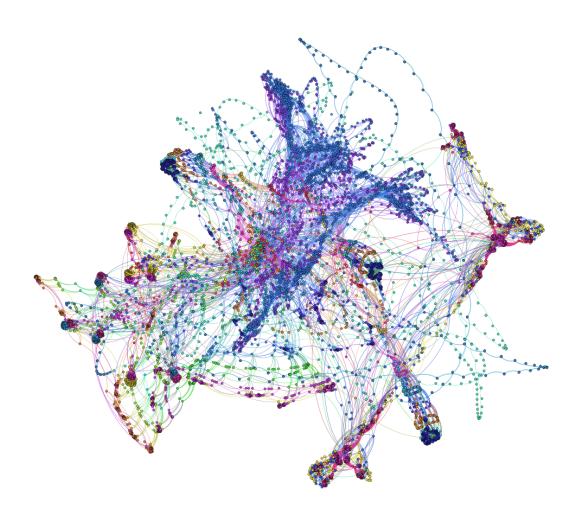

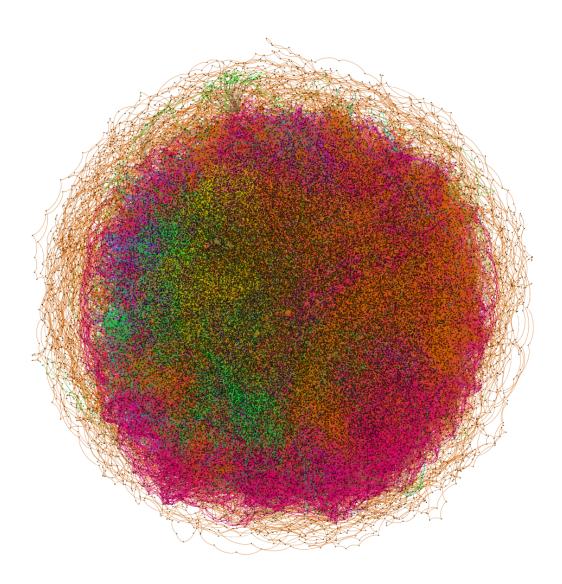

| 9.4  | The rendering of a small portion (i.e. approximatively 80000 action firings and        |     |

|      | 350000 dependencies) of the execution trace graph described in Table 9.4. Action       |     |

|      | firings are colored according to the corresponding actor.                              | 159 |

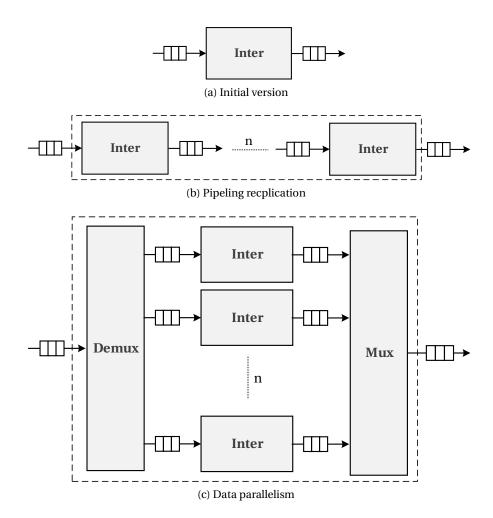

| 9.5  | Refactoring strategies for the Inter-Prediction actor.                                 | 161 |

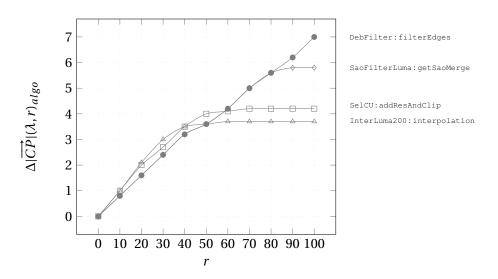

| 9.6  | Impact analysis for the initial version of the Shared-Memory MPEG-HEVC de-             |     |

|      | coder                                                                                  | 164 |

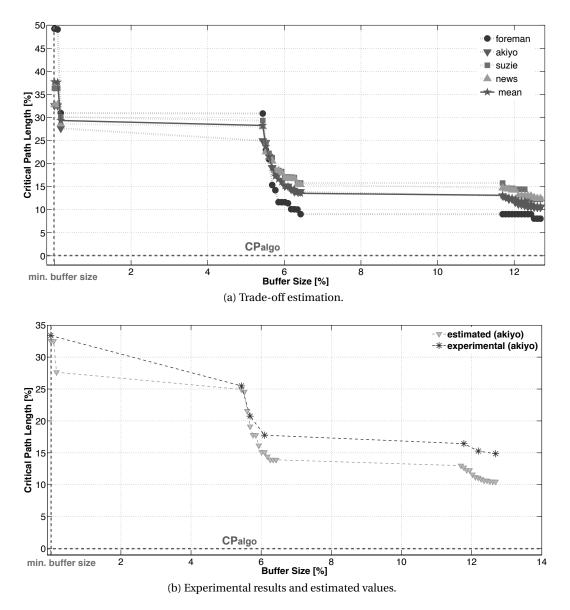

| 9.7  | Buffer size optimization of the MPEG4-SP decoder implemented on an ST Mi-              |     |

|      | croelectronics STHorm platform                                                         | 168 |

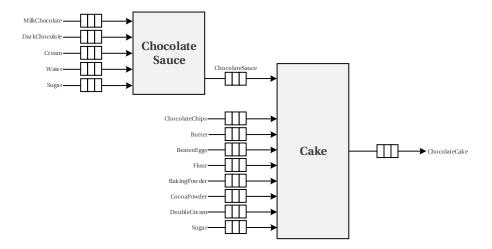

| C.1  | A dataflow representation of the Hello World Cake with Chocolate                       |     |

|      | sauce Chef program illustrated in Listing C.1.                                         | 187 |

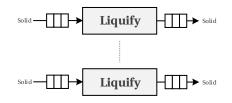

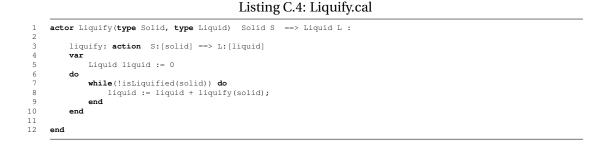

| C.2  | The Liquify CAL actor defined in Listing C.4.                                          | 191 |

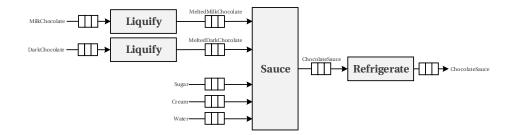

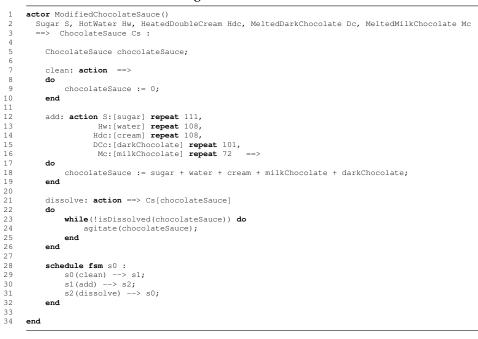

| C.3  | The modified version of the ChocolateSauce CAL actor.                                  | 191 |

## List of Tables

| 2.1                                                                                                   | CAL lexical tokens.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                     |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.2                                                                                                   | Firing of the CAL program described in Section 2.5.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                     |

| 3.1                                                                                                   | Profiled executed operators and statements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38                                     |

| 4.1                                                                                                   | Mapping configurations for the dataflow network illustrated in Figure 2.10. For brevity, the actors Producer, Filter and Consumer are denoted with P, F, C, respec-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                       | tively. The partitioning of the buffers is not considered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48                                     |

| 5.1                                                                                                   | Dependencies kinds, directions, parameters and additional attributes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63                                     |

| 5.2                                                                                                   | Dependencies set <i>S</i> of the execution trace graph depicted in Figure 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                     |

| 5.3                                                                                                   | Firings sequence of the CAL actor Split defined in Listing 2.2 when two in-<br>put sequences are available in its input port I: $I_1 = \{0, 1, -10, -5\}$ and $I_2 =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                       | $\{-1, -1, 0, -1\}$ , respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70                                     |

| 5.4                                                                                                   | Firings with the corresponding internal variable and guard values for the execu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

|                                                                                                       | tion trajectories and graphs depicted in Figure 5.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                     |

| 5.5                                                                                                   | Firing weight parameters for the linear model of Equation 5.10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76                                     |

|                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

| 7.1                                                                                                   | CAL profilers features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 107                                    |

| 7.1<br>9.1                                                                                            | CAL profilers features.       Static code complexity of the MPEG-HEVC decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107<br>156                             |

|                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

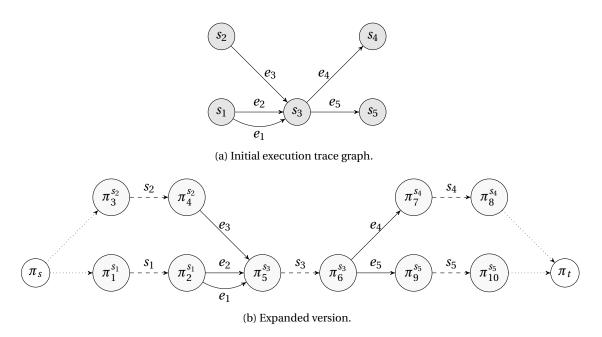

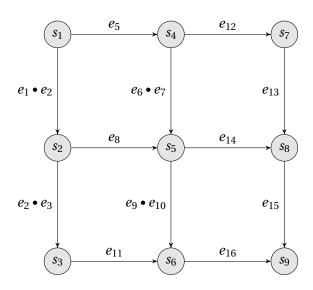

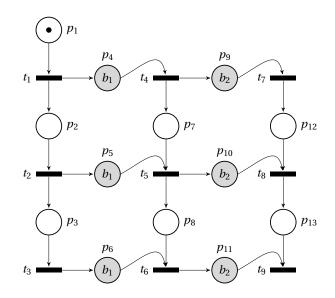

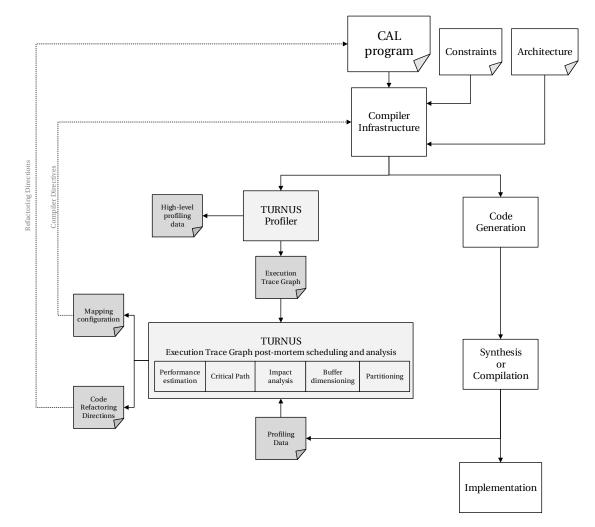

| 9.1                                                                                                   | Static code complexity of the MPEG-HEVC decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 156                                    |