# A (Nearly) Free Lunch: Extending NAND Flash Lifetime by Exploiting Neglected Physical Properties

THÈSE Nº 6388 (2014)

PRÉSENTÉE LE 10 DÉCEMBRE 2014 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE D'ARCHITECTURE DE PROCESSEURS PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

# ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Xavier JIMENEZ

acceptée sur proposition du jury:

Prof. M. Oderesky, président du jury Prof. P. lenne, directeur de thèse Prof. P. Desnoyers, rapporteur Prof. B. Falsafi, rapporteur Prof. S. H. Noh, rapporteur

# Acknowledgements

First of all I would like to express my sincere gratitude to my advisor Prof. Paolo Ienne for his patience, enthusiasm, guidance, and continuous support. Paolo, I am particularly grateful for the trust you put in me and the freedom you gave me throughout my research.

I would also like to thank my thesis committee: Prof. Babak Falsafi, Prof. Peter Desnoyers, and Prof. Sam H. Noh, for their insightful comments and feedback.

My sincere thanks also goes to Dr. David Novo for his invaluable support. Thank you David for all these week-ends and nights spent on improving the writing and flow of my papers. You taught me a lot.

I would like to thank the rest of the *LAPiens*, Chantal Schneeberger, René Beuchat, André Guignard, Prof. Philip Brisk, Dr. Madhura Purnaprajna, Dr. Robert Fasthuber, Dr. Theo Kluter, Dr. Hadi Parandeh-Afshar, Dr. Ali Galip Bayrak, Andrew Becker, Nithin George, Ana Petkovska and Grace Zgheib for the great moments spent at the lab and during our outings. Chantal, thank you for always being cheerful, I will never forget your recognizable laughs. René, André, and Theo thank you for sharing your valuable experience with me.

A special thanks to my colleagues and friends Dr. Romain Rossier, Dr. Thomas Bugnon, Dr. Basile Schaeli, Dr. Florent Garcin, Dr. Fabrice Rousselle, Dr. Rafik Chaabouni, Dr. Julien Andrès, Vahid Babaei, Sami Arpa, Prof. Mike Ferdman, et al. for all the great time spent together at lunch or during dinner parties. Our joyful discussions and board or card game sessions never failed to cheer me up during rough times.

I would like to thank my parents and family for their infinite support and love. Thank you Mom and Dad for providing me with all the resources you could give in order to let me chose my path. Thank you for your trust and care, I am very proud to be your son.

Last but not the least, I would like to thank my wife Audrey for her patience and for the two beautiful kids she gave me during my PhD, Ewan and Alix, certainly my best contributions. Audrey, I know that it was not always easy to get along with my PhD, particularly with two energetic kids at home. I am infinitely grateful for your understanding, courage and love. I could not dream of a better wife. I love you.

# Abstract

NAND flash is a key storage technology in modern computing systems. Without it, many devices would probably not exist today or would at least not benefit from as many features. The very large success of this technology motivated massive efforts to scale it down in order to increase its density further. However, NAND flash is currently facing physical limitations that prevent it reaching smaller cell sizes without severely reducing its storage reliability and lifetime. Accordingly, in the present thesis we aim at relieving some constraints from device manufacturing by addressing flash irregularities at a higher level. For example, we acknowledge the fact that process variation plus other factors render some regions of a flash device more sensitive than others. This difference usually leads to sensitive regions exhausting their lifetime early, which then causes the device to become unusable, while the rest of the device is still healthy, yet not exploitable. Consequently, we propose to postpone this exhaustion point with new strategies that require minimal resources to be implemented and effectively extend flash devices lifetime. Sometimes, our strategies involve unconventional methods to access the flash that are not supported by specification document and, therefore, should not be used lightly. Hence, we also present thorough characterization experiments on actual NAND flash chips to validate these methods and model their effect on a flash device. Finally, we evaluate the performance of our methods by implementing a trace-driven flash device simulator and execute a large set of realistic disk traces. Overall, we exploit properties that are either neglected or not understood to propose methods that are nearly free to implement and systematically extend NAND flash lifetime. We are convinced that future NAND flash architectures will regularly bring radical physical changes, which will inevitably come together with a new set of physical properties to investigate and to exploit.

**Keywords:** NAND flash, SLC, MLC, Characterization, Experiment, Endurance, Lifetime, Performance, Reliability, Wear-leveling.

# Résumé

La mémoire flash NAND est une technologie de stockage clef dans les systèmes informatiques modernes. Sans elle, de nombreux types de dispositifs n'existeraient probablement pas aujourd'hui ou ne bénéficierait pas d'autant de fonctionnalités. Le grand succès de cette technologie a motivé des efforts considérables vers sa miniaturisation afin d'en augmenter plus encore sa densité. Toutefois, la mémoire flash NAND est actuellement confrontée à des limitations physiques qui l'empêchent d'aller vers des tailles de cellules plus petites sans que cela ne dégrade fortement sa fiabilité de stockage et sa durée de vie. Ainsi, dans la présente thèse, nous visons à soulager les contraintes liées à l'élaboration de cette mémoire, en exploitant certaines irrégularités de la mémoire flash depuis un niveau supérieur. Par exemple, nous observons le fait que la varation du processus de fabrication ainsi que d'autres facteurs rendent certaines régions de la mémoire flash plus sensibles que d'autres. Cette différence conduit généralement à des régions sensibles épuisants leur durée vie trop tôt. Ce qui rend alors la mémoire flash inutilisable, quand bien même le reste de sa mémoire est encore en viable, mais non exploitables. Par conséquent, nous proposons de repousser ce point d'épuisement avec de nouvelles stratégies nécessitant un minimum de ressources à mettre en œuvre et permettant d'étendre efficacement la durée de vie des stockages à base de mémoire flash. Les stratégies que nous proposons impliquent parfois des méthodes non conventionnelles pour accéder à la mémoire flash. Celles-ci ne sont pas prises en charge par les documents de spécification des fabricants et, par conséquent, ne doivent pas être utilisées à la légère. Ainsi, nous présentons également un ensemble d'expériences de caractérisation sur de réelles puces flash NAND pour valider nos méthodes et modéliser leurs effets sur les stockages à base de mémoire flash. Enfin, nous évaluons le rendement de nos méthodes en mettant en place un simulateur de disque flash, à travers lequel nous exécutons un grand nombre de traces de disques acquises sur des systèmes réels. Dans l'ensemble, nous exploitons des propriétés qui sont soit négligées ou encore incomprises pour proposer des méthodes à coût négligeable et montrons systématiquement une extension de durée de vie de la mémoire flash NAND. Nous sommes convaincus que les futures architectures flash NAND apporterons régulièrement des changements radicaux dans le processus de fabrication, ce qui amènera inévitablement un nouvel ensemble de propriétés physiques à investiguer et exploiter.

**Mots-clefs :** *NAND flash, SLC, MLC, Characterization, Experiment, Endurance, Lifetime, Performance, Reliability, Wear-leveling.*

# Contents

| Ac                          | Acknowledgements       |                               |    |  |  |  |

|-----------------------------|------------------------|-------------------------------|----|--|--|--|

| Abstract (English/Français) |                        |                               |    |  |  |  |

| 1                           | Intr                   | oduction                      | 1  |  |  |  |

|                             | 1.1                    | Motivation                    | 1  |  |  |  |

|                             | 1.2                    | Efforts So Far                | 2  |  |  |  |

|                             | 1.3                    | Thesis Contributions          | 2  |  |  |  |

|                             | 1.4                    | Organization of this Thesis   | 3  |  |  |  |

| 2                           | NAN                    | ND Flash Memory               | 5  |  |  |  |

|                             | 2.1                    | Storage Mechanism             | 5  |  |  |  |

|                             |                        | 2.1.1 NAND Architecture       | 5  |  |  |  |

|                             |                        | 2.1.2 Programming             | 6  |  |  |  |

|                             |                        | 2.1.3 Reading                 | 7  |  |  |  |

|                             |                        | 2.1.4 Erasing                 | 7  |  |  |  |

|                             | 2.2                    | Reliability                   | 7  |  |  |  |

|                             |                        | 2.2.1 Flash Endurance         | 8  |  |  |  |

|                             |                        | 2.2.2 Error Correcting Codes  | 8  |  |  |  |

|                             |                        | 2.2.3 Data Retention          | 8  |  |  |  |

|                             |                        | 2.2.4 Interferences           | 9  |  |  |  |

|                             | 2.3                    | Multilevel Cells              | 9  |  |  |  |

|                             |                        | 2.3.1 Reading and Programming | 9  |  |  |  |

|                             | 2.4                    | Flash Translation Layer       | 10 |  |  |  |

|                             |                        | 2.4.1 Wear-Leveling           | 11 |  |  |  |

|                             |                        | 2.4.2 Garbage Collection      | 12 |  |  |  |

|                             |                        | 2.4.3 Address Mapping         | 12 |  |  |  |

|                             | 2.5                    | Conclusion                    | 13 |  |  |  |

| 3                           | Flash Characterization |                               |    |  |  |  |

|                             | 3.1                    | Introduction                  | 15 |  |  |  |

|                             | 3.2                    | Measured Responses            | 16 |  |  |  |

|                             |                        | 3.2.1 Access Latency          | 16 |  |  |  |

|                             |                        | 3.2.2 Error Count             | 17 |  |  |  |

|                             |                        |                               |    |  |  |  |

## Contents

|   |      | 3.2.3 Energy                                           | 18         |

|---|------|--------------------------------------------------------|------------|

|   | 3.3  | Influencing Factors                                    | 18         |

|   |      | 3.3.1 Cell Condition                                   | 19         |

|   |      | 3.3.2 Write Data Pattern                               | 19         |

|   |      | 3.3.3 Time                                             | 21         |

|   |      | 3.3.4 Temperature                                      | 21         |

|   |      | 3.3.5 Reference Threshold Voltage                      | 22         |

|   |      | 3.3.6 Physical Cell Position                           | 22         |

|   | 3.4  | Experimental Setup                                     | 23         |

|   |      | 3.4.1 Architecture                                     | 23         |

|   |      | 3.4.2 Characterization Procedure                       | 24         |

|   | 3.5  | Related Work                                           | 25         |

|   | 3.6  | Conclusion                                             | 26         |

| 4 | Libr | a: Balancing Mixed SLC-MLC Wear                        | 27         |

| • | 4.1  |                                                        | <b>2</b> 7 |

|   | 4.2  | SLC-MLC Hybrid Storage                                 | 29         |

|   | 4.3  | Libra: Soft Partitions to Balance Wear                 | 31         |

|   |      | 4.3.1 Faster MLC: Managing MLC as SLC                  | 31         |

|   |      | 4.3.2 Software-Controlled Log Buffer                   | 32         |

|   |      | 4.3.3 Libra Implementation                             | 34         |

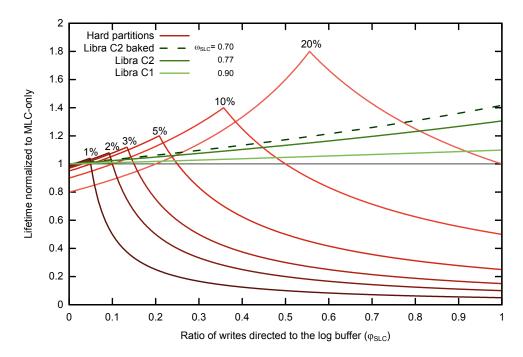

|   |      | 4.3.4 Libra Lifetime Model                             | 35         |

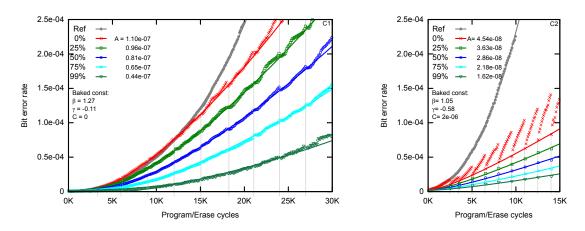

|   | 4.4  | SLC-mode Characterization                              | 36         |

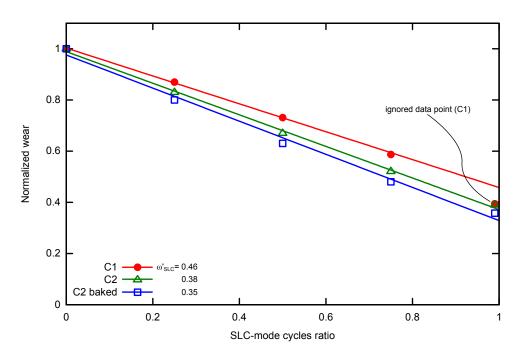

|   |      | 4.4.1 Considering the Recovery Factor                  | 38         |

|   |      | 4.4.2 SLC-mode Wear                                    | 39         |

|   | 4.5  | Results                                                | 42         |

|   |      | 4.5.1 Experimental Setup                               | 42         |

|   |      | 4.5.2 Soft vs. Hard Partitioned Hybrid FTLs            | 45         |

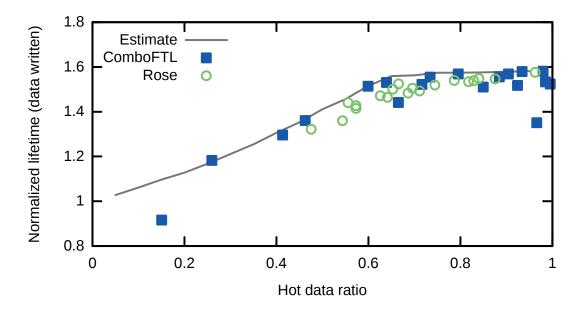

|   |      | 4.5.3 Generalization of Experimental Results           | 46         |

|   | 4.6  | Related Work                                           | 48         |

|   | 4.7  | Conclusions                                            | 49         |

| 5 | Pho  | enix: Reviving MLC Blocks as SLC                       | 51         |

| J | 5.1  |                                                        | 51         |

|   | 5.2  | Reviving Bad Blocks                                    | 51         |

|   | 0.2  | 5.2.1 Reviving MLC Blocks in SLC-mode                  | 52         |

|   | 5.3  | Device Degradation Models                              | 53         |

|   | 0.0  | 5.3.1 Block Endurance Distribution                     | 54         |

|   |      | 5.3.2 Analytical Model of Baseline Device Lifetime     | 55         |

|   |      | 5.3.3 Analytical Upper Bound of Phœnix Device Lifetime | 56         |

|   | 5.4  | Results                                                | 57         |

|   | 5.5  | Future Perspectives                                    | 59         |

|   | 5.6  | Related Work                                           | 60         |

|   | 0.0  |                                                        | 55         |

|    | 5.7                | Conclusion                                              | 61 |  |  |  |  |

|----|--------------------|---------------------------------------------------------|----|--|--|--|--|

| 6  | Wea                | r Unleveling: Relieving Weak Pages to Balance Endurance | 63 |  |  |  |  |

|    | 6.1                | Introduction                                            | 63 |  |  |  |  |

|    | 6.2                | Relieving Pages                                         | 64 |  |  |  |  |

|    |                    | 6.2.1 Definition                                        | 64 |  |  |  |  |

|    |                    | 6.2.2 Page Endurance                                    | 65 |  |  |  |  |

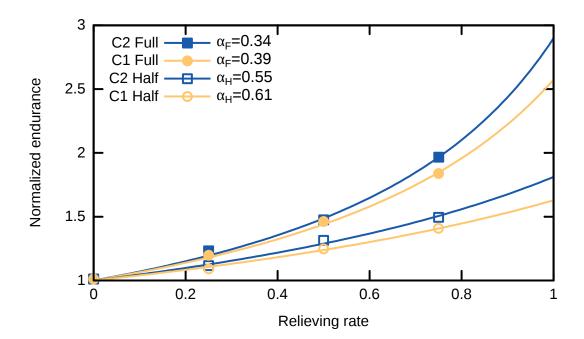

|    |                    | 6.2.3 Understanding the Relieving Effect                | 66 |  |  |  |  |

|    | 6.3                | Implementation in FTLs                                  | 69 |  |  |  |  |

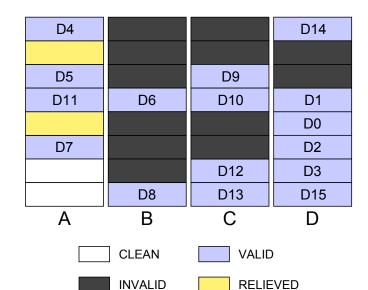

|    |                    | 6.3.1 A New Page State                                  | 69 |  |  |  |  |

|    |                    | 6.3.2 Mitigating the Capacity Loss                      | 70 |  |  |  |  |

|    |                    | 6.3.3 Reactive Approach: Identify Weak Pages on the Fly | 71 |  |  |  |  |

|    |                    | 6.3.4 Proactive Approach: Relieving Plan Ahead of Time  | 73 |  |  |  |  |

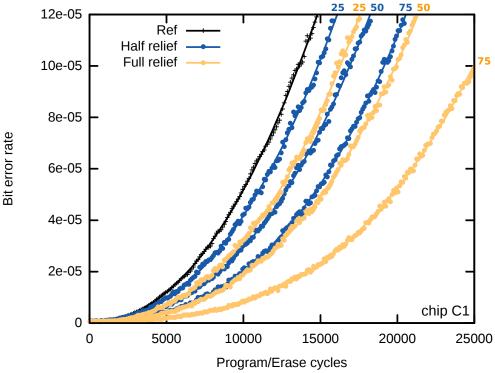

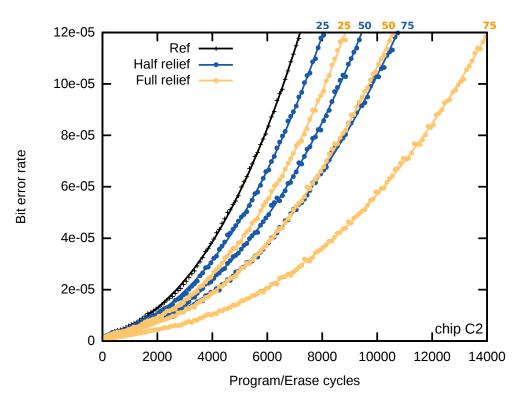

|    | 6.4                | Experiments and Results                                 | 76 |  |  |  |  |

|    |                    | 6.4.1 Collecting Real Traces and Simulating Wear        | 76 |  |  |  |  |

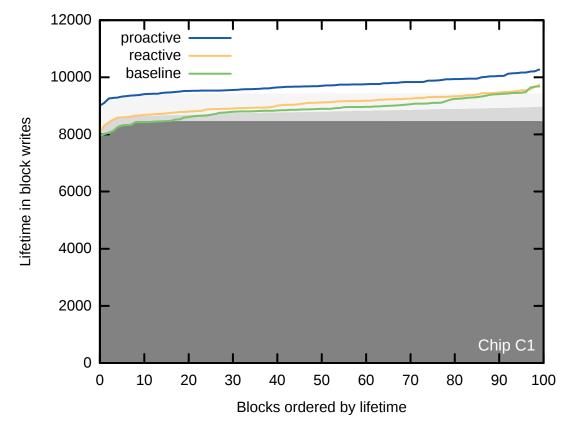

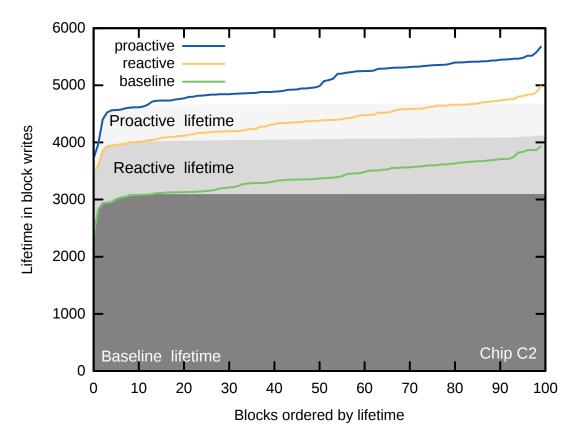

|    |                    | 6.4.2 Block Lifetime Extension                          | 77 |  |  |  |  |

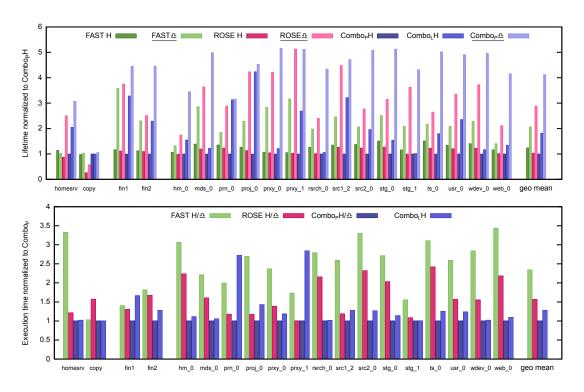

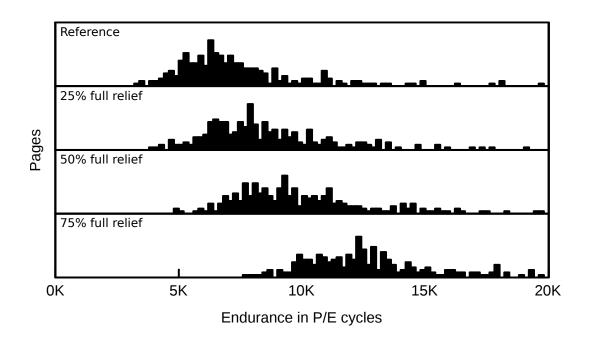

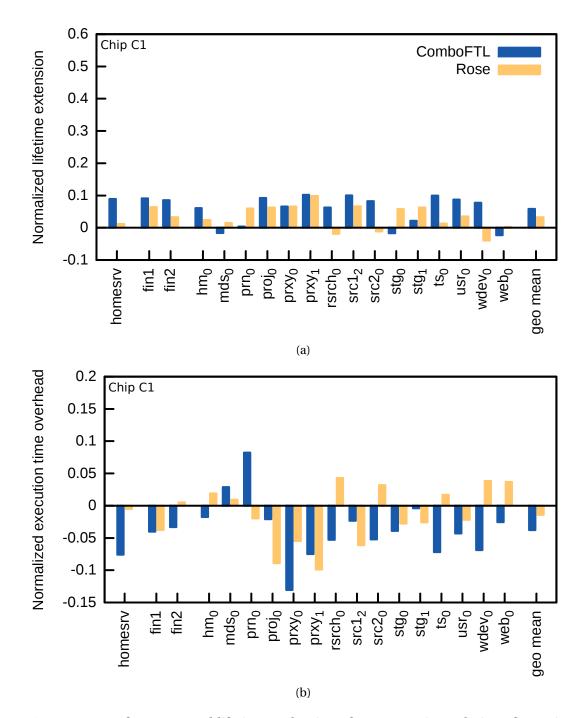

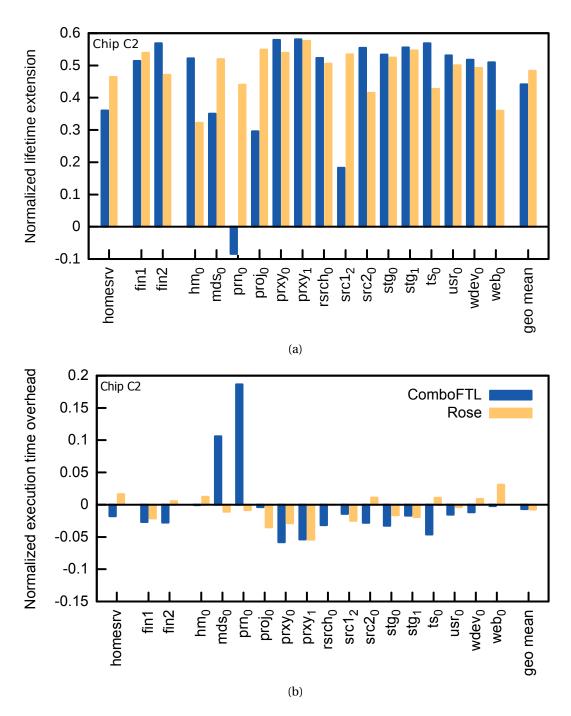

|    |                    | 6.4.3 Device Lifetime Extension                         | 77 |  |  |  |  |

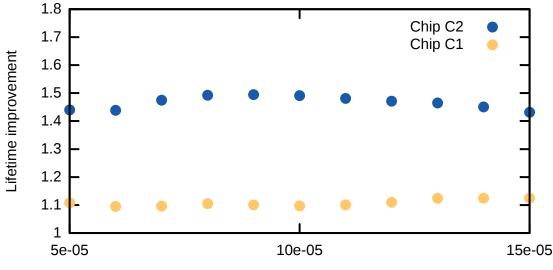

|    |                    | 6.4.4 Lifetime and Performance Evaluation               | 79 |  |  |  |  |

|    | 6.5                | Related Work                                            | 81 |  |  |  |  |

|    | 6.6                | Conclusion                                              | 84 |  |  |  |  |

| 7  | Con                | clusions                                                | 87 |  |  |  |  |

| Bi | Bibliography       |                                                         |    |  |  |  |  |

| Cu | Curriculum Vitae 9 |                                                         |    |  |  |  |  |

# **1** Introduction

NAND flash memory is currently the densest semiconductor memory technology and therefore the cheapest. Added to that factor, its low power consumption, mobility and high performances makes it remarkably successful for light embedded storage applications, particularly for cases where classic magnetic disks are not adapted. Accordingly, NAND flash memory is today by far the leader in storage media for handheld devices. Furthermore, despite the fact that magnetic disks or even tapes remain more cost effective and reliable than NAND flash for very large storage systems, it is not uncommon for large tiered (i.e., hierarchical) storage to use NAND flash at the highest storage levels to act as a fast and low energy storage cache. Therefore, NAND flash is a particularly important actor in the storage ecosystem and can be found in a large range of applications, such as storage for smartphones, tablets, ultrabooks, mp3 players, removable storage, solid state drives or as large storage caching.

# 1.1 Motivation

Although NAND flash memory is already well established, manufacturers continue pushing for higher densities in order to provide the most competitive devices. However, during this progression to smaller technology nodes, several unpleasant NAND flash properties start becoming more cumbersome. For example, flash memory cells can only be written a limited number of times before becoming unreliable and this gets fatally more problematic with smaller cell sizes [23]. Consequently, in order to address these issues, flash manufacturers have to put a considerable effort rethinking their low-level cell architecture at every new technology node. However, manufacturers cannot solve all the issues by themselves and must count on the research community that works on high-level strategies designed to delay the flash device wear out as much as possible. In an effort to open new perspectives in that regard, we put a particular effort in this thesis finding new angles to complement these solutions and efficiently help extending the flash device lifetime further.

# 1.2 Efforts So Far

*Solid State Drives* (SSDs) manufacturers work hard to bring more intelligence in their flash controllers and design new techniques reducing the amount of data written to their storage. For example, one can write less data by compressing it [59, 42] or detecting redundant chunks of data and *deduplicating* them [14], which tend to increase both the device lifetime and its performances. Thereby, a large set of generic solutions applicable on a wide range of device form factors are proposed improving the control logic with more efficient data mapping strategies [37, 10, 16, 22, 11, 26, 52, 15, 47]. Other techniques are specific to an application. For instance, storage policies and architectures have been design to specifically address flash devices acting as a cache for large storage systems [34, 35, 9, 1, 53, 55].

The limitations of NAND flash inspired other researcher to anticipate similar issues for new emerging non volatile memories, such as *Phase-Change Memory* (PCM), Memristors and *Spin-Transfer Torque memory* (STT-RAM). Currently, the most promising emerging technology is the *Phase-Change Memory* (PCM), which Micron produced in relatively large volumes. However, Micron interrupted their PCM production in the beginning of 2014 to focus on the development of new NAND flash architectures. This fact confirms that NAND flash memory will stay an important actor in the years to come.

# **1.3 Thesis Contributions**

Throughout this thesis, we will reveal a set of physical flash properties neglected by manufacturers' specification documents. From these, we could design original approaches to manage flash devices that are nearly free to implement and contribute to extend their lifetime. Rather than trying to improve existing policies, we propose strategies acting from new angles and being as much as possible complementary to traditional existing techniques. Our methods are aimed to be implemented into the flash memory controller that sits between the host file system and the flash chips themselves. Yet, there are a large set of flash controllers with different processing power as well as resources available, which depend on the storage form factor or target application. Consequently, we designed our methods to be as light as possible to implement in order for them to be applicable by the largest set of controller types. A particularity of these methods is that they often have to break the conventions set by flash manufacturers. Accordingly, in this thesis we will present a set of well-designed experiments to characterize properly their effects on the device. These experiments will serve validating the approaches that we propose as well as modeling and quantifying their effects on flash memory storage devices.

# 1.4 Organization of this Thesis

In the next chapter, we provide a background on NAND flash memory. We discuss its basic storage mechanisms as well as its particular cell organization. We also present all the main features that should be expected of a flash controller.

In Chapter 3, we discuss on the process of characterizing NAND flash memories. We present the various factors that could affect and bias the results of characterization experiments. Finally, we describe the experimental setup that we built to perform such experiments.

In Chapter 4, we present *Libra* [30], a method supporting mixed sources of wear, which allows using different storage modes inherent to flash memory in a flexible way. We will show that this flexibility enables sharing the wear across the flash cells more efficiently and provides up to one order of magnitude more lifetime compared to previous rigid approaches. Furthermore, this method requires negligible extra resources to be implemented.

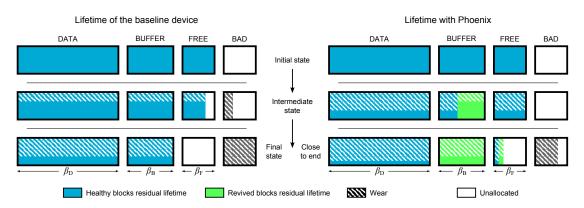

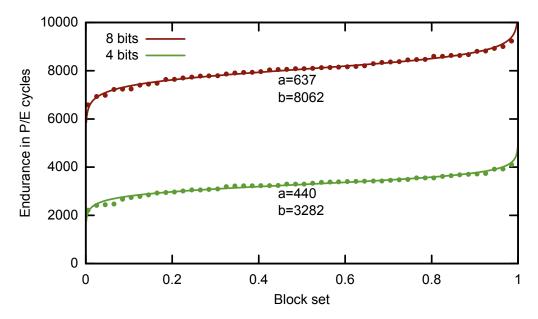

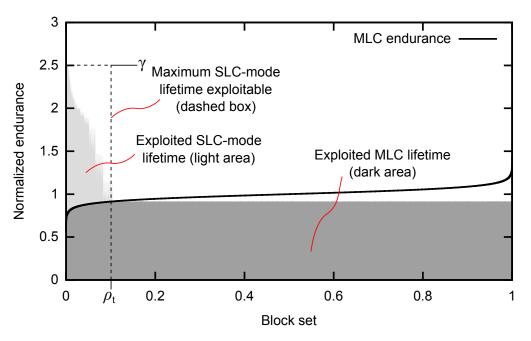

In Chapter 5, we present Phœnix [29], a method that relies on two physical properties of flash. First is the nonuniformity of cell degradation over the flash device: some will wear out significantly earlier than others. Second is the fact that storing less information in memory cells renders them more reliable. Therefore, when too many cells become unreliable (*die*) within a block of cells, we propose reviving this block by restricting it to store less information, which allows a lifetime extension of up to 17% for the studied NAND flash chip and comes for free. Lastly, we model the relationship between the cell lifetime variance and Phœnix potential, which let us envision greater lifetime extension with future flash technology nodes.

We go further in Chapter 6 by addressing this lifetime variance on a smaller granularity than Phœnix. Usually, all cells being part of the same block are written together. Yet, we propose to relieve the weakest ones in order to balance the lifetime within a block [31]. This approach breaks the conventional ways of accessing flash and, therefore, requires careful characterization to understand all its effects. We propose two different strategies relieving weak cells and show that for the considered NAND flash chips, up to 60% lifetime extension can be achieved for a minimal cost.

Finally, we conclude this thesis in Chapter 7.

# 2 NAND Flash Memory

This chapter provides a background on NAND flash memory. It discusses its specific architecture and the peculiar storage mechanisms involved with it. The chapter concludes with a description and comparison of the main flash controller classes.

## 2.1 Storage Mechanism

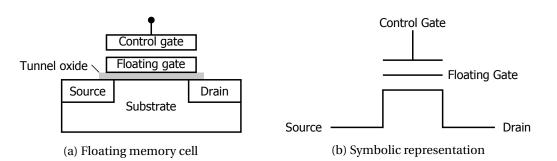

Flash memories store information by using electron tunneling to place and remove charges into *floating gates*. Figure 2.1 illustrates the flash cell structure consisting of a MOS transistor made of two gates instead of one. The floating gate in the middle serves as a recipient for electrons. The action of adding electrons into a cell is called *programming*, whereas the removal of this charge is called *erasing*.

#### 2.1.1 NAND Architecture

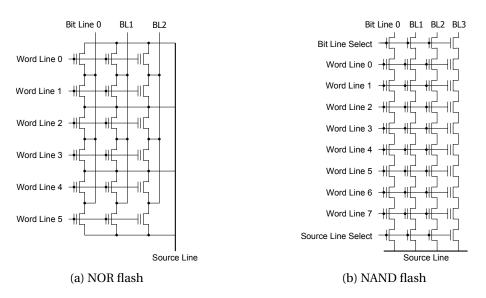

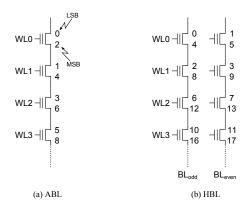

Flash memory comes in two main architecture variants: NOR and NAND, illustrated in Figure 2.2. In NOR flash, cells are connected to the bit line in parallel, which resemble a NOR gate: whenever a word line is brought high, the corresponding bit lines will be pulled down. NOR flash is relatively slow to program but allows fast random reads; thereby, it is mainly used to store devices' firmware or BIOS. In contrast, NAND flash has its cells arranged serially in a NAND gate fashion: the bit line is pulled down only when every word line is brought high. This serial structure brings more density (hence, reduced cost) but increases significantly the read latency. This latency increase is somewhat compensated by enlarging the access granularity to a page level (i.e., typically 4–32 kB) instead of a single byte and allows for larger bandwidth. In summary, compared to NOR flash, NAND flash features slower reads, larger write bandwidth and is cheaper than NOR flash. Furthermore, NAND flash success puts significant pressure on its development and production, which results in a highly optimized technology being more advanced than NOR (e.g., smaller feature size). In this thesis, we will focus on the

Figure 2.1: **Flash cell structure.** A flash cell consists of a MOS transistor built with two gates on top of each other instead of one. The gate in the middle is called the *floating gate*.

Figure 2.2: **NOR and NAND flash cell organization.** In NOR flash, cells are organized as in a NOR gate, in parallel. In NAND, cells are organized in series, much like a NAND gate.

NAND variant, for which limited lifetime is a greater concern compared to typical NOR flash use cases.

### 2.1.2 Programming

Programming cells consists of using the Fowler–Nordheim tunneling effect to inject electrons into the floating gate. This effect occurs by grounding both the source and drain and setting a large voltage  $V_{PGM}$  (typically about 20 V) on the control gate. In the NAND architecture context, the selected word line is set at  $V_{PGM}$ , while every other word line should be biased with an intermediate voltage  $V_{P,PASS}$  (typically 10 V) that lets the current flow in unselected bit lines (pulled high).

The current flowing into the floating gate varies significantly from one cell to another. Consequently, the programming process is divided in multiple program/verify cycles. With this approach, every cell can be programmed independently. Every cell that accumulates a satisfying amount of charges gets its corresponding bit line deactivated and is stopped of being programmed. The process ends when every cell has been programmed. The programming latency depends heavily on the flash parameters and can vary from 250  $\mu$ s to 2 ms or more.

### 2.1.3 Reading

Reading a cell consists of testing the voltage threshold of a cell. An erased cell has a voltage threshold lower than 0 V. Accordingly, a voltage of 0 V on the control gate will activate the cell and let it conduct current. In contrast, a programmed cell has negative charge in its floating gate, which increases the voltage threshold required for the cell to conduct current. Therefore, to read cells, the selected word line is set to 0 V, while the other word lines are set to  $V_{R,PASS}$  (typically 5 V) in order to let them conduct current, programmed or not. Thereby, erased cells will let current flow on their corresponding bit line, while programmed cells will not. It typically takes about 50  $\mu$ s to read a page into the internal buffer of the flash chip.

## 2.1.4 Erasing

Erasing removes the charges from the floating gate and takes about 3 ms. This is achieved by putting a large voltage on the substrate (typically 20 V) while pulling down the word lines of the selected block. Any unselected block sharing the same substrate has its word lines left floating and is unaffected. Within a block, it is not possible to ground only a subset of the word line while letting the rest floating. Due to the proximity of the word lines, this would result in a dielectric breakdown. Therefore, in modern NAND flash, erasing can only be done on the granularity of a block, which is somewhat cumbersome.

The only way to remove charges from the floating gates is to erase them. Therefore, updating a single page of a block would require buffering the complete block, erasing the block and programming back the updated data. Obviously, this would be prohibitive both in terms of time and buffer size requirements. Instead, updating pages must be done *out-of-place*, meaning that every updated page should be programmed in another block with free pages. More on this will be covered in Section 2.4.

# 2.2 Reliability

In this section, we discuss the NAND flash reliability and the main sources of errors that can be observed.

#### 2.2.1 Flash Endurance

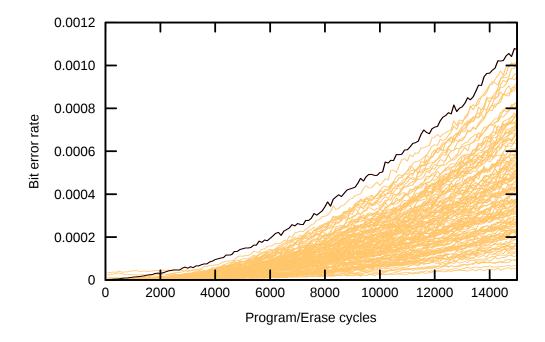

Flash cells degrade while accumulating *Program/Erase* (P/E) cycles [8, 5, 43]. This is provoked by the oxide layer accumulating charge holes, which eases the transfer of electrons. Therefore, cells become progressively less efficient in the retention of charges, more sensitive to neighboring disturbances, and consequently, prone to errors. As a result, all flash blocks experience a gradual *Bit Error Rate* (BER) increase with the number of P/E cycles during their life cycle. Accordingly, manufacturers specify a particular block endurance for their device in terms of P/E cycles. Past this point, flash blocks are considered unreliable and their data integrity becomes compromised. However, even if a uniform wear is assumed among all the blocks, a few flash blocks can wear out before the specified device endurance (and reversely). Indeed, blocks do not present the same level of tolerance towards P/E cycles due to process variation and some blocks might become unreliable significantly sooner than others. Accordingly, flash devices generally reserve a set of spare blocks to replace early failing blocks during the device lifetime [44].

#### 2.2.2 Error Correcting Codes

In NAND flash memory, it is frequent for bits to flip. Consequently, Error-Correcting Codes (ECCs) are used to correct a limited number of bit errors within flash pages. For this, flash pages are extended with spare bytes that are used to store metadata (e.g., P/E count, address mapping) and the redundant bits necessary to implement the ECC. The ECC computation is generally the responsibility of flash controller, but there are also some flash chips integrating directly some ECC logic. The most common ECCs implemented for NAND flash are BCH, Reed Solomon, and more recently Low Density Parity-Check (LDPC) codes. For every new flash technology node, flash cells shrink to smaller sizes and are more sensitive to interferences, resulting in lower data retention properties. Consequently, the ECC strength (i.e., number of errors that can be corrected) that is required to maintain satisfying block endurance increases drastically at every new technology node. However, a stronger ECC grows in size and requires a more complex and longer error decoding process, which degrades the read latency and size advantages of technology scaling. While improving the performances of ECCs [60] and adapting them specifically for NAND flash can directly improve flash longevity and reliability, we believe that complementary alternatives should be investigated, such as the methods that we propose in this thesis.

#### 2.2.3 Data Retention

The charges of a cell leak over time, which degrades the stored data and eventually leads to unrecoverable data loss. Accordingly, manufacturers must specify a minimum data retention time (e.g., one year) together with the endurance (in terms of P/E cycles) to qualify their flash device lifetime. A common approach to prevent this silent and progressive loss of data is to perform data scrubbing: regularly read old data and assess the current error count; when this

count approaches the limits of the ECC unit in use, the data is safely copied elsewhere before it becomes uncorrectable.

#### 2.2.4 Interferences

The charge leakage is not the only source of information loss. Due to the high density of NAND flash, neighboring accesses can interfere with the data stored in a cell. For example, when a word line is read, nearby neighboring word lines get slowly programmed. If too many reads accumulate on the same word line (typically 100,000 times), the direct neighbors risk to accumulate too many charges and lose the stored information. This effect is called read disturb. Similarly, for program disturb, programming a word line interferes with the neighboring word line that is already programmed. In Chapter 3, we will cover some more interference example when describing flash characterization.

## 2.3 Multilevel Cells

The continuous pressure to improve the density of NAND flash memory brought multi-bits per cell technology. While classical *Single-Level Cell* (SLC) flash stores one bit per cell, *Multi-Level Cell* (MLC) flash stores multiple bits in a single cell. The generic MLC term generally refers to 2-bit per cell. Other densities have multiple naming conventions, sometimes not very well chosen. For example, 3-bit per cell flash is often referred to as *Triple-Level Cell* (TLC) flash, while in fact seven levels in total are required to encode three bits. Another naming convention for MLCs uses X3 and X4 MLC to identify 3-bit and 4-bit per cell, respectively. In this section, we describe the storage mechanisms of MLC and discuss the consequences on performance and reliability.

#### 2.3.1 Reading and Programming

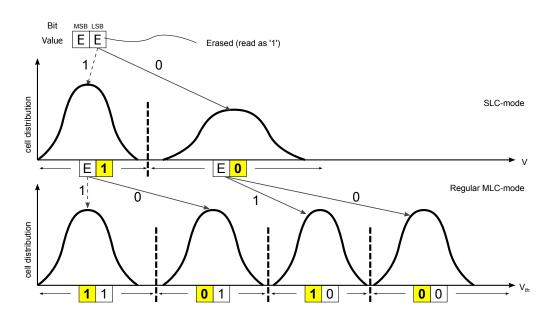

Encoding *n* bits requires to identify  $2^n - 1$  different voltage levels. Thereby, an MLC requires three different voltage thresholds. Supporting more voltage thresholds means that there will be less margin between the voltage levels. Therefore, it will be more likely for bits to flip when interferences occur. Furthermore, these reduced margins will require a more precise programming phase, which will require more time to be executed and degrade performance.

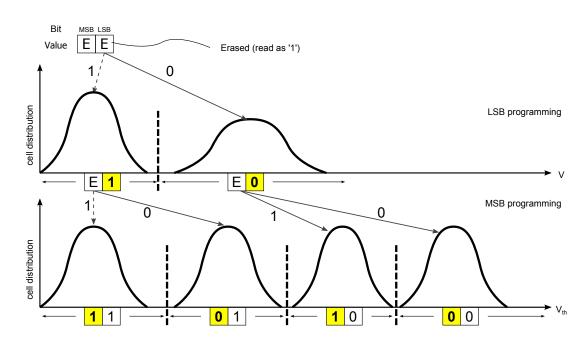

Figure 2.3 illustrates the programming sequence commonly used for MLC. Starting from an erased block, the *Least Significant Bit* (LSB) of every cell is programmed by targeting a single voltage level, which is performed quickly, because this step does not need to be very precise. Then, the *Most Significant Bit* (MSB) of every cell is programmed, which requires reading the current state first (i.e., the LSBs values) and then pushing the cell voltage to either of the three different levels (see solid arrows in the figure). This second programming requires higher precision and it is typically about four to five times longer than the LSB programming [22].

Figure 2.3: **Programming of a 2-bit MLC.** Each bit of a cell is programmed separately. Programming the first bit, or LSB, requires targeting a single level (staying at the erased level is free) and does not need to be very precise. Programming the MSB, requires reading the current state of the cell and targets potentially three different levels, which requires more precision and time.

We also notice in the figure that the bits are not encoded in sequence, but instead use a gray code that prevents a scenario where both cell's bits would flip when shifting from one level to the next one, limiting at the same time the number of errors provoked by such unwanted shifts. In summary, MLC flash brings capacity at the cost of performance and endurance.

### 2.4 Flash Translation Layer

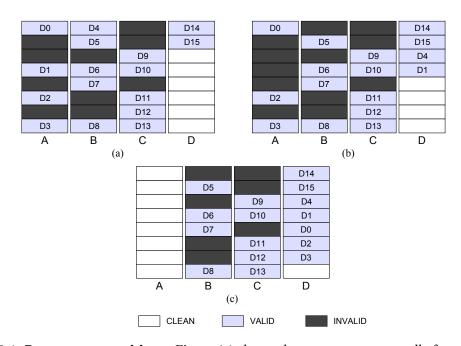

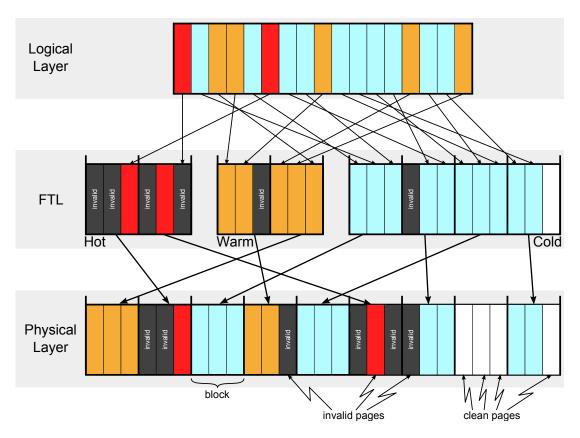

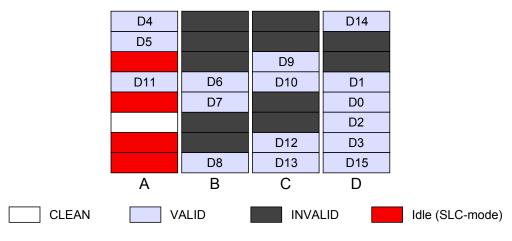

As discussed in the past sections, NAND flash memory requires extensive maintenance and management to overcome its limitations, such as the out-of-place updates or limited lifetime. In order to address those, an indirection layer, called the *Flash Translation Layers* (FTLs), is placed between the file system and the flash storage. It is typically implemented by the flash controllers within the storage device, although there are a few flash file systems that are able to control directly the NAND flash physical interface and will integrate directly this indirection layer. We will focus here on the FTLs integrated in the device, as it is the most common setup. The FTL maps logical addresses to physical flash locations and must maintain the state of every flash page—typical states are *clean*, *valid*, and *invalid*, as illustrated in Figure 2.4. Valid pages cannot be reprogrammed without being erased, which means that the FTL must always have clean page becomes valid and the old copy becomes invalid. This is illus-

Figure 2.4: **Pages state transitions.** Figure (a) shows the page states generally found in typical flash storage: *clean* when it has been freshly erased, *valid* when it holds valid data, and *invalid* when its data has been updated elsewhere. In Figure (b), data D1 and D4 are updated and their previous values are invalidated from blocks A and B. In Figure (c), block A is reclaimed by the garbage collector. The remaining valid data were first copied to block D, before block A was erased.

trated in Figure 2.4(b), where D1 and D4 have been reallocated. The number of invalid pages grows as the device gets written. At some point, the FTL must trigger the recycling of invalid pages into clean pages. This recycling process is known as garbage collection, which selects a victim block according to a certain policy, copies any remaining valid page to available clean pages, and then erases the victim block. An example of garbage collection is illustrated in Figure 2.4(c), where block A is selected as the victim. Next, we describe in further details the most important tasks deployed by typical FTLs.

#### 2.4.1 Wear-Leveling

FTLs implement several techniques that maximize the use of the blocks' limited endurance to guarantee a sufficient device lifetime. One central approach is to even the wear on every block to prevent a few blocks from getting worn out too rapidly. This is generally performed by wear-leveling, which targets a uniform P/E count on every block of the device [61, 12]. Therefore, the maximum capacity of the device can be guaranteed for a longer time.

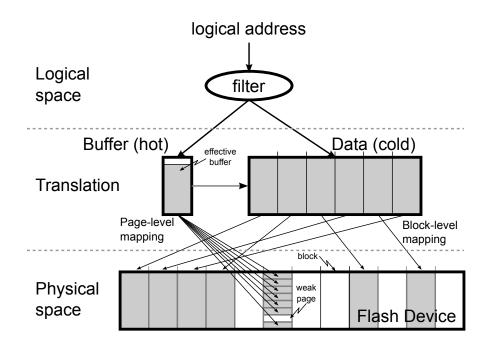

Figure 2.5: **Flash Translation Layer example.** An example of page-level mapping distinguishing update frequencies in three categories: *hot, warm* and *cold*. In this thesis, we will often exploit the fact that hot partitions represent a small capacity proportion of the device, while at the same time a significant ratio of writes gets directed to them.

# 2.4.2 Garbage Collection

Copying the remaining valid data of a victim block represents a significant overhead, both in terms of performance and lifetime. Therefore, it is crucial to select the data that will be allocated onto the same block carefully in order provide an efficient storage system. Wu and Zwaenepoel addressed this problem by regrouping data with similar update frequencies [61]. *Hot* data have a higher probability of being updated and invalidated soon, resulting in *hot* blocks with a large amount of invalid pages that reduce the garbage collection overhead. Figure 2.5 shows an example FTL that identifies three different *temperatures* (i.e., update frequencies), labeled as *hot, warm*, and *cold*. Literature is rich with new heuristics to identify hot data [39, 11, 26, 52, 51].

### 2.4.3 Address Mapping

FTLs can chose different address mapping granularity. Two granularity types that are straightforward for NAND flash are the page-level and block-level granularity. The block-level mapping requires a small mapping table, but generates expensive garbage collection overhead when only a few pages per block must be updated. In contrast, the page-level mapping [24, 41] is much more flexible but requires a large translation table (typically stored in expensive SRAM or DRAM) that is prohibitive for small storage systems with few resources available.

A cost-effective intermediate solution is to use a hybrid mapping. FTLs using this type of mapping are called hybrid FTLs [15, 16, 36, 37, 39]. The device maintains two set of blocks and maps them at a different granularity. A small set of blocks acts as a log buffer that is mapped at the page level. The other set is called the data partition and represents the device capacity. It is mapped at the block level. The purpose is to direct small random writes to the log buffer so that they can be written back to the large data partition in-order as big chunks. Furthermore, it also regroups data that is likely to be overwritten soon into the log buffer, because invalidating a page from the page-level mapped region will generate a significantly lower garbage collection overhead than invalidating a page from a block-level partition. Such an FTL requires a decision level, to decide whether a data write should be directed to the buffer or to the data partition. This decision can for example be taken based on the write request size: relatively large sequential write requests are less likely to be updated in the near future compared to small random writes.

# 2.5 Conclusion

This chapter has introduced background information on NAND flash technology. Specifically, we compared the NAND and NOR architectures, discussed the mechanisms to read, program and erase flash cells, listed the reliability limitations of this technology, and explained the role of the FTLs. In the next chapter, we will discuss about the flash characterization process and present the experiment platform that we design for it.

# **3** Flash Characterization

In this chapter, we cover the basic principles for experimenting on NAND flash memory in order to characterize undisclosed properties. We describe the limited set of outputs available from a typical consumer chip and explain how to derive useful information out of it. We also present the experimental setup that we built to perform all the characterizations presented in this thesis.

# 3.1 Introduction

Characterizing flash devices is a common approach to unveil properties that are typically not published in the manufacturers' specification documents and difficult to predict from the theory or models alone. For example, it can be used to extract statistics on a device performance and quantify temporal or spatial variances. Furthermore, it can be used to observe the effects of original ways to access the flash memory. Indeed, while flash memory is meant to be written sequentially, it can also be used unconventionally, which will often have an influence on its characteristics.

Many previous works proposed new programming schemes while relying on wrong assumptions that can be simply invalidated with a proper characterization of flash devices. A recurrent example is the assumption that the endurance of flash is solely dependent on the number of erases that is performed on a block and not on the data that is programmed in the cells. Accordingly, this led to numerous encoding technique proposals typically inspired from *Write-Once Memories* (WOM) [27, 33, 20, 21], which consists of encoding a set of logical bits on a larger number of cells. For example, a *two write* code would allow storing two bits of information on three cells twice before requiring to erase their corresponding cells, which would increase the effective written bits in the three cells to four bits per P/E cycles. Assuming that the endurance is exclusively related to the P/E cycles, this would trivially bring an endurance improvement. However, as we will discuss in the coming chapters, programming a cell at an intermediate level or at the highest level will generate a significantly different amount of wear and cell-to-cell interference. Specifically, reprogramming a page multiple

#### **Chapter 3. Flash Characterization**

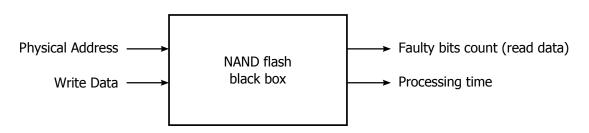

Figure 3.1: **A NAND flash black box model.** The figure illustrates the limited interaction possible with a NAND flash chip.

times will inevitably increase the average programming voltage level of its cells, significantly accelerate the cells degradation, and increase data disturbance, which would severely reduce or even annihilate the benefits originally promised by the proposed encoding. Hence, we believe that characterization is a critical step when designing a storage strategy that is not covered by typical hardware specification documents.

Regarding NAND flash memory consumer chips, only a limited number of responses is accessible, such as the faulty bit count or the access latency. From these, the state of the device can be somehow derived. Figure 3.1 illustrates the black box model of a NAND flash chip. We can input data at a specific physical location and later read back the data and observe how the data was degraded. It can also be useful to monitor the time it takes for each access to be processed. In general, characterization involves cycling the flash device, that is, to program and erase continuously a set of blocks of the flash device and observe how the performance and bit error rate is affected depending on the access patterns. Yet, many factors should be taken into consideration when designing a characterization experiment in order to provide meaningful information, such as the ambient temperature, the cycling frequency, or the data patterns that are programmed. In this chapter, we will present the typical responses that we can measure during the characterization experiments and describe all the factors that we know of and that can have an effect on those responses. In the next section, we start describing the set of response that we can typically extract from a NAND flash chip.

# 3.2 Measured Responses

The process of characterizing a device consists in sending stimuli to a device, often representing a typical usage environment, while collecting and monitoring the responses or state of the device, which we will discuss in the following subsections.

### 3.2.1 Access Latency

In NAND flash memory, the program and erase latencies are subject to variations. In contrast, read accesses remain relatively constant throughout the device's lifetime. Furthermore, we can observe that the programming and erasing times can deviate depending on other factors (e.g., cell condition, ambient temperature) that we will cover in further detail in the next section. One interesting feature is that the more a cell is damaged, the shorter is the programming time [22, 17]. Hence, depending on the time it takes to program a page, it might be possible to evaluate approximately its current health and get a sense of the remaining endurance of a page. As seen in Section 2.3, LSB and MSB programming times are very distinctive. Therefore, the program latency is also a good mean to understand whether we are programming an LSB or MSB page, which is helpful to identify the position of every LSB and MSB page within a block. This helps to recover the internal page mapping, which is not necessarily specified by the manufacturer. Regarding the erase latency, in contrast to the program latency, it increases progressively with cells wearing out. The accumulated charges trapped into the oxide layer make it more difficult for the erase process to achieve a satisfying voltage level.

In order to evaluate the time it takes to perform a programming or erasing command as well as any flash command, we can probe the *busy* signal provided by the ONFI interface. This signal becomes active (low) whenever a command is being processed by the flash memory and is released once the command is processed. Therefore, every time the flash is read, programmed or erased, we can accurately evaluate the time that it takes to perform the operation internally simply by measuring the pulse width of this *busy* signal. It should be noted that advanced features allowing interleaving commands (e.g., caching, multi-banking) hide at least partially the time it takes to perform a single command and will not allow the command time to be evaluated properly. Hence, during our experiments, we enforced regular basic accesses in order to recover the processing time of every access to the flash memory.

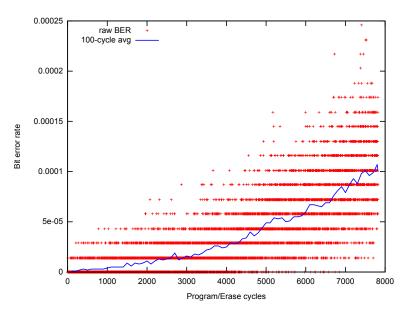

#### 3.2.2 Error Count

The voltage threshold of a programmed cell changes over time for multiple reasons. For example, charges regularly leak out of the floating gate, which will decrease the voltage threshold of a cell as a function of time. Another example comes from the capacitive effects occurring when neighboring cells get programmed, which increases the voltage threshold of every inactive cell nearby. Sometimes, this variation of voltage can be sufficient to shift towards another voltage level, resulting in a bit flipping. The probability for this event to occur is tightly coupled with the cell condition. A damaged cell will leak significantly more charges than a healthy one. Hence, the error rate allows us to appreciate the current condition of a cell. Yet, other factors might influence the instantaneous error rate and it is important to average them out to remove any bias in this type of measurement. For example, as illustrated in Figure 3.2, the error rate is very sensitive to the written data and will vary significantly from one cycle to another.

Counting the amount of faulty bits simply consists in counting how many bits are different between the written and read data. In a real system, counting the number of faulty bits is left to the ECC unit, which can evaluate from the coded data how many bits (or multi-bit

Figure 3.2: **Bit error rate with respect to P/E cycles.** The bit error rate evaluated right after programming a page is reported against the P/E cycles. The variance is significant from one measurement to the one that follows. Therefore, in practice, evaluating the current health of a page cannot be based on a single measurement. Instead, it would require to average a set of measurements.

symbols) are corrected. Of course, past a certain number of errors, the ECC unit capability would be exceeded and would prevent us to assess this number. Therefore, we do not rely on an ECC unit for our experiments; instead, we register the data that was written.

#### 3.2.3 Energy

Another information that can be measured from outside the chip is the energy consumption. Thereby, the energy required to read, program and erase can be characterized. Further analysis would allow to model the energy consumption associated to the programmed data pattern. Yet, energy is one response that we did not consider in our evaluations.

### 3.3 Influencing Factors

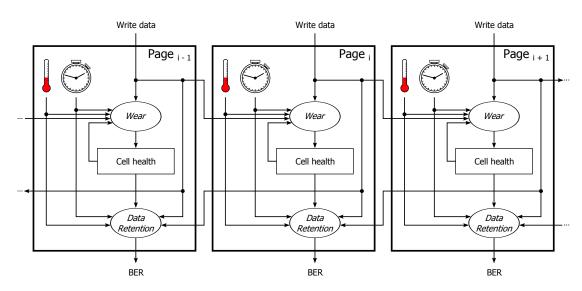

The flash performance can be influenced by a large set of factors that we will list and describe in this section. In order to illustrate the way the main factors interact with the device, we propose a *gray-box* model of the flash page degradation in Figure 3.3 and will refer to it throughout this section. The inputs of this model include the data written to each page, the time between two accesses and the ambient temperature; for the output we only consider the BER here. Similar models could be built for access latency and energy consumption.

Figure 3.3: **Gray-box model of flash pages degradation.** This figures depicts a relatively high level and simplified description of the possible interactions between factors and flash page health. Several aspects are not considered here such as cells being in MLC or a cell-to-cell interference limited to direct neighbors.

#### 3.3.1 Cell Condition

The cell condition drives the retention capability of the memory cells. Worn out memory cells will leak charges more rapidly than healthy cells, rendering them unreliable at some point. In Figure 3.3, this interaction is represented by the arrow between the *Cell health* and *Data retention* boxes. Furthermore, as discussed in Section 3.2.1, damaged cells will tend to get programmed faster than brand new cells [22, 17], which has been verified with our experimental setup. One side effect of a faster programming is that each programming steps become larger and therefore less precise; consequently, the probability to overshoot a cell programming increases. Furthermore, the cells' condition degrades with P/E cycling, hence it can also be considered a response or consequence of a characterization process. Yet, the degree of damage experienced by a cell cannot be probed directly from typical interfaces. Therefore, as discussed in Section 3.2.2, we estimate the cells condition of a page by relying on the fact that it correlates with the BER.

#### 3.3.2 Write Data Pattern

The data to be stored on a cell is encoded into a voltage level. Hence, the written data pattern defines the voltage levels being programmed in a page, which is a factor that correlates with several effects that we will discuss in the next three subsections.

#### Wear

A first effect that correlates with the data patterns written to flash is the wear, or damage, associated to each programming level. This correlation is illustrated in Figure 3.3 by the path between the *Write data* input and the *Cell health*. The damage done to a cell depends largely on the actions that are applied to it. Accordingly, if a cell stays at the erased state during a P/E cycle, fewer charges will transit through the oxide layer; consequently, it will suffer less damage than if it were programmed to a higher level. This effect is often overlooked for a regular use case, where we can assume a uniform distribution of cell programming levels, which can then be averaged out. However, it becomes a key aspect for this thesis, for which we purposely unbalance the programming levels within blocks (see Chapters 4, 5 and 6). Accordingly, in this thesis, we will present a characterization experiment to analyze the degradation speed of cells for most of the technique that we will introduce.

#### Voltage Level Reliability

The second effect relates to the retention data capability: all voltage levels are not equal in this aspect. This effect on the retention is illustrated in Figure 3.3 by the arrow between the *Write data* input and the *Wear*. For example, the leaking current that empties progressively the memory cells correlates with the amount of charges trapped in the floating gates, therefore on the voltage level. Accordingly, the lowest voltage levels are more resistant to leakage, especially the erase state, which is the lowest level and will not change its state by losing charges. Reversely, the highest voltage level are less affected by capacitive effects than the lowest ones. Cai et al. give some insights on that topic by experimenting on a flash chip and reporting a bit error rate breakdown for every voltage level [6]. Overall, the data retention capacity of every voltage levels will largely depend on the threshold levels defined by the manufacturer. It will also be influenced by the longevity of the stored data, which defines how long cells will leak before being updated.

#### **Neighboring Disturbance**

The last effect concerns the disturbances that occur between neighboring cells. Flash memory technology is dense; consequently, the floating gates that capture the charges are relatively close to each other. This proximity incurs capacitive effects that have an influence on the storage reliability: when a cell is programmed to a higher voltage, the resulting voltage shift pushes the neighboring cell voltage a bit higher. This effect is illustrated in Figure 3.3 by the path between the *Write data* of Page *i* to the BER output of Page *i* – 1. During a programming phase, the current neighboring capacitive effects are taken into account when charging the floating gates; hence, past interferences can be 'absorbed' that way. Indeed, the program/verify approach rely on the current voltage threshold that is read on a cell, and it will stop programming a cell, when an absolute voltage level is reached. Yet, after a cell is programmed, it is very likely that a neighboring cell will be programmed in the near future (except for the last page of a block). This neighboring programming increases the capacitive effect in function of the voltage shift applied on the neighboring cells: a larger voltage shift will generate more disturbance. Hence, the worst-case disturbance for a cell is to have its neighbors programmed from the erase state to the highest voltage level, while the cell stays at the same level. In typical MLC devices, this scenario can only be experienced by cells staying at the erased state; in any other state, the partial programming makes this scenario impossible. This explains why manufacturers set a larger step between the erased state to the next voltage level than any other step. For SLC devices, there are two levels, so the worst case happens frequently, but does not have the same consequences than MLC devices, due to its large voltage threshold margins. Therefore, the data that is programmed on a page has a significant effect on the data that is stored on its neighbors. Accordingly, the experiment setup must take proper care to avoid writing patterns that would severely bias the results.

#### 3.3.3 Time

A third factor affecting the storage reliability is time. As seen in Chapter 2, flash cells leak charges over time. The influence of time on data retention is pictured in Figure 3.3 by the arrow between the clock and the *Data retention* block.

Although time has a negative effect on the stored data, it also has a recovery effect on the cell health. This influence is illustrated in Figure 3.3 by the arrow between the clock and the *Wear* block. The stress sustained by flash cells during P/E cycles translates into charges being trapped in the cell oxide layer, which weaken its insulation property. Reversely, during long periods of resting time absent of any programming of erasing process on a set of cells, charges progressively get detrapped from the oxide layer, which restores somehow the oxide properties and the corresponding cells' health. This effect is known as the *recovery process* [45].

When characterizing the BER with respect to factors other than time, it is important to ensure that the various factors tested do not significantly change the experiment total time. For example, assuming an experiment based on two different benchmarks with one taking three weeks of cycling and the other half of it, their results would not be entirely comparable, as the second benchmark would not have benefited the same recovery process level.

On the other hand, if time is the desired factor to consider, experiments requiring to assess the flash cells state after long period of time will obviously be time consuming and not practical. Fortunately, in some cases, temperature can accelerate the effects being characterized and may reduce significantly the experiment time.

#### 3.3.4 Temperature

Temperature is a factor that influences reaction rates by providing more or less energy to the particles of a system. Concerning flash memory, electrons at a higher temperature will have a higher probability to have the energy necessary to leave the floating gate; therefore, high temperature increases the chance of charges to leak and reduces the retention time of cells. Similarly, temperature affects the charges trapped into the oxide layer and the recovery process described in the previous subsection. Accordingly, Lue et al. [40] suggest extending regular flash memory architectures by inserting local heaters, which would increase the temperature of blocks being erased to high levels in order to heal them in the process and, as a result, increase flash memory endurance. Furthermore, the temperature factor is used by manufacturers to emulate in a short time the charge loss that would occur on a long period. Thereby, it becomes possible to estimate the retention time corresponding to a given cell state and error correcting strength. Hence, in Figure 3.3, temperature interactions in the system are similar to time. In our experiments, we will also use this fact to verify whether the techniques that we propose are affected by time.

#### 3.3.5 Reference Threshold Voltage

Besides the reliability difference between threshold voltage levels discussed in Section 3.3.2, the reference threshold voltage during the read out of a page can be a factor influencing the amount of faulty bits that we read. In some very recent NAND flash chips, manufacturers give access to advanced internal control of their decoding circuits. Specifically, it enables flash controllers to set the voltage threshold references that are used to read a page. Thereby, voltage shifts due to charge leakage over significant amount of time can be addressed to a certain extent by adapting the voltage threshold accordingly. This factor can be useful to assess the voltage shift over time or to characterize the variance in the cell voltage distribution after some specific manipulation. In our case, we did not have access to such flash memory chips, but its potential for characterization has already been demonstrated by Cai et al. [7]. We did not include this factor in the model of Figure 3.3.

#### 3.3.6 Physical Cell Position

The cell and page position within a block affects its exposure to stress. The stress experienced is largely dependent on the events occurring in the neighborhood. Hence, cells and pages physically located on the boundaries of a block will generally show different degradation speed than pages located in the center. Furthermore, depending on the page programming sequence and page mapping architecture, the cell-to-cell interference might be unbalanced between one page to another. Hence, when characterizing mechanisms applied on a subset of pages within a block, it is important to make sure that the results are independent from the page position to not bias the results. Typically, alternating the pages from one block to another on which the studied mechanism is characterized will allow averaging out the physical position factor.

Figure 3.4: NAND flash experimental setup system architecture.

# 3.4 Experimental Setup

In this section, we present the experimental setup that we built for characterizing NAND flash chips and describe several specific features that we introduced in order to have full control over the factors presented in the previous section.

# 3.4.1 Architecture

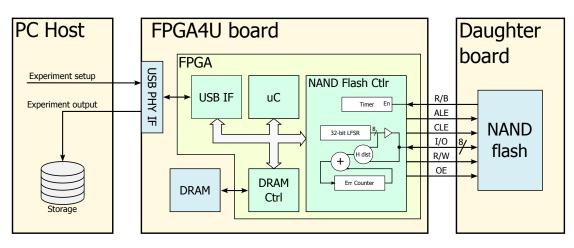

The system is based on an FPGA board [19] that embeds a USB interface used here to collect the experiment output from a computer, and various *General Purpose I/O* (GPIO) pins, which are used in this setup to interface NAND flash chips. The general architecture is illustrated by Figure 3.4. We interface ONFI [49] compliant TSOP-48 NAND flash chips, which is a package commonly found in USB stick drives and SSDs. Those chips do not implement any address translation and let us access directly the raw flash storage, which is not possible with typical flash storage media such as SD memory cards or flash drives.

Characterizing flash memory often requires reading and writing thousands of GB of data in total. Therefore, it is vital to optimize the time it takes to perform a single read or write transaction. For this, we developed a custom flash controller that is optimized for our experiment process. Specifically, it features a 32-bit *Linear Feedback Shift Register* (LFSR) module to read/write pseudo random pattern from/to the NAND flash memory, a register to count the number of faulty bits, and a timer connected to the Ready/Busy line of the NAND flash chip. The timer is used to characterize the time it takes for read, program and erase commands to complete. The error counts and timing data are transmitted through USB to a host computer, which can afterwards perform statistics on the experiment results. For a 1-week experiment, this data represents a total size on the order of 10 GB.

### 3.4.2 Characterization Procedure

Characterization experiments usually consists of repeating the followings steps thousands of times: (1) erasing every block considered for the experiment, (2) programming them with random data, and later (3) reading the data back to count how many bits flipped in the storage. Although a few variations are applied for specific experiments, this is the general procedure of an experiment.

The three steps described correspond to one experiment cycle. During our experiments, we make sure that the cycle frequency stays constant overall the experiment in order to have balanced and comparable cycles. Indeed, not only the flash timings change over time, but also the experiment might involve cycles with variable amount of data written. Hence, if not safeguarded, some cycles would be significantly shorter than others are and generate a bias on the flash characterization. Intuitively, one can think that this bias could come from variable retention times: shorter cycles would leave less time for the cells to leak after being programmed. However, although one cycle might last multiple times longer than another, a single cycle over 100 blocks generally takes less than five minutes to complete and over this time scale the retention effect is not significant. Yet, we can observe a bias from the recovery time, which applies over the total experiment duration. Thereby, for an experiment that takes weeks, the recovery time reduction starts to become significant with the P/E cycles progressively becoming shorter because of the programming latency getting shorter. This bias is not representative of a typical use case: an application will not necessarily program a device more often simply because the programming latency lowers. Therefore, we fix the cycle period to the slowest cycle for the complete experiment.

In order to prevent unbalanced written pattern to bias the results, we write pseudo-random data into the flash. This is performed with the dedicated LFSR, which avoids having to go through the CPU or the memory to read and write the flash memory and maximizes the throughput. Thereby, in order to program a flash page, the CPU only has to initialize the LFSR with a pattern that is kept in memory for later reference. Thereafter, the LFSR directly feeds the flash memory bus with consecutive bytes. To read back the random pattern and count the number of faulty bits, the CPU initializes the LFSR with the pattern that was used to write the page previously and initiate a read procedure. For each byte read, we accumulate into a register the hamming distance between the byte coming from the flash memory bus and the LFSR. At the end of the page reading, the register will report the total number of faulty bits.

While these safeguards are sufficient to provide reliable results in the general case, specific experiments might require more caution in the design of experiment. These will be discussed in the next chapters together with the corresponding experiments.

# 3.5 Related Work

Many researchers rely on characterization to propose different storage strategies, to define models describing low-level aspects of device, or simply to give insights on unpublished properties. We will list some of them here.

Mielke et al. [45] study the recovery process of flash memory cells discussed in Section 3.3.3. Over time, when the cells are not stressed, trapped charges tend to leave progressively the oxide layer, which corresponds to the cell healing or recovering. Accordingly, Mielke et al. let the cell recover for variable amount of time to characterize the recovery effect. In particular, they use the fact that high temperatures accelerate this effect to simulate long periods by baking the flash in an oven at 125°C.

Joo et al. [32] designed an energy characterization platform for NOR flash memory chips to measure the energy consumption associated to each programming level and find significant differences between them. Accordingly, they propose to trade off some of the storage density for energy reduction by favoring some data patterns with an *energy-aware* encoding approach that minimizes the data programming energy cost.

On a similar idea, Grupp et al. [22] designed a characterization platform for NAND flash memory chips to measure the energy consumption and latency associated to the programming, reading and erasing. Without prior knowledge on the partial programming scheme of MLC described in Section 2.3, they identify the difference in energy and time required to program LSB and MSB pages. Furthermore, they acknowledge the fact that the programming time decreases with the cells aging. Accordingly, they propose several strategies to adapt the write performance depending on the workload.

Desnoyers [17] characterizes the performance and endurance of several SLC and MLC NAND flash chips and compares his measurements with the numbers specified by the manufacturers. Similarly to Grupp et al., Desnoyers finds that the programming latency decreases as the cells get weaker. Furthermore, he evaluates the degradation speed and endurance of the chips and estimates it to be around two orders of magnitude larger than specified. Yet, during this evaluation, only a single page is worn out, which does not allow assessing the disturbance effects. Furthermore, the written data is read right after being programmed; therefore, the retention time is not considered, which would be essential to compare the endurance with the specification.

Later, Grupp et al. [23] characterized a large set of SLC and MLC NAND flash chips from various node process sizes. They evidenced the degradation of NAND flash memory characteristics, when going for smaller process sizes and larger densities. Both latency and endurance are degraded with smaller cells and if this trend persists in the future, some important characteristics of flash memory storage will not be as appealing as they are today. Our work contributes to find original and architectural solutions to break this tendency. On a 30 nm class NAND flash chip, Cai et al. [6] characterize separately various sources and types of error. Examples of error sources and types that they consider are read disturb, program disturb, erase errors and retention errors. Furthermore, they identify pages within a block that are systematically more reliable than their neighbors are. They compare how each type of error contributes to the global BER and conclude that the retention time is the most significant factor, although it is difficult to compare factors having completely unrelated units.

Other pieces of work [13, 4] characterize full flash storage systems, which include the FTL. In this type of experiments, the results are mainly dependent on the FTL efficiency rather than the underlying characteristics of the flash. In this thesis, we restrict our characterization to low-level physical properties and exclusively experiment on raw NAND flash chips.

All these pieces of work helped progressively the scientific community to get a deeper understanding of flash memory [18]. We hope that our work will serve the same purpose and help the community to propose new relevant storage strategies.

# 3.6 Conclusion

Experimenting on real flash memory is the most reliable way to validate assumptions when defining novel ways to access the flash memories that involve unspecified mechanisms. Designing reliable experiments highlighting only the effects from the set of factors that we are interested in requires understanding the various factors influencing flash performance. Many bright ideas have to be rejected simply because they are built on wrong assumptions. In this chapter, we detailed the various factors that must enter into consideration when characterizing neglected physical properties of NAND flash memory. We presented our experimental setup and described how to prevent undesired factors to bias the results. We discussed the general procedure of the experimentation, leaving more specific aspects to be described later, in corresponding chapters. In the next chapters, we will propose unconventional methods that change the way flash is degraded. For those methods, it is crucial to provide a good characterization of their effects in order to qualify them adequately for actual storage systems.

# 4 Libra: Balancing Mixed SLC-MLC Wear

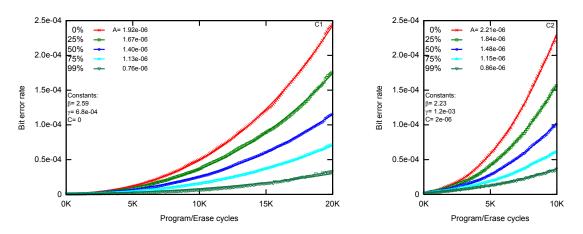

In this chapter, we present and characterize a first example of neglected physical property. Specifically, we evaluate on real flash chips the wear difference when programming one versus two bits in an MLC. Thanks to these experiments, we contradict previous beliefs expecting that writing a single bit would reduce the total number of bit writable during a flash device lifetime compared to a regular use of MLC. With these findings, we bring flash storage devices more flexibility and potential to improve both performance and lifetime.

## 4.1 Introduction

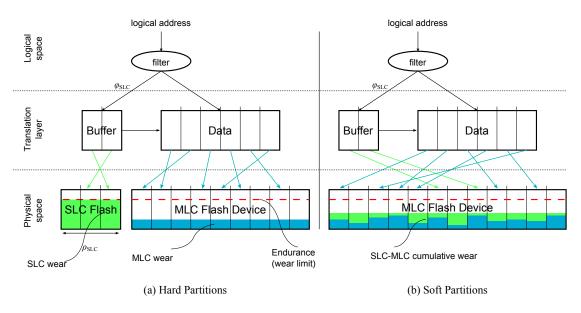

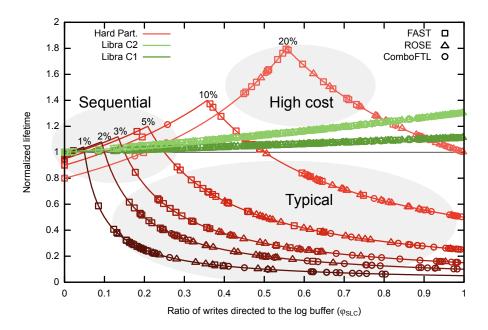

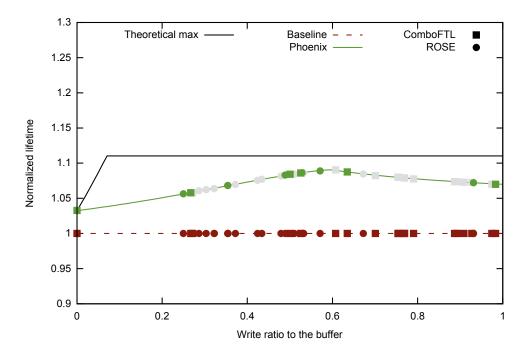

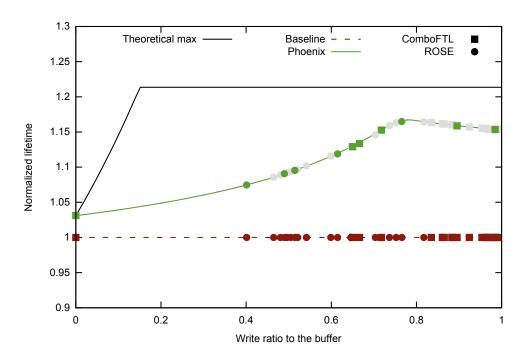

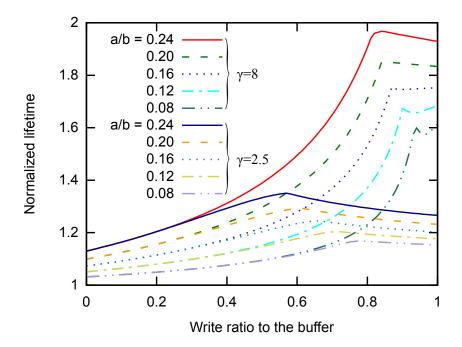

As discussed in Section 2.4, Hybrid-FTLs [15, 16, 36, 37, 39] try to simultaneously achieve the benefits of coarse and fine grained mappings by dividing the flash memory into two regions: (1) a large data partition, which is addressed at the block-level, and (2) a small log buffer partition (typically less than 10% of the storage capacity), which is addressed at the page-level. Considering that a significant amount of write accesses gets directed to the small buffer partition, previous work [11, 26, 52, 47] proposed to build the small *buffer* partition from SLC flash, which provides high performance and low energy consumption but poor density, and the larger *data* partition on MLC of lower performance but higher density. As a result, the flash device has the potential to exhibit performances comparable to SLC (particularly for frequent local updates) while keeping the area efficiency of MLC to a great extent. However, these authors largely disregarded the effect of such SLC-MLC partitioning on the device lifetime. All the previous pieces of work suggest managing the SLC and MLC partitions as distinct physical parts, which can lead to a serious reduction in lifetime. We show that such a configuration can reduce the lifetime by more than half compared to a regular MLC device, assuming typical buffer sizes and utilization. Importantly, MLC endurance is already one order of magnitudes shorter than SLC endurance [23]. Consequently, any further reduction of lifetime may jeopardize the use of SLC-MLC partitions in a practical system, despite their significant advantages in performance and density. Figure 4.1(a) suggests how the extensive use of the buffer partition, due to a particular application write pattern, results in an unbalanced

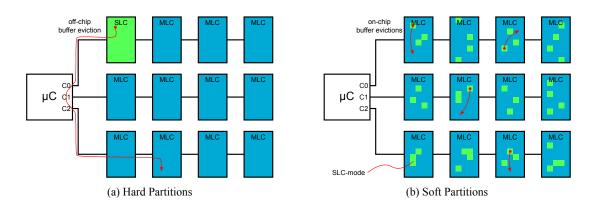

Figure 4.1: **Hard versus soft partitioning.** A hybrid-FTL redirects small writes to a page-level mapped buffer and directs large sequential writes directly to the block-level mapped data partition. The buffer uses SLC to benefit from low write latency and low energy, while the data uses MLC for density. When writes are unbalanced across buffer and data, a hard partition will wear faster than the other, while soft partitioning (the contribution of the present chapter) allows balancing the wear on the global device.

stress causing the device to fail well before most of its cells deteriorate above their maximum wear level (the large data partition is still healthy).

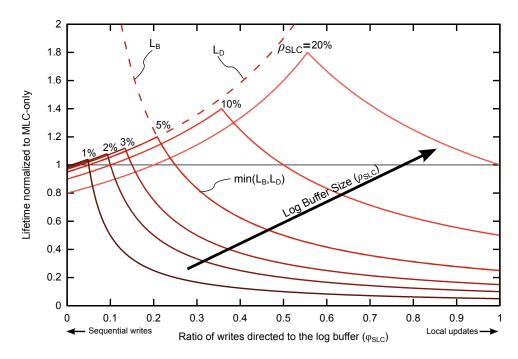

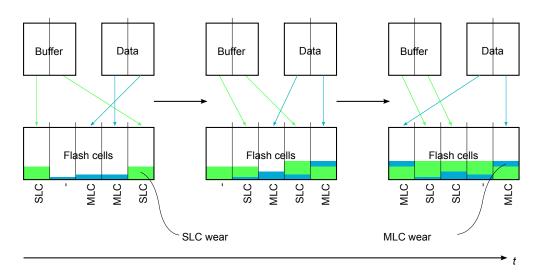

Accordingly, we introduce in this chapter *Libra*, a soft SLC-MLC partitioning architecture that maximizes the device lifetime by dynamically changing the physical allocation of the buffer in order to balance the cumulated stress of each individual flash block. Such technique relies on the fact that an MLC can be managed as an SLC while largely keeping the performance benefits of a physical SLC. Figure 4.1(b) illustrates a device implementing *Libra*, where the buffer uses SLC-mode and each cell has a cumulated wear from MLC- and SLC-mode that can be globally balanced. The proposed soft partitioning is built from a single flash technology instead of two for the hard partitions, which simplifies many aspects of the storage architecture. Furthermore, it can be adapted to existing hybrid-FTLs with minimal effort to significantly increase the device lifetime (between  $1.5-10 \times$  for typical scenarios), while displaying the same benefits in performance, energy and density than hard partitioning. *Libra* is practical and attractive, enhancing an MLC device with performances close to SLC at a modest penalty in density while still being able to provide lifetimes slightly superior to MLC at virtually no extra cost.

# 4.2 SLC-MLC Hybrid Storage

In this section, we introduce SLC-MLC hybrid storages and provide a model to quantify their lifetime. MLC devices store multiple bits per memory cell providing a larger bit density and hence a smaller cost per bit. However, manipulating MLCs is trickier than SLCs: the higher precision required to differentiate the multiple voltage levels translates into about  $3-4\times$  slower page programs and consumes more energy [22]. Furthermore, because of reduced margins between the voltage thresholds, MLC is more sensitive than SLC to charge losses and neighboring cell interferences that typically affect flash reliability, which translates into about an order of magnitude shorter endurance [23]. Therefore, MLC offers a higher bit density than SLC at the expense of a lower performance, higher energy consumption, and reduced lifetime.