### **Energy Efficient VLSI Circuits for MIMO-WLAN**

#### THÈSE N° 6386 (2014)

PRÉSENTÉE LE 31 OCTOBRE 2014

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE CIRCUITS POUR TÉLÉCOMMUNICATIONS

PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Carl Christian Sten Dominic SENNING

acceptée sur proposition du jury:

Prof. D. Atienza Alonso, président du jury Prof. A. P. Burg, directeur de thèse Prof. H. Bölcskei, rapporteur Prof. Y. Leblebici, rapporteur Prof. H. Meyr, rapporteur

The two words 'information' and 'communication' are often used interchangeably,

but they signify quite different things.

Information is giving out; communication is getting through.

— Sydney J. Harris

♥ To my beloved wife Henriette ♥

# Acknowledgments

I would like to thank my PhD adviser Prof. Andreas Burg for giving me the opportunity to work on such an interesting research project and for providing me with a stimulating environment at the start-up company Celestrius Inc., the signal processing circuit and system group at ETH Zurich, and eventually at the telecommunication circuit laboratory at EPFL Lausanne. Furthermore, I want to express my gratitude to Prof. David Atienza, Prof. Yusuf Leblebici, Prof. Heinrich Meyr, and Prof. Helmut Bölcskei, who agreed on being a member of my PhD jury.

Many thanks to my colleagues at Celestrius Inc. for sharing many interesting thoughts and ideas. Amongst others, I would like to particularly thank Simon Häne, Flavio Carbognani, Stefan Zwicky, Claudio Fölmli, Pierre Greisen, Ulrich Schuster, Moritz Borgman, Mikael Feriencik, and Daniel Wagner.

A very special thanks goes to Hubert Käslin, Frank Gürkaynak, and Beat Muheim from the microelectronics design center at ETH Zurich, who provided so much support during all ASIC projects I worked on. They further provided, together with the integrated systems laboratory from ETH Zurich, excellent courses in VHDL design. Especially, the course book, written by Hubert Käslin, provided many insight in digital integrated circuit design and helped my countless times. Furthermore, I would like to thank my colleagues at ETH Zurich from the integrated system laboratory and from the signal processing circuit laboratory. Amongst others, special thank you for interesting discussions to Christian Benkeser, Christoph Studer, Markus Wenk, Peter Lüthi, Stefan Eberli, David Perels, Luka Henzen, and Jürg Treichler.

Then, I would like to thank the members of the telecommunication circuit laboratory at EPFL Lausanne for the good team spirit. For being very active in social event organization, I would like to thank Nicholas Preyss, Jeremy Constantin, Alexios Balatsoukas, Pavle Belanovic, and Maitane Barrenetxea. Moreover, I would like to thank Georgios Karakonstantis, Adi Teman, and Pascal Meinerzhagen for the numerous discussions and their advice.

On a personal level, I am deeply grateful to my parents Mikael and Brita Senning for their continuous support all along the way of my education. Sincere thanks are given to my sisters Beatrice, Patricia, and Jasmine for the high level of family loyalty.

Last but certainly not least, I would like to express my gratitude to my wife Henriette Senning for all enduring support, love, and patience. You gave me much of the strength needed for my work.

Lausanne, 10 September 2014

**Christian Senning**

### **Abstract**

Mobile communication – anytime, anywhere access to data and communication services – has been continuously increasing since the operation of the first wireless communication link by Guglielmo Marconi. The demand for higher data rates, despite the limited bandwidth, led to the development of multiple-input multiple-output (MIMO) communication which is often combined with orthogonal frequency division multiplexing (OFDM). Together, these two techniques achieve a high bandwidth efficiency. Unfortunately, techniques such as MIMO-OFDM significantly increase the signal processing complexity of transceivers. While fast improvements in the integrated circuit (IC) technology enabled to implement more signal processing complexity per chip, large efforts had and have to be done for novel algorithms as well as for efficient very large scaled integration (VLSI) architectures in order to meet today's and tomorrow's requirements for mobile wireless communication systems.

In this thesis, we will present architectures and VLSI implementations of complete physical (PHY) layer application specific integrated circuits (ASICs) under the constraints imposed by an industrial wireless communication standard. Contrary to many other publications, we do not elaborate individual components of a MIMO-OFDM communication system stand-alone, but in the context of the complete PHY layer ASIC. We will investigate the performance of several MIMO detectors and the corresponding preprocessing circuits, being integrated into the entire PHY layer ASIC, in terms of achievable error-rate, power consumption, and area requirement. Finally, we will assemble the results from the proposed PHY layer implementations in order to enhance the energy efficiency of a transceiver. To this end, we propose a cross-layer optimization of PHY layer and medium access control (MAC) layer.

More specifically, at the beginning of the thesis we provide an introduction to the standard IEEE 802.11n, including a discussion of critical constraints imposed by the standard to PHY layer implementations. Further, we present and explain in detail a PHY layer implementation of IEEE 802.11n to provide the context for our subsequent focus on the MIMO detector and specifically on corresponding matrix preprocessing algorithms. Contrary to other works that focus mostly on specific isolated blocks, we discuss several detectors in the context of the overall PHY layer which turns out to have important implications from an implementation perspective. In the first main contribution of this thesis, we develop an architectural template and a design methodology to systematically explore the design space for problems that involve a large number of independent executions of algorithms based heavily on linear algebra. The objective is to provide the basis for the subsequent development of various complex channel-matrix preprocessing techniques, required for the MIMO-OFDM WLAN system under consideration in this thesis.

In the second contribution in Chapter 3, we then focus on linear detection. We discuss hardware architectures for two types of the channel-matrix preprocessing circuits and put them into the context of the PHY layer implementation discussed before.

In the third contribution, we describe a single tree-search (STS) sphere decoder (SD) based MIMO detector and its integration into our reference PHY layer. In this thesis, the focus for the implementation of the STS SD MIMO detector is on the design of an appropriate preprocessing with sorting, as well as on the design of a noise-whitening unit. The latter is required to mitigate the impact of transmit noise. Furthermore, we show again the integration into the overall PHY layer and compare the result to the linear detector based design.

In the fourth contribution, we develop a lattice reduction (LR) aided linear detector based on Seysen's algorithm as an intermediate solution between the linear and the near-optimal STS SD based detector. A number of algorithm improvements and optimizations are proposed to reduce the complexity of the LR preprocessing. Once again, we integrate the design into the reference PHY layer and report area and performance results.

Finally, returning to a system-level view, a novel idea for improving the energy efficiency of an IEEE 802.11n based WLAN receiver is discussed. The basic idea is to extend the PHY layer in such a way that it allows for energy-proportional operation in a sense that energy consumption can be modulated together with the decoding effort. A detailed energy-model of this scalable PHY layer calibrated with post-layout power simulations of the original PHY implementation is used to propose and design an energy-aware rate adaptation strategy. We analyze the potential of such a strategy and show a significant potential for energy savings.

**Keywords:** MIMO, OFDM, VLSI Systems, ASIC, preprocessing circuits for MIMO detectors, PHY layer, energy-efficiency, matrix decompositions, lattice reduction, Seysen's algorithm, energy modeling, rate adaptation, block-floating point, semi-automatic design flow.

# Zusammenfassung

Die Möglichkeiten mobiler Drahtloskommunikation – jederzeit und überall Zugang zu Datenund Kommunikationsangeboten zu haben – ist seit der ersten Funkübertragung von Guglielmo

Marconi kontinuierlich erweitert worden. Das wachsende Verlangen nach höheren Datenraten und

die Limitierung der verfügbaren Bandbreite führten zur Entwicklung von neuen Technologien

wie "multiple-input multiple output" (MIMO) und "orthogonal frequency division multiplexing" (OFDM). Diese beiden Techniken erreichen zusammen eine hohe Bandbreiteneffizienz.

Leider erhöht die Verwendung von Techniken wie MIMO-OFDM auch die Komplexität der

benötigten Signalverarbeitung des Senders, und vor allem des Empfängers. Während es die Fortschritte in der Integrationsdichte von integrierten Schaltungen ermöglichten, immer komplexere

Schaltungen auf einem Chip zu integrieren, waren und sind wesentliche Verbesserungen auch

an den Algorithmen und am Schaltungsentwurf nötig, um die heutige und zukünftige mobile

Kommunikationsinfrastruktur zu ermöglichen.

In dieser Doktorarbeit präsentieren wir darum Architekturen und VLSI Realisierungen einer vollständigen Bitübertragungsschicht (physical layer) für den Standard IEEE 802.11n. Im Gegensatz zu anderen Publikationen untersuchen wir nicht einzelne Teile eines MIMO-OFDM Kommunikationssystem, sondern setzen alle Komponenten in den Kontext der gesamten Bitübertragungsschicht, mit allen Rahmenbedingungen die vom Standard vorgegeben werden. Wir werden im Rahmen dieser Arbeit mehrere MIMO Detektoren und die dazu passenden Vorbereitungsschaltungen, die meistens eine Matrixzerlegung realisieren, vorschlagen und untersuchen. Für alle vorgeschlagenen Schaltungen werden wir die Auswirkung auf die Fehlerrate, den Energieverbrauch und den Flächenbedarf der Bitübertragungsschicht untersuchen. Schliesslich nutzen wir die Resultate aller vorgeschlagenen Schaltungen, um die Energieeffizienz des Empfängers zu erhöhen. Dazu entwickeln wir eine schichtübergreifende Optimierung, welche die "medium access control" (MAC) Schicht sowie die Bitübertragungsschicht umfasst, um den Energieverbrauch für jedes korrekt empfangene Bit stark zu verbessern.

Dazu gibt das erste Kapitel dieser Doktorarbeit eine Einführung zu MIMO-OFDM, wie es in einem der neuesten WLAN Standards, IEEE 802.11n, benutzt wird. Danach untersuchen wir detailliert eine Realisierung einer Bitübertragungsschicht für IEEE 802.11n, um den Kontext für die folgenden Kapitel aufzuzeigen. Im Anschluss werden wir verschiedene MIMO Detektoren und die dazugehörigen Matrixzerlegungsalgorithmen analysieren, optimieren und implementieren. Entgegen anderer Arbeiten, die nur isolierte Schaltungsteile analysieren, diskutieren wir alle vorgeschlagenen MIMO Detektoren im Kontext der gesamten Bitübertragungsschicht. Dies hat wichtige Implikationen für die Realisierung der Schaltungen.

#### Zusammenfassung

Danach entwickeln wir eine architektonische Vorlage und eine dazugehörige Entwurfsmethode für die Implementierung von Schaltungen zur Lösung von vielen unabhängigen, aber gleichartigen Linear-Algebra-Problemen. Der systematische Ansatz erleichtert es uns, von den vielen möglichen Schaltungsrealisierungen die für den Kontext "beste" Variante zu selektieren. Damit bereiten wir die Basis für die Entwicklung von verschiedenen Kanalmatrixzerlegungstechniken, die von allen MIMO Detektoren des untersuchten MIMO-OFDM WLAN Systems benötigt werden.

Darauf folgend diskutieren wir die Realisierung von linearen MIMO Detektoren. Hierfür stellen wir zwei verschiedene Architekturen von linearen MIMO Detektoren und die dazugehörigen Matrixzerlegungsschaltungen für die vorher diskutierte Bitübertragungsschicht vor.

Ausserdem stellen wir einen STS SD basierten MIMO Detektor und seine Integration in die Referenzbitübertragungsschicht vor. Dabei legen wir den Fokus der Diskussion auf die benötigte Matrixzerlegungsschaltung, welche die Datenströme für den Detektor sortiert. Des Weiteren stellen wir eine Methode und ihre Implementierung vor, die Auswirkungen des vom Sender verursachten gefärbten Rauschens auf die Fehlerrate des MIMO Detektors mindert. Auch diese Schaltungen werden in die Gesamtschaltung integriert, um die Resultate mit den vorher diskutierten linearen MIMO Detektoren vergleichen zu können.

Als Kompromiss zwischen dem zuvor vorgestellten linearen MIMO Detektor und dem STS SD basierten MIMO Detektor, entwickeln wir einen linearen MIMO Detektor, der mittels "lattice reduction" (LR) eine deutlich verbesserte Detektionsrate erzielt. Implementiert wird die LR Schaltung basierend auf Seysens Algorithmus. Für diesen werden in dieser Doktorarbeit viele Optimierungen und Verbesserungen vorgeschlagen, die entweder die Schaltungskomplexität reduzieren oder aber die Detektionsrate verbessern. Auch diese Schaltung wird in die Gesamtschaltung integriert, um die benötigte Siliziumfläche, den Energieverbrauch, sowie die Fehlerrate mit den anderen vorher vorgeschlagenen Schaltungen zu vergleichen.

Abschliessend wenden wir uns erneut dem gesamten WLAN-Kommunikationssystem zu und zeigen neue Wege und Ideen auf, um die Energieeffizienz eines IEEE 802.11n kompatiblen Empfängers zu steigern. Die Grundidee ist, die Datenratenanpassung basierend auf Energieeffizienzüberlegungen zu implementieren. Dazu entwickeln wir ein Energiemodel und modifizieren die Bitübertragungsschicht, so dass sich die Energieaufnahme proportional zum Dekodieraufwand verhält. Das benötigte Energiemodell kalibrieren wir anhand von "post-layout" Simulationen und analysieren dann den möglichen Effizienzgewinn für die in der Praxis relevanten Szenarien.

**Stichwörter:** MIMO, OFDM, VLSI Systeme, ASIC, Vorverabeitungsschaltungen für MIMO Detectoren, PHY Schicht, Energieeffizienz, Matrixzerlegung, Gitterreduktion, Seysen's Algorithmus, Energiemodellierung, Ratenanpassung, Blockfliesspunktdarstellung, halbautomatischer Designprozess.

# Contents

| A  | cknov  | vledgme  | ents                                                              | V   |

|----|--------|----------|-------------------------------------------------------------------|-----|

| Al | bstrac | et (Engl | ish/Deutsch)                                                      | vii |

| 1  | Intr   | oductio  | on .                                                              | 1   |

|    | 1.1    | Contri   | butions                                                           | 2   |

|    | 1.2    | Thesis   | Outline                                                           | 5   |

| 2  | A M    | имо с    | OFDM WLAN PHY Layer ASIC for IEEE 802.11n                         | 7   |

|    | 2.1    | The IE   | EEE 802.11n Standard                                              | 8   |

|    |        | 2.1.1    | A Generic IEEE 802.11n Transmitter                                | 8   |

|    |        | 2.1.2    | Frame Formats for IEEE 802.11n                                    | 12  |

|    |        | 2.1.3    | Communication Protocol and Inter-frame Spacing                    | 14  |

|    | 2.2    | An IE    | EE 802.11n compliant PHY Layer ASIC                               | 15  |

|    |        | 2.2.1    | Implementation Strategy                                           | 15  |

|    |        | 2.2.2    | Components of the PHY Layer ASIC                                  | 18  |

|    |        | 2.2.3    | Implementation Results                                            | 31  |

|    | 2.3    | Prepro   | ocessing Architecture for MIMO-OFDM Detectors                     | 35  |

|    |        | 2.3.1    | Typical Preprocessing Algorithms for MIMO Detectors               | 35  |

|    |        | 2.3.2    | Application Specific Processor Versus Pipelined Architecture      | 37  |

|    |        | 2.3.3    | Proposed Design Method for Pipelined Architectures                | 39  |

|    | 2.4    | Summ     | ary                                                               | 46  |

| 3  | Line   | ear MM   | ISE MIMO Detection                                                | 49  |

|    | 3.1    | Algori   | thmic Considerations for MMSE MIMO Detection and Soft-Output Com- |     |

|    |        | putatio  | on                                                                | 49  |

|    | 3.2    | QR De    | ecomposition Based Linear MMSE Detection                          | 51  |

|    |        | 3.2.1    | QR Algorithms                                                     | 52  |

|    |        | 3.2.2    | QR decomposition for Soft-Output MMSE Detection                   | 56  |

|    |        | 3.2.3    | VLSI Implementation                                               | 59  |

|    |        | 3.2.4    | Standalone VLSI Implementation Results and Comparisons            | 65  |

|    |        | 3.2.5    | Integration of the QR Decomposition Based MMSE Detector into the  |     |

|    |        |          | Complete PHY Layer ASIC                                           | 66  |

|    | 3.3    | Moore    | e-Penrose Pseudo Inverse Based Linear MMSE Detection              | 72  |

|   |            | 3.3.1          | Moore-Penrose Pseudo Inverse Computation                                                                                | 73  |

|---|------------|----------------|-------------------------------------------------------------------------------------------------------------------------|-----|

|   |            | 3.3.2          | VLSI Implementation                                                                                                     | 74  |

|   | 3.4        | 3.3.3<br>Compa | Standalone VLSI Implementation Results and Comparison arison of QR Decomposition and Moore-Penrose Pseudo Inverse Based | 77  |

|   |            | MMSE           | E Detection                                                                                                             | 79  |

| 4 | Tree       |                | Based MIMO Detection                                                                                                    | 81  |

|   | 4.1        | _              | cessing Based Computational Complexity Reduction and/or Error Rate                                                      |     |

|   |            | Enhan          | cing Techniques                                                                                                         | 85  |

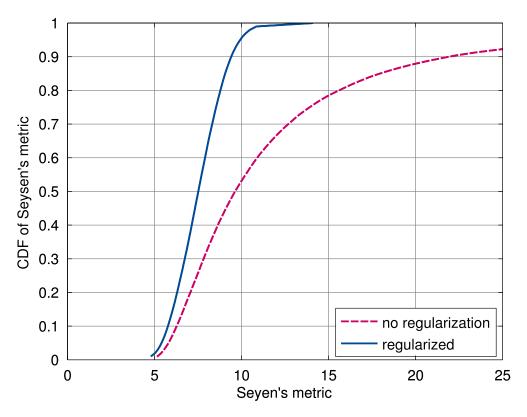

|   |            | 4.1.1          | Regularized QR Decomposition                                                                                            | 85  |

|   |            | 4.1.2          | Spatial Streams Sorting                                                                                                 | 85  |

|   | 4.2        | Regula         | arized and Sorted QR Decomposition for Tree-Search Based MIMO                                                           |     |

|   |            | Detect         | ors                                                                                                                     | 87  |

|   |            | 4.2.1          | VLSI Implementation                                                                                                     | 89  |

|   |            | 4.2.2          | Integration of the STS SD into the Complete PHY Layer ASIC                                                              | 91  |

|   | 4.3        | Transn         | nit Noise-Whitening for Tree-Search Based MIMO Detectors                                                                | 98  |

|   |            | 4.3.1          | Noise Whitening Algorithm                                                                                               | 100 |

|   |            | 4.3.2          | VLSI Implementation                                                                                                     | 101 |

|   |            | 4.3.3          | Integration of the STS SD with the Noise-Whitening Filter into the                                                      |     |

|   |            |                | Complete PHY Layer ASIC                                                                                                 | 102 |

| 5 | Latt       | ice Red        | uction Aided Linear Detection                                                                                           | 107 |

|   | 5.1        | Algori         | thmic Considerations for Lattice Reduction Aided Linear Detection                                                       | 108 |

|   |            | 5.1.1          | Preliminaries                                                                                                           | 109 |

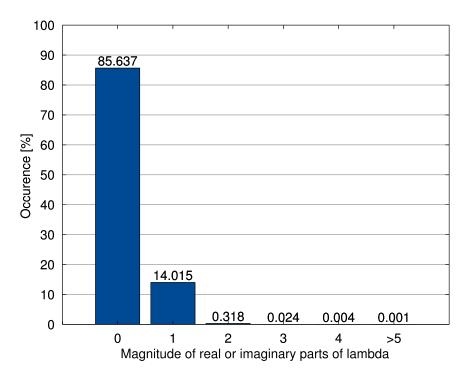

|   |            | 5.1.2          | Seysen's Algorithm for VLSI Implementation                                                                              | 111 |

|   |            | 5.1.3          | Algorithmic Modifications for VLSI Implementation                                                                       | 114 |

|   | 5.2        | Archite        | ecture                                                                                                                  | 121 |

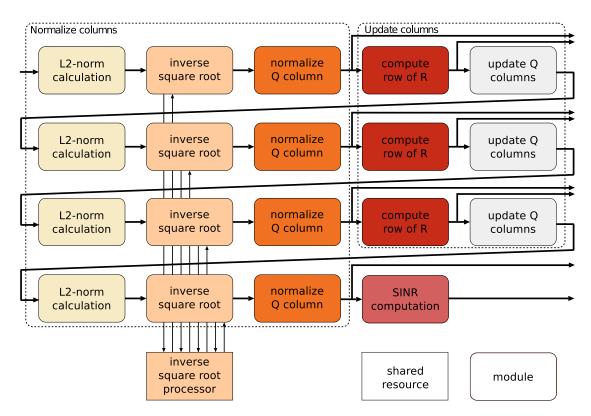

|   |            | 5.2.1          | Preprocessing Architecture                                                                                              | 122 |

|   |            | 5.2.2          | Detection Architecture                                                                                                  | 126 |

|   | 5.3        | Standa         | lone VLSI Implementation Results                                                                                        | 126 |

|   |            | 5.3.1          | ASIC Performance Figures                                                                                                | 128 |

|   |            | 5.3.2          | Comparison of the Proposed Standalone LRALD ASIC to Tree-Search                                                         |     |

|   |            |                | Based and Iterative MIMO Detector Implementations                                                                       | 130 |

|   |            | 5.3.3          | Comparison to other LR Cores                                                                                            | 134 |

|   | 5.4        | Integra        | ation of the LRALD into the Complete PHY layer ASIC                                                                     | 136 |

|   |            | 5.4.1          | Error Rate Performance of the Entire PHY Layer ASIC with a LRALD                                                        | 141 |

|   |            | 5.4.2          | Energy and Power Consumption                                                                                            | 141 |

|   | 5.5        | Compa          | arison of the Proposed PHY Layers with MMSE Detector, STS SD, or                                                        |     |

|   |            | LRAL           | D                                                                                                                       | 143 |

|   |            | 5.5.1          | Area Comparison                                                                                                         | 144 |

|   |            | 5.5.2          | Error Rate Performance Comparison                                                                                       | 146 |

|   | <i>5 (</i> | C              | arv                                                                                                                     | 149 |

| 6  | Cros    | ss-Laye       | r Energy-Efficiency Enhancement                         | 151 |

|----|---------|---------------|---------------------------------------------------------|-----|

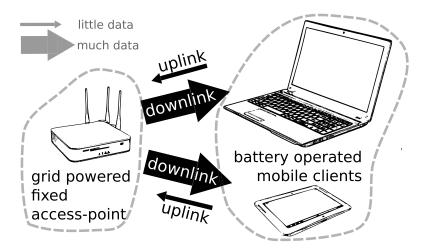

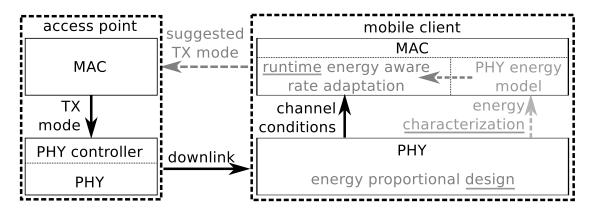

|    | 6.1     | Systen        | n Model                                                 | 153 |

|    |         | 6.1.1         | Transmission Scenario                                   | 153 |

|    |         | 6.1.2         | Proposed Cross-Layer Energy-Efficiency Enhancement      | 154 |

|    |         | 6.1.3         | Receiver Architecture                                   | 156 |

|    | 6.2     | Receiv        | ver Energy Model                                        | 157 |

|    |         | 6.2.1         | Discussion of the Energy Model                          | 158 |

|    |         | 6.2.2         | Energy Model Calibration                                | 158 |

|    | 6.3     | Modifi        | ication to the PHY Layer For Enhanced Energy Efficiency | 160 |

|    |         | 6.3.1         | Energy Proportionality Through Suboptimal Detectors     | 161 |

|    |         | 6.3.2         | Energy Proportionality Through DVFS                     | 161 |

|    | 6.4     | Rate A        | Adaptation                                              | 162 |

|    | 6.5     | Result        | s                                                       | 165 |

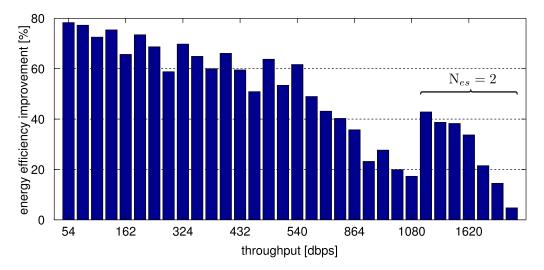

|    |         | 6.5.1         | Results for Fixed PPDU Size                             | 166 |

|    |         | 6.5.2         | Results for Varying PPDU Size                           | 167 |

|    | 6.6     | Summ          | ary                                                     | 168 |

| 7  | Sum     | mary a        | and Conclusions                                         | 171 |

| Gl | ossar   | y             |                                                         | 175 |

| Sy | mbol    | s and N       | otation                                                 | 179 |

| Bi | bliogr  | aphy          |                                                         | 181 |

| Li | st of I | igures        |                                                         | 193 |

| Li | st of T | <b>Tables</b> |                                                         | 197 |

| Li | st of I | Publicat      | tions                                                   | 199 |

| Cı | ırricu  | lum Vi        | tae                                                     | 201 |

# 1 Introduction

Wireless communication has evolved over the last few decades from an expensive, rarely used technology to a standard feature integrated into many mass products, such as notebooks, tablet computers, and smart phones. The rapidly growing number of users, each constantly requesting for higher data rates, and the limitation of the available bandwidth, led to the development of wireless communication techniques with a high bandwidth efficiency. One of these techniques is multiple-input multiple-output (MIMO) communication, where multiple data streams are concurrently transmitted within the same frequency band. MIMO is often combined with a technique called orthogonal frequency division multiplexing (OFDM), dividing a wide-band communication link into multiple orthogonal frequency flat channels.

Techniques that increase the bandwidth efficiency, such as MIMO-OFDM, significantly increased requirements regarding capabilities of signal processing at the transmitter and the receiver. The implementation of the increased signal processing requirements into integrated circuits (ICs) was enabled by the fast improvement in IC technology. The reduction of the feature size led to higher processing capabilities, lower production costs, and lower energy consumption of each integrated circuit.

However, the rapid adoption of wireless techniques is only partially attributed to the IC technology evolution. A large contribution to the success of wireless technologies came from research efforts in very large scaled integrated (VLSI) and architectural design. The combined effort of the researchers resulted in a large number of publications. Solely for MIMO communication, over 25'000 publications have been issued in the last two decades on IEEEXplore. In the same period, more than 31'000 publication present research results on OFDM.

In this significant number of publications all components of a MIMO-OFDM communication system are elaborated. There are many publications about synchronization of MIMO-OFDM system in time and in frequency domain [WSF04, PSF07, PHB+06]. Further publications present architectures and implementations of FFTs [KNM+13, WYC+14, Joh92] used for OFDM. Another large group of publications discusses algorithms, optimization methods, and implementations of MIMO detectors [CHJR10, BMR+09, BSS+10, SG09, WKA+12, YW02]. Further papers discuss

data encoding or decoding [FG93, HBP+05, CMM13, RBBH14], either from an information theoretic point or from the implementation side. A further topic presented in many research papers is impairment mitigation [SWB10, Per08]. However, most of the publications focus on individual tiny components of the entire communication system and elaborate on this component isolatedly. Hence, many publication ignore inter-dependencies of different components of a MIMO-OFDM system or use ideal, or at least simplified, assumptions while discussing their system component.

Another large group of publications optimize the overall MIMO-OFDM system based on measurements or simplified models of fairly large components of a wireless communication system. A typical example is research on entire network interface cards (NICs) [FN01, AGD<sup>+</sup>11, LPLW12]. Mostly, these publications treat the underlying MIMO-OFDM system as a black box.

Unfortunately, the interaction of all components in a MIMO-OFDM system can only be studied in case the entire system is actually built. Although, also for algorithmic consideration all components have to be defined, many interaction and dependencies of the individual components can only be investigated in case an actual MIMO-OFDM system is implemented. More specifically, it's only possible on the entire implemented system to truly compare the implementation of different algorithms for a specific component, as different realizations of the same component may interact differently on specific characteristics of other components. A typical example is the MIMO detector, where more sophisticated near APP detectors suffer significantly from colored noise, while simpler linear detectors are not affected. Other components of the MIMO-OFDM system may be sensitive to precise frame synchronization, to the accuracy of the FFT, to the number of bits used to represent the reliability of a detected bit, or to all sorts of noise, such as thermal-, quantization-, saturation-, and phase-noise.

To account for all these effects, we investigate on an entirely IEEE 802.11n compliant physical (PHY) layer in this thesis, and prove all proposed circuits to be working withing that PHY layer. Furthermore, the integration of all proposed circuits into the PHY layer forces the implementation of a complete system without unrealistic or idealized assumptions for the circuit components of the entire MIMO-OFDM communication system.

#### 1.1 Contributions

The goal of this thesis is to show how silicon area usage, error rate performance, and energy efficiency of wireless MIMO-OFDM communication systems can be optimized. In the entire thesis, we strictly apply an industry standard in order to provide relevant results for real-life applications and practical implementations. However, most of the proposed approaches and findings can also be applied to other wireless MIMO-OFDM systems.

At the beginning of this thesis, the signal processing task with the highest computational complexity within an IEEE 802.11n compliant PHY layer implementation, the separation of the spatially

multiplexed data streams, is identified. We further propose an architecture and a design method to implement different variations of this signal processing task. In addition, we provide multiple implementation for this component, which we refer to as space time processing and which all include a MIMO detector. The proposed implementations of the space time processing differ significantly in computational complexity (i.e., required silicon area), error rate performance, and power consumption. In the elaboration of the space time processing, we focus on the one-time preprocessing circuit, that in many implementations has a significantly larger silicon area compared to the actual MIMO detector. This one-time preprocessing circuit computes all operations for MIMO detection that do not depend on the actual transmitted data symbols. We further show, for all propsoed implementations of the space time processing, how they are integrated into complete PHY layer ASICs.

Finally, we assemble the findings in order to propose a cross-layer energy-efficiency optimization. To this end, we propose a receiver based, energy-aware rate adaptation (RA) scheme. Based on a novel PHY layer energy model and a genie based RA, we lay out the achievable efficiency gains of this approach.

In detail, the contributions of this thesis are the following:

- A wireless MIMO-OFDM communication industrial standard, IEEE 802.11n, is described

in order to identify critical specifications of the standard that significantly impacts the

architecture of the transmitter and the receiver.

- A complete real-life PHY layer chip is described and analyzed in terms of functionality and area requirements. Based on this, the key components for an energy efficient PHY layer design are identified and the true silicon complexity of the used circuit components is reported, including all the required helper circuitry (e.g., control path, buffer, monitoring). The integration of a complete PHY layer ASIC that could be used in a real product prevents from unrealistic simplifications during the design and testing phase, and thus makes the results more relevant for practical implementations. Therefore, all the circuits proposed in this thesis have been integrated into PHY layer ASICs in order to evaluate their *true* silicon implementation costs.

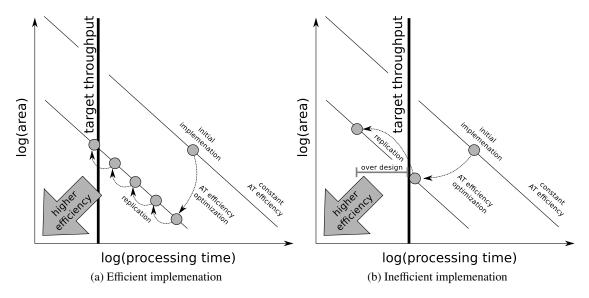

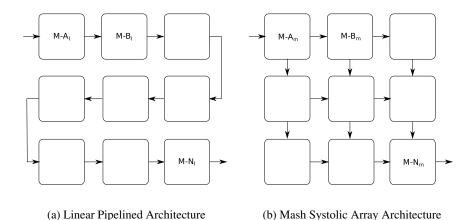

- To implement the one-time MIMO preprocessing circuit (and in some cases also the MIMO detector) with minimal area while achieving the stringent latency requirements imposed by the communication standard, we analyze the data structure and the data flow seen in the space time processing. Based on this data flow and knowledge about typical algorithms utilized in one-time preprocessing circuits, we propose a pipelined architecture and a suitable implementation strategy. This strategy extends the achievable Pareto-optimal front in the area times time domain, that is close to the area times time efficiency of the most efficient implementation. Therefore, the implementation strategy allows to implement circuits that are tailored for the throughput and latency requirements of the system, without sacrificing the area times time efficiency. Furthermore, the proposed implementation

strategy increases the implementations reusability in case the component is used for a communication system with altered throughput or latency requirements.

The proposed pipelined architecture and implementation strategy are applied to several space time processing circuits employing three different MIMO detection algorithms. Thereby we demonstrate their practical usability and efficiency.

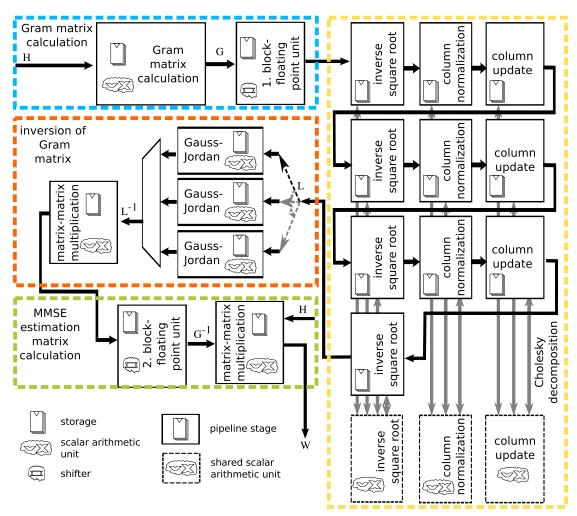

- We present two space time processing circuits employing linear MMSE MIMO detectors. These implementations result in low silicon area requirements and low power consumption, but unfortunately, linear MMSE MIMO detectors suffer from a low to moderate error rate performance. One of the implementations is based on a QR decomposition triangularizing the linear equation system, a subsequent back-substitution based MIMO detection, and concluded with a reliability of the estimation (i.e., LLRs) calculation circuit. The second MMSE MIMO detector implementation employs a Cholesky decomposition based Moore-Penrose pseudo matrix inversion within the one-time preprocessing. This inverted matrix is used in the subsequent MIMO detector, during the data detection phase, to compute an estimate of the bit sequence for each receive symbol.

- The space time processing employing linear MMSE MIMO detectors represent low complexity solutions. To cover the entire complexity range, we propose space time processing circuits employing tree-search based MIMO detectors with near a posteriori probability (APP) error rate performance. To this end, we discuss a suitable one-time preprocessing circuit for tree-search based MIMO detectors. We show the area requirements and the error rate performance achieved by entire PHY layer ASICs with such tree-search based MIMO detectors. Finally, we show for such APP MIMO detectors, how transmit impairments can be mitigated in the corresponding one-time preprocessing circuits.

- While linear MIMO detector based space time processing suffers in terms of error rate performance, APP MIMO detector based space time processing results in significantly increased area requirements of corresponding PHY layer ASICs. Therefore, we propose a compromise in terms of error rate performance and computational complexity. To this end, we enhance the suitability of Seysen's lattice reduction algorithm for VLSI implementations by proposing algorithmic modifications. We implement the space time processing with hard-output lattice reduction aided linear detection (LRALD) and proof its superior error rate performance compared to soft-output linear detection. We also show, that for practical systems using a large number of spatial streams and a high modulation order, LRALD may outperform sphere decoder based near APP detection.

- Finally, it is explained in this thesis how the energy efficiency of the entire PHY layer ASIC can be improved by appropriate management. We propose a cross-layer energy-efficiency optimization for a typical down-link scenario. For this scenario, we develop an energy-model of the PHY layer used in a receiver and show potential improvements in terms of energy spend per successfully received data bit. These improvements result from a joint optimization of the PHY layer in terms of algorithm, architecture, and circuit

techniques, as well as the MAC layer in terms of rate adaptation. We provide energy data of the achievable gains based on our proposed approach, for fixed and varying frame sizes.

#### 1.2 Thesis Outline

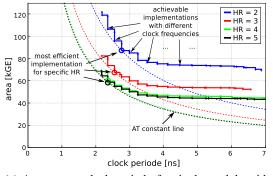

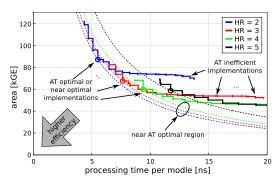

In Chapter 2, we first investigate the industry standard for wireless MIMO-OFDM communication, IEEE 802.11n, in order to identify the necessary signal processing tasks and to identify critical specifications, such as, receiver and transmitter latency. We then elaborate a standard compliant PHY layer ASIC design, and present the corresponding area and error rate figures. Based on this elaboration, the space time processing in the receiver is identified as the most complex computational task in PHY layer ASICs for MIMO-OFDM communication systems. Surprisingly, we identify the one-time MIMO preprocessing, being an important part of most MIMO detection algorithms, as significantly area dominant. Therefore, we propose a pipelined architecture, suited to implement one-time preprocessing circuits for MIMO-OFDM PHY layer ASICs. Furthermore, we suggest an implementation strategy for the pipelined architecture and show how this strategy can be used to tune the implementation for the specific system requirements – in terms of throughput and latency – without significantly decreasing its area times time efficiency.

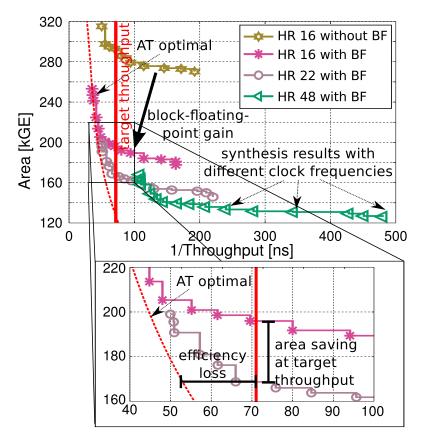

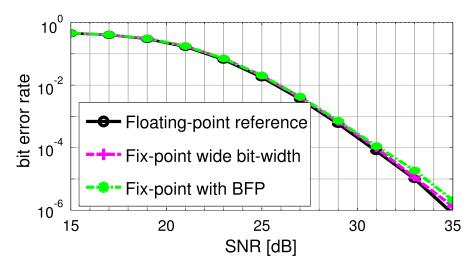

The developed architecture and design strategy are applied, in Chapter 3, to two different space time processing circuits employing linear MIMO detectors. For these low complexity MIMO detectors, we propose to use either a QR decomposition based one-time preprocessing circuit, or a Cholesky decomposition based Moore-Penrose matrix inversion as preprocessing circuit. Along with explaining the algorithm, the architecture, and the VLSI implementation of both space time processing circuits, we further show how the area consumption of the circuits can be improved by using a special floating point format for the representation of the computed data items.

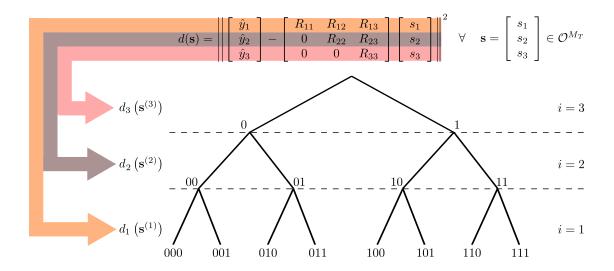

In addition to the low complexity solutions presented in Chapter 3, we investigate the implementation of a space time processing circuit with near APP MIMO detectors. Therefore in Chapter 4, we integrate tree-search based MIMO detectors. Similar to the integration of the MMSE detectors, we focus on the implementation of suitable one-time MIMO preprocessing circuits. The one-time MIMO preprocessing implementation triangularizes the channel matrix and therefore is a crucial prerequisite to perform any tree-search based MIMO detection algorithm. We also demonstrate how to implement techniques to enhance the error rate performance or to reduce the average computational complexity of tree-search based MIMO detectors within the MIMO preprocessing circuit.

We further analyze, in Section 4.3, the impact of transmit impairments to near APP tree-search based MIMO detectors, such as the single-tree-search sphere decoder. Based on this analysis, we propose, for the first time, a VLSI implementation of an extended one-time preprocessing circuit, being able to mitigate the negative effects of real-world transmit impairments.

#### **Chapter 1. Introduction**

As shown in Chapter 3, the use of linear MIMO detectors results in low area requirements, low power consumption, but unfortunately also poor error rate performance. And as presented in Chapter 4, near APP MIMO detectors provoke a large increase in computational complexity and silicon area consumption. Furthermore, near APP MIMO detectors significantly suffer in case the noise characteristics deviate from the assumptions made during the development of the algorithm. Therefore, we propose a novel space time processing circuit, achieving a compromise in terms of error rate performance and computational complexity, i.e., a compromise between linear MIMO detection and near APP MIMO detection. The novel circuit comprises an one-time preprocessing circuit based on a modified version of Seysen's algorithm for lattice reduction and a corresponding linear MIMO detector. Finally, we demonstrate how the energy efficiency per bit of the receiver can be significantly improved for this space time processing circuit.

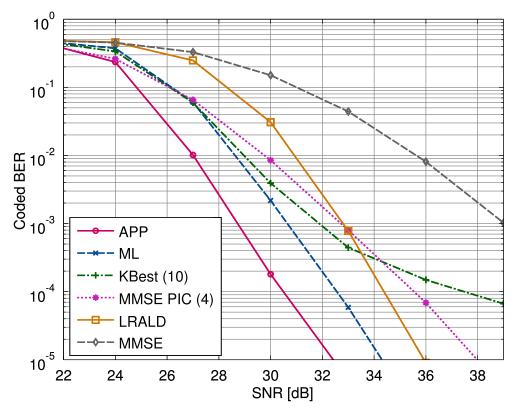

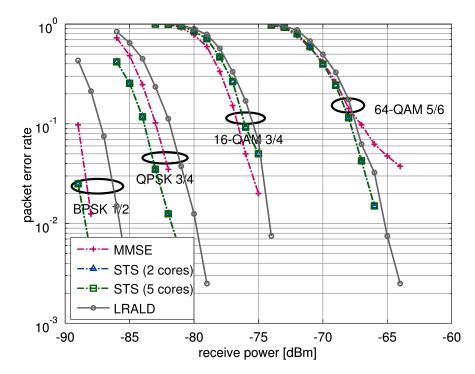

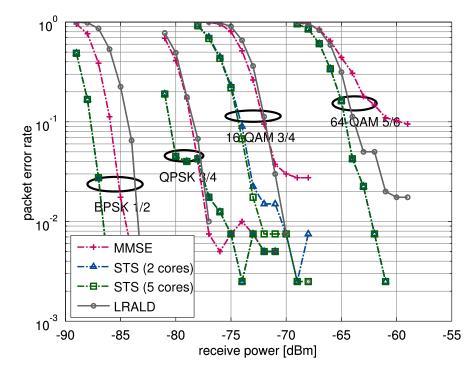

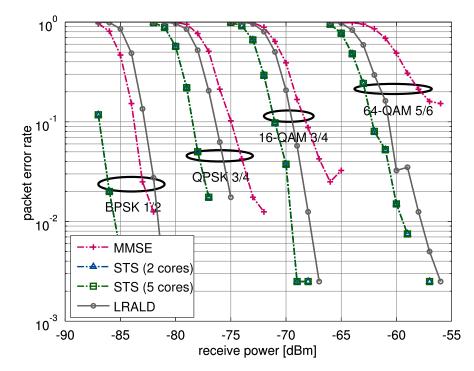

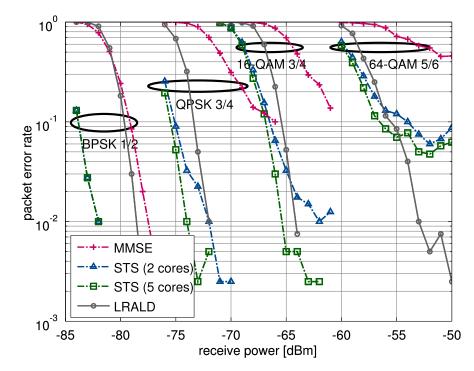

In Section 5.5, we compare the PHY layer implementations employing linear MIMO detectors, near APP MIMO detectors, and the novel LRALD in terms of silicon area consumption and error rate performance.

Finally, all findings are combined in order to enable an energy-efficient PHY layer design, in Chapter 6. To this end, a joint optimization of MAC layer rate adaptation, dynamic selection of a detection algorithm, and implementation of the PHY layer is proposed. Initially, the energy consumption of all the components of the PHY layer ASIC are analyzed. Based on this, an energy per bit consumption model is developed. This energy model is used to evaluate several strategies to enhance the energy efficiency of a receiver. The evaluated methods include detection algorithm selection, adaption of the number of active receive chains, and "dynamic" voltage and frequency scaling, which are combined with a receiver based rate adaptation. This rate adaptation is happening in the medium access layer and optimized for enhanced energy efficiency. Together, all methods jointly optimize and improve the PHY layer's energy efficiency.

Chapter 7 summarizes the achieved findings presented in the various chapters concluding this thesis.

# 2 A MIMO OFDM WLAN PHY Layer ASIC for IEEE 802.11n

Nowadays, IEEE 802.11n is a popular wireless communication standard, used in many products, from computers to smart phones. The standard specifies a multiple-input multiple-output (MIMO) extension to the orthogonal frequency division multiplexing (OFDM) based communication standard IEEE 802.11a. In addition, the maximum bandwidth used for IEEE 802.11n has doubled compared to IEEE 802.11a. With both extensions, MIMO and the increased bandwidth, the maximum achievable data rate, specified in the IEEE 802.11n standard, reaches 600 Mbits/s. However, not only the maximum data rate is increased, the MIMO extension of IEEE 802.11n also enables to enlarge the range and the coverage of a wireless communication system.

In this chapter, we will review the specifics of the wireless standard IEEE 802.11n, which are required to generate transmitted signal compliant to the standard. The review starts with elaborating a generic IEEE 802.11n transmitter as specified by the standard. Based on this generic transmitter, we show all signal processing operations required to generate the transmitted signal. In a next step, we analyze the frame formats specified in IEEE 802.11n. The frame formats together with the transmission protocol are impacting several important design decisions, which are required for a standard compliant PHY layer implementation.

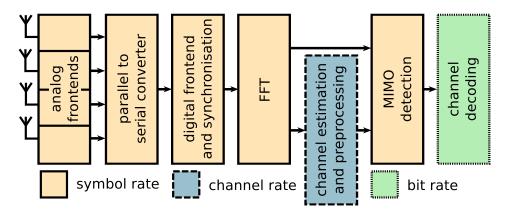

After presenting the necessary specifics of the IEEE 802.11n standard, we elaborate the implementation of a standard compliant PHY layer application specific integrated circuit (ASIC). We explain the design principles used for the implementation of the PHY layer ASIC and the processing paradigm employed by all its components. Then, we will present the IEEE 802.11n compliant transmitter. While the signal processing tasks have been explained based on the generic transmitter, during the discussion of the implementation of the transmitter we focus on timing related issues, imposed by the protocol defined in the IEEE 802.11n standard. Thereafter, we outline each component of the receiver, discussing their signal processing task. Finally, we will present the VLSI realization for selected components of the receiver.

Based on the realization of the entire transceiver, we will identify the demultiplexing of the

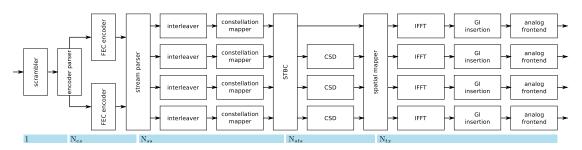

Figure 2.1 – Generic transmitter defined in IEEE 802.11n.

spatial streams (often referred as MIMO detection) as the signal processing task with the highest computational complexity in the ASIC. As we will further show, a significant part of the signal processing complexity, required to perform MIMO detection, has to be performed only once per frame. We will focus in almost the entire thesis on this preprocessing part of the MIMO detector that enables to relax the stringent latency constraint on the receiver imposed by IEEE 802.11n.

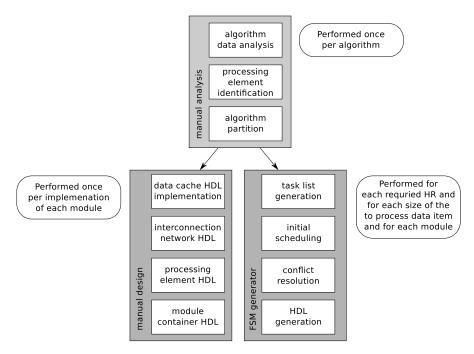

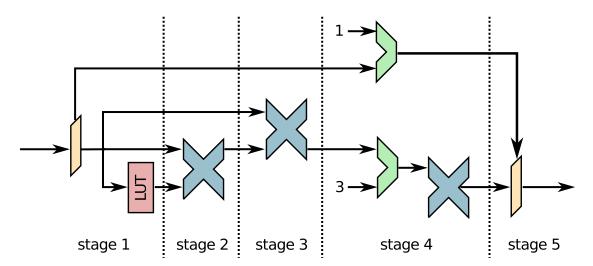

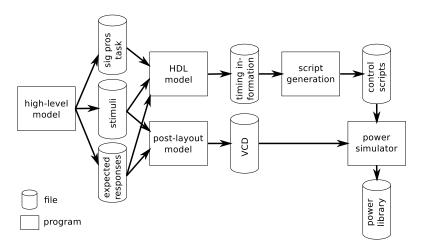

Therefore, we will conclude the chapter by proposing an architecture and implementation strategy for preprocessing circuits of MIMO detectors in OFDM systems, such as the presented PHY layer ASIC. To this end, we will compare application specific processor architectures with data oriented pipelined architectures, in the context of the PHY layer presented before. We will conclude, that for the constraints imposed by the system, partially attributed to the IEEE 802.11n standard, pipelined architectures are beneficial, if it's possible to precisely meet the system requirements (e.g., throughput, latency). In a next step, we will propose an implementation strategy that allows to design a configurable pipelined architecture, enabling with one HDL implementation to explore a large design space. Based on the design space exploration a specific implementation meeting the system requirements can then be selected for integration. Based in this implementation strategy, we will propose in the subsequent chapters several implementations for preprocessing circuits of MIMO detectors implemented for wireless local area network (WLAN) systems.

#### 2.1 The IEEE 802.11n Standard

In this section, we will first investigate a generic transmitter, as it is proposed in the IEEE 802.11n standard, to explain all signal processing operations necessary to generate a standard compliant transmit signal. Thereafter, we will elaborate the frame formats and some critical protocol specifics, defined in the standard. Both, the frame format and the specific protocol impose certain design decisions for the implementation of a standard compliant transceiver.

#### 2.1.1 A Generic IEEE 802.11n Transmitter

In Fig. 2.1, a generic transmitter implementing the physical layer convergence protocol (PLCP) is illustrated including all components required to transmit a PLCP service data unit (PSDU)

compliant with the standard. Based on the generic transmitter, we will present all signal processing tasks necessary to encode the bit stream output from the medium access control (MAC) layer into the transmit signal, as specified in the IEEE 802.11n standard. We intentionally focus on the encoding of the PSDU and neglect the overhead associated with the generation and insertion of the PLCP protocol data unit (PPDU) header. In the next paragraphs, we will therefore elaborate on all signal processing operations, from the data source to the antennas.

**Scrambler:** The scrambler is the first module that processes the bits of the PSDU. The aim of the scrambler is to reduce the probability of long sequences of zeros or ones in the bit stream. To this end, the scrambler is initiated with a pseudo-random nonzero seed, which is used to generate a scrambling sequence. The generated pseudo random sequence is then XORed with the bit stream of the PSDU.

**Encoder parser:** Subsequent to the scrambler, a forward error correction (FEC) encoder is employed. If binary convolutional code (BCC) encoding is used, two parallel encoders are employed for transmissions with a data rate larger than 300 Mbps. Therefore, a component called encoder parser demultiplexes the scrambled bits among the  $N_{es} = \{1, 2\}$  used BCC encoders in a round-robin manner. If a FEC encoder different to a BCC encoder is used, then the demultiplexing of the data stream is not performed and consequently the encoder parser is bypassed.

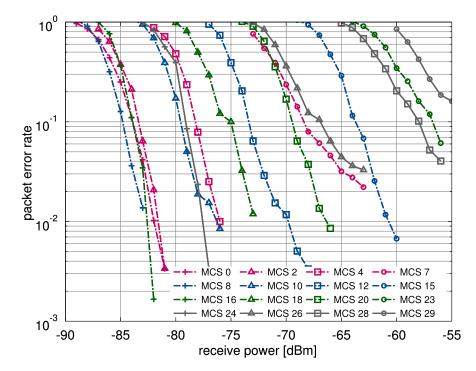

**FEC encoder:** The aim of the FEC encoder is to encode the data in order to enable error correction at the receiver. The IEEE 802.11n standard specifies two types of FEC code. The first type of FEC code is a BCC that is followed by puncturing. The data stream is initially extended and scrambled with a rate 1/2 convolutional encoder. In the resulting extended data stream, some encoded output bits are punctured (i.e., removed from the stream) to perform code rate adaptation. The second type of FEC code specified in the IEEE 802.11n standard is an optional low density parity check (LDPC) code. Both FEC encoder support multiple code rates (1/2, 2/3, 3/4, 5/6), which are set for the specific transmission by the MAC layer through the selection of a specific modulation and coding scheme (MCS). The mandatory MCS defined in the standard are listed in Tbl. 2.1

**Stream parser:** The encoded data stream is forwarded from all utilized FEC encoders to the stream parser. The parser divides the outputs of the FEC encoders into multiple bit sequences that are referred to as spatial streams. Each spatial stream is then sent to an individual interleaver and mapping device. The number of spatial streams  $N_{ss}$  used for transmission is, similar to the code rate, specified in the MCS. This MCS is controlled separately for each transmission by the MAC layer.

| MCS | N <sub>ss</sub> | modu-<br>lation | code<br>rate | bits per<br>subcarrier | MCS | $N_{ss}$ | modu-<br>lation | code<br>rate | bits per<br>subcarrier |

|-----|-----------------|-----------------|--------------|------------------------|-----|----------|-----------------|--------------|------------------------|

| 0   | 1               | BPSK            | 1/2          | 1/2                    | 16  | 3        | BPSK            | 1/2          | 3/2                    |

| 1   | 1               | QPSK            | 1/2          | 1                      | 17  | 3        | QPSK            | 1/2          | 3                      |

| 2   | 1               | QPSK            | 3/4          | 3/2                    | 18  | 3        | QPSK            | 3/4          | 9/2                    |

| 3   | 1               | 16-QAM          | 1/2          | 2                      | 19  | 3        | 16-QAM          | 1/2          | 6                      |

| 4   | 1               | 16-QAM          | 3/4          | 3                      | 20  | 3        | 16-QAM          | 3/4          | 9                      |

| 5   | 1               | 64-QAM          | 2/3          | 4                      | 21  | 3        | 64-QAM          | 2/3          | 12                     |

| 6   | 1               | 64-QAM          | 3/4          | 9/2                    | 22  | 3        | 64-QAM          | 3/4          | 27/2                   |

| 7   | 1               | 64-QAM          | 5/6          | 5                      | 23  | 3        | 64-QAM          | 5/6          | 15                     |

| 8   | 2               | BPSK            | 1/2          | 1                      | 24  | 4        | BPSK            | 1/2          | 2                      |

| 9   | 2               | QPSK            | 1/2          | 2                      | 25  | 4        | QPSK            | 1/2          | 4                      |

| 10  | 2               | QPSK            | 3/4          | 3                      | 26  | 4        | QPSK            | 3/4          | 6                      |

| 11  | 2               | 16-QAM          | 1/2          | 4                      | 27  | 4        | 16-QAM          | 1/2          | 8                      |

| 12  | 2               | 16-QAM          | 3/4          | 6                      | 28  | 4        | 16-QAM          | 3/4          | 12                     |

| 13  | 2               | 64-QAM          | 2/3          | 8                      | 29  | 4        | 64-QAM          | 2/3          | 16                     |

| 14  | 2               | 64-QAM          | 3/4          | 9                      | 30  | 4        | 64-QAM          | 3/4          | 18                     |

| 15  | 2               | 64-QAM          | 5/6          | 10                     | 31  | 4        | 64-QAM          | 5/6          | 20                     |

**Interleaver:** Afterwards, each spatial stream is processed in a separate interleaver. Interleaving is only applied to the bits of a spatial stream in case BCC encoding is used in the FEC encoder. The aim of interleaving is to change the order of the bits within the spatial stream to prevent long sequences of adjacent noisy bits from entering the BCC decoder at the receiver. Note that the interleaver is bypassed in case a LDPC encoder is used.

**Constellation mapper:** The coded, parsed, and possibly interleaved bit stream is then input into the constellation mapper. The bits of each spatial stream are separately divided into groups of bits. Each of this group of bits is then mapped to a corresponding constellation point (i.e., a complex number) according to the MCS. In IEEE 802.11n four modulation schemes are defined: BPSK, QPSK, 16 QAM, and 64 QAM.

**STBC encoder:** The output of all constellation mappers is forwarded to an optional space time block code (STBC) module. The aim of STBC is to spread the constellation points of the  $N_{ss}$  spatial streams onto  $N_{sts}$  space-time streams. The optional STBC can only be used if  $N_{ss}$  is smaller than the number of space-time streams. In this thesis, no STBC is used and therefore the spatial streams are directly mapped one-to-one on the space-time streams.

Cyclic shift delay (CSD): To prevent unintentional beamforming in case  $N_{ss}$  is smaller than the number of transmit antennas  $N_{tx}$ , the tones (i.e., subcarriers) of each OFDM symbol are

cyclically shifted. The standard defines a separate shift value for each space-time stream. The first CSD module can be omitted, as the first spatial stream does not require to be shifted (i.e., shifted by zero). CSD insertion may be done before or after the inverse fast Fourier transform (IFFT). If CSD is performed before the IFFT, CSD is implemented by multiplying the samples with a rotating phasor, otherwise CSD can only be implemented based on a large memory.

**Spatial mapper:** The space time streams have to be mapped to  $N_{tx}$  transmit chains. This is performed by a component named spatial mapper. In IEEE 802.11n, three types of spatial mapping are defined. The first type is direct mapping, where the constellation points from each space-time stream are mapped directly to the transmit chains. If STBC is used, this one-to-one mapping limits the number of active receive antennas to the number of space-time streams. If direct mapping but no STBC is employed, the number of active receive antennas is  $N_{ss}$ . The second standardized spatial mapping, is named spatial expansion. For each subcarrier, the vector of constellation points from all space-time streams is expanded to produce the input for all used transmit chains by a matrix vector multiplication. The third spatial mapping type defined in IEEE 802.11n is beamforming. Here, the vector of constellation points of all space-time streams is multiplied with a beamforming (or steering) matrix resulting in the input of the transmit chains. Contrary to the first two spatial mapping types, the number of space-time streams and the number of active transmit chains may be equal during beamforming.

**IFFT:** Vectors of constellation points for all  $N_{tx}$  transmit chains are then grouped in OFDM symbols. Each of the vectors (or transmit symbols) is assigned to an OFDM tone. In addition to the OFDM tones used for data transmission, some reserved tones are inserted for piloting. Depending on the bandwidth and frame format used for transmission, the number of vectors grouped per OFDM symbols in IEEE 802.11n is either 52, 56, or 114. After grouping the vectors into OFDM symbols, an IFFT for each spatial stream separately converts the group of vectors into the time domain representation of the OFDM symbol.

Guard interval (GI): Subsequent to the Fourier transformed waveform a circular extension of itself is prepended to each OFDM symbol, thereby forming a GI. In IEEE 802.11n two differently sized GIs are specified: the regular GI has a duration of  $0.8 \,\mu s$ , while a short GI is lasts only for  $0.4 \,\mu s$ .

**Analog frontend:** Each transmit chain is terminated with an analog frontend. The aim of the analog frontend is first to convert the transmit signal to the analog domain. And further, the analog frontend converts the baseband signal generated by the digital part of the transmitter up to the desired transmit frequency band.

Afterwards, the output signal of the analog frontend is radiated over the antennas. Before it

#### Chapter 2. A MIMO OFDM WLAN PHY Layer ASIC for IEEE 802.11n

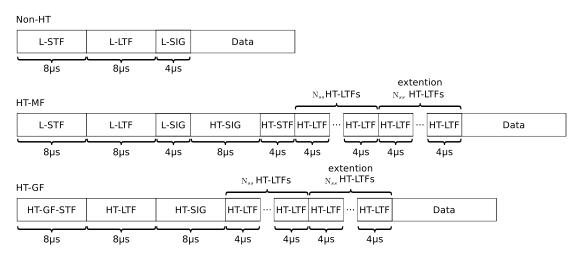

Figure 2.2 – Frame formats defined in IEEE 802.11n.

arrives at the receiver, the radiated signal is reflected, scattered, and delayed in the environment. The role of the receiver is to reverse the effect of the channel and the transmitter in order to restore the original PSDU. We will explain in Section 2.2.2 how a standard compliant receiver can be implemented.

#### 2.1.2 Frame Formats for IEEE 802.11n

All frame formats, specified in IEEE 802.11n, share the basic fields. They are initiated by a preamble, named short training field (STF), that is used at the receiver to detect a frame start. After the STF, a training sequence is transmitted to estimate the channel state information (CSI) at the receiver. The training sequence is referred to in IEEE 802.11n as long training field (LTF). As the data can be transmitted using different modulation and coding schemes, and further the number of data streams transmitted concurrently in the same frequency band may vary, a header field, named signal (SIG), is transmitted before the actual data, signaling to the receiver the used MCS. In addition, the header includes information about the length of the transmission as well as the bandwidth of the transmitted signal. The header also entails information about sounding (i.e., additional training sequences), which type of STBC is used, the type of FEC encoding employed, and a cyclic redundancy check (CRC) of the transmitted bit sequence. Subsequent to the header, additional training is may transmitted. The packet is concluded with the actual data payload. IEEE 802.11n specifies three frame formats presented in the following paragraphs:

Non-HT: As the standard is an extension of its predecessor, the first frame format specified, is similar to the legacy frame format used by the IEEE 802.11a wireless communication standard. In Fig. 2.2 the frame format for non high-throughput (non-HT) frames (i.e., an IEEE 802.11a compliant frame format) is shown. The frame starts with a legacy-STF with a duration of  $8\,\mu s$ , followed by a legacy-LTF with the same duration. Subsequent to the training fields, the legacy-

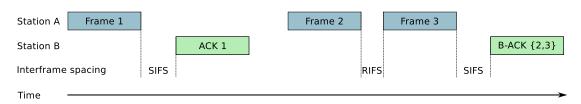

Figure 2.3 – Illustration of the communication protocol defined in IEEE 802.11n.

SIG field is transmitted. The field contains the code rate used, the length of the frame in octets, and a parity bit. After the legacy-SIG field the data itself is transmitted.

HT-MF: The first high-throughput (HT) frame format extending the capabilities of IEEE 802.11n compared to IEEE 802.11a, is the HT-mixed format (MF). The HT-MF format is also illustrated in Fig. 2.2. The frame format is designed to be used when stations with HT capability operate in the range of stations without HT support. Consequently, the HT-MF frame starts with the same sequence as the non-HT frame format. In the legacy-signal field the length of the packet is transmitted, in order to inform the legacy stations about the duration of the packet. Subsequent to the legacy-SIG field, a HT-SIG field is transmitted. As the HT-SIG field contains more information than the legacy-SIG field, its duration is twice as long. The HT-SIG field encodes the following information: the MCS, the bandwidth (20 MHz or 40 MHz), the data length in octets (up to 65'535 octets), whether sounding is enabled, whether the packet is aggregated, the type of STBC used, the type of FEC encoder, the length of the GI, and an 8 bit CRC. Subsequent to the HT-SIG field, HT training sequences are transmitted to allow the receiver to estimate the CSI for the MIMO channel. Finally, the actual data is transmitted.

HT-GF: The second HT frame format of IEEE 802.11n, allowing to use MIMO communication, is the HT green field (GF) frame format. The aim of the HT-GF frame format is to provide an HT transmission mode without the overhead of signaling the length of the transmission to IEEE 802.11a compliant stations. Accordingly, this frame format can only be used in case all stations in the transmission range support HT modes. The HT-GF compliant frame starts with an HT-GF-STF followed by an HT-GF-LTF. After the that, the HT-SIG field is directly transmitted. The remaining frame contains additional HT-LTFs to sound the spatial dimensions that have not be sounded by the initial HT-LTF. If channel sounding is applied, additional training fields are transmitted before the actual data is sent. The frame format is also concluded by the actual payload data.

All packets transmitted by an IEEE 802.11n compliant station are structured according to one of the three above elaborated frame formats. The same also applies to all control frames, which do not contain user data. Control frames include ready-to-send (RTS) frames, clear-to-send (CTS) frames, acknowledgment frames, and block acknowledgment frames.

|                                                       | Non-HT     | HT (20 MHz) | HT (40 MHz) |

|-------------------------------------------------------|------------|-------------|-------------|

| Number of data OFDM tones per OFDM symbol             | 48         | 52          | 108         |

| Number of pilot tones per OFDM symbol                 | 4          | 4           | 6           |

| Total number of tones per OFDM symbol N <sub>sd</sub> | 52         | 56          | 114         |

| IFFT/FFT period                                       | $3.2\mu s$ | $3.2\mu s$  | 3.2 µs      |

| regular GI duration                                   | $0.8\mu s$ | $0.8\mu s$  | 0.8 µs      |

| short GI duration                                     | -          | $0.4\mu s$  | 0.4 µs      |

| SIFS duration (2.4 GHz band)                          | 10 μs      | 10 μs       | 10 μs       |

| SIFS duration (5 GHz band)                            | 16 μs      | 16 µs       | 16 μs       |

| RIFS duration                                         | -          | $2 \mu s$   | $2 \mu s$   |

| max frame duration                                    | -          | 10 ms       | 10 ms       |

| max frame length [octets]                             | 4095       | 65535       | 65535       |

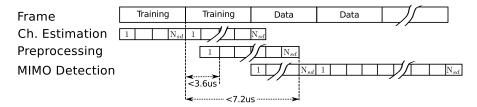

#### 2.1.3 Communication Protocol and Inter-frame Spacing

For the design of an IEEE 802.11n compliant receiver, the communication protocol and specifically the time between multiple transmissions is an important issue. As IEEE 802.11n specifies a carrier sense multiple access protocol, with no station completely controlling the communication media, the standard specifies the time between certain subsequent frames. These times are named inter-frame spacing (IFS) in IEEE 802.11n. While the larger IFSs are of less importance for the design of a PHY layer ASIC, the spacing between a received frame and the subsequent frame to be transmitted is critical. In IEEE 802.11n, the shortest IFS between frames transmitted from different stations is a short IFS (SIFS). The SIFS therefore determines the maximum receiver and transmitter latency.

A sequence of transmissions is illustrated in Fig. 2.3. In a first step, station A transmits a frame. Within a SIFS after the end of frame 1, station B has to completely demodulate and decode it and has to potentially start transmitting the according acknowledgment (if no error occurred during the reception of frame 1). In a second sequence of transmissions, station A sends two frames separated by a reduced inter-frame spacing (RIFS), and station B again has to send a block-acknowledgment within one SIFS. While the RIFS imposes no latency constraint, we will see in the next section that the maximum receiver latency imposed by the SIFS is a critical issue for the design of a PHY layer ASIC.

To complete the discussion about the IEEE 802.11n standard, important timing properties of the standard are listed in Tbl. 2.2. Among others, the number of subcarriers, the number of pilot tones, the duration of an OFDM symbol, and its GI are shown in Tbl. 2.2.

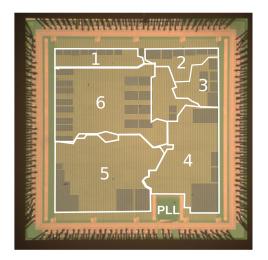

#### 2.2 An IEEE 802.11n compliant PHY Layer ASIC

In this section, we present an IEEE 802.11n compliant baseband modem ASIC, originally developed as a collaboration between ETH Zurich and Celestrius AG. The baseband modem embodies the PLCP and the digital part of the physical medium dependent (PMD). The ASIC supports the IEEE 802.11 PHY modes for the sub-standards a,g, and n. It further allows either 20 MHz or 40 MHz (channel bonding) transmission and reception. Further, the ASIC supports MIMO with up to four spatial streams. The baseband modem modulates the PPDU using OFDM, the header of the PPDU is modulated with BPSK and the remaining data with BPSK, QPSK, 16 QAM, or 64 QAM. The ASIC is able to encode the PSDU with four code rates (1/2, 2/3, 3/4, and 5/6) using up to two BCC encoder. Both GI durations, 0.8 µs for regular GI and 0.4 µs for short GI, are supported by the baseband modem. Furthermore, the ASIC supports all three PPDU formats specified in the IEEE 802.11n standard (non-HT, HT-MF, HT-GF), illustrated in Fig. 2.2.

We will first explain the strategy used to implement the PHY layer ASIC. To this end, we define a standard interface type used for all components in the data path of the ASIC. The components of the ASIC communicate only with these interfaces. All data transactions from one component to another are synchronized using a hand-shake protocol. In addition to the interface and the hand-shake protocol used for implementation, we will also discuss the clocking strategy used for all components of the PHY layer ASIC, as all together have an important impact on several design decisions made during the development of the circuits proposed in this thesis.

In the subsequent subsection, the components of the PHY layer ASIC implementation are discussed. To this end, the transmitter is described first, focusing on the implemented transmit latency reduction strategy. In a second step, the receiver is discussed. The receiver is decomposed into individual modules. And for all major components their implementation is discussed.

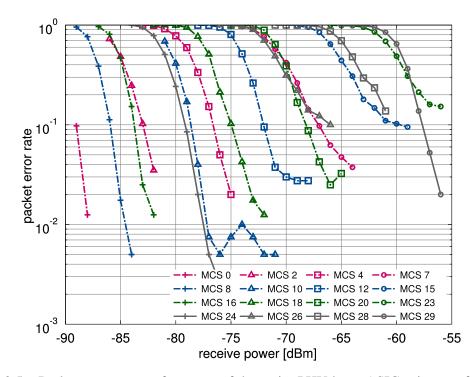

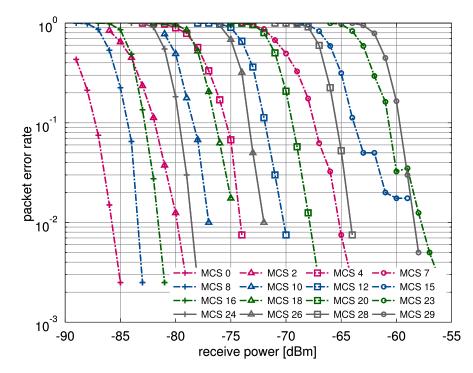

Finally, we present implementation results in terms of circuit area of all major components and in terms of error rate performance of the overall PHY layer ASIC for channel conditions specified by the task-group-n (TGn).

#### 2.2.1 Implementation Strategy

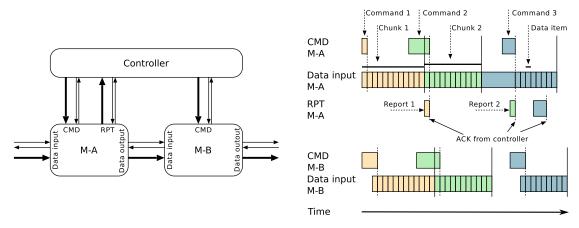

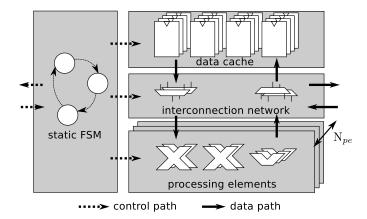

The data path of the ASIC implementation is constructed based on concatenated modules. The modules are orchestrated with a common controller and may contain further sub-modules. Each single module is completely agnostic to the sequence of operation required to process the data, but it is controlled by commands issued by the common controller. As soon as a module has finished the operations related to a command, the module reports its status back to the common controller.

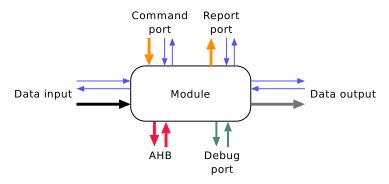

Figure 2.4 – Interface architecture of all modules.

#### Standard Module Interface

In Fig. 2.4, the standardized module interface is illustrated. All modules exchange data between each other via two data ports and are controlled by the associated controller over a command port. Beside these mandatory interfaces, some modules report their status to its controller via a report port. Modules which have internal configuration memories or internal configuration registers are slaves on a global bus. The bus follows the definition of the advanced high-performance bus (AHB) specification according to the advanced microcontroller bus architecture (AMBA) version two protocol. In addition to the functional ports, selected modules have a debug port. The debug port enables to monitor certain internal handshaking interfaces.

#### Hand-Shake based Data and Command Synchronization

All modules process the input data in chunks of one or multiple data items. A typical chunk of data items is, for example, the set of receive vectors belonging to a single OFDM symbol. A data item itself is defined as the data transferred to the module with a single handshake event. The module starts processing a chunk of data as soon as the corresponding controller issues a command. The command controls the number of data items that comprise a data chunk for the specific command and further determines the operation performed with the associated chunk of data. The module synchronizes each command with its associated chunk of data by acknowledging a command in the same clock cycle as the first data item of the data chunk associated to the specific command. Pipelined modules may start processing new chunks of data, before all data items of the previous chunk of data have been processed. If a module has a report interface, no new command is accepted until the report is acknowledged.

In Fig. 2.5, the processing paradigm for the example of two modules and a common controller is illustrated. Three commands are issued to the two modules M-A and M-B. While M-A starts processing immediately when command 1 is issued, M-B delays the acknowledgement of its first command until the first data item is available at its data input interface. Command 2 issued for M-A is also delayed as the first data item of the data chunk associated to command 2 is not

Figure 2.5 – Illustration of the processing paradigm used for all modules.

available at its data input port. As report 2 associated to command 2 is issued with a delay by M-A, command 3 and the corresponding data items are delayed at the input interfaces of M-A. This delay results in a postponement of the data items associated to the data chunk 3 at the data input interface of M-B.

#### **Clocking Strategy**

The receive signal from the analog frontend is sampled at 80 MHz to simplify the analog filter requirements. All clocks distributed on the PHY layer ASIC are an integer multiple of the sampling frequency. In total, three clock frequencies are provided to the modules of the PHY layer ASIC. The sampling clock of 80 MHz is internally used for the AHB bus only. The interfaces to the analog frontend operate at twice the sampling frequency in order to reduce the pin-out of the ASIC. To this end, the I and the Q channel are forwarded in an interleaved manner to or from the baseband modem. In addition, the 160 MHz clock is used for most of the modules. Only specific modules, and memories requiring an increased memory bandwidth, are clocked with four times the sampling frequency. To generate the clock-frequency, a phase locked loop (PLL) generates based on a 80 MHz reference clock the fastest clock used in the implementation. The resulting 320 MHz clock is then divided in order to generate the 160 MHz and the 80 MHz clocks.

Clock gating is a well known low-power strategy, that temporarily shuts down the clock signal for all those register banks of which output is not required. For all three clock nets in the PHY layer ASIC, we have implemented multistage clock gating. Each sub-module generates a busy signal, that is forwarded to the next higher module. Based on these busy signals from the sub-modules, its internal state, and the hand-shake signals, each module computes its own busy signal. The busy signal of each module indicates to the clock gate whether or not the module can be gated or not. For modules that are clocked with multiple clocks, the clock gate is replicated to clock gate all clock nets for the module. For all clock nets, clock-gating is applied on up to four clock

gating stages to achieve a fine-grained clock distribution. In addition to the busy signals from each module, clock-gating can be globally suppressed in the PHY layer ASIC by a status register configurable over the AHB.

#### 2.2.2 Components of the PHY Layer ASIC

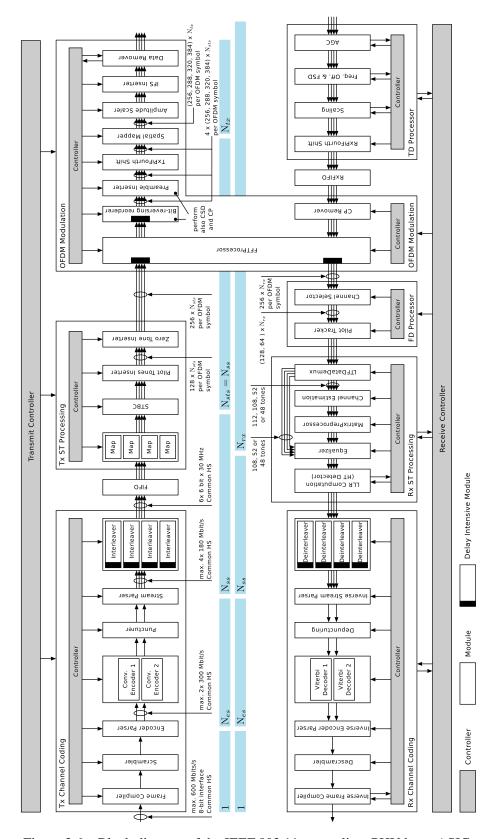

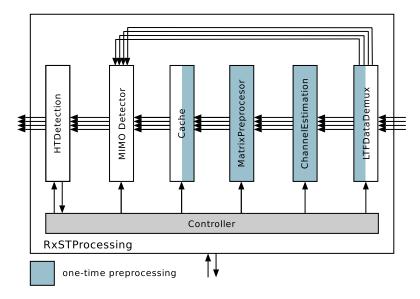

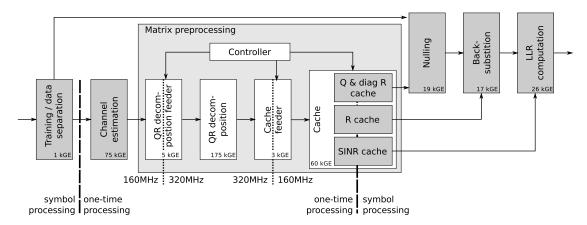

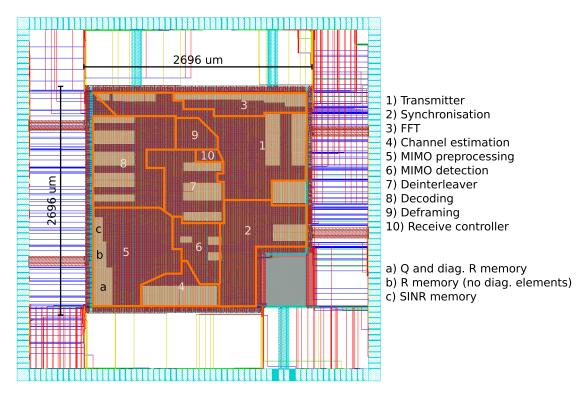

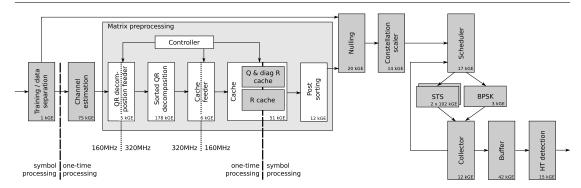

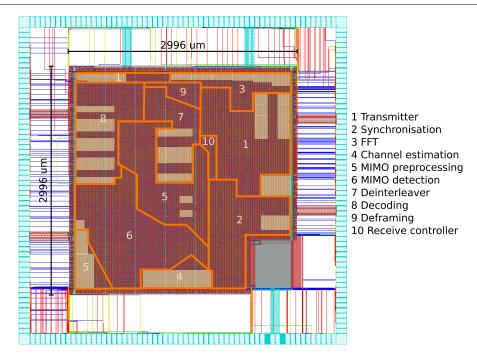

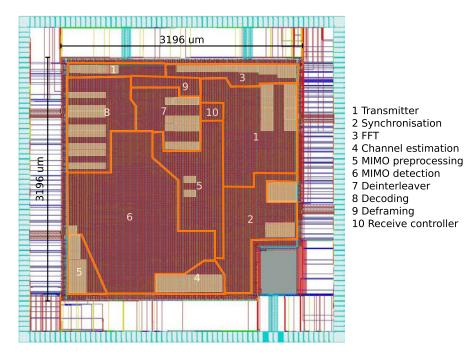

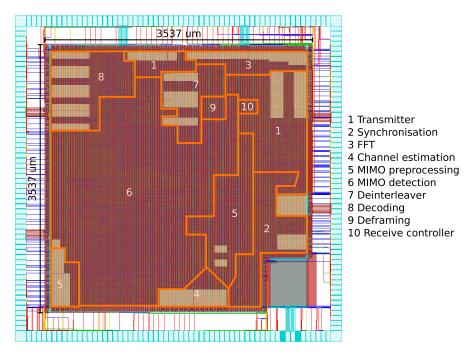

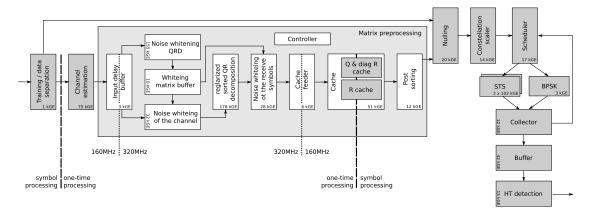

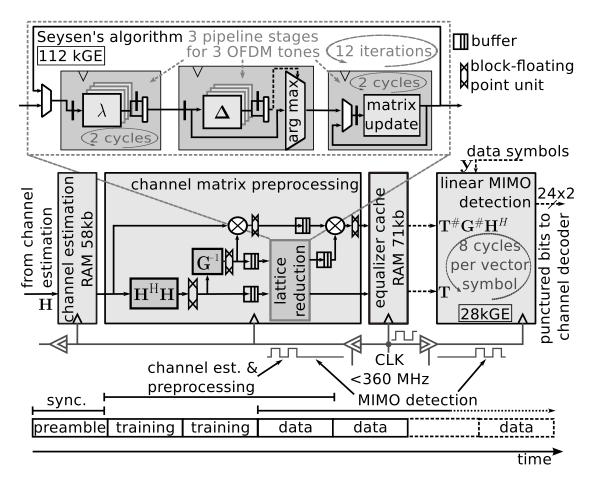

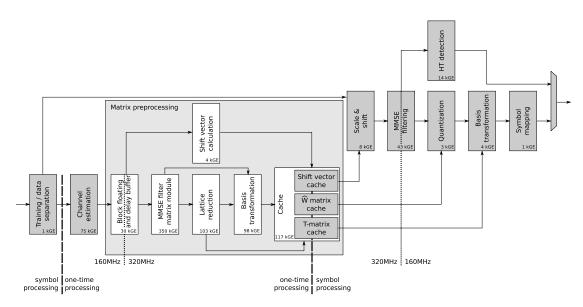

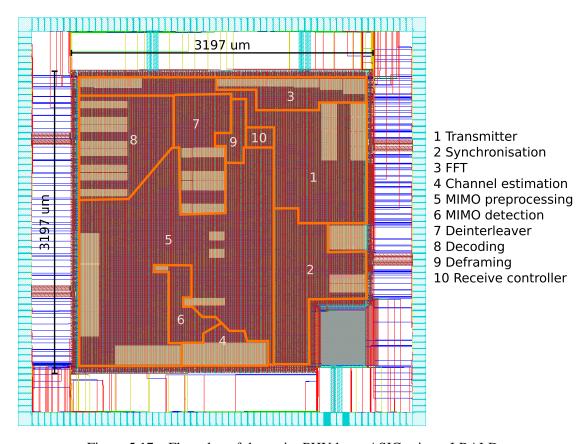

The entire PHY layer ASIC is composed of seven first-level modules. Three first-level modules (i.e., TxChannelCoding, TxSTProcessing, and OFDMModulation) compose the transmitter. The remaining first-level modules compose the receiver, whereas the OFDMModulation module is shared between the transmitter and the receiver. An overview of the PHY layer ASIC is shown in the block diagram in Fig. 2.6.

In this subsection, we will first discuss the transmitter. While the basic functionality of the transmitter is explained in Section 2.1.1, we now focus on the transmit delay minimization. After discussing the transmitter, we will elaborate the individual modules of the receiver.

#### **Transmitter**

In principle the preamble and the training sequence in the header of the PPDU could be modulated with the same signal processing steps as the PSDU. Unfortunately, as illustrated in Fig. 2.6, the transmitter has three modules which introduce an extended delay. The interleaver, the FFT processor, and the bit-reversing reorderer require all at least all data items associated to one OFDM symbol to perform their tasks. Therefore, all these three modules introduce latency to the transmitter that is proportional to the duration of an OFDM symbol resulting in a large transmitter latency.

However, the combined latency of the transmitter and the receiver has to be smaller than a SIFS in order to meet the specification of IEEE 802.11n. Due to the much higher computational complexity and latency of the receiver, results this, in minimizing the transmitter latency. Therefore, should the time be minimized between the MAC layer commanding the PHY layer to transmit a PPDU and the first signal being radiated over the antenna.

In this implementation, the preamble and training sequence is generated in the time domain in order to avoid large transmitter latency imposed by the three above mentioned modules. To this end, the sequences being repeated multiple times to generate the preamble and training sequence are stored in hard-coded look-up tables (LUTs) in a module named PreambleInserter. To generate STFs, legacy-LTFs, HT-LTFs for 20 MHz bandwidth, and HT-LTFs for 40 MHz transmissions, four LUTs, with 256 words each, are hard-coded for each possible space-time stream. The preamble is directly generated including the CSD for each space-time stream and also including the cyclic GI. To enable time-domain beamforming in the spatial mapper, the circuit required to generate the preamble for one space-time stream is replicated eight times, each generating the preamble for two streams in an interleaved manner. Afterwards, the resulting preamble and training sequences are forwarded to the TxPiFourthShift module shown in Fig. 2.6.

Figure 2.6 – Block diagram of the IEEE 802.11n compliant PHY layer ASIC.

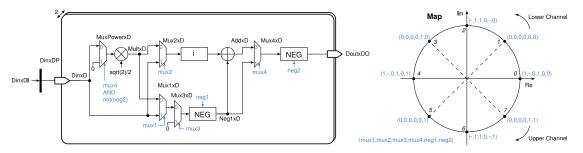

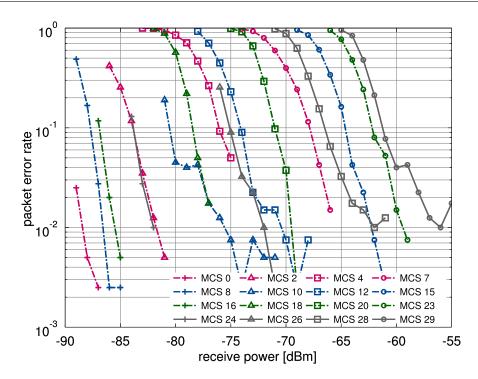

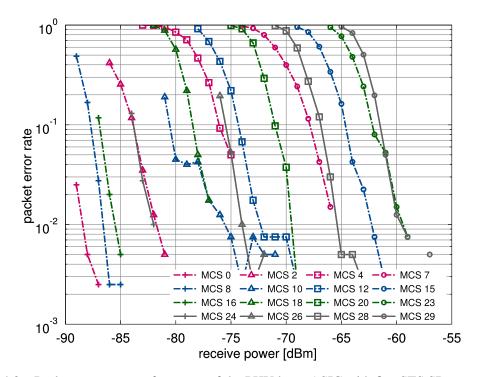

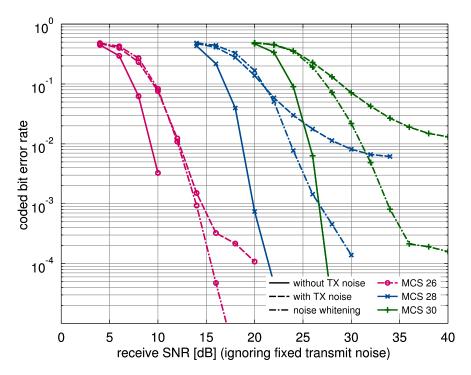

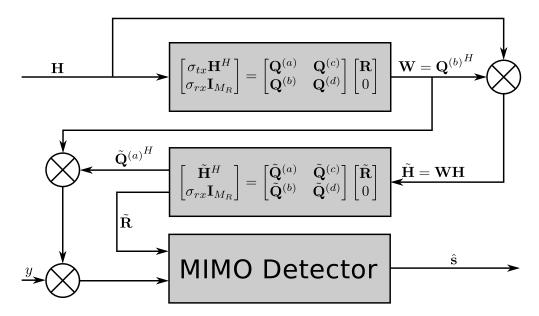

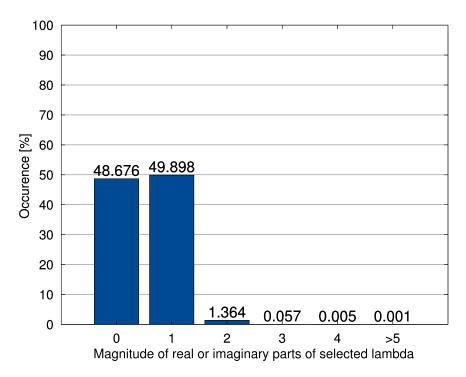

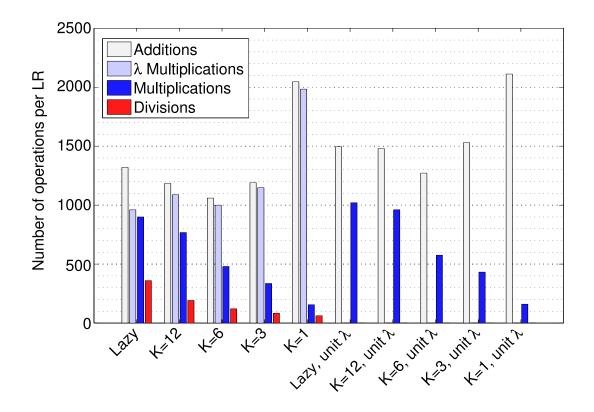

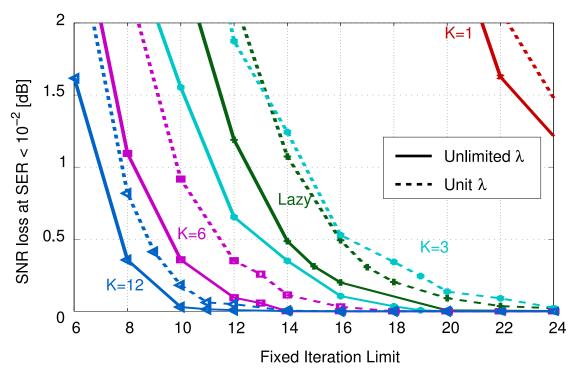

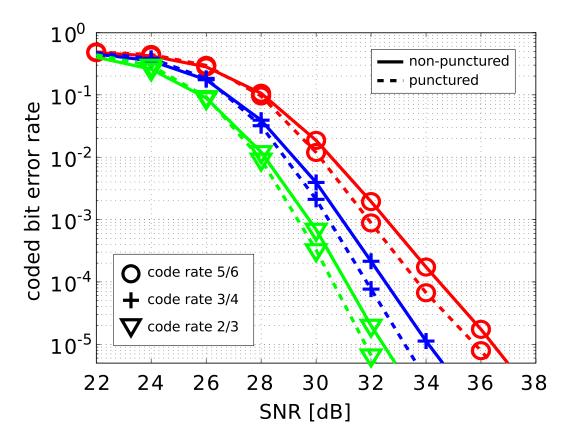

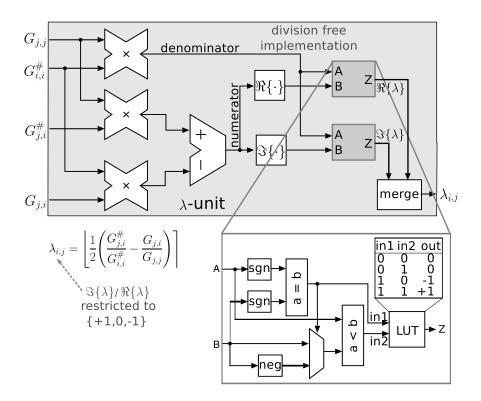

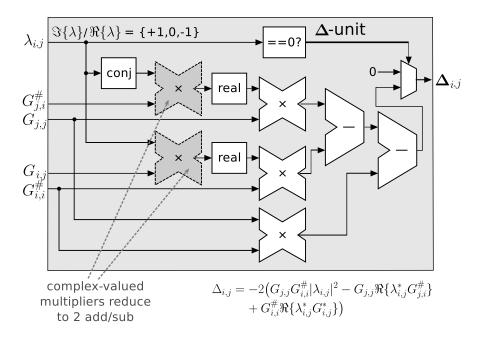

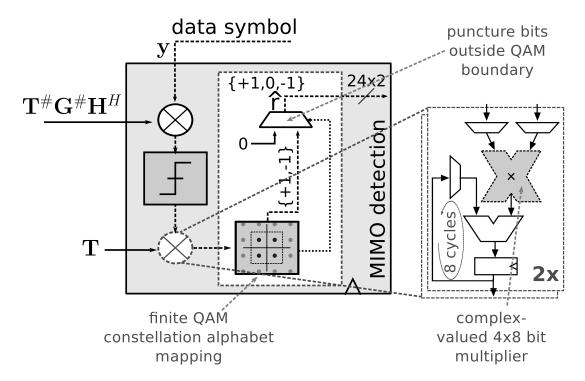

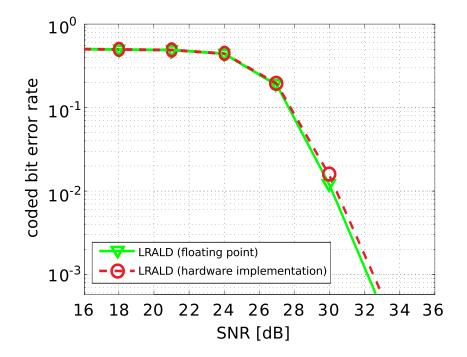

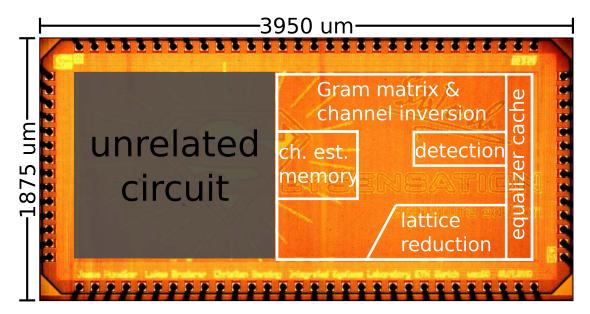

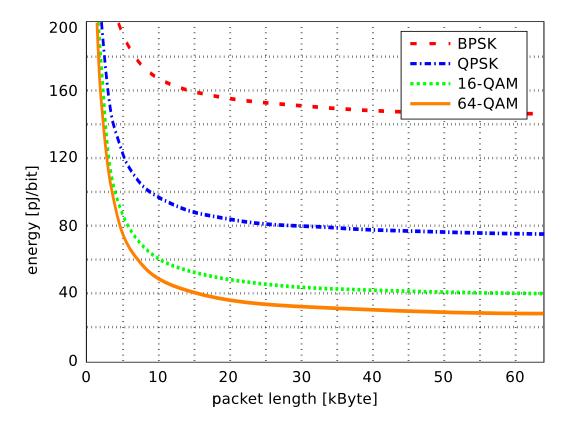

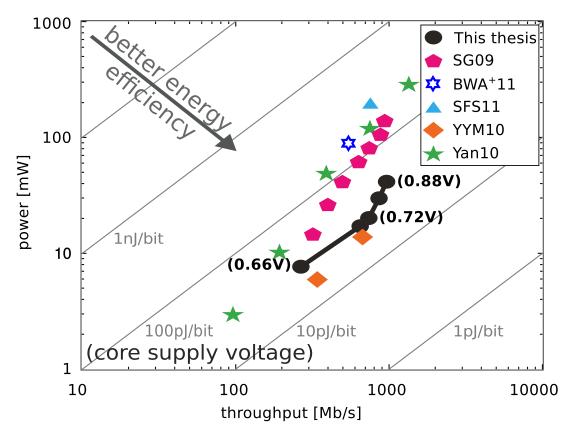

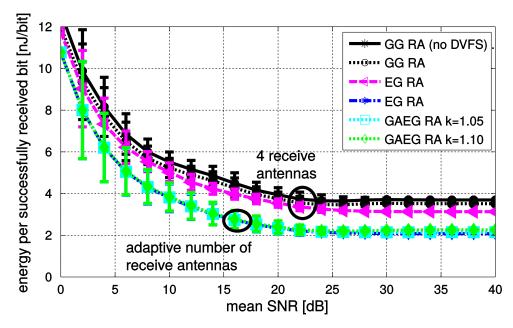

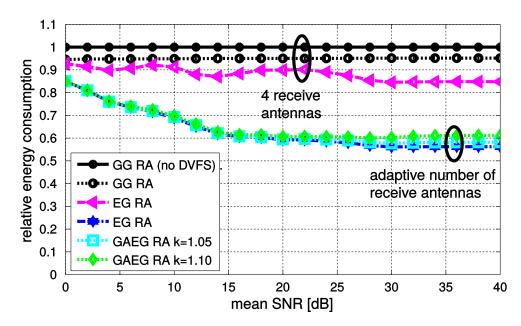

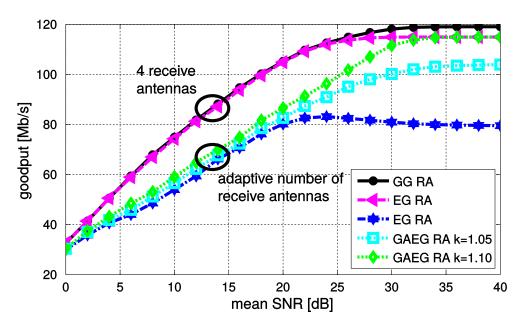

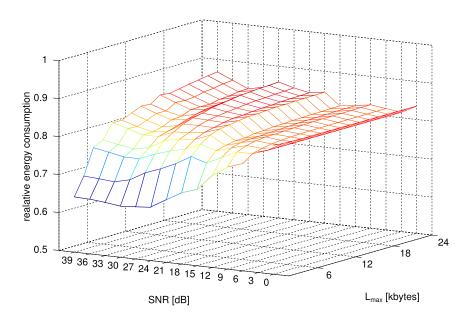

The overall transmitter is designed to support 40 MHz transmissions. All 20 MHz transmissions are generated in the primary band of a 40 MHz signal (i.e., either the lower or the upper 20 MHz). To be able to transmit the 20 MHz transmission on a centered band, the generated signal has to be shifted in frequency by 10 MHz. As the preamble and training sequence are composed in the time domain, the signal is multiplied in the time domain by a rotating phasor to compute the frequency shift. Similar to the PreambleInserter, the circuit is replicated to perform its task on 16 streams, to enable beamforming in the time domain by the spatial mapper. In a next step, the potentially shifted signal is forwarded to the spatial mapper module.