## Multi-Band Outphasing Power Amplifier Design for Mobile and Base stations

THÈSE Nº 6410 (2014)

PRÉSENTÉE LE 13 OCTOBRE 2014 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR GROUPE SCI STI CD PROGRAMME DOCTORAL EN GÉNIE ÉLECTRIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

### Omid TALEBI AMIRI

acceptée sur proposition du jury:

Prof. M. Paolone, président du jury Dr C. Dehollain, Dr A. Koukab, directeurs de thèse Dr E. Abou-Allam, rapporteur Prof. M. Green, rapporteur Prof. M. Kayal, rapporteur

To my parents...

## Acknowledgements

First and foremost, I would like to thank my thesis advisor, Dr. Adil Koukab, for his exceptional support and guidance throughout my studies at EPFL. Many ideas and outcomes presented in this thesis are coming directly from his valuable hints. I am also thankful to Dr. Catherin Dehollain for her support.

I would like to thank the distinguished members of the jury for PhD exam, Prof. Michael Green, Dr. Eyad Abou-Allam, Dr. Maher Kayal and Prof. Mario Paolone for taking the time reviewing this thesis and offering me their valuable comments. I would also express my gratitude to Dr. Jean-Michel Sallese, for his valuable time and kind advices, to Andre Badertscher, Joseph, Raymond, Isabelle and Karin for their logistic and administrative supports, and to my sister for preparing the French abstract.

I would like to acknowledge my previous supervisors, Prof. Mehrdad Sharif Bakhtiar and Prof. Seyed Mohammad Hossein Alavi from whom I learned electronics.

I am really thankful to all my colleagues and former colleagues in Kandou Bus, RFIC group, ELAB, LSI, EDLAB, ISDL-Sharif and my Iranian friends for all the pleasant moments that we had together.

Last but not least, I want to express my deepest and heartiest thanks to my family, specially my parents for their support and to my wife for standing by my side.

### Abstract

New generations of wireless communication systems require linear efficient RF power amplifiers (PAs) for higher transmission data rates and longer battery life. On the contrary, conventional PAs are normally designed for peak efficiency under maximum output power ( $P_{out}$ ). Thus, in power back-off, the overall efficiency degrades significantly and the average efficiency is much lower than the efficiency at maximum  $P_{out}$ . Chireix outphasing PA, also called LINC (Linear amplification using Non-linear Components), is one of the most promising techniques to improve the efficiency at power back-off. In this method, a variable envelope input signal is first decomposed into two constant-envelope phase-modulated signals and then amplified using two highly efficient non-linear PAs. The output signals are combined preferably in a loss-less power combiner to build the desired output signal. In this way, the PA exhibits high efficiency with good linearity.

In this thesis, first we analyze a complex model of outphasing combiner considering its nonidealities such as reflection and loss in transmission lines (TL). Then we propose a compact model with analytical formula that is validated through several comparative tests using ADS and Spectre RF. Furthermore, we analyze the effect of reactive load in Chireix combiner with stubs (a parallel inductor and capacitor), while distinguishing between its capacitive and inductive parts. It is demonstrated that only the capacitive part of the reactive load degrades the performances. Based on this, a new architecture (Z-LINC) is proposed where the power combiner is designed to provide a zero capacitive load to the PAs whatever the outphasing angle. The theory describing the operations of the system is developed and a 900 MHz classical LINC and Z-LINC PAs are designed and measured. In addition, a miniaturization technique is proposed which employs  $\lambda/8$  or smaller TLs instead of conventional  $\lambda/4$  TLs in outphasing power

combiner. This technique is applied to implement a 900 MHz PA using LDMOS power transistors.

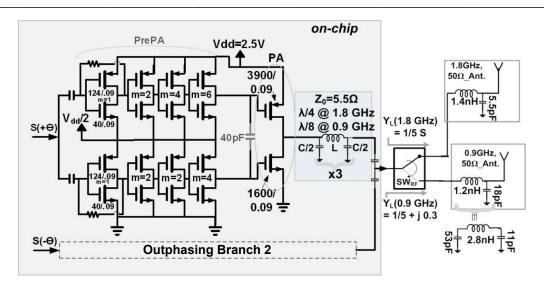

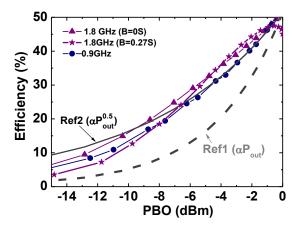

Besides single-band PAs, dual-band PAs are more and more needed because of an increasing demand for wireless communication terminals to handle multi-band operation. In chapter 5, a new compact design approach for dual-band transmitters based on a reconfigurable outphasing combiner is proposed. The objective is to avoid the cumbersome implementations where several PAs and matching network are used in parallel. The technique is applied to design a dual band PA with a fully integrated power combiner in 90 nm CMOS technology. An inverter-based class D PA topology, particularly suitable for outphasing and multimode operations is presented. The TLs in the combiner, realized using a network of on-chip series inductors and parallel capacitors, are reconfigurable from  $\lambda/4$  in 1800 MHz to  $\lambda/8$  in 900 MHz. In order to maximize the efficiency, the on-chip inductors are implemented using high quality factor on-chip slab inductors. The measured maximum  $P_{out}$  at 900/1800 MHz are 24.3 and 22.7 dBm with maximum efficiencies of 51% and 34% respectively.

**Keywords**: Chireix, outphasing, LINC, power amplifier, power combiner, transmission line, slab inductor, dual band, LDMOS, CMOS, RF integrated circuits.

## Résumé

Les nouvelles générations de systèmes de communication sans fils nécessitent des amplificateurs linéaires de puissance RF pour des vitesses de transmission de données plus rapides et des batteries ayant des durées de vie plus longues. Au contraire, les PAs conventionnels sont normalement conçus pour un rendement optimum à la puissance de sortie maximum. Ainsi, à la puissance reculer l'efficacité totale est significativement réduite et l'efficacité moyenne est bien plus basse que l'efficacité au maximum Pout. "Chireix outphasing PA" aussi appelé LINC (Linear amplification using Non-linear Components) est une des techniques les plus prometteuses pour améliorer l'efficacité à la puissance back-off. Dans cette méthode, un signal d'entrée d'enveloppe variable est d'abord décomposé en deux signaux à phase modulée d'enveloppe constante et ensuite est amplifié en utilisant deux PAs non linéaire de haute efficacité. Les signaux de sortie sont combinés préférentiellement en combinateur de puissance sans perte pour construire le signal de sortie voulu. De cette façon, le PA présente une haute efficacité avec une bonne linéarité.

Dans cette thèse, nous analysons tout d'abord un modèle complexe de combinateur déphasé en considérant ses caractéristiques non idéales telles que la réflexion et les pertes dans les lignes de transmission (TL). Ensuite nous proposons un modèle compact avec une formule analytique qui est validée à travers plusieurs tests comparatifs en utilisant ADS et Spectre RF. Par la suite, nous analysons l'effet de charge réactive dans le combinateur Chireix avec des plaques (un inducteur parallèle et une capacité), en distinguant les parties capacitives et inductives. Il est démontré que seule la partie capacitive de la charge réactive dégrade les performances. Basée la dessus, une nouvelle architecture (Z-LINC) est proposée dans laquelle le combinateur de puissance est conçu pour fournir une charge zéro capacitive au PAs quel que soit l'angle de déphasage. La théorie qui décrit les opérations du système est développée, un 900 MHz LINC classique et Z-LINC PAs sont conçues et mesurés. De plus, une technique de miniaturisation est proposée qui emploie lambda/8 ou de plus petits TLs à la place des conventionnels lambda/4 TLs dans le combinateur de puissance déphasé. Cette technique est appliquée en implémentant un 900 MHz PA en utilisant des LDMOS transistors de puissance.

Outre les PAs à une seule bande, les PAs à deux bandes sont de plus en plus nécessaires à cause de la demande croissante pour les terminaux de communication sans fils pour gérer des opérations à bandes multiples. Dans le dernier chapitre, une nouvelle approche de design compact pour des transmetteurs à deux bandes, basée sur un combinateur de déphasage reconfigurable, est proposée. L'objectif est d'éviter les implémentations lourdes où les nombreux PAs et le "matching network" sont utilisés en parallèle. Cette technique est appliquée pour concevoir un PA à bande double avec un combinateur de puissance totalement intégré dans une technologie CMOS 90 nm. Un inverseur, basé sur la classe D et une topologie PA particulièrement approprié pour des opérations de déphasage et multimode, est présenté. Les TLs dans le combinateur, réalisés en utilisant un réseau de on-chip capacités en série et d'inducteurs en parallèle, sont reconfigurables de lambda/4 à 1800 MHz à lambda/8 à 900 MHz. Afin de maximiser l'efficacité, les inducteurs on-chip sont implantés en utilisant des plaques d'inducteurs on-chip de hauts facteurs de qualité. Les  $P_{out}$  maximums mesurés à 900/1800 MHz sont 24.3 et 22.7 dBm avec des efficacités maximums de 51% et 34% respectivement.

Mots clés: Chireix, déphasage, LINC, amplificateur de puissance, combinateur de puissance, lignes de transmission, plaques d'inducteurs, doubles bandes, LDMOS, CMOS, circuits intègres RF.

# List of figures

| Fig. | 1-1: Enormous development in mobile industry; Martin Cooper shows his first handheld                  |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | mobile phone and one latest small smart phone [1]                                                     | 2  |

| Fig. | 1-2: Conventional multi-standard transmitter with dedicated PA for each band                          | 4  |

| Fig. | 2-1: Simplified schematic of a PA                                                                     | 8  |

| Fig. | 2-2: Output power Probability Density Function (PDF).                                                 | 9  |

| Fig. | 2-3: $P_{sat}$ and $P_{1-dB}$ of the PA output power                                                  | 9  |

| Fig. | 2-4: Spectral mask versus frequency [2]1                                                              | 0  |

| Fig. | 2-5: EVM representation in IQ plane 1                                                                 | 0  |

| Fig. | 2-6: Schematic of polar modulation/EER technique 1                                                    | 1  |

| Fig. | 2-7: Doherty PA and its normalized efficiency versus normalized output power [4] 1                    | 2  |

| Fig. | 2-8: Generalized PWPM PA and output power of an ideal Class E PA versus input pulse                   |    |

|      | duty cycle [6] 1                                                                                      | 3  |

| Fig. | 2-9: Simple schematic of outphasing modulation 1                                                      | 4  |

| Fig. | 2-10: LDMOS cross section schemantic and photo [12] 1                                                 | 7  |

| Fig. | 2-12: Technology selection based on operating frequency and output power [13] 1                       | 9  |

| Fig. | 2-11: LDMOS device with input and output matching inside the package [12] 1                           | 9  |

| Fig. | 3-1: Simplified diagram of Outphasing Tx                                                              | 22 |

| Fig. | 3-2: A general four-terminal combiner, a) Wilkinson with $B = 0$ , b) Chireix with $R_{iso} = \infty$ |    |

|      | and $B = 0$ , and c) Chireix with stub and $R_{iso} = \infty$                                         | 23 |

| Fig. | 3-3: The input impedance of a) Wilkinson, b) Chireix and c) Chireix with stub power                   |    |

|      | combiners. d) Efficiency vs. Normalized $P_{OUT}$ for different types of combiners                    | 27 |

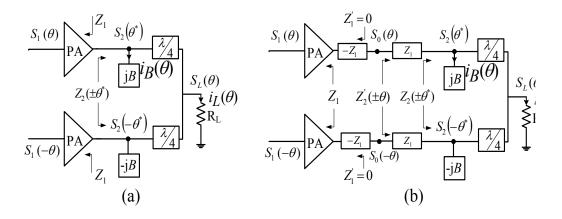

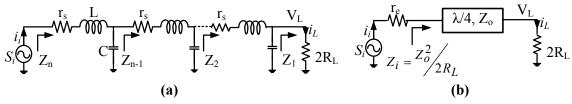

| Fig. | 3-4: a) Chireix-Outphasing topology with stub and b) simplified topology 2                            | 28 |

| Fig. | 3-5: a) Chireix-outphasing model with stub and b) simplified topology                                 | 29 |

|      |                                                                                                       |    |

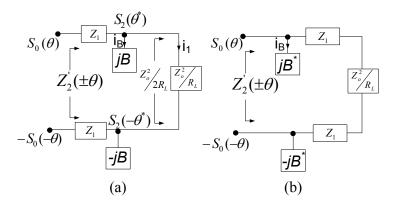

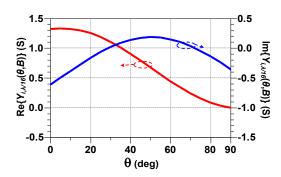

| Fig. 3-6: The simulated and calculated imaginary and real part of Y' <sub>2</sub> versus $\theta$ with Z <sub>1</sub> varying  |

|--------------------------------------------------------------------------------------------------------------------------------|

| from 0 to 6 $\Omega$ and B calculated for $\theta_o = 10$                                                                      |

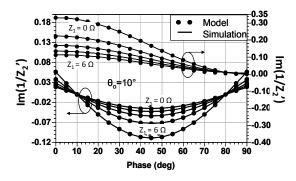

| Fig. 3-7: Simulated and calculated output power and normalized efficiency ( $\eta_N$ ) versus phase                            |

| ( $\theta$ ) with a) Z <sub>1</sub> varying from 0 to 4.5 $\Omega$ with a step of 0.75 $\Omega$ , b) B varying from 0 to 0.1 ( |

| i.e. $\theta_o$ varying from $0^\circ$ to $20^\circ$ in steps of $5^\circ$ )                                                   |

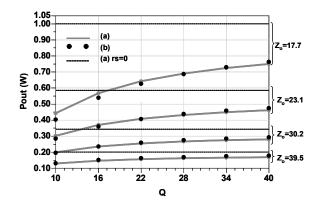

| Fig. 3-8: a) Transmission line and b) its model for Chireix-LINC                                                               |

| Fig. 3-9: Simulated output power of the circuits of Fig. 3-8 (a and b) with Q varying from 10                                  |

| to 40 and $Z_o$ varying from 17.7 $\Omega$ to 39.5 $\Omega$                                                                    |

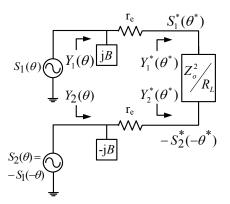

| Fig. 3-10: Equivalent schematic of LINC                                                                                        |

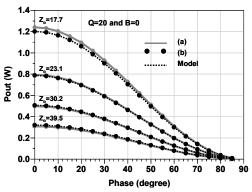

| Fig. 3-11: Output power vs phase, simulated using (3-49) for a LINC with the circuit (a) and                                   |

| (b) of Fig. 3-8 as TLs and calculated (Model) using (3-50) with $Q = 20$ , $B = 0$ and Zo                                      |

| varying from 17.7 to 39.5                                                                                                      |

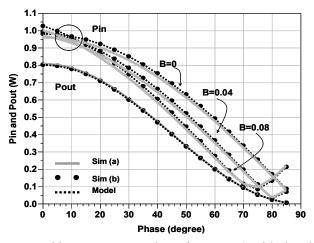

| Fig. 3-12: Output and input power vs phase for a LINC with the circuit (a) and (b) of Fig. 3-8                                 |

| as TLs and calculated (Model) using (3-50) with $Q = 20$ , $Zo = 22.8$ and $B$ varying from 0                                  |

| to 0.08                                                                                                                        |

| Fig. 3-13: Simulated and calculated efficiency with $Q = 20$ , $Zo = 22.8$ and $B$ varying from 0 to                           |

| 0.08                                                                                                                           |

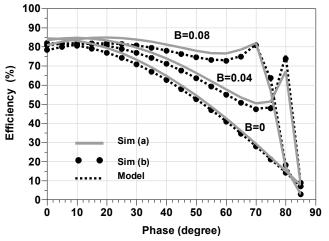

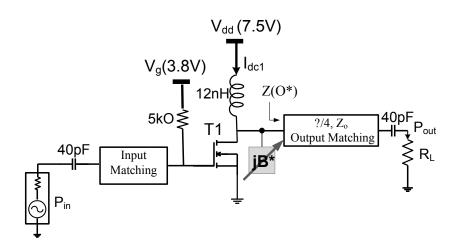

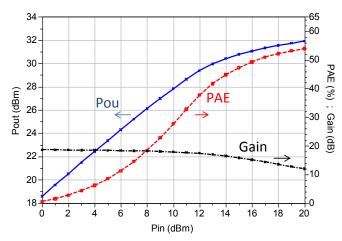

| Fig. 4-1: Schematic of the PA designed to be used in the LINC Tx                                                               |

| Fig. 4-2: Simulated output power and power added efficiency of the PA with $V_{dd} = 7.5$ V and                                |

| P <sub>in</sub> varying from 0 to 20 dBm                                                                                       |

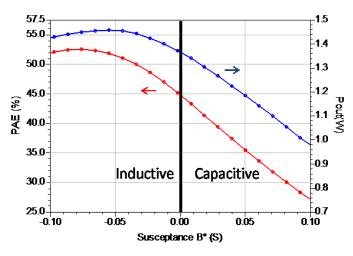

| Fig. 4-3: Simulated $P_{out}$ and $PAE$ of the PA shown in Fig. 4-1 with $V_{dd} = 7.5$ V, $P_{in} = 16$ dBm                   |

| and <i>B</i> * varying from -0.1 S to 0.1 S                                                                                    |

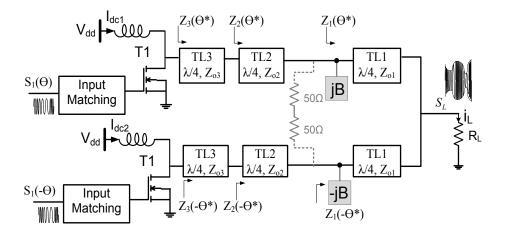

| Fig. 4-4: Schematic of the Chireix-LINC using the PA of Fig. 4-1. The Chireix combiner is                                      |

| transformable to Wilkinson combiner by adding two 50 $\Omega$ resistors                                                        |

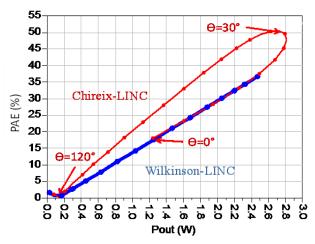

| Fig. 4-5: Simulated <i>PAE</i> vs $P_{out}$ of Chireix-LINC and Wilkinson-LINC with $V_{dd} = 7.5$ V, $P_{in} =$               |

| 18 dBm and $\theta$ varying from 0 to 120°                                                                                     |

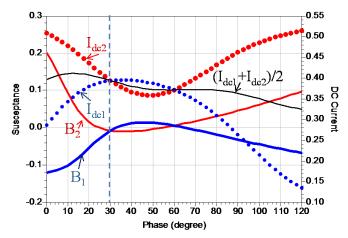

| Fig. 4-6: Simulated imaginary parts of the admittances seen by the PAs $(B_{1,2})$ and the dc                                  |

| current consumed by the Chireix-LINC ( $I_{dc1,2}$ )                                                                           |

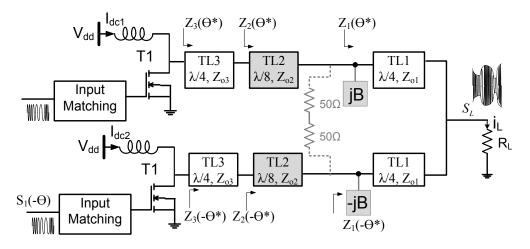

| Fig. 4-7: Schematic of the proposed Z-LINC. The power combiner is transformable to                                             |

| Wilkinson by adding the two 50 $\Omega$ resistors                                                                              |

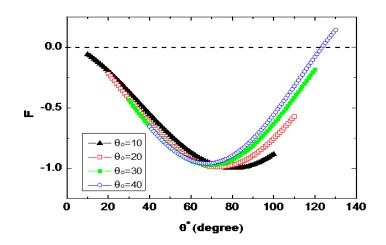

| Fig. 4-8: Calculated values of the function F in (4–8) for $\theta^*$ varying from $\theta_o$ to $90^\circ + \theta_o$ and $\theta_o$ |

|---------------------------------------------------------------------------------------------------------------------------------------|

| equal to 10, 20, 30, and 40 degree                                                                                                    |

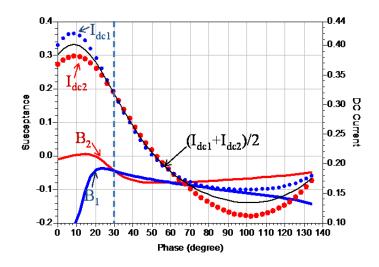

| Fig. 4-9: Simulated imaginary parts of the admittances seen by the PAs $(B_{1,2})$ and the                                            |

| consumed dc currents in Z-LINC                                                                                                        |

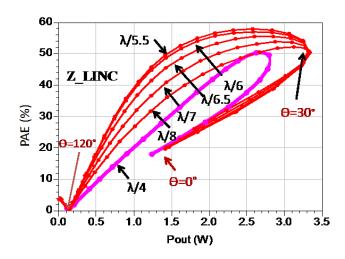

| Fig. 4-10: Simulated <i>PAE</i> vs. $P_{out}$ of Z-LINC with $V_{dd}$ = 7.5 V, $P_{in}$ = 18 dBm, $\theta$ varying from 0             |

| to 120° with different values for TL2 electrical length                                                                               |

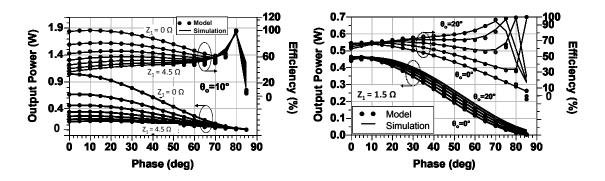

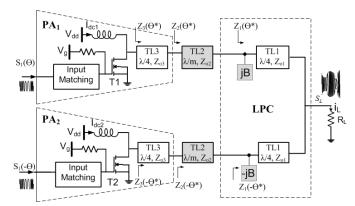

| Fig. 4-11: Classical ( $m = 4$ for TL2) and modified ( $m = 8$ for TL2) LINC topologies                                               |

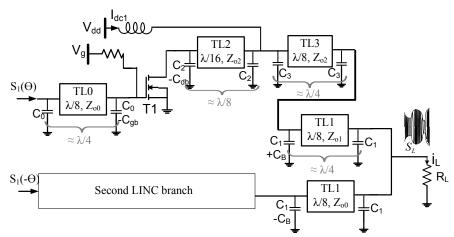

| Fig. 4-12: Modified Z-LINC topology, implemented using shorter TLs and shunt capacitors. 52                                           |

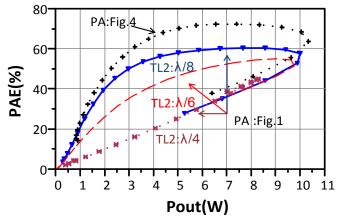

| Fig. 4-13: Simulated <i>PAE</i> versus $P_{out}$ of the circuit in Fig. for $\theta$ varying from 0 to 120° and                       |

| with $m = 4, 6, 8$ ( $V_{dd} = 13.5$ V, $V_g = 3.8$ V, $P_{in} = 19$ dBm and $\theta_o = 20^\circ$ )                                  |

| Fig. 4-14: Measurement setup used to measure LDMOS transistors modified LINC PAs 54                                                   |

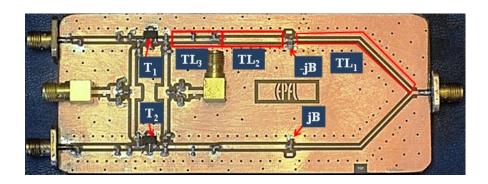

| Fig. 4-15: Photo of the Z-LINC prototype                                                                                              |

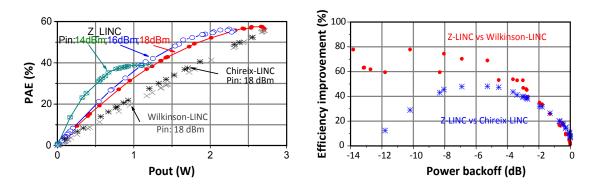

| Fig. 4-16: a) Measured <i>PAE</i> vs. $P_{out}$ of Z-LINC for $P_{in} = 14$ , 16 and 18 dBm. The measured                             |

| results of Wilkinson-LINC and Chireix-LINC are also reported. b) Relative efficiency                                                  |

| improvement ( $\Delta PAE/PAE$ ) of Z-LINC with respect to the classical Chireix and Wilkinson                                        |

| LINC with $P_{in} = 18 \text{ dBm}$                                                                                                   |

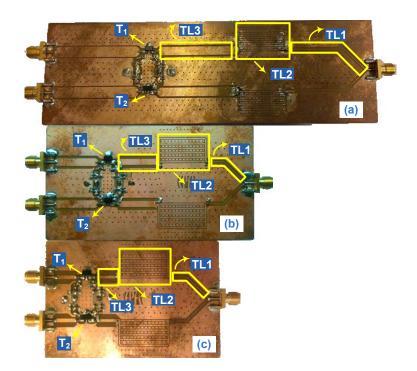

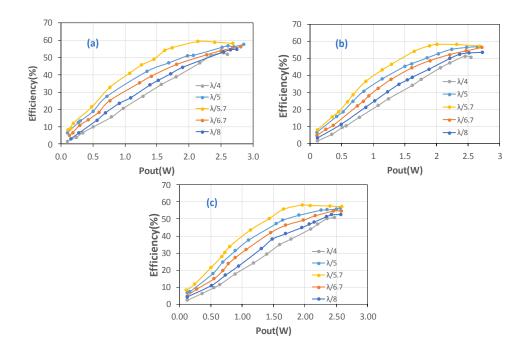

| Fig. 4-17: Z-LINC prototypes with variable TL2 and shorter TL as input and output stages of                                           |

| LDMOS transistors ( $T_1$ and $T_2$ ) respectively for circuits (a), (b) and (c)                                                      |

| Fig. 4-18: Measured efficiency versus output power for the prototypes shown in Fig. 4-17 57                                           |

| Fig. 4-19: Photo of Z-LINC prototype with shorter TLs                                                                                 |

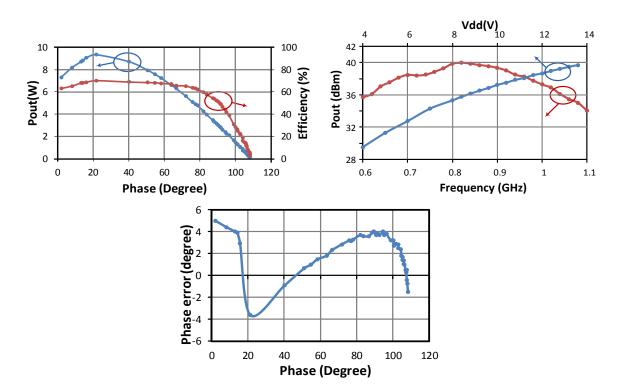

| Fig. 4-20: a) Measured $P_{out}$ and $PAE$ versus input outphasing angle ( $\theta$ ), b) Measured $P_{out}$                          |

| versus frequency and supply voltage                                                                                                   |

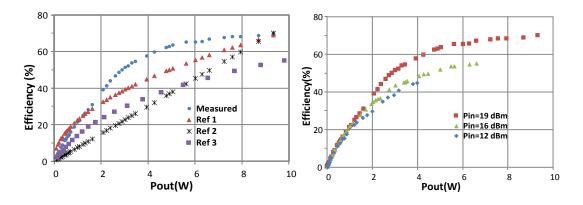

| Fig. 4-21: a) Measured Efficiency versus Output power, b) Measured Efficiency versus Output                                           |

| power for different <i>P<sub>in</sub></i>                                                                                             |

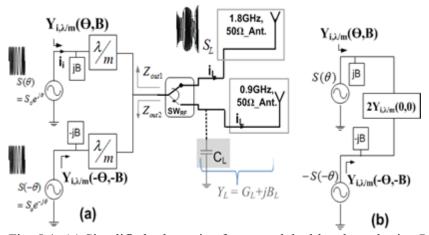

| Fig. 5-1: (a) Simplified schematic of proposed dual-band outphasing PA and (b) its equivalent                                         |

| simplified circuit                                                                                                                    |

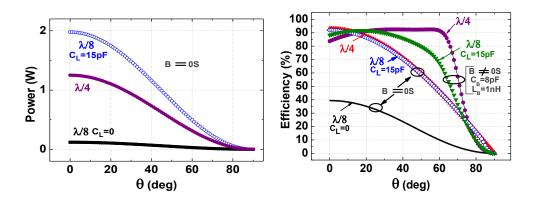

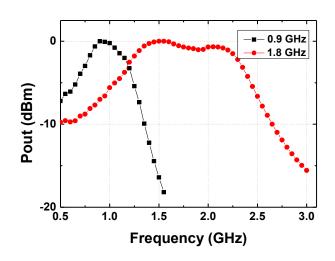

| Fig. 5-2: Simulated output power and efficiency of the circuit Fig. 5-1a at 1.8 GHz ( $\lambda/4$ ), 0.9                              |

| GHz ( $\lambda/8$ ), without stub ( $B = 0$ ) and with stub (implemented using $C_B = 8$ pF and                                       |

| $L_B = 1$ nH and corresponding to $B = 0.09$ S at 1.8 GHz)                                                                            |

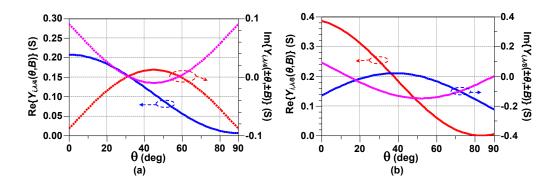

| Fig. 5-3: Simulated real and imaginary parts of the input admittance, $Y_{i,\lambda/m}(\theta, B)$ with stub         |

|----------------------------------------------------------------------------------------------------------------------|

| (realized using the same parameters as Fig. 5-2) at a) 1.8 GHz ( $\lambda/4$ ), and b) 0.9 GHz.                      |

| (λ/8)67                                                                                                              |

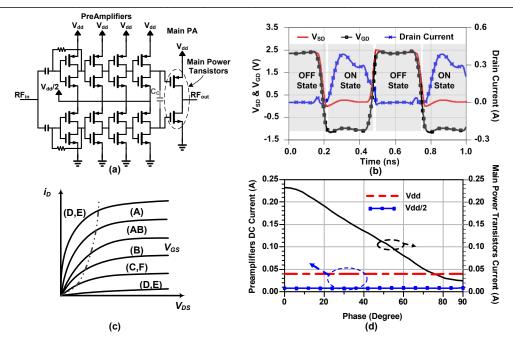

| Fig. 5-4: a) Proposed modified Class D PA and b) V <sub>SD</sub> , V <sub>GD</sub> and Drain current versus time for |

| main PMOS transistor                                                                                                 |

| Fig. 5-5: n-stage LC model of a transmission line (TL)                                                               |

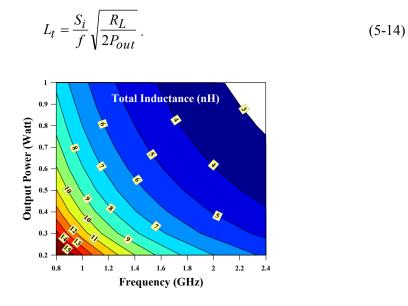

| Fig. 5-6: The value of the power combiner inductance versus frequency and output power with                          |

| a 50- $\Omega$ antenna resistance and a $S_i$ of 1.25 V                                                              |

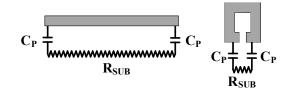

| Fig. 5-7: Fundamental model of a slab and one-turn spiral inductor                                                   |

| Fig. 5-8: Schematic of the proposed dual-band outphasing PA                                                          |

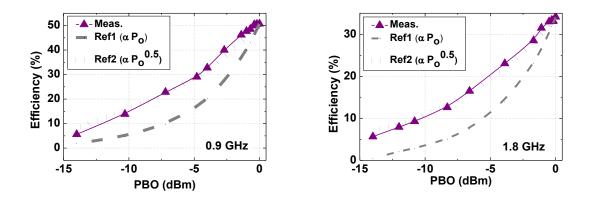

| Fig. 5-9: Simulated efficiency versus power back-off (PBO) of the circuit in Fig. 5-8 at 1.8                         |

| GHz ( $\lambda/4$ ), 0.9 GHz ( $\lambda/8$ ), without stub ( $B = 0$ ) and with stub ( $B = 0.27$ S corresponding to |

| $\theta_0 = 32^\circ$ ). Ref1 and Ref2 are calculated by assuming ideal Class A (proportional to $P_{out}$ )         |

| and ideal class B (proportional to $P_{out}^{0.5}$ ) respectively                                                    |

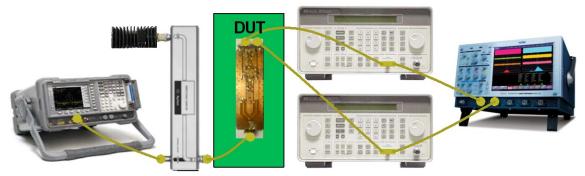

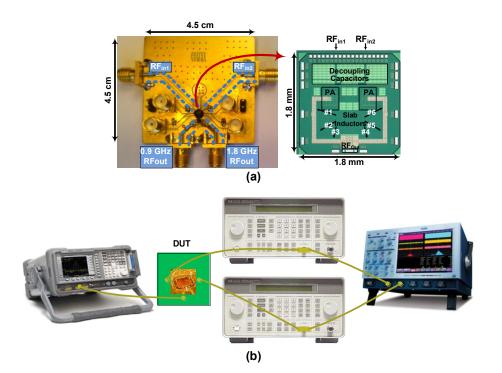

| Fig. 5-10: a) Photograph of the PCB and the chip and b) Measurement setup consisting of two                          |

| Agilent 8648C Synthesized RF Signal Generators, one Agilent 4404B spectrum analyzer,                                 |

| one Lecroy WaveMaster 8000A oscilloscope and the device under test (DUT)74                                           |

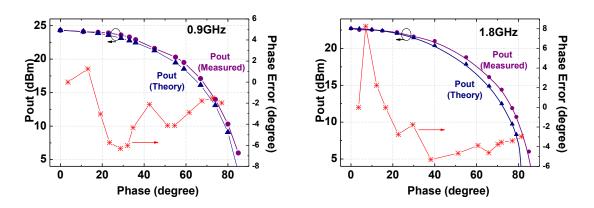

| Fig. 5-11: Measured and theoretical Pout versus input phase at 0.9 and 1.8 GHz and the                               |

| corresponding phase error74                                                                                          |

| Fig. 5-12: Measured efficiencies versus power back-off at (a) 0.9 and (b) 1.8 GHz and the                            |

| corresponding reference curves (Ref1 and Ref2) which are calculated by assuming ideal                                |

| Class A (proportional to $P_{out}$ ) and ideal class B (proportional to $P_{out}^{0.5}$ ) PAs respectively.          |

|                                                                                                                      |

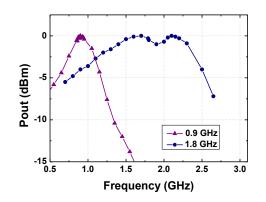

| Fig. 5-13: Measured <i>P</i> <sub>out</sub> versus frequency for the two bands                                       |

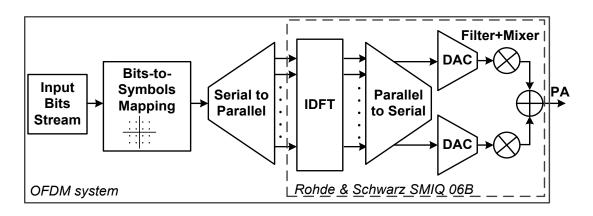

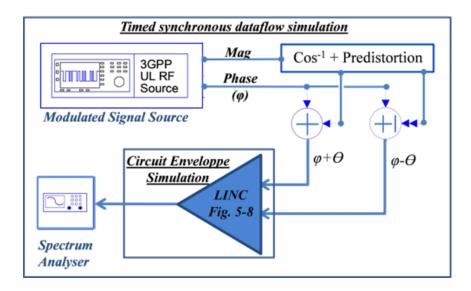

| Fig. 6-1: Functionality of an OFDM system                                                                            |

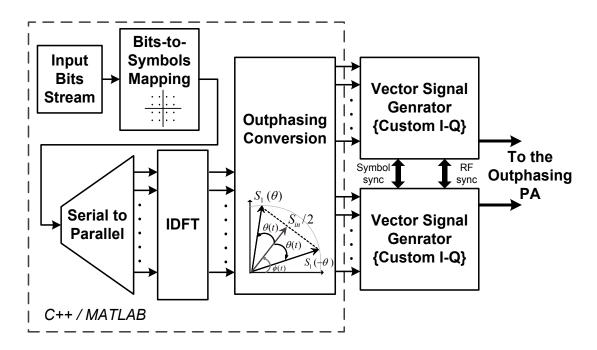

| Fig. 6-2: Generating outphase input signal                                                                           |

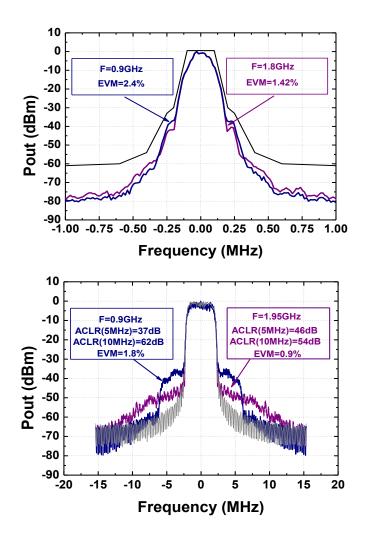

| Fig. 6-3: Simulated output power versus frequency for the two bands of the circuit in Fig. 5-8.                      |

|                                                                                                                      |

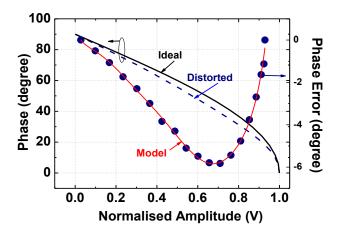

| Fig. 6-4: Ideal and simulated distorted phases versus normalized output amplitude at the                             |

| antenna of the circuit in Fig. 5-8 and the corresponding phase error (difference between                             |

| the simulated and ideal phase) with its 3rd order polynomial fitting model85                                         |

| Fig. 6- | -5: ADS test bench used for system level simulation.                                                    | 85 |

|---------|---------------------------------------------------------------------------------------------------------|----|

| Fig. 6- | -6: Normalized output power spectrums, EVM and ACLR simulated using the test benc                       | :h |

| 0       | of Fig. 6-5 for EDGE and WCDMA test signals.                                                            | 86 |

| Fig. 7- | -1: Simulated real and imaginary parts of the input admittance, $Y_{i,\lambda/16}(\theta, B)$ with stub |    |

| (1      | realized using the same parameters as Fig. 5-3 at 450MHz.                                               | 92 |

## List of tables

| Table 2.1. Comparison of semiconductor Technologies.    16 |

|------------------------------------------------------------|

| Table 5.1. Performance Comparison of Dual-Band PAs.    76  |

## Contents

| Ał | ostract.  | i                                                                       |

|----|-----------|-------------------------------------------------------------------------|

| Ré | ésumé .   | iii                                                                     |

| Li | st of fig | guresv                                                                  |

| Li | st of ta  | bles x                                                                  |

| Co | ontents   | xi                                                                      |

| 1  | Intr      | oduction1                                                               |

|    | 1.1       | Wireless communication Evolution, Challenges and Future Possibilities 1 |

|    | 1.2       | Motivation                                                              |

|    | 1.3       | Thesis Organization                                                     |

|    | Refere    | nces                                                                    |

| 2  | Intr      | oduction to the power amplifiers                                        |

|    | 2.1       | Power Amplifier metrics                                                 |

|    | 2.2       | Efficiency enhancement techniques                                       |

|    | 2.2.1     | Polar modulation                                                        |

|    | 2.2.2     | 2 Doherty Amplifier                                                     |

|    | 2.2.3     | Pulse-Width Pulse-Position Modulation (PWPM) 12                         |

|    | 2.2.4     | 4 Outphasing Modulation                                                 |

|    | 2.3       | Technology selection for power amplifiers                               |

|   | 2.3.1   | LDMOS power transistors                                           | 17 |

|---|---------|-------------------------------------------------------------------|----|

|   | Referer | nces                                                              | 20 |

| 3 | Theo    | pretical analysis                                                 | 21 |

|   | 3.1     | Classical outphasing PA modeling with ideal voltage sources       | 22 |

|   | 3.2     | Modeling outphasing PA considering PA's non-idealities            | 26 |

|   | 3.3     | Circuit oriented approach to simplify Chireix outphasing PA       | 29 |

|   | 3.4     | Validation of the proposed model                                  | 32 |

|   | 3.5     | Losses consideration in outphasing power combiner                 | 33 |

|   | 3.6     | Validation of the proposed model                                  | 35 |

|   | 3.7     | Summary                                                           | 39 |

|   | Referer | nces                                                              | 40 |

| 4 | Mod     | lified LINC architecture for base station applications            | 41 |

|   | 4.1     | Variable reactive load in LINC                                    | 41 |

|   | 4.2     | Theoritical analysis of Zero-capacitive LINC (Z-LINC) concept     | 47 |

|   | 4.3     | Reduced size power combiner with shorter TLs                      | 50 |

|   | 4.4     | Laboratory tests                                                  | 53 |

|   | 4.4.1   | Layout considerations                                             | 53 |

|   | 4.4.2   | Measurement setup                                                 | 54 |

|   | 4.4.3   | Measurement results of the 2-W PAs                                | 54 |

|   | 4.4.4   | Measurement results of the 10-W PA                                | 57 |

|   | 4.5     | Conclusion                                                        | 59 |

|   | Referer | nces                                                              | 60 |

| 5 | AM      | iniaturized Power Combiner for Multi-Band outphasing Transmitters | 61 |

|   | 5.1     | Dual-band outphasing PA                                           | 61 |

|   | 5.1.1   | Classical implementation                                          | 62 |

|   | 5.1.2   | Reconfigurable non-isolating power combiner                 | 63 |

|---|---------|-------------------------------------------------------------|----|

|   | 5.2     | Power Amplifier Design                                      | 67 |

|   | 5.2.1   | Reliability issues in CMOS technology                       | 67 |

|   | 5.3     | Implementation                                              | 69 |

|   | 5.4     | Measurement Results                                         | 73 |

|   | 5.5     | Conclusion                                                  | 76 |

|   | Referen | nces                                                        | 78 |

| 6 | Disc    | cussion on the linearity of the proposed PA                 | 81 |

|   | 6.1     | Outphase-component signal generator                         | 81 |

|   | 6.2     | Linearity performance of the Dual-Band Outphasing PA        | 82 |

|   | Referen | nces                                                        | 87 |

| 7 | Sum     | mary and Conclusion                                         | 89 |

|   | 7.1     | Summary                                                     | 89 |

|   | 7.2     | Conclusion                                                  | 89 |

|   | 7.3     | Future Directions                                           | 91 |

|   | 7.3.1   | Hybrid implementation                                       | 91 |

|   | 7.3.2   | Integration of Doherty PA using "reduced-size TL" technique | 91 |

|   | 7.3.3   | Z-LINC and HEMT devices                                     | 91 |

|   | 7.3.4   | WLAN IEEE 802.11 application                                | 92 |

|   | 7.3.5   | Reduced size $\lambda/16$ TL                                | 92 |

## 1 Introduction

#### 1.1 Wireless communication Evolution, Challenges and Future Possibilities

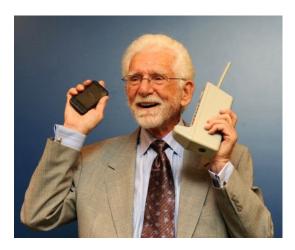

The wireless market has experienced a remarkable development since introducing the first modern mobile phone systems, with a steady increase in the number of subscribers, new application areas, and higher data rates. For instance, the first handheld mobile phone demonstrated by Martin Cooper of Motorola, was weighted around 1 Kg with less than 35 minutes talk time (Fig. 1-1) [1]. Now, with more than 6 billion wireless phone subscribers around the world, cellular phones are used as a GPS navigator, a multimedia center, a shopping terminus, a compact camera and lastly a telephone.

Cellular phones are not the sole example of a market that has prompted recent research activity but also wireless local-area networks (WLAN's) are another relatively new application of radio frequency (RF) circuit design. As mobile phones and wireless connectivity have become consumer mass markets, the major goal of the integrated circuit (IC) manufacturers is to provide low-cost solutions to maximize their profits. Accordingly, the inevitable task and ultimate goal of the modern wireless communication industry is the full integration of analog, digital and even RF circuits. To this end, the industry has devoted great effort to designing wireless terminals using a common semiconductor process that utilizes a single chip. The RF circuits have been predominantly designed in GaAs FET and silicon bipolar, due to the better performance [2].

Fig. 1-1: Enormous development in mobile industry; Martin Cooper shows his first handheld mobile phone and one latest small smart phone [1].

However, during the last decade, complementary metal oxide semiconductor (CMOS) has been the extensive choice for digital integrated circuits due to its high level of integration, low-cost, and constant improvements in performance [2]. To minimize the costs and allow full integration of a whole radio System-on-Chip (SoC), it is desirable to integrate the digital, analog and RF blocks in a single CMOS chip.

#### 1.2 Motivation

While digital circuits benefit from the technology scaling, because of the intrinsic drawbacks of standard CMOS processes from the RF perspective, several obstacles, especially low quality factor (Q) passive inductors, lossy and low resistive substrate, and low breakdown voltage of transistors [3], are hindering the realization of a fully-integrated CMOS transceiver. Low oxide breakdown voltage forces high output power CMOS RF power amplifiers (PAs) to operate under low input impedance and high current levels where they are sensitive to parasitics. On the other hand, efficiency is a big concern in linear PAs. Because of power back-off in modern communication systems, it is essential to improve the efficiency of the PA when it is not operating at its maximum output power. Since the PA is often the most power hungry component in the transmitter, its efficiency dominates system overall efficiency and thus battery

life-time of portable devices. The same problem happens in cellular base stations where a significant portion of the operating costs, come from losses in the PAs, including electricity expenses and additional costs because of bulky heat sinks. As a result, implementation of RF front-ends especially the PA in CMOS technology remains challenging task. This has recently triggered extensive studies to investigate the impact of different efficiency enhancement and linearization techniques, such as polar modulation and outphasing, in advanced CMOS technologies.

We mentioned that from a performance oriented point of view, CMOS technologies are not a good choice to implementing RF PAs. However, CMOS technology follow an aggressive down-scaling roadmap that is unbeatable when compared to any other semiconductor technology. Therefore, the integrability and versatility of CMOS technologies will be welcomed. Narrowing down the focus to the cost of PAs, CMOS technologies would be the cheapest among other candidates such as III-V HBT, III-V PHEMT, SiGe HBT, and MOSFET technologies [2].

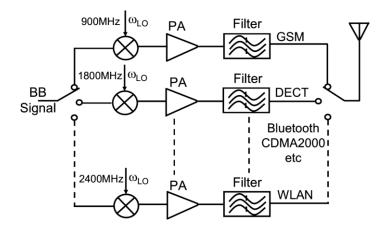

Besides low efficiency drawback of RF PAs at power back-off, multi-band connectivity is another issue to be dealt with in modern communication systems. Both mobile phone systems and WLANs have recently experienced a shift from a single to multi-standard connectivity. For example, a smart phone such as Galaxy S4 connects to 802.11 b/g/n Wi-Fi, Bluetooth 4.0, GLONASS, GPS, GSM / GPRS / EDGE, UMTS / HSDPA / HSUPA, and CDMA / EV-DO Revision A standards. These standards operate on the following frequencies: 800MHz, 850MHz, 900MHz, 1.9GHz, 2.1GHz, 2.4GHz, and 5.0GHz [4]. Today, each frequency requires its own wireless radio, as shown in Fig. 1-2.

This trend has been accelerated by the emergence of new communication technologies, such as software defined radio (SDR) and Cognitive Radio (CR) [5]. In fact, the success of SDR and CR technologies depends largely on the ability to design agile terminals, able to work simultaneously in different frequency bands and supporting various modulation schemes. Although several advances have been made in this direction, the success was restricted to the baseband and RF front-ends circuits [6]. Because of its challenging design, the PA has been excluded from this trend. Except a few attempts that are principally based on MEMS adaptive

Fig. 1-2: Conventional multi-standard transmitter with dedicated PA for each band.

matching networks [7], the multi-PAs implementations are still the dominant choice [8]. Thus, the second objective of the project is implementing the multi-band PAs. In chapter 5, we address the possibility of integrating dual-band, linear and power-efficient PAs in nanometer CMOS technologies at GHz frequencies.

#### **1.3** Thesis Organization

The outline of this thesis is as follow:

Chapter II briefly reviews several PA's performance metrics and different efficiency enhancement and linearization techniques. These techniques are compared and their benefits and drawbacks are briefly summarized. Furthermore, prevalent technologies for RF PAs are reviewed and compared. The device scaling and power supply trend in CMOS technology and its effect on PA design are also explained in this chapter.

Chapter III, provides a comprehensive analysis of outphasing PA modeling methods and challenges. A new analyzing method using a circuit-oriented approach is proposed. The new expressions are validated through several comparative tests using ADS and SpectreRF. Finally, the theoretical analysis is enhanced by including the losses in the power combiner.

Chapter IV explains the implementation of two outphasing PAs using LDMOS transistors. In this chapter we first explain the feature of the employed transistor. Then, two approaches of designing outphasing TX are explained, Zero capacitive LINC and power combiner miniaturization technique. Furthermore, simulation and measurement results are presented to validate the designs.

In chapter V, a prototype of the proposed outphasing CMOS PA is illustrated. The design procedure of a single band, slab- based power combiner and theoretical analysis of the proposed dual band outphasing power combiner are explained. In addition, the details of the PA design, its challenges, and the reliability issues in CMOS PAs are also described. To validate the design, the simulation and measurement results are presented.

Chapter VI, discuss the challenges in measuring the linearity performance of the outphasing PA and chapter VII concludes the thesis.

#### References

- [1] "Father of the Cell Phone," Economist, June 4, 2009.

- [2] T. Johansson, J. Fritzin, "A Review of Watt-Level CMOS RF Power Amplifiers," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 62, no. 1, pp. 111-124, Jan. 2014.

- [3] A. Hajimiri, "Next-generation CMOS RF power amplifiers," IEEE Mi-crow. Mag., vol. 12, no. 1, pp. 38–45, Feb. 2011.

- [4] http://www.samsung.com/

- [5] F. M. Ghannouchi, "Power Amplifier and Transmitter Architectures for Software Defined Radio Systems," *IEEE Circuits and Systems Magazine*, vol. 10, no. 4, pp. 56–63, 2010.

- [6] A. Koukab, Y. Lei, and M. Declercq, "A GSM-GPRS/UMTS FDDTDD/WLAN 802.11a-b-g multi-standard carrier generation system," *IEEE J. Solid-State Circuits*, vol. 41, no. 7, pp. 1513–1521, Jul. 2006.

- [7] A. van Bezooijen, M. A. d. Jongh, C. Chanlo, L. C. H. Ruijs, F. v. Straten, R. Mahmoudi, et al., "A GSM/ EDGE/WCDMA adaptive series-LC matching network using RF-MEMS switches," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 10, pp. 2259-2268, Oct. 2008.

- [8] A. Afsahi, A. Behzad, V. Magoon, and L. E. Larson, "Linearized Dual-Band Power Amplifiers With Integrated Baluns in 65 nm CMOS for a 2 × 2 802.11n MIMO WLAN SoC," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 955–966, May. 2010.

## 2 Introduction to the power amplifiers

Designing a PA for wireless communication standards that uses complex modulation schemes, needs a good understanding of the characteristics of the PA. This is essential to optimize its performance in terms of linearity and efficiency. There are different ways to measure the PA's linearity and the efficiency such as Spectral mask, EVM, Drain efficiency and PAE. In this chapter we will discuss these indices.

Furthermore, a trade-off between linearity and efficiency always exists in classic power amplifiers. Linear mode PAs like class-A and class-AB are good for linearity and switch mode PAs like class-E and class-F are good for efficiency. To overcome this trade-off, efficiency enhancement techniques such as Doherty, LINC, Envelop tracking and Polar Modulation are employed. In this chapter, these techniques and the appropriate technologies to implement mobile/base-station PAs are compared.

#### 2.1 **Power Amplifier metrics**

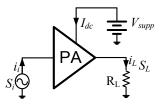

Output power is one of the key figures in designing PAs. It can be calculated [1] by measuring output voltage over the matched load or connecting PA output to the power meter (Fig. 2-1),

$$P_{out} = \frac{S_L^2}{2R_L}, \qquad (2-1)$$

where  $S_L$  is the voltage amplitude of the output signal. The gain of the PA can be defined as

Fig. 2-1: Simplified schematic of a PA.

Power Gain :

$$A_P = \frac{P_{out}}{P_{in}}$$

, (2-2)

Voltage Gain :

$$A_v = \frac{S_L}{S_i}$$

, (2-3)

where  $S_i$  and  $P_{in}$  are the input voltage amplitude and the input power respectively.  $A_P$  and  $A_V$  are equal in dB if the input and output impedance are equal and matched. The efficiency of a PA is a critical factor to measure how effectively input DC power is converted to RF power. The input DC power is,

$$P_{dc} = V_{supp} \times I_{dc}, \qquad (2-4)$$

Thus, the efficiencies can be defined as,

Drain Efficiency :

$$\eta_D = 100 \times \frac{P_{out}}{P_{dc}}$$

, (2-5)

Power Added Efficiency :

$$PAE = 100 \times \frac{(P_{out} - P_{in})}{P_{dc}}$$

. (2-6)

The term *PAE*, shows the ratio between the RF power added by the PA, and its DC power consumption. It is a better representative of the PA efficiency than the Drain efficiency, as it includes  $P_{in}$ . The most convincing method to measure the efficiency performance of the PA, used to amplify the variable envelope signal, is the average efficiency as it directly relates to the battery life time.

$$\overline{\eta}_{AVG} = 100 \times \frac{\left(\overline{P}_{out} - \overline{P}_{in}\right)}{\overline{P}_{dc}}, \qquad (2-7)$$

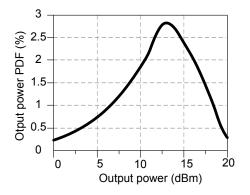

Fig. 2-2: Output power Probability Density Function (PDF).

and the average input and output power can calculated as

$$\overline{P}_{out} - \overline{P}_{in} = \int_{0}^{P_{out,\max}} (P_{out}(P_{out}) - P_{in}(P_{out})) \times PDF(P_{out}) dP_{out},$$

(2-8)

$$\overline{P}_{out} - \overline{P}_{in} = \int_{0}^{P_{out,\max}} P_{dc}(P_{out}) \times PDF(P_{out}) dP_{out},$$

(2-9)

where  $PDF(P_{out})$  is the output power Probability Density Function (PDF) shown in Fig. 2-2.

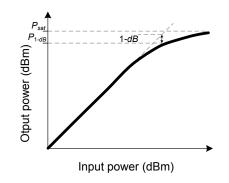

Two important parameters,  $P_{sat}$  and  $P_{1dB}$  are used to characterize PA output power.  $P_{sat}$  shows that maximums output power level, while  $P_{1dB}$  indicates output power level when the gain falls by 1dB below its linear value shown in Fig. 2-3.

Fig. 2-3:  $P_{sat}$  and  $P_{1-dB}$  of the PA output power.

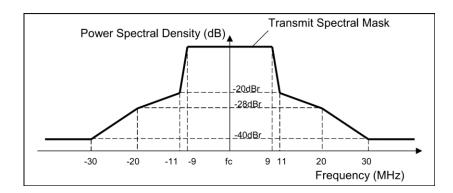

Fig. 2-4: Spectral mask versus frequency [2].

The PA linearity can be quantified by using output power spectral mask. Although the transmitted signal spectrum should be limited to the assigned frequency band, the transmitter nonlinearity spreads the spectrum to the adjacent channels. Each wireless standard has its own specific spectral mask. In general, it shows the in-band power density as a flat top and a mask that limits the out-of-band power radiation. Fig. 2-4 shows the spectral mask of a standard versus frequency. Another signal linearity metric is the Error Vector Magnitude (EVM) that is calculated on I and Q plane (Fig. 2-5). Due to several imperfections in the PA like non-linearity of the transistors, IQ imbalance, gain variations, noise, the constellation points of the transmitted signal deviate from their ideal locations. The difference between the measured signal and the ideal reference signal generates the error vector and in general is defined as the rms value of the error vector over time. The EVM value can be defined as

$$EVM = \begin{vmatrix} \vec{e} \\ \vec{r} \end{vmatrix}.$$

(2-10)

$$(2-10)$$

Fig. 2-5: EVM representation in IQ plane.

Fig. 2-6: Schematic of polar modulation/EER technique [3].

#### 2.2 Efficiency enhancement techniques

As discussed in previous section, complex modulations used in modern wireless communications impose considerable linearity requirements on the transmitter. As a result, PA efficiency should be sacrificed to provide the required linearity. To avoid this trade-off in linear PAs, a variety of new PA architecture have been proposed. Such architectures should satisfy the linearity limitation of the standard with an enhanced efficiency in power back-off mode. Among different types of new architecture, four important techniques are polar modulation, Doherty amplifier, Pulse-Width Pulse-Position Modulation (PWPM), and outphasing modulation.

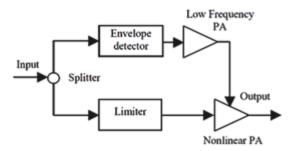

#### 2.2.1 Polar modulation

Polar modulation (Fig. 2-6), also known as Envelope Elimination and Restoration (EER) technique [3], was first introduced by Kahn in 1952. In a simplified model shown in Fig. 2-6, the amplitude and phase information in the variable envelope input signal are separated using an envelope detector and a limiter. As the envelope information is eliminated from the input signal, it can be amplified by a highly efficient switching PAs. The amplitude information is then amplified through a low frequency PA (Supply Modulator) and restored when modulates the PA's power supply. This method transfers efficiency-linearity trade-off from PA side to the Supply Modulator. To reach the highest efficiency, switching PAs are used in the supply modulator as well. But the efficiency of the supply modulator degrades significantly as bandwidth increases. During Cartesian to Polar conversion, the bandwidth of the amplitude signal expands by a factor of 5-10. As a result, this technique is typically suitable for low-

Fig. 2-7: Doherty PA and its normalized efficiency versus normalized output power [4].

bandwidth applications. Another drawback of the Polar modulation is the delay mismatch between the envelope and phase paths. This issue is exacerbated in GHz range frequencies.

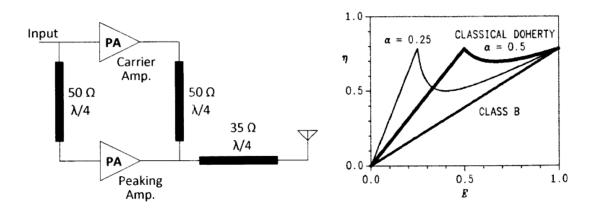

#### 2.2.2 Doherty Amplifier

The Doherty PA (Fig. 2-7) was first reported in 1936 by William H. Doherty of Bell Laboratories that was originally implemented using vacuum tubes [4], [5]. Fig. 2-7 shows its simple schematic which consists of a main and an auxiliary PA. The main (carrier) PA is biased in class-B/AB mode while the auxiliary (Peaking) PA is biased in Class-C mode. With this configuration, the auxiliary PA turns on only after the input amplitude exceeds a specific value. This means that at small input power, only the main PA is operational. As the input power is increasing the PA reaches its first maximum efficiency point. At this moment, the auxiliary PA is turned on. By reaching the maximum output power, the efficiency of the auxiliary PA and thus the total efficiency reach their maximum value. Therefore, the Doherty PA enhances the efficiency over a wide range of output power. The location of first peaking efficiency can be optimized depending on the PDF (Probability Density Function) of the output power. The main drawbacks of this technique is the three  $\lambda/4$  TLs which is very difficult to integrate at the typical frequencies used in modern telecommunication systems (0.8-3 GHz).

#### 2.2.3 Pulse-Width Pulse-Position Modulation (PWPM)

The Pulse-Width Pulse-Position Modulation (PWPM) technique employs pulse width modulated input signal to generate variable envelope output signal (Fig. 2-8). The output voltage

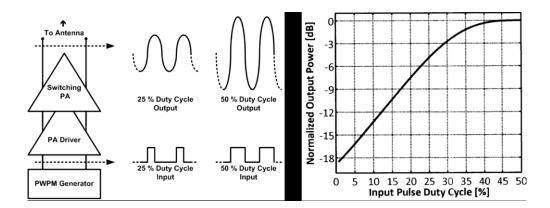

Fig. 2-8: Generalized PWPM PA and output power of an ideal Class E PA versus input pulse duty cycle [6].

in a Class-E [6] switching PA, depends on the conduction interval of the transistors and thus the duty cycle of input signal. The output phase is controlled by the position of the input pulse. PWPM achieved higher efficiency than the standard Doherty PA because it uses Switching PAs instead of Class-B/AB/C PAs. The main drawback of PWPM technique is its small PAPR (Peak to Average Power Ratio). For instance, Fig. 2-8 shows that in an ideal Class-E PA, the power back-off is less than 20 dB when the duty cycle is reduced to 1%. Besides the difficulty of generating such narrow pulses in GHz applications, these pulses are usually filtered by the large transistor input capacitance. In practice, the PAPR is less than 10 dB that is lower than the modern communication requirements.

#### 2.2.4 Outphasing Modulation

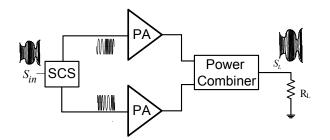

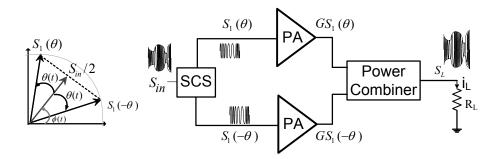

Outphsing technique, also named LINC (linear amplification using nonlinear components), was first proposed by Chireix in 1935 [7]. In this technique, the variable amplitude input signal (Fig. 2-9) decomposed to two phasors with constant envelope using signal component separator (SCS) shown in Fig. 2-9. By means of this decomposition the amplitude information transfers to phase domain. Thus, highly efficient switching PAs are used to amplify the phasors. The output of the PAs are summed in the power combiner to produce a linear amplified version of the input signal. In the next chapter, detailed theoretical analysis outphasing is explained.

Fig. 2-9: Simple schematic of outphasing modulation.

One of the drawbacks of Outphaisng, is its power combiner. Typical combiners (e.g. Wilkinson) achieve its maximum efficiency only at maximum output power. But, when the phasors are outphased and the output power is decreased, the remaining power is wasted in power combiner isolating resistor. This results in a degraded efficiency in power back-off. In the next chapter, our solutions for efficient combining will be explained. Delay mismatch is another drawback of outphasing technique. Fortunately, unlike polar modulation, the two paths are identical. Thus, the mismatch is minimized by using improved layout strategies in integrated applications. In the next chapter, the details of outphasing modulation will be discussed.

#### 2.3 Technology selection for power amplifiers

In this section, we describe two major semiconductor technologies CMOS and LDMOS, to implement integrated PAs for mobile applications and high-power PAs for base-station applications. Silicon has been preferred as semiconductor material because of its integrability and functionality along with a constant increase in its performance. By combining the low cost and integration capabilities of CMOS/BiCMOS, these technologies were the choice of RF transceivers with fully-integrated PAs, as long as RF and system design goals can be achieved. As wireless functionality has been integrated into more and more applications and entered mass-consumer markets, silicon-based technologies have continuously replaced the traditional semiconductors. Currently, the market of integrated wireless transceivers is dominated by CMOS, where fully-integrated solutions, including the PA, have been presented. Silicon-based technologies will be the choice for high volume and cost sensitive markets, but is not expected to be the choice when the PA metrics are very high gain, very high output power, and extremely low noise.

First, a short comparison of the specific properties of III-V compounds and silicon is given here because it was one of the first semiconductors used in RF design and is still used in PA design. Key characteristics of the basic materials are shown in Table 2.1. For example, the carrier velocity and mobility of the electrons are higher than the holes and its difference is much larger in III-V devices (e.g. GaAs) than for silicon devices [8]. In addition, the carrier velocity and mobility of electrons are lower in silicon devices. Because of the large gap in complementary III-V devices and the lower hole carrier velocity and mobility in GaAs, silicon technologies are more suitable for high speed complementary logic applications. Conversely, for high-speed applications, n-based GaAs devices has advantageous as long as no complementary devices are used.

Thermal conductivity is another important factor in complementary logic circuits. Considering too many transistors for example in an integrated PA, heating dissipation may cause problem. Thus, a good thermal conductivity of the substrate material is mandatory to ensure that the chip is not overheated. The comparable integration level in GaAs is typically limited to approximately 1000 transistors [8].

Substrate resistivity is another weakness of the silicon devices that is relatively low compared to the III-V semiconductors, and degrades the quality factor of integrated passives [9]. An advantage of silicon and CMOS is its production cost, and the relative speed performance between the electron and hole carrier based devices. This makes silicon a superior choice for complementary logic circuits. Integration of PA could further reduce the cost and BiCMOS solves the integration of the PA and with better RF performance of the bipolar devices compared to the MOSFET devices. It has around 20% higher mask count and thus a higher price for the same technology [10].

Although GaAs has a lower mask price thus lower prototype cost, Silicon has the advantage of higher yield and using larger wafers. As a result Silicon is the cheaper option in mass fabrication.

The historical trend of CMOS scaling has enabled high-speed CMOS devices a preferable solution in complementary logic circuits, and the trend is expected to continue, but at the expense

of lower supply voltages. The supply voltage and thus the RF output power of III-V technologies are higher. Therefore these technologies is the dominant choice in the market of PAs for handset applications [11]. For higher output power, SiC, GaN, and also LDMOS have better performance over the other devices, because of their higher supply voltage and thermal conductivity, with the cost of a lower level of integration.

|                          | Silicon    | SiC        | InP       | GaAs    | GaN        |

|--------------------------|------------|------------|-----------|---------|------------|

| Electron mobility a 300K | 1500       | 700        | 5400      | 8500    | 1000-2000  |

| [cm <sup>2</sup> /Vs]    |            |            |           |         |            |

| Hole mobility at 300K    | 450        | n.a        | 150       | 400     | n.a        |

| [cm <sup>2</sup> /Vs]    |            |            |           |         |            |

| Bandgap [eV]             | 1.1        | 3.26       | 1.35      | 1.42    | 3.49       |

| Critical breakdown field | 0.3        | 3.0        | 0.5       | 0.4     | 3.0        |

| [MV/cm]                  |            |            |           |         |            |

| Thermal                  | 1.5        | 4.5        | 0.7       | 0.5     | >1.5       |

| conductivity [W/(cm K)]  |            |            |           |         |            |

| Substrate resistivity    | 1-20       | 1-20       | >1000     | >1000   | >1000      |

| [Ωcm]                    |            |            |           |         |            |

| Number of transistors    | >1 billion | <200       | <500      | <1000   | <50        |

| in IC                    |            |            |           |         |            |

| Transistors              | MOSFET,    | MESFET,    | MESFE,    | MESFET, | MESFET,    |

|                          | Bipolar,   | HEMT       | HEMT,     | HEMT,   | HEMT       |

|                          | HBT,       |            | HBT       | HBT     |            |

|                          | LDMOS      |            |           |         |            |

| Costs prototype,         | High,      | Very high, | High,     | Low,    | Very high, |

| mass fabrication         | low        | n.a.       | very high | high    | n.a.       |

Table 2.1. Comparison of semiconductor Technologies [8]

#### 2.3.1 LDMOS power transistors

About 20 years ago LDMOS (Laterally Diffused Metal-Oxide-Semiconductor) transistors were introduced as a replacement of BJT (Bipolar Junction Transistor) for RF power applications [12]. In fact, LDMOS devices are enhanced Nchannel MOSFETs (Metal-Oxide-

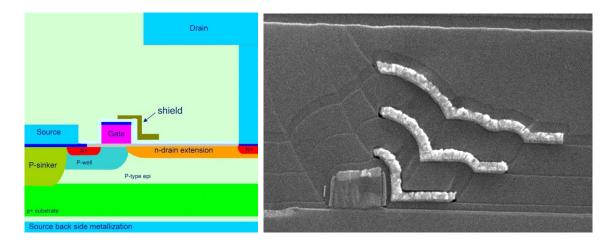

Fig. 2-10: LDMOS cross section schemantic and photo [12].

Semiconductor Field-Effect Transistor). Today, LDMOS technology is the leading RF power technology for base station applications, in particular for GSM-EDGE at 1 and 2 GHz, WCDMA at 2.2 GHz and more recently for WiMax applications at 2.7 GHz and 3.8 GHz. The power range of LDMOS spans more than three decades ranging from a few watts for driver devices up to hundreds of watts for base station applications.

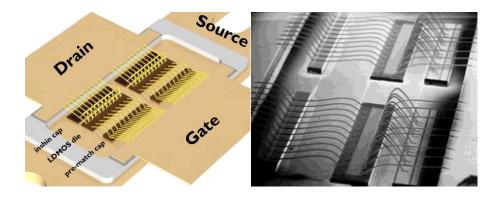

The cross section of the device (Fig. 2-10) is optimized for high frequency and high voltage operation with small parasitic capacitance. It is designed to realize higher  $f_T$ , lower third order intermodulation and higher  $g_m$  and gain at high power level. These specifications enables to design PAs with better efficiency and fewer gain stages compare to BJT. Its main difference with standard CMOS is that an LDMOS transistor has a drain extension region to support a higher breakdown voltage. To provide high power, LDMOS devices are mounted with multiple fingers in parallel inside the package (Fig. 2-12). The flange is soldered to the source at backside of the device however the drain and gate are connected via bond wires to the pads. The input and output impedance of the device can be below a few ohms, thus input and output matching could be employed inside the package to transform the impedance level.

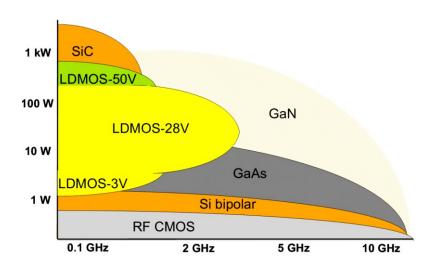

Fig. 2-11 shows a summary of the preferred technologies for today's PA design as a function of output power and operating frequency. It is shown that LDMOS is expanding towards the high frequency and high power applications.

Fig. 2-12: LDMOS device with input and output matching inside the package [12].

Fig. 2-11: Technology selection based on operating frequency and output power [13].

#### References

- [1] B. Razavi, RF Microelectronics, Second Edition, Prentice-Hall, 2012.

- [2] Wireless LAN and Medium Access Control (MAC) and Physical Layer (PHY) Specifications: *High-speed Physical Layer in the 5GHz Band*, IEEE Std. 802.11a-1999.

- [3] J. S. Walling and D. J. Allstot, "Design considerations for supply modulated EER power amplifiers," *IEEE* 14th Annual Wireless and Microwave Technology Conference (WAMICON), pp. 1-4, April 2013.

- [4] B. Kim, I. Kim and J. Moon "Advanced Doherty architecture," *IEEE Microwave Mag.*, vol. 5, pp.72 -86 2010

- [5] R. Darraji, and F. M. Ghannouchi, "RF/DSP Codesign Methodology of Enhanced Doherty Amplifiers," *IEEE Trans. Circuits Syst.* II, vol. 59, no. 4, pp. 219–223, Apr. 2012.

- [6] J. S. Walling, H. Lakdawala, Y. Palaskas, A. Ravi, O. Degani, K. Soumyanath and D. J. Allstot "A class-E PA with pulse-width and pulse-position modulation in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 6, pp.1668 -1678, 2009.

- [7] H. Chireix, "High power outphasing modulation," Proc. IRE, Vol. 23, No.11, pp 1370-1392, Nov 1935.

- [8] F. Ellinger, *Radio Frequency Integrated Circuits and Technologies*, Berlin, Germany: Springer, Second Edition, 2008.

- [9] B.A. Floyd, C.-M. Hung, K.K. O, "The Effects of Substrate Resistivity on RF Component and Circuit Performance," *IEEE International Interconnect Technology Conference*, pp. 164-166, June 2000.

- [10] S. Bennett, R. Brederlow, J.C. Costa, P.E. Cottrell, W.M. Huang, A.A. Immorlica, J.-E. Mueller, M. Racanelli, H. Shichijo, C.E. Weitzel, B. Zhao, "Device and Technology Evolution for Si-Based RF Integrated Circuits," *IEEE Transactions on Electron Devices*, vol. 52, no. 7, pp. 1235-1258, July 2005.

- [11] M.J. Franco, "Mobile handset power amplifiers," *IEEE Microwave Magazine*, vol. 10, no. 7, pp.16-19, December 2009.

- [12] S. J. C. H. Theeuwen and J. H. Qureshi, "LDMOS technology for RF power amplifiers," *IEEE Trans. Microw. Theory Tech.*, vol. 60, no. 6, pp. 1755–1763, Jun. 2012.

- [13] S.J. Theeuwen and H. Mollee, "LDMOS transistors in power microwave applications," White Paper, NXP semiconductors.

# **3** Theoretical analysis

The design of PAs, particularly for highly efficient and linear operation, remains a difficult problem that needs theoretical models for preliminary analysis, parameters specification and performance optimization before starting circuits design and simulation. In the particular case of outphasing PA, the theoretical analysis with an ideal power combiner was proposed first in [1]. This work was later completed in [2] by considering the effect of impedance mismatch between the amplifiers and the combiner. Despite the simplification of the problem by neglecting the power combiner non-idealities, the expressions describing outphasing TX are too complex and far from intuitive [2]. This chapter provides a comprehensive analysis of outphasing PA modeling methods and challenges. We study different types of outphasing combiners and explain how they introduce reactive loads and impact the efficiency and linearity of the PA. Then, we analyze a complex model of Chireix combiner considering the reflection due to impedance mismatch and the effects of compensating stubs. Afterwards, a new analyzing method using a circuit-oriented approach is proposed. A simplified analytical formula expressing the output power directly in terms of the non-distorted input phase is derived. The new expressions are validated through several comparative tests using ADS and SpectreRF. Finally, the theoretical analysis is enhanced by including the losses in the power combiner.

Fig. 3-1: Simplified diagram of Outphasing Tx.

# 3.1 Classical outphasing PA modeling with ideal voltage sources

Our analysis starts by considering the classical outphasing PA [1], [3] shown in Fig. 3-1. The envelope modulated input signal

$$S_{in}(t) = |S_{in}(t)|e^{j\varphi(t)},$$

(3-1)

is transformed in two constant envelope signals

$$S_1(\pm\theta(t)) = S_m e^{j(\varphi(t)\pm\theta(t))}, \qquad (3-2)$$

where

$$\theta(t) = \cos^{-1} \left( |S_{in}(t)| / 2S_m \right).$$

(3-3)

Since the signals  $S_1(\pm\theta)$  exhibit no envelope variation, highly efficient nonlinear PAs (e.g. class F, D or saturated class B) can be used for their amplification [4]. After amplification, the signals are combined, resulting ideally in an amplified replica of the input signal at the antenna, i.e.

$$S_L(t) = G(S_1(\theta) + S_1(-\theta)) = GS_{in}(t).$$

(3-4)

where G is the gain of the non-linear PAs. An efficient power combining method is needed to combine the two amplified outphased signals and produce the desired output signal. Basically two families of power combiners can be used for this operation: isolating combiners (e.g. Hybrid

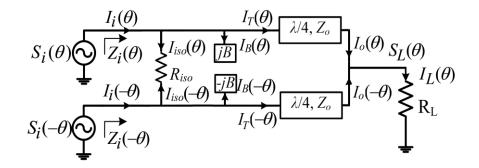

Fig. 3-2: A general four-terminal combiner, a) Wilkinson with B = 0, b) Chireix with  $R_{iso} = \infty$  and B = 0, and c) Chireix with stub and  $R_{iso} = \infty$ .

or Wilkinson) and non-isolating combiners (e.g. Chireix [3] or transformers [5]). Fig. 3-2 shows a general four-terminal outphasing combiner. Each PA replaced by an ideal voltage source without loss of generality. From (3-2) and Fig. 3-1, the signal at the input of power combiner is

$$S_i(\pm\theta(t)) = GS_1(\pm\theta(t)) = GS_m e^{j(\varphi(t)\pm\theta(t))}.$$

(3-5)

For simplicity, the phase of the input signal,  $\varphi(t)$ , can be ignored without affecting the analysis. Therefore we can write

$$S_i(\pm\theta) = S_{max} e^{\pm j\theta}, \qquad (3-6)$$

where  $S_{max} = GS_m$ . Now we replace the PAs by ideal voltage sources (without loss of generality), as illustrated in Fig. 3-2 and we use ABCD matrix of the TL with an electrical length  $\alpha = 90^{\circ}$ and a characteristic impedance of  $Z_o$

$$\begin{bmatrix} S_i \\ I_T \end{bmatrix} = M_{\lambda/4} \begin{bmatrix} S_L \\ I_o \end{bmatrix} = \begin{bmatrix} \cos \alpha & jZ_o \sin \alpha \\ \frac{j \sin \alpha}{Z_o} & \cos \alpha \end{bmatrix}_{\alpha = 90^\circ} \begin{bmatrix} S_L \\ I_o \end{bmatrix} = \begin{bmatrix} 0 & jZ_o \\ j/Z_o & 0 \end{bmatrix} \times \begin{bmatrix} S_L \\ I_o \end{bmatrix}, \quad (3-7)$$

the output current and voltage are expressed as follows,

$$I_o(\pm\theta) = -j.\frac{1}{Z_o}.S_i(\pm\theta) = -j.\frac{1}{Z_o}S_{max}e^{\pm j\theta},$$

(3-8)

$$S_L(\theta) = Z_L \times I_L(\theta) = Z_L \cdot (I_o(+\theta) + I_o(-\theta)) = -j \cdot \frac{2R_L}{Z_o} S_{max} \cos(\theta) .$$

(3-9)

The output power is therefore given by

$$\left|P_{out}(\theta)\right| = \left|\frac{S_L^2(\theta)}{2R_L}\right| = \frac{2R_L}{Z_o^2} S_{max}^2 \cos^2(\theta), \qquad (3-10)$$

and varies from 0 at  $\theta = 90$  to its maximum value  $(2R_LS^2_{max} Z_o^{-2})$  at  $\theta = 0$ . In order to calculate the input power ( $P_{in}$ ) and thus the efficiency, we start by analysing the input resistance. From (3-7) and (3-9) the input current of Wilkinson power combiner in Fig. 3-2.a, can be expressed as

$$I_{i,Wilk}(\theta) = I_T + I_{iso} = \frac{2R_L}{Z_o^2} S_{max} \cos(\theta) + \left(S_i(+\theta) - S_i(-\theta)\right) / R_{iso}, \qquad (3-11)$$

In a matched condition where  $R_{iso} = Z^2_O/R_L$ , the input impedance of the Wilkinson combiner is

$$Z_{i,Wilk}(\pm\theta) = S_i(\pm\theta) / I_{i,Wilk}(\pm\theta) = \frac{Z_o^2}{2R_L}.$$

(3-12)

In isolating condition, the input impedance and thus the input power are independent of  $\theta$ . Indeed, the constant value of  $Z_{i,wilk}$  results in a constant input power,

$$\left|P_{in,Wilk}(\theta)\right| = \left|\frac{S_i^2(\theta)}{2Z_{i,Wilk}(\theta)}\right| + \left|\frac{S_i^2(-\theta)}{2Z_{i,Wilk}(-\theta)}\right| = \frac{2R_L}{Z_o^2}S_{max}^2.$$

(3-13)

As a consequence the efficiency of Wilkinson combiner,

$$\eta_{Wilk}(\theta) = \frac{\left|P_{out}\right|}{\left|P_{in,Wilk}\right|} \times 100 = \cos^{2}(\theta) \times 100 \ (\%) \propto \left|P_{out}(\theta)\right|, \tag{3-14}$$

is significantly degraded when  $\theta$  is increased (power back-off mode). The difference between input and output power, is wasted as heat in the isolating resistor ( $R_{iso}$ ). This loss nullifies the efficiency advantage inherent to the use of non-linear PAs and thus, limits the attractiveness of these combiners for LINC. In contrast, a non-isolating power combiner (Fig. 3-2.b) preserves the LINC efficiency even in power back-off mode [1]. In this method the isolating resistor is removed to provide a pure reactive power combiner, commonly known as Chireix combiner. In this case, from (3-7) and (3-9) we have

$$I_{i,Chireix}(\pm\theta) = \frac{2R_L}{Z_o^2} S_{max} \cos(\theta), \qquad (3-15)$$

$$Z_{i,Chireix}(\pm\theta) = S_i(\pm\theta) / I_{i,Chireix}(\pm\theta) = \frac{Z_o^2}{R_L} \cdot (1 \pm j \tan(\theta))$$

$$= \left[Y_{i,Chireix}(\pm\theta)\right]^{-1} = \left[\frac{R_L}{Z_o^2} \cdot (2\cos^2(\theta) \mp j\sin(2\theta))\right]^{-1}.$$

(3-16)

In Chireix combiner the magnitude of the input impedance,

$$\left|Z_{i,Chireix}(\pm\theta)\right| = \frac{Z_o^2}{2R_L\cos(\theta)},$$

(3-17)

represents an increasing function of  $\theta$  for  $0^{\circ} < \theta < 90^{\circ}$ . Consequently, the input power

$$\left|P_{in,Chireix}(\theta)\right| = \left|\frac{S_i^2(\theta)}{2Z_{i,Chireix}(\theta)}\right| + \left|\frac{S_i^2(-\theta)}{2Z_{i,Chireix}(-\theta)}\right| = \frac{2R_L}{Z_o^2}S_{max}^2\cos(\theta), \qquad (3-18)$$

is a decreasing function of  $\theta$ , which results in an improved efficiency in power back-off. In fact we can write,

$$\eta_{Chireix}(\theta) = \frac{|P_{out}|}{|P_{in,Chireix}|} \times 100 = \cos(\theta) \times 100 \ (\%) \propto \sqrt{|P_{out}(\theta)|} \ . \tag{3-19}$$

Although Chireix combiner exhibits better efficiency compare to Wilkinson combiner, it still suffers from a diminution of the efficiency at high power back-off, principally because of the reactive loads introduced by the  $\lambda/4$  TLs. Indeed, from (3-16) the imaginary part of the input admittance is

$$\operatorname{Im}(Y_{i,Chireix}(\pm\theta)) = \mp R_L \sin(2\theta) / Z_o^2.$$

(3-20)

Now, by placing the shunt stubs  $\pm jB$ , as shown in Fig. 3-2.c, and by choosing its susceptance as

$$B = R_L \sin(2\theta_0) / Z_o^2, \qquad (3-21)$$

the imaginary part of the input impedance becomes null at the specific angle  $\theta_0$  and at 90 -  $\theta_0$ [1]. Therefore, the theoretical efficiency reaches 100% at these two angles. The input impedance of Chireix combiner with stub can be expressed as

$$Z_{i,Stub}(\pm\theta) = Z_{i,Chireix}(\pm\theta) \left\| B^{-1} = \frac{Z_o^2}{R_L} \cdot \left( 2\cos^2(\theta) \mp j(\sin(2\theta) - \sin(2\theta_0)) \right)^{-1} \right\|$$

(3-22)

Thus, the input power and efficiency are given by

$$\left|P_{in,Stub}(\theta)\right| = \left|\frac{S_i^2(\theta)}{2Z_{i,Stub}(\theta)}\right| + \left|\frac{S_i^2(-\theta)}{2Z_{i,Stub}(-\theta)}\right| = \frac{R_L}{Z_o^2} S_{max}^2 \sqrt{4\cos^4(\theta) + (\sin(2\theta) - \sin(2\theta_0))^2} \quad (3-23)$$

$$\eta_{Stub}(\theta) = \frac{|P_{out}|}{|P_{in,stub}|} \times 100 = \frac{2\cos^2(\theta)}{\sqrt{4\cos^4(\theta) + (\sin(2\theta) - \sin(2\theta_0))^2}} \times 100 \ (\%) \ . \tag{3-24}$$

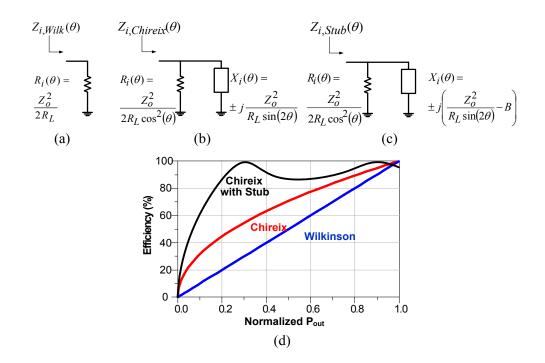

Fig. 3-3 summarized the input impedance of the mentioned combiners and shows their efficiencies versus normalized output power. As expected, Chireix combiner with stub exhibits the best efficiency performance, with a theoretical value of 100 % for the output powers corresponding to  $\theta_0$  and at 90 -  $\theta_0$ .

# 3.2 Modeling outphasing PA considering PA's non-idealities

In the models developed in the last section, the PAs were replaced by ideal voltage source. In practical cases however, voltage mode PAs (e.g. class D or F) can be approximated by an ideal voltage source and a series resistance to consider their finite output impedance in the models. On the other hand, the combiner provides variable loads with  $\theta$  (3-22) and hence working in a matched condition for all output powers is impossible [2]. The principal

Fig. 3-3: The input impedance of a) Wilkinson, b) Chireix and c) Chireix with stub power combiners. d) Efficiency vs. Normalized  $P_{OUT}$  for different types of combiners.

consequence of this mismatch is a reflection of power at the output of the PAs. A PA driving a mismatched load (with a reflection coefficient of  $\Gamma$ ) has an efficiency equal to  $(1-|\Gamma|^2)\eta_{max}$ ; where  $\eta_{max}$  is the efficiency of a PA driving a matched load.

Fig. 3-4.a shows PAs driving Chireix combiner with stubs. Unlike previous section, here we use two PAs with a gain of *G* and output resistance of  $Z_1$ . El-Asmar et al. demonstrate in [2] after a tremendous theoretical calculations, the following expression for  $Z_2$  as a function of  $\theta$  and the normalized stub suceptance  $\beta$ , when reflected waves are considered:

$$Z_{2}(\beta,\theta^{*}) = \frac{1}{\frac{y^{2}}{R_{L}} \left( 2\cos^{2}(\theta^{*}) + j[\beta - \sin(2\theta^{*})] \right)},$$

(3-25)

where  $y = R_L/Z_o$  and  $\beta = B.R_L/y^2$ . And  $\theta^*$  is given by

Fig. 3-4: a) Chireix-Outphasing topology with stub and b) simplified topology.

$$\theta = \theta^* - \text{phase}(1 + \Gamma(\beta, \theta^*)) . \tag{3-26}$$

where  $\Gamma(\beta, \theta^*)$  is the reflection coefficient caused by the mismatch between  $Z_1$  and the power combiner input impedance,  $Z_2$ ,

$$\Gamma(\beta, \theta^*) = \frac{Z_2(\beta, \theta^*) - Z_1}{Z_2(\beta, \theta^*) + Z_1}.$$

(3-27)

The output voltage and efficiency according to [2] are

$$S_L(\beta, \theta^*) = 2y.G.S_{max} | 1 + \Gamma(\beta, \theta^*)| .\cos(\theta^*), \qquad (3-28)$$

$$\eta(\beta, \theta^*) = \frac{8y^2 \cos^2(\theta^*)}{\left(1 + 2y^2 \cos^2(\theta^*)\right)^2 + y^4 \left(\beta - \sin(2\theta^*)\right)^2} \times 100 \ (\%) , \qquad (3-29)$$

where  $\theta^*$  can be derived from the following equation [2]

$$\cos(\theta^*) = \frac{1 + y^2 \beta \tan(\theta)}{\sqrt{\left(1 + y^2 \beta \tan(\theta)\right)^2 + \left((1 + 2y^2) \tan(\theta) - y^2 \beta\right)^2}}.$$

(3-30)

In outphasing Tx, the phase ( $\theta$ ) and the amplitude ( $S_m$ ) are accurately calculated in order to reproduce the envelope variation of the modulated signal at the antenna. The unavoidable distortion of these parameters results in a severe degradation of the transmitted signal.

Fig. 3-5: a) Chireix-outphasing topology with stub and b) simplified topology.

Nevertheless, the complexity of the mathematical treatment of the nonlinear relations between  $\eta$ ,  $\theta^*$  and  $\theta$  illustrated in (3-29) and (3-30), makes the development and implementation of predistortion functions extremely difficult.

# 3.3 Circuit oriented approach to simplify Chireix outphasing PA

In this section, we introduce an alternative method [6] to investigate the possible circuit transformations that would simplify the mathematical treatment and enable a more compact model. Because the phase distortion  $\theta^*$  is the origin of the complexity of (3-30), we propose to bypass this parameter during the analysis. For this, we will create fictive nodes with voltages  $S_0(\pm\theta)$ , by adding the impedances  $-Z_1$  and  $+Z_1$  at the output of the PA (Fig. 3-4.b). In fact, the impedances seen at these points (i.e  $Z_1$ ) are zero and thus the reflection coefficients ( $\Gamma$ ) are equal to 1, which explains the non-distortion of the phase and amplitude at these nodes.  $S_0(\pm\theta)$  is thus expressed as

$$S_0(\pm\theta) = G.S_1(\pm\theta)[1+\Gamma] = 2GS_m e^{\pm j\theta}.$$

(3-31)

Notice that this transformation enables us to express  $Z_2(\pm\theta^*)$  in terms of the non-distorted phase  $\theta$  if  $Z_2'(\pm\theta)$  is known (i.e.  $Z_2(\pm\theta^*) = Z_2'(\pm\theta) - Z_1$ ). In order to calculate  $Z_2'(\pm\theta)$ , other transformations are required. The impedances seen at the input of the two  $\lambda/4$  transition lines at  $\theta^* = 0$  are equal to  $Z_o^2/2R_L$ . Consequently, the part of the circuit driven by  $S_0(\pm\theta)$  in Fig. 3-4.b can be simplified to the circuit (a) in Fig. 3-5. Now we assume that the current  $i_B$  in Fig. 3-5.a is very small respect to  $i_1$ . This assumption will be validated later. In this case, we can write

$$|S_{2}(\theta^{*}=0)| = \frac{\frac{Z_{o}^{2}/2R_{L}}{2R_{L}}}{\frac{Z_{o}^{2}/2R_{L}}{2R_{L}} + |Z_{1}|} |S_{0}| = |i_{B}|B^{-1}.$$

(3-32)

Since  $i_B$  is very small, it has a negligible impact on the current over  $Z_1$ . Therefore, we can shift the place of the stubs in Fig. 3-4 towards the nodes  $S_0(\pm\theta)$ , as shown in Fig. 3-5.b. On the other hand, in order to keep the currents  $i_L$  and thus,  $i_B$  the same in Fig. 3-5 (a) and (b), the value of *B* is changed to  $B^*$ , calculated from (3-32) as

$$B^{*} = \frac{|i_{B}|}{|S_{0}|} = B \frac{\frac{Z_{o}^{2}}{2R_{L}}}{\frac{Z_{o}^{2}}{2R_{L}} + |Z_{1}|}.$$

(3-33)

In this way, the circuit (a) of Fig. 3-5 is simplified to (b), where the two signals  $S_0(\pm\theta)$  differentially drive the impedance  $Z_3$  ( $Z_3 = 2Z_1 + Z_O^2/R_L$ ). This enables to determine  $Z_2'(\pm\theta)$  as

$$Z_{2}'(\pm B, \pm \theta) = \left(\frac{1}{Z_{3}} \frac{S_{0}(\theta) + S_{0}(-\theta)}{S_{0}(\pm \theta)} \pm jB\right)^{-1} = \left\lfloor \frac{1}{Z_{3}} \left(2\cos^{2}(\theta) \pm j\left(B^{*}Z_{3} - \sin(2\theta)\right)\right) \right\rfloor.$$

(3-34)

Now, we return to the circuit of the transmitter in Fig. 3-4.b and we express the  $Z_2$  (i.e.  $Z'_2 - Z_1$ ) and  $S_i$  in terms of the non-distorted phase and amplitude (i.e.  $\theta$  and  $G.S_m$ ) as

$$Z_{2}(\pm\theta) = \left[\frac{1}{Z_{3}} \left(2\cos^{2}(\theta) \pm j\left(B^{*}Z_{3} - \sin(2\theta)\right)\right)\right]^{-1} - Z_{1}.$$

(3-35)

$$S_{2}(\pm\theta) = S_{0}(\pm\theta) \cdot \left(1 - \frac{Z_{1}}{Z_{2}}(\pm\theta)\right) = 2GS_{m}e^{\pm j\theta} \cdot \left[1 - \frac{Z_{1}}{Z_{3}}\left(2\cos^{2}(\theta) \pm j\left(B^{*}Z_{3} - \sin(2\theta)\right)\right)\right] (3-36)$$

This approach makes it possible to completely bypass  $\theta^*$  (3-30) and its inherent complex mathematical treatment. The power delivered to the load can now be determined from (3-35) and (3-36) in terms of the non-distorted phase and amplitude as

$$P_{out} = Mag \left( S_2(\pm \theta) \right)^2 \operatorname{Re} \left( \frac{1}{Z_2(\pm \theta)} \right).$$

(3-37)

On the other hand, the theoretical determination of the efficiency is more complex since it depends on dc power consumption of the PAs. To gain insights into efficiency evolution with design parameters we will make two assumptions. First, we can suppose the maximum voltage that the PA (i.e. in saturation) can deliver to a load, when its output impedance is null, is equal to its power supply ( $V_{DD}$ ). In our case, this means that  $V_{DD}$  is equal to  $2GS_m$ . Furthermore, the dc current consumed by the PA is in general, proportional to its output RF current (e.g.  $I_{dc} = k.(i_1 + i_B) = k.2GS_m.Mag(1/Z_2^2)$ , k is a constant). From that, we can define a normalized efficiency as