# Architectural Support to Accelerate Fine-Grain Program Monitoring

#### THÈSE N° 6257 (2014)

PRÉSENTÉE LE 3 OCTOBRE 2014

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE D'ARCHITECTURE DE SYSTÈMES PARALLÈLES

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Sotiria FYTRAKI

acceptée sur proposition du jury:

Prof. M. Grossglauser, président du jury Prof. B. Falsafi, directeur de thèse Dr E. Bugnion, rapporteur Dr Ph. Gibbons, rapporteur Prof. S. Kaxiras, rapporteur

## Acknowledgements

First and foremost, I would like to thank my academic advisor Babak Falsafi for giving me the opportunity to make this journey. Over years, Babak taught me everything that I will ever need for my career, always aiming to get the very best out of me. Babak always provided me with an excellent working environment at Parallel Systems Architecture Laboratory (PARSA), École Polytechnique Fédérale de Lausanne. Additionally, Babak introduced Sushi to me and other PARSA fellows during a memorable outing at SushiAnn, New York. Thank you for everything!

I would like to thank Edouard Bugnion, Phillip B. Gibbons and Stefanos Kaxiras for serving on my thesis committee, and for improving my thesis with their insightful comments. Additionally, I would like to thank Matthias Grossglauser for serving as the jury president for my thesis exam.

I would like to thank Boris Grot and Evangelos Vlachos for our excellent collaboration. Working with them was a great experience that fueled my graduate studies, and helped me to grow academically. Apart from being great colleagues, Boris and Evangelos have also been good friends. Thank you both!

Special thanks go to Onur Kocberber for our great collaboration during our junior years at PARSA. Additionally, I would like to thank Onur for his friendship and for accompanying me to HPCA 2014, in Orlando.

I am grateful for having great colleagues at EPFL. I will remember Stavros Volos for being a good friend and for providing excellent feedback on my research and various drafts over years. I would like to thank Djordje Jevdjic and Cansu Kaynak for being good friends and excellent proof-

readers for my papers. I would also like to thank the rest of my friends and colleagues at PARSA group for providing invaluable feedback on my work, and for attending my practise talks: Mike Ferdman, Al Mutaz Adileh, Effi Georgala, Javier Picorel Obando, Alexandros Daglis and Pejman Lotfi-Kamran. Additionally, I would like to thank Rodolphe Buret for providing technical support, Stéphanie Baillargues and Valérie Locca for providing administrative advice, and Ousmane Diallo for his advice on job finding. I am also grateful to Manos Athanassoulis and Ioannis Alagiannis; during these years, Manos, Ioannis and I exchanged useful information related to swiss and EPFL bureaucracy.

During my undergraduate studies at Technical University of Crete, Greece, I had the opportunity to work with excellent researchers, and take classes with inspiring teachers. Specifically, I would like to thank Dionisios Pnevmatikatos, who supervised my undergraduate and master theses, Apostolos Dollas, and Kostas Kalaitzakis for providing me with a strong background, and for encouraging me to pursue a Ph.D. degree.

I am lucky to have close friends that have shared good and bad times with me. Many thanks go to my childhood friends Eleftheria Kili, Stelina Tsafaraki and Theodosia Fiotodimitraki, my friends from my undergraduate studies Angelos Arelakis, Giorgos Smaragdos and Panos Ainalis, and my recent friends Yiannis Sotiropoulos, Kostas Matakos, Kostas Sougias and Margarita Maouni.

I am deeply and forever indebted to my parents, Giorgos Fytrakis and Katerina Antoniou-Fytraki, for their love, support and encouragement throughout my entire life, and to my sister, Lia Fytraki, who always makes my life brighter and colorful.

I would like to dedicate this thesis to Yiannis Papadakis for this love, support and patience, and for our motorcycle rides throughout all these years.

Finally, I would like to express my appreciation to Jean-Eudes Ranvier for helping me with the French version of my thesis abstract. I gratefully acknowledge the funding support from Swiss National Science Foundation, Project No. 200021\_140551/1.

vii .

### **Abstract**

Software robustness is an ever-challenging problem in the face of today's evolving software and hardware that has undergone recent shifts. The increase in computational power has been accompanied by an unprecedented increase in the occurrence of software bugs and vulnerabilities that not only leads to breaches in privacy or financial loss, but may eventually cause catastrophic failures.

Instruction-grain program monitoring is a powerful technique to detect and mitigate bugs. Instruction-grain monitors track the execution of individual instructions to identify anomalous behavior. Tracking instruction execution at speed requires custom hardware which can only detect a particular bug or class of bugs. Firmware allows for flexibility to detect a variety of bugs but comes with a 10x slowdown in execution, while without hardware support the slowdown can be as high as 100x. Although general monitoring tools with low runtime overhead would significantly assist the debugging process, none of the techniques available today provide a flexible solution with affordable performance degradation.

This thesis proposes architectural support for a flexible at-speed Filtering Accelerator for Decoupled Event processing, or FADE. FADE is based on the observation that much of that instruction-grain monitoring overhead can be virtually eliminated because either bugs are rare (e.g., most application accesses go to an allocated memory region), or the applications have an expected behavior that requires no monitoring action (e.g., applications mostly operate on non-pointer data).

Based on these observations, the monitoring activity in response to common application activity can be *filtered* thereby significantly reducing the runtime overhead of software monitors for a variety of memory, security, and concurrency bugs. To allow for flexibility, the unfiltered application activity is delegated to software for further processing. Unlike prior work on architectural support for monitoring that necessitated a dedicated core to run the monitors software, this thesis shows that when filtering most of the monitor's activity with complexity-effective hardware structures, there is no need for a duplicate set of hardware resources. As parallel software constitutes a large fraction of modern software, the thesis develops hardware extensions to support the monitoring of single- and multi-threaded applications alike.

**Keywords:** software robustness, application monitoring, support for single- and multithreaded applications, architectural extensions, filtering accelerator, software bugs, debugging. ix .

### Résumé

La robustesse du logiciel est un problème difficile due à la constante évolution des logiciels et du matériel. L'augmentation de la puissance de calcul a été accompagnée par une augmentation sans précédent du nombre de bugs logiciels et de failles qui non seulement conduisent à des violations de vie privée ou des pertes financières, mais peuvent également provoquer des défaillances catastrophiques.

Le suivi des programmes par évaluation des instructions est une technique prometteuse permettant de détecter et atténuer les bugs. Le suivit des programmes permet de suivre l'exécution des instructions individuelles afin d'identifier un comportement anormal. Effectuer ce suivi sans altérer la vitesse d'exécution des programmes nécessite un matériel sur mesure qui ne peut détecter qu'un bug ou une catégorie de bugs. Les approches basées sur des hardwares généralistes permettent de détecter une plus grande variété de bugs, mais sont accompagnés de ralentissement de l'ordre d'un facteur 10. Cependant, sans support matériel, le ralentissement peut être de l'ordre d'un facteur 100. Bien que des outils de suivi impactant faiblement le temps d'exécution aideraient considérablement le processus de débogage, aucune des techniques disponibles aujourd'hui à un prix abordable ne fournit une solution flexible sans dégrader les performances.

Cette thèse propose une extension architecturale pour un accélérateur de filtrage découplant le traitement des évènements/instructions (FADE : Filtering Accelerator for Decoupled Event Processing). FADE est basé sur l'observation que beaucoup de ralentissements liés au suivi des programmes peuvent être évités pour deux raisons : 1) Les bugs logiciels sont rares (ex. la plupart des accès mémoires se font dans des zones allouées préalablement. Les dépassements de mémoires

sont donc relativement rares.), 2) Les programmes ont des comportements ne requérant qu'un suivi basique (ex. Les programmes travaillent rarement avec des pointeurs).

Sur la base de ces observations, le suivi des programmes déclenché par la plupart des évènements générés par l'application peuvent être filtrés afin de réduire de manière significative le ralentissement due au logiciel de suivi pour plusieurs types de bugs (bug de mémoire, bug de sécurité, bug de concurrence). Dans un but de flexibilité, les évènements non filtrés sont délégués à un logiciel. Contrairement aux approches précédentes d'extension architecturales permettant le suivie des programmes qui accaparaient un cœur complet, cette thèse montre que le filtrage de la plupart des évènements grâce à un hardware efficace, permet de s'affranchir du cœur dédié. Etant donné que les applications multithread constituent une part importante des applications modernes, cette thèse propose une extension matérielle pour supporter le suivit programmes mono et multithread.

**Mots-clefs**: robustesse du logiciel, suivi des programmes mono et multithread, extension architecturale, accélérateur de filtrage, bugs logiciels, débogage.

## **Table of Contents**

| Acknowled    | gements                                            | iii |

|--------------|----------------------------------------------------|-----|

| Abstract     |                                                    | vii |

| Résumé       |                                                    | ix  |

| Table of Co  | ontents                                            | xi  |

| List of Figu | ıres                                               | XV  |

| List of Tab  | les                                                | xix |

| Chapter 1    | Introduction                                       | 1   |

| 1.1          | The Multi-Core Era                                 | 2   |

| 1.2          | How to Mitigate Bugs                               | 4   |

| 1.3          | Prior Work on Dynamic Instruction-Grain Monitoring | 6   |

| 1.4          | Thesis Contributions                               | 8   |

| Chapter 2    | Background                                         | 11  |

| 2.1          | Instruction-Grain Monitoring                       | 11  |

| 2.2          | Metadata Organization                              | 13  |

| 2.3          | Studied Monitors                                   | 14  |

| Chapter 3    | Why Filter?                                        | 19  |

| 3.1          | Generalized Monitor Functionality                  | 19  |

| 3.2          | Filtering Common Application Events                | 22  |

| 3.3       | Implications of Filtering on Monitoring Systems' Design | 24 |

|-----------|---------------------------------------------------------|----|

|           | 3.3.1 Fast Monitoring                                   | 24 |

|           | 3.3.2 Flexible Monitoring                               |    |

|           | 3.3.3 Resource-Efficient Monitoring                     | 25 |

| 3.4       | Summary                                                 | 28 |

| Chapter 4 | Event Management                                        | 29 |

| 4.1       | Motivation                                              | 29 |

| 4.2       | A Quantitative Analysis                                 | 31 |

|           | 4.2.1 System Description                                | 31 |

|           | 4.2.2 Event Producer                                    | 32 |

|           | 4.2.3 Event Queue                                       | 34 |

|           | 4.2.4 Filtering Accelerator                             | 36 |

|           | 4.2.5 Unfiltered Event Queue and Consumer               | 37 |

| 4.3       | Summary                                                 | 38 |

| Chapter 5 | FADE                                                    | 41 |

| 5.1       | Baseline Filtering Accelerator                          | 43 |

|           | 5.1.1 Filtering Unit                                    | 44 |

|           | 5.1.2 Stack-Update Unit                                 | 49 |

| 5.2       | Non-Blocking FADE                                       | 49 |

|           | 5.2.1 Observations                                      | 49 |

|           | 5.2.2 Extensions to the Baseline Pipeline               | 51 |

| 5.3       | Methodology                                             | 52 |

| 5.4       | Evaluation                                              | 55 |

|           | 5.4.1 FADE versus Unaccelerated System                  |    |

|           | 5.4.2 Performance for Different Core Types              |    |

|           | 5.4.3 Single-Core versus Two-Core System                |    |

|           | 5.4.4 Benefits of Non-Blocking Filtering                |    |

|           | 5.4.5 Area and Energy Efficiency                        |    |

| 5.5       | Summary                                                 | 61 |

|           |                                                         |    |

| Chapter 6 | Parallel FADE                       |                                                |    |  |

|-----------|-------------------------------------|------------------------------------------------|----|--|

| 6.1       | Backg                               | 64                                             |    |  |

| 6.2       | Baseline Parallel Monitoring System |                                                |    |  |

| 6.3       | Accel                               | erating Parallel Monitoring                    | 68 |  |

|           | 6.3.1                               | Parallel FADE                                  | 68 |  |

|           | 6.3.2                               | Comparison to Prior Work                       | 70 |  |

| 6.4       | Parall                              | el FADE's Design                               | 71 |  |

|           | 6.4.1                               | Dependence Recorder                            | 71 |  |

|           | 6.4.2                               | Dependence Checker & Progress Publisher++      | 71 |  |

|           | 6.4.3                               | Dependence Queue                               | 74 |  |

| 6.5       | Acces                               | sses to Shared Metadata                        | 75 |  |

|           | 6.5.1                               | Metadata Coherence                             | 75 |  |

|           | 6.5.2                               | Racing Metadata Accesses                       | 76 |  |

| 6.6       | Evalu                               | Evaluated Systems                              |    |  |

| 6.7       | Metho                               | Methodology                                    |    |  |

| 6.8       | Evaluation                          |                                                |    |  |

|           | 6.8.1                               | Monitoring Load                                | 80 |  |

|           | 6.8.2                               | Filtering Efficiency                           | 82 |  |

|           | 6.8.3                               | Parallel FADE versus Unaccelerated System      | 83 |  |

|           | 6.8.4                               | Dedicated Monitoring Core versus HW thread     | 86 |  |

|           | 6.8.5                               | Scalability Analysis                           | 87 |  |

|           | 6.8.6                               | Discussion                                     | 89 |  |

| 6.9       | Relax                               | ed Memory Models                               | 90 |  |

| 6.10      | Summary                             |                                                |    |  |

| Chapter 7 | Relat                               | ted Work                                       | 93 |  |

| 7.1       | Softw                               | are Monitoring Systems                         | 93 |  |

|           | 7.1.1                               | Dynamic Binary Instrumentation Approaches      | 93 |  |

|           | 7.1.2                               | Software Monitoring Tools for Sequential Bugs  | 94 |  |

|           | 7.1.3                               | Software Monitoring Tools for Concurrency Bugs | 96 |  |

| 7.2       | Hardv                               | vare-Based Monitoring Systems                  | 98 |  |

| Curriculum Vitae |                                       |                                                              |     |  |

|------------------|---------------------------------------|--------------------------------------------------------------|-----|--|

| Bibliograph      | ıy                                    |                                                              | 113 |  |

| 8.1              | 8.1 Future Directions                 |                                                              |     |  |

| Chapter 8        | Conc                                  | lusions                                                      | 109 |  |

|                  | 7.3.3                                 | Deterministic Record & Replay                                | 108 |  |

|                  | 7.3.2                                 | Hardware Approaches                                          | 106 |  |

|                  | 7.3.1                                 | Software Approaches                                          | 106 |  |

| 7.3              | 7.3 Support for Parallel Applications |                                                              |     |  |

|                  | 7.2.6                                 | Hardware-Assisted Multi-Cores                                | 104 |  |

|                  | 7.2.5                                 | Systems Implementing the Monitor on a Different HW Substrate | 103 |  |

|                  | 7.2.4                                 | Watchpoint-Based Monitoring Systems                          | 103 |  |

|                  | 7.2.3                                 | Monitoring Systems Using Hardware of Contemporary Processors | 101 |  |

|                  | 7.2.2                                 | Specialized Hardware-Based Monitoring Systems                | 100 |  |

|                  | 7.2.1                                 | Hardware Support for Dynamic Information Flow Tracking       | 98  |  |

## List of Figures

| FIGURE 1:  | The first computer bug. Source: U.S. Naval Historical Center Online Library     |

|------------|---------------------------------------------------------------------------------|

|            | Photograph. 2                                                                   |

| FIGURE 2:  | End of Dennard scaling in 2004. Note that the number of cores per chip is one   |

|            | until 2004. Source: NRC                                                         |

| FIGURE 3:  | A simple memory checker                                                         |

| FIGURE 4:  | A simple instruction-grain monitor                                              |

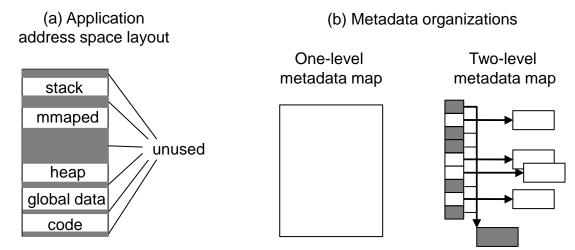

| FIGURE 5:  | (a) Application address space layout. (b) Metadata organized in an one-level    |

|            | metadata map (on the left), and a two-level metadata map (on the right). The    |

|            | figure has been initially presented in the LBA paper [23]                       |

| FIGURE 6:  | (a) A SW handler for a load instruction event. (b) A SW handler for a stack-    |

|            | update event                                                                    |

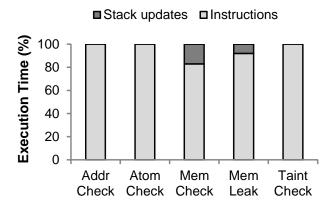

| FIGURE 7:  | The sources of instruction-grain monitoring slowdown for instruction and stack- |

|            | update events                                                                   |

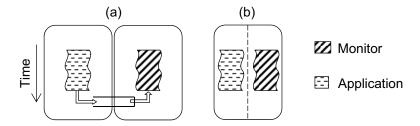

| FIGURE 8:  | (a) A two-core monitoring system, and (b) a single-core monitoring system with  |

|            | filtering support                                                               |

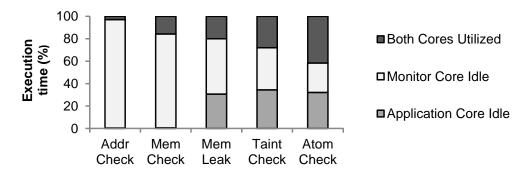

| FIGURE 9:  | The core utilization in the two-core monitoring system                          |

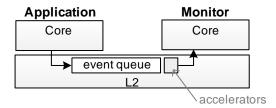

| FIGURE 10: | Log-Based Architectures (LBA) overview. 30                                      |

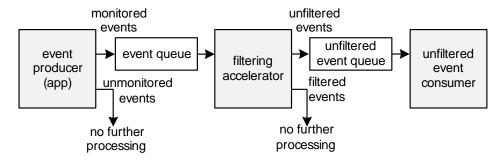

| FIGURE 11: | A monitoring system with filtering support                                      |

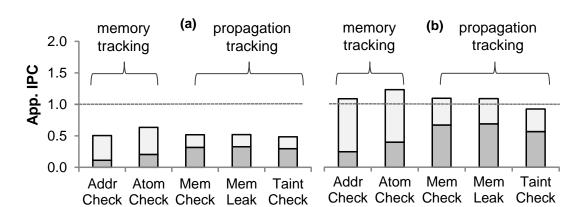

| FIGURE 12: | Breakdown of application IPC to monitored and unmonitored, averaged across      |

|            | benchmarks for each monitor (a) for an in-order core, and (b) for a 4-way OoO   |

|            | core                                                                            |

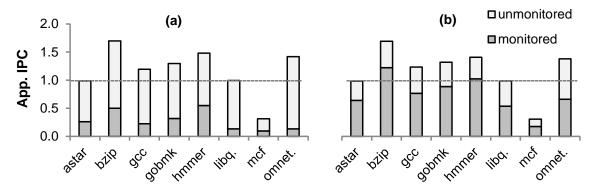

| FIGURE 13: | Breakdown of application IPC to monitored and unmonitored per-benchmark for     |

|            | (a) AddrCheck and (b) MemLeak. 34                                               |

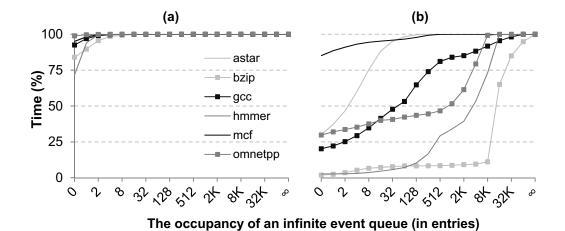

| FIGURE 14: | The occupancy of an infinite event queue for (a) AddrCheck and (b) MemLeak                                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------|

|            |                                                                                                                                 |

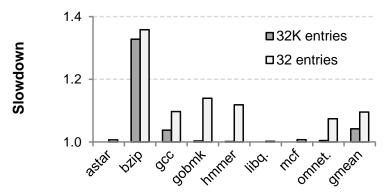

| FIGURE 15: | The effect of event queue size on performance for MemLeak                                                                       |

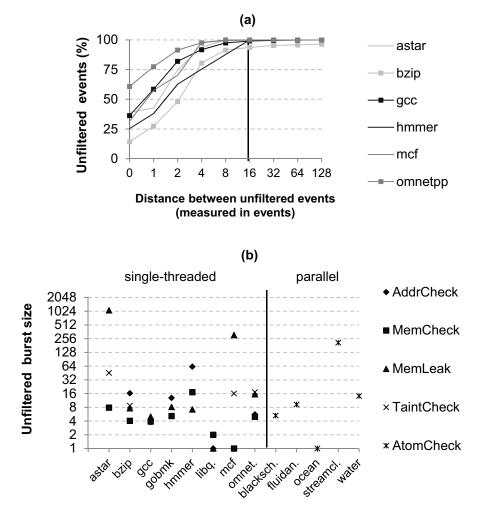

| FIGURE 16: | (a) Cumulative distribution of distances between unfiltered events for MemLeak.                                                 |

|            | (b) Unfiltered burst size for all monitors and benchmarks                                                                       |

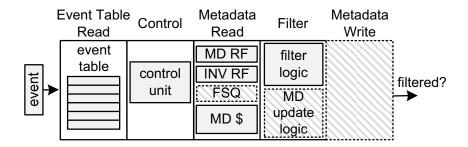

| FIGURE 17: | Filtering Unit pipeline. Striped structures show pipeline extensions for Non-                                                   |

|            | Blocking Filtering. 44                                                                                                          |

| FIGURE 18: | Event table entries. The size of an event table entry is 96 bits                                                                |

| FIGURE 19: | Event entry format                                                                                                              |

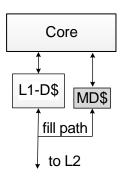

| FIGURE 20: | The MD cache in the cache hierarchy. 46                                                                                         |

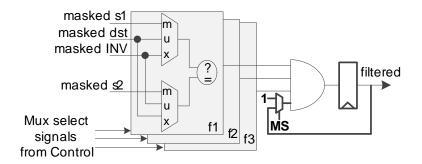

| FIGURE 21: | The internals of filter logic. 47                                                                                               |

| FIGURE 22: | Evaluated systems. 52                                                                                                           |

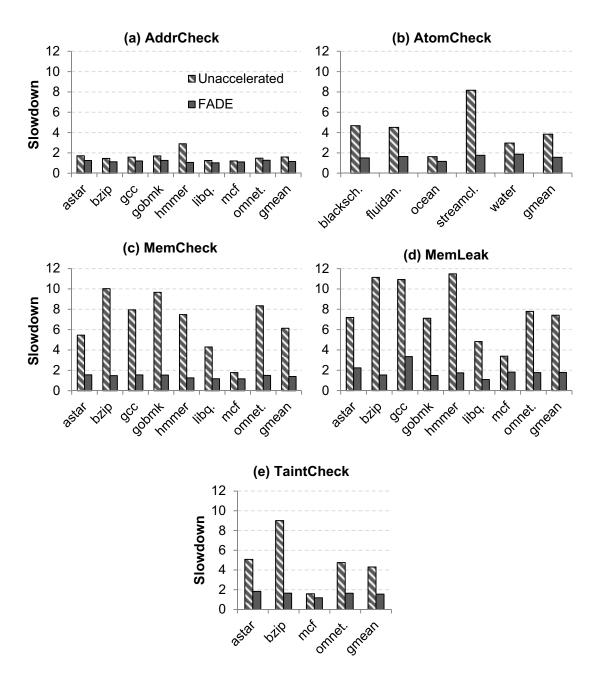

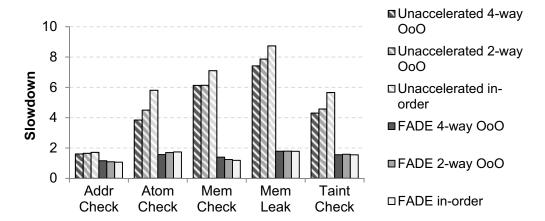

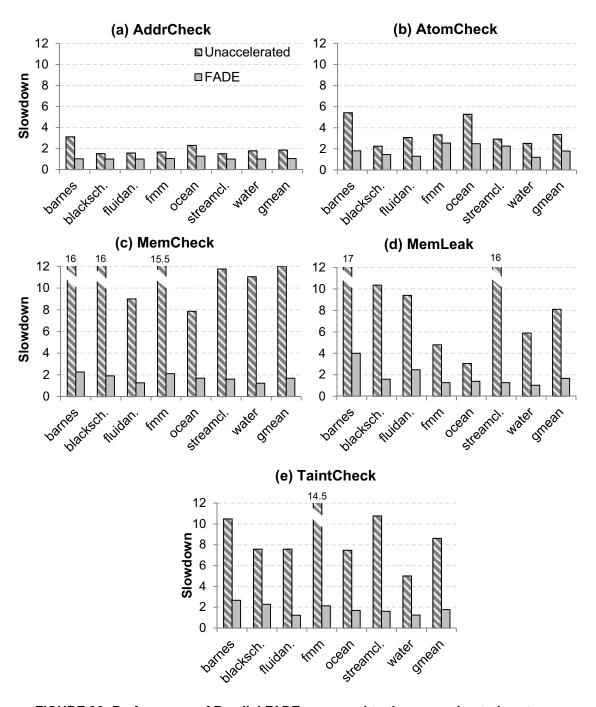

| FIGURE 23: | Performance of FADE compared to the unaccelerated system                                                                        |

| FIGURE 24: | Performance of the single-core monitoring system for different core types 58                                                    |

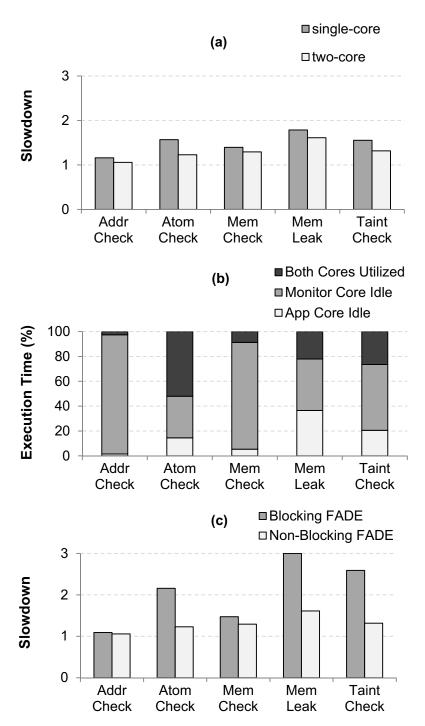

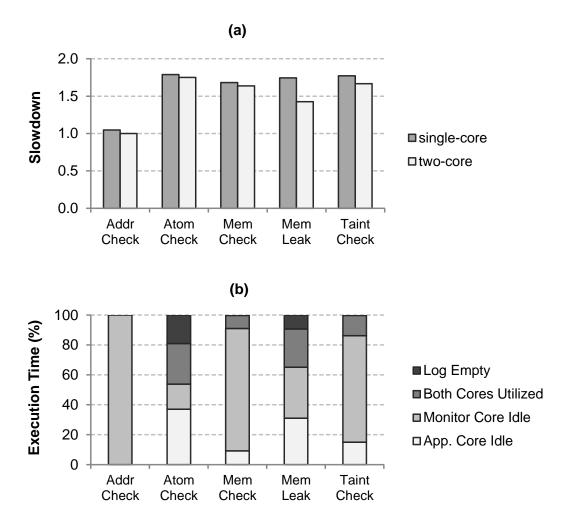

| FIGURE 25: | (a) Performance of the single- versus two-core monitoring systems with FADE.                                                    |

|            | (b) Core utilization in the two-core system. (c) Performance benefits of Non-                                                   |

|            | Blocking Filtering. 60                                                                                                          |

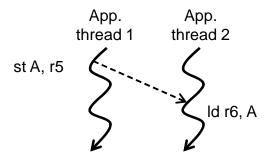

| FIGURE 26: | Event order under parallel monitoring. To maintain correctness, the monitoring                                                  |

|            | process has to follow the commit and dependence order of the application                                                        |

|            | instructions                                                                                                                    |

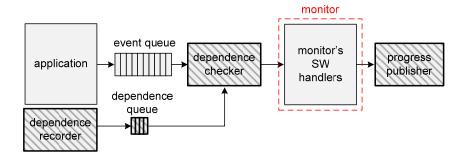

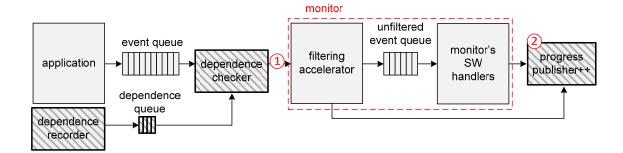

| FIGURE 27: | The baseline monitoring system. The striped structures allow the monitoring                                                     |

|            | process to follow the application dependence order                                                                              |

| FIGURE 28: | Numbered the two requirements to ensure correctness of the monitors execution                                                   |

|            | with Parallel FADE (including Non-Blocking Filtering support): (1) The events                                                   |

|            | are delivered to the filtering accelerator in commit and dependence order. (2) The event progress is advertised in commit order |

|            | event progress is advertised in commit order                                                                                    |

xvii .

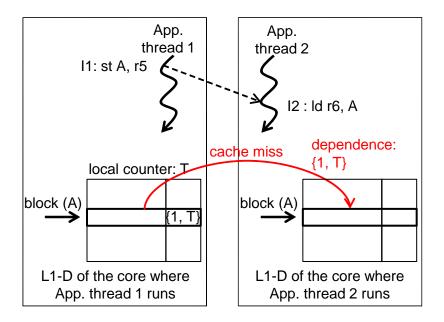

| FIGURE 29: | Leveraging coherence activity to infer inter-thread dependences                  |

|------------|----------------------------------------------------------------------------------|

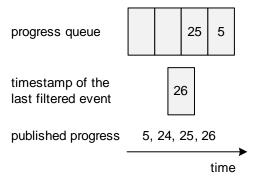

| FIGURE 30: | A snapshot of the progress queue and the timestamp of the last filtered event.   |

|            | along with published progress                                                    |

| FIGURE 31: | The event queue entries that carry dependences. The graph shows ranges (e.g.     |

|            | 6% means >3% and up to 6%)                                                       |

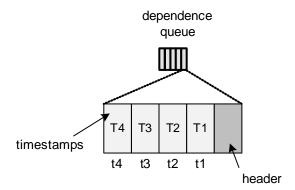

| FIGURE 32: | The dependence queue design for four monitored threads                           |

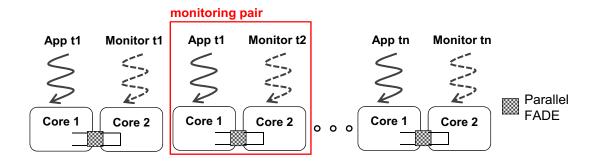

| FIGURE 33: | Evaluated System I: The monitor runs on a dedicated monitoring core              |

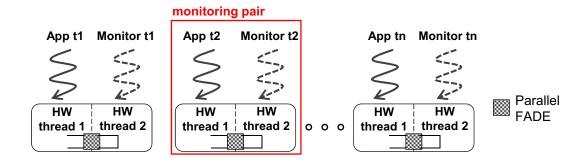

| FIGURE 34: | Evaluated System II: The monitor runs on a dedicated HW thread                   |

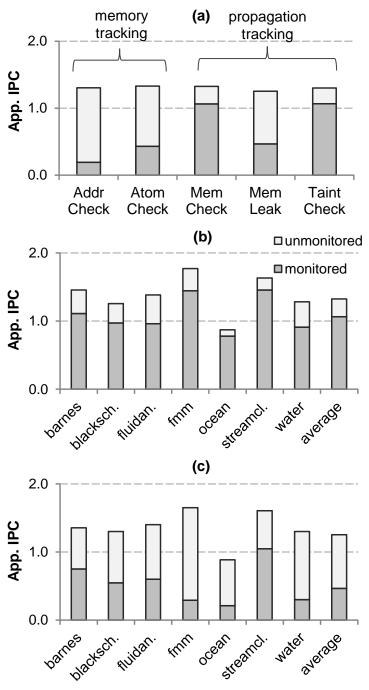

| FIGURE 35: | Parallel FADE: Breakdown of application IPC to monitored and unmonitored: (a)    |

|            | averaged across benchmarks for each monitor, and per-benchmark for (b)           |

|            | TaintCheck and (c) MemLeak. 81                                                   |

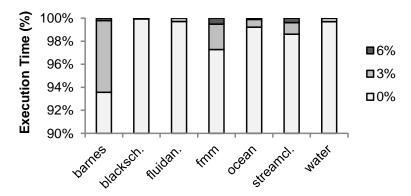

| FIGURE 36: | Performance of Parallel FADE compared to the unaccelerated system                |

| FIGURE 37: | (a) Performance of a dedicated monitoring core versus a dedicated monitoring     |

|            | HW thread. (b) Core utilization in the two-core system                           |

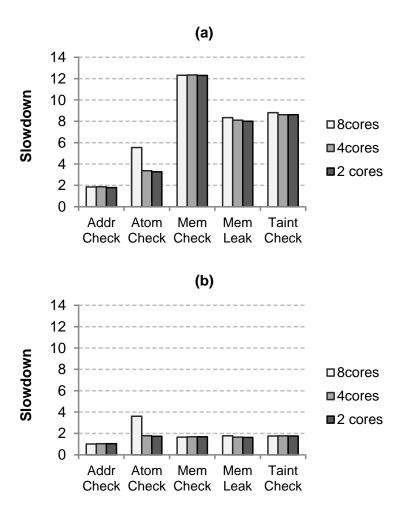

| FIGURE 38: | Performance of (a) the unaccelerated system and (b) Parallel FADE for 2, 4 and 8 |

|            | monitoring pairs running on 2, 4 and 8 multi-threaded cores, respectively 88     |

| FIGURE 39: | The function that calculates the Euclidean distance in streamcluster benchmark   |

|            | 89                                                                               |

xix

## List of Tables

| Table 1: | Eight cases of access interleavings. All accesses are to the same shared variable |  |  |  |

|----------|-----------------------------------------------------------------------------------|--|--|--|

|          | Subscript r denotes remote interleaving access; superscript i and p denotes or    |  |  |  |

|          | access and its preceding access from the same thread. The table has been          |  |  |  |

|          | presented in the AVIO paper [65]                                                  |  |  |  |

| Table 2: | Filtered instruction events.                                                      |  |  |  |

| Table 3: | Monitors functionality and the associated clean checks and redundant updates.     |  |  |  |

|          | stands for metadata of memory and registers. The events are based on the SPAR     |  |  |  |

|          | ISA2                                                                              |  |  |  |

| Table 4: | Simulation setup.                                                                 |  |  |  |

| Table 5: | System setup.                                                                     |  |  |  |

| Table 6: | Filtering efficiency in Parallel FADE.                                            |  |  |  |

### Chapter 1

### Introduction

Fabrication technology advancements have led to an unprecedented increase in computational power enabling the deployment of a wide range of services that have substantially improved the quality of life. For over four decades, we have seen an exponential proliferation of digital computing platforms penetrating all aspects of a modern life including government, commerce, entertainment, health and social infrastructure. However, the growth of computational power is accompanied by high software complexity and concerns about software robustness [26].

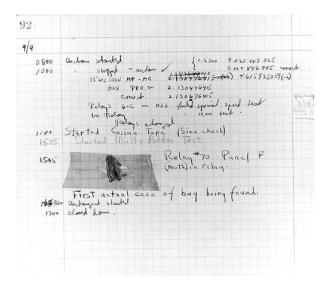

Bugs are prevalent in modern software, not only decreasing productivity, but also introducing vulnerabilities that can lead to security and privacy breaches and catastrophic system failures [104]. The term *bug* originates back in 1946, when an actual moth was found trapped in the Mark II Aiken Relay Calculator while the machine was being tested at Harvard University, on September 9th, 1945. The operators tapped the moth to the computer log and wrote the comment: "First actual case of bug being found" (Figure 1) [78].

Over time, bugs have had severe consequences ranging from financial loss to loss of human lives. The list of the infamous bugs is long including (1) Therac-25 radiation therapy machine, which was directly responsible for patients deaths, in the 1980s; (2) Ariane 5 rocket, an \$1 billion prototype of the European Space Agency, which has been destroyed in less than one minute after launch, in 1996; (3) Northeast Blackout, which has been associated with an immense financial damage of 6\$ billion, in 2003; (4) Knight Capital's computer bug, which cost over 440\$ million, in 2012.

FIGURE 1: The first computer bug. Source: U.S. Naval Historical Center Online Library Photograph.

Unfortunately, debugging (i.e., the art of diagnosing the source of a bug and fixing it) is a difficult and time-consuming task. In the late 1940s, Maurice Wilkes, computer pioneer, described his realization that much of the rest of his life would be spent finding mistakes in his own programs. To ease the debugging process and to assist the developers, academia and industry have proposed a large body of debugging techniques.

#### 1.1 The Multi-Core Era

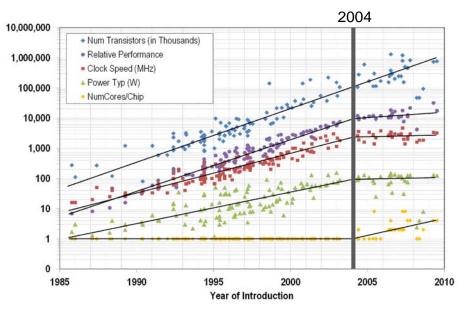

For the past three decades Dennard scaling (1974) [34] along with Moore's law (1965) [72] have driven the development of computer systems. Moore's law provided the processor designers with a doubling number of transistors per unit area every 18 months. Most importantly, Dennard's scaling enabled designers to improve performance by increasing the frequency of a single core per chip. Consequently, newer processor generations allowed single-threaded applications to run faster, meeting the demand for additional computational power.

FIGURE 2: End of Dennard scaling in 2004. Note that the number of cores per chip is one until 2004. Source: NRC.

To meet the heat dissipation and cooling constraints, while improving the aggregate chip performance, computer system designers turned to multicore architectures. As shown in Figure 2, the number of cores per chip has been increasing as of 2004. Today, multicores have invaded all segments of the processors market including servers, desktops, even mobile phones.

Multicore chips can be an attractive solution given that software can scale accordingly. Unfortunately, the development of parallel software has not been commensurate with the proliferation of multicore chips. Both, writing parallel code from scratch and parallelizing a piece of serial code are notoriously difficult tasks that require substantial manual effort. Although the efficient (ideally automated) development of scalable parallel code remains an open research problem, providing robust and practical debugging tools is determinant towards this direction.

#### 1.2 How to Mitigate Bugs

A number of complementary techniques have been proposed to assist developers in finding software bugs. These can be broadly categorized into *static* tools, *symbolic* tools, *post-mortem* tools and *dynamic* tools. Static tools (e.g., RacerX [38], CP-Miner [61], MUVI [63], RELAY [113]) aim at identifying bugs before the application executes. Symbolic tools (e.g., Cloud9 [15], KLEE [18], S2E [25], Bitblaze [101], ESD [123]) leverage symbolic values, instead of the actual values, so as to analyze a program and enumerate possible execution paths. Post-mortem tools (e.g., LXR [4], BugNet [77], FDR [118], RTR [120]) attempt to identify what went wrong after the application crashes. Dynamic tools (e.g., Valgrind [81], Purify [51], Eraser [93], CCured [28], PIN [69]) monitor the application as it executes so as to identify what went wrong during a specific run. In this thesis, we study dynamic techniques that observe programs behavior at runtime and we focus on application written in unmanaged languages (i.e., C, C++), while managed languages (e.g., C#) are out of our scope.

Dynamic tools with the ability to monitor programs at the granularity of individual instructions<sup>1</sup> possess a unique advantage stemming from their access to detailed runtime events, such as memory references, control flow and runtime inputs. Instruction-grain monitoring tools allow for the development of a wide range of bug-finding tools, and can effectively handle anomalous application behavior ranging from memory bugs, such as memory leaks [71], to concurrency bugs, such as atomicity violations [65]. Hereafter, we refer to these tools as *monitors*.

The monitors rely on *metadata*, which is per memory location and/or register information related to the bug-finding task. The monitor performs metadata checks to ensure that certain

<sup>1.</sup> Although dynamic tools commonly monitor fine-grain events (i.e., instructions), certain tools may monitor coarse-grain events. For instance, Dimmunix [55] that allows programs to develop resistance against already observed dead-locks, takes a monitoring action upon less frequent events, such as locks acquisition and release.

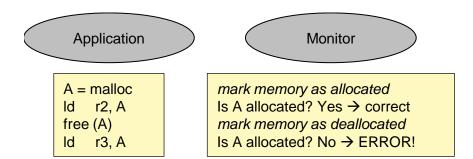

FIGURE 3: A simple memory checker.

invariants hold, for each application *event of interest*. In Chapter 3, we study a diverse set of monitors (detailed in Section 2.3), and we show that commonly monitors take actions in response to three categories of application events: (1) instruction events (e.g., add, load), (2) stack-update events (i.e., events that modify the stack pointer, such as function calls and returns), and (3) other events (e.g., memory allocation routines). For instance, a monitor that checks whether application accesses go to an allocated memory region, as the one shown in Figure 3, keeps information about the allocation status of each memory location when the application executes malloc-like and free-like routines. As shown in the figure, when the application generates a memory instruction (i.e., load or store), the monitor obtains and checks the status of the associated memory location. In general, monitoring belongs to *tagged memory* approaches, which rely on metadata to infer meta-information about applications. Other tagged-memory use cases include but are not limited to security [59], reliability [100], performance bugs [52], garbage collection [53], and transactional memory [20].

Without loss of generality, we consider two design points: *serial monitoring* and *parallel monitoring*. Under serial monitoring, a single-threaded monitor observes the behavior of a single-threaded application. Under parallel monitoring, the application and the monitor are multithreaded processes running on a CMP. Each monitoring thread is associated with an application thread.

Parallel monitoring entails more challenges compared to serial monitoring due to its inherent concurrency [112], but also allows for the development of a much broader class of monitors, such as data race [41, 93] and atomicity violation [40, 65] detectors. Under serial monitoring, the only requirement to guarantee correctness is to process application's activity in program order, which is trivially satisfied by processing the application's dynamic instructions in commit order. However, under parallel monitoring, this task is complicated because the monitoring threads have to consider the relative order of concurrent application events. An additional requirement for parallel monitoring is to ensure synchronization and atomicity for monitor's accesses at low cost. To allow for wide adoption, a monitoring approach should support both serial and parallel monitoring.

#### 1.3 Prior Work on Dynamic Instruction-Grain Monitoring

A number of projects have targeted effective instruction-grain monitoring. Here, we briefly summarize the main attributes of software-only and hardware-assisted schemes; a comprehensive discussion is provided in Chapter 7.

Software-only monitoring frameworks rely on Dynamic Binary Instrumentation (DBI) [79] to implement the monitoring functionality dynamically. Specifically, DBI (discussed in more detail in Section 7.1) rewrites the original application code and instruments it with the monitoring code. These frameworks (e.g., Valgrind [81], PIN [69], DynamoRIO [13], DTrace [19]) enable the development of flexible, programmable, and accurate monitoring tools to detect memory access violations [51], atomicity violations [40, 65], etc. However, this flexibility comes at a steep performance penalty of 10-100x [81], since for common application events, a software handler is dispatched to check and/or update metadata. The overhead comes from (1) the instrumentation (i.e., saving and restoring registers for the application and the monitor), (2) the resource sharing between the application and the monitor, and (3) the execution of the monitoring handlers [24].

Algorithm-specific optimizations that try to reduce the performance overhead, still incur substantial slowdown (e.g., 8x for a race detector [41]).

To mitigate the performance bottleneck, researchers have investigated *hardware-assisted* solutions. *General hardware-assisted* schemes [24, 96, 112] provide hardware support for dispatching software handlers, thus eliminating the instrumentation overhead, but do not help in mitigating the handler execution time, resulting in up to 10x slowdown versus unmonitored code [23, 24]. An alternative general hardware-assisted scheme (to be studied in the future) is one that combines Dynamic Binary Translation (DBT)<sup>2</sup> [16, 8] with hardware support. In contrast to DBI, which is a heavy-weighted process, DBT translates the original binary through a "thin" indirection layer, but without the instrumentation overhead, thus resulting in marginal performance degradation. As a result, DBT could be used along with hardware support to lower the monitoring slowdown while maintaining flexibility.

A number of proposals aimed to bring down the performance cost through *specialized hard-ware* targeted at specific monitors (e.g., [35, 36, 46]). To avoid the shortcomings of monitor-specific tools, prior work proposed *hardware-based reconfigurable* tools [33, 57]. Although these tools offer flexibility, their wide adoption is limited because they are programmed in low-level hardware languages that escape the comfort zone of most programmers.

Our goal is to provide a general hardware-assisted monitoring system that combines *flexibility* and *low slowdown*, the positive attributes of prior work, with *resource efficiency*. Specifically, we would like to offer flexibility similar to software-only schemes [13, 19, 69, 81] and low slowdown similar to systems relying on specialized hardware [32, 35, 36, 46, 108], while at the same time reducing the amount of resources (i.e., a separate core [22, 32, 96]) dedicated to the monitoring task.

<sup>2.</sup> Popular dynamic binary translators include VMware binary translator [16], which supports x86-to-x86 binary translation, and QEMU [8], which supports cross-platform binary translation.

#### 1.4 Thesis Contributions

This thesis provides a practical and general monitoring system for both single- and multithreaded applications. The statement of the thesis reads as follows:

#### **Thesis Statement**

Identifying and filtering common monitoring activity with simple monitor-agnostic hard-ware enables the design of fast, flexible and resource-efficient monitoring systems for single- and multi-threaded applications.

By studying a set of monitors and through cycle-accurate simulations we demonstrate that:

• Instruction and stack-update events are the main contributors to the monitoring slowdown. While instructions dominate the monitor's execution profile, stack updates account for up to 17% of the execution time, thus representing an attractive acceleration target. Instruction events require fine-grained accesses to monitor's metadata, most of which can be filtered through (1) hardware-executed checks of metadata state against an invariant, and (2) detection and elimination of redundant updates that leave the metadata state unmodified. Across a diverse set of monitors targeting from memory bugs to atomicity violations, the filtering efficiency for instruction events is 84-99%. Stack-update events perform bulk metadata initialization in response to function calls and returns and can be efficiently handled with a simple state machine in hardware. Although the thesis focuses on SPARC ISA, our prior study (BugSifter [43]) shows that our observations also hold for x86 ISA.

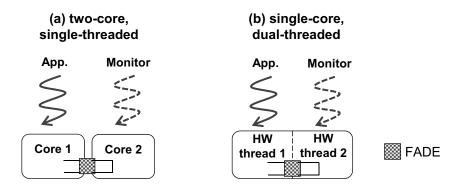

- While 84-99% of the monitored events can be filtered in hardware, the rest of the events are delegated to software thus allowing for full flexibility and generality. Unlike prior work that dedicated a whole core to the monitoring task, we show that a dual-threaded core provides sufficient resources for the application and the monitor. In doing so, we show that 59-96% of the time one of the two cores is idle in a two-core monitoring system with filtering support.

- By studying a broad range of bug-finding functionality and applications, we make the following observations: (1) The monitoring load rarely exceeds one event per cycle even with an aggressive OoO core producing events. (2) Both filterable and unfilterable events arrive in bursts that must be buffered to reduce stalls due to backpressure. (3) Shallow queues of 16 to 32 events are sufficient for this purpose and allow for decoupling of the filtering accelerator from the core running the application.

- To maintain a high filtering rate, filtering has to happen concurrently with the processing of unfiltered events, a task that is complicated due to data dependencies between unfilterable and subsequent filterable events. To decouple filtering and the processing of the unfiltered events, we observe that there is only minimal state that is critical for deciding if a dependent event is filterable. We show that this state can be updated for unfilterable events directly in the accelerator with simple hardware extensions. We name our technique *Non-Blocking Filtering*.

- Building on our observations, listed above, we develop an architecture, along with full microarchitectural support, for a flexible at-speed Filtering Accelerator for Decoupled Event processing, or FADE. FADE is fully programmable and can support a broad range of monitoring tasks with high filtering coverage and low hardware overhead. FADE supports Non-Blocking Filtering that dynamically resolves dependencies between unfilterable events and subsequent events, eliminating data-dependent stalls and maximizing accelerator's performance. Using full-system cycle-accurate simulation, we show that FADE is highly efficient, filtering out 84-99% of

events that would otherwise be handled in software, thereby reducing the application slowdown to only 1.2-1.8x (versus 1.6-7.4x for unaccelerated execution). In the 40nm technology, an instance of FADE requires 0.12mm<sup>2</sup> of area and 273mW of power at peak per core.

- We present *Parallel FADE* a parallel monitoring accelerator that allows for the design of flexible, fast and resource-efficient parallel monitoring systems. Parallel FADE combines Non-Blocking Filtering, the state-of-the-art hardware filtering technique to accelerate monitoring, with the necessary hardware extensions to handle the inherent concurrency of parallel applications, overall reducing the design complexity over prior parallel monitoring accelerators.

- To showcase the applicability of FADE (including Non-Blocking Filtering support) in the context of parallel monitoring, we provide a formal proof and we perform an experimental study. Our study of a suite of diverse monitors and a number of multi-threaded benchmarks shows that Parallel FADE filters 81-99% of events that would otherwise be handled in software and reduces the slowdown to an average of only 1.1-1.8x (versus 1.9-11.5x for unaccelerated execution), thus making monitoring practical.

The rest of this thesis is organized as follows. In Chapter 2, we give background on instruction-grain monitoring and the debugging tools used in this study. In Chapter 3, we show why filtering enables the design of a fast, flexible and resource-efficient monitoring system. In Chapter 4, we study the event management in monitoring systems with filtering support. In Chapter 5, we introduce FADE's micro-architecture, along with Non-Blocking Filtering. In Chapter 6, we present Parallel FADE. Finally, we discuss related work in Chapter 7, and we conclude in Chapter 8.

The material in Chapter 4 and Chapter 5 was previously presented in the 20th IEEE International Symposium on High Performance Computer Architecture (HPCA 2014): "Sotiria Fytraki, Evangelos Vlachos, Onur Kocberber, Babak Falsafi and Boris Grot. *FADE: A Programmable Filtering Accelerator for Instruction-Grain Monitoring*".

## Chapter 2

## Background

#### 2.1 Instruction-Grain Monitoring

A number of tools have been proposed to assist developers in finding bugs. These can be grouped into five general categories: (1) static tools (e.g., RacerX [38], CP-Miner [61], MUVI [63], RELAY [113]), (2) post-mortem tools (e.g., LXR [4], BugNet [77], FDR [118], RTR [120]), (3) dynamic tools (e.g., Valgrind [81], Purify [51], CCured [28], PIN [69]), (4) symbolic tools (e.g., Cloud9 [15], KLEE [18], S2E [25], Bitblaze [101], ESD [123]), and (5) model checking tools (e.g., BLAST [9], CHESS [74], Java Pathfinder [110]). While these tool categories can be considered complementary, dynamic tools with the ability to monitor at the granularity of individual instructions possess a unique advantage stemming from their access to detailed runtime events, such as memory references and information flow. This capability affords a wide range of powerful bug-finding tools, generally referred to as *monitors*, that span the spectrum from frequently occurring memory bugs to hard-to-reproduce concurrency bugs. In addition to facilitating bug finding at development time, instruction-grain monitors may be useful in the field by enabling on-the-fly recovery from errors, reducing susceptibility to security exploits, and improving damage confinement.

In general, instruction-grain monitors work by maintaining certain *invariants* and checking that these invariants hold for each application *event of interest*. Invariants might specify that every accessed memory location has been allocated and initialized, or that the value used as a jump target is not suspicious. Monitors take actions in response to three categories<sup>3</sup> of application events:

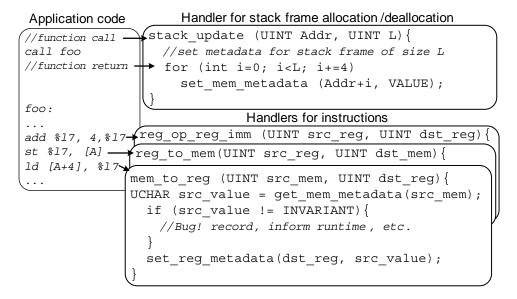

FIGURE 4: A simple instruction-grain monitor.

(1) instruction events (e.g., add, load), (2) stack-update events (i.e., events that modify the stack pointer, such as function calls and returns), and (3) other events (e.g., memory allocation routines). To assist analysis, monitors maintain bookkeeping information, or *metadata*, about application memory and registers. Depending on the event, the relevant metadata are checked against the invariant and/or updated with a new value.

A code snippet for a representative monitor, along with a slice of monitored application code, is shown in Figure 4. The monitor performs propagation-based analysis used by a number of bug-finding tools (e.g., MemCheck [81], which checks whether every referenced memory location has been initialized). In the example, each application instruction triggers a software handler associated with the monitor. For each of the instruction's source operands, the handler accesses and checks the metadata. If the metadata value differs from the invariant (e.g., a referenced memory location has not been allocated or initialized), an action is taken to inform the user and/or the run-

<sup>3.</sup> Although this thesis focuses on SPARC ISA, our prior study (BugSifter [43]) shows that these categorization also holds for x86 ISA.

FIGURE 5: (a) Application address space layout. (b) Metadata organized in an one-level metadata map (on the left), and a two-level metadata map (on the right). The figure has been initially presented in the LBA paper [23].

time. The handler also updates the metadata for destination operands based on the metadata state of the source operands.

#### 2.2 Metadata Organization

Prior monitoring (software and hardware) frameworks organize metadata either in an one-level metadata map [107, 108], as shown in Figure 5(b)-left, or in a two-level metadata map [22, 81], as shown in Figure 5(b)-right. The two metadata organizations are also discussed in the LBA paper [23].

The one-level design uses a contiguous memory region, which is allocated when the monitor is initialized. This design allows for simple metadata lookups, because the metadata can be obtained directly through a simple pointer arithmetic operation, given an application address. Although this design point simplifies metadata addressing, it allocates a significant amount of virtual memory for the metadata unnecessarily. The two-level design resembles page tables and requires an intermediate translation step before obtaining the metadata address given an applica-

tion address. However, this design only allocates the metadata being accessed by the monitor, thus being more efficient.

#### 2.3 Studied Monitors

We use a suite of five diverse monitors. These monitors effectively cover a broad range of memory, security, and concurrency bugs.

AddrCheck [81] checks whether every memory access is to an allocated memory region. AddrCheck monitors non-stack memory accesses. It maintains one bit of metadata per application byte to encode the two possible states: *allocated* or *unallocated*. The tool keeps track of the calls to allocation routines (e.g., malloc(), free()) and update the associated metadata. For instance, when processing a malloc (free), AddrCheck sets the metadata corresponding to the malloced (freed) memory to allocated (unallocated).

*MemCheck* [81] extends AddrCheck to detect the use of uninitialized values. MemCheck maintains two bits per application byte; one bit to encode the *accessibility* status of a memory location, similar to AddrCheck, and one bit to encode the *initialization* status of a memory location. These two bits encode three metadata states (i.e., *unallocated*, *uninitialized*, and *initialized*).

The accessibility bits are updated as in AddrCheck. The initialization bits are cleared after free function calls and they are set when a constant is written to a memory location. When processing an instruction, MemCheck propagates metadata values from the source operand(s) to its destination operand. The destination operand becomes uninitialized, if at least one of the source operands is uninitialized.

MemCheck performs metadata checks to ensure correctness. When loading an uninitialized value, MemCheck does not issue an error (e.g., copying a partially initialized structure). However,

MemCheck detects an error when an uninitialized value is used in critical ways — i.e., being dereferenced as a pointer, used in conditional tests, or passed into system calls.

TaintCheck [82] is a security monitoring tool that checks for overwrite-related security exploits (e.g., due to buffer overruns, format string vulnerabilities). It performs propagation tracking to monitor the use of spurious data throughout the program execution. Program input data, such as data from the network, are marked as suspect or *tainted*. TaintCheck intercepts the necessary library calls (e.g., read, write) so as to mark the associated metadata as tainted. An error is raised, if tainted data are used in critical ways, such as in jump target addresses, or system call arguments. Although TaintCheck has two metadata states (*untainted* and *tainted*), we use one byte of metadata per application word, in order to avoid sub-byte access cost for common four-byte application operations.

MemLeak [71] uses a reference counting algorithm to identify leaked heap objects (i.e., objects that are no more reachable through an application pointer). MemLeak maintains one metadata word per application word, which is a pointer to the context of the corresponding malloc and a null value otherwise. The context includes an allocation ID, the PC, and a reference counter. The allocation ID is a unique identifier assigned to an object at the time of allocation.

MemLeak performs propagation tracking of pointer values throughout program's execution. Loading a pointer to a register and using the pointer to generate a new address, propagates a pointer status to the destination register. When a pointer is written back to memory (on the heap) a new reference is created, thus increasing the corresponding reference counter. When this action overwrites the pointer to a another object, the reference counter of this object is decreased. Pointers stored in the stack do not require reference counting, as they get overwritten when the stack frame is popped. A memory leak is identified if an object's reference counter reaches the zero value, while the object is not deallocated.

Table 1: Eight cases of access interleavings. All accesses are to the same shared variable. Subscript r denotes remote interleaving access; superscript i and p denotes one access and its preceding access from the same thread. The table has been presented in the AVIO paper [65].

| # | Interl                                   | eaving             | Description                                | Serializability | Equivalent<br>Serial<br>Access                               | Problem                                                                                                               |

|---|------------------------------------------|--------------------|--------------------------------------------|-----------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0 | read <sup>p</sup><br>read <sup>i</sup>   | read <sub>r</sub>  | two reads<br>interleaved by a read         | YES             | read <sup>p</sup><br>read <sup>i</sup><br>read <sub>r</sub>  | N/A                                                                                                                   |

| 1 | write <sup>p</sup><br>read <sup>i</sup>  | read <sub>r</sub>  | read after write interleaved by a read     | YES             | write <sup>p</sup><br>read <sup>i</sup><br>read <sub>r</sub> | N/A                                                                                                                   |

| 2 | read <sup>p</sup><br>read <sup>i</sup>   | write <sub>r</sub> | two reads<br>interleaved by a write        | NO              | N/A                                                          | The interleaving write makes the two reads have different views of the same memory location                           |

| 3 | write <sup>p</sup><br>read <sup>i</sup>  | write <sub>r</sub> | read after write interleaved by a write    | NO              | N/A                                                          | The local read does not get the local result it expects                                                               |

| 4 | read <sup>p</sup><br>write <sup>i</sup>  | read <sub>r</sub>  | write after read<br>interleaved by a read  | YES             | read <sub>r</sub><br>read <sup>p</sup><br>write <sup>i</sup> | N/A                                                                                                                   |

| 5 | write <sup>p</sup><br>write <sup>i</sup> | read <sub>r</sub>  | two writes interleaved by a read           | NO              | N/A                                                          | Intermediate result assumed to be invisible to other threads is read by a remote thread                               |

| 6 | read <sup>p</sup><br>write <sup>i</sup>  | write <sub>r</sub> | write after read<br>interleaved by a write | NO              | N/A                                                          | The local write relies on a value<br>from the preceding local read that<br>is then overwritten by the remote<br>write |

| 7 | write <sup>p</sup><br>write <sup>i</sup> | write <sub>r</sub> | two writes interleaved by a write          | YES             | write <sup>p</sup> write <sub>r</sub><br>write <sup>i</sup>  | N/A                                                                                                                   |

AtomCheck [65] detects atomicity violations by checking access interleavings. For this purpose, AtomCheck keeps information for the last access by each thread to each memory location, maintaining one piece of metadata per application word. The main structures are (1) a global table to keep the status bit (Private/Shared) and the id of the thread that last referenced each memory location, and (2) local per-thread tables to keep the type (Read/Write) of the last access by each thread. Implementation-wise, AtomCheck encodes the thread status bit and the thread id in one byte.

For each memory access, AtomCheck performs one of the following actions: (1) If the status bit indicates that the data are thread-private, no further action is required. (2) If the status bit indicates that the data are shared, AtomCheck first checks the global table and the current thread id. If they match (i.e., the memory location was previously referenced by the same thread), which happens in the common case, a simple software handler is dispatched to update the metadata of the local table for the current thread with the type of the last access (Read/Write). (3) Otherwise, a complex handler is dispatched to check if there is a potential atomicity violation. In the last case, where there are consecutive accessed to a memory location by two different threads, there are eight possible interleavings, shown in Table 1. If the interleaving is unserializable, a potential atomicity violation is identified and the program counter of the instruction is reported.

In AtomCheck, the metadata are initially marked as uninitialized. Upon their first access, they are marked as thread-private. Any consequent access by a different thread, sets the metadata to the shared state.

# Chapter 3

# Why Filter?

In this Chapter, we motivate our design choices that lead to a fully generalized monitoring accelerator allowing for low runtime and resource overhead. First, we identify common high-level functionality inherent in a wide range of monitors, targeting memory, security and concurrency bugs. Next, we provide intuition on how filtering can eliminate much of the run-time overhead associated with commonly occurring monitoring activities. Finally, we discuss the implications of filtering on the design of monitoring systems.

# 3.1 Generalized Monitor Functionality

The existence of different bug types dictates that monitors should be specialized for each particular type of a bug. Moreover, for a given bug type, several bug-finding algorithms may exist that differ in their coverage guarantees, resource requirements, implementation complexity, etc. Despite the resulting diversity of bug-finding tools and algorithms, we find that virtually all monitors have functionally-similar characteristics at a high level. These can be summarized as follows, with Figure 6 serving as an illustrative example.

Simple checks and updates for instruction events: The bulk of monitoring activity in response to individual application instructions involves some combination of metadata accesses, metadata checks against an invariant, and metadata updates. As most instructions in ISAs of contemporary general-purpose processors operate on one or two source operands and update one destination operand, the per-instruction handlers typically manipulate three small pieces of metadata

#### Handler for a load instruction (e.g., Id [A+4], %I7)

(a)

```

mem_to_reg (UINT src_mem, UINT dst_reg) {

UCHAR src_value = get_mem_metadata(src_mem);

if (src_value != INVARIANT) {

//Bug! record, inform runtime, etc.

}

set_reg_metadata(dst_reg, src_value);

}

```

(b)

Handler for a stack frame allocation/deallocation

```

stack_update (UINT Addr, UINT L)

{

//set metadata for the stack frame

//the stack frame's size is L

for (int i=0; i<L; i+=4)

set_mem_metadata (Addr+i, VALUE);

}</pre>

```

FIGURE 6: (a) A SW handler for a load instruction event. (b) A SW handler for a stack-update event.

or less (for their source and destination operands), with each metadata item associated with a given application register or memory location. Figure 6(a) shows a representative software handler for a load instruction.

Bulk updates for stack-update events: Software engineering practices call for abstraction and encapsulation of functionality, leading to software with many short functions and frequent function invocations at execution time. When the stack pointer of the application is adjusted, a frame is allocated/deallocated on the application stack (upon a function call/return). We refer to both types of activity as *stack updates*. Stack updates must be shadowed by the monitor to properly track what memory has been allocated to an application. As a result, each function call and return event in the application triggers a handler in the monitor that sets a region of metadata memory to a known value (e.g., *allocated+uninitialized* upon a call, *unallocated* upon a return). Figure 6(b) shows a software handler for a stack update instruction.

FIGURE 7: The sources of instruction-grain monitoring slowdown for instruction and stack-update events.

Complex or uncommon functionality for other events: Occasionally, monitors invoke functionality that differs from the two cases above. This happens whenever the application performs a high-level event of interest (e.g., malloc or free), initializes the metadata, or when a bug is found.

Figure 7 breaks down the monitors' execution time into (1) simple metadata checks and updates for application instruction events, and (2) metadata bulk updates in response to applications' stack frame allocations and deallocations. In this graph, we do not show complex events as they account for less than 5% of the run time for all monitors. The five studied monitors, described in Section 2.3, cover a broad spectrum of bugs. The benchmarks along with our methodology<sup>4</sup> can be found in Section 5.3.

As the figure shows, monitoring of instructions dominates the execution profile; however, stack updates consume up to 17% of the execution time in two out of five monitors due to a large number of instructions (over 100, on average) committed by the stack update handlers iterating through a memory region.

<sup>4.</sup> The monitors run on the baseline Log-Based Architectures system [22], also shown in Figure 8(a).

Table 2: Filtered instruction events.

| AddrCheck | AtomCheck | MemCheck | MemLeak | TaintCheck |

|-----------|-----------|----------|---------|------------|

| 99.5%     | 85.5%     | 98.0%    | 87.0%   | 84.0%      |

## 3.2 Filtering Common Application Events

In this Section, we analyze the monitors behavior in response to the two common application events types: instructions and the stack updates. We show that the majority of the common application events can be filtered.

**Instruction events:** For instruction events, we make two observations: First, most of the time applications behave as expected and the metadata match the expected invariant (e.g., memory accesses reference memory that has been allocated and initialized). We refer to these events as *clean checks*. The associated handlers do not affect the outcome of the monitoring algorithm, as they just confirm that the application behaves as expected. Second, propagation event handlers that copy metadata values from source to destination operands commonly update the metadata with the same value, because metadata are stable (e.g., memory that has been initialized remains initialized while the actual value in application memory may change). We call these events *redundant updates*, as they do not affect the metadata state. As the instruction events that fall into either clean checks or redundant updates do not change the monitoring outcome and the monitor's state, they can be filtered.

Table 2 shows the percentage of instruction event handlers that fall into either the clean check or redundant update category. The benchmarks along with our methodology can be found in Section 5.3. For AddrCheck, almost all instruction events result in clean checks, because applications access allocated memory. For MemCheck the vast majority of instruction events (98%) are either clean checks or redundant updates as most application data are initialized. For MemLeak 87% of the events are clean checks because most of the applications data are not pointers. In con-

Table 3: Monitors functionality and the associated clean checks and redundant updates. M stands for metadata of memory and registers. The events are based on the SPARC ISA.

| Monitor functionality                                                                                                                                                                | Clean Checks/Redundant Updates                                                                                                                                    |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| AddrCheck                                                                                                                                                                            |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| The metadata values are checked to detect unallocated memory accesses.                                                                                                               | Example: ld %rd, mem(saddr) clean check if (M[saddr] == allocated)                                                                                                |  |  |  |  |  |  |  |  |

| AtomCheck                                                                                                                                                                            |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| The metadata values are checked to detect potential atomicity violations through access interleavings.                                                                               | Example: ld %rd, mem(saddr) clean check if (M[saddr] == thread-private)                                                                                           |  |  |  |  |  |  |  |  |

| TaintCheck                                                                                                                                                                           |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| <ol> <li>The metadata values are propagated through instructions, such as ld.</li> <li>An error occurs when tainted data are used in critical ways, such as jump targets.</li> </ol> | 1) Example: ld %rd, mem(saddr) redundant update if (M[saddr] == M[rd]) 2) Example: jne %rs clean check if (M[rs] == untainted)                                    |  |  |  |  |  |  |  |  |

| Mer                                                                                                                                                                                  | nCheck                                                                                                                                                            |  |  |  |  |  |  |  |  |

| The metadata values are propagated through instructions, such as add.     An error occurs when uninitialized data are used in critical ways, such as library call arguments.         | 1) Example: add %rd, %rs1, %rs2 redundant update if (M[rd] == (M[rs1] & M[rs2])) 2) Example: ld %rd, mem(saddr) clean check if (M[rd] == M[saddr] == initialized) |  |  |  |  |  |  |  |  |

| MemLeak                                                                                                                                                                              |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| 1) The metadata values (allocation ID/pointer status) are propagated through instructions, such as ld.                                                                               | 1) Example: ld %rd, mem(saddr) clean check if (M[rd] == M[saddr] == non-pointer)                                                                                  |  |  |  |  |  |  |  |  |

trast, TaintCheck's rate is lower (84%) than that of MemLeak, as TaintCheck performs value propagation that results in long propagation chains with a higher frequency of metadata updates. For AtomCheck, over 85% of events are clean checks as most application data are consecutively accessed by the same thread and do not risk an atomicity violation. Overall, we show that 84-99% of instruction event handlers result in either clean checks or redundant updates. In Table 3, we present examples of clean checks and redundant updates for the five studied monitors.

**Stack update events:** Stack update events, namely function calls and returns, contribute up to 17% of the monitoring execution time, as shown in Figure 7. We observe that these handlers set a range of metadata to a predefined value and do not check for bugs directly. Our proposal is to

accommodates stack update events in a dedicated hardware unit that updates metadata in bulk, thereby filtering the associated software handler dispatch.

Prior work proposing architectural support for monitoring has largely ignored the acceleration of *stack-update* events; Prior work either assumes a hardwired policy for all stack accesses (e.g., all memory references to the stack access initialized data) [96], or does not provide acceleration for bulk updates, thus suffering from the associated runtime overhead [23, 48]. In our prior study, BugSifter [43], we show the runtime overhead due to the lack of hardware support for bulk updates for the five studied monitors running on the LBA framework [23].

# 3.3 Implications of Filtering on Monitoring Systems' Design

In the previous sections, we identified common high-level functionality inherent in a wide range of monitors, and we showed that the majority of the monitored events can be filtered without affecting the monitors coverage. In this Section, we explain why filtering allows for the design of a monitoring system with three key characteristics: (1) fast, (2) flexible, and (3) resource-efficient.

## 3.3.1 Fast Monitoring

We envision a Filtering Accelerator, with monitor-agnostic hardware, that filters the application event stream for diverse monitors based on our observations in Section 3.2. The accelerator handles instructions and stack updates, as they are the main contributors to the monitoring slow-down.

To handle instruction events, the Filtering Accelerator includes a simple event filtering mechanism in hardware that elides the execution of costly SW handlers for clean checks (i.e., when the metadata match an invariant), and redundant updates (i.e., when the metadata of the source and destination operands are the same). To accommodates stack-update events, the Filter-

ing Accelerator includes a dedicated hardware unit that performs multi-block writes. Our observation is that stack update handlers set a large range of metadata to a predefined value, but do not check for bugs directly.

Overall, the proposed accelerator can filter 84-99% of the common monitoring activity in hardware, thus eliminating most of the runtime overhead and allowing for fast instruction-grain monitoring.

# 3.3.2 Flexible Monitoring

While the Filtering Accelerator can handle the common case in hardware, the unfiltered events require further processing. We identify two possible options for the processing of the unfiltered events: (1) to implement the monitoring functionality on reconfigurable fabric, and (2) to implement the monitoring functionality in software, which executes on a general-purpose core.

Reconfigurability offers flexibility, but limits wide adoption because it requires programming in a low-level hardware language that escapes the comfort zone of most programmers. An additional limitation is that a reconfigurable fabric, with an internal clock rate that is typically well under a gigahertz, may struggle to keep up [33] with today's processors commonly running at multi-gigahertz frequencies.

Our preferred approach is to write the monitor on mainstream programming languages and development tools. This guarantees maximum monitoring flexibility through software execution for any unfiltered event, and accessibility to a broad range of developers.

# 3.3.3 Resource-Efficient Monitoring

To allow for full flexibility, the SW handlers for the unfiltered events are executed on a general-purpose core, in contrast to other approaches that implement the monitor on specialized HW.

FIGURE 8: (a) A two-core monitoring system, and (b) a single-core monitoring system with filtering support.

To guarantee isolation and containment, the monitor and the application execute in a separate process We consider two possible integration options for the Filtering Accelerator, as shown in Figure 8.

The *two-core monitoring system* (Figure 8(a)) executes the application and the monitor on separate cores, with an intermediate buffer to communicate the application activity to the monitor [23]. In this system, the Filtering Accelerator inspects the application events and decides whether an event requires further processing. Once the event queue is full, the application core stalls.

Upon an unfiltered event, a software handler is executed on the monitor's core. Because the handler updates metadata state potentially read by subsequent events, filtering stops during the software handler execution. When the handler execution completes, filtering resumes, draining the event queue and allowing the application to make progress. In Chapter 5, we propose Non-Blocking Filtering, a technique that overcomes this restriction and allows for the overlapped execution of the filtering process and the SW handlers for unfiltered events.

Figure 9 shows the execution time breakdown in the two-core system for our five monitoring tools (our methodology is detailed in Section 5.3). The execution time is broken down into three categories: cycles in which (1) the application core is idle due to a full event queue; (2) the

FIGURE 9: The core utilization in the two-core monitoring system.

monitor core is idle because events are filtered by the Filtering Accelerator; and (3) both, the application and monitor cores are not idle.

As the figure shows, 59% to 96% of the time one of the two cores is idle, because the two-core accelerated system is either effectively filtering the incoming event stream (idling the monitor core) or spends a significant amount of time in handler execution (stalling the application core). With both cores utilized just 16% of the time, on average, the benefit of the second core is clearly limited.