# High-Performance Communication Primitives and Data Structures on Message-Passing Manycores: Broadcast and Map

#### THÈSE Nº 6328 (2014)

PRÉSENTÉE LE 11 SEPTEMBRE 2014

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE DE SYSTÈMES RÉPARTIS

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Omid SHAHMIRZADI

acceptée sur proposition du jury:

Prof. B. Falsafi, président du jury Prof. A. Schiper, directeur de thèse Prof. P. Felber, rapporteur Prof. R. Guerraoui, rapporteur Prof. P. Sens, rapporteur

### **Abstract**

The constant increase in single core frequency reached a plateau during recent years. This is due to a physical phenomenon, known as power wall, where the produced heat inside the chip is so high that cannot be cooled down by existing technologies. An alternative to harvest more computational power per die is to fabricate more number of cores into a single chip. Therefore *manycore* chips with more than thousand cores are expected by the end of the decade. These environments provide a high level of parallel processing power while their energy consumption is considerably lower than their multi-chip counterparts. Although shared-memory programming is the classical paradigm to program these environments, there are numerous claims that taking into account the full life cycle of software, the message-passing programming model have numerous advantages. The direct architectural consequence of applying a message-passing programming model is to support message passing between the processing entities directly in the hardware. Therefore manycore architectures with hardware support for message passing are becoming more and more visible. These platforms can be seen in two ways: (i) as a High Performance Computing (HPC) cluster programmed by highly trained scientists using Message Passing Interface (MPI) libraries; or (ii) as a mainstream computing platform requiring a global operating system to abstract away the architectural complexities from the ordinary programmer. In the first view, performance of communication primitives is an important bottleneck for MPI applications. In the second view, kernel data structures have been shown to be a limiting factor. In this thesis (i) we overview existing state-of-the-art techniques to circumvent the mentioned bottlenecks; and (ii) we study high-performance broadcast communication primitive and map data structure on modern manycore architectures, with message-passing support in hardware, in two different chapters respectively.

In one chapter, we study how to make use of the hardware features to implement an efficient broadcast primitive. We consider the Intel Single-chip Cloud Computer (SCC) as our target platform which offers the ability to move data between on-chip Message Passing Buffers (MPB) using Remote Memory Access (RMA). We propose OC-Bcast (On-Chip Broadcast), a pipelined k-ary tree algorithm tailored to exploit the parallelism provided by on-chip RMA. Experimental results show that OC-Bcast attains considerably better performance in terms of latency and throughput compared to state-of-the-art solutions. This performance improvement highlights the benefits of exploiting hardware features of the target platform: Our broadcast algorithm takes direct advantage of RMA, unlike the other broadcast solutions which are based on a higher-level send/receive interface.

In the other chapter, we study the implementation of high-throughput concurrent maps in

message-passing manycores. Partitioning and replication are the two approaches to achieve high throughput in a message-passing system. This chapter presents and compares different strongly-consistent map algorithms based on partitioning and replication. To assess the performance of these algorithms independently of architecture-specific features, we propose a communication model of message-passing manycores to express the throughput of each algorithm. The model is validated through experiments on a 36-core TILE-Gx8036 processor. Evaluations show that replication outperforms partitioning only in a narrow domain.

**Keywords**: High Performance, Communication Primitive, Data Structure, Message Passing, Manycore, Broadcast, Map, HPC, Operating System.

### Résumé

La fréquence des cœurs de calcul a arrêté d'augmenter depuis quelques années. Ceci est lié au phénomène physique appelé "power wall", qui fait que, avec l'augmentation de la fréquence, la chaleur dissipée par le processeur devient trop importante par rapport aux capacités des systèmes de refroidissement. Pour continuer à améliorer les performances des processeurs, une alternative est alors d'augmenter le nombre de cœurs par processeur. Donc des processeurs manycore incluant des centaines de coeurs sont attendus pour la fin de la décennie. Ces environnements offrent un haut niveau de puissance de calcul parallèle alors que leur consommation énergétique est considérablement plus faible que celle des environnements multi-processeurs. Bien que la programmation par mémoire partagée soit le paradigme classique pour programmer ces environnements, plusieurs personnes estiment qu'en tenant compte du cycle de vie complet d'un logiciel, la programmation par échange de messages à de nombreux avantages. La conséquence directe de l'utilisation du modèle de programmation par échange de messages est l'émergence d'architectures supportant la transmission de messages entre les entités de calcul au niveau matériel. Ces plateformes peuvent être utilisées de deux manières : (i) un *cluster* de calcul haute performance programmé par des scientifiques hautement qualifiés utilisant, par exemple, une bibliothèque MPI (Message Passing Interface) pour les communications; (ii) une plateforme ordinaire nécessitant un système d'exploitation permettant au programmeur de s'affranchir de la complexité matérielle. Dans le premier cas, les performances des primitives de communication sont déterminantes pour les applications MPI. Dans le second cas, ce sont les performances des structures de données du noyau qui sont un facteur limitant. Dans cette thèse, (i) nous présentons les solutions de l'état de l'art pour traiter ces deux problèmes, puis (ii) nous consacrons deux chapitres à l'étude de primitives de broadcast (diffusion de type un-vers-tous) et à l'étude de structures de données de type tableau associatif, sur des architectures *manycore* modernes fournissant un support pour l'échange de messages au niveau matériel.

Dans le premier chapitre, nous étudions comment utiliser les fonctionnalités matérielles pour mettre en œuvre la diffusion un-vers-tous de manière efficace. Nous considérons la puce *Single Chip Cloud* (SCC) d'Intel comme plateforme cible. Cette plateforme offre la possibilité de déplacer des données sur la puce entre les tampons de transmission de messages (*Message-Passing Buffer - MPB*) des différents cœurs par accès mémoire distants (*Remote Memory Acces* - RMA). Nous proposons un algorithme de diffusion en arbre pipeliné d'arité k, appelé OC-Bcast, conçu pour exploiter le parallélisme offert par les accès mémoire distants. Les résultats expérimentaux montrent qu'OC-Bcast atteint des performances nettement supérieures aux

algorithmes de l'état de l'art en termes de latence et de débit. Ces résultats mettent en évidence les avantages d'exploiter les fonctionnalités matérielles de la plateforme cible. Nos algorithmes de diffusion profitent directement des avantages des accès mémoire distants contrairement aux autres algorithmes qui sont fondés sur une interface de type émission/réception de plus haut niveau.

Dans le second chapitre, nous étudions la mise en œuvre de tableaux associatifs efficaces dans les architectures *manycore* à échange de messages. Partitionner et répliquer une structure de donnée sont les deux approches pour en améliorer le débit dans un système à échange de messages. Ce chapitre présente et compare différents algorithmes de tableau associatif avec une cohérence forte, fondés sur le partitionnement et la réplication. Pour évaluer les performances de ces algorithmes indépendamment des caractéristiques propres à une architecture spécifique, nous proposons un modèle des communications par échange de messages au sein des processeurs *manycore* pour exprimer le débit de chaque algorithme. Le modèle a été validé grâce à des expériences réalisées sur un processeur TILE-Gx8036 incluant 36 cœurs. Les résultats montrent que la réplication surpasse le partitionnement uniquement dans un petit sous-ensemble de cas.

**Mots clés** : Haute performance, primitive de communication, structure de données, échange de messages, *manycore*, diffusion, tableau associatif, calcul haute performance, système d'exploitation.

# Acknowledgements

I am extremely grateful of my supervisor Prof. Andre Schiper as well as my colleague Thomas Ropars for their direct guide and support to write my thesis. I am also thankful to Intel and Tilera for providing us with the required infrastructure and technical support. Specifically I express my gratitude for Ted Kubaska at Intel and Chris Croft-White at Tilera for their availability whenever we encountered technical issues. I was honored to have Prof. Pascal Felber, Prof. Rachid Guerraoui and Prof. Pierre Sens as the members of the thesis jury to evaluate my thesis, and Prof. Babak Falsafi for chairing the jury. I am appreciative to all other LSR members, namely Darko Petrovic, Zarko Milosevic and Martin Beily, for their useful feedback during presentations and proofreadings. I also never forget the guides I was given by Sergio Mena and Fatemeh Borran during my first months in a research environment. And the last but not the least, I express my great appreciation for France Faille to support us whenever needed during all these years.

Omid

# Contents

| Al | bstra | ct (English/Français)                                    | 7    |

|----|-------|----------------------------------------------------------|------|

| A  | cknov | vledgements                                              | ix   |

| Li | st of | figures                                                  | xi   |

| Li | st of | tables                                                   | xiii |

| Li | st of | algorithms                                               | X    |

| 1  | Intr  | oduction                                                 | 1    |

|    | 1.1   | Message-Passing Programming Model and Manycore Platforms | 2    |

|    | 1.2   | High-Performance MPI Communication Primitives            | 4    |

|    |       | 1.2.1 Point-to-point communication                       | 5    |

|    |       | 1.2.2 Collective communication                           | 8    |

|    | 1.3   | High-Performance Kernel Data Structures                  | 10   |

|    |       | 1.3.1 Improve synchronization                            | 10   |

|    |       | 1.3.2 Minimize shared data                               | 13   |

|    |       | 1.3.3 Avoid shared data                                  | 13   |

|    |       | 1.3.4 Relaxing consistency                               | 14   |

|    | 1.4   | Thesis Overview                                          | 14   |

|    |       | 1.4.1 High-performance broadcast                         | 15   |

|    |       | 1.4.2 High-performance map                               | 16   |

| 2  | Hig   | h-Performance Broadcast                                  | 19   |

|    | 2.1   | Introduction                                             | 19   |

|    | 2.2   | The Intel SCC                                            | 21   |

|    |       | 2.2.1 Architecture                                       | 21   |

|    |       | 2.2.2 Inter-core communication                           | 22   |

|    | 2.3   | Assumptions and Goal                                     | 22   |

|    | 2.4   | RMA-based Broadcast                                      | 23   |

|    | 2.5   | Experimental Evaluation                                  | 27   |

|    |       | 2.5.1 Setup                                              | 27   |

|    |       | 2.5.2 Evaluation of OC-Bcast                             | 28   |

|    | 2.6   | Related Work                                             | 30   |

#### **Contents**

| 3  | Higl   | h-Performance Map                    | 33 |

|----|--------|--------------------------------------|----|

|    | 3.1    | Introduction                         | 33 |

|    | 3.2    | The Tilera TILE-Gx8036               | 35 |

|    |        | 3.2.1 Architecture                   | 35 |

|    |        | 3.2.2 Inter-core communication       | 36 |

|    | 3.3    | Assumptions and Goal                 | 36 |

|    | 3.4    | Algorithms and Analytical Modeling   | 37 |

|    |        | 3.4.1 Performance modeling           | 37 |

|    |        | 3.4.2 Linearizable map               | 39 |

|    |        | 3.4.3 Sequential consistent map      | 53 |

|    | 3.5    | Evaluation                           | 55 |

|    |        | 3.5.1 Modeling TILE-Gx8036           | 56 |

|    |        | 3.5.2 Model validation               | 57 |

|    |        | 3.5.3 Analysis of the map algorithms | 59 |

|    |        | 3.5.4 Discussion                     | 65 |

|    | 3.6    | Related Work                         | 66 |

| 4  | Con    | clusion                              | 69 |

| Bi | bliog  | craphy                               | 82 |

| Cu | ırricı | ulum Vitae                           | 83 |

# **List of Figures**

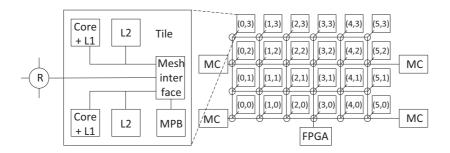

| 2.1  | SCC architecture                                                                                  | 22 |

|------|---------------------------------------------------------------------------------------------------|----|

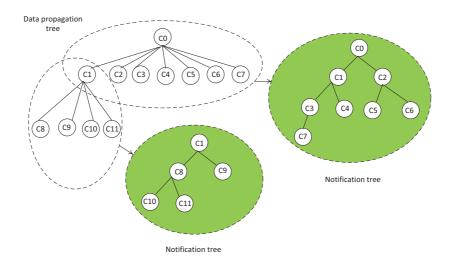

| 2.2  | k-ary message propagation tree ( $k = 7$ ) and binary notification trees                          | 24 |

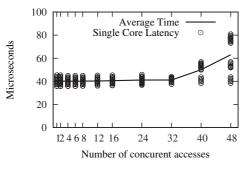

| 2.3  | MPB contention evaluation                                                                         | 27 |

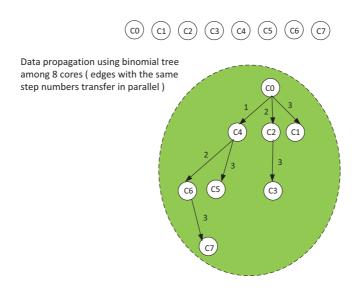

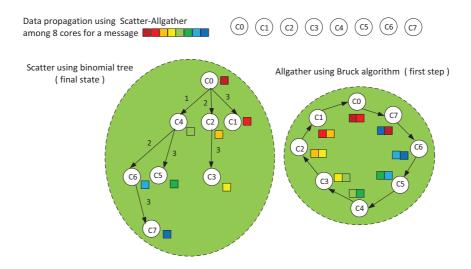

| 2.4  | Message propagation using binomial tree                                                           | 29 |

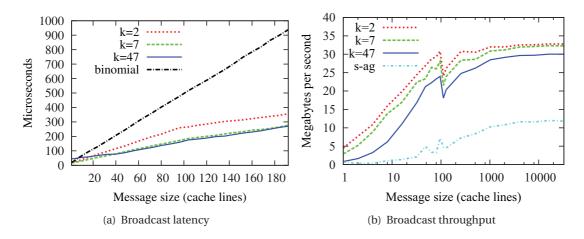

| 2.5  | Experimental comparison of broadcast algorithms (k=x: OC-Bcast with the                           |    |

|      | corresponding value of k; binomial : RCCE_comm binomial; s-ag : RCCE_comm                         |    |

|      | scatter-allgather)                                                                                | 30 |

| 2.6  | Message propagation using <i>scatter-allgather</i>                                                | 31 |

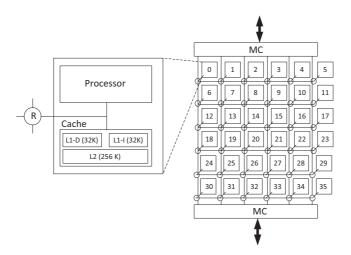

| 3.1  | TILE-Gx8036 architecture                                                                          | 36 |

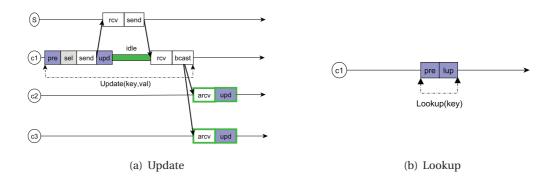

| 3.2  | Simple partitioning                                                                               | 40 |

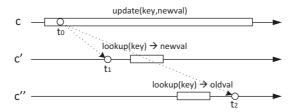

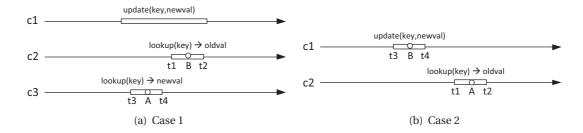

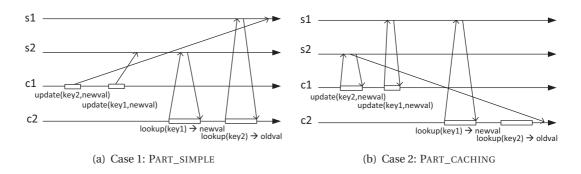

| 3.4  | Non-linearizable execution with a replicated map                                                  | 41 |

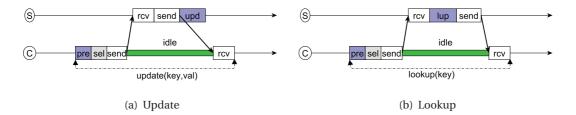

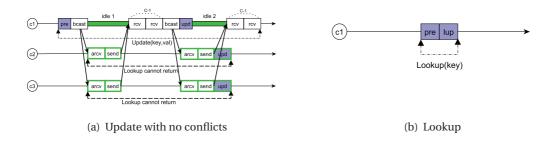

| 3.5  | Replication with remote synchronization for lookups                                               | 43 |

| 3.7  | Replication with no remote synchronization for lookups                                            | 45 |

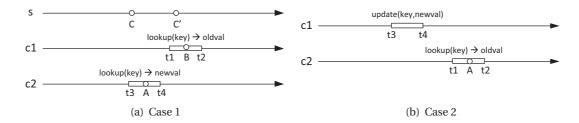

| 3.9  | Scenarios used to prove the Theorem 3.4.1                                                         | 47 |

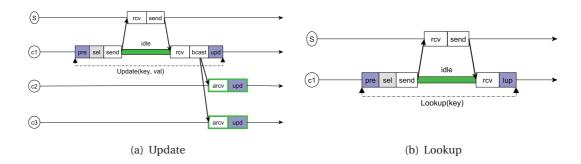

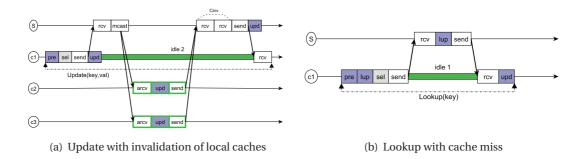

| 3.10 | Replication using two phase commit                                                                | 48 |

| 3.12 | Partitioning with local caches                                                                    | 49 |

| 3.14 | Scenarios used to prove the Theorem 3.4.2                                                         | 51 |

| 3.15 | Sequential consistent replication                                                                 | 53 |

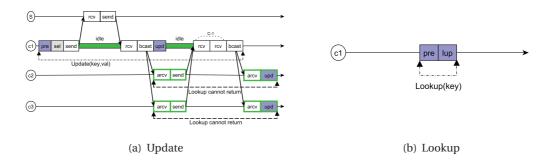

| 3.17 | $Impossibility \ of \ exploiting \ sequential \ consistency \ for \ partitioning \ algorithms  .$ | 55 |

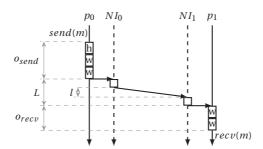

| 3.18 | Point-to-point communication on the TILE-Gx for a 2-word message $m$ ( $NI$ :                     |    |

|      | network interface)                                                                                | 56 |

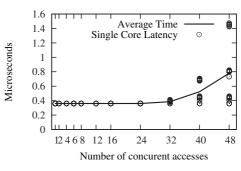

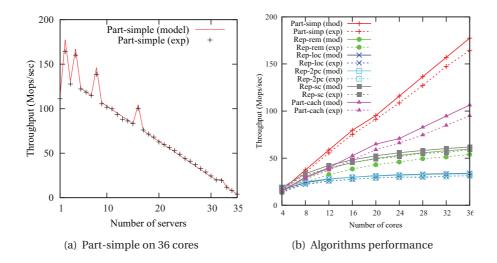

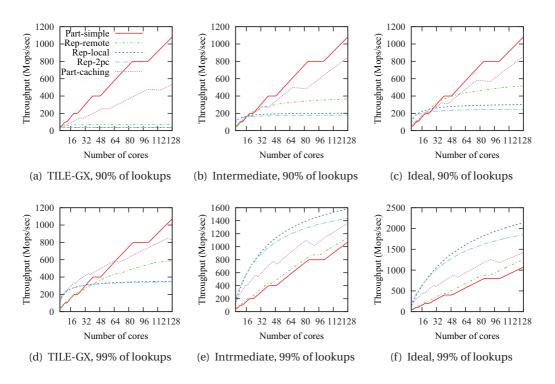

| 3.19 | Model validation on Tilera TILE-Gx processor (90% of lookup operations) $ \ldots $                | 58 |

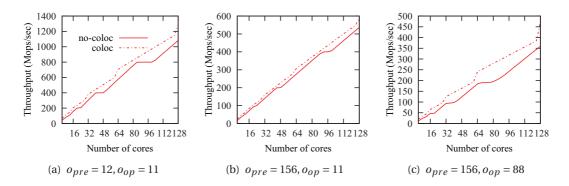

| 3.20 | Performance on the three platforms ( $o_{pre} = 12$ , $o_{op} = 11$ )                             | 60 |

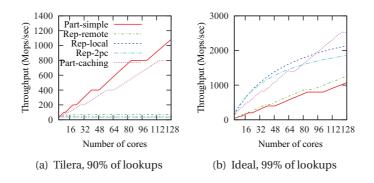

| 3.21 | Impact of the computational costs ( $\it ideal$ platform, 99% of lookups)                         | 62 |

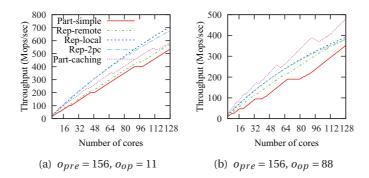

|      | Impact of the access pattern ( $o_{pre} = 12$ , $o_{op} = 11$ )                                   | 62 |

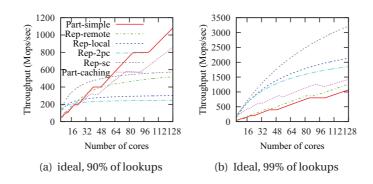

| 3.23 | Impact of weakening consistency criteria ( $o_{pre} = 12$ , $o_{op} = 11$ )                       | 63 |

| 3.24 | Impact of colocating clients and servers on ideal platform (PART SIMPLE)                          | 64 |

# **List of Tables**

| 1.1 | Different strategies to implement parallel programs                               | 3  |

|-----|-----------------------------------------------------------------------------------|----|

| 1.2 | Metrics to compare message-passing and shared-memory programming models           | 3  |

| 1.3 | Existing techniques for high-performance MPI primitives on manycores              | 5  |

| 1.4 | Existing techniques for high-performance kernel data structures on manycores      | 10 |

|     |                                                                                   |    |

| 3.1 | Model parameters                                                                  | 39 |

| 3.2 | Parameters value in cycles (A "-" means that the value is the same as on TILE-Gx) | 57 |

# **List of Algorithms**

| 1  | OC-Bcast (code for core $c$ )       | 28 |

|----|-------------------------------------|----|

| 2  | PART_SIMPLE (code for client $c$ )  | 41 |

| 3  | Part_simple (code for server $s$ )  | 41 |

| 4  | Rep_remote (code for replica $c$ )  | 44 |

| 5  | Rep_remote (code for server $s$ )   | 44 |

| 6  | Rep_local (code for replica $c$ )   | 46 |

| 7  | Rep_local (code for server $s$ )    | 46 |

| 8  | Rep_2pc (code for replica $c$ )     | 48 |

| 9  | PART_CACHING (code for client $c$ ) | 50 |

| 10 | Part_caching (code for server $s$ ) | 50 |

| 11 | Rep_sc (code for replica $c$ )      | 54 |

| 12 | REP_SC (code for server s)          | 54 |

## 1 Introduction

Hitting the power wall prevents the semiconductor industry to improve the single core performance according to the Moore law [21]. The alternative to obtain a higher performance is to increase the level of parallelism by putting many ordinary cores on the same chip. With the same power budget, it has been shown that the aggregate performance of a chip with big number of simple cores exceeds that of a chip with small number of complex cores [20]. Therefore manycore processors featuring tens, if not hundreds, of ordinary cores communicating with a highly efficient network-on-chip (NoC) are becoming more and more available.

Taking advantage of the high degree of parallelism provided by such architectures is challenging and raises questions about the programming model to be used [99, 72]. Most existing processors are still based on cache-coherent shared memory. Designing a scalable concurrent algorithm for cache-coherent processors is a difficult task because it requires understanding the subtleties of the underlying cache coherence protocol which is not inherently scalable [27]. On the other hand, though less popular among mainstream programmers, message-passing model looks appealing because it provides the programmer with explicit control of the communication between cores which can lead to significant benefits for the full life-cycle of software [57]. However, compared to the vast literature on concurrent programming in shared-memory systems [49], message-passing programming on manycore processors is not yet a mature research topic. The natural consequence of adopting a message-passing programming model on the architecture of these platforms is to provide message-passing support in hardware, although it can be also emulated on top of a shared address space with considerable performance penalties.

Considering the low latency and high throughput of a NoC, manycore chips are very similar to parallel High Performance Computing (HPC) clusters. In order to provide inter-process communication, HPC applications take advantage of different Message Passing Interface(MPI) libraries. Performance of MPI communication primitives are a major bottleneck in HPC applications, and have been widely studied in different contexts. However, results show that porting an HPC communication library to manycore platforms requires rethinking the design of the communication primitives [83].

Apart from running scientific HPC applications, these chips can be seen as the ordinary computing platform to run general-purpose applications, where a global operating system abstracts away the architectural complexities from the mainstream programmer. Kernel data structures have been shown to be an important performance bottleneck for the operating systems designed for these environments [109, 16, 19]. To increase the performance of data structures in shared memory architectures, several well-known techniques can be used [49]. In message-passing systems, improving the performance of concurrent data structures requires fundamentally different approaches [36]. Existing studies made in distributed message-passing systems are of little help because the high performance of NoCs provides a completely different ratio between computation and communication costs compared to large scale distributed systems.

In the rest of the introduction, we discuss the motivations for applying the message-passing programming model on manycores as well as its architectural implications on these platforms. Afterwards we briefly explain the existing techniques to improve the performance of MPI communication primitives and kernel data structures on manycore environments, with different communication infrastructures. Finally we present an overview of the thesis.

#### 1.1 Message-Passing Programming Model and Manycore Platforms

Message passing and shared memory are the two models to program parallel applications. In a message passing model, access to the shared data is managed by explicit communication with no shared address space while in a shared memory model, shared data is located on a shared address space. A study done in [57] by Intel tries to choose the right programming model to address the specific features of manycore architectures. To do this comparison, they consider full cycle of software development including writing, debugging, validating, optimizing and maintaining of the parallel program. They evaluate different strategies for designing parallel applications against different metrics, covering full life-cycle of a software development. The chosen strategies, derived from [96], cover a broad range of parallel applications: agenda parallelism, result parallelism and specialist parallelism. In agenda parallelism, an application is divided into a particular agenda of tasks and each process is assigned to pick a task from the agenda and do the tasks repeatedly until the job is done. In result parallelism, the ultimate goal of the application is to come up with a data structure as the final result and each process is assigned to produce one piece of the result. In specialist parallelism, an application is based on some logical networks of specialists and each process is assigned to perform one specific kind of work. Each strategy uses different patterns for designing parallel algorithms (See Table 1.1). Each pattern is assessed with respect to a set of concrete metrics inspired from [46], namely generality, expressiveness, viscosity, composition, validation and portability (See Table 1.2 for a brief description of each).

The message-passing programming model is claimed to be a better choice with respect to composition, validation and portability, independently of the chosen strategy for parallelism.

#### 1.1. Message-Passing Programming Model and Manycore Platforms

| Parallelization Strategies | Parallelization Strategies   Design Patterns |                 |

|----------------------------|----------------------------------------------|-----------------|

| agenda parallelism         | task parallelism / divide and conquer        | tasks           |

| result parallelism         | geometric decomposition / data parallelism   | data structures |

| specialist parallelism     | producer consumer / event based coordination | events          |

Table 1.1: Different strategies to implement parallel programs

| Metric         | Description                                                          |

|----------------|----------------------------------------------------------------------|

| composition    | ability to modularize parallel programs                              |

| validation     | possibility of validating program correctness                        |

| portability    | easy portability of the program to different platforms               |

| generality     | ability to express any parallel algorithm                            |

| expressiveness | existence of concise concurrency abstractions                        |

| viscosity      | possibility of implementing incremental changes to a working program |

Table 1.2: Metrics to compare message-passing and shared-memory programming models

Parallel programs can be decomposed into different isolated modules, each working on its own private memory, interacting with each other through a well-defined communication interface. Decomposing a program in this way can be naturally expressed in a message-passing programming model. To validate a program we need to guarantee that every legal interleaving of active threads leads to a correct execution. In a message-passing programming model, the programmer only needs to consider combinations of different messaging events. In a shared-memory programming model, validating a program is shown to be an NP-complete problem [55]. Moreover message-passing programming is more portable since it imposes less constraints on the consistency model of different platforms.

Regarding other metrics, namely generality, expressiveness and viscosity, message-passing model seems to be a better option if specialist parallelism is applied. Considering the pipeline algorithms, movement of data between different levels can be naturally expressed in a messagepassing model. Moreover it does not suffer from the error-prone synchronization during data movement, a phenomenon in which shared-memory programmer suffers from. Considering event-based algorithms, message-passing programmers should be careful about unpredictable flow of messages between processes. However this issue can be circumvented using a higher-level model in which flows of messages are controlled. The actor model can provide such a coordination for event-based algorithms and it is a natural fit for messagepassing programming model. Implementing actor model in shared-memory needs complex synchronization hassles. On the other hand, shared-memory model is argued to be a better choice for agenda and result parallelism. For example, applying a divide and conquer pattern is a better fit for shared-memory programming model since a task is recursively divided into a number of smaller tasks where the data associated with each task must be decomposed. In message-passing programming model, where decomposition of data is explicit, it is difficult to apply when lots of tasks are created dynamically. Shared memory model avoids this problem since all threads have access to the shared data. Moreover considering data parallelism pattern, shared memory model seems more suitable since it does not require complicated

data movements during execution of collective operations.

Whatever the choice of the programming model, it puts requirements on the hardware that supports it. A programming model that requires a shared address space, in order to run efficiently, requires hardware-supported cache coherence. By increasing the number of cores, the overhead of the hardware-based cache coherency limits scalability. This is mainly due to the increase in architectural complexity, coherency traffic on the interconnect and needed storage to track the cached values. These increasing costs mean that, as the cores grow, a cache coherency protocol eventually limits the achievable performance of the parallel cores. On the other end of the spectrum, a programming model that needs message passing, in order to run efficiently, requires an architecture with hardware-based message-passing interface <sup>1</sup>. A message-passing manycore chip, with no support for cache coherency, can be suitable for software implemented using the message-passing model. In this case, there is no coherency barrier and these architectures can scale up to a much larger number of cores.

As you might already conclude, message-passing programming model seems attractive for both programming model and architecture layers. The benefits magnify as the number of cores increase. Following these observations, manycore architectures with programmer-accessible message passing support in hardware are becoming more and more visible. These architectures provide message passing between different cores through shared on-chip buffers. The sender acts by putting its message into the shared buffer and the receiver acts by getting those messages from the shared buffer. In some of these architectures, the programmer is in charge of providing the required synchronization between senders and receivers during their access to the shared buffer. Examples of such architectures include: Intel Polaris [50], Intel SCC [52], Calray MPPA [4] and Adapteva Epiphany [1]. In another set of architectures, this synchronization task is abstracted away from the programmer and is totally managed by the hardware. Examples of such architectures include: Tilera TILE [8], Intellasys SEAfourth [3] and Picochip DSP [7]. To the best of our knowledge, the TILE architecture from Tilera is the only case where all cores have access to a cache-coherent shared address space while they are also provided with a hardware-based message-passing interface.

#### 1.2 High-Performance MPI Communication Primitives

Manycore environments resemble HPC clusters while occupying smaller space and consuming less energy. The performance of MPI communication primitives is a major bottleneck for HPC applications running on manycore environments [86]. We overview some of the existing techniques used to improve the performance of MPI communication primitives in these environments. We start by point-to-point communication primitives followed by collective ones. A summary of these techniques are mentioned in Table 1.3. Note that we only mention those which are specific to manycore environments, avoiding the general techniques which

<sup>&</sup>lt;sup>1</sup>Ignoring faults, each of the two programming models can be implemented on top of an architecture which suits with the requirements of the other one. However this sacrifices the performance.

| Communication  | Techniques                               |  |  |

|----------------|------------------------------------------|--|--|

| point to point | avoid system calls                       |  |  |

|                | minimize copying (at run time)           |  |  |

|                | minimize copying (at compile time)       |  |  |

|                | hardware implementation                  |  |  |

| collective     | leverage kernel facilities               |  |  |

|                | topology awareness                       |  |  |

|                | hardware implementation                  |  |  |

|                | exploit hardware features and properties |  |  |

Table 1.3: Existing techniques for high-performance MPI primitives on manycores

are applicable independently of the target architecture.

#### 1.2.1 Point-to-point communication

In the absence of hardware-based message-passing interface, implementing message passing on top of shared memory is the only viable solution to benefit from the message passing programming model. This leaves a rather vast space for performance optimizations. Proposed techniques are mainly based on avoiding costly systems calls as well as minimizing the number of memory copies during message transfers. We briefly go over some of these techniques.

#### Avoiding system calls

The most intuitive way to implement communication between processes, located on different cores, is to use kernel facilities of the operating system. These facilities include Unix domain sockets, TCP and UDP sockets, pipes, IPC and POSIX message queues. Despite some differences, their underlying mechanisms are similar. Using all facilities, a buffer in the kernel space is shared amongst a set of senders and receivers. To send a message, a sender invokes a system call which copies the message from the user space to the kernel space and adds it to the buffer. To receive a message, a receiver invokes another system call that copies the incoming message, if any, from the kernel-space buffer to a user-space buffer.

The main drawback of the above, is the costly system calls which are invoked during each message transfer. Message-passing mechanism in the Barrelfish operating system [2] avoids these costly system calls by functioning totally in user space. For each sender/receiver pair, there are two limited size circular buffers of messages which act as unidirectional communication channels. Each message entry is composed of a header and of a content. The header contains notification flags for the purpose of synchronization, *e.g.* to inform the receiver that the message can be read. Whenever a sender wants to send a message from its private buffer, it first checks if there is enough room in the channel for a new message. If it is the case, it copies the message from its private buffer to the communication buffer. The receiver knows the location of the next entry to be read from the communication channel. To receive a message, it polls the header of the message at that location, waiting for the notification to be written.

As soon as the notification is written by the sender, the receiver copies the message from the communication buffer to its own buffer and sends an acknowledgement back to the sender. A study done in [15] compares the throughput of kernel-based techniques with message-passing mechanism implemented in Barrelfish on a shared-memory manycore architecture. As expected, the achievable throughput of message-passing mechanism in Barrelfish outperforms the kernel-based techniques, especially for the case of small messages.

#### Minimize copying (at run time)

Previous techniques need two memory copies to transfer a message from the sender to the receiver. Several techniques have been proposed to reduce the number of copies, during point-to-point communication, to only one. Most of these techniques rely on the memory mapping facilities of the operating system kernel. We overview some of these techniques.

A method based on Linux KNEM kenerl module [79], tries to improve the performance of MPI communication on manycores by minimizing the number of memory copies. The main trick roots in the kernel's ability to access the memory of all user-space processes beyond its address space boundary. Therefore inter-core communication via the kernel thread can be done using only one memory copy. Although this method exhibits a better throughput compared to the techniques based on an intermediate shared-memory buffer, its small-message latency suffers from the context switch overhead between user and kernel threads.

ZIMP (Zero-copy Inter-core Message Passing) [15] is an efficient inter-core communication mechanism for manycores functioning totally in user space which, unlike message-passing mechanism in Barrelfish, provides a zero-copy send primitive by allocating messages directly in the shared communication channels. To send a message, a sender first gets the address of the next available entry in the channel. Afterwards it waits for that entry to become free, *i.e.* all receivers have read the previous message at this entry, by polling on a flag. When it is the case, the sender writes the content of the message in that entry followed by updating the synchronization flags. To receive a message, a receiver first gets the index of the next message that can be read. If there is a message to be read, it updates the index of the next message to be read, copies the content of that entry and resets a flag indicating that the message is read. Comparison of the message-passing mechanisms of ZIMP and Barrelfish shows an order of magnitude throughput improvement in favor of ZIMP.

In [40], the authors have implement a Hybrid MPI (HMPI) library, as an abstraction layer on top of existing MPI libraries, to investigate single-copy message-passing techniques on manycores. To implement message passing on top of shared memory, memory used for communication is mapped to the same virtual address on every process. They implement two incoming message queues per receiver. The first queue is globally accessible by all processes. Senders write messages to this global queue which is owned by the destination process. The second queue is private. When a receiver attempts to match incoming messages to its local receives, it empties its global queue and adds incoming messages to its private queue. However processes have to

map the memory region of other processes to their own address space, which means that the total size of the page tables can become large due to excessive mappings.

XPMEM [9] is a Linux kernel module that enables any process to map the memory space of another process into its own virtual address space. After a process maps the memory region of another process to its own address space, it can access that memory region using a single memory copy operation. Similarly to HMPI, this mechanism suffers from a high number of mappings and growing size of the page tables.

SMARTMAP [24] is another strategy based on address space mapping which is implemented in some lightweight kernels. Similar to XPMEM, SMARTMAP enables a process to map the memory of another process into its address space. On SMARTMAP, unlike XPMEM, page table entries that are used for a remote address mapping are shared. A process can access memory of another process by updating the corresponding shared entries. Therefore the total size of the page tables does not grow as in the previous cases. However implementing SMARTMAP in the Linux kernel is hard since the memory management of the Linux does not allow shared page table entries.

PGAS (partitioned global address space) programming model [110] is becoming popular as a suitable programming approach for manycore architectures. In PGAS applications, global arrays are partitioned amongst participating processes. Access to remote part of a global array, located on a remote process, takes place through inter-core communication. Most PGAS languages currently use some shared-memory solutions to implement such communication. However these solutions lead to either two memory copy operations in case of applying a shared buffer or large page tables in case of applying a memory mapping schema. In [93], a new process model named PVAS (partitioned virtual address space), provides a solution that implements single-copy inter-core communication for PGAS languages without suffering from the page table size issue. The main idea is to allow a PGAS process to access the memory region of another process directly, by eliminating the address space boundary between them.

#### Minimize copying (at compile time)

The study in [25] presents a compiler-based optimization for MPI applications that directly transfer application data structures from senders to receivers without paying the cost of message serialization and deserialization on a shared-memory architecture. It exploits the fact that the code to serialize and deserialize data structures typically does a simple iteration through the communication buffer. This makes it possible to match the serialization writes in the sender's source code with the deserialization reads in the receiver's source code. Therefore a data structure can be transferred between senders and receivers using direct memory access.

#### Hardware implementation

Implementing message passing on shared-memory architectures requires processor intervention for the data movement and synchronization. By implementing these functions in hardware, cores are freed from having to interfere with message transfers, which allows them to perform some other useful work. Pronto message-passing system [58] provides a DMA-based mechanism for message transfers which performs buffer management and message synchronization directly in hardware. Messages are moved between local memories of each tile through hardware-managed message-passing buffers. This shows an advantage over message-passing architectures with one-way communication primitives, *e.g.* Intel SCC, where message synchronization and buffer management are entirely done by the programmer. Moreover modern manycore chips, *e.g.* Tilera TILE series, provide a mechanism similar in the sense that a high-performance message-passing system between cores is entirely implemented in hardware. Therefore the programmer does not need to deal with message synchronization and buffer management issues of inter-core communication.

#### 1.2.2 Collective communication

A significant performance overhead of the HPC applications is caused by collective communication, which involves several tasks in one communication. Profiling study in [87] shows that MPI applications spend more than eighty percent of their communication time in collective operations. Improving performance of point-to-point communication indirectly improves the performance of collective operations that are implemented on top of them. However several proposed techniques directly improve the performance of collective operations. We briefly present some of these techniques including: taking advantage of kernel facilities, taking into account topology of on-chip network, direct implementation of collective primitives in hardware and exploiting architectural features and properties during the design phase.

#### Leverage kernel facilities

Leveraging kernel facilities have shown to be beneficial for the performance of MPI collectives on manycores. In [68], the author implements a high-performance broadcast operation on a shared memory architecture, as an example of MPI collective operations, utilizing the KNEM kernel facility. As mentioned earlier, KNEM is a Linux kernel module that enables inter-core communication with only a single memory copy. Recent versions of this module support multiple processes being able to read or write to the communication buffer simultaneously. Utilizing this module not only decreases the on-chip traffic by reducing the number of memory copies, but also results in higher level of parallelism in designing collective operations. Experiments show a significant performance improvement of kernel-assisted collectives compared to the existing state-of-the-art MPI implementations.

#### **Topology awareness**

With the increasing number of computing cores and memory hierarchies integrated into a single chip, the distribution of participating MPI processes inside a chip becomes more critical for the performance of collective operations. As the first try to leverage on-chip topology information to improve performance of collective operations, [69] proposes an automated framework for MPI libraries to detect and take advantage of the process distances during runtime. Based on runtime process distance information, the MPI library constructs an adaptive communication topology for each collective operation. These topology-aware operations provide optimal performance for a given placement of participating processes. This automated optimization approach at the level of the MPI library can complement the clever process placement approaches mentioned in the context of HPC clusters [29, 53].

#### Hardware implementation

Hardware support can prevent collective communication from becoming a system bottleneck. Authors in [108] propose some hardware features to deal with the communication overheads of on-chip message passing. The main idea is to offload the application from computation-intensive tasks such as collective operations in a transparent way. They propose an interface between processing cores and the on-chip network using a hardware module called Small Network Adapter. Using this interface, they offload the basic mechanism of point-to-point message passing to the hardware, which is leveraged subsequently to implement collective operations. Moreover some recent manycore products, *e.g.* Kalray MPPA [4], Adapteva Epiphany [1] and Picochip DSP [7], provide hardware support for multicast operation with a programmer-accessible interface. Such a support can achieve substantial throughput improvements and power savings, since cores are not involved in the actual transfer of messages. Numerous works investigate implementation of other collective protocols. An an example authors in [67] propose a hardware mechanism for reduction operations. However it targets hardware protocols, *e.g.* cache coherency, and provides no software interface. We are not aware of a manycore chip that provides hardware support for other MPI collectives.

#### Exploiting hardware features and properties

Implementations of MPI collectives take advantage of shared-memory manycore architectures in the following ways: (i) collectives are built on top of point-to-point message-passing, which uses shared memory as its transport layer; or (ii) collectives are implemented directly on top of the shared memory, where processes can copy a message into the shared memory space so that all communicating processes can have access to it. This feature can reduce the number of memory transfers in collective operations which leads to a better performance [44, 71]. Moreover as the number of cores per chip grows, cores exhibit more and more non-uniform memory access (NUMA) behaviour. A work done in [61], takes the NUMA property into account for better implementation of MPI collectives.

#### **Chapter 1. Introduction**

| Techniques              | Flavours                                                      |  |  |  |

|-------------------------|---------------------------------------------------------------|--|--|--|

| improve synchronization | increase parallel access (fine-grain locks / RW locks / RCU ) |  |  |  |

|                         | reduce memory contention (exponential backoff / queue locks)  |  |  |  |

|                         | reduce remote memory referrences (server-based / combining)   |  |  |  |

|                         | lock-free synchronization                                     |  |  |  |

| minimize shared data    | address range / shares / kernel cores                         |  |  |  |

| avoid shared data       | replication / partitioning                                    |  |  |  |

| relaxing consistency    |                                                               |  |  |  |

Table 1.4: Existing techniques for high-performance kernel data structures on manycores

#### 1.3 High-Performance Kernel Data Structures

Manycore architectures are becoming accessible to main-stream programmers. This introduces important challenges for operating systems designed for these environments in terms of scalability when the number of cores increases [16, 109, 22, 65, 23]. Some studies reveal that poor scalability of some operating system services can dominate application performance [43, 105]. An important source for poor scalability of such services is the use of concurrent kernel data structures, which are accessed by multiple cores at the same time. In this section, we discuss some of the state-of-the-art techniques proposed to improve the performance of data structures in manycore environments. Note that we limit ourselves to general techniques that are applicable to all data structures, and avoid techniques that target a specific data structure. Performance improvement techniques can be classified into the following categories: (i) improving synchronization; (ii) minimizing shared data; (iii) avoiding shared data; and (iv) relaxing consistency. We overview different flavours of each category, which are summarized in Table 1.4, throughout this section.

#### 1.3.1 Improve synchronization

The usual technique to implement high-performance concurrent data structures in shared-memory manycore architectures is to improve the synchronization methods which is used for controlling mutual access to the shared data. This can be done using different approaches: (1) by increasing the parallel access to the data structure; (2) by reducing the contention on the cache lines; (3) by delegating the task of synchronization to another set of cores; and (4) by applying lock free synchronization provided that hardware support is available. Some of these techniques are extensively used in the Linux operating system [5] and its proposed extension to support manycores [22]. We go briefly through each approach.

#### Increase parallel access

The first version of Linux kernel with multi threading support, applied a single lock to protect critical kernel data structures. Soon it became a major performance bottleneck of the kernel and was subsequently replaced by fine grain locking [100]. Fine grain locking is a mechanism

used to break a single lock into smaller locks where each of them is responsible to protect a single portion of the shared data structure. Operations on the data structure are required to obtain one or more of these locks in order to read or write the corresponding portion of the data structure. Fine-grain locking is able to improve the performance of the operating system due to its ability to let more operations proceed in parallel.

A similar benefit can be provided by having locks that allow multiple concurrent readers, known as reader-writer locks [32]. They allow reader threads to access the shared data concurrently, but exclusively from the writer threads. However depending on the implementation, either readers or writers might face with starvation if other threads keep performing the opposite operation. Therefore variants of these locks with different fairness properties between reader and writer threads are also proposed.

The read-copy-update (RCU) algorithm [75] is a special form of reader-writer locks which is used in Linux kernel. In contrast with conventional locking primitives that provide mutual exclusion among concurrent threads, no matter whether they are readers or writers, or with reader-writer locks that allow concurrent reads but not in the presence of writes, RCU supports a single writer and multiple readers to occur concurrently. This property ensures unconditional progress for read operations.

#### **Reduce memory contention**

An important aspect of designing a lock, is to come up with a strategy if trying to acquire a taken lock fails. In a unicore machine, the common solution is to give the core to another thread. However in the case of more than one cores inside a single machine, trying repeatedly to acquire a lock is needed since the lock can be released at any time by a thread which is executing in another core. Spinlocks are made based on this technique. Spinning threads can also be scheduled to get blocked, but this makes sense if the scheduling overhead does not exceed the spinning overhead and cores have something else to do. However spinning on a single synchronization variable can be a severe performance bottleneck, since it can introduce a high memory contention and interconnect traffic.

A solution to deal with pitfalls of spinning is to apply a technique known as exponential backoff [10]. Using this solution, a thread with unsuccessful spinning attempts, waits for a while before trying again. The waiting time grows with the number of failed attempts. This leads to less memory contention and interconnect traffic due to the less unsuccessful attempts.

Exponential backoff can lead to a situation where the lock is free, while all threads trying to acquire it have been delayed and none of them can make progress. A way to avoid such a scenario is to create a logical queue of competing threads so that a lock, upon its release, can be owned by the next waiting thread. Each queue thread can have a flag to inform the next thread to get the lock upon its release. To obtain a lock, a thread adds itself atomically to the tail of the waiting queue. Afterwards it spins on the flag of its predecessor to know whether it

can obtain the lock. Note that each thread spins on its local cacheline in a cache-coherent architecture. Some variants of queue locks implement the queue using an array [12, 45], while other variants implement the queue using a list [33, 70, 76]. Several reader-writer locks are also proposed, applying a similar queue-based technique [77, 56, 91].

#### Reduce remote memory references

The number of Remote Memory References (RMR) during a synchronization protocol is an important performance bottleneck in a cache-coherent architecture, since accessing memory is an order of magnitude more expensive than accessing local caches. The previous techniques based on queue-locks require a constant number of RMRs to acquire a lock, thanks to the local spinning. However other solutions try to further reduce the number of RMRs. The key idea of these solutions is to delegate execution of the critical section to the core where shared data is located. Two main proposed approaches to achieve this goal include: the server-based approach [66, 31], and the combining approach [48, 38, 39].

In server-based approach, clients send operations to a dedicated server, that contains the shared data structure, to execute them on their behalf. The shared data structure remains in the cache of the server, since it is the only entity that accesses the data structure. Therefore the only possible RMRs during execution of a critical section, are related to the communication between the clients and the server. This simple approach is very efficient when a small number of critical sections are highly contended [66].

An approach based on combining does not require dedicated servers. A so called combiner thread which holds a lock on a shared data structure, executes operations of other threads on the critical section in addition to its own. In order to prevent combiner from being starved, if the number of requests are high, its role changes among different threads over time. Similar to server-based approach, possible RMRs only happen during the communication between the combiner and other threads. Despite complexities involved in synchronizing threads, this approach prevents wasting of CPU cycles in case of no pending critical section requests.

As a further optimization, in [82] authors take advantage of hardware-based message passing to perform the communication between clients and server/combiner. Their message-passing variants of server-based and combining approaches show a considerable gain of performance compared to their shared-memory counterparts, specially in case of small critical sections. Their results clearly shows benefits of using hardware message passing, which leads to decreased number of RMRs during communication between clients and the entity who executes critical section operations.

#### Lock-free synchronization

Using locks to provide mutual exclusion inherently suffers from several liveness issues including: deadlock, preemption or interruption of the lock holder, priority inversion and convoying.

Moreover there should be a strategy to release the shared resources in case the lock holder fails. An alternative to avoid these issues is to provide synchronization without locks, a method which is known as lock-free synchronization. Concurrent access to a lock-free data structure guarantees that some thread makes progress independently of the behaviour of other threads. However lock-free synchronization requires support of special atomic operations in hardware, such as atomic swap, test-and-set, fetch-and-add, compare-and-swap and load-link/store-conditional. Lock-free synchronization can provide better performance without suffering from liveness issues of locks, although contention and starvation are still a possibility. The difficulty of applying this approach comes from the lack of a general recipe to design a lock-free data structure, hence each data structure should be studied on its own [49]. The authors of [73] propose a multicore operating system kernel which is implemented based on lock-free data structures.

#### 1.3.2 Minimize shared data

To deal with the scalability challenges of traditional operating systems on cache-coherent manycores with respect to kernel data structures, the Corey operating system [23] proposes a new policy: the kernel assumes each data structure is modifiable by only one core, unless applications request a different policy. In this way applications are in charge of controlling sharing of data structures. The application is the entity that has enough information to make sharing decisions. This can include operating system services, application-level libraries and user-level applications. Therefore the operating system pays the sharing costs (*e.g.* cache misses) only when the application logic finds it necessary. To achieve this goal, they introduced three operating system abstractions: address ranges, shares and kernel cores. We introduce each abstraction briefly.

Address ranges allow applications to decide which portions of the address space is private to each core and which are shared amongst all. Accessing private regions does not suffer from contention and invalidations of TLB on other cores. Declaration of shared regions allows sharing of hardware page tables. This reduces the number of page faults, which can happen when a core references pages that are present in physical memory but are not mapped in the hardware page table. Shares are lookup tables for kernel data structures that allow applications to control which data structures are visible to different cores. Finally kernel cores are dedicated cores that are asked by applications to run a specific kernel task. Kernel cores avoid contention on the data that are used by their specified function.

#### 1.3.3 Avoid shared data

Recent operating system prototypes targeting architectures with a very large number of cores, consider a fundamentally different approach to implement kernel data structures. They look at the operating system as a distributed system of functional units, communicating explicitly using message passing. Implementation of kernel data structures avoids sharing to provide

scalability through different approaches: while some consider replication of a shared data structure on client cores, others consider a set of servers to provide the functionality of a shared data structure.

Barrelfish [16] considers the operating system as a distributed system of cores, communicating with each other through explicit message passing. Unlike kernel data structures in traditional operating systems, which are shared and protected by locks, kernel data structures in Barrelfish are replicated across cores. Therefore any potentially shared data structure is considered as if it is a local replica. Consistency amongst replicas is maintained by exchanging messages. Their claim to improve scalability by replication comes from reducing the interconnect traffic, memory contention, synchronization overhead and access latencies.

FOS [109] and Tessellation [65] operating systems consider a set of servers to provide functionality of kernel data structures to applications through message-passing requests. Kernel data structures can be replicated or partitioned amongst servers to further improve the performance. This architecture behaves similarly to the internet servers, which allows them to scale up to a large number of machines.

#### 1.3.4 Relaxing consistency

All previous approaches try to improve the implementation of a kernel data structure to achieve a better performance. However performance can also be improved through relaxing the semantics of a data structure. As the number of cores grows, similarly to the internet services, this relaxation can be more beneficial. Although the concurrent data structures designed for shared memory architectures mostly ensure linearizability [49], recent manycore operating systems might tolerate kernel data structures with weaker consistency criteria. As an example, an implementation of a replicated naming service for the FOS operating system ensures eventual consistency [18]. In [92], authors claim that relaxation of consistency criteria is a necessary step towards providing scalable data structures for future manycores and propose a concurrent quiescent-consistent stack as their proof of concept. However relaxing the consistency semantics of different data structures on manycore architectures is not yet a well studied topic.

#### 1.4 Thesis Overview

In this thesis, we consider a message-passing programming model on top of manycore architectures with programmer-accessible message-passing support in hardware. We study important performance bottlenecks of HPC applications and operating systems designed for these environments, *i.e.* MPI communication primitives and kernel data structures respectively. More specifically, we study high-performance MPI communication primitives, considering the case of broadcast, as well as high-performance kernel data structures, considering the case of a map, in two different chapters. We overview the context and contributions

of each chapter.

#### 1.4.1 High-performance broadcast

High Performance Computing (HPC) is defined as employing aggregating computing power to deliver a much higher performance than one can obtain from a typical workstation in order to solve computationally-intensive problems in science, engineering, and business. Single Program Multiple Data (SPMD) programming, where multiple independent processors simultaneously execute the same program in parallel, is a popular programming technique for implementation of HPC applications. The Message Passing Interface (MPI) [80] is the *de facto* standard for programming SPMD HPC applications. MPI defines a set of primitives for point-to-point as well as collective communication, *i.e.* operations involving more than two parties, between processes. Performance of collective operations have been shown to be an important bottleneck for MPI applications [86].

Architecture of recent manycore chips, *e.g.* the low latency and high throughput of a NoC as well as lack of cache coherency between the cores, makes them very similar to parallel HPC clusters. However they are fabricated inside a much smaller space while consuming much less energy. In order to provide inter-process communication, manycore HPC applications take advantage of different MPI libraries which are ported to these environments. However, porting of MPI communication libraries to a specific manycore platform, without tailoring the design of communication primitives to the underlying architecture, can lead to non-optimal performance.

The Intel Single-Chip Cloud Computer (SCC) is an example of a message-passing manycore chip [52] that resembles an HPC cluster. It integrates 24 2-core tiles on a single chip connected by a high-performance 2D-mesh NoC. Each tile has its own private memory, hence there is no coherency among the caches of different cores. It is provided with on-chip low-latency memory buffers, called *Message Passing Buffers* (MPB), physically distributed across the tiles. *Remote Memory Access* (RMA) to these MPBs allows fast inter-core communication using one-sided *put* and *get* primitives. Several works study the implementation of point-to-point communications on the Intel SCC, but only little attention has been paid to the implementation of collective operations.

In this chapter, we investigate a high-performance implementation for the most useful MPI collective operation, *i.e.* broadcast, on a message-passing manycore chip, *i.e.* the Intel SCC. The broadcast operation allows one process to send a message to all processes in the application. Considering the SPMD paradigm, *e.g.* MPI applications, the broadcast operation is executed by having all processes in the application call the communication function with matching arguments: the sender calls the *broadcast* function with the message to broadcast, while the receiver processes call it to specify the reception buffer. We focus on understanding how to exploit the on-chip RMA-based communication to come up with a high-performance broadcast algorithm.

Contributions of this chapter include:

- Identifying contention sources on the Intel SCC

- Coming up with a new contention-aware broadcast algorithm based on on-chip RMA

- Evaluating the new algorithm against existing solutions and confirm its significant gains

#### 1.4.2 High-performance map

Manycore chips can be seen as ordinary computing platforms to run the general-purpose applications, where a global operating system abstracts away the architectural complexities from the mainstream programmer. Traditional kernel data structures, located on a shared address space, have been shown to be an important performance bottleneck for the operating systems designed for these environments [23]. The main performance penalties come from contention on the locks as well as unnecessary costs of cache coherency. These costs can increase linearly with the grow in number of cores.

In order to avoid the scalability issues of shared kernel data structures, several manycore operating systems prototypes [16, 109, 65] consider operating systems as a distributed system where different entities communicate with each other using explicit message passing, therefore avoiding sharing data in a shared address space. In a message-passing system, partitioning and replication are the two main approaches to improve the throughput of concurrent data structures [36]. Using partitioning, a data structure is partitioned among a set of servers that answer clients requests. Using replication, each client has a local copy of data structure in its private memory and replicas maintain their consistency by exchanging messages amongst themselves. Both strategies have been considered in recent message-passing operating systems for manycores, but performance comparisons are lacking.

Among different data structures, maps are heavily used in many systems including operating system kernels [60]. Their performance is often crucial to the operating systems and have been shown to be an important performance bottleneck [16, 109]. Implementation of a map can benefit from both partitioning and replication: since operations on different keys are independent, maps are easily partitionable [19]; and because a large majority of operations are usually lookup operations [14], replication can help handling a large number of local lookup requests concurrently.

In this chapter, we present a performance comparison of replication and partitioning for the implementation of strongly-consistent concurrent maps in message-passing manycores. Note that existing studies made in distributed message-passing systems are only of little help because the high performance of NoCs provides a completely different ratio between computation and communication costs compared to large scale distributed systems.

Contributions of this chapter include:

- Devising different strongly-consistent concurrent map algorithms to represent the design space of partitioning and replication

- Coming up with a performance model to be able to compare different algorithms independently of their underlying architecture

- Evaluating our algorithms using our model under different assumptions and settings and showing that, under strong consistency, replication can outperform partitioning only in a narrow domain

# 2 High-Performance Broadcast

**Publication:** D. Petrovic, O. Shahmirzadi, T. Ropars, and A. Schiper. High-Performance RMA-Based Broadcast on the Intel SCC. In 24th ACM Symposium on Parallelism in Algorithms and Architectures (SPAA), Pittsburg, PA, USA, June 2012.

Manycore environments could be seen as HPC clusters, providing a high degree of parallelism with much lower energy consumption. Performance of HPC applications is directly affected by efficiency of collective operations, such as broadcast. The Intel Single-Chip Cloud Computer (SCC) is a prototype of a message-passing manycore chip. It offers the ability to move data between on-chip Message Passing Buffers (MPB) using Remote Memory Access (RMA). In this chapter, we study how to make use of the MPBs to implement an efficient broadcast algorithm for the SCC. We propose *OC-Bcast* (*On-Chip Broadcast*), a pipelined *k*-ary tree algorithm tailored to exploit the parallelism provided by on-chip RMA. Experimental results show that, compared with the state-of-the-art solutions, OC-Bcast attains almost three times better throughput, and improves latency by at least 27%. These performance gains highlight the benefits of exploiting hardware features of the target platform: Our broadcast algorithm take direct advantage of RMA, unlike the other broadcast algorithms based on a higher-level send/receive interface.

# 2.1 Introduction

The Intel Single-Chip Cloud Computer (SCC) is an example of a message-passing manycore chip [52]. The SCC integrates 24 2-core tiles on a single chip connected by a 2D-mesh NoC. It is provided with on-chip low-latency memory buffers, called *Message Passing Buffers* (MPB), physically distributed across the tiles. *Remote Memory Access* (RMA) to these MPBs allows fast inter-core communication.

The natural choice to program a high-performance message-passing system is to use Single Program Multiple Data (SPMD) algorithms. The Message Passing Interface (MPI) [80] is the *de facto* standard for programming SPMD HPC applications. MPI defines a set of primitives for

point-to-point communication, and also defines a set of collective operations, *i.e.* operations involving a group of processes. Several works study the implementation of point-to-point communications on the Intel SCC [104, 90, 85], but only little attention has been paid to the implementation of collective operations. This chapter studies the implementation of collective operations for the Intel SCC. It focuses on the broadcast primitive (*one-to-all*), with the aim of understanding how to efficiently leverage on-chip RMA-based communication. Note that the need for efficient collective operations for manycore systems, especially the need for efficient broadcast, goes far beyond the scope of MPI applications, and is of general interest in these systems [99].

We are investigating the implementation of efficient broadcast algorithms for a message-passing manycore chip, such as the Intel SCC. The broadcast operation allows one process to send a message to all processes in the application. Considering the SPMD paradigm, *e.g.* MPI applications, the broadcast operation is executed by having all processes in the application call the communication function with matching arguments: the sender calls the *broadcast* function with the message to broadcast, while the receiver processes call it to specify the reception buffer.

To take advantage of on-chip RMA, we propose OC-Bcast (On-Chip Broadcast), a pipelined k-ary tree algorithm based on one-sided communication: k processes get the message in parallel from their parent to obtain a high degree of parallelism. The degree of the tree is chosen to avoid contention on the MPBs. To provide efficient synchronization between a process and its children in the tree, we introduce an additional binary notification tree. Double buffering is used to further improve the throughput.

We confirm the gains of our broadcast algorithms through experiments. The comparison of OC-Bcast with the RCCE\_comm binomial tree and *scatter-allgather* algorithms based on two-sided communication shows that: (i) our algorithm has at least 27% lower latency than the binomial tree algorithm; (ii) it has almost 3 times higher peak throughput than the *scatter-allgather* algorithm. These results clearly show that collective operations for message-passing manycore chips should be based on one-sided communication in order to fully exploit the hardware resources. The main reason is that OC-Bcast reduces the amount of data moved between the off-chip memory and the MPBs on the critical path.

To sum up, contributions of this chapter include:

• *Identifying contention sources on the Intel SCC*: we identify three possible sources of contention on this platform, which include the NoC mesh, the off-chip memory and the MPBs. Our evaluations show that at the current scale, excessive load on the network links and on the off-chip memory do not degrade the performance. However evaluations show that more than a certain number of cores accessing the same MPB at the same time can create measurable contention. In our algorithms, we take into account this property to limit the number of cores who access the same MPB simultaneously.

- Coming up with a new contention-aware broadcast algorithm based on on-chip RMA: to exploit the on-chip RMA, we propose a pipelined *k*-ary tree algorithm based on one-sided communication where *k* processes get the message in parallel from their parent's MPB to obtain a high degree of parallelism. The degree of the tree is chosen to avoid contention on the MPBs. To provide efficient synchronization between a process and its children in the tree, we introduce an additional binary notification tree. Double buffering technique is added to further improve the throughput.

- Evaluating the new algorithm against existing solutions and confirm its significants gains: to confirm the benefits of our algorithm, we compare its latency and throughput against the best existing solutions through experiments. Our results show that our algorithm has at least 27% lower latency as well as almost 3 times higher peak throughput than the state-of-the-art solutions. These results clearly show that design of collective operations for message-passing manycore chips should take into account the specific hardware features of the target architecture to achieve optimal performance.

This chapter is structured as follows. In Section 2.2 we describe the architecture and the communication features of our testbed architecture. Section 2.3 presents assumptions and goal of this chapter. Section 2.4 is devoted to our RMA-based broadcast algorithm. Experimental evaluations on our testbed architecture are presented in Section 2.5. Finally related work are discussed in 2.6.

# 2.2 The Intel SCC

The SCC is a general-purpose manycore prototype developed by Intel Labs. We consider this platform as the testbed of our studies in this part. In this section we describe the SCC architecture and inter-core communication.

#### 2.2.1 Architecture

The cores and the NoC of the SCC are depicted in Figure 2.1. There are 48 Pentium P54C cores, grouped into 24 tiles (2 cores per tile) and connected through a 2D mesh NoC. Tiles are numbered from (0,0) to (5,3). Each tile is connected to a router. The NoC uses high-throughput, low-latency links and deterministic virtual cut-through X-Y routing [54]. Memory components are divided into (i) message passing buffers (MPB), (ii) L1 and L2 caches, as well as (iii) off-chip private memories. Each tile has a small (16KB) on-chip MPB equally divided between the two cores. The MPBs allow on-chip inter-core communication using RMA: each core is able to read and write in the MPB of all other cores. There is no hardware cache coherence for the L1 and L2 caches. By default, each core has access to a private off-chip memory through one of the four memory controllers, denoted by *MC* in Figure 2.1. The off-chip memory is physically shared, so it is possible to provide portions of shared memory by changing the default configuration. However we view the SCC as a pure message-passing platform. In

Figure 2.1: SCC architecture

addition, an external programmable off-chip component (FPGA) is provided to add new hardware features to the prototype.

#### 2.2.2 Inter-core communication

To leverage on-chip RMA, cores can transfer data using the one-sided *put* and *get* primitives provided by the RCCE library [102]. Using *put*, a core (a) reads a certain amount of data from its own MPB or its private off-chip memory and (b) writes it to some MPB. Using *get*, a core (a) reads a certain amount of data from some MPB and (b) writes it to its own MPB or its private off-chip memory. The unit of data transmission is the cache line, equal to 32 bytes. If the data is larger than one cache line, it is sequentially transferred in cache-line-sized packets. During a remote read/write operation, each packet traverses all routers on the way from the source to the destination. The local MPB is accessed directly or through the local router<sup>1</sup>. Cores are also able to notify each other using inter-process interrupts (IPI).

# 2.3 Assumptions and Goal

The study assumes a fault-free manycore architecture where a large set of single-threaded cores are connected through a network on chip. We assume that each core executes a single thread and that threads do not migrate between cores. Cores have their own on-chip private memory and can only communicate through message passing. Communication channels are asynchronous and FIFO. Messages are composed of a set of words and can have various size.