# 3D Integrated Architectures for Microelectronic Two-Phase Flow Cooling Applications

#### THÈSE Nº 6323 (2014)

PRÉSENTÉE LE 4 SEPTEMBRE 2014

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE TRANSFERT DE CHALEUR ET DE MASSE

PROGRAMME DOCTORAL EN ENERGIE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Yassir MADHOUR

acceptée sur proposition du jury:

Prof. J. A. Schiffmann, président du jury Prof. J. R. Thome, Dr B. Michel, directeurs de thèse Prof. D. Atienza Alonso, rapporteur Prof. G. P. Celata, rapporteur Prof. B. Wunderle, rapporteur

## Acknowledgements

I had never planned on pursuing a PhD title. The "plan" was to obtain my Master's degree, secure a hopefully interesting job in the industry and move on with my career. But one can never plan too much, for sometimes lifetime opportunities surprise us. That was the case when Professor John Thome and Dr. Bruno Michel offered me to stay at IBM Research in Zürich for the next 4 and something years. I had previously thoroughly enjoyed working with the Advanced Thermal Packaging Team (now the Advanced Micro Integration team) within IBM Research, during my six months diploma thesis, so the decision was not a difficult one, especially given the nature of the project: the construction of the first worldwide three-dimensional arrangement of silicon chips, each with its own embedded thermal management system. Sounds like a challenge.

A challenge that would not have existed nor could have been surmounted without a very large team. Let me start by offering my sincerest gratitude to my thesis supervisor, Professor John Richard Thome. Professor Thome has, ever since my first bachelor-level semester project in 2007, offered me chances to expand my horizons through multiple projects involving heat transfer, including the latest one, CMOSAIC, a Swiss Nano-Tera project that funded my research between 2010 and 2014 and for which I am very grateful. Professor Thome's motivation to always put the Laboratory of Heat and Mass Transfer (LTCM) on the map and be amongst the best is infectious, and guided me through my thesis years. He was my mentor during my studies, my mentor during my thesis and always had sound advice even when discussing my future career options. To him I am eternally grateful.

My sincerest gratitude is also bestowed upon my co-thesis supervisor and manager at IBM Research, Dr. Bruno Michel. With Prof. Thome, he opened the IBM gates to me, and allowed me to become a much better engineer by working under him, within his team and with all the other IBMers. He is one of the few people I dare call visionary, in his will of expanding IBM activities beyond computer hardware and software. I wish him all the luck and continued success for his multiple ongoing revolutionary projects.

I would like to especially thank Dr. Thomas Brunschwiler for introducing me to the world of Electronic Packaging. Thomas is one of those people who make you want to become a better scientist. His thirst for knowledge is amazing. He was not only my mentor at IBM but also a great friend. Through him I was able to travel to international packaging conferences and meet with some of the brightest in the business, and this thesis could never have happened without his fantastically smart input. Thomas, thank you so much!

Speaking of people without whom this work could not have been possible, let me deeply thank my friend and colleague Michael Zervas, who "suffered" with me the creation of the Through-Silicon-Vias. Michael thank you for your patience and dedication and for all the trips you had to make to Zurich by car to visit me. Looking back, it was enormous fun!

Special thanks also to Dr. Gerd Schlottig, for his collaboration, for teaching me about fracture mechanics and for all the philosophical discussions about family and food. I would also like to thank Stephan Paredes, for his engineering input and for always staying very late at work to help me set up my experiments, Dr. Chin Lee Ong for all the two-phase flow debates and his help during my experiments, and Dr. Arvind Sridhar for his friendship and for taking over the Movie Club at IBM. I would be remiss of course if I did not extend my appreciation to all the members of the AMI team, old and new, Dr. Patrick Ruch, Dr. Sarmenio Saliba, Dr. Brian Burg, Dr. Ingmar Meijer, Jonas Zürcher, Dr. Werner Escher, Dr. Adrian Renfer and Dr. Timo Tick. Thank you all for all the passionate discussions during 4 years worth of lunchtimes and coffee breaks.

Since a big part of this work was carried out in the clean room environment at the BRNC Nanotechnology Center on the IBM Research site in Rüschlikon (Zürich), I had the opportunity to work and learn from a number of exceptional people, some of them I would like to mention. Enormous thanks to Ute Drechsler, who basically taught me everything about MEMS microfabrication techniques, and without whom, I am convinced, the entire Science & Technology department at IBM Research would only partially function. Huge thank you to Martin Witzig, now retired, who taught me everything about flip-chip bonding, and who is the kindest and most patient person. Big thank you also to Ralph Heller for his help with PCB packaging and wire-bonding, Richard Stutz for setting up the electroplating baths, Dr. Yuksel Temiz and Steffen Reidt for their assistance with mask writing, Andreas Bischof for his help with the Focused Ion Beam, Lukas Czornomaz for his knowledge of the EDX analysis technique, Daniel Jubin for his help with the interferometer, Dr. Nicolas Daix for the improved sample polishing technique, Chander Sharma for his assistance with ANSYS modeling, Daniele Caimi for the automated wafer dicing process, Dr. Hesham Ghoneim for his help with SEM imaging and most importantly his friendship, and last but not least Dr. Walter Riess for so efficiently managing our Science and Technology department at IBM and for always taking an interest in all his Pre-Docs' projects.

I would also like to sincerely thank my friends and colleagues at the LTCM laboratory and STI department on the EPFL campus. Even though I was not working on the same site, their availability and assistance never came short. All my gratitude goes to Dr. Brian D'Entremont, Dr. Jackson Braz Marcinichen, Dr. Eugene Van Rooyen, Dr. Jonathan Olivier, my mentor during my diploma thesis, Dr. Etienne Costa-Patry, Nicolas Lamaison and Peter Brühlmeier for his help with PCB design.

Being an almost unreasonably large cinephile, I could not resist but found a Movie Club here at IBM Research, within the already established and highly appreciated ZRL Hobby Club. I would like to thank all the people who allowed me to carry out my vision but also everybody who regularly attended the Movie Night events. Big thanks to Chris Sciacca and his Hobby Club team, Christophe Rossel, Catherine Trachsel, Heiko Wolf, Silvia Derks, Trudi Ender, Christa and Arnold Schwyzer and Roy Cidecyan.

Last but not least, a very special thank you to Dr. Severin Zimmermann, my "office wife" at IBM. Going to work everyday with him in the office, all the discussions about work, movies, football, hockey, video games and the Playstation 4 coming out and camping in front of a store all night in sub-zero temperatures to be the first ones to buy it, all these memories make the thesis one of the best times of my life. Thank you Severin!

I would also like to mention and immensely thank my friends, Faouzi, Thierry, Jérôme and all the people from the now defunct Streetconcept and from my hometown, Fribourg, for their constant presence and their ability to take my mind off of things and cheer me up whenever needed. Guys, you're the best!

Finally and most importantly, I would like to say how grateful I am for being surrounded by an amazing family. I am very grateful to my parents, for all the obvious reasons and for motivating and pushing me from the start of my studies at EPFL when I still had doubts about my career. I would also like to thank my sister, for her love and support in my everyday life, and for constantly reminding me that not everything in life is about Science. I would like to extend my gratitude to my wife, Dominique, my other half, for being the most wonderful, kind, generous, calm and loving person I have ever met. She is my source of love, comfort and happiness, and I could not possibly be where I am now nor could I envision my life without her.

And about my newborn daughter Lara, what can I say... Lara I love you, and I hope someday you might flip through these pages to see what your old man was up to when he was young.

Zurich, June 5th, 2014

Yassir Madhour

## **Abstract**

Higher computational performance demands microchips with more and more cores and cache memory that communicate via long wires, consuming a lot of energy and generating a lot of heat. As a solution, three-dimensional (3D) stacking of integrated-circuit (IC) dies by vertical integration increases system density and package functionality. Area-array Through-Silicon-Vias (TSVs) reduce global interconnects lengths and signal delay times, resulting in a better performance and reduced energy consumption. Ongoing miniaturization of ICs increases chip-level power densities and together with vertical integration renders cooling a major challenge. Thus, the development of new chip cooling concepts is very important and therefore scalable interlayer cooling solutions for chip stacks need to be investigated. This thesis aims to show the feasibility of such a prototype for two-phase flow cooling applications. It starts by presenting a new concept for the integration of intra chip stack fluidic cooling structures, using a newly developed patterned thin-layer eutectic solder bonding technique for the stack assembly which is compatible with the fabrication constraints caused by the implementation of interlayer cooling. 5-layer chip stacks with embedded microchannels and high aspect ratio TSVs were successfully fabricated. Optical inspections demonstrated the proper bond line formation and electrical tests indicated the successful combination of TSVs with thin-layer solder interconnects. Mechanical shear tests showed the strength of the patterned thin-layer solder bond and an added solder ring-pad component to seal the electrically active pad from any conductive liquid coolant was experimentally implemented, resulting in strict design rules to avoid solder reflow instabilities. Secondly, this thesis proposes an innovative approach for electrical chip to substrate and chip to chip interconnects using solder balls and rails on a single chip for higher solder area fill factor that supports power delivery and heat removal for highperformance flip-chip-on-board as well as 3D stack applications. After establishing design and fabrication rules for these novel structures to avoid solder reflow instabilities, numerical results were obtained via surface energy minimization to predict solder shape after reflow with a deviation of less than 9%.

To optimize heat spreading and fluid flow using interlayer two-phase evaporative cooling within a multi-microchannel evaporator chip stack, a new thermal model and simulation method are presented to enable the study of ideal local heat load placement. The design used to test the model mimicked the actually built 3D chip stacks. This new model simultaneously solves heat and two-phase flow spreading effects, the latter due to the pressure drop's sensitivity to heat flux/vapor quality. Several heat load patterns were implemented and compared. Simulation results showed a strong effect of thermal spreading between the dies, since these have a small thermal resistance compared to the convective heat

transfer coefficient in the channels, which is effective in flattening thermal gradients from non-uniform heating within the chip stack.

Flow boiling of refrigerants 236fa and 1234ze (R236fa & R1234ze) were experimentally investigated within two different test sections. First-of-a-kind high pressure fluidic tests were successfully achieved within a 3D chip stack with interlayer cooling capabilities and high aspect ratio TSVs. However, fabrication defects and a scarce amount of TSV wafers rendered the heat transfer study within the chip stack impossible. Finally, pressure drop measurements and local junction temperatures were measured on a 2D silicon pin fin test section as a potential candidate for future 3D modules. A good cooling performance was demonstrated, with a junction temperature response of 40°C for a base heat flux of 66.6 W/cm². The observed high pressure drops were a result of the very small flow cross-sectional area.

#### Keywords

Electronic packaging, thermal management, 3D integration, chip stacking, solder bonding, microscale flow boiling, refrigerants.

## Résumé

L'empilement tri-dimensionnel de circuits intégrés de manière verticale permet d'augmenter la densité d'un système ainsi que la fonctionalité d'un paquet électronique. L'intégration verticale de puces à l'aide de Voies Traversant le Silicium (VTS) réduit la longueur des connections globales et par conséquent le délai du signal. D'un autre côté, la miniaturisation continue des puces a pour conséquence l'augmentation croissante de leur densité de puissance. Le développement de nouvelles techniques de refroidissement devient ainis crucial. Par conséquent, des techniques à échelle modifiable comme le refroidissement inter-couches doivent être étudiées. Cette thèse présente un nouveau concept pour l'intégration de refroidissement fluidique à l'intérieur même d'un empilement tridimensionnel de puces par l'intermédiaire de microcanaux usinés directement à l'arrière des puces, pour le management thermique à travers écoulements mono- ou biphasiques, en utilisant une technique de fine micro-soudure pour l'assemblage vertical des puces. Les résultats ont montré la fabrication fructueuse d'un empilement à 5 couches avec microcanaux fluidiques intégrés et VTS à rapport hauteur/largeur élevé. Des inspections optiques ont demontré la bonne formation du lien de soudure entre les puces et des analyses électriques ont indiqué la combinaison fructueuse de VTS avec la technique de fine microsoudure. Des tests de cisaillement méchaniques ont aussi démontré la force et durabilité de la fine couche de micro-soudure (16MPa). De plus, le design d'un anneau de soudure additionnel a été recherché dans le but d'isoler le plot de soudure principal, actif électriquement, d'un potentiel liquide de refroidissement conducteur. Des tests de refusion sur ces anneaux ont montré l'apparition d'accumulations locales de soudure. Il a été découvert que ces accumulations disparaissaient quand le rapport hauteur/ largeur de l'anneau (hauteur de la quantité de soudure déposée/ largeur de l'anneau) était maintenu endessous de 0.65, valeur critique observée expérimentalement. Additionnellement, cette thèse propose une approche innovative pour l'interconnection électrique entre 2 puces de silicium ainsi qu'entre une puce de silicium et un substrat en polymer. La potentielle coexistence de boules ainsi que de rails de soudure sur une seule et même puce, permettant la livraison de puissance et évacuation de chaleur pour paquets électroniques de haute performance à travers un taux de remplissage surfacique de soudure plus élevé, est discutée dans le travail qui suit. Après refusion, les géométries en rails peuvent parfois résulter d'une largeur maximale bien supérieure à leurs plots de soudure de base respectifs. De plus, il a été observé qu'un design imparfait du rail pouvait engendrer deux types d'instabilités : formation locale d'une boule de soudure et accumulation asymétrique de soudure le long du rail. Les expériences de refusion sur ces nouvelles géométries ont été complétées par des résultats numériques obtenus via une technique de minimisation de surface d'énergie. Une qualité de prédiction avec déviations inférieures à 9% a été identifiée, indicant ainsi l'applicabilité de cette technique au design de futures geométries de soudure. Au final, les résistances thermiques d'interfaces boules et rails ont été mesurées et comparées et il s'est avéré que l'interface rail, avec un taux de remplissage surfacique de soudure de 57%, possède une résistance thermique d'interface 7 fois plus petite.

Cette thèse introduit aussi un nouveau modèle thermique et une méthode de simulation permettant l'étude en profondeur du placement idéal de charges calorifiques à l'intérieur d'un module à puces empilées avec système de refroidissement intégré (microcanaux), afin d'optimiser la diffusion de chaleur et le passage du fluide tout en utilisant une technique de refroidissement biphasique par évaporation, à l'intérieur d'un design identique à celui de l'empilement de puces fabriqué et mentionné plus haut. Ce nouveau modèle inclus la résolution simultanée de la diffusion calorifique et fluidique, cette dernière étant due à la sensibilité de la perte de charge au flux de chaleur ainsi qu'au titre. Plusieurs dispositions de charges calorifiques ont été ainsi implementées et comparées. Les résultats de simulation ont montré un effet non négligeable de la diffusion thermique entre les puces empilées, étant donné que celles-ci sont dotées d'une petite résistance thermique comparé au coefficient de transfert de chaleur par convection aux microcanaux, ce qui aide à atténuer une potentielle disposition non uniforme de charges calorifiques à l'intérieur du module 3D.

Finalement, des études expérimentales ont été conduites sur l'évaporation des réfrigérants 236fa et 1234ze (R236fa & R1234ze) à l'intérieur de deux sections de test différentes, respectivement un module tri-dimensionnel de puces et une puce en silicium avec micro-structures intégrées. Des mesures de pertes de charge et de coefficients de transfert de chaleur ont été effectuées dans le but d'améliorer le design de ces micro-échangeurs de chaleur et de faciliter leurs implémentations respectives pour les futures modules tri-dimensionnels de puces commercialisés.

#### Mots-clés

Packaging électronique, management thermique, intégration 3D, empilement de puces, micro-soudure, évaporation de flux à échelle microscopique, réfrigérants.

## Contents

| Yassir MAI   | DHOURii                                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------------------|

| Acknowled    | lgementsii                                                                                                                |

| Abstract     | vi                                                                                                                        |

| Keywords     | vii                                                                                                                       |

| Résumé       | i)                                                                                                                        |

| Mots-clés    | )                                                                                                                         |

| List of Figu | resx\                                                                                                                     |

| List of Tab  | lesxxii                                                                                                                   |

| -            | Of the importance of vertical integration and thermal management for essor and memory chips in the semiconductor industry |

| 1.1          | Vertical integration                                                                                                      |

|              | 1.1.1 Motivation and importance [1]                                                                                       |

|              | 1.1.2 Enabling technologies                                                                                               |

| 1.2          | Thermal management of ICs                                                                                                 |

|              | 1.2.1 Importance, past and current concepts: from air to liquid cooling [16] [17]                                         |

|              | 1.2.2 Microscale flow boiling of refrigerants                                                                             |

|              | 1.2.3 Chip stacks and thermal management limitations                                                                      |

|              | 1.2.4 Interlayer cooling: a scalable solution                                                                             |

| 1.3          | Thesis outline and objectives of this work11                                                                              |

| Chapter 2    | Patterned solder bonding for die-to-die attachment: novel structures 13                                                   |

| 2.1          | Introduction: inter-tier thermal management                                                                               |

| 2.2          | Electrodeposition and reflow of thin eutectic 3.5Ag96.5Sn12                                                               |

|              | 2.2.1 Thin film micro C4s14                                                                                               |

| 4.1       | Nomenclature                                                                             | 73 |

|-----------|------------------------------------------------------------------------------------------|----|

| -         | Modeling of three-dimensional multi-cavity dielectric evaporative sfer                   |    |

| 3.3       | Conclusions                                                                              |    |

| 2.2       | 3.2.5 Pressure drop results and discussion                                               |    |

|           | 3.2.4 Operating conditions                                                               |    |

|           | 3.2.3 Test facility                                                                      |    |

|           | 3.2.2 Design, fabrication & assembly                                                     |    |

|           | 3.2.1 Introduction & purpose                                                             |    |

| 3.2       | Experimental investigation – 3D test vehicle                                             |    |

| 2.2       | 3.1.7 Results and discussion                                                             |    |

|           | 3.1.6 Data reduction                                                                     |    |

|           | 3.1.5 Operating conditions                                                               |    |

|           | 3.1.4 Test facility                                                                      |    |

|           | 3.1.3 Test section                                                                       |    |

|           | 3.1.2 Introduction                                                                       |    |

|           | 3.1.1 Nomenclature                                                                       |    |

| 3.1       | Experimental investigation: 2D silicon pin fin test vehicle                              |    |

| Chapter 3 | Intra chip stack dielectric evaporative flow                                             |    |

| 2.5       | Conclusions                                                                              |    |

|           | 2.4.2 Thermal resistance of high fill factor structures                                  |    |

|           | 2.4.1 Thin film micro C4s for 3D chip stacking                                           |    |

| 2.4       | Experimental campaign: flip-chip bonding of eutectic 3.5Ag96.5Sn                         |    |

|           | 2.3.4 Modeling vs. experiments                                                           | 26 |

|           | 2.3.3 Solder shape: engineering the dimensions                                           | 24 |

|           | 2.3.2 Surface minimization method                                                        | 23 |

|           | 2.3.1 Motivation and implementation                                                      | 21 |

| 2.3       | Investigation of high fill factor solder patterns for power delivery and removal support |    |

|           | 2.2.3 Sealing rings                                                                      | 19 |

|           | 2.2.2 Rails                                                                              | 19 |

|        | 4.2    | Design framework: CMOSAIC chip stack package                                                                 | ′4 |

|--------|--------|--------------------------------------------------------------------------------------------------------------|----|

|        | 4.3    | Method of simulation7                                                                                        | '4 |

|        | 4.4    | Simulation cases                                                                                             | '8 |

|        | 4.5    | Results8                                                                                                     | 30 |

|        | 4.6    | Conclusions9                                                                                                 | 0  |

| Chap   | ter 5  | Conclusions and outlook 9                                                                                    | 13 |

|        | 5.1    | Thesis contributions and impact9                                                                             | 13 |

|        |        | 5.1.1 Solder bonding technology – novel structures9                                                          | 13 |

|        |        | 5.1.2 3D integrated chip stack with embedded cooling structures - fabrication, assembly and fluidic testing9 |    |

|        |        | 5.1.3 Modeling of three-dimensional heat and mass transfer in multi-cavity systems9                          |    |

|        | 5.2    | Looking into the Future9                                                                                     | )5 |

| Appe   | ndix A | A9                                                                                                           | 17 |

| Appe   | ndix E | В10                                                                                                          | 13 |

| Refe   | rences | s10                                                                                                          | )7 |

| List o | f scie | ntific publications11                                                                                        | .7 |

| Curri  | culum  | Nitae11                                                                                                      | 9  |

## List of Figures

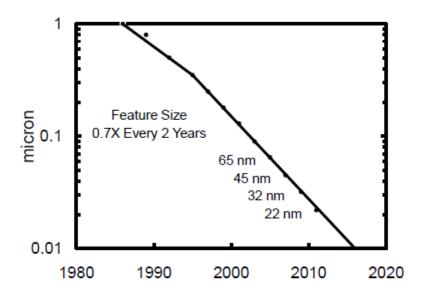

| Figure 1.1 Shrinking transistor dimensions [4]2                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

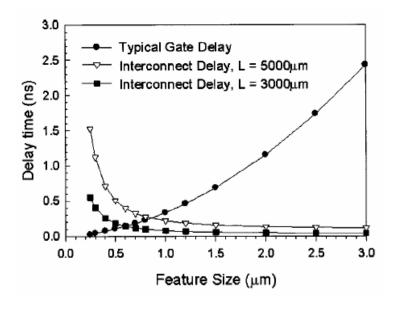

| Figure 1.2 Gate delay versus interconnect delay for shrinking technology nodes [5]                                                                                                                                                                                                                                |

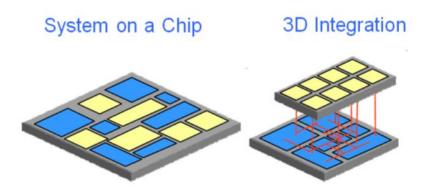

| Figure 1.3 Left: SoC with multiple processor cores and cache memories.  Right: Corresponding 3D stacked IC with considerably smaller area and shorter vertical interconnects [6]                                                                                                                                  |

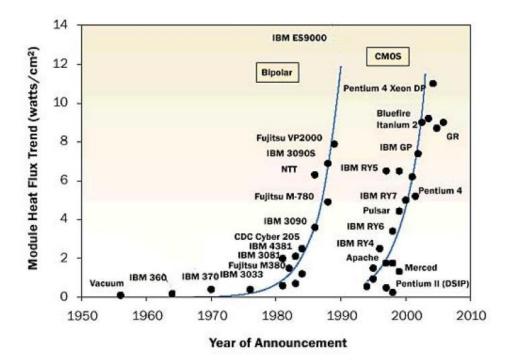

| Figure 1.4 Module and chip heat flux densities for IBM chips, from the 1950s until early 2000s [22]. According to IBM Zürich Research, module heat fluxes between 0 and 14 W/cm² roughly correspond to chip heat fluxes between 0 and 80 W/cm², knowing that these chips occupy around 7/38th of the module area. |

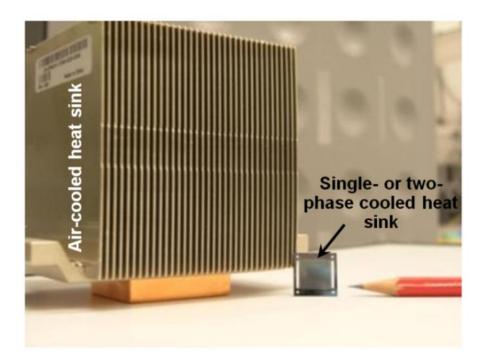

| Figure 1.5 General size comparison between air-cooled heat sinks and single- or two-phase cooled heat sinks (Source: IBM Research, Zürich)6                                                                                                                                                                       |

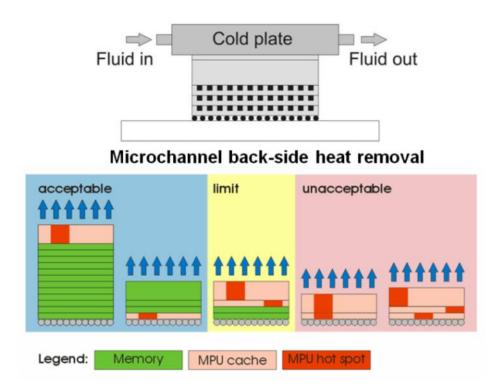

| Figure 1.6 Chip stack configuration with acceptable, close to the limit and unacceptable junction temperatures with backside water heat removal.  Maximum allowable MPU junction temperature is 80°C, acceptable memory temperature limit is 95°C, and fluid inlet temperature is 20°C [50]                       |

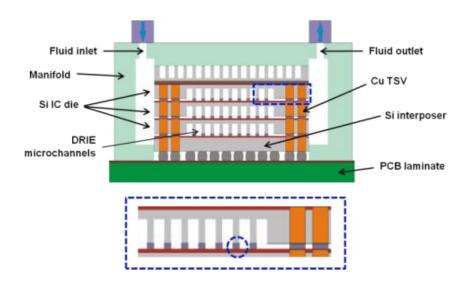

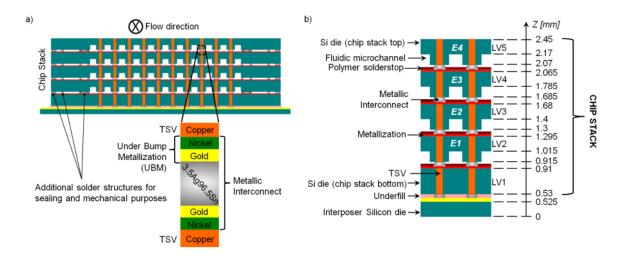

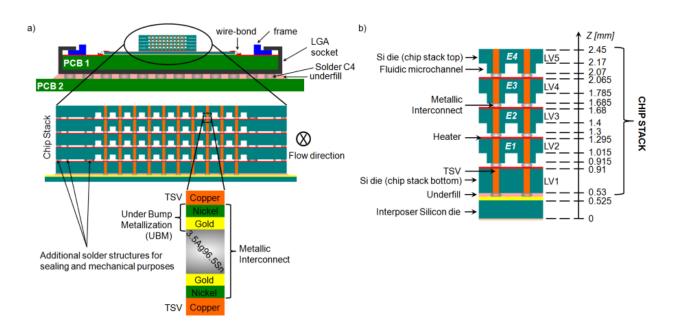

| Figure 2.1 Patterned thin film solder bond concept for mechanical and electrical connection in 3D chip stacks with integrated cooling capabilities. The highlighted part shows the needed patterned thin film solder interconnect                                                                                 |

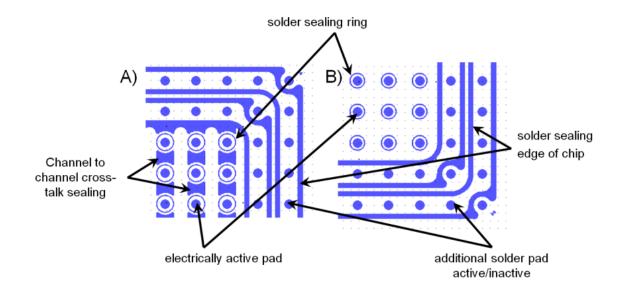

| Figure 2.2 Additional solder structures needed for a scalable cooling solution (top view on single die, blue is solder). A) Silicon-etched microchannels as heat removal structures. B) Silicon pin fins as heat removal structures.                                                                              |

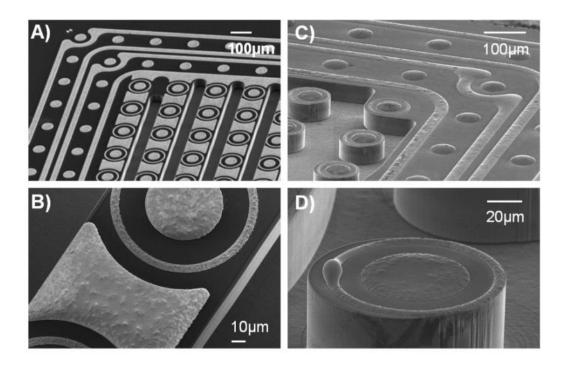

| Figure 2.3 Scanning Electron Microscopy (SEM) real-life images corresponding to the solder concepts presented in Figure 2.2. A & B) With silicon chip-embedded microchannels. C & D) With silicon chip-embedded pin fins                                                                                          |

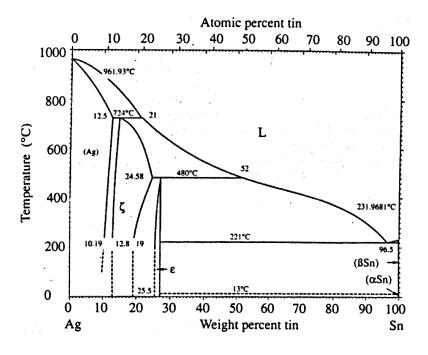

| Figure 2.4 Silver Tin alloy phase diagram [58]15                                                                                                                                                                                                                                                                  |

| Figure 2.5 Thin film solder fabrication process                                                                                                                                                                                                                                                                   |

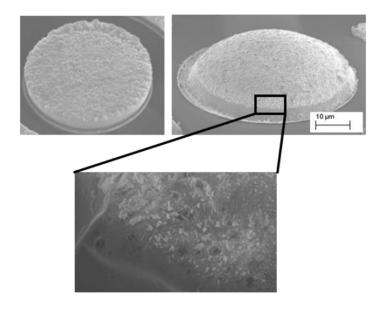

| Figure 2.6 <i>Left:</i> plated ( $8\mu m$ -thick) AgSn solder thin film pad ( $50\mu m$ diameter). <i>Middle and bottom:</i> after fluxless reflow at 265°C, with tin oxide layer on the surface                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.7 FIB cross-section of fluxless reflowed solder bump. <i>Left:</i> top view of solder pad with oxide layer. <i>Right:</i> corresponding cross-section17                                                                                                                                                                                                                                                          |

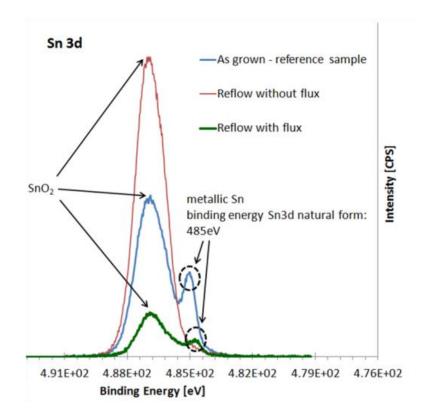

| Figure 2.8 Tin (Sn3d) XPS measurements for plated die (after deposition, blue), reflowed die without flux (ambient atmosphere, red) and reflowed die with flux treatment (green).                                                                                                                                                                                                                                         |

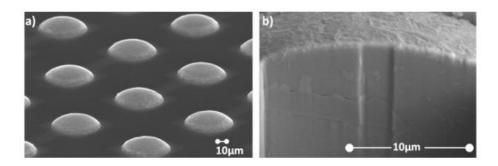

| Figure 2.9 a) Flux-reflowed solder pads, 58μm in diameter and 12μm thick. b) FIB cross-section of a reflowed solder bump18                                                                                                                                                                                                                                                                                                |

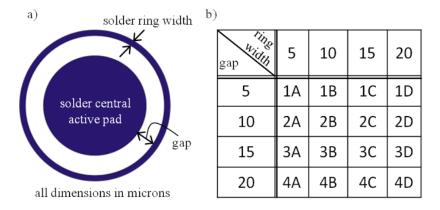

| Figure 2.10 Solder fluidic sealing concept. a) Design and geometry. b) Range of studied combinations of parameters and their different designations                                                                                                                                                                                                                                                                       |

| Figure 2.11 a) Solder ring pads after electroplating. b) Ring pad structures 3A to 3D after reflow on hot plate and cleaning20                                                                                                                                                                                                                                                                                            |

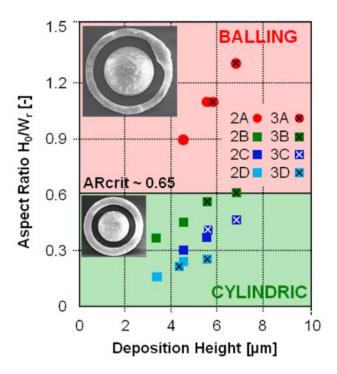

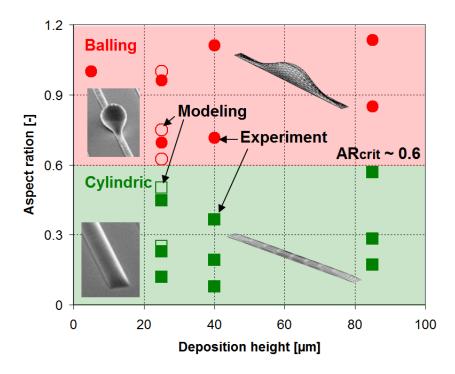

| Figure 2.12 Experimental categorization of ring pad solder shapes after reflow for varying deposition heights $H_0$ and ring aspect ratios (deposition height $H_0$ to ring width $W_r$ ). Dome- (squares) and ball-(circles) like shapes were identified below and above the critical aspect ratio of 0.65. Inserts depict SEM photographs                                                                               |

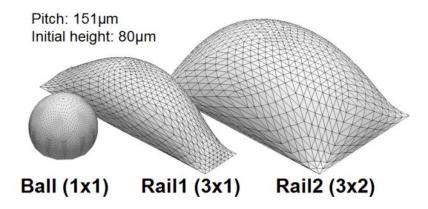

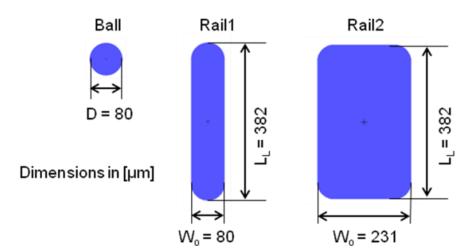

| Figure 2.13 Isometric view of distinct solder shapes after reflow resulting from circular and rectangular pads as predicted by numerical modeling (see § 2.3.2). The initial height of 80 $\mu$ m corresponds to the solder height after electrodeposition. The AxB metric indicates the size of the pad in unit cells with a pitch of 151 $\mu$ m in X and Y direction. The width or diameter of the pads is 80 $\mu$ m. |

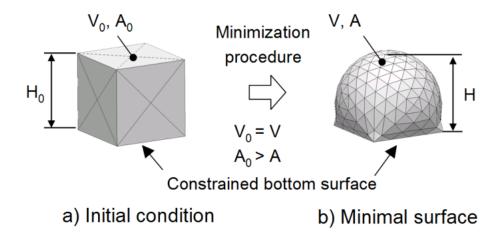

| Figure 2.14 (a) Initial volume defined in the Surface Evolver, representing the solder after electroplating. (b) Geometry with minimal surface for a constant volume and constrained bottom surface, considering surface tension only.                                                                                                                                                                                    |

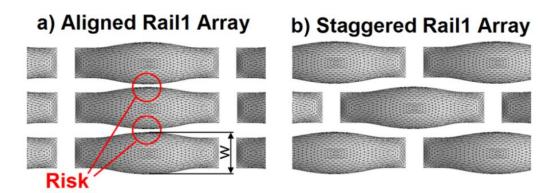

| Figure 2.15 Top view of solder arrays with Rail1 unit cells (Figure 2.13) in aligned (a) and staggered (b) arrangement. The minimal distance between rails is 3 times larger in case of (b) with an accordingly reduced shorting risk                                                                                                                                                                                     |

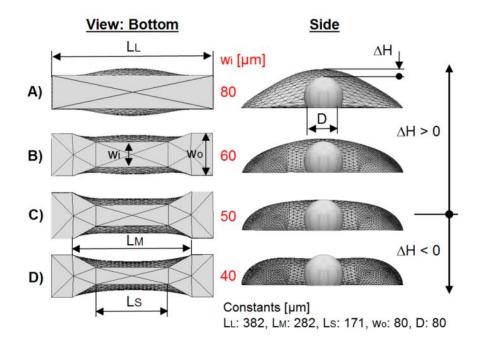

| Figure 2.16 Bottom (left) and side (right) view of Bone Rails at varying bone width $w_i$ . The height difference $\Delta H$ with respect to a Ball is depicted. The Ball height is smaller in case (a) and (b), but equal for (c). A                                                                                                                                                                                     |

| case (d)26                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.17 Top view of pad and solder geometry for different solder shapes: Ball, Rail1, and Rail2. The patterns were arranged across their respective chips in arrays with a pitch of 151 $\mu$ m (Ball, Rail1) and 302 $\mu$ m (Rail2)                                                                                                                                                                                                                       |

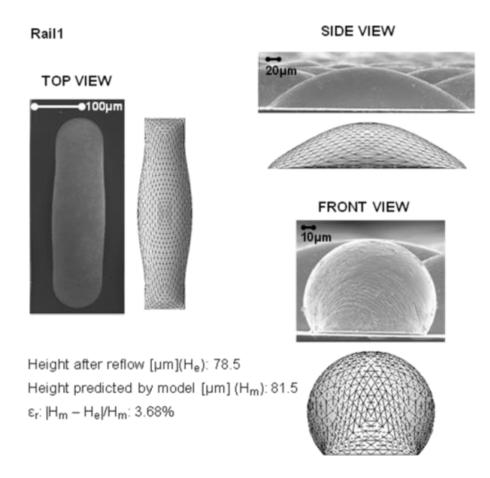

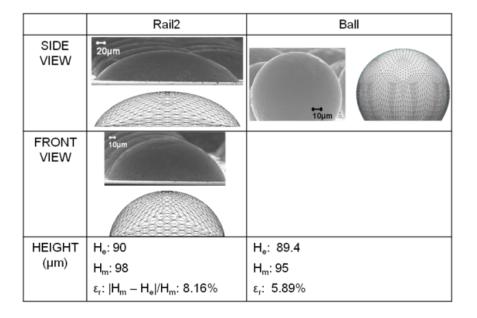

| Figure 2.18 Top, side and front view SEM photographs of Rail1 structure after reflow, with their corresponding Surface Evolver model view28                                                                                                                                                                                                                                                                                                                     |

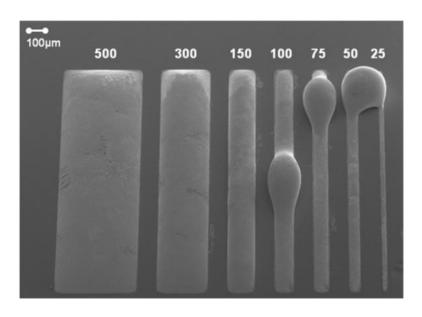

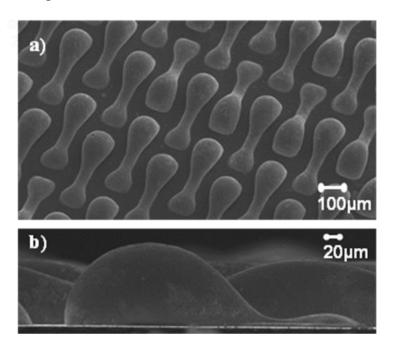

| Figure 2.19 SEM photograph of solder reflow shapes of 2 mm long rails with indicated varying widths in $[\mu m]$ , but equal initial solder height of 85 $\mu m$ . Local solder accumulation, called "Balling", occurs for lines below a critical line width of 100 $\mu m$ . Dome-shaped geometries result for wider rails.                                                                                                                                    |

| Figure 2.20 Experimental (full) and numerical (empty) categorization of solder shapes after reflow for varying deposition heights H0 and rail aspect ratios (AR) (deposition height H0 to rail width wo). Dome- (green squares) and ball- (red circles) like shapes were identified below and above the critical aspect ratio of 0.6. Inserts depict SEM photographs and Surface Evolver results.                                                               |

| Figure 2.21 Isometric (a) and side-view (b) SEM photographs depicting Asymmetric Solder Accumulation from Bone Rail pads after reflow in comparison with numerical, symmetric results presented in Figure 2.1631                                                                                                                                                                                                                                                |

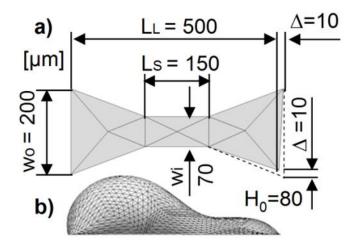

| Figure 2.22 (a) Asymmetric Bow Tie rail with an offset $\Delta$ of 10 $\mu$ m of the lower right corner. (b) Modeling result depicting Asymmetric Solder Accumulation as observed in the experiment (Fig. 9) for the pad geometry shown in (a)                                                                                                                                                                                                                  |

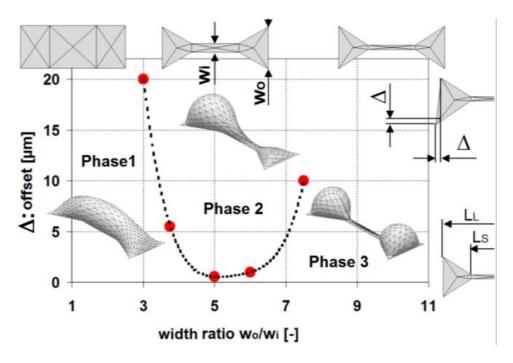

| Figure 2.23 Bow Tie Phase diagram depicting three reflow phases in the width ratio to offset plane. The red points and their interpolation (dashed line) were derived numerically and indicate the phase transition. Geometrical representations of the phases are shown as isometric inserts. The pad geometry variation along the different dimensions is depicted as well (Bow Tie dimensions [ $\mu$ m]: $L_L$ : 382, $L_S$ : 171, $W_O$ : 150, $H_O$ : 60) |

| Figure 2.24 Test vehicle description—chip stack package with silicon embedded heat transfer structures. a) Ensemble view of package with all components. b) Vertical cross-section describing the multiple layers and their respective thicknesses.                                                                                                                                                                                                             |

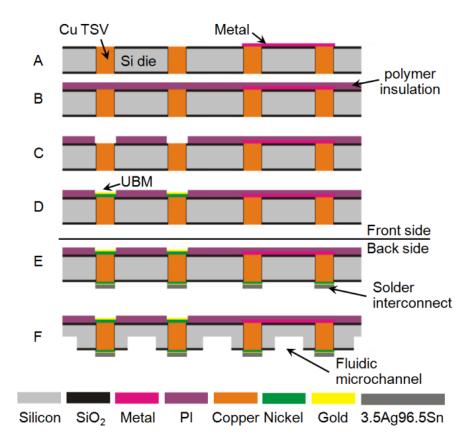

| Figure 2.25 Process integration flow for the fabrication of a middle die within the chip stack (LV2 to LV4, see Fig. 1b), after TSV implementation. 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

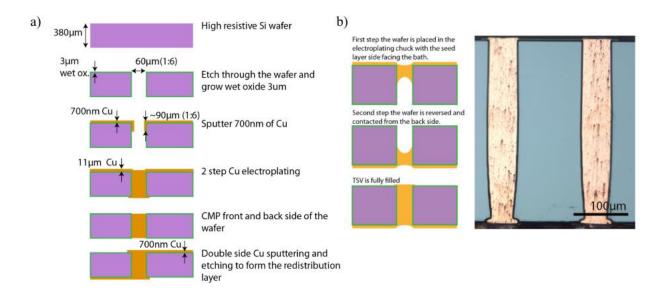

| Figure 2.26 a) Illustration of the TSV process flow. b) Illustration of the two-step TSV electroplating process with a cross-section of the reults35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

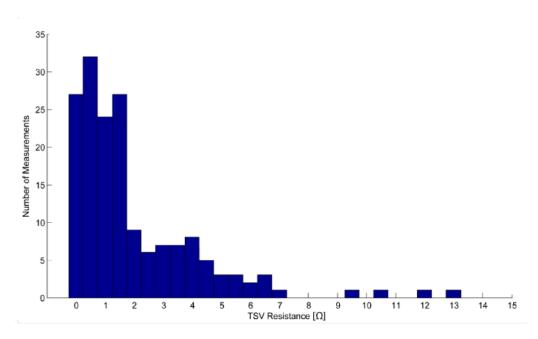

| Figure 2.27 Histogram of the calculated TSV resistance. Most of the TSVs have a value below $2\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

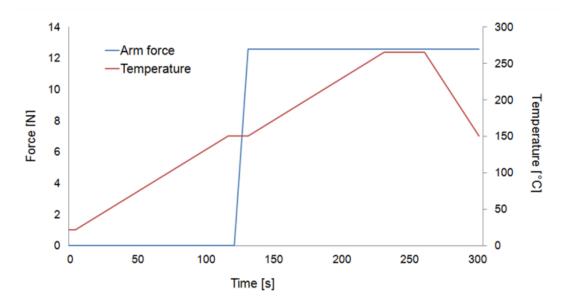

| Figure 2.28 Flip chip bonding (force-controlled reflow) process used for die-to-die bonding and chip stacking. In blue: force control. In red: temperature control for both chip and carrier side                                                                                                                                                                                                                                                                                                                                                                                                                                             |

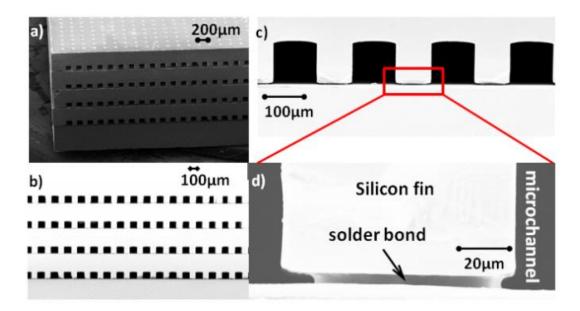

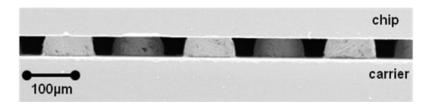

| Figure 2.29 a) Isometric view of a 5-layer chip stack (4 fluid cavities, 4 active layers with TSVs). b) Front view of $100X100\mu m$ fluidic microchannels. c) Zoom-in on cavities, fin thickness is $100\mu m$ . d) View of the die-to-die thin-layer eutectic solder bond ( $5\mu m$ ), the silicon fin as well as the fluidic microchannel.                                                                                                                                                                                                                                                                                                |

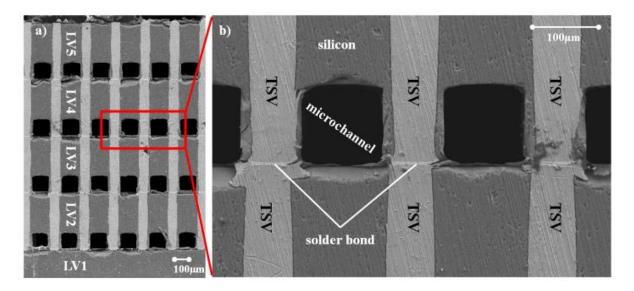

| Figure 2.30 a) Cross-section of the assembled chip stack. The LV1 to LV5 chips, the microchannels, the TSVs as well as the thin-layer solder bonds are all visible. b) Zoom-in on microchannels, TSVs and solder pads39                                                                                                                                                                                                                                                                                                                                                                                                                       |

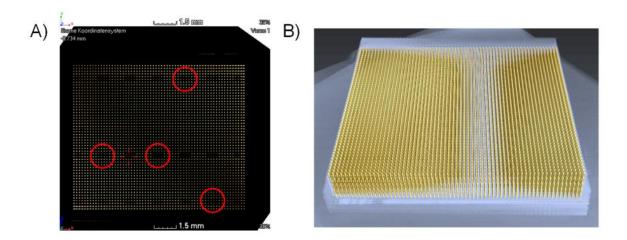

| Figure 2.31 X-ray tomography pictures on a fabricated chip stack. A) 2D top view of LV2 chip surface, showing uniform presence of solder interconnects. Highlighted "missing spots" are the locations of the hot spot heaters' electrical leads (design presented in § 3.2). B) 3D top view of chip stack showing the properly filled TSVs. Due to (already impressive) 8µm resolution, thin film solder interconnects are not visible. The author would like to thank Prof. Dr. Bernhard Wunderle (TU Chemnitz, Germany) as well as Marcus Hildebrandt (Fraunhofer ENAS, Germany) for their tremendous help in obtaining these photographs39 |

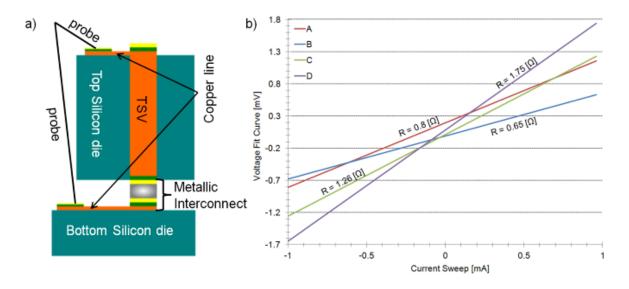

| Figure 2.32 a) Schematic of the 4-point DC Kelvin measurement for a single TSV plus thin-layer solder pad combination. b) DC current sweep (-1 [mA] to 1 [mA]) with corresponding voltage response to determine the resistance of a single TSV plus thin-layer solder pad combination. A and B as well as C and D designate similar daisy-chain locations measured on different samples and are representative values                                                                                                                                                                                                                         |

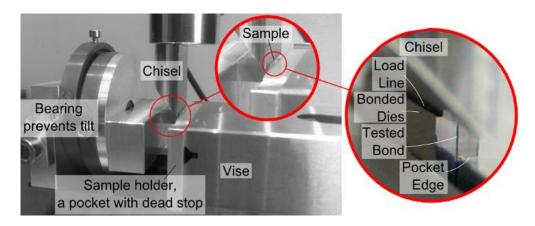

| Figure 2.33 Setup to shear test the thin-layer solder bonds41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

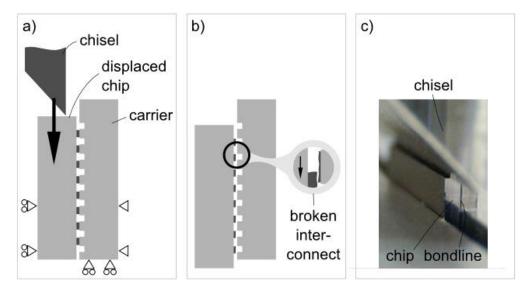

| Figure 2.34 a) Shear principle. b) Sheared state. c) Corresponding photo41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

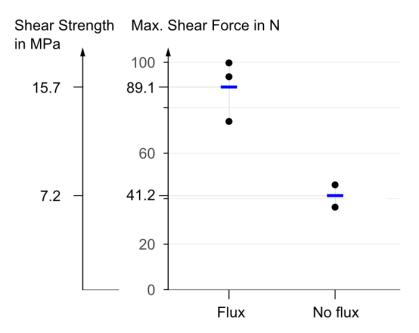

| Figure 2.35 Shear test results42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

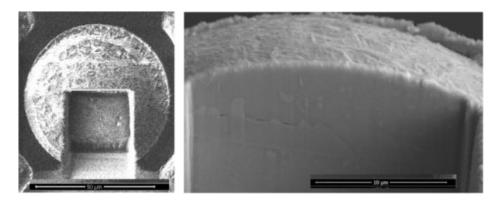

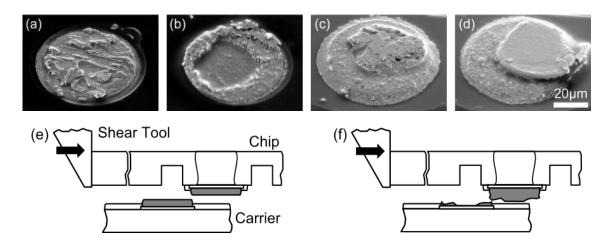

| Figure 2.36 Failure modes observed across the sheared carrier and chip (left to right). a) Ductile through solder (carrier side). b) Partial solder lift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (carrier side). c) Ductile through solder (chip side). d) Partial solder lift (chip side). All pad diameters are equal to 58µm. The schematics (e) and (f) describe the failure mode principle for each, ductile and partial solder lift                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

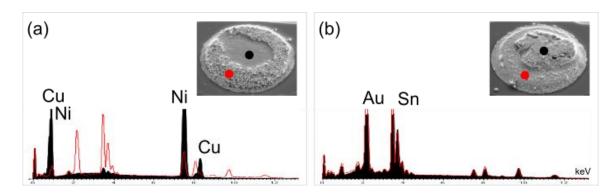

| Figure 2.37 EDX results of the different regions left behind after shearing: the partial solder lift (a) shows a clean separation between the solder components and the pad UBM metallization                                                                                                                                                                                                                                                                                                         |

| Figure 2.38 Front view SEM micrograph of a flip-chip bonded device using Rail1 structures                                                                                                                                                                                                                                                                                                                                                                                                             |

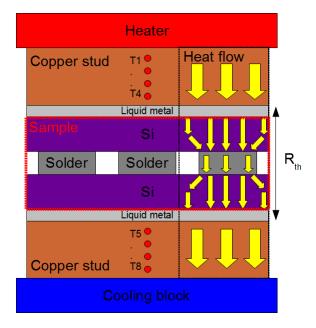

| Figure 2.39 Illustration of the bulk thermal tester. Heat is dissipated uniformly from the top copper stud into the specimen and finally out of the bottom copper stud. Thermal coupling from copper into the specimen is performed by a liquid metal interface. Temperature gradients are monitored with two pairs of four thermocouples to derive the copper stud surface temperature and the dissipated heat flux. The liquid metal interface resistance was determined in an upfront measurement. |

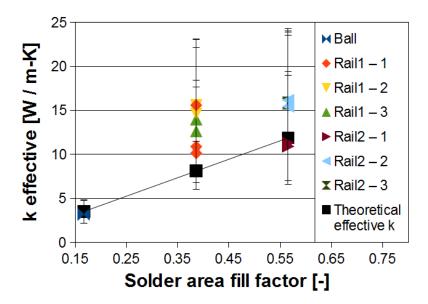

| Figure 2.40 Resulting bond-line effective thermal conductivity $k_{eff}$ of the Ball, Rail1 and Rail2 specimens at their solder area fill factor. Three different specimens were characterized and compared in case of the rail shapes. The trend of the measured results is compared with theoretical values derived from effective solder thermal conductivities, published in [71], and the solder area fill factors                                                                               |

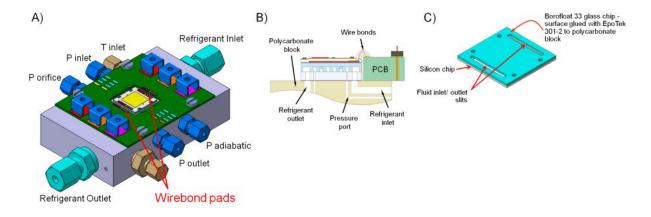

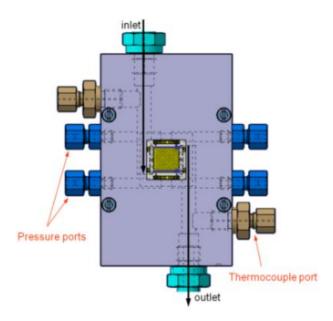

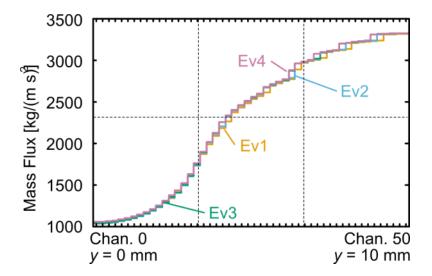

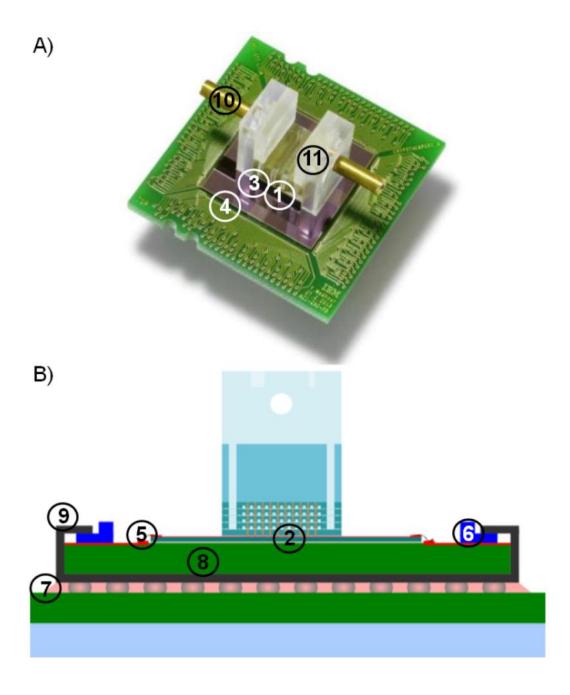

| Figure 3.1 A) Complete 3D CAD drawing of test package with metrology.  B) Test package cross section. C) Flipped view of test chip showing the glass die as well as the fluid inlet and outlet slits                                                                                                                                                                                                                                                                                                  |

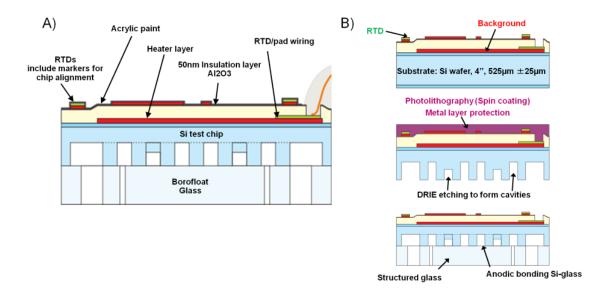

| Figure 3.2 A) Test chip cross section. B) Fabrication process flow52                                                                                                                                                                                                                                                                                                                                                                                                                                  |

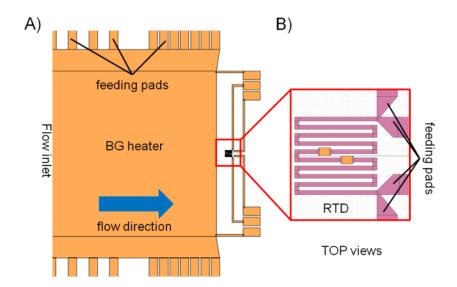

| Figure 3.3 A) Top view of NiCr background heater with indicated feeding pads and flow direction. B) Top view of RTD inside outlet plenum53                                                                                                                                                                                                                                                                                                                                                            |

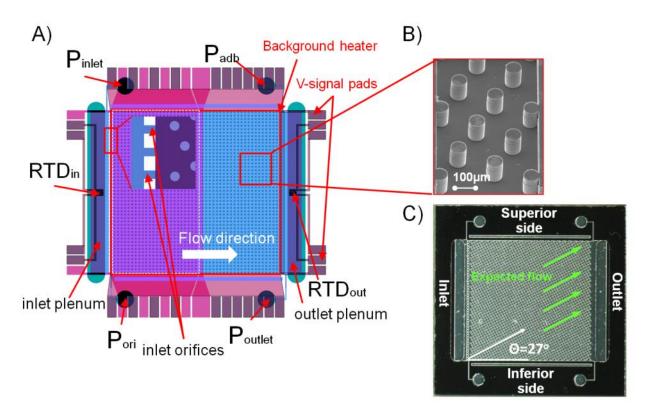

| Figure 3.4 A) Schematic of silicon pin fins test chip, top view. B) SEM image of Silicon pin fins. C) Top view microscope image of test chip, showing a potential flow deviation due to staggered position of pins, as seen in [82].                                                                                                                                                                                                                                                                  |

| Figure 3.5 Top view of PC manifold, showing the flow path from inlet to outlet as well as the available metrology54                                                                                                                                                                                                                                                                                                                                                                                   |

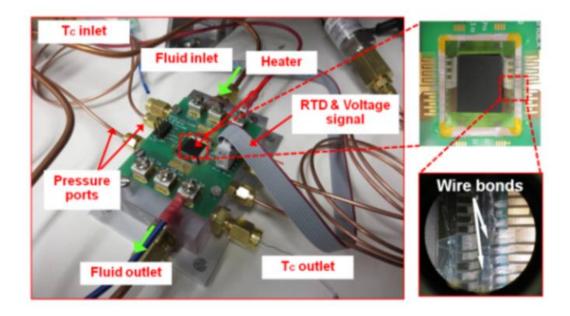

| Figure 3.6 Complete test section attached to the experimental facility, showing the inlet and outlet thermocouples, the pressure ports, the                                                                                                                                                                                                                                                                                                                                                           |

| electrical connections                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

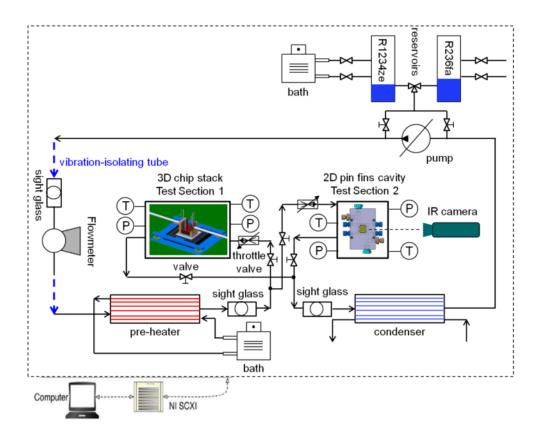

| Figure 3.7 Flow boiling test facility55                                                                                                                                                                                                                                                                |

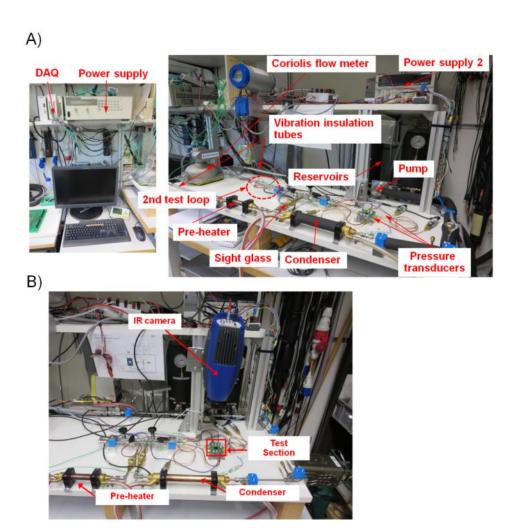

| Figure 3.8 A) Left: Test facility's power supply and data acquisition system. Right: complete test facility. B) Test section and IR camera setting                                                                                                                                                     |

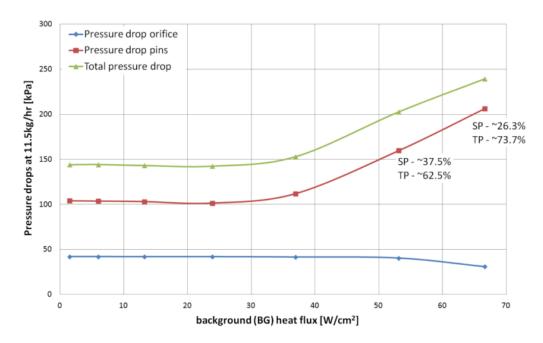

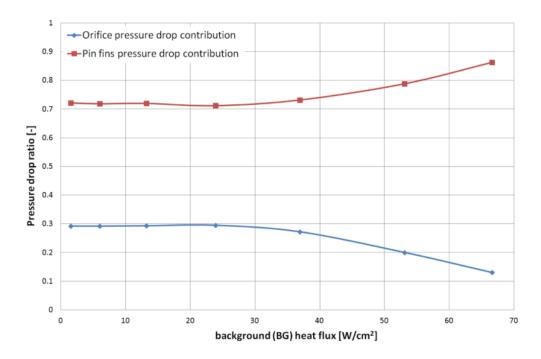

| Figure 3.9 Pressure drop components evolution for increasing base heat fluxes at a mass flow rate of 11.5kg/hr for R1234ze60                                                                                                                                                                           |

| Figure 3.10 Total pressure drop relative contributions for increasing base heat fluxes at a mass flow rate of 11.5kg/hr for R1234ze60                                                                                                                                                                  |

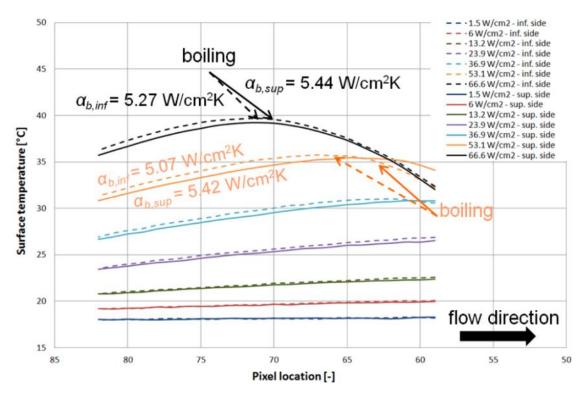

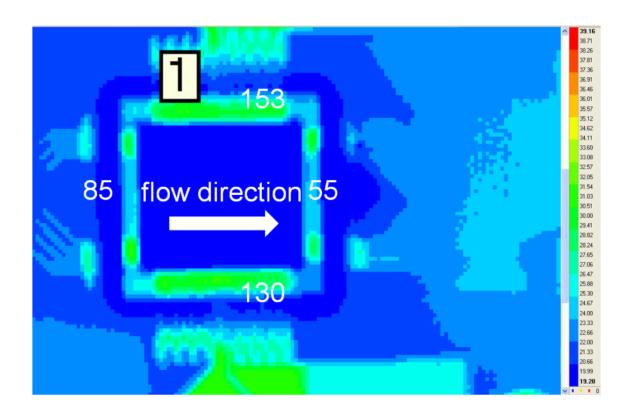

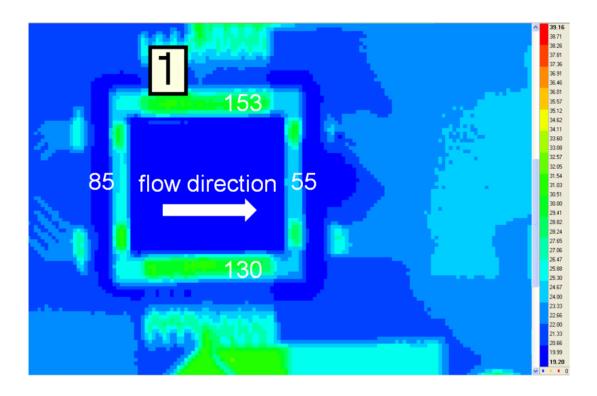

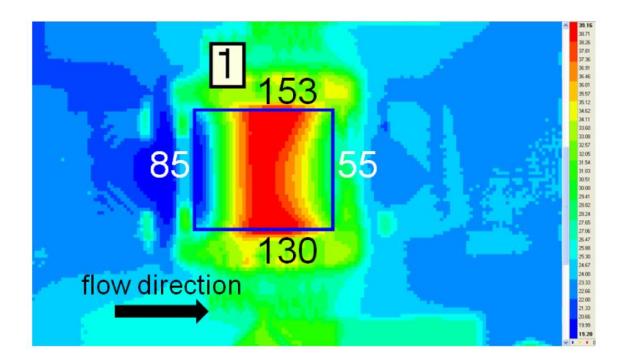

| Figure 3.11 Background heater junction temperatures along flow direction for increasing base heat fluxes at a mass flow rate of 11.5kg/hr for R1234ze, at two locations across the test section width, for an inlet subcooling of 13°C and inlet saturation temperature of 30°C62                      |

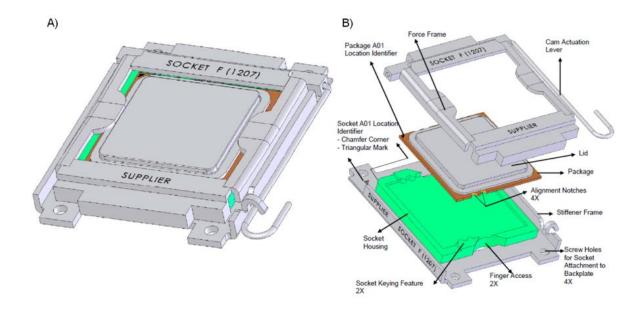

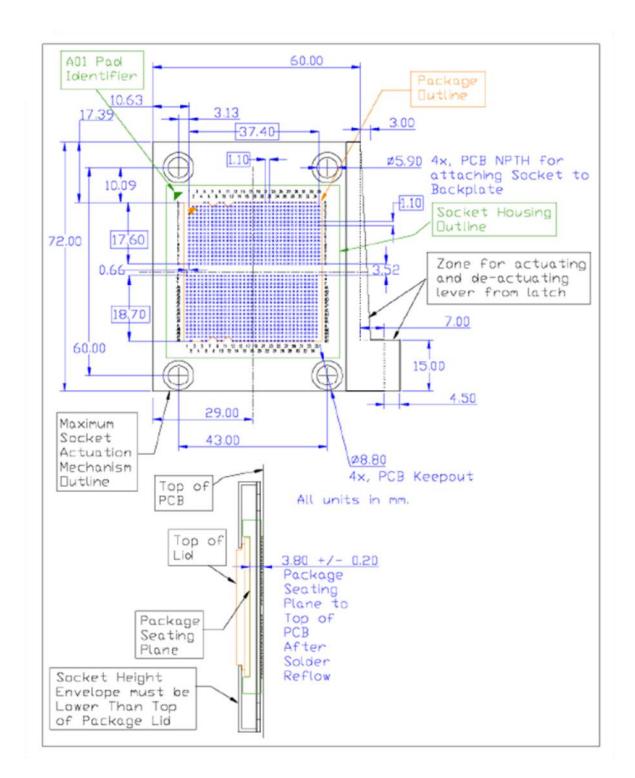

| Figure 3.12 CMOSAIC Test Vehicle description—chip stack package with silicon embedded heat transfer structures. a) Ensemble view of package with all components. b) Vertical cross-section describing the multiple layers and their respective thicknesses                                             |

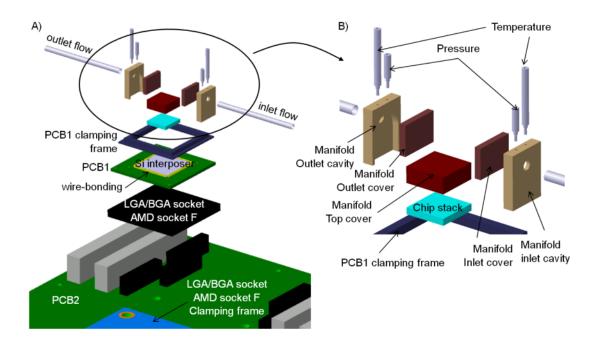

| Figure 3.13 Exploded views of the 3D chip stack package showing all different components                                                                                                                                                                                                               |

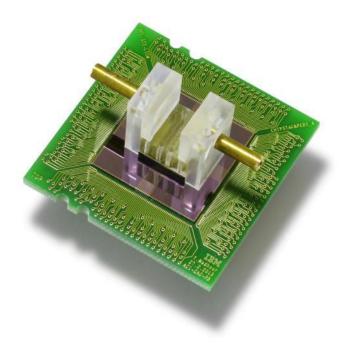

| Figure 3.14 Assembled CMOSAIC demonstrator. Manifold parts here are PMMA for visual and aesthetic purposes only                                                                                                                                                                                        |

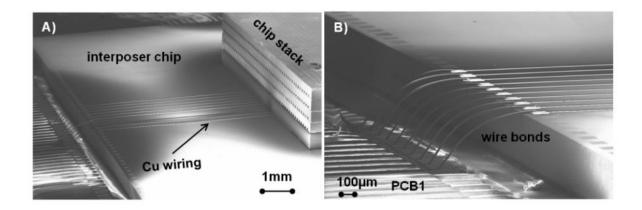

| Figure 3.15 A) SEM photograph of chip stack on interposer. B) SEM photograph of aluminium wire-bonds between interposer chip and PCB1.65                                                                                                                                                               |

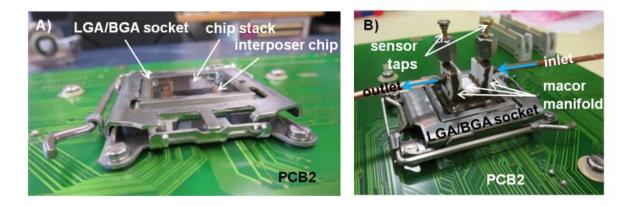

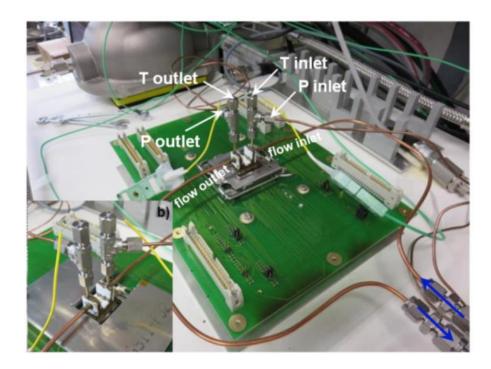

| Figure 3.16 A) Chip stack with interposer glued to PCB1 and plugged into LGA/BGA socket. The socket is C4 bonded to PCB2. B) Complete 3D module attached to PCB2, showing inlet and outlet tubing as well as inlet and outlet temperature and pressure taps locations                                  |

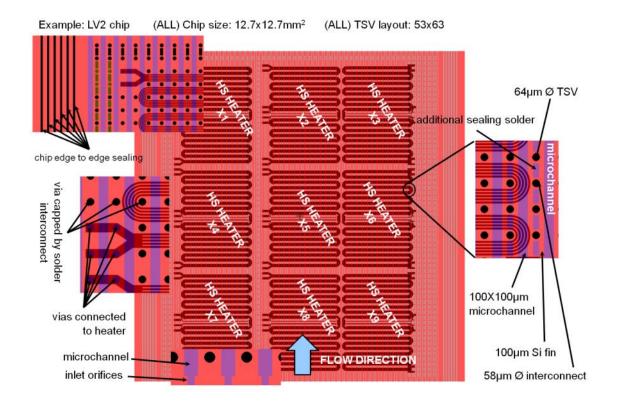

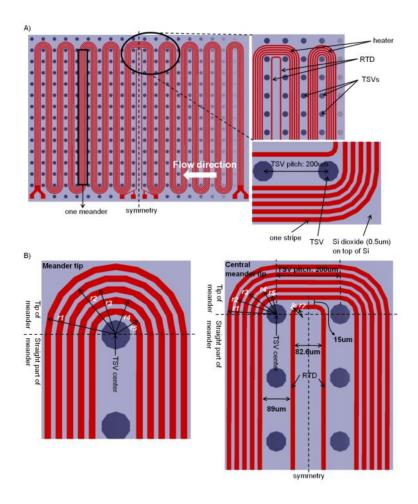

| Figure 3.17 Chip-level design, with all frontside and backside structures visible                                                                                                                                                                                                                      |

| Figure 3.18 Top view illustration of the design of a Hot Spot (HS) sputter-deposited heater with its own RTD, both 500nm-thick. The heater requires a current of 211 mA and a voltage drop of 8.92 V to output 50 W/cm <sup>2</sup> . The resistance of the heater at ambient temperature is 34.9 Ohms |

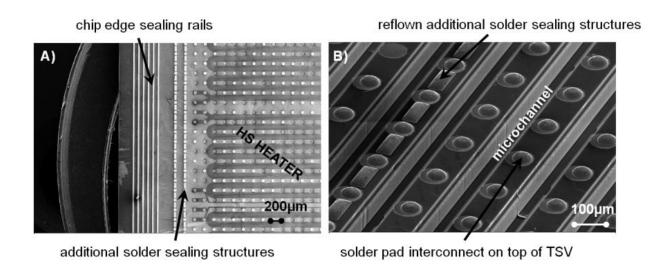

| Figure 3.19 A) SEM photograph of the LV2 chip frontisde, showing the added solder sealing structures (UBM side). B) SEM photograph of the LV3 chip backside, showing the solder interconnects and added sealing structures                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.20 Complete 3D chip stack module test section attached to experimental facility (Test Section 1, Figure 3.7), with inlet and outlet manifold temperature and pressure measurements69                                                                              |

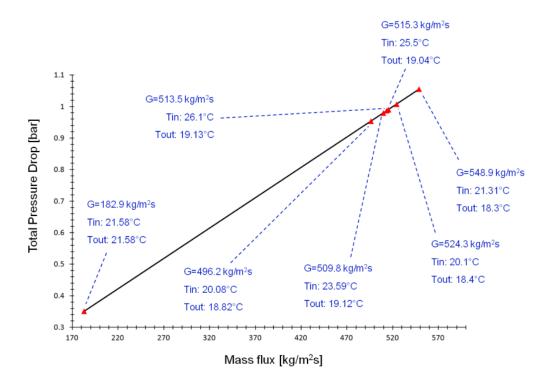

| Figure 3.21 Total adiabatic pressure drop values for increasing channel mass fluxes from 183 to 549 kg/m²s. Inlet and outlet temperature conditions are indicated for each pressure drop data point70                                                                      |

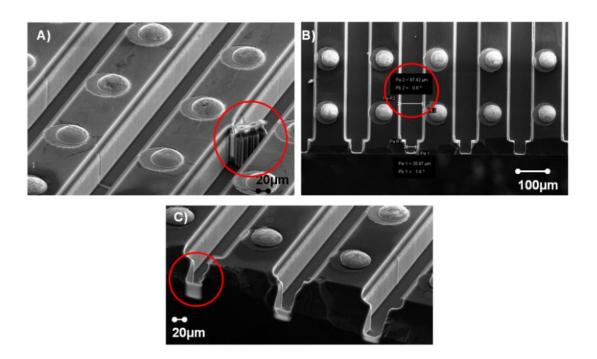

| Figure 3.22 SEM photographs of defects due to the DRIE process of the microchannels on the backside of chips LV1 to LV5. A) Blocked microchannels. B) Narrower than expected microchannels. C) Much smaller depth of cavity for inlet orifices in front of microchannels71 |

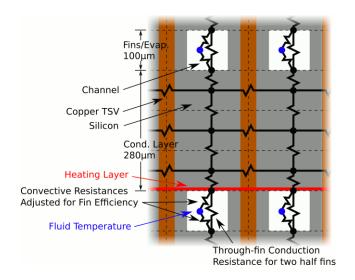

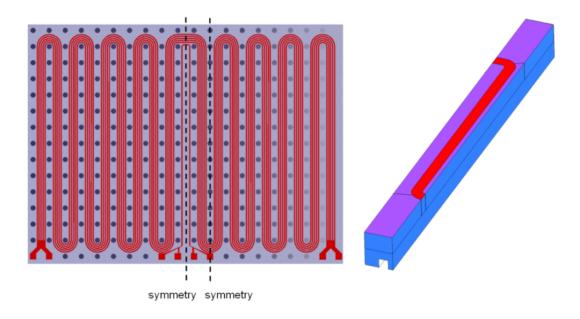

| Figure 4.1 Discretization scheme of chip stack75                                                                                                                                                                                                                           |

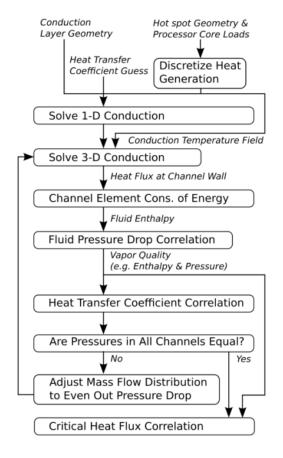

| Figure 4.2 Block diagram of solution technique75                                                                                                                                                                                                                           |

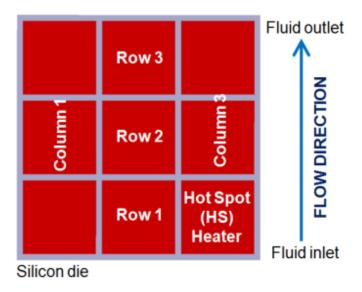

| Figure 4.3 front view of single 10×10 mm2 chip with 3x3 hot spot array layout. Microchannels are etched on the back79                                                                                                                                                      |

| Figure 4.4 Illustrations of the various patterns of active heaters applied to studied chip stack package80                                                                                                                                                                 |

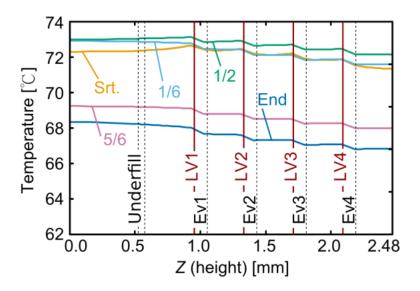

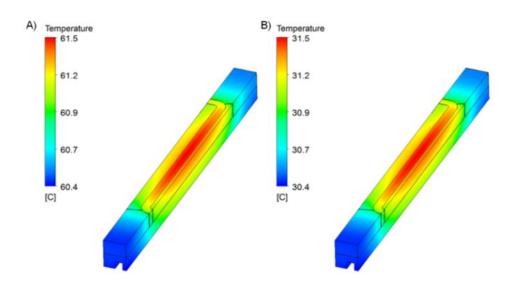

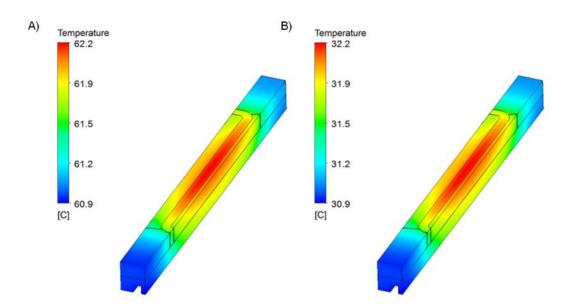

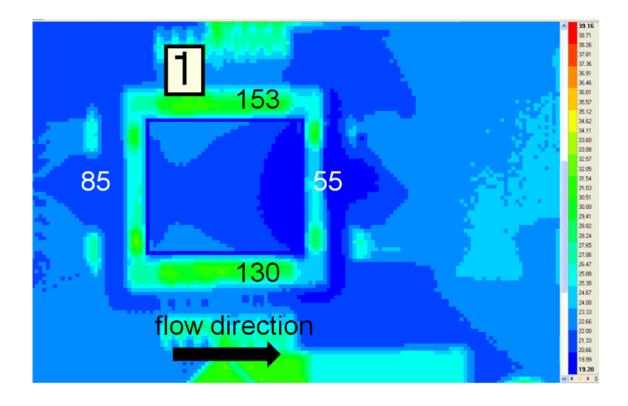

| Figure 4.5 Temperature vs. vertical position within the chip stack for Heat Load Pattern 1 at 50 W/cm <sup>2</sup> per chip81                                                                                                                                              |

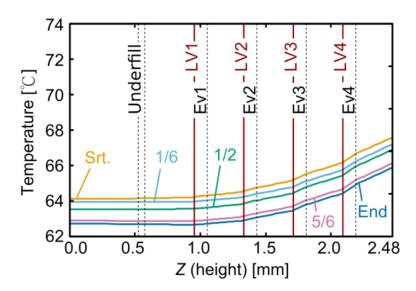

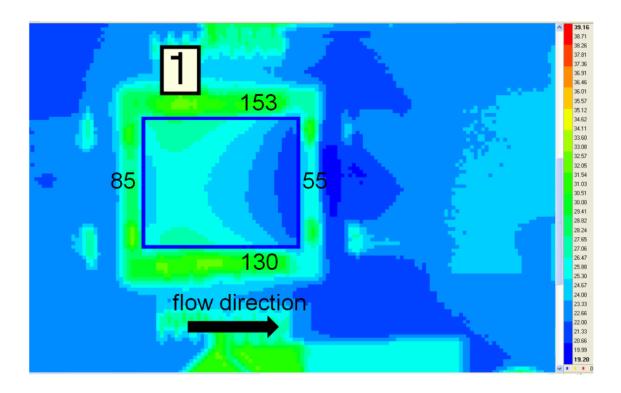

| Figure 4.6 Temperature vs. vertical position within the chip stack for Heat load Pattern 2 at 50 W/cm <sup>2</sup> per chip82                                                                                                                                              |

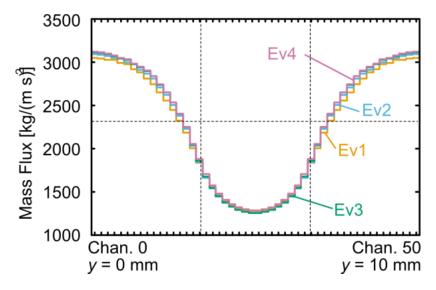

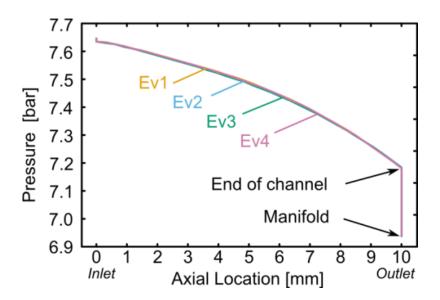

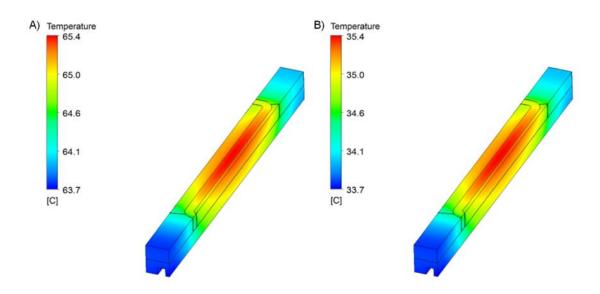

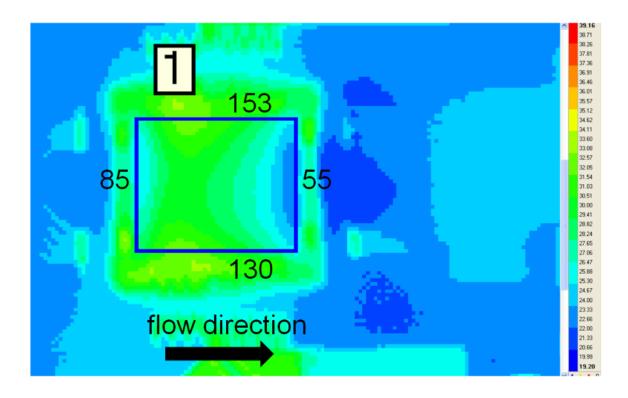

| Figure 4.7 Mass flux by channel across each evaporator; $10\times10 \text{ mm}^2$ chip; Heat Load Pattern 3 at 38 W/cm <sup>2</sup> ; $T_{SAT} = 60^{\circ}\text{C}$ 83                                                                                                    |

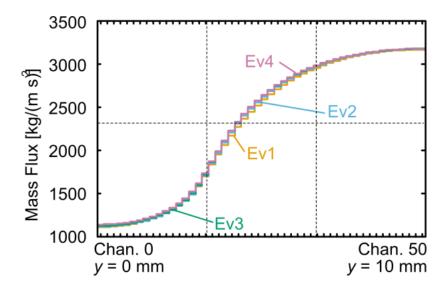

| Figure 4.8 Mass flux by channel across each evaporator; $10\times10 \text{ mm}^2$ chip; Heat Load Pattern 4 at 24 W/cm <sup>2</sup> ; $T_{SAT} = 60^{\circ}\text{C}$ 84                                                                                                    |

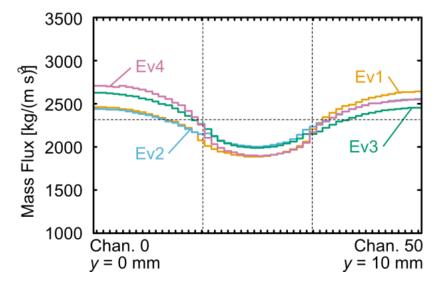

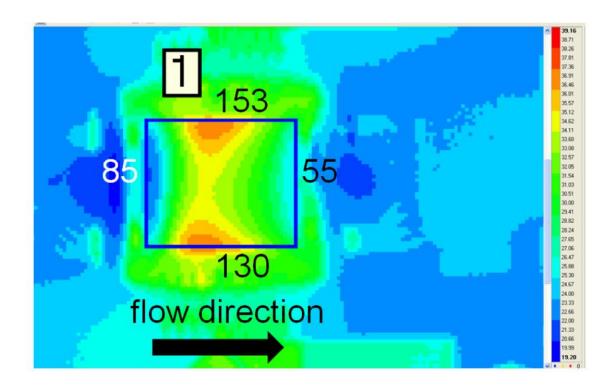

| Figure 4.9 Mass flux by channel across each evaporator; $10\times10 \text{ mm}^2$ chip; Heat Load Pattern 5 at 50 W/cm <sup>2</sup> ; $T_{SAT} = 60^{\circ}\text{C}$ 84                                                                                                    |

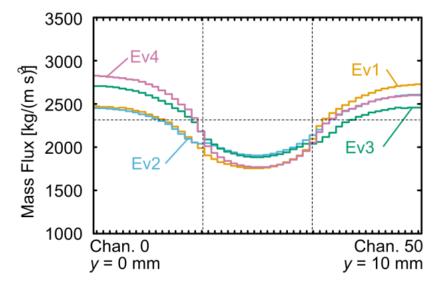

| Figure 4.10 Mass flux by channel across each evaporator; $10\times10~\text{mm}^2$ chip; Heat Load Pattern 5 at 82 W/cm <sup>2</sup> ; $T_{SAT} = 60^{\circ}\text{C}$ 85                                                                                                    |

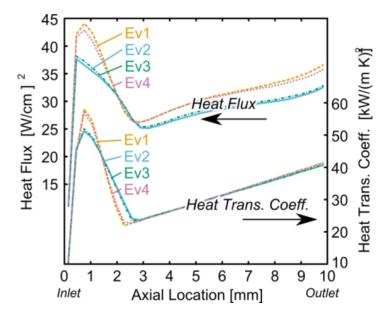

| Figure 4.11 Heat flux and heat transfer coefficient versus axial position along the center channel. Heat Load Pattern 5 at 82 W/cm $^2$ ; $T_{SAT} = 60^{\circ}C86$                                                                                                        |

| Figure 4.12 Fluid pressure along the center channel, Heat Load Pattern 5 at 82 W/cm <sup>2</sup> ; T <sub>SAT</sub> = 60°C                                                                                                                                                 |

Figure 4.13 Mass flux by channel across each evaporator;  $10\times10~\text{mm}^2$  chip; Heat Load Pattern 4 at 24 W/cm<sup>2</sup>;  $T_{SAT} = 30^{\circ}\text{C}$ .....89

#### List of Tables

| Table 2.1 Initial (after deposition) and final (after reflow) solder shape dimensions considering different pad geometries (Figure 2.13)25                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2 Experimental solder height after reflow (He) versus height prediction by Surface Evolver (Hm), for Rail2 and Ball structures29                                                                                                                                                                 |

| Table 2.3 Shear test results43                                                                                                                                                                                                                                                                           |

| Table 2.4 Average initial solder height H0, average final bond-line height and bond-line thermal resistance for different solder joint types44                                                                                                                                                           |

| Table 3.1 Thermo-physical saturation properties of R1234ze at 30°C59                                                                                                                                                                                                                                     |

| Table 4.1 Chip stack relevant thermal conductivities in W/mK74                                                                                                                                                                                                                                           |

| Table 4.2 R236fa saturation properties at 30 and 60°C78                                                                                                                                                                                                                                                  |

| Table 4.3 Results for Heat Load Pattern 1 at 50 W/cm <sup>2</sup> per chip82                                                                                                                                                                                                                             |

| Table 4.4 Results for Heat Load Pattern 2 at 50 W/cm <sup>2</sup> per chip83                                                                                                                                                                                                                             |

| Table 4.5 Summary of results for parallel-to-flow hot spots                                                                                                                                                                                                                                              |

| Table 4.6 Summary of results for perpendicular-to-flow hot spots88                                                                                                                                                                                                                                       |

| Table 4.7 Comparison of results for Heat Load Pattern 4 at 24 W/cm <sup>2</sup> per HS, for two different fluid inlet temperatures. The junction temperatures are only about 9-10 K above the saturation temperatures in both cases, illustrating the effectiveness of the interlayer cooling approach90 |

| mustrating the enectiveness of the interiager cooling approach                                                                                                                                                                                                                                           |

# Chapter 1 Of the importance of vertical integration and thermal management for processor and memory chips in the semiconductor industry

#### 1.1 Vertical integration

#### 1.1.1 Motivation and importance [1]

In the semiconductor industry, integrated-circuit (IC) feature sizes have been gradually reduced to integrate more transistors. This trend, as predicted by Moore's Law [2], consists in shrinking the transistors' gate dimensions to allow the reduction of the gate delay, the switching time of an individual transistor, thus decreasing operating voltages, improving electrical performance and of course increasing the number of transistors on a single chip [3] (Figure 1.1, [4]). However the speed of an electrical signal in an IC is also governed by the signal propagation time between transistors, and the performance of the interconnect wires is degraded as technology nodes continue to scale down, since smaller cross section wires have increased resistance and narrower metal pitches due to increased transistor density can raise the capacitance, as it can be seen on Equation 1.1 where R is the metal wire resistance, C the interlevel dielectric capacitance, C the line length, and C is the metal pitch. The sum of the two delays will thus increase with each new technology node as the interconnect delay starts to take over the gate delay [3] [5] (see Figure 1.2).

$$RC delay = 2\rho\varepsilon(4L^2/P^2 + L/T^2)$$

(1.1)

Remaining in a two dimensional plane and switching to larger System-On-Chip (SOC) dies with mixed technology designs does not provide a long term solution, since the integration of different technologies on a single chip would, on top of increasing the die area, require different processes to produce these different functions, which would raise materials, fabrication and cost issues. Meanwhile, the form factor of computing systems continues to be reduced for several applications, from servers to handheld devices.

Three-dimensional (3D) stacking of integrated-circuit dies presents itself as an interesting alternative. It corresponds to the integration in the Z direction of multiple 2D devices [3] (see Figure 1.3). It increases system density and package functionality by vertically integrating two or more chips. The vertical integration of IC chips using Through Silicon Vias

(TSVs) reduces the length of global interconnects and accordingly the signal delay time, while also improving bandwidth. Furthermore, the shorter communication distances help improve energy efficiency, by reducing power dissipation. Aside from the gain in electrical performance, other drivers such as a decrease in power consumption and noise, a form factor improvement, lower costs and more functionality show the significant benefits of 3D integration.

Figure 1.1 Shrinking transistor dimensions [4].

Figure 1.2 Gate delay versus interconnect delay for shrinking technology nodes [5].

Figure 1.3 Left: SoC with multiple processor cores and cache memories. Right: Corresponding 3D stacked IC with considerably smaller area and shorter vertical interconnects [6].

#### 1.1.2 Enabling technologies

3D integration of ICs would not be possible without the establishment and development of some of the following technologies. For an exhaustive list, the reader is encouraged to consult [7].

#### Through-Silicon-Via (TSV) technology

In layman's terms, a Through Silicon Via (TSV) is a metal-filled hole "drilled" in a silicon chip or wafer. It serves to electrically connect one side of a silicon chip or wafer to its other side by creating a metallic and electrically conductive via within the bulk silicon between the two surfaces. Thus, they are the key element to 3D stacking of ICs, in that they enable the communication from the bottom most die in a stack to the top most die, and they most importantly allow the integration of different types of components onto a single stack (e.g. sensors, CMOS, DRAM etc.) [8]. Easier packaging, increased silicon area dedicated to electronics and optimized technology for each chip layer are enabled through the use of TSVs [8].

Several fabrication technologies need to be combined in order to create such vias. The following describes some of the essential techniques necessary to the creation of a TSV (presented later in detail in §2.2). For more TSV fabrication subtleties, the reader is encouraged to consult [8] and [9].

- Deep Reactive Ion Etching (DRIE) technique, also known as the Bosch process, introduced by Bosch in the mid-1990s [10] [11], used to etch the TSVs into the silicon. Its high etching rate and compatibility with high aspect ratio vias make it very popular for high interconnect density applications [12].

- Thermal oxidation process, necessary for the creation of a silicon dioxide (SiO<sub>2</sub>) dielectric coating to electrically isolate the bulk silicon from the metal-filled TSVs. The thickness of the liner depends on its growth temperature and the time spent at that temperature, as well as on the quality of isolation desired. The definition of the high-

est allowable temperature for oxide growth on silicon is set by the number of preexisting metallization layers. If none, the temperature can be in the range of 700-900°C or even higher. Oxide growth is also possible by Chemical Vapor Deposition (CVD) [13].

- Electrochemical deposition of metal (also called electroplating), used to fill the etched TSV with an electrical conductor. Currently copper (Cu) and tungsten (W) are the most widely used metals, but other materials such as poly-silicon are also being explored. Overall, several techniques are possible to realize metal deposition: electroplating, CVD, electroless plating and Physical Vapor Deposition (PVD, sputter-deposition). All are all capable of filling high aspect ratio TSVs except for the sputtering method [14]

- Chemical Mechanical Polishing, used to planarize both surfaces of the wafer. This process follows directly the metal filling of the TSV, and is mainly designed to remove any over-deposited metal that might be protruding from the TSV trench [8]. Following this step, development on the surfaces of the wafer can begin.

#### Wafer thinning technology

Wafer thinning is used to reduce the thickness of a wafer prior to its dicing, in order to facilitate the stacking and high density packaging of ICs, by improving and reducing the form factor of electronic components whose sizes need to adapt to the more and more compact electronic products, such as smartphones [7].

#### Alignment and bonding technologies

In the MEMS fabrication world, alignment techniques are generally used for lithography and wafer or die-level bonding purposes. Bonding is a necessary technique to build 3D ICs, and is possible at different levels: wafer-to-wafer (W2W), die-to-wafer (D2W) and die-to-die (D2D) techniques, using interconnect technology. Wafer-to-wafer is mostly used for industry and production purposes, while die-to-die is mostly done at research level for prototype building [7], as is the case for this thesis (Chapter 2). Several bonding techniques are available today, such as solder, wire, polymer or anodic bonding [15].

#### 1.2 Thermal management of ICs

## 1.2.1 Importance, past and current concepts: from air to liquid cooling [16] [17]

Efficient heat dissipation in IC packages is crucial to support the packing density and performance scaling of future systems [18] [19]. The ongoing miniaturization trend of ICs results in constantly increasing chip-level power densities (Figure 1.4). The demand for higher computational performance results in microchips with more and more cores and cache memory. These cores communicate via long wires which consume a lot of energy and gen-

erate a considerable amount of heat. The International Technology Roadmap for Semiconductors (ITRS) projects that the power density of a single chip package will increase to 108 W/cm² for cost performance applications in 2018 [20], from the current power density of 60–80 W/cm². Thus, heat removal has become an ever increasing challenge, and the development of new chip cooling concepts is of utmost importance. Indeed, the reliability, performance, and power dissipation of interconnects and transistors are heavily dependent on their operating temperature.

These IC packages are traditionally air-cooled. Through forced (or natural) convection, heat is forced out of an IC package via a backside-attached copper heat sink and released into the atmosphere, which allows modern microprocessors nowadays to operate at safe temperatures. However the increase in typical microprocessor heat fluxes in the recent years as mentioned above has rendered air-cooled packages very large in size and complexity, as shown on Figure 1.5, and they are becoming inadequate in meeting the demands brought by the ongoing miniaturization trend of ICs. Therefore, backside micro-channel fluidic cooling concepts, be it single-phase water or two-phase dielectric evaporative cooling using environmentally-friendly refrigerants, were introduced into high-end server products [21] [17].

Figure 1.4 Module and chip heat flux densities for IBM chips, from the 1950s until early 2000s [22]. According to IBM Zürich Research, module heat fluxes between 0 and 14 W/cm² roughly correspond to chip heat fluxes between 0 and 80 W/cm², knowing that these chips occupy around 7/38th of the module area.

Due to this, microscale heat transfer has gained attention in the heat transfer community, and in the last few years, a significant research effort has begun around the world to de-

velop the necessary methods for designing and optimizing microscale heat spreaders for cooling of processor chips. Single-phase water cooling has seen the most interest to date because of its ease of use, low pressures involved, and water's high heat capacity. The feasibility of electronic cooling using water as coolant has been demonstrated [23] and resulted in sophisticated designs for single cavity backside heat removal [24] [25] [26] [27]. Water has the obvious disadvantages, however, of significant temperature gradients along the cooled device, a high freezing point temperature for shipping, and the danger of having water near electrical connections. This is where two-phase flow boiling in microscale heat sinks becomes interesting.

Figure 1.5 General size comparison between air-cooled heat sinks and single- or two-phase cooled heat sinks (Source: IBM Research, Zürich).

#### 1.2.2 Microscale flow boiling of refrigerants

#### Introduction [17]

Although liquid cooling may be the preferred near-term solution due to reasons mentioned above, cooling of processors through flow boiling of refrigerant does not encounter the problems described above and seems to be the ideal long-term solution, especially because it answers several of the desirable features in electronic cooling systems, as outlined by Agostini et al. [28].