### Ultra-high resolution A/D converters Analysis, modeling and optimization tools

THÈSE Nº 6174 (2014)

PRÉSENTÉE LE 27 JUIN 2014 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE D'ÉLECTRONIQUE GÉNÉRALE 1 PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Sylvain MARÉCHAL

acceptée sur proposition du jury:

Dr J.-M. Sallese, président du jury Prof. M. Kayal, Dr F. Krummenacher, directeurs de thèse Dr Ph. Deval, rapporteur Prof. F. Maloberti, rapporteur Dr A. Schmid, rapporteur

## Abstract

This thesis addresses the design of Sigma-Delta A/D converters over 20 bits. The main limitation in the design of  $\Sigma\Delta$  ADCs is the validation of the circuits before production. As transistor-level simulators are too slow, models are required to validate the circuits.

The main contribution of this thesis is a software to simulate switched capacitors  $\Sigma\Delta$  converters. The simulator distinguish itself by a direct description of the components - amplifiers, switches and capacitors - unlike existing high-level simulators, that use functional blocks: integration, subtraction, etc.

Modeling on the components level offers manifold benefits. The validation of the circuit is improved, as the model of the circuit is close to the final version: the sequence of the phases is identical, the common-mode is taken into account and the transfer functions for the signal and for the reference do not suffer from any approximation related to the architecture of the converter.

The new features provided by the simulator speed up the design of  $\Sigma\Delta$  modulators. The implementation with switched capacitors is taken into account from the early design phases. It makes possible to compare the effects of components imperfections in several architectures and implementations in order to select a suited topology. Moreover, the sensitive capacitive parasitic couplings are easily identifiable to guide the layout, and the layout can finally be validated, simulating an extracted view in the high-level simulator.

As the acquisition of an electrical signal through an acquisition chain is not limited by the sole  $\Sigma\Delta$  modulator, a fully digital solution - optimal filtering - is investigated to improve the resolution. Pre-amplification of the signal is also studied to optimize the power consumption and the noise level.

The theoretical contributions of this thesis are approved with the design of an integrated circuit including a front-end, an incremental  $\Sigma\Delta$  modulator and digital filters. The converter exhibits a resolution of 20 bits with a sample rate of 64 Sps. The power consumption is lower than 400 $\mu$ W. **Keywords** - Analog-to-Digital Converter; Sigma-Delta Modulation; Switched-Capacitors; Ultra-high resolution; Modeling; High-level Simulator; Incremental Converter; Optimal Filter; System-on-Chip.

## Résumé

Cette thèse traite du développement de convertisseurs A/D Sigma-Delta atteignant des résolutions supérieures à 20 bits. La principale limitation dans la conception des ADC  $\Sigma\Delta$  provient de la validation du circuit avant l'intégration. Les simulateurs de bas-niveau étant inadaptés car trop lents, il est nécessaire de valider ces circuits avec des modèles.

Le principal apport de cette thèse est un simulateur de convertisseurs  $\Sigma\Delta$  à capacités commutées. L'aspect novateur du simulateur est une représentation directe des composants - amplificateurs, interrupteurs et capacités - contrairement aux simulateurs de haut-niveau existants où des blocs fonctionnels sont utilisés : intégration, soustraction, etc.

Les intérêts d'une telle modélisation sont multiples ; la validation est améliorée, car la représentation du circuit est proche de sa version finale : le séquençage des phases est identique, le mode-commun est pris en compte et les fonctions de transfert pour le signal et le bruit ne souffrent d'aucune approximation liée à l'architecture du convertisseur.

La conception de modulateurs  $\Sigma\Delta$  est accélérée avec les nouvelles fonctionnalités offertes par le simulateur. Une sélection de l'implémentation avec des capacités commutées est prise en charge, dès les premières phases de design. Différentes architectures et implémentation peuvent ensuite être comparées vis-à-vis des imperfections des composants. Finalement, les couplages parasites sensibles peuvent être identifiés aisément afin de guider le layout, et le layout validé en simulant une vue extraite directement dans le simulateur de haut-niveau.

Comme l'acquisition d'un signal électrique à travers une chaîne d'acquisition complète ne se limite pas au seul modulateur  $\Sigma\Delta$ , une solution purement digitale - le filtrage optimal - est investiguée afin d'augmenter la résolution. La pré-amplification du signal est aussi étudiée pour optimiser la consommation et le niveau de bruit.

Les contributions théoriques de cette thèse sont approuvées avec la réalisation d'un circuit intégré incluant un front-end, un modulateur  $\Sigma\Delta$  incrémental et les filtres digitaux. Le convertisseur atteint une résolution de 20 bits lorsqu'il acquiert 64 échantillons par seconde. La puissance dissipée est inférieure à 400 $\mu$ W. **Mots-clefs** - Convertisseur Analogique-Numérique ; Modulation Sigma-Delta, Capacités-Commutées ; Ultra-haute résolution ; Modélisation ; Simulateur de haut-niveau ; Convertisseur Incrémental ; Filtre optimal ; SoC.

## Remerciements

Je voudrais remercier premièrement ceux qui ont permis à ce projet de voir le jour et m'ont donné la chance de faire cette recherche en partenariat avec l'industrie : mon directeur de thèse, Prof. Maher Kayal, Dr. Jean-Paul Bardyn et François Salchli. J'aimerais aussi remercier ceux qui ont accepté de se pencher sur ce travail avec un regard intéressé et critique : le président du jury, Dr. Jean-Michel Sallese, et les experts Prof. Franco Maloberti, Dr. Philippe Deval et Prof. Alexandre Schmid pour avoir conclu cette thèse sur une discussion utile et intéressante.

Tout au long de ce travail, j'ai eu la chance d'être encadré au niveau technique par trois personnes sans qui cette recherche n'aurait pas été ce qu'elle est. Merci à mon co-directeur de thèse, François Krummenacher, Olivier Nys et Michel Chevroulet pour m'avoir guidé, conseillé et avoir partagé leur savoir lors de toutes nos discussions.

Je tiens à remercier tous mes collègues du laboratoire pour entretenir une atmosphère de travail plaisante et agréable. Merci aux secrétaires du labo, Isabelle et Karin, sans qui la vie de doctorant serait bien plus compliquée.

Merci à Cédric, Didier, François et Guillaume et plus particulièrement Andrea, mes collègues de bureau, pour les innombrables discussions techniques ponctuées de franches rigolades. Sans vous, le plaisir de venir chaque jour au bureau n'aurait pas été le même.

Ma gratitude va finalement à ma famille et à mes parents pour leur soutien inconditionnel qui, sans forcément comprendre mon travail, ont toujours cru en moi. A ceux qui contribuent aussi à faire jour après jour de moi celui que je suis, mes amis, Merci pour tous les bons moments, jeux, débats, ripailles et aventures plus ou moins dangereuses. Merci P. & N., F., S. & S., M., A.P. & M., J. & X., M. & Y., M. & S., M., C. & S., M. & D., M. & T., N. & J.B., et à celle qui partage ma vie depuis de nombreuses années, merci Estelle.

Lausanne, 28 Mai 2014

Sylvain Maréchal

| Ab  | ostra   | ct (English/Français)                 | iii |

|-----|---------|---------------------------------------|-----|

| Re  | mer     | ciements                              | vii |

| Lis | st of : | figures                               | xii |

| Li  | stof    | tables xv                             | iii |

| 1   | Intr    | oduction                              | 1   |

|     | 1.1     | Problems and Imperfections            | 3   |

|     | 1.2     | Selected approach                     | 3   |

|     | 1.3     | Thesis outline                        | 4   |

| 2   | Bas     | ic concepts                           | 7   |

|     | 2.1     | Sampling and oversampling             | 7   |

|     | 2.2     | Quantization error and noise shaping  | 8   |

|     | 2.3     | Feedback and feedforward modulators   | 9   |

|     |         | 2.3.1 Feedback structure              | 10  |

|     |         | 2.3.2 Feedforward                     | 12  |

|     | 2.4     |                                       | 13  |

|     | 2.5     | 0                                     | 14  |

|     | 2.6     | 0 1                                   | 15  |

|     | 2.7     | Conclusions                           | 15  |

| 3   | Opt     | imal decoding                         | 17  |

|     | 3.1     | First order                           | 18  |

|     |         | 3.1.1 Optimal filter – thresholds     | 21  |

|     | 3.2     | Second-order – MASH 1-1               | 26  |

|     | 3.3     | I I I I I I I I I I I I I I I I I I I | 36  |

|     |         | 1.                                    | 39  |

|     | 3.4     | ľ                                     | 44  |

|     | 3.5     | Conclusion                            | 51  |

| 4 | ADO | C Input stage - A comparative study                 | 53  |

|---|-----|-----------------------------------------------------|-----|

|   | 4.1 | Two-phases architectures                            | 55  |

|   | 4.2 | Symmetrical architectures                           | 59  |

|   | 4.3 | Comparative study                                   | 61  |

|   | 4.4 | Conclusion                                          | 63  |

| 5 | Мос | dels                                                | 65  |

|   | 5.1 | Integrator                                          | 66  |

|   |     | 5.1.1 Ideal Integrator                              | 69  |

|   |     | 5.1.2 Amplifier - DC Gain and Offset                | 69  |

|   |     | 5.1.3 Amplifier - Voltage Saturation                | 71  |

|   |     | 5.1.4 Amplifier - Non-linear Gain                   | 71  |

|   |     | 5.1.5 Amplifier - Transient - SR                    | 74  |

|   |     | 5.1.6 Amplifier - Transient - SR Hyperbolic Tangent | 80  |

|   |     | 5.1.7 Switches - Transient                          | 81  |

|   |     | 5.1.8 Switches - Clock Feedthrough                  | 85  |

|   |     | 5.1.9 Non-linear Capacitors                         | 87  |

|   |     | 5.1.10 Thermal Noise                                | 92  |

|   |     | 5.1.11 Quantizer                                    | 96  |

|   |     | 5.1.12 DAC                                          | 98  |

|   | 5.2 | Linear Circuit                                      | 99  |

|   |     | 5.2.1 Matrix Representation                         | 100 |

|   | 5.3 | Conclusion                                          | 101 |

| 6 | Sim | nulator                                             | 103 |

|   | 6.1 | Design steps and simulators                         | 103 |

|   |     | 6.1.1 Definition of the architecture                | 104 |

|   |     | 6.1.2 Implementation with switched capacitors       | 104 |

|   |     | 6.1.3 Implementation of the digital blocks          | 105 |

|   |     | 6.1.4 Design of the analog blocks                   | 106 |

|   |     | 6.1.5 Post-layout validation                        | 106 |

|   |     | 6.1.6 Summary of the design steps                   | 107 |

|   | 6.2 | Specifications                                      | 108 |

|   | 6.3 | Simulator Core                                      | 108 |

|   |     | 6.3.1 Simulator - Top Classes                       | 109 |

|   |     | 6.3.2 Simulator - Architecture Classes              | 109 |

|   |     | 6.3.3 Simulator - Integrator Classes                | 111 |

|   |     | 6.3.4 Simulator - Linear Circuit                    | 112 |

|   | 6.4 | Applications                                        | 115 |

|   |     | 6.4.1 Testbenches                                   | 115 |

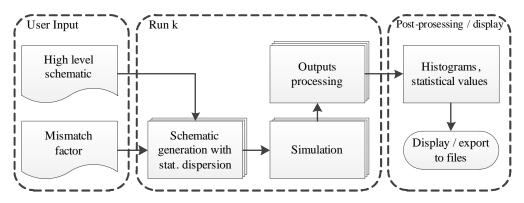

|   |     | 6.4.2  | Mismatch Analysis                                                                                                                |

|---|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

|   |     | 6.4.3  | Parasitic Coupling 118                                                                                                           |

|   |     | 6.4.4  | Comparison of Architectures                                                                                                      |

|   |     | 6.4.5  | Conclusion                                                                                                                       |

| - |     |        | 100                                                                                                                              |

| 7 | ADC |        | 129                                                                                                                              |

|   | 7.1 | -      | ications                                                                                                                         |

|   | 7.2 |        | ion of the architecture                                                                                                          |

|   |     | 7.2.1  | Structure                                                                                                                        |

|   |     | 7.2.2  | $OSR - C_{in} \dots \dots$ |

|   |     | 7.2.3  | Topology - Order                                                                                                                 |

|   | 7.3 | •      | mentation                                                                                                                        |

|   |     | 7.3.1  | Protection for the reference input 134                                                                                           |

|   |     | 7.3.2  | Clock feedthrough 136                                                                                                            |

|   |     | 7.3.3  | Parasitic coupling                                                                                                               |

|   |     | 7.3.4  | $2^{nd}$ and $3^{rd}$ integrators                                                                                                |

|   |     | 7.3.5  | Incremental and $\Sigma\Delta$ modes                                                                                             |

|   |     | 7.3.6  | Coefficients 141                                                                                                                 |

|   |     | 7.3.7  | Sizing                                                                                                                           |

|   | 7.4 | Digita | l controls and filters                                                                                                           |

|   |     | 7.4.1  | Controls                                                                                                                         |

|   |     | 7.4.2  | Filters                                                                                                                          |

|   |     | 7.4.3  | Mathematical relationships                                                                                                       |

|   | 7.5 | Concl  | usion                                                                                                                            |

| _ |     |        |                                                                                                                                  |

| 8 | PGA |        | 153                                                                                                                              |

|   | 8.1 |        | Zero Amplifier                                                                                                                   |

|   |     | 8.1.1  | Offset and Flicker Noise Reduction Techniques 154                                                                                |

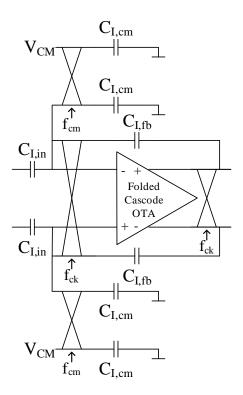

|   |     | 8.1.2  | Proposed Circuit 155                                                                                                             |

|   |     | 8.1.3  | Implementation                                                                                                                   |

|   | 8.2 | Noise  | Analysis                                                                                                                         |

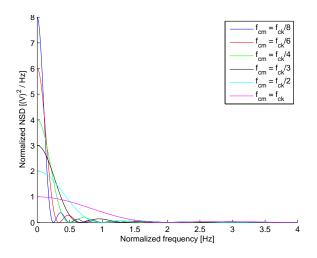

|   |     | 8.2.1  | 1/f noise - Auxiliary chain                                                                                                      |

|   |     | 8.2.2  | 1/f noise - Main amplifier                                                                                                       |

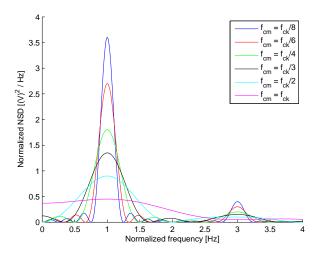

|   |     | 8.2.3  | Thermal noise - Amplifiers 163                                                                                                   |

|   |     | 8.2.4  | Thermal noise - Input chopper                                                                                                    |

|   |     | 8.2.5  | Thermal noise - Resistors                                                                                                        |

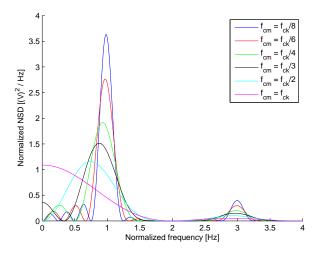

|   |     | 8.2.6  | Common-mode control circuits                                                                                                     |

|   |     | 8.2.7  | Power Consumption                                                                                                                |

|   |     | 8.2.8  | Noise Contributions - Summary 172                                                                                                |

|   | 8.3 | Comn   | non-mode rejection                                                                                                               |

|   |     |        |                                                                                                                                  |

|    |                  | 8.3.1 Proposed solution 17 | '5 |  |  |

|----|------------------|----------------------------|----|--|--|

|    |                  | 8.3.2 Nonideal effects     | 7  |  |  |

|    |                  | 8.3.3 Implementation       | '8 |  |  |

|    | 8.4              | Output buffers             | '9 |  |  |

|    |                  | 8.4.1 Passive resistors    | '9 |  |  |

|    |                  | 8.4.2 Active buffers       | 30 |  |  |

|    | 8.5              | Conclusion                 | 31 |  |  |

| 9  | Cha              | acterization 18            | 3  |  |  |

|    | 9.1              | Functional tests - ADC     | 34 |  |  |

|    | 9.2              | Functional tests - PGA 18  | 37 |  |  |

|    | 9.3              | Performances               | 39 |  |  |

|    | 9.4              | Conclusions                | )1 |  |  |

| 10 |                  | lusion 19                  | 3  |  |  |

|    | 10.1             | Main contributions         | 13 |  |  |

|    | 10.2             | Future perspectives        | )4 |  |  |

| Bi | Bibliography 204 |                            |    |  |  |

| 2.1  | Block diagram of a Sigma-Delta A/D converter.                               | 7  |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | Transfer functions and quantization error of (left) multi- and (right)      |    |

|      | single-bit quantizers                                                       | 8  |

| 2.3  | Linear representation of the first-order $\Sigma\Delta$ modualtor           | 9  |

| 2.4  | Second-order unstable modulator                                             | 9  |

| 2.5  | Second-order CIFB modulator.                                                | 10 |

| 2.6  | Second-order CIFB modulator with input feedforward                          | 11 |

| 2.7  | Second-order CIFB modulator with input feedforward                          | 11 |

| 2.8  | Second-order CIFF modulator with input feedforward                          | 12 |

| 2.9  | MASH 1-1-1 modulator.                                                       | 13 |

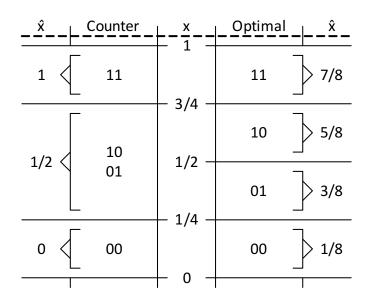

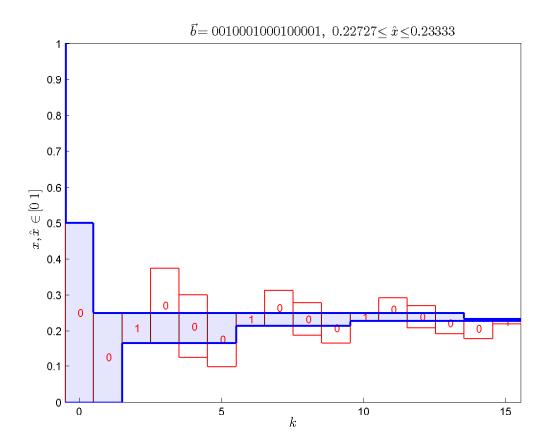

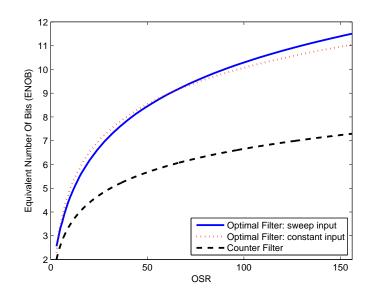

| 3.1  | Comparison of the counter and optimal filters for an OSR of two bits.       | 19 |

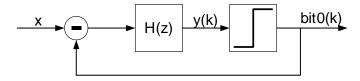

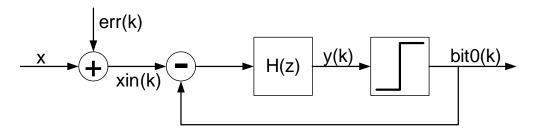

| 3.2  | First order modulator.                                                      | 19 |

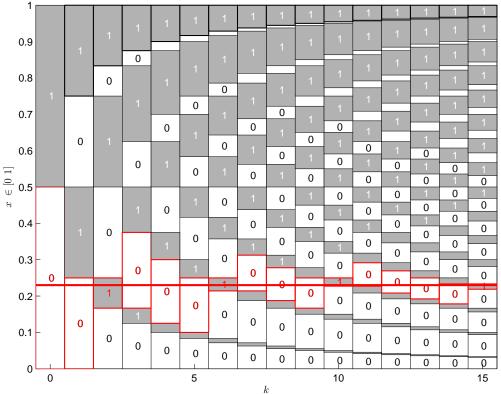

| 3.3  | Thresholds for the 16 first bits of the first order modulator.              | 22 |

| 3.4  | Example of an update of the input space. After each bit, the possible       |    |

|      | input space (blue) is compared to the bit[k] thresholds (red boxes) and     |    |

|      | updated accordingly                                                         | 23 |

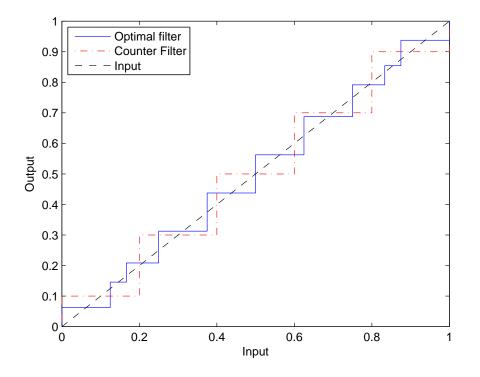

| 3.5  | Transfer function using counter filter (dash-dot line) and optimal filter   |    |

|      | (solid line) for $nbits = 4$                                                | 24 |

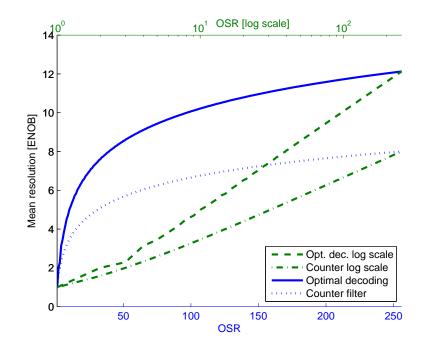

| 3.6  | Mean resolution using counter filter (dotted line) and optimal filter       |    |

|      | (solid line). The dashed lines are referenced to the upper logarithmic      |    |

|      | scale                                                                       | 25 |

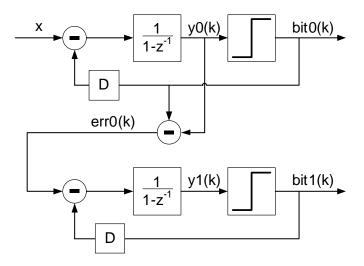

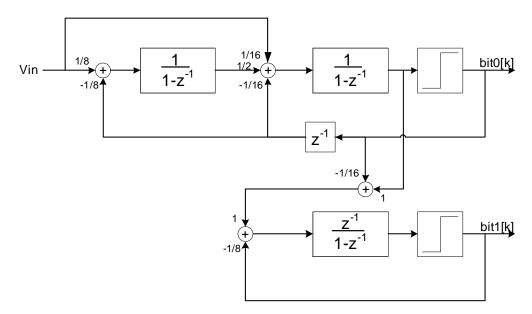

| 3.7  | Block diagram of a MASH11 $\Sigma\Delta$ modulator with a constant input    | 26 |

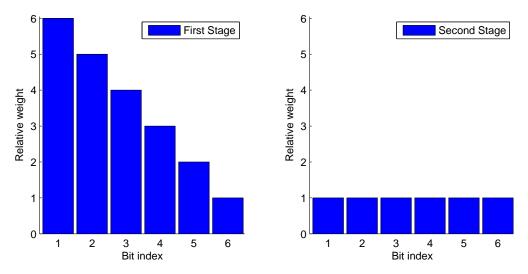

| 3.8  | Linear filter relative coefficients for the first (left) and second (right) |    |

|      | stage for an over-sampling ratio of $nbits = 6$                             | 29 |

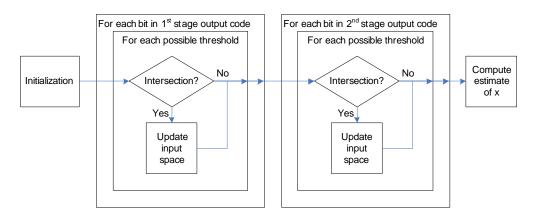

| 3.9  | Optimal filter decoding flow.                                               | 30 |

| 3.10 | Transfer function of the MASH 1-1 optimal filter (solid), and of the linear |    |

|      | filter (dash dots).                                                         | 34 |

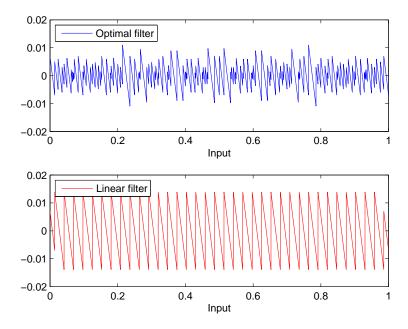

| 3.11 | Quantization error using the MASH 1-1 optimal filter (top), and the         |    |

|      | linear filter (bottom) for $nbits = 8$                                      | 35 |

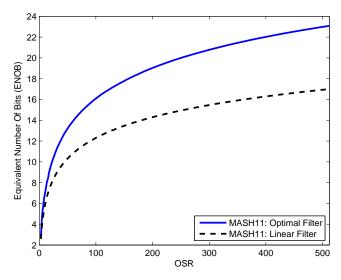

| 3.12 Mean resolution of the MASH 1-1 optimal filter (solid line), and of                                                                                                                    | the                                                                                                                                                         |                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| linear filter (dashed line).                                                                                                                                                                |                                                                                                                                                             | 6                                                             |

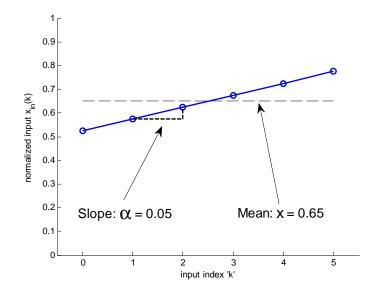

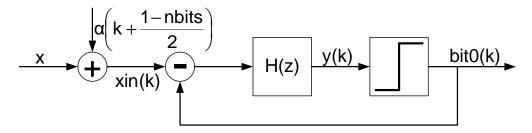

| 3.13 Sweep input: mean value and slope                                                                                                                                                      | 3                                                                                                                                                           | 7                                                             |

| 3.14 Block diagram of first-order $\Sigma\Delta$ modulator with sweep input                                                                                                                 | 3                                                                                                                                                           | 7                                                             |

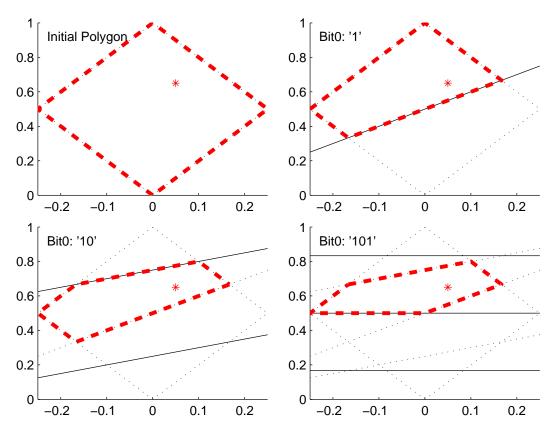

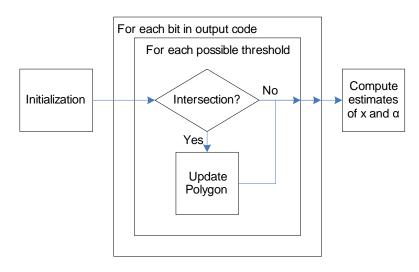

| 3.15 Iterative process to generate a polygon using thresholds, $nbits = 3$ .                                                                                                                | Тор                                                                                                                                                         |                                                               |

| left figure is the starting polygon, inside which the modulator is                                                                                                                          | not                                                                                                                                                         |                                                               |

| saturated. Axes are $\alpha$ (horizontal) and $x$ (vertical). Input has a sl                                                                                                                | ope                                                                                                                                                         |                                                               |

| $\alpha = 0.05$ and a normalized mean $x = 0.65$ (star)                                                                                                                                     | 4                                                                                                                                                           | 0                                                             |

| 3.16 Optimal filtering procedure                                                                                                                                                            | 4                                                                                                                                                           | 1                                                             |

| 3.17 Mean resolution of the optimal filter with sweep input (solid line),                                                                                                                   | and                                                                                                                                                         |                                                               |

| of the counter filter (dashed line).                                                                                                                                                        | 4                                                                                                                                                           | 5                                                             |

| 3.18 First order modulator with a noisy input                                                                                                                                               | 4                                                                                                                                                           | 5                                                             |

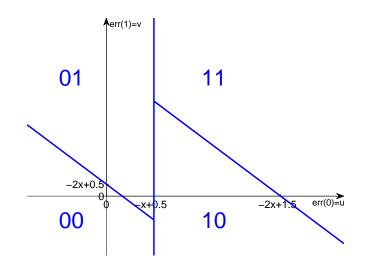

| 3.19 Graphical representation of the probability domains (integration                                                                                                                       | sur-                                                                                                                                                        |                                                               |

| faces) for the two-bits OSR. The input <i>x</i> is a parameter, shifting the b                                                                                                              | olue                                                                                                                                                        |                                                               |

| lines. The axis $u$ and $v$ represent the uncorrelated error $err(0)$ and $e$                                                                                                               | err(1). 4                                                                                                                                                   | 7                                                             |

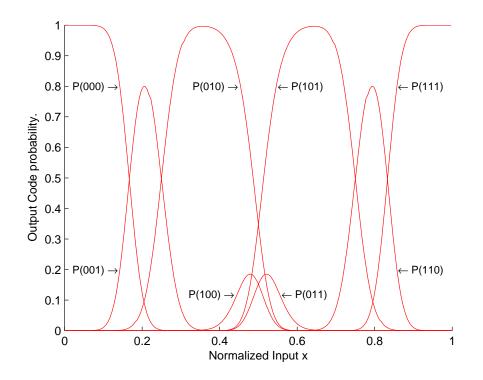

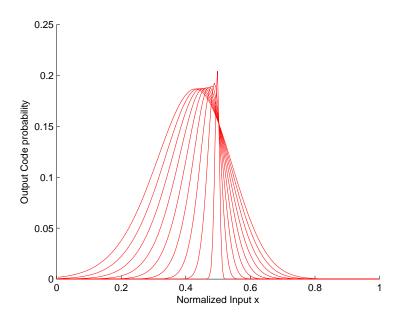

| 3.20 Probability functions for the 8 output codes of a three-bits output.                                                                                                                   | The                                                                                                                                                         |                                                               |

| considered noise function has a Gaussian shape and a deviation $\sigma$ =                                                                                                                   | = 0.05. 4                                                                                                                                                   | 9                                                             |

| 3.21 Probability functions of the code 100 for values of $\sigma$ from 0.17 to 0                                                                                                            | ).01.                                                                                                                                                       |                                                               |

| The left plot corresponds to $\sigma$ = 0.17 while the narrow one, around                                                                                                                   |                                                                                                                                                             |                                                               |

| was generated with $\sigma = 0.01$                                                                                                                                                          | 5                                                                                                                                                           | 0                                                             |

|                                                                                                                                                                                             |                                                                                                                                                             |                                                               |

| 4.1 High-level representation of a first-order modulator                                                                                                                                    | 5                                                                                                                                                           | 3                                                             |

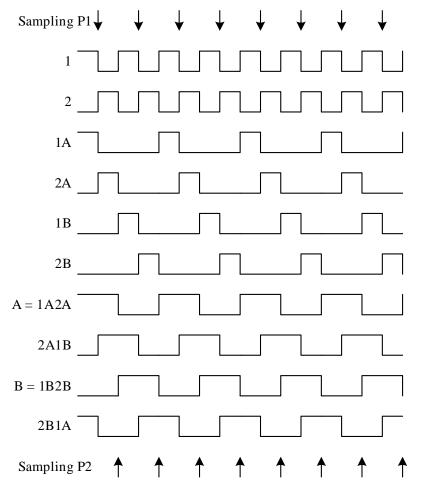

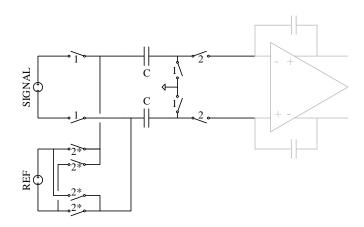

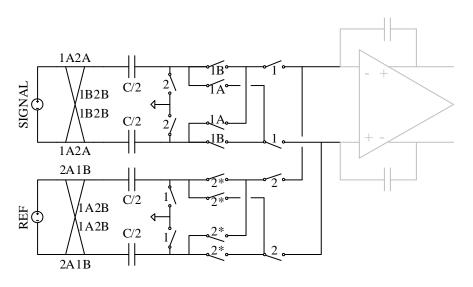

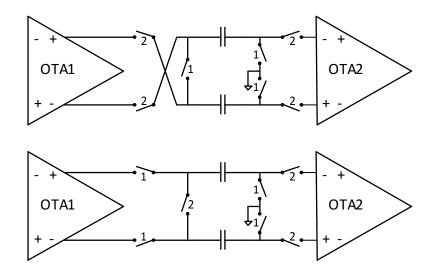

| <ul><li>4.1 High-level representation of a first-order modulator</li></ul>                                                                                                                  |                                                                                                                                                             | 3                                                             |

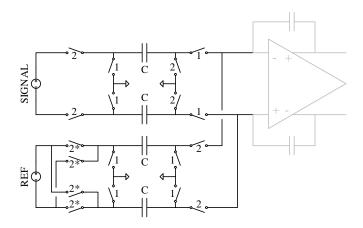

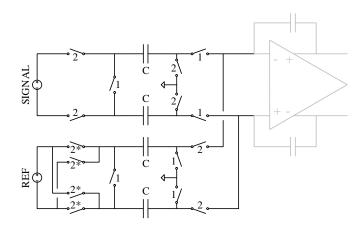

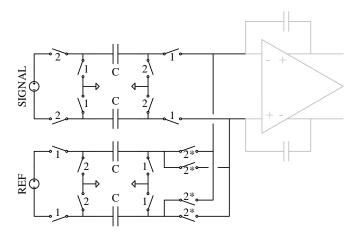

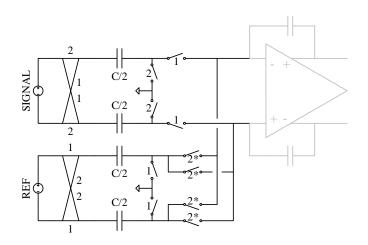

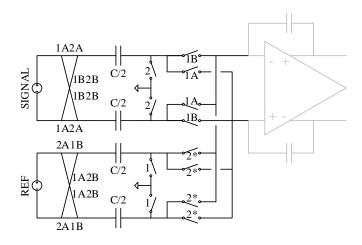

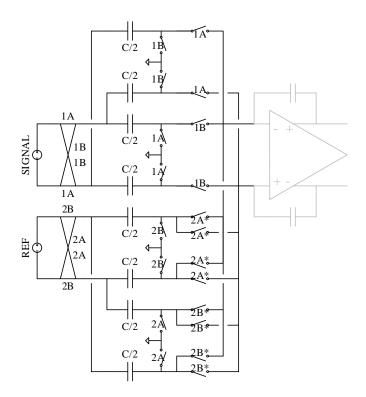

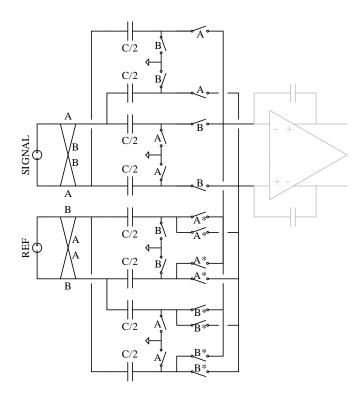

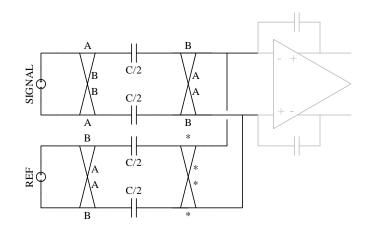

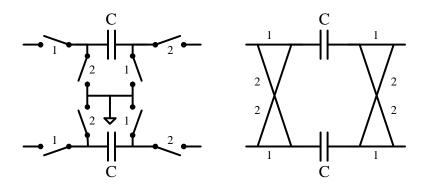

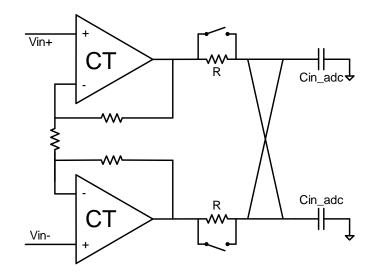

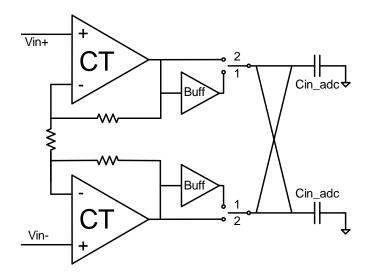

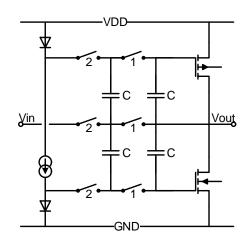

|                                                                                                                                                                                             | 5                                                                                                                                                           | 4                                                             |

| 4.2 Control signals for the architectures #1 to #9                                                                                                                                          | 5<br>5                                                                                                                                                      | 4                                                             |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5<br>5<br>5                                                                                                                                                 | 4<br>5                                                        |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li> <li>4.3 Architecture #1</li> <li>4.4 Architecture #2</li> </ul>                                                            | 5<br>5<br>5                                                                                                                                                 | 4<br>5<br>5                                                   |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5<br>5<br>5<br>5                                                                                                                                            | 4<br>5<br>5<br>6                                              |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li> <li>4.3 Architecture #1</li> <li>4.4 Architecture #2</li> <li>4.5 Architecture #2b</li> <li>4.6 Architecture #3</li> </ul> | 5<br>5<br>5<br>5<br>5                                                                                                                                       | 4<br>5<br>6<br>6                                              |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5<br>5<br>5<br>5<br>5<br>5                                                                                                                                  | 4<br>5<br>6<br>6                                              |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5<br>5<br>5<br>5<br>5<br>5<br>5                                                                                                                             | 4<br>5<br>6<br>6<br>7                                         |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5          5          5          5          5          5          5          5          5          5          5          5          5                       | 4<br>5<br>6<br>6<br>7<br>8                                    |

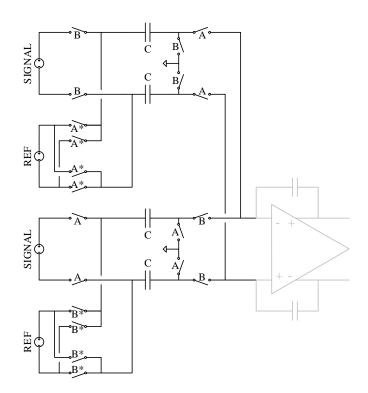

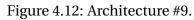

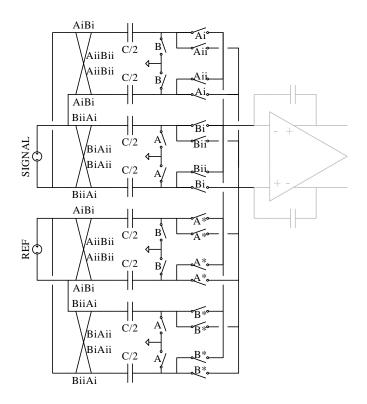

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5          5          5          5          5          5          5          5          5          5          5          5          5          5            | 4<br>5<br>6<br>6<br>7<br>8<br>8                               |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | 5          5          5          5          5          5          5          5          5          5          5          5          5          5          5 | 4<br>5<br>6<br>6<br>7<br>8<br>8<br>9                          |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | $     \begin{array}{ccccccccccccccccccccccccccccccccc$                                                                                                      | 4<br>5<br>6<br>6<br>7<br>8<br>8<br>9<br>0                     |

| <ul> <li>4.2 Control signals for the architectures #1 to #9</li></ul>                                                                                                                       | $     \begin{array}{ccccccccccccccccccccccccccccccccc$                                                                                                      | 4<br>5<br>6<br>6<br>6<br>7<br>8<br>8<br>9<br>0<br>0           |

| 4.2       Control signals for the architectures #1 to #9.                                                                                                                                   | $     \begin{array}{ccccccccccccccccccccccccccccccccc$                                                                                                      | 4<br>5<br>5<br>6<br>6<br>6<br>7<br>8<br>8<br>9<br>0<br>0<br>1 |

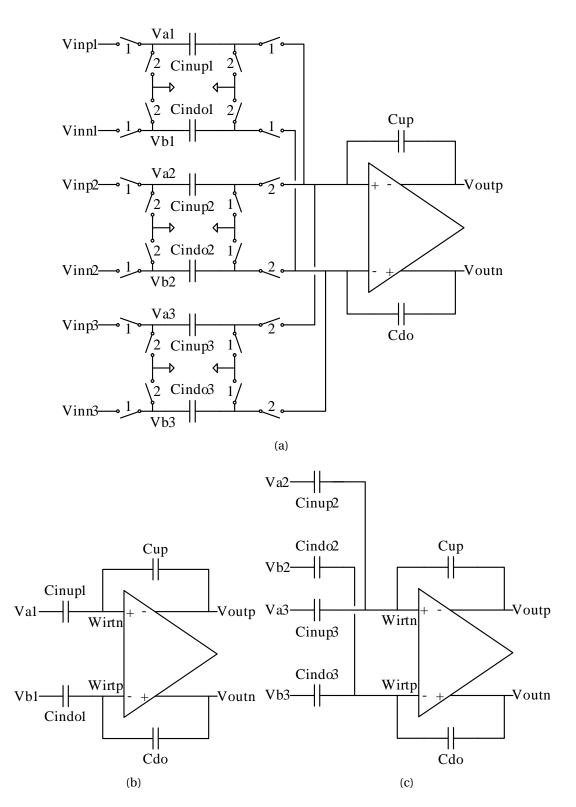

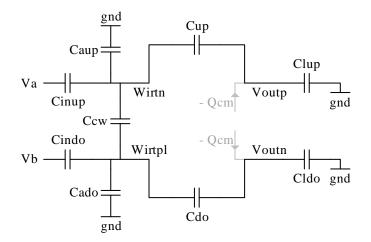

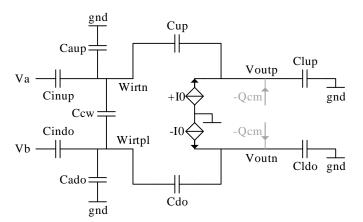

| 5.3  | Representation of a two-phases integrator (a) into two similar subcircuit    |    |

|------|------------------------------------------------------------------------------|----|

|      | for phase 1 (b) and phase 2 (c).                                             | 68 |

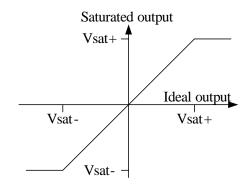

| 5.4  | Saturation transfer function. The saturated output cannot reach voltages     |    |

|      | beyond the $V_{sat-}$ and $V_{sat+}$ limits                                  | 71 |

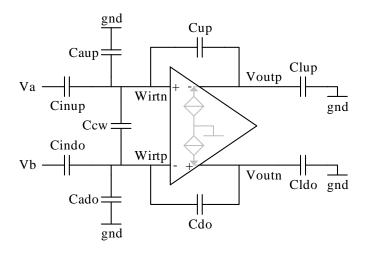

| 5.5  | Representation of the model of the integrator considering an amplifier       |    |

|      | with a non-linear gain. The parasitic capacitors taken into account in       |    |

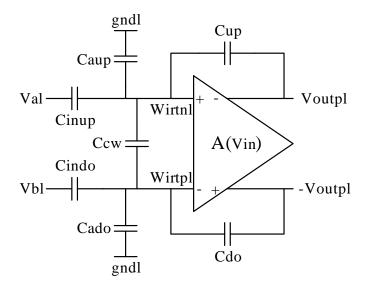

|      | the model are displayed                                                      | 72 |

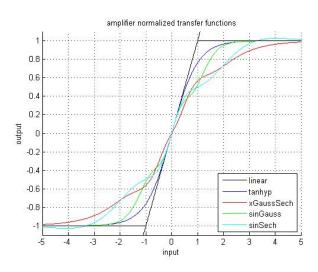

| 5.6  | Graphical representation of the normalized gain functions (5.15) of the      |    |

|      | amplifier                                                                    | 74 |

| 5.7  | Model of the amplifier with a limited output current                         | 75 |

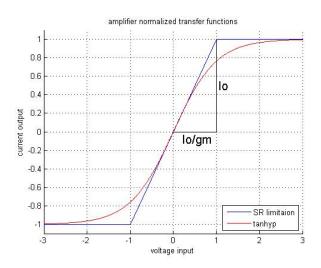

| 5.8  | Normalized amplifier transconductances with a maximal slew rate. The         |    |

|      | model of the amplifier with a constant transconductance $g_m$ and a cur-     |    |

|      | rent limit $I_0$ is described with the dark blue piecewise linear function.  |    |

|      | The red curve is the continuous hyperbolic tangent representation, sec-      |    |

|      | tion 5.1.6                                                                   | 75 |

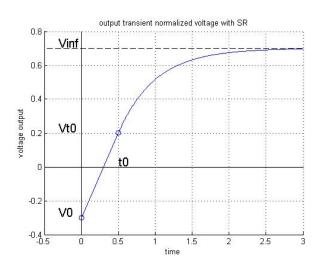

| 5.9  | Ouput transient voltage with a slewing phase between $t = 0$ and $t = T_0$   |    |

|      | followed by a settling phase for $t > T_0$                                   | 76 |

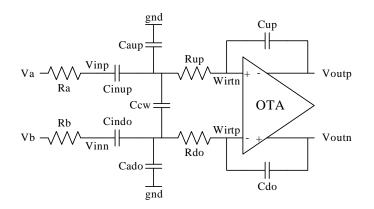

| 5.10 | Equivalent linear circuit during initialization.                             | 77 |

| 5.11 | Equivalent linear circuit during the slewing phase                           | 78 |

| 5.12 | Equivalent model of the integrator with non-ideal switches                   | 82 |

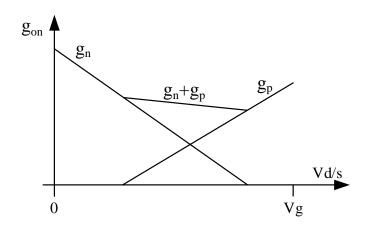

| 5.13 | Graphical representation of the equivalent conductance of a transmis-        |    |

|      | sion gate. The equivalent conductance is the sum of the conductance          |    |

|      | $g_n$ of the NMOS and of the conductance $g_p$ of the PMOS                   | 83 |

| 5.14 | Illustration of the clock feedthrough for one of the switches on high-       |    |

|      | impedance nodes. While the switch is opened, the variation of the gate       |    |

|      | voltage $V_g$ forces a charge transfer of the charges held in the Gate-Drain |    |

|      | and Gate-Source capacitors                                                   | 86 |

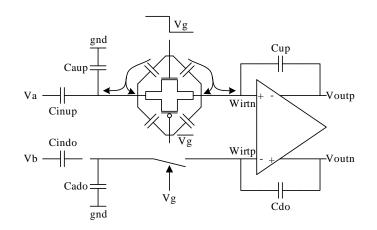

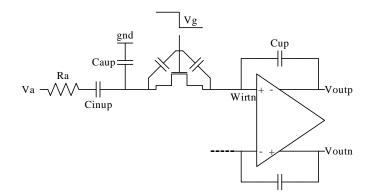

| 5.15 | Simplified representation of the charge distribution test-bench. The line    |    |

|      | and sensor impedances are modeled with a serial resistance $R_a$             | 86 |

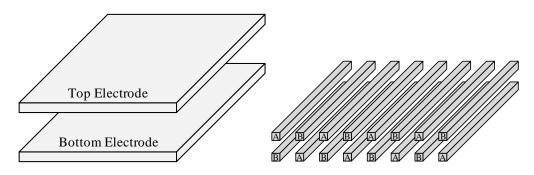

| 5.16 | (a) MIM capacitance created between two metal layers. (b) Fingers            |    |

|      | capacitance, interleaving both electrodes on each metal layer                | 88 |

| 5.17 | Equivalent model for an integrator with non-linear capacitors                | 88 |

| 5.18 | (a) Equivalent model of one of the input branches during pre-charge.         |    |

|      | (b) Small-signal representation including noise sources                      | 93 |

| 5.19 | Simplified (single-ended) representation of the equivalent input of the      |    |

|      | integrator including parasitic capacitors.                                   | 95 |

| 5.20 | (a) Equivalent simplified model of the integrator during the charge trans-   |    |

|      | fer. (b) Small-signal representation including noise sources                 | 96 |

| 5.21 | Linear and non-linear transfer functions.                                    | 97 |

|      |                                                                              |    |

| 5.22 | Non-linear transfer function with hysteresis.                                          | 97  |

|------|----------------------------------------------------------------------------------------|-----|

| 5.23 | DAC implementation with switched-capacitors.                                           | 98  |

| 5.24 | Splitting of a circuit into linear (gray) and non-linear (white) subcircuits.          | 100 |

| 6.1  | Analog and digital fundamental elements of a $\Sigma\Delta$ converter. $\ \ . \ . \ .$ | 103 |

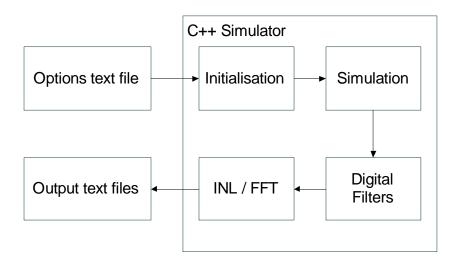

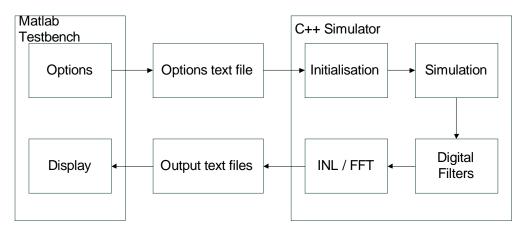

| 6.2  | IOs and main processing functions of the simulator.                                    | 108 |

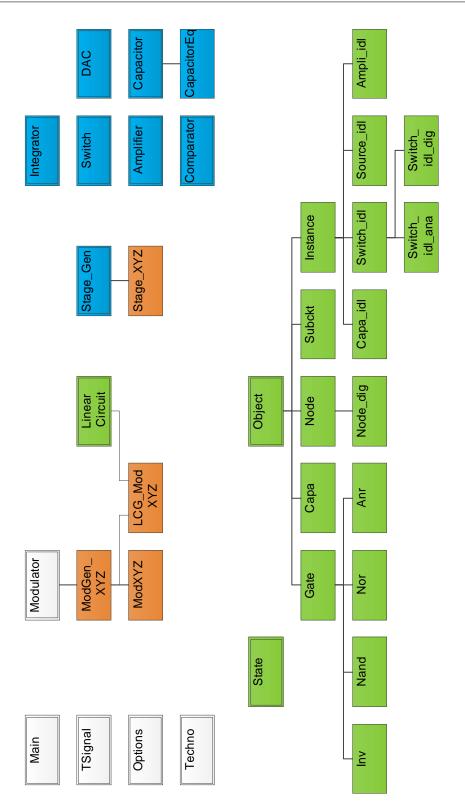

| 6.3  | Classes of the simulator. Connections are inheritance from parent class.               |     |

|      | Colors are used to distinguish the two simulators (blue - green), the                  |     |

|      |                                                                                        | 110 |

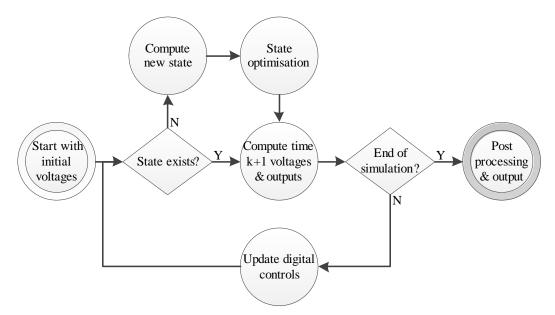

| 6.4  | Simulation flow of the linear simulator.                                               | 113 |

| 6.5  | Block view of the communication with the simulator                                     | 115 |

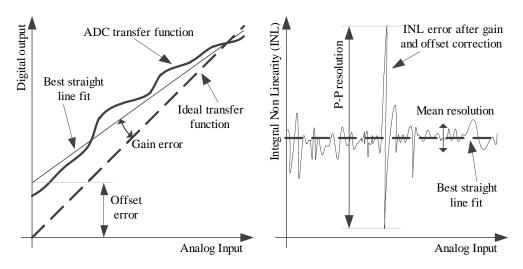

| 6.6  | Definition of gain error, offset error, INL error from the transfer function           |     |

|      | (left) and Peak-Peak and RMS resolution (right)                                        | 116 |

| 6.7  | Monte-Carlo simulation flow.                                                           | 117 |

| 6.8  | Schematic of a MASH 1-1 $\Sigma\Delta$ modulator                                       | 117 |

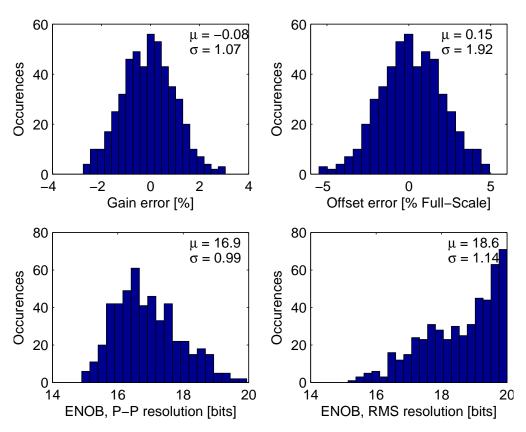

| 6.9  | Statistical distributions of gain and offset error, P-P and RMS resolution             |     |

|      | L.                                                                                     | 118 |

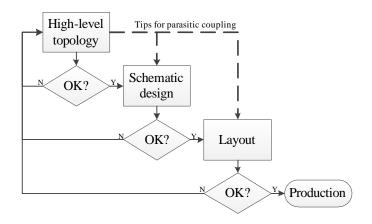

|      | Top-down design flow and contribution of the tool for parasitic coupling.              | 119 |

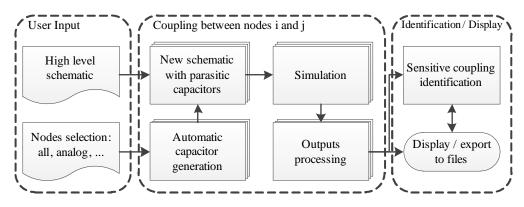

| 6.11 | Parasitic coupling simulation flow.                                                    | 119 |

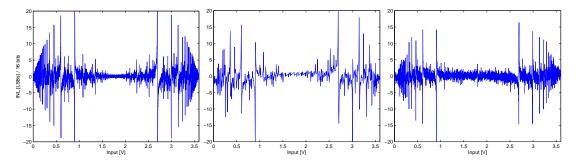

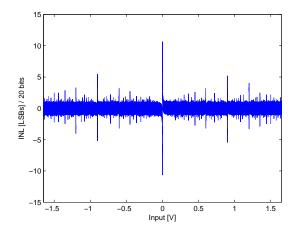

| 6.12 | INL error of a $\Sigma\Delta$ ADC with a parasitic coupling problem. Left: using pro-  |     |

|      | posed tool. Middle: using a transistor level simulator with macro blocks               |     |

|      | for amplifiers, comparators, etc. Right: measured INL. The asymmetry                   |     |

|      |                                                                                        | 120 |

|      |                                                                                        | 121 |

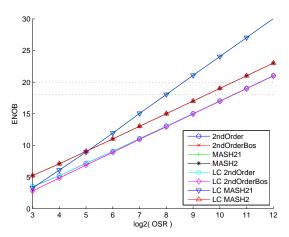

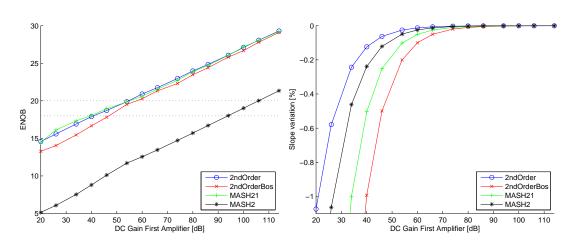

|      | 0 1                                                                                    | 122 |

| 6.15 | Simulated INL of the MASH 1-1 architecture with a finite DC gain in the                |     |

|      |                                                                                        | 122 |

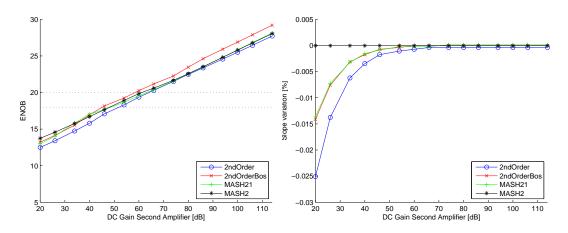

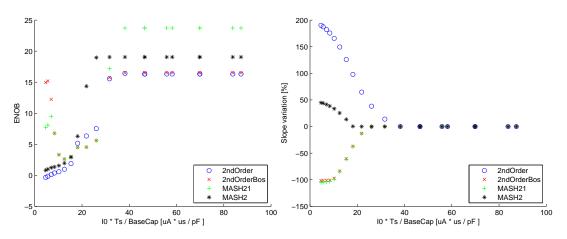

|      | Evolution of the resolution with a finite DC gain in the second amplifier.             | 122 |

| 6.17 | Evolution of the resolution with a constant integrated capacitor ( $C_{in}OSR$         |     |

|      | product). The right plot shows a thermal noise 8 times lower as the                    |     |

|      |                                                                                        | 123 |

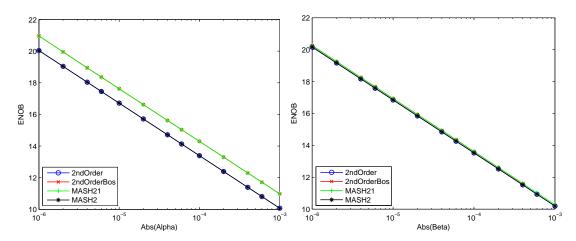

|      |                                                                                        | 124 |

|      | 1 5                                                                                    | 124 |

| 6.20 | Variation of the first-order (left) and of the second-order (right) voltage            |     |

|      | L L                                                                                    | 125 |

| 6.21 | Distortions of the INL due to parasitic capacitors.                                    | 125 |

| 7.1  | 1                                                                                      | 129 |

| 7.2  | 6                                                                                      | 132 |

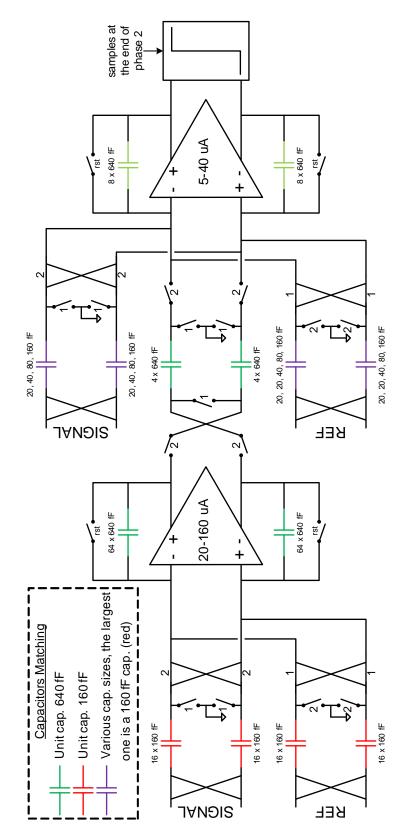

| 7.3  | First-order stage.                                                                     | 133 |

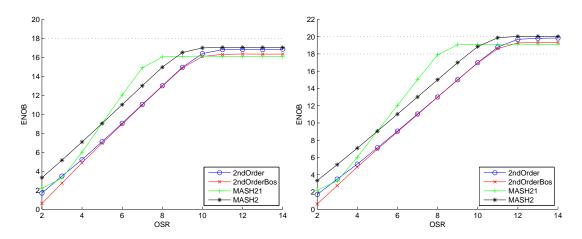

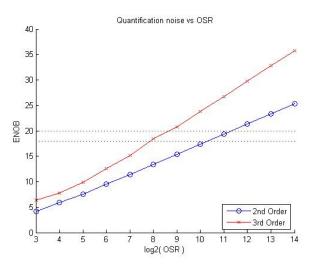

| 7.4          | Evolution of the resolution with the OSR in noiseless ideal modulators.                                                   | 133        |

|--------------|---------------------------------------------------------------------------------------------------------------------------|------------|

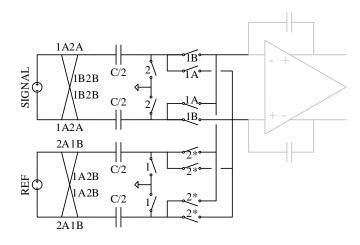

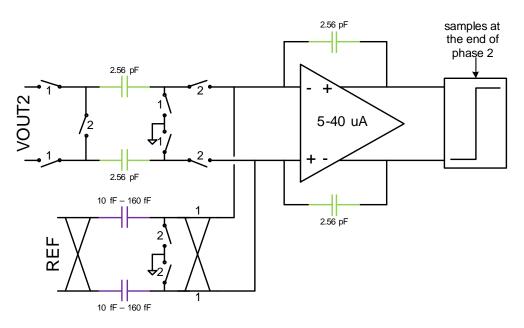

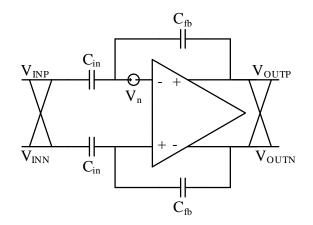

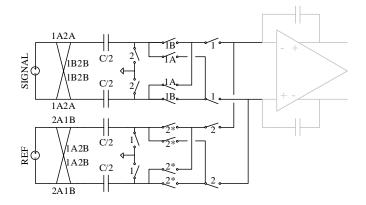

| 7.5          | Switched capacitors input with switching scheme #5                                                                        | 134        |

| 7.6          | Left: Voltage limitation implemented with capacitors. Right: implemen-                                                    |            |

|              | tation with serial resistors.                                                                                             | 135        |

| 7.7          | Distribution of the charges of the switch into the input and the integra-                                                 |            |

|              | tion capacitances                                                                                                         | 136        |

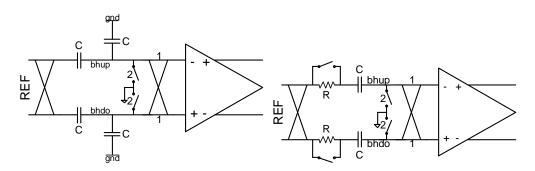

| 7.8          | Modification of the structure #5 to avoid critical capacitive parasitic                                                   |            |

|              | coupling                                                                                                                  | 138        |

| 7.9          | Charge transfer between the two first integrators. Top: direct connection.                                                |            |

|              | Bottom alternate connection                                                                                               | 139        |

| 7.10         | High-level view of the implemented architecture.                                                                          | 141        |

| 7.11         | Implementation of the first stage.                                                                                        | 143        |

| 7.12         | Implementation of the second stage.                                                                                       | 144        |

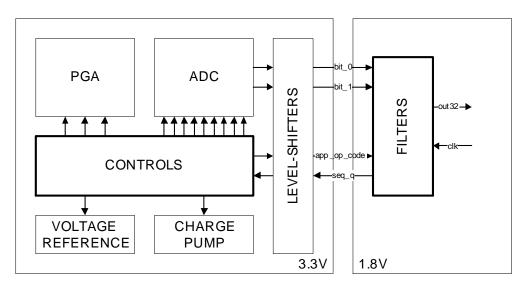

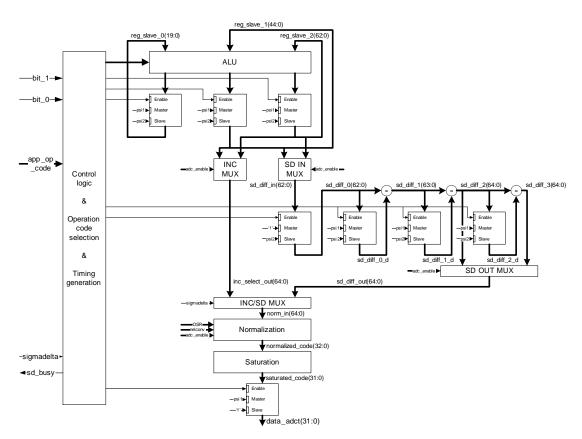

| 7.13         | General view and connections of the two dedicated digital blocks                                                          | 146        |

| 7.14         | Blocks view of the digital filters                                                                                        | 148        |

|              |                                                                                                                           |            |

| 8.1          | Acquisition chain.                                                                                                        | 153        |

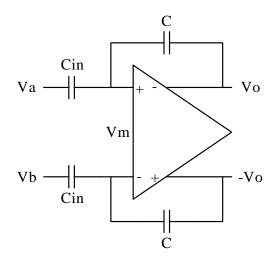

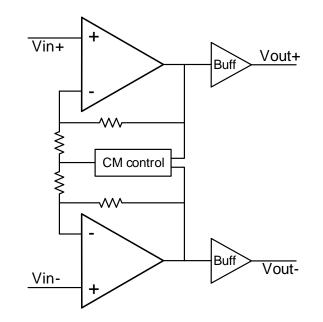

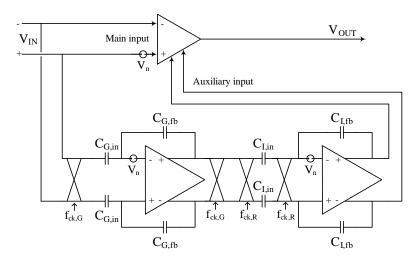

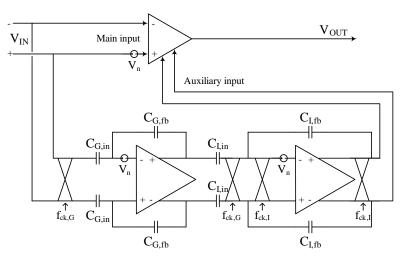

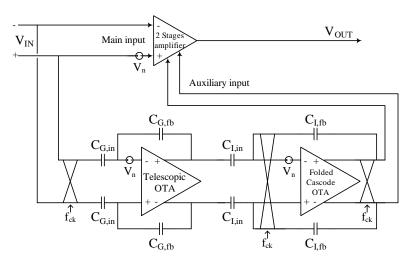

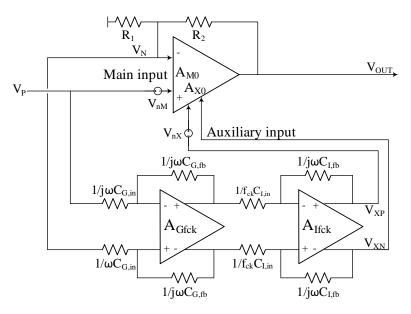

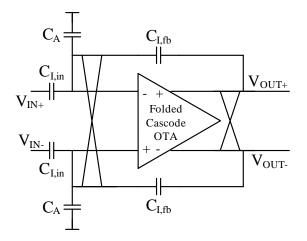

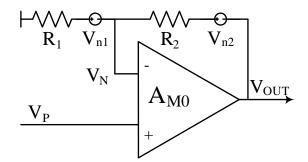

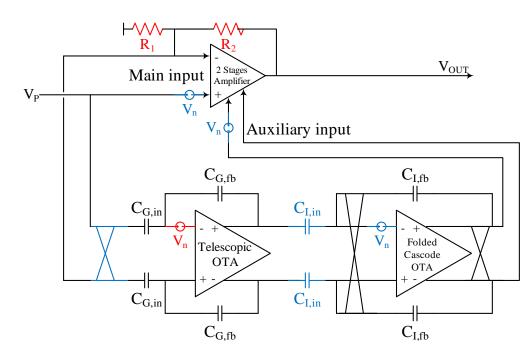

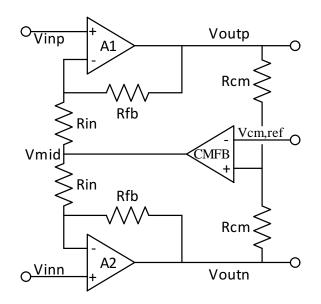

| 8.2          | Architecture of the implemented front-end                                                                                 | 154        |

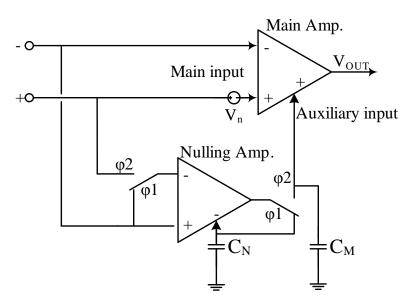

| 8.3          | Classic continuous time auto-zeroed amplifier.                                                                            | 156        |

| 8.4          | Flicker noise rejection using chopper modulation.                                                                         | 156        |

| 8.5          | Auto-zero amplifier principle                                                                                             | 157        |

| 8.6          | Switched-capacitors resistor using left: standard implementation, right:                                                  |            |

|              | symmetrical implementation with choppers.                                                                                 | 158        |

| 8.7          | Auto-zero amplifier: step 1                                                                                               | 159        |

| 8.8          | Auto-zero amplifier: step 2                                                                                               | 159        |

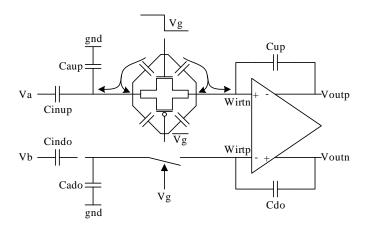

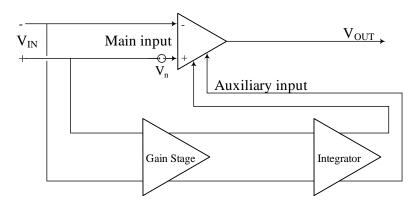

| 8.9          | Auto-zero amplifier: final implementation                                                                                 | 160        |

| 8.10         | Complex representation of the nulling amplifier in the signal baseband                                                    |            |

|              | (low frequencies).                                                                                                        | 161        |

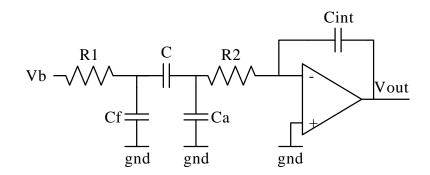

| 8.11         | Parasitic capacitors in the integrator.                                                                                   | 164        |

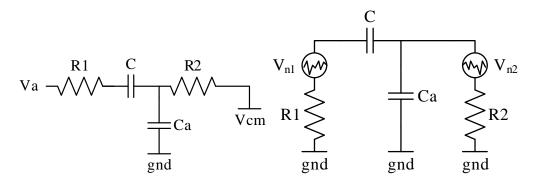

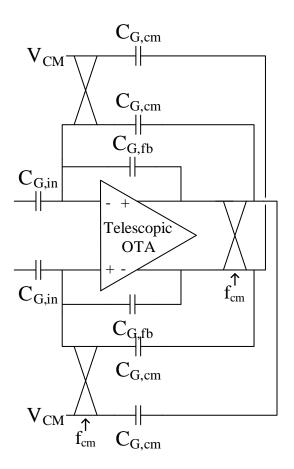

| 8.12         | Resistors noise.                                                                                                          | 165        |

| 8.13         | Gain stage input CMFB.                                                                                                    | 166        |

| 8.14         | Input-referred modulated noise.                                                                                           | 168        |

| 8.15         | Input-referred demodulated noise                                                                                          | 168        |

| 8.16         | Input-referred noise contribution of the gain stage CMFB circuit                                                          | 168        |

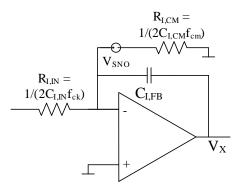

| 8.17         | Integrator input CMFB.                                                                                                    | 170        |

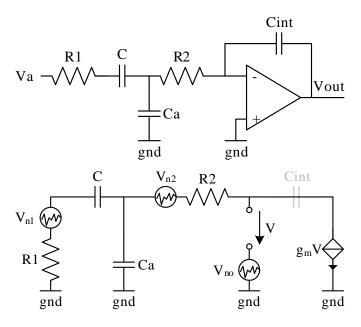

| 8.18         | Simplified (single ended) continuous-time representation of the noise                                                     |            |

|              | contribution of the CMFB circuit in the integrator.                                                                       | 171        |

| 8.19         | Auto-zero main noise sources.                                                                                             | 172        |

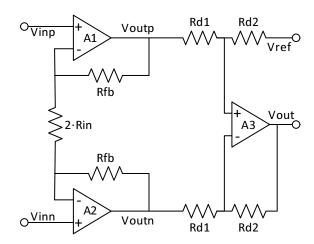

| 8.20         | Classic three-op-amp instrumentation amplifier.                                                                           | 175        |

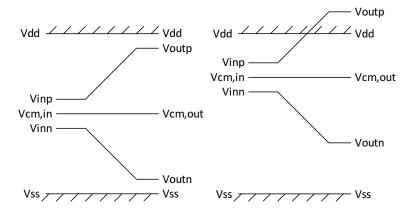

| 8.18<br>8.19 | Simplified (single ended) continuous-time representation of the noise contribution of the CMFB circuit in the integrator. | 171<br>172 |

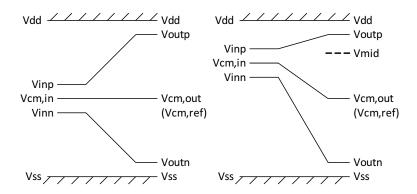

| 8.21 | Amplification of input signal with different common-mode voltages.        | 175 |

|------|---------------------------------------------------------------------------|-----|

|      | Left: Common-mode centered. Right: Common-mode close to $V_{dd}$          | 175 |

|      | Instrumentation amplifier with a controlled common-mode                   | 176 |

| 8.23 | Amplification of input signal with different common-mode voltages         |     |

|      | using the output common-mode rejection circuit. Left: Input common-       |     |

|      | mode equal to the reference common-mode. Right: Input common-             |     |

|      | mode close to $V_{dd}$                                                    | 176 |

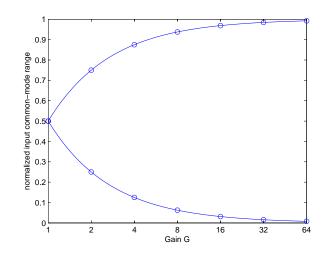

| 8.24 | Input common-mode range.                                                  | 177 |

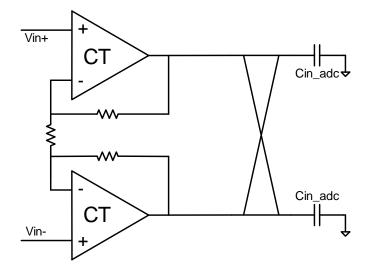

| 8.25 | Equivalent output load, including the input capacitors of the ADC         | 179 |

| 8.26 | PGA output current limitation with serial resistors.                      | 180 |

| 8.27 | PGA output structure using buffers.                                       | 180 |

| 8.28 | Output buffer.                                                            | 181 |

|      |                                                                           |     |

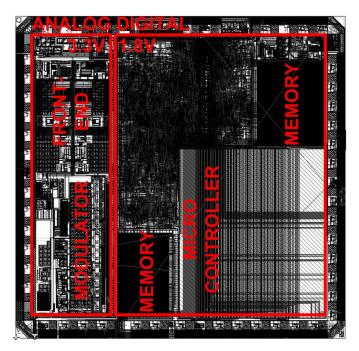

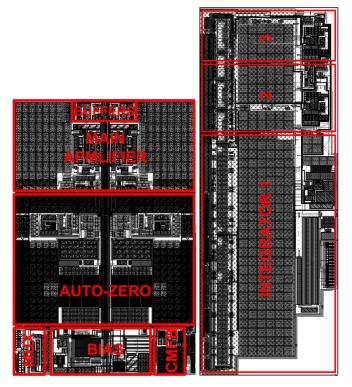

| 9.1  | Layout of the integrated circuit.                                         | 183 |

| 9.2  | Layout of the front-end (left) and of the modulator (right)               | 184 |

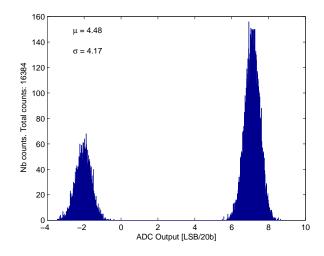

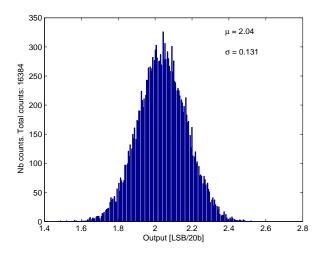

| 9.3  | Measured noise distribution caused by a reset phase too short             | 185 |

| 9.4  | Measured noise distribution of the ADC with an extended reset phase.      | 186 |

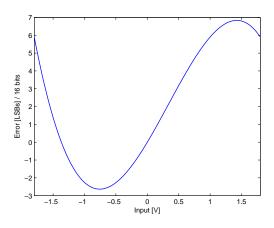

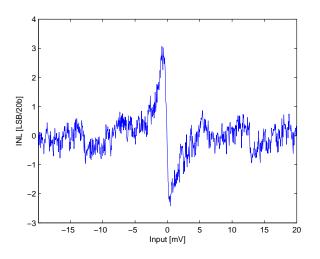

| 9.5  | Measured INL of the topology #5 around mid-scale.                         | 186 |

| 9.6  | Modified version of the topology #5. The four extra switches, named '1'   |     |

|      | and '2', are the ones connected to the virtual ground of the amplifier.   | 187 |

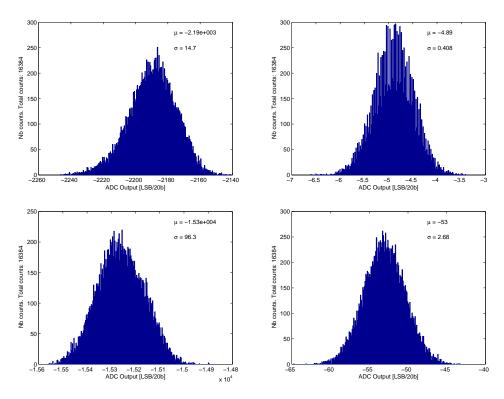

| 9.7  | Output noise distribution of the PGA without the Auto-Zero (left) and     |     |

|      | with the auto-zero enabled (right). The upper plots show the flicker      |     |

|      | noise rejection with a gain of 8, while a gain of 64 was set in the lower |     |

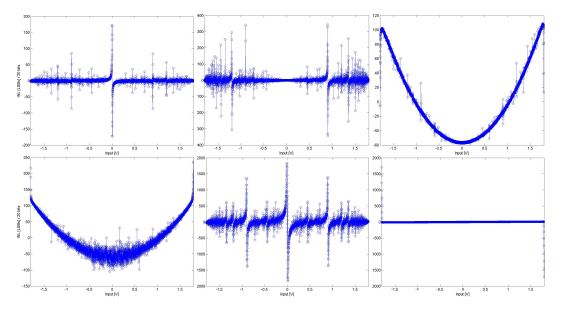

|      | plots.                                                                    | 188 |

|      |                                                                           | 100 |

## List of Tables

| 3.1 | Estimates of the three-bits codes. 1 <sup>st</sup> order modulator and constant input | 50  |

|-----|---------------------------------------------------------------------------------------|-----|

| 4.1 | Advantages and drawbacks of the selected implementations                              | 63  |

| 6.1 | Main design steps of a $\Sigma\Delta$ ADC with a top-down procedure                   | 107 |

| 6.2 | Comparison of four architectures.                                                     | 126 |

| 7.1 | Operating conditions.                                                                 | 130 |

| 7.2 | Block specifications.                                                                 | 130 |

| 7.3 | Gain error coefficients.                                                              | 151 |

| 8.1 | Auto-zero amplifier: noise summary and key characteristics                            | 174 |

| 9.1 | Performance comparison                                                                | 190 |

## **1** Introduction

This thesis is dedicated to the analysis, modeling and optimization of discrete-time analog-to-digital converters implemented with switched capacitors.

The quality of an A/D converter can be estimated with a limited set of factors, starting with the resolution. The notion of resolution may be confusing. On one hand, there is the number of bits on the digital output and, on the other hand, the noise level and the linearity of the converter. As it is possible to artificially increase the width of the digital output bus, the effective resolution is preferred in this thesis. The Effective Number Of Bits (ENOB) is taking into account the noise level of the converter.

The second main characteristic of an ADC is the sampling frequency. In most of the data acquisition devices, the user is free to exchange time for precision, i.e. select between a high resolution and a slow sampling rate or a lower resolution with a faster refresh rate.

The power consumption is the third main characteristic of the quality of an ADC. Its importance is occasionally underestimated as it is often invisible for the end user, which can neither measure nor optimize the power consumption of most electronic devices. The power consumption is nevertheless a key characteristic of a converter, as it is possible to enhance the resolution or the frequency increasing the power consumption.

Apart the three previously cited criteria, other ones influence the design. They are either dependent on fabrication costs - process, silicon area, trimming, production yield; or related to external environmental constraints - temperature range, input impedance... All these parameters strongly depend on the end use for which the ADC is sized. It is thus inconvenient to use these parameters to measure and compare the performances of data converters.

It is convenient to aggregate the three main quality factors in: resolution (ENOB or

SNR) and energy per conversion, common measure of the frequency and of the power consumption.

The elaboration of a common figure of merit including the power P and the sampling frequency  $f_s$  is subject to controversy. Two FOM are nevertheless widely spread. The first one is:

$$FOM_1 = \frac{P}{2^{ENOB} f_s} \tag{1.1}$$

Historically the oldest one, it is not suited for converters in which the thermal noise dominates (i.e.  $NSD \propto kT/C$  or  $NSD \propto 4kTR$ ), as for each extra bit the power consumption is increased by a factor 4.

The second figure of merit, mainly used to compare high-resolution converters is:

$$FOM_2 = \frac{P}{2^{2ENOB} f_s} \tag{1.2}$$

Obviously, the best way to agree with both definitions would be to compare only converters with identical resolutions.

The resolution of oversampling data converters is limited by three main factors:

- The quantization noise: Determined by the order of the converter. There is no direct relationship between the quantization noise and the sampling frequency or the power consumption.

- The thermal and the flicker noises: The thermal noise is proportional to the power consumption (or to the frequency if an averaging is possible). The noise power of 1/f noise sources is inversely proportional to the current consumption and to the gate area of active transistors. As the spectrum of the 1/f noise is not white, circuit techniques are commonly implemented to reduce its level in the signal baseband.

- Circuit imperfections: Non-ideal effects of the analog part of the converter. Fundamentally, these effects are not directly related to the frequency or to the power consumption.

While the first two limitations - quantization and thermal/flicker noises - are well known and are easily estimable, it is more fastidious to take the last category into account.

Reducing the non-ideal effects requires a special care and a very good knowledge of the architectures and implementations of the converters. Most of the design effort should thus be invested to guarantee a negligible degradation of the resolution and a minimal consumption overhead.

### 1.1 Problems and Imperfections

The designer of a  $\Sigma\Delta$  modulator should be aware of the design issues limiting the resolution of the converters. The non-ideal effects may be classified into two main groups: first the ones related to the base components and then the ones related to the architecture. The best-known limitations for the blocks are:

- Amplifiers: Offset, finite gain, non-linear gain, limited bandwidth and slew-rate.

- Switches: On-resistance, clock feedthrough.

- Quantizers: linearity, hysteresis.

- DACs: Mismatch, non-linearity.

Furthermore, the problems related to the signal dynamic range and to the closed loop architecture of the  $\Sigma\Delta$  modulator have also to be taken into account:

- Saturation of the amplifiers.

- Excessive loop delay.

- Noise shaping and noise rejection.

- Loop stability.

- Insufficient common-mode rejection.

- Excessive signal amplitude (loss of charges through the power supplies).

In addition to problems related to the analog modulator, it is also necessary to check the analog-digital interfaces to ensure that the control signal are driving in a correct order the analog switches (in particular if the driving signals are passing through level shifters, or if non-overlap conditions should be guaranteed). Parasitic couplings between analog signals, and from digital to analog signals, have also to be taken into account.

Most of the architectural problems are related to the implementation of the integrators with switched capacitors. E.g., excessive signal amplitude at the output of amplifiers can be reduced increasing the integration capacitors. Loop delay may also be adjusted using appropriate switching phases.

### 1.2 Selected approach

The selected approach in this thesis to study, design and optimize high-resolution converters is the following:

• Modeling: Two key elements are missing to fulfill the design toolset: an efficient

validation of the implementation and a verification of the parasitic coupling in a reasonable time. As the implementation of  $\Sigma\Delta$  modulators with switches and capacitors is not integrated into existing high-level simulation tools, models have to be developed and integrated into a dedicated simulator. The simulator has to account for commonly known non-ideal effects to precisely evaluate the quality of  $\Sigma\Delta$  topologies.

- **Comparative study** based on a limited number of architectures. The aim of the comparison is firstly to validate the models and the simulator with existing circuits and secondly to compare accurately several implementations with switched capacitors.

- **Design** of a switched capacitors incremental converter following a top-down methodology. The choices of implementation and the optimization of the blocks are carried out with the developed simulator.

The modulator is the key component of any  $\Sigma\Delta$  acquisition chain. However, it is possible to improve the resolution with pre- and post-processing.

- **Digital filters**: Classic linear filters perform a weighted average of the output stream of the modulator. The hypotheses on the quantization noise considered as white noise lead to a suboptimal estimation of the input signal. The gradual shift to submicron technologies reduces the costs (power consumption and silicon area) of the digital, while improving the available features. Non-linear filtering is studied to improve the decoding of the output of the modulator.

- **Front-end**: The best performances of data converters are obtained when the range of the input signal is close to full-scale. In order to be compatible with a large selection of sensors, pre-processing of the analog signal may be accomplished in a prior gain stage. The aim of the front-end is on one hand to amplify the signal and, on the other hand, to provide an input impedance for sensors with limited output current.

### 1.3 Thesis outline

The next chapter provides the necessary bases to understand  $\Sigma\Delta$  modulators. The linear model is introduced and the most common architectures are discussed. Differences and tradeoffs of the main categories of architectures are briefly stated.

Chapter 3 studies optimal filters. It shows that useful information on the input signal is lost with linear filters and provides algorithms to enhance the resolution. Several architectures are covered assuming various hypotheses on the input signal: constant input, sweep input and constant with Gaussian noise.

Chapter 4 compares implementations with switched capacitors. Ten types of input connection achieving the same high-level functionality are analyzed. The main performances - noise, power consumption - are compared, as well as the sensitivity to non-ideal effects.

Chapter 5 models  $\Sigma\Delta$  converters. The integrator is first modeled, including best known limitations in switched capacitors topologies. Secondly, a linear model is expressed to model the full modulator and account for capacitive parasitic coupling. In both cases, special care is taken to minimize the required mathematical complexity.

Chapter 6 introduces a simulator. A comparative review of existing tools discusses first the features of the simulator. An object-oriented software architecture is then defined to be compatible with a large selection of  $\Sigma\Delta$  ADC topologies. The scope of operations of the simulator is finally exhibited through a comparative study of four existing converters.

Chapter 7 discusses the design of a  $\Sigma\Delta$  ADC in a top-down methodology. This design example takes advantage of prior studies and of the simulator to define an architecture suited for ultra-high resolution converters. Each critical design issue, identified with the developed tools, is discussed.

Chapter 8 introduces a new architecture for a low-noise low-power front-end. A novel common-mode control for instrumentation amplifiers is discussed. A detailed analysis is then performed on an auto-zero amplifier with a fully differential cancellation path to optimize the noise and power consumption performances.

Chapter 9 provides the results measured on the implemented ADC and discusses the observed limitations.

Finally, chapter 10 concludes this thesis, highlights the main contributions and provides suggestions for future developments and improvements.

## 2 Basic concepts

This chapter briefly introduces the basic concepts of  $\Sigma\Delta$  A/D conversion and reviews the common architectures.

This chapter is not intended to cover in details all aspects of  $\Sigma\Delta$  modulation; instead, it provides the information necessary to understand the next chapters.

### 2.1 Sampling and oversampling

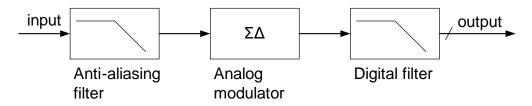

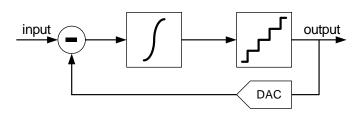

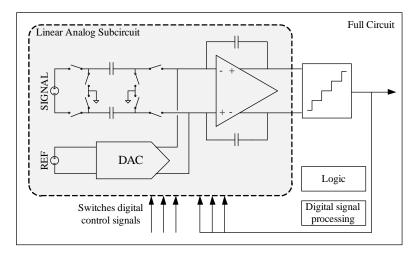

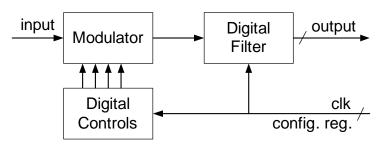

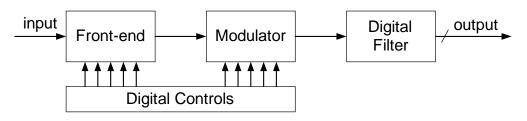

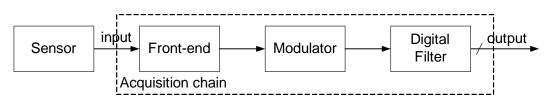

Figure 2.1 shows a block diagram of a  $\Sigma\Delta$  A/D converter that includes an anti-aliasing filter, a modulator and a digital filter.

Figure 2.1: Block diagram of a Sigma-Delta A/D converter.

The anti-aliasing filters suppresses the signal spectral components over half of the sampling frequency. One of the main benefits of the oversampling converters is the relaxation of the requirements of this filter. Indeed, a sharp cut-off is not required, and a first-order filtering is usually sufficient.

The modulator samples and quantizes the signal. In addition to these two operations performed by any A/D converter, a  $\Sigma\Delta$  modulator shifts most of the energy of the quantization noise out of the signal baseband. This effect is named noise shaping. The output of the modulator is a digital stream at the oversampling frequency with a limited number of levels.

The signal then enters in the digital filter. The aim of the filter is firstly to suppress the high-frequency components of the modulated signal and then to under-sample the signal to the Nyquist frequency.

The output of the converter is finally a representation of the input signal, coded in a large number of bits, at the Nyquist rate.

## 2.2 Quantization error and noise shaping

Amplitude quantization of a signal is required in any A/D conversion. In a  $\Sigma\Delta$  modulator, a flash converter with a limited number of levels (usually between 1 and 5 bits) is used.

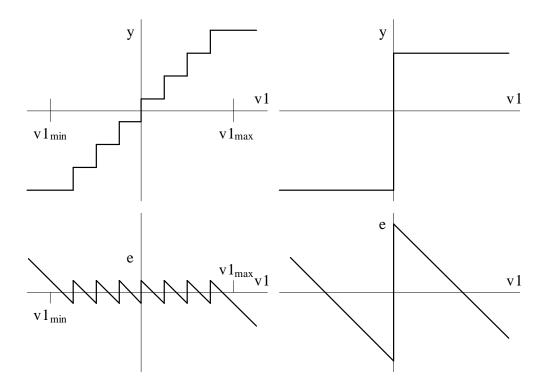

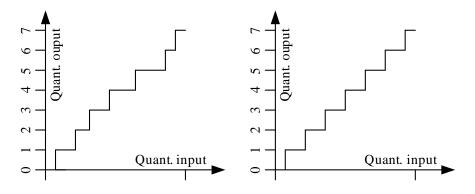

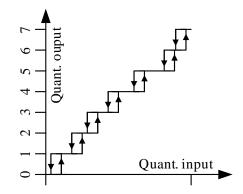

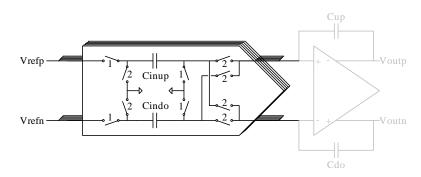

The transfer function of an ideal quantizer is shown in Fig. 2.2. In a multi-level comparator, an input range is defined, beyond which the quantizer is saturated at a constant value. If the quantizer is single-bit (comparator), the output is always saturated and toggles as soon as the comparison threshold is crossed. The input range is thus not defined in a comparator.

Figure 2.2: Transfer functions and quantization error of (left) multi- and (right) singlebit quantizers.

The difference between the input signal of the quantizer  $v_1[k]$  and its output y[k] is

called quantization error, e[k].

$$y[k] = v1[k] + e[k]$$

(2.1)

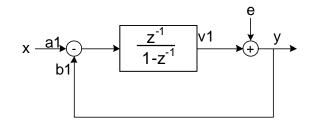

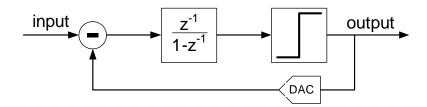

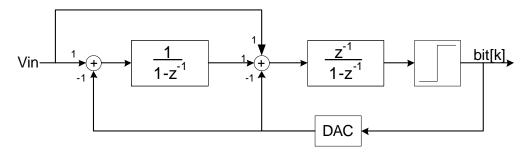

The linear representation of the first-order  $\Sigma\Delta$  modulator is illustrated in Fig. 2.3. Such a linear view allows deriving the transfer functions for the signal (STF) and for the quantization noise (NTF).

Figure 2.3: Linear representation of the first-order  $\Sigma\Delta$  modualtor.

The analysis of the linear representation of the first-order system with unit coefficients leads to the following results:

$$STF = \frac{y}{x} = z^{-1}$$

$$NTF = \frac{y}{e} = 1 - z^{-1}$$

$$v1 = z^{-1}x - z^{-1}e$$

(2.2)

The STF exhibits an all-pass response and the NTF provides a first-order high-pass filtering.

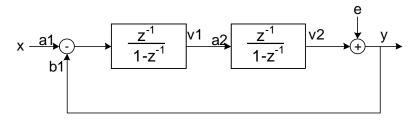

### 2.3 Feedback and feedforward modulators

The most straightforward method to construct high order modulator is to cascade several integrators in the forward path. However, the direct implementation, Fig. 2.4, is unstable.

Figure 2.4: Second-order unstable modulator.

Two structures are commonly used to stabilize the modulator. In the first one called a Cascade of Integrator with distributed FeedBack (CIFB) [1, 2], each integrator receives feedback from the quantizer. Alternatively, weighted feedforward can be added in a Cascade of Integrators with weighted FeedForward summation (CIFF) [3, 4].

#### 2.3.1 Feedback structure

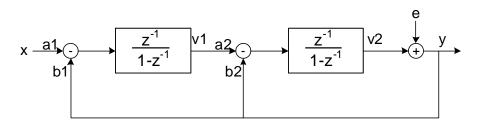

The feedback topology is illustrated for a second-order modulator in Fig. 2.5.

Figure 2.5: Second-order CIFB modulator.

The analysis of this topology with the coefficients a1=a2=b1, b2=2 leads to the following results:

$$STF = \frac{y}{x} = z^{-2}$$

$$NTF = \frac{y}{e} = (1 - z^{-1})^{2}$$

$$v1 = z^{-1} (1 + z^{-1}) x - z^{-1} (1 - z^{-1}) e$$

$$v2 = z^{-2} x - z^{-1} (2 - z^{-1}) e$$

(2.3)

The STF is flat and the NTF is a second-order high-pass filter. The main disadvantage of this configuration is that the signals at the output of the amplifiers, v1 and v2, are a function of the input signal x. In this feedback structure, the design of the amplifiers is difficult, firstly because a large output dynamic range is required and secondly because the non-linearity of the amplifiers distorts the transfer function of the ADC.

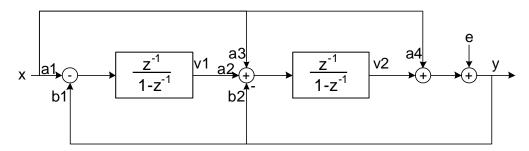

The signal-dependent term in (2.3) may be suppressed injecting the signal at the output of the amplifiers. The generalized version of the CIFB structure, sometimes named CIFB with Input Feedforward is displayed in Fig. 2.6.

This structure with the coefficients a1=a2=a4=b1=1, a3=b2=2 leads to a flat STF and ensures that the output of the integrators v1 and v2 are not correlated with the input signal<sup>1</sup>. The NTF remains identical than in (2.3).

<sup>&</sup>lt;sup>1</sup>Assuming that the quantization error is stochastic and thus not correlated with the input signal.

Figure 2.6: Second-order CIFB modulator with input feedforward.

Besides the extra load on the input and the increased complexity of the circuit, one of the main disadvantages of this structure is the delay-free path from the input, through the quantizer, and back to the input of the modulator [5].

The independence of v1 relatively to the input signal may however be partially guaranteed in an architecture without any direct path from the input to the quantizer. An example of implementation is shown in Fig. 2.7.

Figure 2.7: Second-order CIFB modulator with input feedforward.

The transfer functions of the structure, Fig. 2.7, are:

$$STF = \frac{y}{x} = z^{-1} (2 - z^{-1})$$

$$NTF = \frac{y}{e} = (1 - z^{-1})^{2}$$

$$v1 = (1 - z^{-1}) x - (1 - z^{-1}) e$$

$$v2 = z^{-1} (2 - z^{-1}) x - z^{-1} (2 - z^{-1}) e$$

(2.4)

If the oversampling frequency is much larger than the input signal frequency, the output of the amplifier v1 is only related to the quantization error. The output of the second amplifier is still proportional to x, however, the design constraints on the second amplifier are less restrictive.

The drawback of this implementation is the non-constant STF. In particular, the STF exhibits a gain of 3 at half of the oversampling frequency. This amplification of out-ofband frequencies is not critical for converters with large oversampling ratio, but adds more constraints on the anti-alias filter in ADCs with limited OSR.

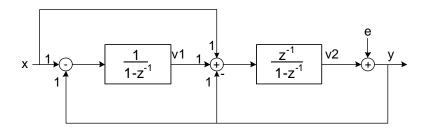

### 2.3.2 Feedforward

The second common way of ensuring stability in high-order  $\Sigma\Delta$  modulators is to add forward paths to the quantizer. The generic structure of CIFF with input feedforward is illustrated in Fig. 2.8 for a second-order modulator.

Figure 2.8: Second-order CIFF modulator with input feedforward.

The coefficients<sup>2</sup> a1=a2=b1=1, a3=2, a4=0 lead to the following results:

$$STF = \frac{y}{x} = z^{-1} (2 - z^{-1})$$

$$NTF = \frac{y}{e} = (1 - z^{-1})^{2}$$

$$v_{1} = (1 - z^{-1}) x - (1 - z^{-1}) e$$

$$v_{2} = z^{-2} x - z^{-2} e$$

(2.5)

The main characteristics, STF, NTF and output of the first integrator (v1) are identical to the ones of the CIFB structure, Fig. 2.7. The output of the second integrator is slightly less sensitive to the quantization error, but remains proportional to the input signal

The previous analysis showed that the basic characteristics of the feedback and of the feedforward structures are equivalent. The drawbacks of each topology emerge during the implementation. A CIFF modulator requires an extra adder before the quantization and loads more the output of the first amplifier. Both feedback paths in the CIFB structure must be properly matched to avoid a mismatch between the analog and the digital.

<sup>&</sup>lt;sup>2</sup>Here as well, the a4 coefficient is zero to avoid a direct path from the input to the quantizer

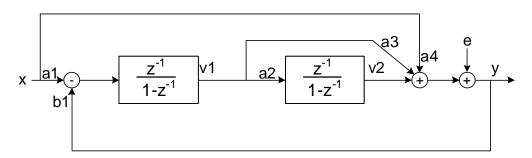

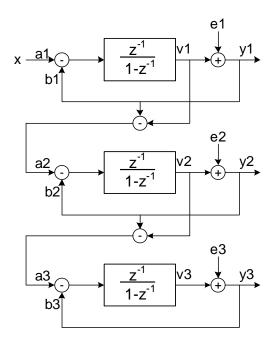

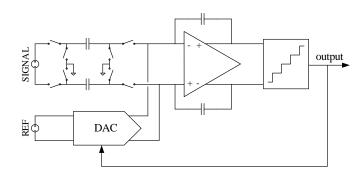

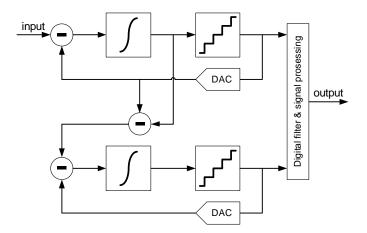

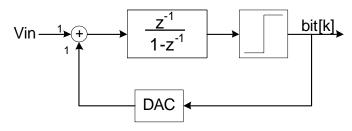

### 2.4 Cascaded modulators

Single-stage modulators shift the quantization noise out of the signal base-band. Another technique to lower the quantization noise is to measure and subtract it. In cascaded, or MASH, topologies, each modulator (stage) measures the quantization noise of the previous stage. The bit-streams are then combined in the digital logic in order to cancel the quantization noise of all stages, excepting the last one.

A third-order cascaded ADC is shown in Fig. 2.9. This converter is named MASH 1-1-1 as each stage is a first order modulator.

Figure 2.9: MASH 1-1-1 modulator.

Cascaded ADCs made of first- or second-order modulators are stable by construction. Moreover, for identical order and OSR, the quantization noise is lower than in singleloop topologies. The drawback of the cascaded architecture is the good matching required between the analog and digital circuits [6]. Particularly, for high-resolution ADCs, an excellent matching of the capacitors, a long enough settling time as well as a huge DC gain of the amplifiers are needed.

MASH converters are better suited for modulators with limited OSR. They are thus mainly used in fast ADCs with limited resolution [7].

### 2.5 Sigma-Delta or Incremental converters

The difference between  $\Sigma\Delta$  converters and incremental converters is the reset of the integrators before each conversion in incremental modulators.

In incremental ADCs, the successive samples are not correlated. These data converters are thus suited for multiplexed inputs, when the input signal is delivered by distinct sensors. The second advantage of these converters is the suppression of the idle tones, visible in  $\Sigma\Delta$  ADCs for static inputs<sup>3</sup>.

The generation of the clocks is however more complicated as extra phases for the resets have to be created. Moreover, the sampling of the signal is not uniformly spread over time as no sample is acquired during the reset phases.

The analog implementation of  $\Sigma\Delta$  and incremental converters is almost identical. Digital filters are on the other side fundamentally different. In  $\Sigma\Delta$  converters, a sinc filter is applied. The order of the filter is equal to the order of the modulator plus one. E.g. in a second-order modulator with an OSR of 4, the filter is:

$$H_{s}(z) = \left(1 + z^{-1} + z^{-2} + z^{-3}\right)^{3}$$

= 1 + 3z^{-1} + 6z^{-2} + 10z^{-3} + 12z^{-4} + 12z^{-5} + 10z^{-6} + 6z^{-7} + 3z^{-8} + z^{-9} (2.6)

In incremental converters, the filtering philosophy is different. After each cycle of the modulator, the output of the last integrator res[k] is estimated, and a portion of the reference is added or subtracted. After OSR cycles, the residue within the last integrator is a weighted sum of the input and of the reference:

$$res[OSR] = \sum_{k=0}^{OSR-1} (OSR - k) (x[k] - bit[k])$$

(2.7)