# High Performance, Vertically Stacked SiNW/Fin Based 3D FETs for Biosensing Applications

#### THÈSE Nº 6258 (2014)

PRÉSENTÉE LE 27 JUIN 2014

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DES DISPOSITIFS NANOÉLECTRONIQUES

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

#### Elizabeth BUITRAGO GODINEZ

acceptée sur proposition du jury:

Prof. M. Gijs, président du jury

Prof. M. A. Ionescu, Dr M. Fernandez-Bolanos Badia, directeurs de thèse

Dr U. Dürig, rapporteur

Prof. A. van den Berg, rapporteur

Prof. L. G. Villanueva Torrijo, rapporteur

## Acknowledgements

I want to thank Prof. A.M. Ionescu for giving me the opportunity to work at the Nanolab, for his trust, for giving us so much freedom to explore, mature and become better engineers and scientists. Though sometimes hard to find, your advice is always thoughtful, insightful and it shows you care about your students. You also have a hilarious side by the way. You, Karin and Isabelle have created a lab where people are happy to be at, I will miss the Nanolab. Isabelle and Karin, thank you for all your help you are truly the best. Marie Halm, you go above and beyond to help us and are always super kind and welcoming, thank you for being so great. To my wonderful PhD jury and president: Dr. Urs Duerig, Prof. Van den Berg, Prof. Guillermo Villanueva, and Prof. Martin Gijs thank you for your fair and kind comments about my work. Thank you for your critical assessment about what was missing and for all your input. I really appreciate that you took the time and effort to review my thesis. To my fellow Nanolabers: Alejito Russu, Livio Lattanzio, Luca De Michielis, Mariazel Maqueda, Emmanuel Casu, Pankaj Sharma, Wladek Grabinski, Antonios Bazigos, Sara Rigante, Cem Alper, Sebastian Bartsch-Garcia Marquez, Wolfgang Vitale, Clara Moldovan, Matthieu Bartolome and Nilay Dagtekin and EPFL friends: Lucian Barbut, Enver Kilinc, Nasibeth Pouransi, Banafsheh Abasahl, and Hamide Jafarpoorchekab you have enriched my life in Lausanne and helped me greatly during my PhD, thank you. Especially Banita and Hamide you girls have taught me a lot, it has been a pleasure to have you as a friend. To the other two of the "trío fantástico:" Arnab Biswas (aka. Anoldo) and Hoel Güerin (Hoelino), thank you for being so funny all the time. Arnoldo I know you will miss me but you can come visit us whenever you want. Hoelino who am I gonna complain about life in general with now? A mi "office-mate" y post-doc personal, y la mejor co-supervisora, algún día, en otro lugar hablaremos en Español siempre, gracias por todo. You have been a great friend, I am really glad we got to spend all this time together, your advice and attitude in life is always positive and I will forever remember your face during my defense ©. To my colleagues and friends from Tyndall (Giorgos Fagas, Ran Yu, Olan Lotti, Yordan Georgiev) and Imperial (Adrian Nightingale), it was a pleasure to work with

you. Yordan, thank you for all your kind advice and great sense of humor. We have to work together again. Thanks to my master students Xander Van Kooten and Natacha Berthaut for their hard work during your time at the Nanolab. To the staff of the CMi, in particular Didier Bouvet, Cyrille Hibert, Phillipe Flückiger, Claudia D'Agostino, Kevin Lister, Zdenek Benes, Joffrey Pernollet, Antony Guillet, and Laszlo Petho thank you for your support and mentoring, you make the work of many people at EPFL possible.

To my love Mat, ten years, two continents, eight cities, at least twelve moves, three degrees, four universities, three jobs and millions of yummy tortillas later, thank you for loving me, taking care of me and always pushing me forward. I love you, the PhD is for the two of us. To Ruth, Bernhard and Oma Berchtold, thank you for being my wonderful Swiss family, believing in me and caring for me. I am really grateful to have you in my life. A mi familia, especialmente a mamá Luz, papá Ramón, Karina, Gustavo, Martha, Carmen y Ramón gracias por estar siempre conmigo aunque sea de lejos. Sin ustedes nunca se hubiera podido lograr nada. Tama, Penny, Julie, my little girls always make smile, I am proud of you. To Karina and Martha especially, you have been my biggest supporters and inspiration, where would I be without you? You are my aunts, sisters, mothers, everything. I love you. A Gustavo, there are no words to describe my admiration for you, I couldn't pick a better farther, but you did pick me, thank you. A papá Ramón, gracias por siempre decirme que yo iba ser presidenta de México, todavía no, pero ahí vamos. A mamá Luz, me parezco tanto a ti que me da miedo. Ma, te admiro de muchas maneras y sin ti mi vida no seria lo mismo, pero por que no te portas bien? Los amo y les debo todo a ti y a papa Ramón. To my mother, I have never ever known somebody with so much drive to work, study and be happy no matter what, even in the worst most painful of times. I wish I had an ounce of your sarcastic sense of humor. I miss you, love you and think of you every day.

## **Abstract**

Nanostructured 3D materials such as vertically stacked silicon nanowires (SiNW) and Fins have long been suggested as promising candidates for a myriad of sensing applications. Such structures are of great interest for implementations that could particularly benefit from the possibility of detecting bio-important molecules at ultra-low concentrations with high selectivity. Nonetheless, their integration into bio-compatible electronic devices has proved challenging. To achieve commercial success into the highly stringent medical device market for example, their fabrication by cheap yet reliable mass production methods needs to be positively attained. Careful design of the fabrication process flow is further complicated when dealing with possibly fragile structures that need to operate reliably in a liquid (possibly corrosive) environment and perfect protection for the integrated circuit (IC) components is mandatory. In this work, 3D vertically stacked silicon nanowire and Fin field effect transistors (FETs) featuring a high density array (up to 8 × 20 SiNWs, > 4 Fins vertically stacked) of fully depleted, ultra-thin (SiNWs diameters down to dnw ~ 15 - 30 nm, Fin width/height  $F_w \sim 30$  nm/ $F_h \sim 150$  nm), long (L < 10 µm) and suspended channels have been successfully designed and fabricated by a top-down, complementary metal oxide semiconductor (CMOS) compatible process on silicon-on-insulator (SOI) and bulk-Si substrates. Through a clever design, optimization of critical steps, and by simply leaving the stacked nanostructures within their SiO<sub>2</sub> enclosure until the end of the fabrication process (at which point they can be easily released in a buffered oxide etch) it is possible to produce robust, uniform and reliable electronic biosensor devices. Our fabrication scheme is competitive in terms of scaling and NW density (with a vertical density as high as 10 SiNWs/µm) in comparison to other bottom-up and top-down approaches with the added benefit of using a CMOS-compatible, high yield (> 90%) and reproducible process.

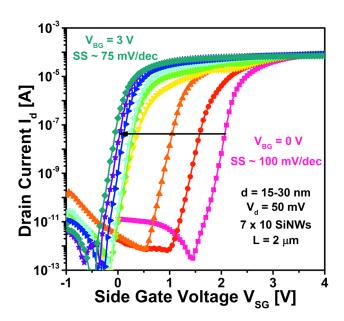

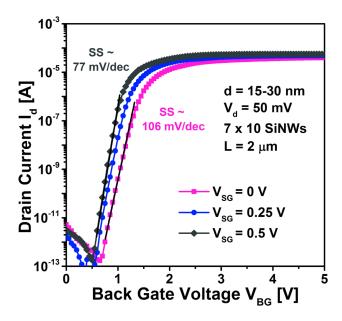

SiNWs and Fins (single or one level arrays) continue to draw great interest as biological sensors having the potential to provide low cost, real time, label-free, ultra-sensitive and selective (through surface modification) detection for a countless number of analytes. The nanoscale dimensions give rise to large surface to volume ratios (S/V) and consequently to high sensitivities due to an improved gate electrostatic control (nanoscale cross sections) and a large surface area for biomolecule attachment (sensing). The vertical stacking in our structure allows for higher utilization of the Si substrate, high output currents and high chances for biomolecule interaction as the number of conduction channels increases in two directions (Z, X). Also, as the NWs/Fins are suspended, their entire surface area is exposed to the sensing analyte for detection. The configuration of the 3D sensor additionally offers excellent electrostatic control of the channels by the possibility of applying symmetric or asymmetric gate potentials to tune the subthreshold slope (and hence the sensitivity) and optimize the power consumption. The vertically stacked liquid-gated FET structures produced here additionally show superb transistor characteristics with low drain leakage currents  $I_{off}$  < 20 × 10<sup>-6</sup> mA/ $\mu$ m, high on-currents  $I_{on}$  > 1 mA/ $\mu$ m (normalized to nanowire diameter  $d_{NW}$  = 30 nm), high  $I_{on}/I_{off}$  ratios > 106, great maximum transconductance values  $g_m$  > 10  $\mu$ S and subthreshold slopes  $SS = d(V_{Ref})/d(log_{10}I_d)$  as low as 85 mV/dec in an electrolyte solution. An excellent  $I_d - V_{SG}$  subthreshold slope of ~ 75 mV/dec was achieved (in isopropanol) with the suspended structures thanks to the high backgate coupling that controls the SS as the  $V_{BG}$  increases (~ 100 mV/dec when  $V_{BG}$  = 0 V vs. ~ 75 mV/dec when  $V_{BG}$  = 1.5 V). State-of-the-art detection of ultralow concentrations of the protein streptavidin (~ 17 aM) with a biotinylated SiO2 gate dielectric was successfully demonstrated (with large current changes ~ 500 nA). Furthermore, high, long-term and reproducible pH sensing responses with a drain current change per pH value  $\Delta I_d/pH$  of up to 0.8 dec/pH were also achieved with a (3-Aminopropyl)-triethoxysilane (APTES) modified SiO<sub>2</sub> sensor gate dielectric (when operated in the subthreshold regime). Finally, a vertically stacked SiNW FET fabricated on bulk-Si was efficiently realized as a proof-of-concept device for its future implementation into low cost biosensing systems. Keywords: SiNW, FinFET, sensor, biosensor, 3D, vertically stacked, bio-FET, ISFET, streptavidin, pH sensor.

## Zusammenfassung

Nanostrukturierte 3D Materialien wie vertikal gestapelte Silizium-Nanodrähte (SiNW) und Fins sind seit langem als vielversprechende Kandidaten für eine Vielzahl von Sensoranwendungen vorgeschlagen worden. Solche Strukturen sind von großem Interesse für Implementierungen die besonders von der Möglichkeit profitieren könnten, bio-wichtige Moleküle bei extrem niedrigen Konzentrationen mit hoher Selektivität zu erkennen. Dennoch hat sich ihre Integration in biokompatible elektronische Geräte als Herausforderung erwiesen. Für einen kommerziellen Erfolg, beispielsweise im hochstringenten Markt für medizinische Geräte, ist die Herstellung mit kostengünstigen und dennoch zuverlässigen Methoden der Massenproduktion erforderlich. Die sorgfältige Gestaltung des Fabrikationsprozessablaufs wird noch komplizierter wenn es sich um Strukturen handelt die möglicherweise zerbrechlich sind, zuverlässig in einer flüssigen (möglicherweise ätzender) Umgebung arbeiten müssen und ein perfekter Schutz der Komponenten des integrierten Schaltkreis (IC) zwingend notwendig ist. In dieser Arbeit wurden 3D vertikal gestapelte Silizium-Nanodrähte und Fin-Feldeffekttransistoren (FETs) mit einem Array von hoher Dichte (bis zu 8 × 20 SiNWs, > 4 Fins vertikal gestapelt) vollständig verarmter, ultradünner (SiNWs Durchmesser bis hinunter zu dnw ~ 15 - 30 nm, Fin Breite/Höhe  $F_w \sim 30 \text{ nm/}F_h \sim 150 \text{ nm}$ ), langer (L < 10 µm) suspendierter Kanäle entworfen und erfolgreich mit einem Top-Down, CMOS (Complementary metal-oxide-semiconductor) kompatiblen Prozess auf SOI (Silicon on insulator) und Bulk-Siliziumsubstrat hergestellt. Durch ein geschicktes Design, durch Optimierung der kritischen Schritte und durch die Beibehaltung der gestapelten Nanostrukturen innerhalb ihres SiO2-Gehäuses bis zum Ende des Herstellungsprozesses (an welcher Stelle sie leicht durch eine gepufferten Oxidätzung freigelegt werden) ist es möglich, robuste, gleichmäßige und zuverlässige elektronische Biosensoren zu produzieren. Unser Fertigungsschema ist wettbewerbsfähig im Hinblick auf Skalierung und SiNW-Dichte (mit einer vertikalen Dichte bis zu 10 SiNWs/µm) im Vergleich zu anderen Bottom-Up und Top-Down Ansätzen, jedoch mit dem zusätzlichen Vorteil dass ein CMOS-kompatibler und reproduzierbarer Prozess mit hoher Ausbeute (> 90%) verwendet werden kann.

SiNWs und Fins (Einzelne oder Arrays in einer Ebene) ziehen weiterhin großes Interesse als Biosensoren auf sich, da sie das Potential haben zu niedrigen Kosten, in Echtzeit, markierungsfrei, hochempfindlich und selektiv (durch Oberflächenmodifikation) eine unzählige Anzahl von Analyten zu erkennen. Die nanoskalige Dimensionen führen zu großen Oberflächen-Volumen-Verhältnissen (S/V) und damit zu hohen Empfindlichkeiten aufgrund einer verbesserten elektrostatischen Gate-Steuerung (nanoskalige Querschnitte) und einer großen Oberfläche für die Biomolekülanbindung (Erkennung). Die vertikale Stapelung in unserer Struktur ermöglicht eine höhere Ausnutzung des Siliziumsubstrats, hohe Ausgangsströme und hohe Wahrscheinlichkeiten für Biomolekül-Wechselwirkungen durch die steigende Anzahl der Leitungskanäle in zwei Richtungen (Z, X). Da die Nanodrähte/Fins aufgehängt sind, liegt ihre gesamte Oberfläche zum Nachweis der zu erkennenden Analyten frei. Die Konfiguration des 3D-Sensors bietet zusätzlich eine ausgezeichnete elektrostatische Steuerung der Kanäle durch die Möglichkeit symmetrische oder asymmetrische Gate-Potentiale zur Abstimmung der Empfindlichkeit und zur Optimierung Stromverbrauchs des zu erzeugen. Die hier produzierten vertikal gestapelten flüssigkeitsgesteuerten FET-Strukturen zeigen zusätzlich hervorragende Transistoreigenschaften wie niedrige Drain-Leckströme  $I_{off}$  < 20 × 10<sup>-6</sup> mA/ $\mu$ m, hohe Ein-Ströme  $I_{on}$  > 1 mA/ $\mu$ m (normalisiert auf den Nanodraht-Durchmesser  $d_{NW}$  = 30 nm), hohe Ein-/Aus-Stromverhältnisse > 106, große maximale Gegenwirkleitwerte  $g_m > 10 \mu S$  und unterschwellige Eigenschaften SS so niedrig wie 85 mV/dec in einer Elektrolytlösung. Ausgezeichnete Id - VsG unterschwellige Eigenschaften (75 mV/dec in Isopropanol) wurden mit den suspendierten Strukturen dank der hohen Back-Gate Kopplung, die die SS kontrolliert wenn  $V_{BG}$  erhöht wird ( $V_{BG}$  = 1.5 V), erreicht. Der Nachweis von ultra-niedrigen Konzentrationen des Proteins Streptavidin (~ 17 aM) entspricht der Stand der Technik und wurde mit einem biotinylierten SiO2 Gate-Dielektrikum erfolgreich demonstriert. Außerdem wurden hohe, langfristige und reproduzierbare pH-Sensorantworten mit einer Drain-Stromänderung pro pH-Wert  $\Delta I_d/pH$  von bis zu 0.8 dec/pH auch mit einem (3-Aminopropyl)triethoxysilan (APTES) modifizierten SiO<sub>2</sub>-Gate-Dielektrikum (beim Betrieb im unterschwelligen Regime) demonstriert. Schließlich wurde als Machbarkeitsnachweis ein vertikal gestapelter SiNW FET auf Bulk-Siliziumsubstrat für eine zukünftige Implementierung in kostengünstige Biosensorsysteme hergestellt. Keywords: SiNW, FinFET, sensor, biosensor, 3D, vertikal gestapelte, bio-FET, ISFET, streptavidin, pH sensor.

## Contents

| Acknowle    | edgements                                                  | vii   |

|-------------|------------------------------------------------------------|-------|

| Abstract.   |                                                            | ix    |

| Zusamme     | enfassung                                                  | xi    |

| List of Fig | ures                                                       | xviii |

| List of Ta  | bles                                                       | xxv   |

| List of Eq  | uations                                                    | xxvi  |

| Technica    | Acronyms and Abbreviations                                 | xxvii |

| Chapter 1   | Thesis overview                                            | 1     |

| Chapter 2   | Introduction                                               | 7     |

| 2.1         | Motivation                                                 | 7     |

| 2.2         | Field effect transistors as biosensors                     | 8     |

| 2.3         | Principle of operation                                     | 9     |

| 2.4         | SiNW FETs                                                  | 12    |

|             | 2.4.1 SiNW FET biosensors                                  | 12    |

|             | 2.4.2 The vertically stacked SiNW FET biosensor            | 13    |

|             | 2.4.3 Junctionless SiNW biosensors                         | 14    |

| 2.5         | State-of-Art: vertically stacked nanostructure fabrication | 16    |

| 2.6         | State-of the-Art: pH and biotin-streptavidin sensing       | 20    |

| 2.7         | Design considerations                                      | 24    |

|             | 2.7.1 SiNW/Fin cross section, channel doping concentration | 24    |

|             | 2.7.2 Sensing area                                         | 24    |

|           | 2.7.3 Sensing interface                                         | 25 |

|-----------|-----------------------------------------------------------------|----|

|           | 2.7.4 Sensing analyte                                           | 27 |

|           | 2.7.5 Gating                                                    | 28 |

| 2.8       | Summary                                                         | 30 |

| Chapter 3 | Fabrication of vertically stacked Si nanostructures             | 33 |

| 3.1       | Short-loop process optimization-vertically stacked SiNWs        | 33 |

| 3.2       | Short-loop process optimization-vertically stacked Fins         | 41 |

| 3.3       | Vertically stacked sensor process flow                          | 43 |

|           | 3.3.1 Mask 1: NW formation                                      | 44 |

|           | 3.3.2 Mask 2: Implantation                                      | 44 |

|           | 3.3.3 Mask 3 and 4: Side-gate and S/D contact metallization     | 48 |

|           | 3.3.4 Mask 5: SU-8 protection mask                              | 49 |

|           | 3.3.5 Mask 6: NW release                                        | 50 |

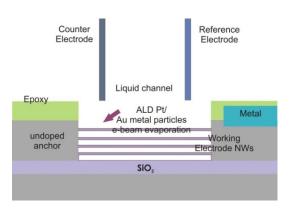

| 3.4       | Analyte delivery                                                | 50 |

| 3.5       | Heterogeneous system integration                                | 53 |

|           | 3.5.1 Process flow with TSV integration                         | 53 |

| 3.6       | Fabrication challenges                                          | 56 |

|           | 3.6.1 Fabrication of 3D structures and yield                    | 56 |

|           | 3.6.2 Mechanical characterization by AFM                        | 58 |

| 3.7       | Summary                                                         | 62 |

| Chapter 4 | Methods and functionalization challenges                        | 65 |

| 4.1       | Electrical characterization                                     | 65 |

|           | 4.1.1 Transistor characterization under dry, ambient conditions | 65 |

|           | 4.1.2 Transistor characterization in wet, ambient conditions    | 65 |

| 4.2       | Sensor characterization                                         | 66 |

| 4.3       | Organic surface functionalization                               | 68 |

|           | 4.3.1 Aminosilanization for pH sensing                          | 68 |

|           | 4.3.2 Biotinylation for streptavidin sensing                    | 69 |

|           | 4.3.3 Oligonucleotide immobilization for DNA sensing            | 69 |

| 4.4       | Summary                                                                          | 74  |

|-----------|----------------------------------------------------------------------------------|-----|

| Chapter 5 | Transistor characterization                                                      | 76  |

| 5.1       | Device description                                                               | 76  |

| 5.2       | Dry characterization prior to SiNW release                                       | 77  |

|           | 5.2.1 Contact characterization                                                   | 77  |

|           | 5.2.2 Transfer characteristics                                                   | 79  |

| 5.3       | Dry characterization after SiNW release                                          | 80  |

| 5.4       | Liquid-gated experiments after SiNW release                                      | 82  |

|           | 5.4.1 Transistor characteristics                                                 | 82  |

|           | 5.4.2 Leakage and Ion current                                                    | 85  |

|           | 5.4.3 Transconductance                                                           | 88  |

|           | 5.4.4 Drain induced barrier lowering                                             | 88  |

|           | 5.4.5 Subthreshold slope                                                         | 89  |

|           | 5.4.6 Gate dielectric                                                            | 89  |

|           | 5.4.7 Symmetric and asymmetric gating in a liquid environment                    | 92  |

| 5.5       | Transfer characteristics in an electrolyte                                       | 97  |

| 5.6       | Summary                                                                          | 98  |

| Chapter 6 | Sensor performance characterization                                              | 101 |

| 6.1       | Side-gated results                                                               | 101 |

|           | $6.1.1~\text{pH}$ sensing with aminosilanized $HfO_2$ or $SiO_2$ gate dielectric | 101 |

|           | 6.1.2 Streptavidin sensing with SiO <sub>2</sub> gate dielectric                 | 105 |

| 6.2       | Reference electrode results                                                      | 106 |

|           | 6.2.1 pH sensing with aminosilanized surfaces                                    | 107 |

|           | 6.2.2 pH sensing with unmodified SiO <sub>2</sub> surfaces                       | 111 |

|           | 6.2.3 Robust and long term operation                                             | 113 |

|           | 6.2.4 Streptavidin sensing                                                       | 115 |

| 6.3       | Summary                                                                          | 118 |

| Chapter 7 | Low cost vertically stacked sensor                                               | 121 |

| 7      | 7.1    | Bulk fabricated SiNW FETS                                  | 121 |

|--------|--------|------------------------------------------------------------|-----|

| 7      | 7.2    | The vertically stacked bulk sensor                         | 123 |

|        |        | 7.2.1 Transistor characteristics                           | 123 |

| 7      | 7.3    | Summary                                                    | 124 |

| Chapt  | er 8   | Conclusion and outlook                                     | 125 |

| 8      | 3.1    | Achieved results                                           | 125 |

| 8      | 3.2    | Outlook                                                    | 126 |

|        |        | 8.2.1 Amperometric vertically stacked SiNW sensor          | 126 |

|        |        | 8.2.2 Energy harvester with vertically stacked SiNWs       | 127 |

|        |        | 8.2.3 Vertically stacked SiNW-based cantilever flow sensor | 129 |

| Appen  | ndix   | A: TCAD Simulations                                        | 131 |

| A      | 4.1. J | unctionless and enhancement mode tri-gated structures      | 131 |

|        |        | A.1.1. TCAD Simulations                                    | 131 |

|        |        | A.1.2. Transistor characteristics                          | 132 |

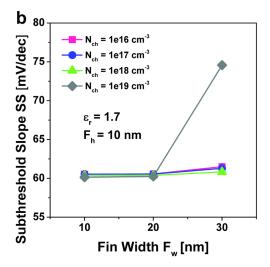

|        |        | A.1.3. Subthreshold slope                                  | 134 |

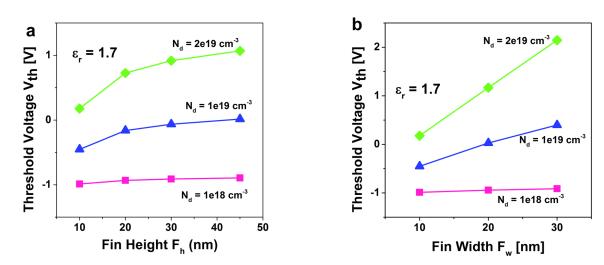

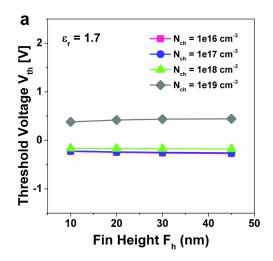

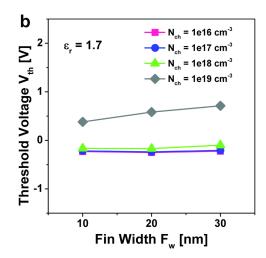

|        |        | A.1.4. Threshold voltage                                   | 136 |

| A      | A.2. C | Gate-all-around structures                                 | 138 |

|        |        | A.2.1. TCAD Simulations                                    | 138 |

|        |        | A.2.2. Transistor characteristics                          | 139 |

|        |        | A.2.3 Results                                              | 139 |

| Appen  | ndix   | B: ISFET/REFET differential pair                           | 141 |

|        |        | B1.1. Differential circuit with resistors                  | 141 |

|        |        | B.1.2. Simulations                                         | 142 |

| Biblio | grap   | ohy                                                        | 145 |

| Public | catio  | ons                                                        | 159 |

| Journa | al Pa  | apers:                                                     | 159 |

| Confe  | renc   | res/Workshons/Meetings·                                    | 160 |

| •   |   |    | 1 |     |

|-----|---|----|---|-----|

| U.0 | n | te | n | FS: |

# List of Figures

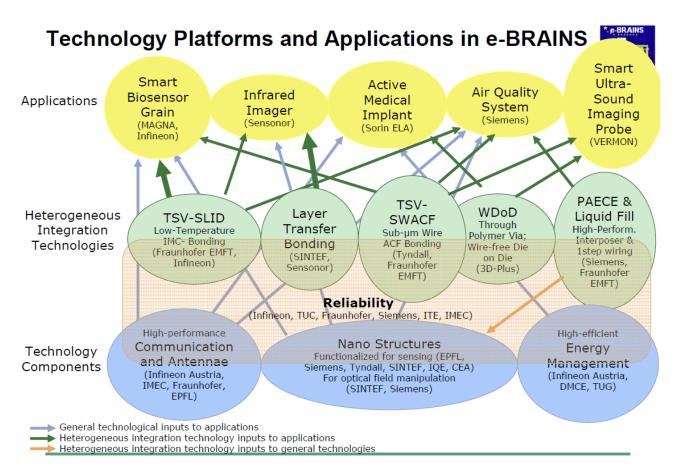

| Figure 1-1: Technology platforms and applications in e-BRAINS, adapted from [2]2                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

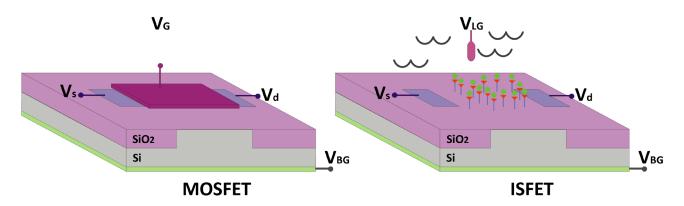

| Figure 2-1: Schematic of planar MOSFET and ISFET9                                                                                                                                                                                                                                                                                                                                                                                                            |

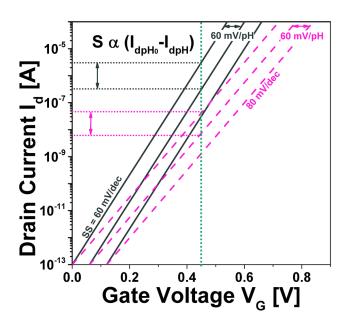

| Figure 2-2: $I_d - V_G$ curves illustrating how the drain current and hence the sensitivity changes with a change of pH that induces a $V_{th}$ shift of 60 mV/pH, for a transistor with a $SS$ slope of 60 mV/dec (grey-solid curves) and 80 mV/dec (pink-dashed curves), in subthreshold11                                                                                                                                                                 |

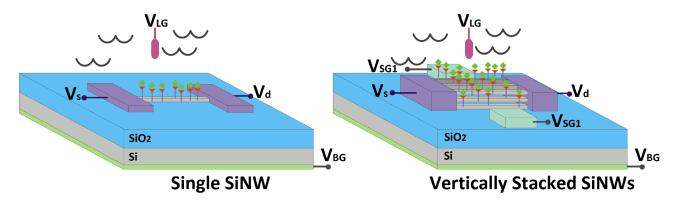

| Figure 2-3: Schematic of single SiNW FET biosensor and vertically stacked SiNW FET biosensor (3 rows of 3 SiNWs vertically stacked)                                                                                                                                                                                                                                                                                                                          |

| Figure 2-4: Schematic of JNT FinFET SOI junctionless sensor system, left. Source-channel-drain regions have same type $P^+$ - $P^+$ - $P^+$ and doping concentrations $N_d$ , without junctions n-channel enhancement mode FinFET SOI sensor system. $N$ - $P$ $S$ / $D$ junctions are clearly shown in schematic (right).                                                                                                                                   |

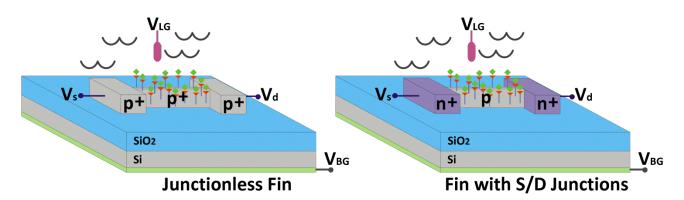

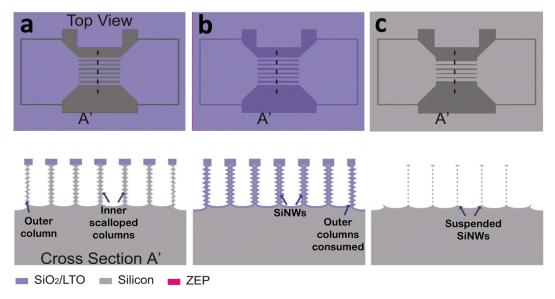

| Figure 3-1: Schematic top-view and cross section of A' of (a) wafer with LTO hard mask, (b) ZEP definition after e-beam patterning and (c) hard mask defined by dry etch                                                                                                                                                                                                                                                                                     |

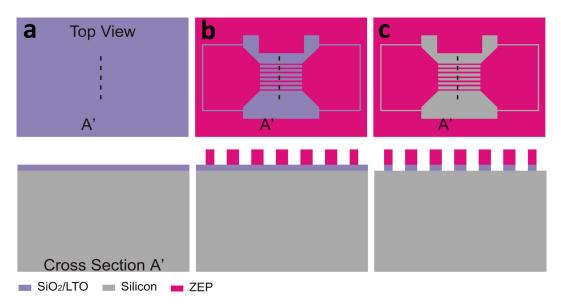

| Figure 3-2: Schematic top-view and cross section of A' of (a) scalloped columns after BOSCH, (b) SiNWs formed after thermal oxidation and (c) suspended NWs formed after BOE wet etch                                                                                                                                                                                                                                                                        |

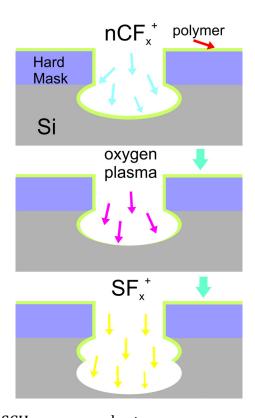

| Figure 3-3: Schematic of BOSCH process cycle steps                                                                                                                                                                                                                                                                                                                                                                                                           |

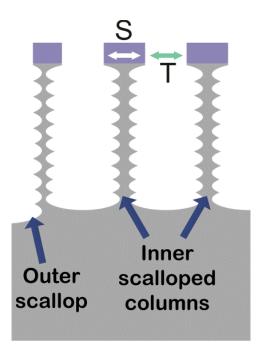

| Figure 3-4: Trench opening T and silicon spacer S shown schematically. Left outer silicon spacer designed to be smaller than inner ones to be consumed after thermal oxidation. Scallop shape depends on trench opening width which results in oddly shaped outer column36                                                                                                                                                                                   |

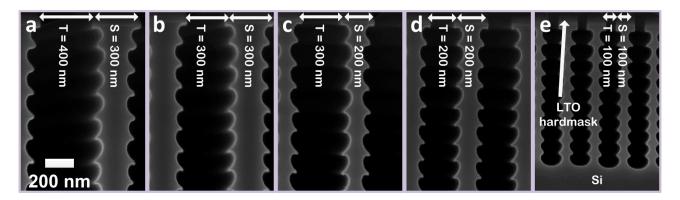

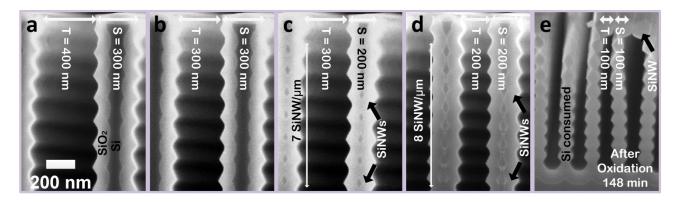

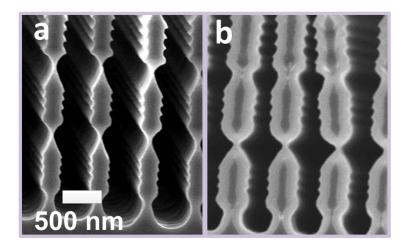

| Figure 3-5: SEM cross section views of scalloping resulting from the BOSCH process with different trench openings and silicon spacer dimensions: (a) $T = 400$ nm, $S = 300$ nm, (b) $T = 300$ nm, $S = 300$ nm, (c) $T = 300$ nm, $S = 200$ nm, (d) $S = 200$ nm, $S = 200$ nm, (e) $S = 100$ nm. |

| Figure 3-6: SEM cross section views of the SiNWs resulting after the scalloped structures from Figure 3-5 have been processed under the same thermal oxidation conditions37                                                                                                                                                                                                                                                                                  |

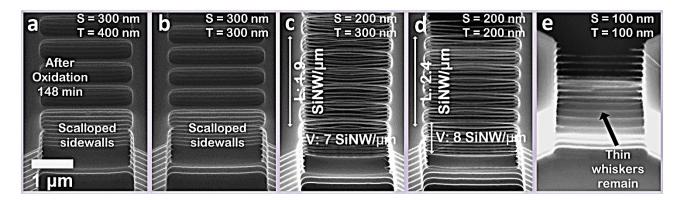

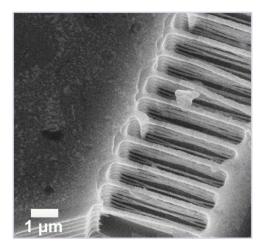

| Figure 3-7: SEM top-side tilted-views of SiNWs and undulating columns resulting from the BOSCH process with different trench openings and silicon spacer dimensions as shown above after thermal oxidation and BOE SiO <sub>2</sub> removal                                                                                                                                                                                                                  |

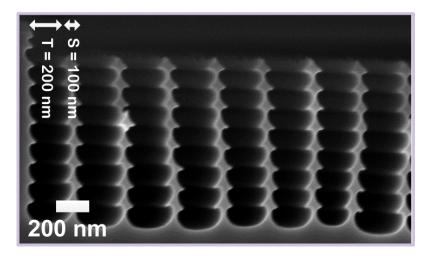

| Figure 3-8: SEM cross section views of scalloping resulting from the BOSCH process with a trench opening and silicon spacer dimensions of $T=200$ nm, $S=100$ nm. Non-uniform scallops result.                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

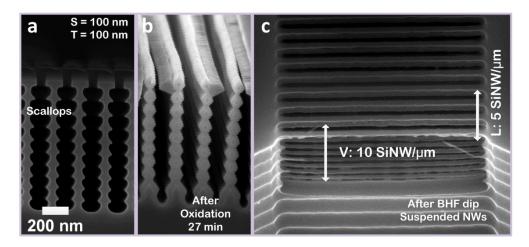

| Figure 3-9: SEM cross section of highest density structure with T = 100 nm, S = 100 nm, (a) after BOSCH, (b) after thermal oxidation and (c) after BOE etch ( $d_{NW} \sim 15$ -25 nm)40                                                                                                                                                                                             |

| Figure 3-10: SEM top-side, tilted-views of SiNWs formed with the same T and S dimensions, $S = T = 200$ nm $(a - c)$ , $S = 200$ nm, $T = 300$ nm $(d - f)$ but oxidized with different times40                                                                                                                                                                                      |

| Figure 3-11: SEM top-side tilted-views of SiNWs resulting from the BOSCH process with different trench openings and silicon spacer dimensions after thermal oxidation and BOE $SiO_2$ removal for structures with L = 5 $\mu$ m and: (a) T = 300 nm, S = 200 nm, (b) T = 200 nm, S = 200 nm. High number of channels N in two directions (y, z) can be achieved41                    |

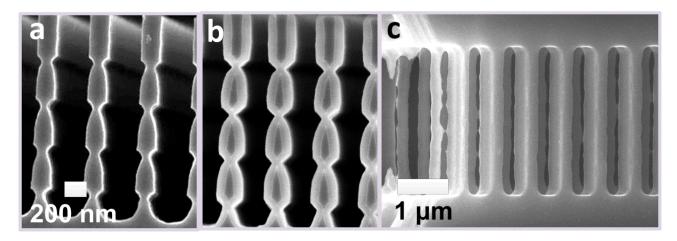

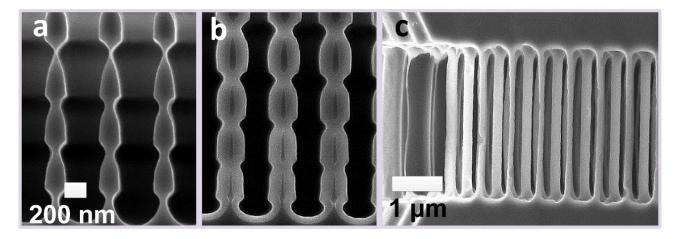

| Figure 3-12: SEM cross sections of Fins formed with a combination of BOSCH and isotropic dry etches before (a) and after (b) oxidation42                                                                                                                                                                                                                                             |

| Figure 3-13: SEM cross sections of Fins formed with a combination of anisotropic and isotropic (non-sharp scallop) dry etch steps before oxidation (a), after oxidation (b) and top-side view of Fins after BOE release (c).                                                                                                                                                         |

| Figure 3-14: SEM cross sections of Fins formed with a combination of anisotropic and isotropic (sharp scallop with $O_2$ step included) etches before oxidation (a), after oxidation (b) and top-side view after BOE release (c)43                                                                                                                                                   |

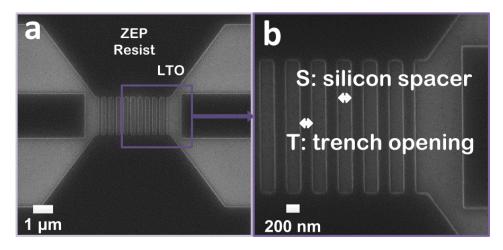

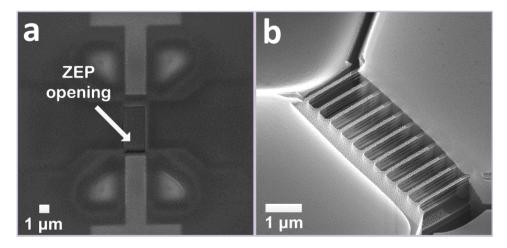

| Figure 3-15: (a, b) SEM top-view and close-up of pattern after e-beam with silicon spacer and trench openings clearly labeled                                                                                                                                                                                                                                                        |

| Figure 3-16: Contour plots of the net active concentration (B + P) of the simulated vertically stacked NW cross sections with increasing implantation doses from 1e15 to 5e16 cm <sup>-2</sup> with constant energy (320 keV), RTA temperature (1000 °C) and RTA flat time of 30 seconds. The meshed simulated contour plot of the corresponding simulated structure is also shown46 |

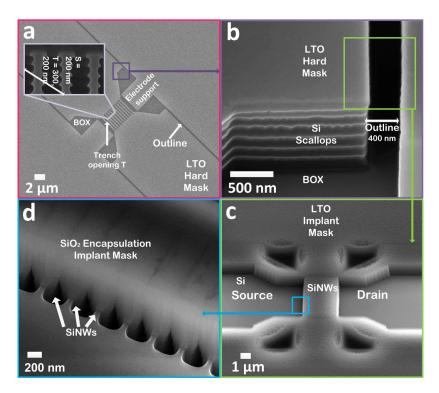

| Figure 3-17: (a) Top-side view of etched structure's outline, inset shows the scallops produced by BOSCH ( $S = 200 \text{ nm}$ and $T = 200 \text{ or } 300 \text{ nm}$ ), (b) tilted-side view of scalloped outline right on top the SOI's BOX layer, (c) tilted-side view of structure after LTO hard mask is deposited and S/D openings are etched for implantation              |

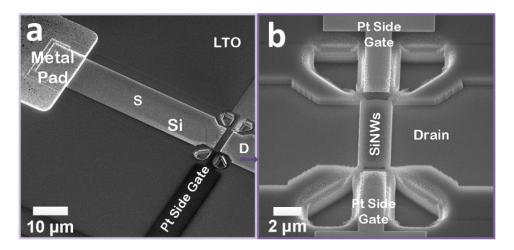

| Figure 3-18: (a) SEM tilted-view after metallization of contact pads by lift-off and (b) magnified view of side-gated device                                                                                                                                                                                                                                                         |

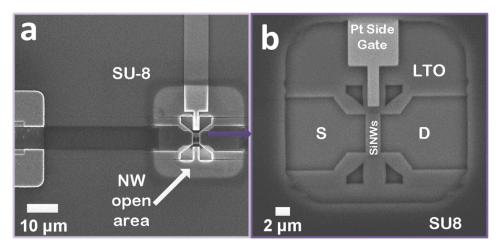

| Figure 3-19: (a) SEM top-side and (b) magnified views after SU-8 definition by optical lithography. Only the NW/Fin area is exposed                                                                                                                                                                                                                                                  |

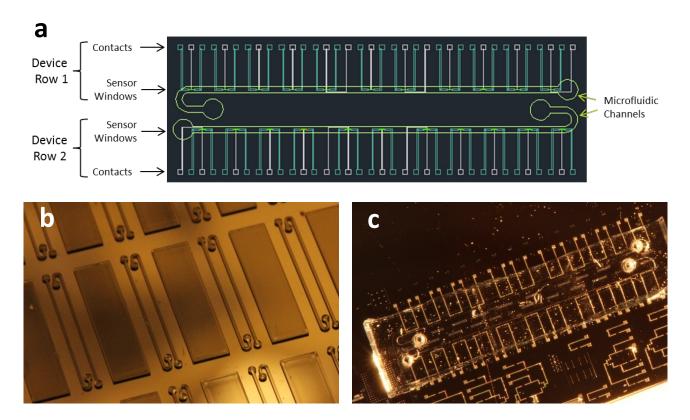

| Figure 3-20: Schematic showing layout of devices and the microfluidic channel geometry used to supply the sensors with fluid (a), SU-8 mold and (c) PDMS microfluidic stamp on top of chip. Courtesy of A. M. Nightingale, Imperial College London51                                                                                                                                 |

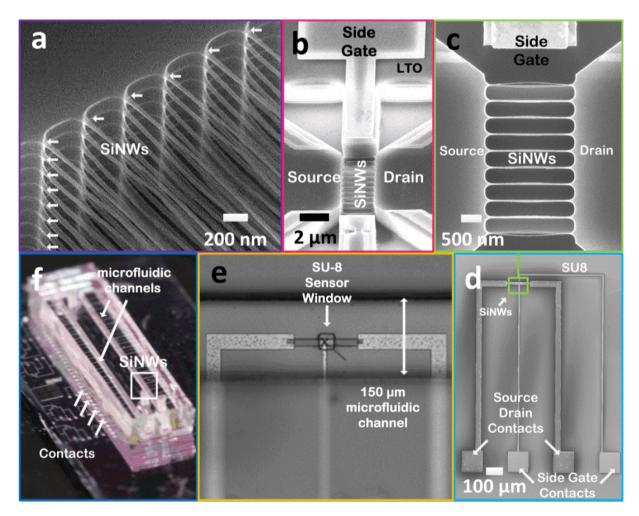

| Figure 3-21: (a) SEM tilted-view of SiNWs, (b) SEM top-side tilted-view showing side-gate from side and (c) top-view, (d) SEM top-side view of entire structure that shows source/drain and side-gate contacts. (e) Image showing top-view of PDMS stamp containing 150 $\mu$ m-wide microfluidic channel on top of SU-8 sensor window, (f)                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

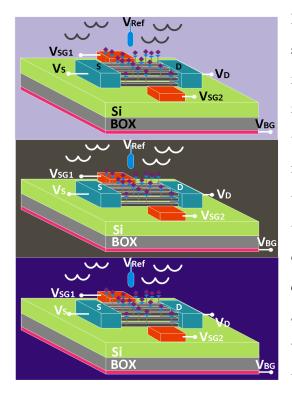

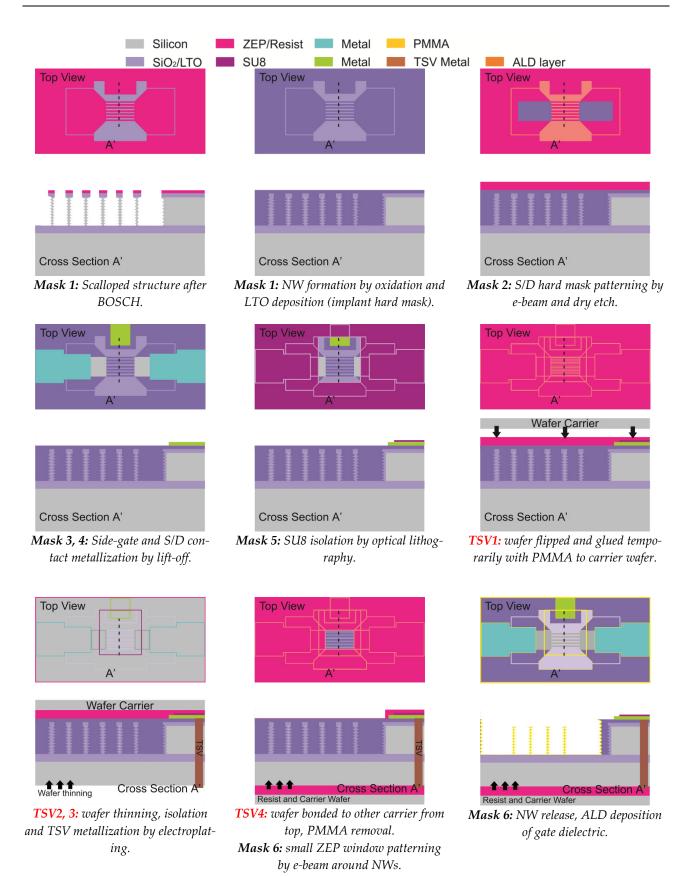

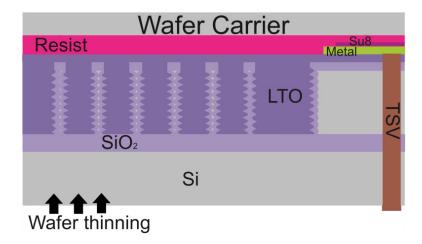

| Figure 3-22: Top and cross section schematic views of structure after specified process steps with TSV integration                                                                                                                                                                                                                                                  |

| Figure 3-23: Cross section schematic view of structure with TSV. NWs are safely enclosed within the $SiO_2$ and LTO making TSV fabrication possible                                                                                                                                                                                                                 |

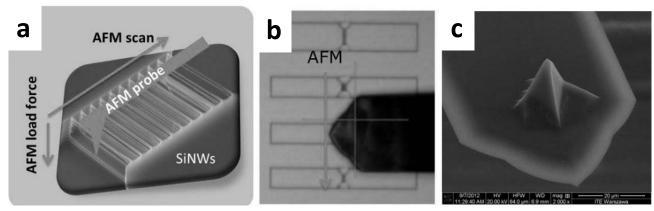

| Figure 3-24: (a) AFM-based testing methodology, (b) view during the AFM test, (c) SEM images of the one of the AFM probes used– Bruker MPP31220. Adapted from [121]59                                                                                                                                                                                               |

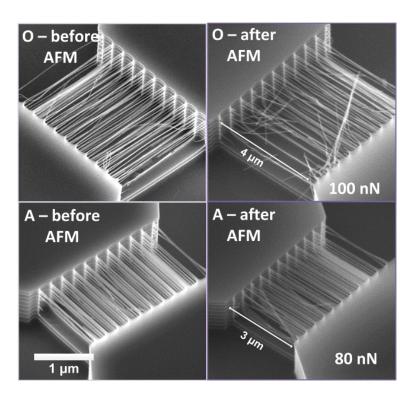

| Figure 3-25: SEM top-side tilted images of test structures with native oxide alone (L = 4 $\mu$ m) and with an ALD Al <sub>2</sub> O <sub>3</sub> layer (L = 3 $\mu$ m) before and after AFM with a load force of 100 and 80 nN respectively. Courtesy of T. Bieniek, ITE60                                                                                         |

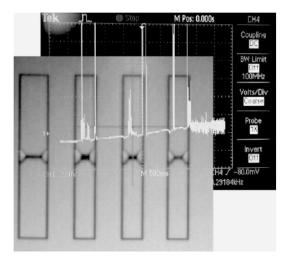

| Figure 3-26: Lateral signal recorded compared with an optical image of the structures. There is a rise in the signal when the tip strikes the wires. Adapted from [121]61                                                                                                                                                                                           |

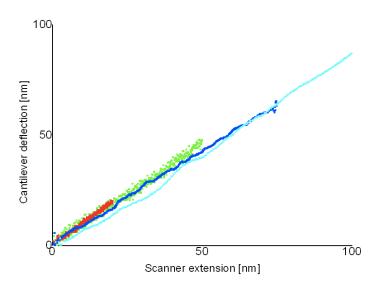

| Figure 3-27: Force microscopy curves for $7 \times 10$ SiNWs structures $L = 2 \mu m$ . Adapted from [121]61                                                                                                                                                                                                                                                        |

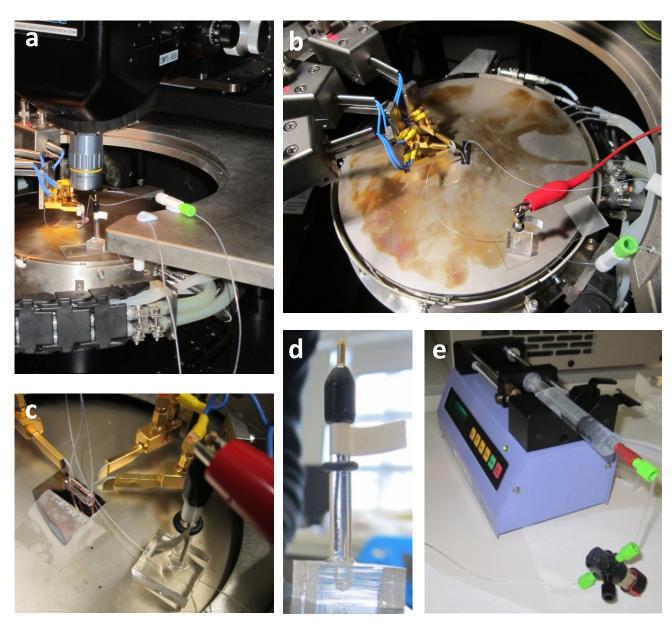

| Figure 4-1: (a, b, c) Images showing an integrated device ready for measurement within the Cascade probe station with the tubing used to hydrodynamically transfer fluid to/from the device with integrated flow-cell reference electrode. (b) Reference electrode and flow cell close-up. (e) Syringe pump with attached T-junction 10 cm away from syringe exit66 |

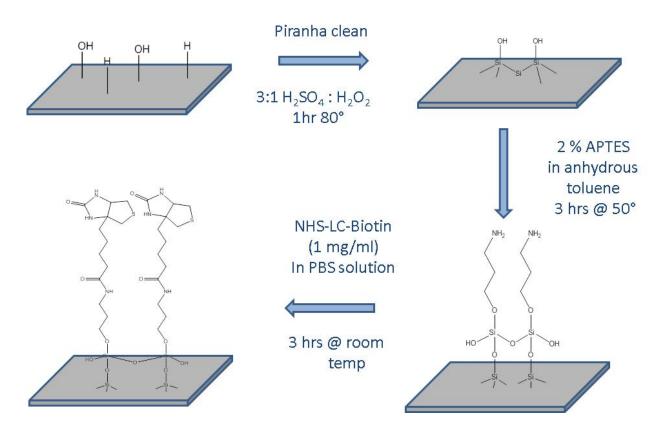

| Figure 4-2: Cartoon illustrating surface modification protocol: hydroxylation, APTES modification, biotinylation. Courtesy of O. Lotty, Tyndall National Institute, Cork, Ireland69                                                                                                                                                                                 |

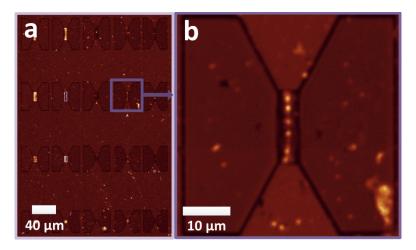

| Figure 4-3: (a) Scanned fluorescent image taken by CLSM at 40X magnification and (b) amplified view of butterfly structures after silanization and oligonucleotide immobilization at 63X magnification. The fluorescence signal is highest at the center of the structure where the NWs are                                                                         |

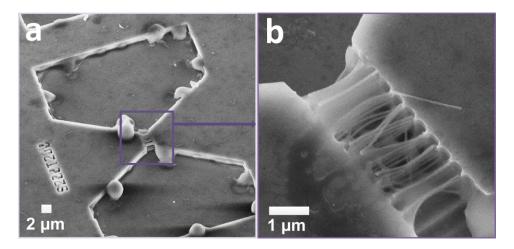

| Figure 4-4: (a) Top-side tilted-view of butterfly test structure covered with a $10 \text{ nm}$ ALD $Al_2O_3$ conformal layer after the silanization based oligomer immobilization and hybridization process and (b) close-up with some SiNWs broken72                                                                                                              |

| Figure 4-5: (a) SEM top-view of ZEP window to selectively remove SiO <sub>2</sub> around NW area and (b) released structure on which Au has been deposited by e-beam evaporation through ZEP window. The ZEP window is slightly misaligned to the left, allowing for Au deposition on the top of the S/D anchor                                                     |

| Figure 4-6: Top-side tilted-view of butterfly test structure after the thiol-based oligomer immobilization                                                                                                                                                                                                                                                          |

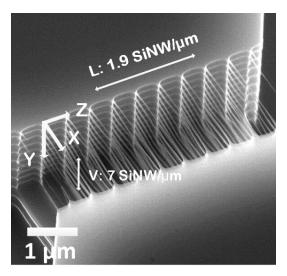

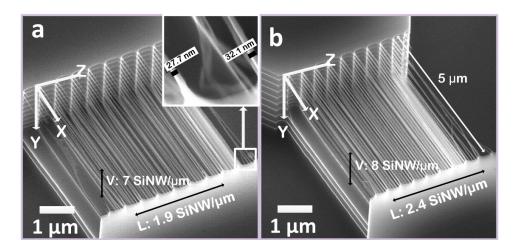

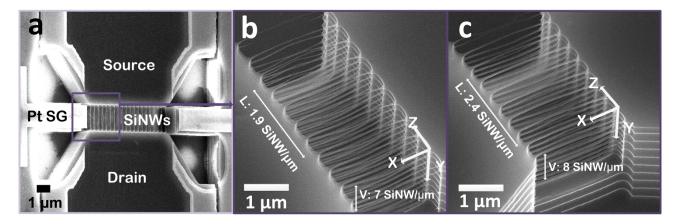

| Figure 5-1: SEM top-side tilted-views of SiNWs arrays with two different vertical and horizontal SiNW densities and diameters: (a) V = 7 SiNWs/ $\mu$ m, H = 1.9 SiNWs/ $\mu$ m, $d_{NW}$ = 15 – 30 nm and (b) V = 8 SiNWs/ $\mu$ m, H = 2.4 SiNWs/ $\mu$ m, $d_{NW}$ = 25 – 35 nm ( $L$ = 2 $\mu$ m). 76                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

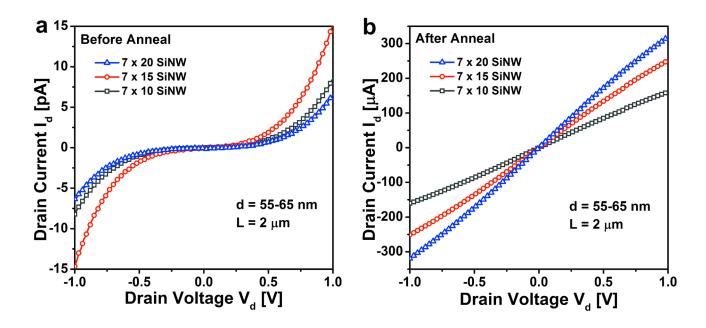

| Figure 5-2: $I_d - V_d$ output characteristics for devices with different NW densities: 10, 15, 20 NWs × 7 NWs (a) before and (b) after metal anneal respectively. The NWs are still within their SiO <sub>2</sub> encapsulation and therefore the NW size still bigger than the targeted size $d_{NW} < 40$ nm.                              |

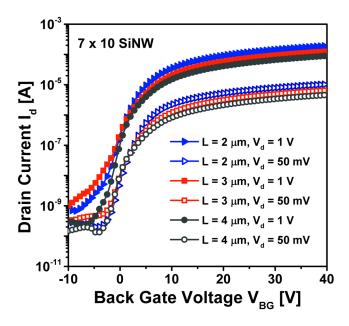

| Figure 5-3: $I_d$ – $V_{BG}$ curves for high ( $V_d$ = 1 V) and low ( $V_d$ = 50 mV) drain potentials for 7 × 10 SiNWs structures ( $V_{SG}$ = 0 V, $d_{NW}$ = 45 – 55 nm) prior to oxide removal by BOE) as the length increases $L$ = 2, 3 and 4 $\mu$ m.                                                                                   |

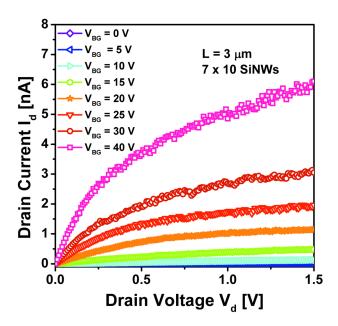

| Figure 5-4: $I_d$ – $V_d$ curves with increasing backgate potentials ( $V_{BG}$ from 0 to 40 V) for a 7 × 10 SiNWs structure after oxide removal ( $V_{SG}$ = 0 V, $L$ = 3 $\mu$ m, $d_{NW}$ = 15 – 30 nm)81                                                                                                                                  |

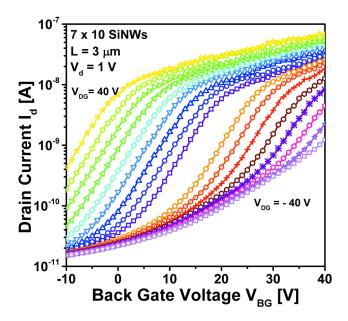

| Figure 5-5: $I_d - V_{BG}$ as the double gate potential $V_{DG}$ increases from -40 V to 40 V for a 7 × 10 SiNWs structure after oxide removal ( $V_d = 1$ V $L = 3$ $\mu$ m, $d_{NW} = 15 - 30$ nm)82                                                                                                                                        |

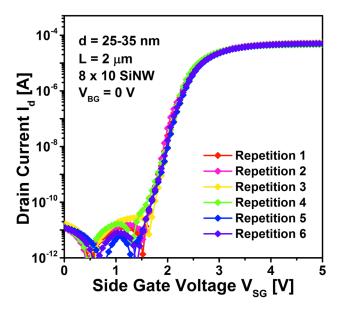

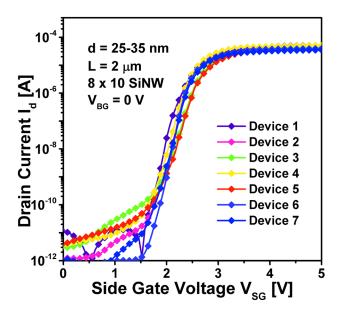

| Figure 5-6: $I_d$ – $V_{SG}$ measurement repeated several times for a 8 × 10 SiNWs structure, $L$ = 2 $\mu$ m, $d_{NW}$ = 25 – 35 nm, $V_d$ = 50 mV and SiO <sub>2</sub> gate dielectric83                                                                                                                                                    |

| Figure 5-7: $I_d$ – $V_{SG}$ measurements for different devices with the same geometric characteristics within the same die for a 8 × 10 SiNWs structure, $L$ = 2 $\mu$ m, $d_{NW}$ = 25 –35 nm, $V_d$ = 50 mV and SiO <sub>2</sub> gate dielectric                                                                                           |

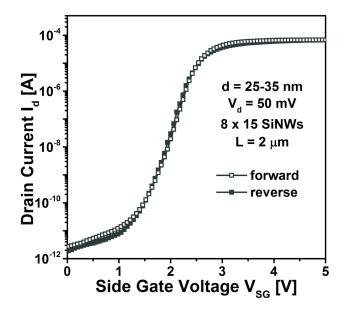

| Figure 5-8: $I_d$ – $V_{SG}$ curves for forward (solid) and reverse (open) sweep for a 8 × 10 SiNWs structure, $L$ = 2 $\mu$ m, $d_{NW}$ = 25 – 35 nm and SiO <sub>2</sub> gate dielectric85                                                                                                                                                  |

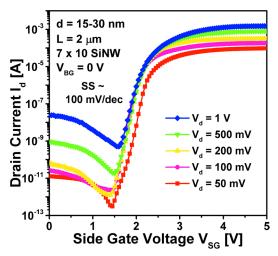

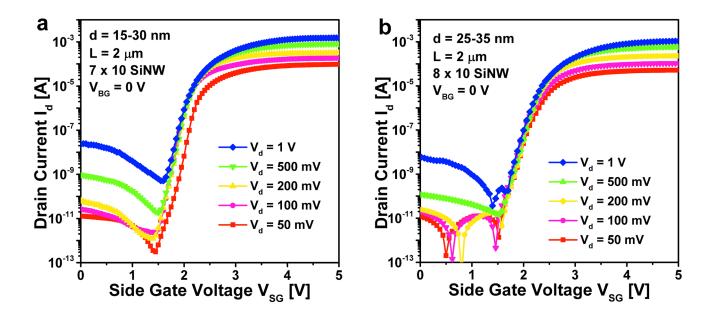

| Figure 5-9: $I_d$ – $V_{SG}$ for increasing drain potentials ( $V_d$ =50 mV – 1 V) for a (a) 7 × 10 SiNWs structure, $d_{NW}$ = 15-30 nm and (b) a 8 × 10 SiNWs structure, $d_{NW}$ = 25-35 nm with $L$ = 2 $\mu$ m, SiO <sub>2</sub> gate dielectric                                                                                         |

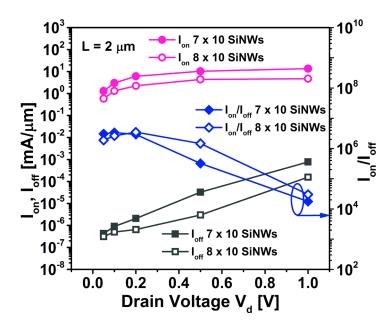

| Figure 5-10: $I_{on}$ and $I_{off}$ (left) normalized to nanowire diameter ( $d_{NW}$ = 15-30 nm for 7 × 10 SiNWs and $d_{NW}$ = 25-35 nm or 8 × 10 SiNWs FET) and $I_{on}/I_{off}$ current ratios (right) as a function of drain voltage with $L$ = 2 $\mu$ m, SiO <sub>2</sub> is the gate dielectric                                       |

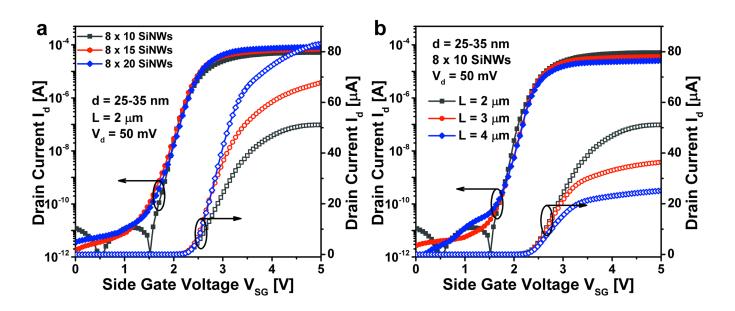

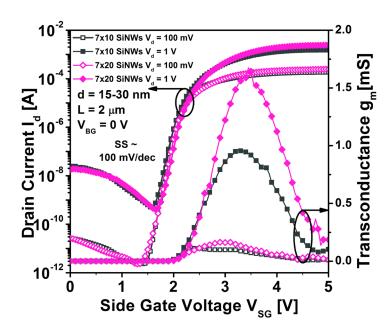

| Figure 5-11: (a) $I_d$ – $V_{SG}$ curves when $V_d$ = 50 mV for structures with a constant vertical density of 8 SiNWs/ $\mu$ m and increasing number of NWs in the horizontal direction (10, 15, 20 SiNWs) with $L=2~\mu$ m, $d_{NW}=25-35~n$ m, (b) for 8 × 10 SiNWs structures with increasing channel lengths ( $L=2$ , 3 and 4 $\mu$ m). |

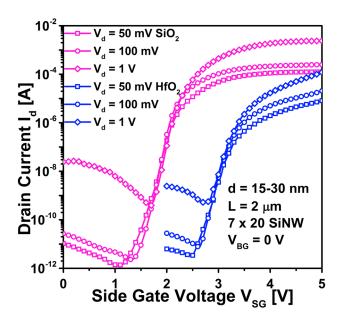

| Figure 5-12: $I_d$ – $V_{SG}$ curves at high and low drain potentials for 7 × 10 and 7 × 20 SiNWs structures with $L=2~\mu\text{m}$ , $d_{NW}=15\text{-}30~\text{nm}$ , tested in a liquid environment (left). Transconductances for the same devices are shown on the right axis                                                             |

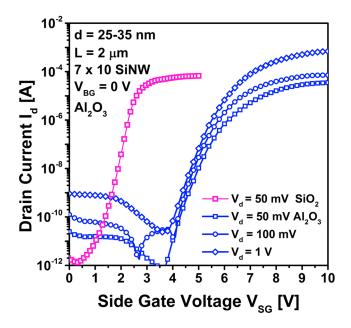

| Figure 5-13: $I_d$ – $V_{SG}$ curves at high and low drain potentials for 7 × 10 SiNWs ( $V_d$ = 50, 100 mV, 1 V) with and without HfO <sub>2</sub> , $L$ = 2 $\mu$ m, $d_{NW}$ = 25-40 nm90                                                                                                                                                  |

| Figure 5-14: $I_d$ – $V_{SG}$ curves at high and low drain potentials for 7 × 10 SiNWs ( $V_d$ = 50, 100 mV, 1 V) with and without Al <sub>2</sub> O <sub>3</sub> ( $V_d$ = 50 mV), $L$ = 2 $\mu$ m, $d_{NW}$ = 25-40 nm92                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-15: $I_d$ – $V_{SG}$ curves for different backgate potentials ( $V_{BG}$ = 0 – 3 V) for a 7 × 10 SiNWs structure, $L$ = 2 $\mu$ m, $d_{NW}$ = 15-30 nm, $V_d$ =50 mV, SiO <sub>2</sub> gate dielectric93                                                                                                                                                      |

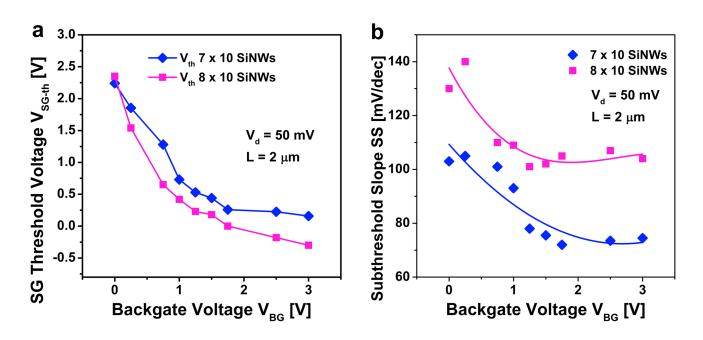

| Figure 5-16: (a) $V_{th}$ from $I_d$ – $V_{SG}$ curves as the backgate voltage value increases from 0 to 3 V and (b) $SS$ from $I_d$ – $V_{SG}$ curves as the backgate voltage value increases from 0 to 3 V for a 7 × 10 and 8 × 10 NWs structure, $L$ = 2 $\mu$ m, $V_d$ = 50 mV, SiO <sub>2</sub> gate dielectric93                                                 |

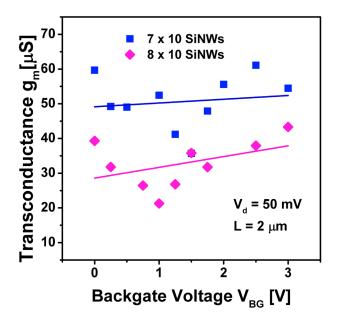

| Figure 5-17: Extracted maximum transconductances from $I_d$ – $V_{SG}$ curves as the backgate voltage value increases from 0 to 3 V for a 7 × 10 and 8 × 10 NWs structure, $L$ = 2 $\mu$ m at low drain biases $V_d$ = 50 mV, tested in a liquid environment94                                                                                                         |

| Figure 5-18: $I_d$ – $V_{BG}$ curves for different side-gate potentials ( $V_{SG}$ from 0 V to 0.5 V) for 7 × 10 SiNWs structure, $L$ = 2 $\mu$ m, $d_{NW}$ = 15-30 nm, $V_d$ =50 mV, SiO <sub>2</sub> gate dielectric95                                                                                                                                               |

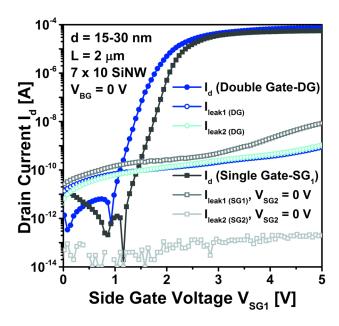

| Figure 5-19: $I_d$ , and side-gate leakage currents as either one (SG) of the side-gates are swept alone or both side-gates (DG) are swept together for a 7 × 10 SiNWs structure, $L$ = 2 $\mu$ m tested in a liquid environment96                                                                                                                                     |

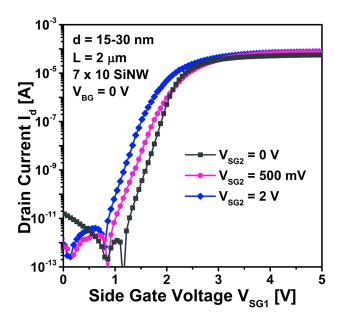

| Figure 5-20: $I_d$ as one side-gate is swept (SG <sub>1</sub> ) and the other is kept constant (SG <sub>2</sub> ) for a 7 × 10 SiNWs structure, $L$ = 2 $\mu$ m, SiO <sub>2</sub> gate dielectric96                                                                                                                                                                    |

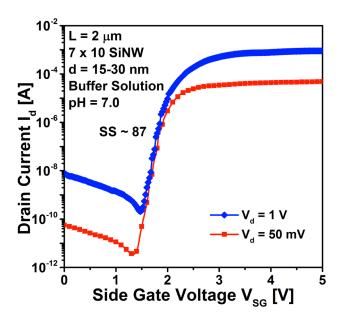

| Figure 5-21: $I_d - V_{SG}$ curves at high and low drain potentials for $7 \times 10$ SiNWs ( $V_d = 50$ mV, 1 V), $L = 2$ µm, $d_{NW} = 15-30$ nm, SiO <sub>2</sub> gate dielectric, tested in PBS (pH = 7)98                                                                                                                                                         |

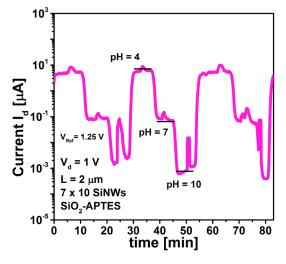

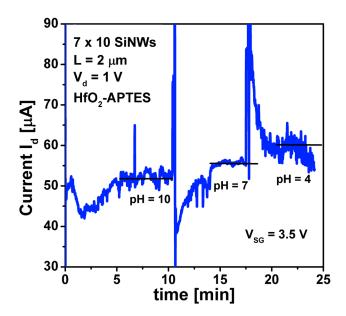

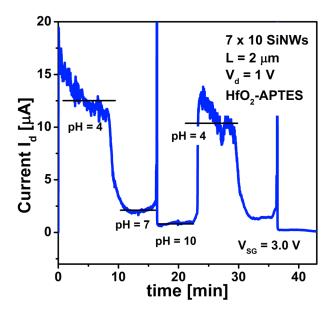

| Figure 6-1: $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m, $d_{NW}$ = 25 – 40 nm $V_d$ = 1 V and an HfO <sub>2</sub> gate dielectric as the device is operated in strong inversion $V_{SG}$ = 3.5 V                                                                                |

| Figure 6-2: $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m, $d_{NW}$ = 25 – 40 nm $V_d$ = 1 V and an HfO <sub>2</sub> gate dielectric as the device is operated in weak inversion $V_{SG}$ = 3.0 V                                                                                  |

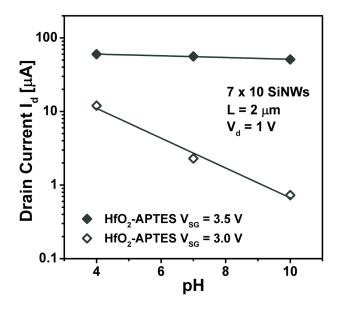

| Figure 6-3: $I_d$ as the pH value is changed from pH = 4 to 10 for an APTES functionalized structure with 7 × 10 SiNWs, $L = 2 \mu m$ , $d_{NW} = 25 - 40 \text{ nm}$ and an HfO <sub>2</sub> gate dielectric as the device is operated in the weak inversion ( $V_{SG} = 3 \text{ V}$ ) and strong inversion ( $V_{SG} = 3.5 \text{ V}$ ) regime, $V_d = 1 \text{ V}$ |

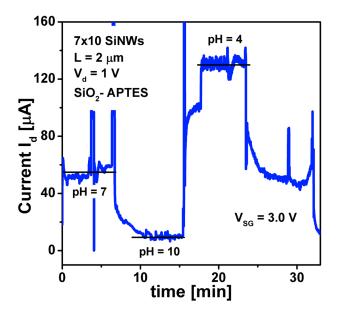

| Figure 6-4: $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m and a SiO <sub>2</sub> gate dielectric as the device is operated in the linear regime with $V_{SG}$ = 3 V, $V_d$ = 1 V                                                                                                   |

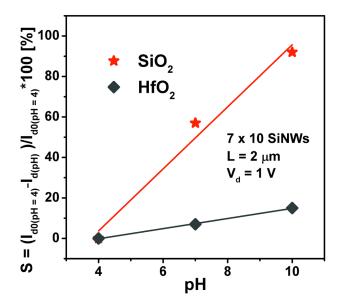

| Figure 6-5: Relative sensitivity as a function of pH for an APTES functionalized structure with $7 \times 10$ SiNWs, $L = 2 \mu m$ and $V_d = 1$ V with a HfO <sub>2</sub> or SiO <sub>2</sub> gate dielectric as the devices are operated in the strong inversion regime104                                                                                           |

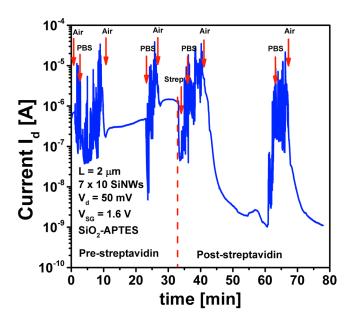

| Figure 6-6: $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 as the device is operated in the subthreshold regime $V_{SG}$ = 1.6 V, $V_d$ = 50 mV for a biotin functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m, $d_{NW}$ = 15 – 30 nm and a SiO <sub>2</sub> gate dielectric106                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

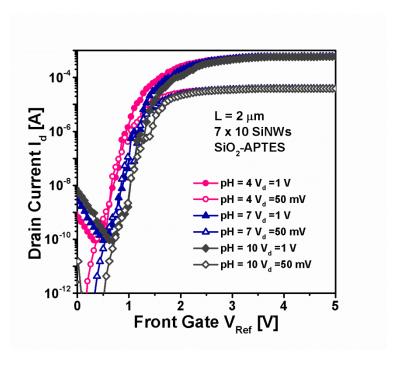

| Figure 6-7: $I_d$ – $V_{Ref}$ curves as the pH increases (pH = 4, 7, 10) for high and low drain potentials $V_d$ = 50 mV, 1 V for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m, $d_{NW}$ = 15 – 30 nm and a SiO <sub>2</sub> gate dielectric                                                                                                                                                                                                                                                               |

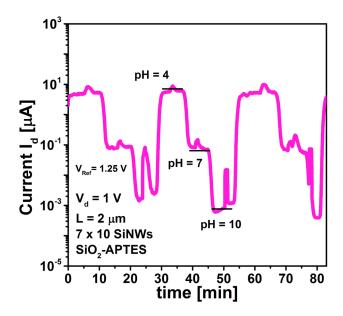

| Figure 6-8: $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 as the device is operated in the subthreshold regime for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m, $d_{NW}$ = 15 – 30 nm and a SiO <sub>2</sub> gate dielectric                                                                                                                                                                                                                                                                   |

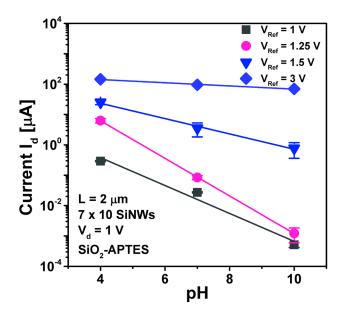

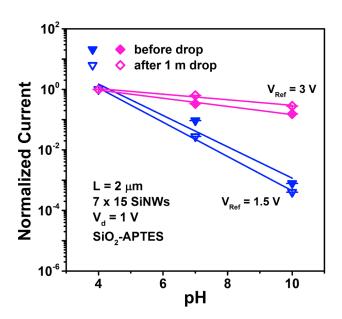

| Figure 6-9: $I_d$ – pH as the pH value is changed from pH = 4 to 10 as the device is operated below threshold $V_{Ref}$ = 1, 1.25 V and in weak inversion $V_{Ref}$ = 1.5 V and strong inversion $V_{Ref}$ = 3 V for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m, $d_{NW}$ = 15-30 nm and a SiO <sub>2</sub> gate dielectric                                                                                                                                                                              |

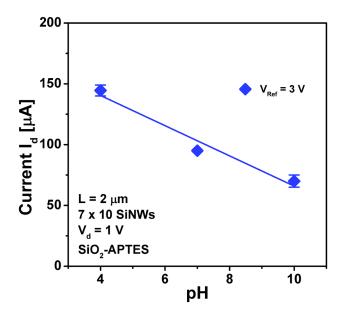

| Figure 6-10: $I_d - pH$ as the pH value is changed from pH = 4 to 10 for an APTES functionalized structure with 7 × 10 SiNWs, $L = 2 \mu m$ , and a SiO <sub>2</sub> gate dielectric as the device is operated in strong inversion $V_{Ref} = 3$ V plotted in a linear scale (Figure 6-9)                                                                                                                                                                                                                                          |

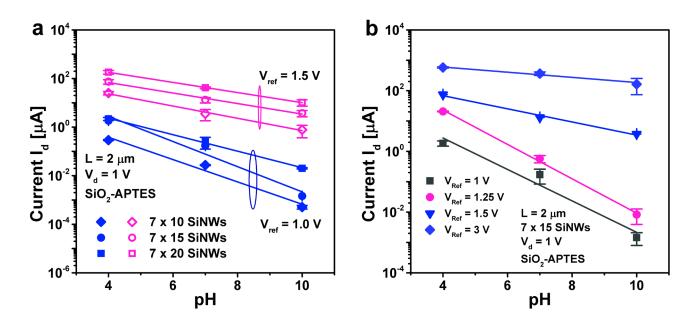

| Figure 6-11: (a) $I_d - pH$ for structures with increasing number of SiNWs 7 × 10, 15, 20 $\mu$ m as the device is operated in subthreshold and weak inversion $V_{Ref} = 1$ , 1.5 V, respectively and (b) $I_d - pH$ as the device is operated below threshold $V_{Ref} = 1$ , 1.25 V and in weak inversion $V_{Ref} = 1.5$ V and strong inversion $V_{Ref} = 3$ V for 7 × 15 SiNWs array. Devices are APTES functionalized, have channel lengths $L = 2 \mu m$ , $d_{NW} = 15 - 30 nm$ and a SiO <sub>2</sub> gate dielectric111 |

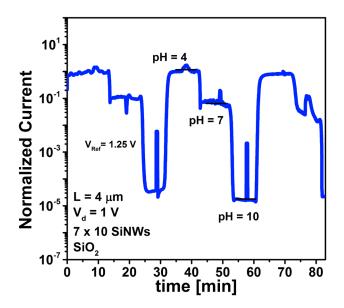

| Figure 6-12: (a) $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 as the device is operated in the subthreshold regime $V_{Ref}$ = 1.25 V, $V_d$ = 1 V for an unmodified SiO <sub>2</sub> structure with 7 × 10 SiNWs, $L$ = 4 $\mu$ m, $d_{NW}$ = 15-30                                                                                                                                                                                                                                                                   |

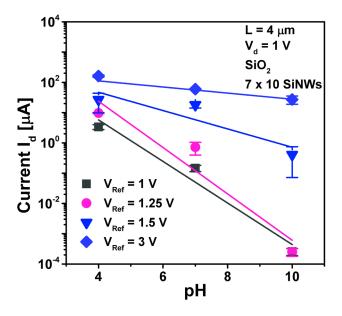

| Figure 6-13: $I_d$ – pH as the pH value is changed from pH = 4 to 10 as the device is operated below threshold $V_{Ref}$ = 1, 1.25 V and in weak inversion $V_{Ref}$ = 1.5 V and strong inversion $V_{Ref}$ = 3 V for an unmodified SiO <sub>2</sub> structure with 7 × 10 SiNWs, $L$ = 4 $\mu$ m, $d_{NW}$ = 15-30112                                                                                                                                                                                                             |

| Figure 6-14: Normalized $I_d$ – $pH$ response before and after a one meter drop from the ground for an APTES functionalized a structure with 7 × 15 SiNWs, $L$ = 2 $\mu$ m, and a SiO <sub>2</sub> gate dielectric as the device is operated in weak and strong inversion $V_{Ref}$ = 1.5, 3 V, respectively113                                                                                                                                                                                                                    |

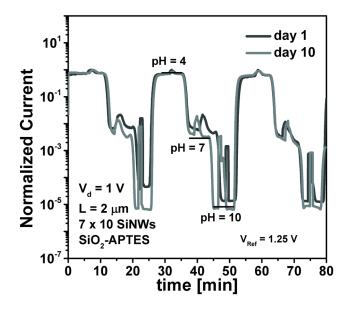

| Figure 6-15: (a) $I_d$ – $t$ as the pH value is changed in cycles (3) from pH = 4 to 10, $V_d$ = 1 V in the subthreshold regime at high drain voltage potentials $V_d$ = 1 V and 10 days after the first measurement for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m                                                                                                                                                                                                                                      |

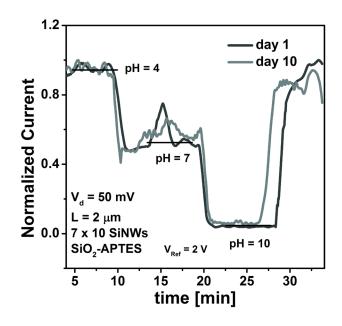

| Figure 6-16: $I_d$ – $t$ as the pH value is changed and the device is operated in strong inversion at low drain voltage potentials $V_d$ = 50 mV and 10 days after the first measurement for an APTES functionalized structure with 7 × 10 SiNWs, $L$ = 2 $\mu$ m                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

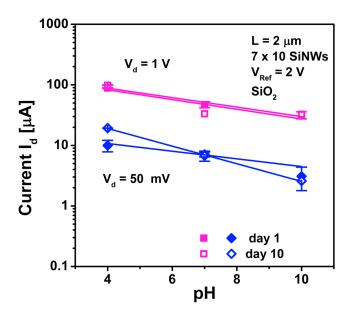

| Figure 6-17: $I_d$ – $t$ as the pH value is changed from pH = 4 to 10 as the device is operated in the strong inversion $V_{Ref}$ = 2 V at high ( $V_d$ = 1 V) and low ( $V_d$ = 50 mV) drain potentials and 10 days after the initial measurement for an unmodified SiO <sub>2</sub> structure with 7 × 10 SiNWs, $L$ = 4 $\mu$ m, $d_{NW}$ = 15 – 30 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

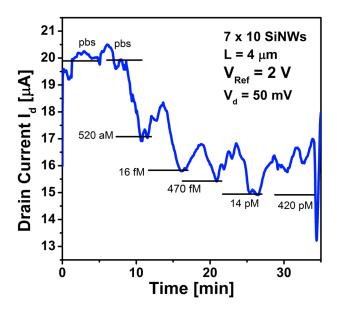

| Figure 6-18: $I_d$ – $t$ as increasing concentrations of streptavidin in PBS solutions are administered for a structure with 7 × 10 SiNWs, $L$ = 4 $\mu$ m as the device is operated in strong inversion regime $V_{Ref}$ = 2 V, $V_d$ = 50 mV                                                                                                         |

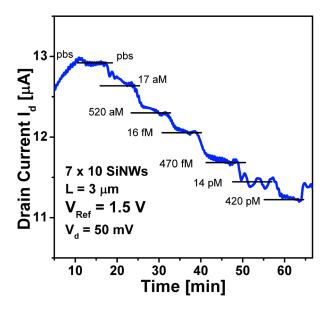

| Figure 6-19: $I_d$ – $t$ as increasing concentrations of streptavidin in PBS solutions are administered for a structure with 7 × 10 SiNWs, $L$ = 3 $\mu$ m as the device is operated in the weak inversion regime $V_{Ref}$ = 1.5 V, $V_d$ = 50 mV                                                                                                     |

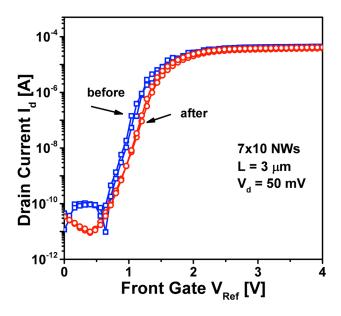

| Figure 6-20: $I_d - V_{Ref}$ for a biotinylated structure with $7 \times 10$ SiNWs and $L = 3$ µm before and after the streptavidin in PBS solutions were administered ( $V_{Ref} = 1.5$ V, $V_d = 50$ mV)                                                                                                                                             |

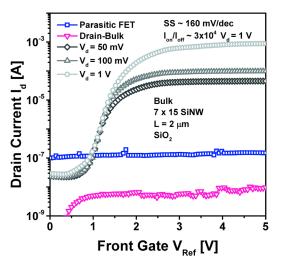

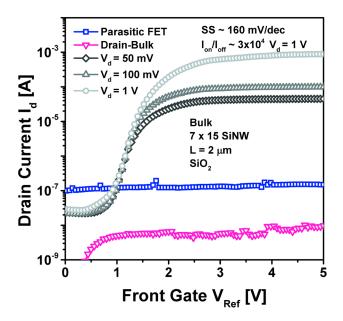

| Figure 7-1: $I_d$ – $V_{Ref}$ for a biotinylated structure with 7 × 15 SiNWs, $L$ = 2 $\mu$ m and fabricated in bulk-Si in PBS solutions for different drain voltage potentials $V_d$ = 50, 100 mV, 1 V)123                                                                                                                                            |

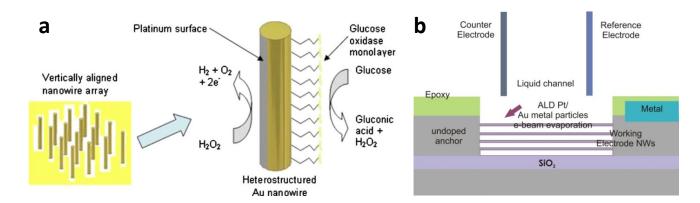

| Figure 8-1: (a) Schematic of hetero-structure Au/Pt nanowire for glucose amperometric sensing, modified from [137]. (b) Schematic cross section of proposed vertically stacked SiNW amperometric sensor                                                                                                                                                |

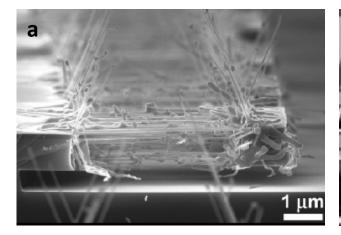

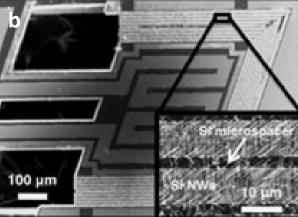

| Figure 8-2: (a) SEM image of cross section view of suspended SiNW array micro-paddle fabricated by VLS, modified from [138]. (b) Thermally isolated suspended Si mass connected to the bulk-Si through the SiNW array, adapted from [139]                                                                                                              |

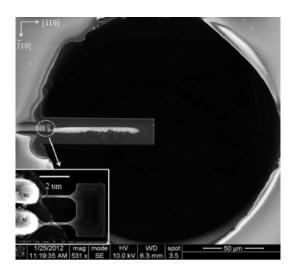

| Figure 8-3: SEM image of SiNW-based cantilever flow sensor, adapted from [144]130                                                                                                                                                                                                                                                                      |

## List of Tables

| Table 2-1: The evolution of the vertically stacked SiNW/Fin FET18                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-2: State-of-the-art for SiNW-FET based protein sensing. APTMS: (3-Aminopropyl)-trimethoxysilane, HEPES: 4-(2-hydroxyethyl)-1 piperazineethanesulfonic acid21                                   |

| Table 2-3: State-of-the-art literature results for SiNW-FET based pH sensing when $SiO_2$ is used as the gate dielectric alone or it has been surface functionalized22                                 |

| Table 2-4: State-of-the-art literature results for SiNW-FET based pH sensing when an insulator with a high- $\kappa$ dielectric constant is used. HMDS: Hexamethyldisiloxane26                         |

| Table 2-5: State-of-the-art literature results for SiNW-FET based pH sensing when a double gate (DG) configuration has been used to amplify the pH sensing response. SG: side-gate 29                  |

| Table 3-1: Short description of process steps for 3D integration                                                                                                                                       |

| Table 3-2: AFM results as the tip is raked against $7 \times 10$ SiNWs structures with increasing lengths $L=2$ , 3, 4 $\mu$ m with different load forces (20 – 100 nN). Courtesy of T. Bieniek, ITE60 |

| Table 7-1: State-of-the-art literature results for SiNW-FET based biosensors fabricated by top-down processes in bulk silicon                                                                          |

# **List of Equations**

| Equation 2.1 | 9   |

|--------------|-----|

| Equation 2.2 | 9   |

| Equation 2.3 | 10  |

| Equation 2.4 | 10  |

| Equation 2.5 | 10  |

| Equation 2.6 | 10  |

| Equation 2.7 | 24  |

| Equation 2.8 | 27  |

| Equation 5.1 | 78  |

| Equation 5.2 | 78  |

| Equation 5.3 | 89  |

| Equation 5.4 | 91  |

| Faustion 8.1 | 128 |

# Technical Acronyms and Abbreviations

| Acronym/Abbreviation | Description                                          |  |  |

|----------------------|------------------------------------------------------|--|--|

| ADE                  | Analog design environment                            |  |  |

| AFM                  | Atomic force microscopy                              |  |  |

| ALD                  | Atomic layer deposition                              |  |  |

| APTES                | (3-Aminopropyl)-triethoxysilane                      |  |  |

| APTMS                | (3-Aminopropyl)-trimethoxysilane                     |  |  |

| BCA                  | Binary collision approximation                       |  |  |

| BG                   | Backgate                                             |  |  |

| BOE                  | Buffered oxide etch                                  |  |  |

| BOX                  | Bottom oxide, buried oxide                           |  |  |

| BSA                  | Bovine serum albumin                                 |  |  |

| С                    | Fitting parameter                                    |  |  |

| $C_{BG}$             | Backgate capacitance                                 |  |  |

| Cdiff                | Differential capacitance                             |  |  |

| Cdl                  | Double layer capacitance                             |  |  |

| $C_{dm}$             | Depletion width capacitance                          |  |  |

| $C_{LG}$             | Solution gate capacitance                            |  |  |

| CLSM                 | Confocal laser scanning microscopy                   |  |  |

| CMi                  | Center for micro-technology                          |  |  |

| CMOS                 | Complementary metal oxide semiconductor              |  |  |

| $C_{ox}$             | Gate oxide capacitance                               |  |  |

| CVD                  | Chemical vapor deposition                            |  |  |

| D                    | Drain                                                |  |  |

| DG                   | Dual-gate/double-gate                                |  |  |

| DIBL                 | Device induced barrier lowering                      |  |  |

| DMF                  | Dimethylformamide                                    |  |  |

| DNA                  | Deoxyribonucleic acid                                |  |  |

| dNW                  | Nanowire diameter                                    |  |  |

| EBL                  | Electron beam lithography                            |  |  |

| e-BRAINS             | Best reliable intelligent ambient nano sensor system |  |  |

| EOT                  | Equivalent oxide thickness                           |  |  |

| EPFL                 | École Polytechnique Fédérale de Lausanne             |  |  |

| FET                  | Field effect transistor                              |  |  |

| FG                   | Front-gate                                           |  |  |

| $F_h$                | Fin height                                           |  |  |

| FIB                  | Focused ion beam                                     |  |  |

| $F_W$                | Fin width                                            |  |  |

| Acronym/Abbreviation | Description                                                 |  |  |

|----------------------|-------------------------------------------------------------|--|--|

| GAA                  | Gate all around                                             |  |  |

| GCS                  | Gouy-Chapman-Stern mode                                     |  |  |

| $g_m$                | Transconductance                                            |  |  |

| Şm,max               | Maximum transconductance                                    |  |  |

| Н                    | Height                                                      |  |  |

| ħ                    | Normalized Plank's constant                                 |  |  |

| HEPES                | (4-(2-hydroxyethyl)-1-piperazineethanesulfonic acid         |  |  |

| HMDS                 | Hexamethyldisiloxane                                        |  |  |

| I                    | Ionic strength                                              |  |  |

| IBS                  | Ion beam services                                           |  |  |

| IC                   | Integrated circuit                                          |  |  |

| ICP                  | Inductively coupled plasma                                  |  |  |

| $I_d$                | Drain current                                               |  |  |

| ID                   | Inner diameter                                              |  |  |

| $I$ d $\phi$ 0       | Baseline current                                            |  |  |

| $I_{d\phi 1}$        | Current induced by the sensing event                        |  |  |

| Ileak1(DG)           | Leakage current measured from side-gate 1                   |  |  |

| Ileak2(DG)           | Leakage current measured from side-gate 1                   |  |  |

| <i>Ioff</i>          | Leakage, off-current                                        |  |  |

| Ion                  | On-current On-current                                       |  |  |

| IPA                  | Isopropanol                                                 |  |  |

| ISFET                | Ion sensitive field effect transistor                       |  |  |

| ITE                  | Institute of Electron Technology                            |  |  |

| JNT                  | Junctionless nanowire transistor                            |  |  |

| KATEC                | ATEC-CONT probe with Concorde-nose like tip spring constant |  |  |

| $k_B$                | Boltzmann constant                                          |  |  |

| КМРР                 | Veeco/Bruker MPP21220 probe spring constant                 |  |  |

| L                    | Length                                                      |  |  |

| LAAS                 | Laboratory for Analysis and Architecture of Systems         |  |  |

| $L_G$                | Local-gate/liquid-gate                                      |  |  |

| LOR                  | Lift-off-resist                                             |  |  |

| LTO                  | Low thermal oxide                                           |  |  |

| m*                   | Effective carrier mass                                      |  |  |

| MC                   | Monte-Carlo                                                 |  |  |

| MEMS                 | Microelectromechanical systems                              |  |  |

| MMA                  | Methyl methacrylate                                         |  |  |

| MOSFET               | Metal oxide semiconductor field effect transistor           |  |  |

| n                    | Electron                                                    |  |  |

| $N_A$                | Avogadro number                                             |  |  |

| $N_{ch}$             | Channel doping concentration                                |  |  |

| $N_d$                | Doping concentration                                        |  |  |

| Ni                   | Intrinsic doping concentration                              |  |  |

|                      | munisie dopnig concentration                                |  |  |

| Acronym/Abbreviation | Description                                             |  |  |

|----------------------|---------------------------------------------------------|--|--|

| Nsd                  | S/D doping concentration                                |  |  |

| NW                   | Nanowire                                                |  |  |

| OD                   | Outer diameter                                          |  |  |

| OTA                  | Operational transconductance amplifiers                 |  |  |

| р                    | Proton                                                  |  |  |

| PBS                  | Phosphate buffered saline                               |  |  |

| PCB                  | Printed circuit board                                   |  |  |

| PCR                  | Polymerase chain reaction                               |  |  |

| PDMS                 | Polydimethylsiloxane                                    |  |  |

| PE                   | Polyethylene                                            |  |  |

| $pH_{pzc}$           | pH near the point of zero charge                        |  |  |

| PMMA                 | Poly methyl methacrylate                                |  |  |

| PSA                  | Prostate specific antigen                               |  |  |

| PTFE                 | Polytetrafluoroethylene                                 |  |  |

| q                    | Elementary charge                                       |  |  |

| $Q_B$                | Depletion layer charge in the silicon                   |  |  |

| $Q_m$                | Mobile charge density                                   |  |  |

| $Q_{ox}$             | Oxide charge                                            |  |  |

| Qss                  | Interface charge                                        |  |  |

| Rc                   | Contact resistance                                      |  |  |

| RE                   | Reference electrode                                     |  |  |

| REFET                | Reference FET                                           |  |  |

| RIE                  | Reactive ion etching                                    |  |  |

| $R_{NW}$             | SiNW resistance                                         |  |  |

| RTA                  | Rapid thermal anneal                                    |  |  |

| S                    | Source                                                  |  |  |

| S                    | Silicon spacer                                          |  |  |

| SR                   | Sensitivity or sensor response                          |  |  |

| Sv                   | Seebeck coefficient                                     |  |  |

| S/V                  | Surface to volume ratio                                 |  |  |

| SB                   | Site-binding                                            |  |  |

| SCE                  | Short channel effects                                   |  |  |

| SEM                  | Scanning electron microscopy                            |  |  |

| SG                   | Side-gate                                               |  |  |

| SiNAPS               | Semiconducting nanowire platform for autonomous sensors |  |  |

| SiNW                 | Silicon nanowire                                        |  |  |

| SOI                  | Silicon-on-insulator                                    |  |  |

| SRH                  | Shockley-Read-Hall                                      |  |  |

| SS<br>T              | Subthreshold slope                                      |  |  |

| T                    | Temperature                                             |  |  |

| TCAD                 | Trench opening                                          |  |  |

| TCAD                 | Technology computer aided design                        |  |  |

| Acronym/Abbreviation             | Description                                                |  |  |

|----------------------------------|------------------------------------------------------------|--|--|

| ta                               | Dielectric thickness                                       |  |  |

| TG                               | Top-gate                                                   |  |  |

| TLM                              | Transfer length method                                     |  |  |

| TNI                              | Tyndall National Institute                                 |  |  |

| $t_R$                            | Response time                                              |  |  |

| $T_{si}$                         | Silicon thickness                                          |  |  |

| TSV                              | Through silicon vias                                       |  |  |

| $U_T$                            | Thermal voltage                                            |  |  |

| $V_{\it BG}$                     | Backgate potential                                         |  |  |

| $V_d$                            | Drain potential                                            |  |  |

| $V_{fb}$                         | Flat-band                                                  |  |  |

| $V_{FG}$                         | Front-gate voltage                                         |  |  |

| $V_G$                            | Gate voltage                                               |  |  |

| $V_{LG}$                         | Local-gate potential, liquid-gate potential                |  |  |

| VLS                              | Vapour liquid solid                                        |  |  |

| VOC                              | Volatile organic carbon                                    |  |  |

| $V_{ov}$                         | Overdrive voltage                                          |  |  |

| $V_{\it Ref}$                    | Reference electrode potential                              |  |  |

| $V_s$                            | Source to drain potential                                  |  |  |

| $V_{SG}$                         | Side-gate voltage                                          |  |  |

| $V_{\it th}$                     | Threshold voltage                                          |  |  |

| W                                | Width                                                      |  |  |

| XPS                              | X-ray photoelectron spectroscopy                           |  |  |

| ZT                               | The dimensionless figure of merit (thermoelectric devices) |  |  |

| $\alpha$                         | Sensitivity parameter                                      |  |  |

| $\alpha'$                        | Coupling efficiency                                        |  |  |

| $eta_{int}$                      | Intrinsic buffer capacitance of the dielectric             |  |  |

| $\mathcal{E}_{o}$                | Vacuum dielectric constant                                 |  |  |

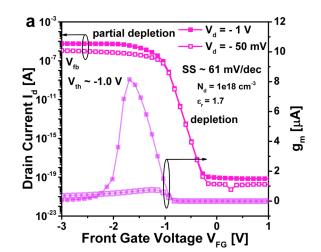

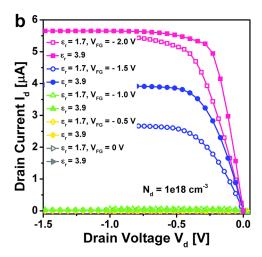

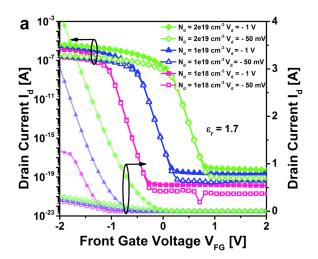

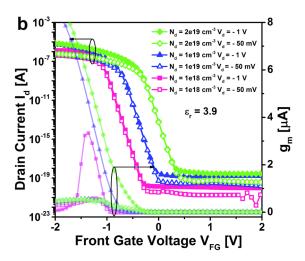

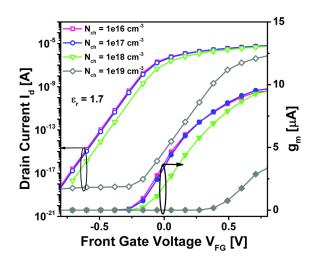

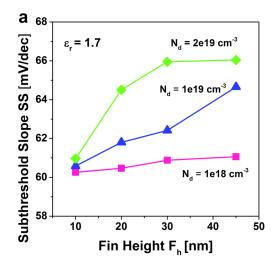

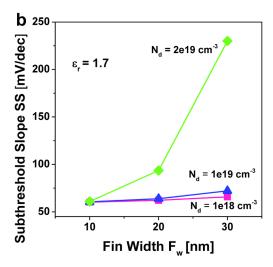

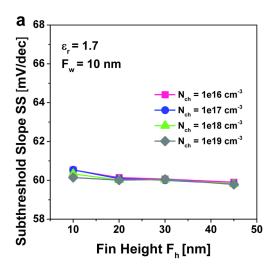

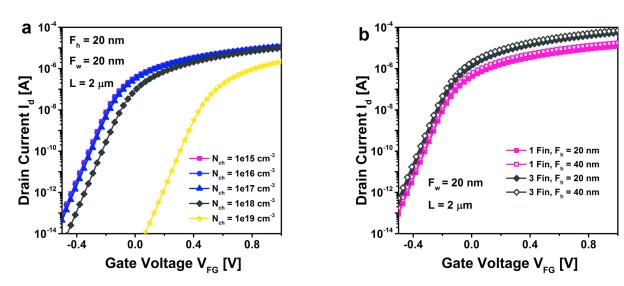

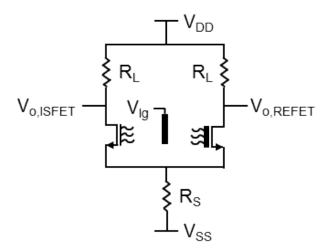

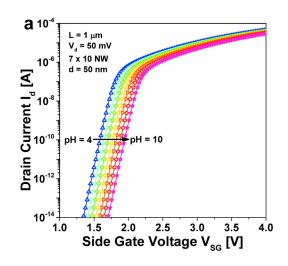

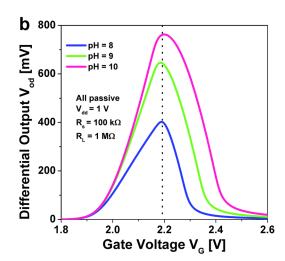

| $\mathcal{E}r$                   | Dielectric constant of the material                        |  |  |