#### Modeling and Design Techniques for 3-D ICs under Process, Voltage, and Temperature Variations

THÈSE Nº 5543 (2012)

PRÉSENTÉE LE 21 NOVEMBRE V2012 À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI) PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Hu XU

acceptée sur proposition du jury:

Prof. B. Rimoldi, président du jury Prof. G. De Micheli, directeur de thèse Prof. L. Benini, rapporteur Prof. Y. Leblebici, rapporteur Prof. D. Soudris, rapporteur

Try not to become a man of success, but rather try to become a man of value. — Albert Einstein

To my parents...

## Acknowledgements

Pursuing and completing my PhD degree is definitely one of the most exciting and challenging activities in the first 30 years of my life. I have shared both the sweet and difficult parts of this journey with many people. It has been a pleasant challenge and enjoyment to spend four years in EPFL, and its members will always remain dear to me.

First of all, I want to express my deep thanks to my thesis supervisor, Professor Giovanni De Micheli, for his continuous encouragement and thoughtful guidance along my pursuit of PhD. Professor De Micheli has set an excellent example for my research and future career. I want to show my sincere thanks to Professor Vasilis F. Pavlidis, for his kind patience and indispensable help to my work in EPFL. Professor Pavlidis' inspiring and scrupulous guidance has led me into the world of 3-D ICs. I also thank the other members of my PhD thesis committee: Professors Bixio Rimoldi, Yusurf Leblebici, Luca Benini, and Dimitris Soudris, for their precious time and helpful suggestions to improve my research and this thesis. I am very grateful to Professor Wayne P. Burleson, whose beneficial advices and kind concerns have helped me to carry forward my work and improve my research capability.

I want to express my gratitude to all my colleagues in Integrated Systems Laboratory, EPFL. Thanks to their warm help and kindness, I have spent a pleasant time in Lausanne, in both my PhD research and daily life. I am especially happy to thank Mme. Christina Govoni for her careful and tireless administrative service. I also want to thank the students I have worked with, Mr. Xifan Tang, Mr. Cheng Zhang, Mr. Muhammad Waqas Chaudhary, and Mr. Dimitrios Anagnostos, for their help to improve my research works.

Last but not the least, I am honoured to acknowledge my gratitude to Swiss National Science Foundation and Intel Braunschweig Lab (Germany), for their generous support.

Lausanne, 26 October 2012

Hu XU

### Abstract

*Three-dimensional* (3-D) integration is a promising solution to further enhance the density and performance of modern *integrated circuits* (ICs). In 3-D ICs, multiple dies (tiers or planes) are vertically stacked. These dies can be designed and fabricated separately. In addition, these dies can be fabricated in different technologies. The effect of different sources of variations on 3-D circuits, consequently, differ from 2-D ICs. As technology scales, these variations significantly affect the performance of circuits. Therefore, it is increasingly important to accurately and efficiently model different sources of variations in 3-D ICs.

The process, voltage, and temperature variations in 3-D ICs are investigated in this dissertation. Related modeling and design techniques are proposed to design a robust 3-D IC. Process variations in 3-D ICs are first analyzed. The effect of process variations on synchronization and 3-D clock distribution networks, is carefully studied. A novel statistical model is proposed to describe the timing variation in 3-D clock distribution networks caused by process variations. Based on this model, different topologies of 3-D clock distribution networks are compared in terms of skew variation. A set of guidelines is proposed to design 3-D clock distribution networks with low clock uncertainty.

Voltage variations are described by power supply noise. Power supply noise in 3-D ICs is investigated considering different characteristics of potential 3-D power grids in this thesis. A new algorithm is developed to fast analyze the steady-state *IR*-drop in 3-D power grids. The first droop of power supply noise, also called resonant supply noise, is usually the deepest voltage drop in power distribution networks. The effect of resonant supply noise on 3-D clock distribution networks is investigated. The combined effect of process variations and power supply noise is modeled by skitter consisting of both skew and jitter. A novel statistical model of skitter is proposed. Based on this proposed model and simulation results, a set of guidelines has been proposed to mitigate the negative effect of process and voltage variations on 3-D clock distribution networks.

Thermal issues in 3-D ICs are considered by carefully modeling *thermal through silicon vias* (TTSVs) in this dissertation. TTSVs are vertical vias which do not carry signals, dedicated to facilitate the propagation of heat to reduce the temperature of 3-D ICs. Two analytic models are proposed to describe the heat transfer in 3-D circuits related to TTSVs herein, providing proper closed-form expressions for the thermal resistance of the TTSVs. The effect of different physical and geometric parameters of TTSVs on the temperature of 3-D ICs is analyzed. The proposed models can be used to fast and accurately estimate the temperature to avoid the overuse of TTSVs occupying a large portion of area.

#### Abstract

A set of models and design techniques is proposed in this dissertation to describe and mitigate the deleterious effects of process, voltage, and temperature variations in 3-D ICs. Due to the continuous shrink in the feature size of transistors, the large number of devices within one circuit, and the high operating frequency, the effect of these variations on the performance of 3-D ICs becomes increasingly significant. Accurately and efficiently estimating and controlling these variations are, consequently, critical tasks for the design of 3-D ICs.

**Keywords:** 3-D ICs, process variations, power supply noise, temperature variation, clock distribution networks, power distribution networks, clock skew, clock jitter, thermal model

## Résumé

L'intégration dans la *Troisième-Dimension* (3-D) est une solution prometteuse pour continuer d'accroitre la densité et la performance des Circuits Intégrés (Integrated Circuits - ICs) modernes. Dans les circuits 3-D, de multiples puces sont empilées verticalement. Chacune de ces puces peut être conçue et fabriquée séparément. De plus, ces puces peuvent être fabriquées dans des technologies variées. Les effets des différentes sources de variations sur les circuits 3-D, diffèrent ainsi des circuits 2-D. A mesure que les technologies évoluent, les variations affectent significativement les performances des circuits. Ainsi, il est d'une important capitale de modéliser de façon précise et efficace les différentes sources de variations des circuits 3-D. Les variations dues aux procédés de fabrication, aux alimentations et là température sont étudiées dans ce manuscrit. La modélisation associée, ainsi que des techniques de conception adaptées sont proposées afin de concevoir des circuits 3-D robustes.

Les variations dues aux procédés de fabrication des circuits 3-D sont dans un premier temps analysées. Les effets des procédés de fabrication sur la synchronisation et la distribution de l'horloge sont étudiés minutieusement. Un nouveau modèle statistique est alors proposé pour décrire les variations de timing dans les réseaux 3-D de distribution d'horloge, sous l'influence des variations dans les procédés de fabrication. S'appuyant sur ce modèle, différentes topologies de réseaux d'horloge 3-D sont comparées en termes de skew. Une méthodologie de conception est alors proposée pour des distributions d'horloge 3-D avec une faible incertitude sur l'horloge.

Les variations de la tension sont décrites au moyen de bruit sur l'alimentation. Le bruit sur l'alimentation dans les circuits 3-D est étudié en considérant différents maillages pour la distribution d'alimentation. Un nouvel algorithme est alors développé pour permettre une analyse rapide de la chute statique du produit courant-résistance dans les mailles d'alimentation des circuits 3-D. Le premier pic sur le bruit d'alimentation, aussi appelé bruit résonnant d'alimentation, correspond habituellement la plus importanter chute de tension du réseau. L'effet de la résonnance d'alimentation sur le réseau de distribution d'horloge est étudié. L'effet combiné de la variation des procédés de fabrication et du bruit sur l'alimentation est modélisé par du skew et du jitter. Un nouveau modèle statistique de skitter est alors proposé. Basé sur le modèle proposé et sur des résultats de simulation, un jeu de règles a été décrit afin de réduire l'effet négatif des variations sur le réseau de distribution d'horloge 3-D.

Les contraintes thermiques dans les circuits 3-D sont considérées par une modélisation soignée des contacts thermiques 3-D (Thermal Through Silicon Vias - TTSVs). Les TTSVs sont des interconnexions verticales ne transmettant pas de signaux mais dédiées faciliter

#### Résumé

l'évacuation de chaleur et donc de réduire la température des circuits 3-D. Deux modèles analytiques sont proposés pour décrire les transferts thermiques dans les circuits 3-D en présence de TTSVs, en proposant une forme close pour la résistance thermique des TTSVs. L'effet sur la température de différentes géométries et dimensions de TTSVs a été analysé. Les modèles proposés sont utilisables pour une estimation rapide et précise de la température afin d'éviter une utilisation abusive de TTSVs, qui occupent une large surface.

Dans cette thèse, un jeu de modèles et de techniques de conception est proposé afin de décrire et de réduire les effets nuisibles de la variation des procédés de fabrication, de l'alimentation et de la température dans les circuits 3-D. En raison de la réduction des dimensions des transistors, du grand nombre de composants au sein d'un même circuit et de l'importante fréquence de fonctionnement, les effets de ces variations sur les performances des circuits 3-D deviennent de plus en plus importants. L'estimation fine et efficace, ainsi que le contrôle de ces variations sont ainsi une tâche critique dans la conception de circuits 3-D.

**Mots-clés :** Circuits 3-D, variations de procédés, buit d'alimentation, variation de température, réseau de distribution d'horloge, réseau de distribution d'alimentation, skew, jitter, modèles thermiques

# Contents

| Ac | knov            | wledge   | ments                                                     | v   |

|----|-----------------|----------|-----------------------------------------------------------|-----|

| Ał | ostra           | ct (Eng  | lish/Français)                                            | vii |

| Li | st of [         | Figures  | S                                                         | xiv |

| Li | ist of Tables x |          | xx                                                        |     |

| 1  | Intr            | oducti   | on                                                        | 1   |

|    | 1.1             | Backg    | round of 3-D ICs                                          | 1   |

|    | 1.2             | Classi   | fication of 3-D Circuits                                  | 6   |

|    |                 | 1.2.1    | System-in-Package                                         | 6   |

|    |                 | 1.2.2    | System-on-Package                                         | 8   |

|    |                 | 1.2.3    | Fine-grain 3-D ICs                                        | 8   |

|    | 1.3             | Manu     | facturing Technologies for 3-D ICs                        | 10  |

|    |                 | 1.3.1    | TSV-based 3-D ICs                                         | 11  |

|    |                 | 1.3.2    | Physical and electrical characteristics of TSVs           | 12  |

|    | 1.4             | Clock    | Distribution Networks in 3-D ICs                          | 15  |

|    |                 | 1.4.1    | Synchronous circuits                                      | 16  |

|    |                 | 1.4.2    | Clock signal distribution                                 | 17  |

|    |                 | 1.4.3    | 3-D clock trees                                           | 20  |

|    | 1.5             | Contr    | ibutions                                                  | 22  |

|    | 1.6             | Assun    | nptions and Limitations                                   | 22  |

|    | 1.7             | Organ    | nization of the Dissertation                              | 23  |

| 2  | Pro             | cess, Vo | oltage, and Temperature Variations in Integrated Circuits | 25  |

|    | 2.1             | Proce    | ss Variations                                             | 25  |

|    |                 | 2.1.1    | Sources of process variability                            | 25  |

|    |                 | 2.1.2    | Effect of process variations on timing and power          | 28  |

|    |                 | 2.1.3    | Delay model for devices and interconnects                 | 30  |

|    | 2.2             | Power    | Supply Noise                                              | 33  |

|    |                 | 2.2.1    | Power distribution networks                               | 33  |

|    |                 | 2.2.2    | Sources and effect of power supply noise                  | 36  |

|    |                 | 2.2.3    | Modeling techniques for power supply noise                | 38  |

#### Contents

|   | 2.3 | Temp    | erature Variations                                         | 40  |

|---|-----|---------|------------------------------------------------------------|-----|

|   |     | 2.3.1   | Thermal issues in integrated circuits                      | 40  |

|   |     | 2.3.2   | Thermal modeling methods for integrated circuits           | 42  |

|   | 2.4 | Sumn    | nary                                                       | 44  |

| 3 | Pro | cess Va | uriations in 3-D ICs                                       | 47  |

|   | 3.1 | Proce   | ss Variations Modeling for Integrated Circuits             | 47  |

|   |     | 3.1.1   | Monte-Carlo simulations                                    | 47  |

|   |     | 3.1.2   | Statistical static siming analysis                         | 48  |

|   |     | 3.1.3   | Related works on process variations in 3-D ICs             | 49  |

|   | 3.2 | The E   | ffect of Process Variations on Clock Distribution Networks | 51  |

|   |     | 3.2.1   | Process-induced statistical skew                           | 52  |

|   |     | 3.2.2   | Spatial correlation                                        | 53  |

|   | 3.3 | A Nov   | rel Model for Process-Induced Skew in 3-D ICs              | 54  |

|   |     | 3.3.1   | Problem formulation for modeling skew variation            | 55  |

|   |     | 3.3.2   | Modeling the statistical delay of a buffer stage           | 55  |

|   |     | 3.3.3   | Modeling the statistical skew in 3-D circuits              | 58  |

|   |     | 3.3.4   | Accuracy of the proposed model                             | 63  |

|   |     | 3.3.5   | Extension of the model to include interconnect variations  | 66  |

|   | 3.4 | Proce   | ss Variations Tolerant 3-D Clock Distribution Networks     | 68  |

|   |     | 3.4.1   | Skew variation of conventional 3-D clock trees             | 68  |

|   |     | 3.4.2   | A novel multi-group 3-D clock tree                         | 75  |

|   |     | 3.4.3   | Mitigating skew variations with clock grids                | 78  |

|   |     | 3.4.4   | 3-D clock trees with multiple domains                      | 79  |

|   | 3.5 | Sumn    | nary                                                       | 85  |

| 4 | Pow | ver Sup | pply Noise in 3-D ICs                                      | 87  |

|   | 4.1 | 3-D P   | ower Distribution Networks                                 | 87  |

|   | 4.2 |         | hod for Fast <i>IR</i> -Drop Analysis of 3-D ICs           | 88  |

|   |     | 4.2.1   | Problem formulation                                        | 88  |

|   |     | 4.2.2   | Row-based algorithm for 3-D PDNs                           | 92  |

|   |     | 4.2.3   | Simulation results                                         | 94  |

|   | 4.3 | Mode    | ling Resonant Supply Noise in 3-D ICs                      | 95  |

|   |     | 4.3.1   | Resonant Noise <i>vs</i> . On-Chip Current                 | 97  |

|   |     | 4.3.2   | Resonant Noise <i>vs.</i> Resistance of TSVs               | 100 |

|   |     | 4.3.3   | Resonant Noise <i>vs</i> . Number of Tiers                 | 100 |

|   |     | 4.3.4   | High-Frequency Power Supply Noise                          | 101 |

|   | 4.4 | Clock   | Jitter due to the First Droop of Power Supply Noise        | 101 |

|   | 4.5 | Sumn    | nary                                                       | 104 |

|   |     |         |                                                            |     |

| 5 | Con | nbined         | Effect of Process and Voltage Variations on Clock Uncertainty                 | 107 |

|---|-----|----------------|-------------------------------------------------------------------------------|-----|

|   | 5.1 | Skitte         | r: A Unified Treatment of Skew and Jitter                                     | 107 |

|   | 5.2 | Mode           | ling Skitter in 2-D Clock Distribution Networks                               | 109 |

|   |     | 5.2.1          | Delay distribution of a buffer stage                                          | 109 |

|   |     | 5.2.2          | Skitter considering process variations and power supply noise $\ldots \ldots$ | 111 |

|   |     | 5.2.3          | Skitter for different buffer insertions                                       | 114 |

|   |     | 5.2.4          | Decreasing skitter in 2-D circuits                                            | 122 |

|   | 5.3 | Exten          | ding the Skitter Model to 3-D Clock Distribution Networks                     | 124 |

|   |     | 5.3.1          | Linear statistical model for buffers and interconnects                        | 125 |

|   |     | 5.3.2          | Modeling setup and hold skitter                                               | 127 |

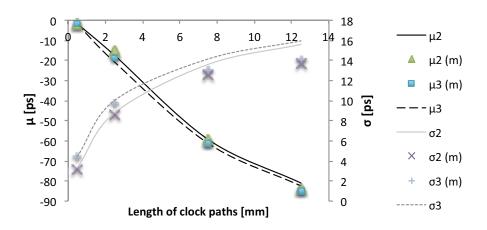

|   |     | 5.3.3          | Skitter <i>vs</i> . length of clock paths                                     | 131 |

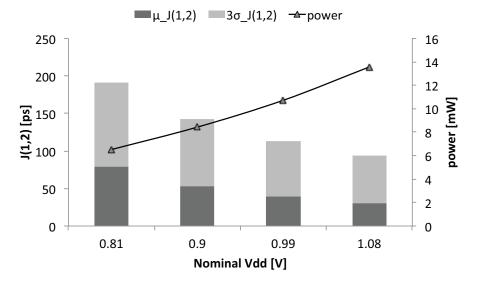

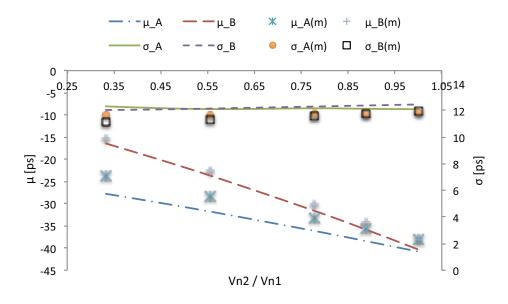

|   |     | 5.3.4          | Skitter <i>vs.</i> $V_n$ in different tiers                                   | 132 |

|   |     | 5.3.5          | The effect of $\phi$ on skitter                                               | 136 |

|   |     | 5.3.6          | The effect of $f_n$ on skitter                                                | 139 |

|   | 5.4 | Metho          | odologies for Skitter Mitigation in 3-D ICs                                   | 141 |

|   |     | 5.4.1          | Skitter for different buffer insertion                                        | 141 |

|   |     | 5.4.2          | Tradeoffs between skitter and power consumption                               | 143 |

|   |     | 5.4.3          | Guidelines to mitigate skitter                                                | 143 |

|   | 5.5 | Case S         | Study of 3-D Clock Trees                                                      | 145 |

|   |     | 5.5.1          | 3-D clock tree synthesis                                                      | 145 |

|   |     | 5.5.2          | Skitter in synthesized 3-D clock trees                                        | 147 |

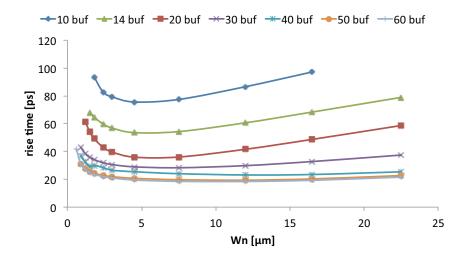

|   | 5.6 | Fast B         | uffer Insertion for 3-D Trees                                                 | 151 |

|   |     | 5.6.1          | Uniform buffer insertion                                                      | 153 |

|   |     | 5.6.2          | Delay model of 3-D interconnects for buffer insertion                         | 153 |

|   |     | 5.6.3          | Iterative buffer insertion algorithm                                          | 156 |

|   |     | 5.6.4          | Simulation results                                                            | 160 |

|   | 5.7 | Sumn           | nary                                                                          | 163 |

| 6 | Нор | t Tranc        | sfer Model of Thermal TSVs                                                    | 165 |

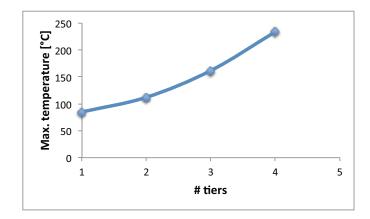

| U | 6.1 |                | nal Issues in 3-D ICs                                                         |     |

|   | 6.2 |                | cation and Structure of Thermal TSVs                                          | 167 |

|   | 6.3 |                | tical Heat Transfer Model for Thermal TSVs                                    |     |

|   | 0.5 | 6.3.1          | Lumped heat transfer model for TTSVs                                          |     |

|   |     | 6.3.1<br>6.3.2 | Distributed heat transfer model for TTSVs                                     |     |

|   | 6.4 |                |                                                                               | 171 |

|   | 6.4 | 6.4.1          | of the Physical Parameters of TTSVs on 3-D ICs                                |     |

|   |     | 6.4.1<br>6.4.2 |                                                                               |     |

|   |     |                | The effect of the thickness of the dielectric liner                           |     |

|   |     | 6.4.3          | The effect of the thickness of the silicon substrate                          |     |

|   |     | 6.4.4          | The effect of TTSV density                                                    | 177 |

|   | 0 - | 6.4.5          | 3-D DRAM- $\mu$ P Case Study                                                  |     |

|   | 6.5 | Sumn           | nary                                                                          | 179 |

#### Contents

| 7  | Con                   | clusions and Future Directions | 181 |

|----|-----------------------|--------------------------------|-----|

|    | 7.1                   | Conclusions                    | 181 |

|    | 7.2                   | Future Directions              | 183 |

| Bi | Bibliography 200      |                                |     |

| Li | List of Abbreviations |                                |     |

| Cu | Curriculum Vitae      |                                | 203 |

# List of Figures

| 1.1  | The development of integrated circuits over time, where (a) and (b) are the           |    |

|------|---------------------------------------------------------------------------------------|----|

|      | increase in the number of transistors and the clock frequency of Intel processors,    |    |

|      | respectively [1,2]                                                                    | 2  |

| 1.2  | The increase in interconnect delay with technology generations [3]                    | 3  |

| 1.3  | Different levels of 3-D integration, where (a) is the cross-section of a 3-D circuit  |    |

|      | consisting of two dies [4] and (b) is a vertically stacked inverter [5]               | 4  |

| 1.4  | Lengths of the longest and average interconnects vs. the number of tiers [6]          | 5  |

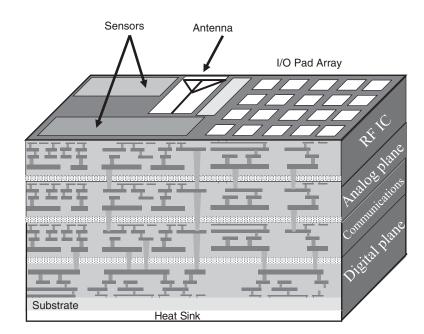

| 1.5  | An example of a heterogeneous 3-D circuit containing both digital and analog          |    |

|      | circuitries [7].                                                                      | 6  |

| 1.6  | System-in-Packages implemented with different methods: (a) wire bonding [8],          |    |

|      | (b) interconnects on the periphery of dies [9], (c) vertical interconnect array [10], |    |

|      | and (d) interconnects on the faces of a 3-D stack [9].                                | 7  |

| 1.7  | Xilinx Virtex-7 FPGA based on 2.5-D System-on-Package [11]                            | 8  |

| 1.8  | Different types of fin-FETs, where (a) and (b) are an Intel Tri-Gate [12] and a 3-D   |    |

|      | fin-FET [13], respectively.                                                           | 9  |

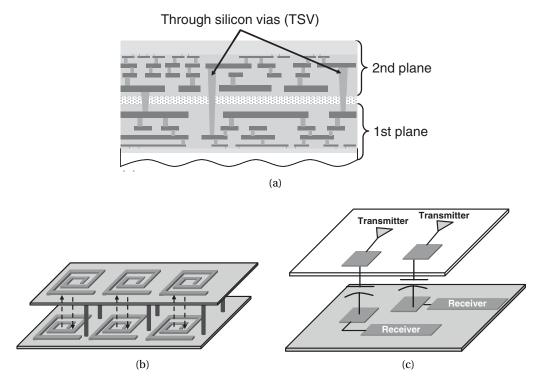

| 1.9  | Communication mechanisms in different fine-grain 3-D ICs [7]: (a) TSVs, (b)           |    |

|      | inductive coupling, and (c) capacitive coupling.                                      | 10 |

| 1.10 | Typical fabrication steps for 3-D ICs [7]: (a) wafer preparation, (b) TSV etching,    |    |

|      | (c) wafer thinning, bumping, and handle wafer attachment, (d) wafer bonding,          |    |

|      | and (e) handle wafer removal                                                          | 11 |

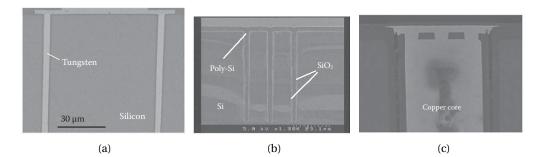

| 1.11 | Examples of TSVs using different filling materials: (a) IBM tungsten TSV [14], (b)    |    |

|      | Tohoku University polysilicon TSV [15], and (c) Cu TSV [16]                           | 13 |

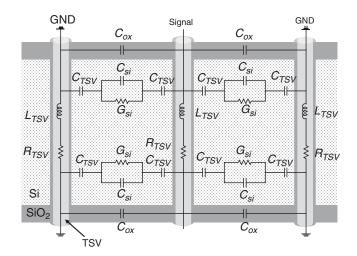

| 1.12 | Electrical model of a TSV [7,17].                                                     | 13 |

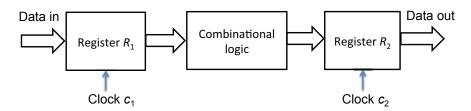

|      | A data path including combinational and sequential circuits                           | 15 |

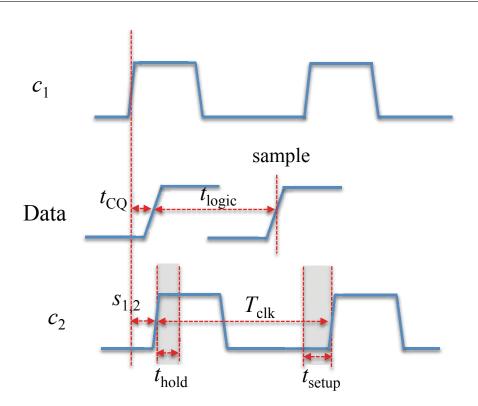

| 1.14 | The waveforms of clock and data signals of the components in Fig. 1.13                | 16 |

|      | An unbalanced clock tree [18].                                                        | 17 |

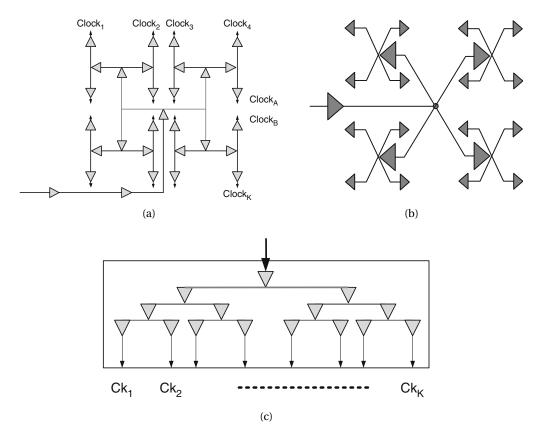

| 1.16 | Balanced clock trees, where (a), (b), and (c) are an H-tree, an X-tree, and a binary  |    |

|      | tree, respectively [18].                                                              | 18 |

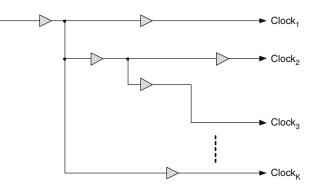

|      | A clock distribution network consisting of three clock spines [18]                    | 19 |

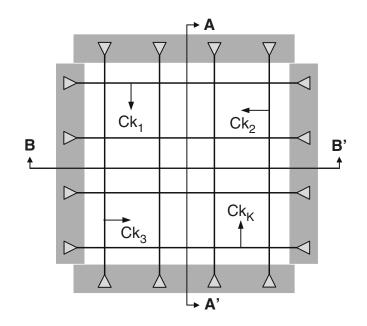

| 1.18 | A clock grid with clock drivers on four sides [18].                                   | 20 |

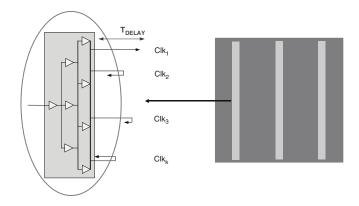

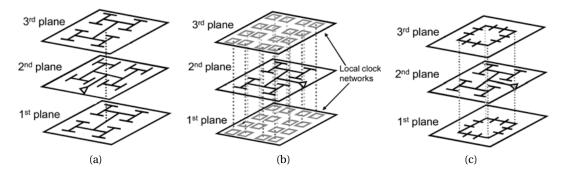

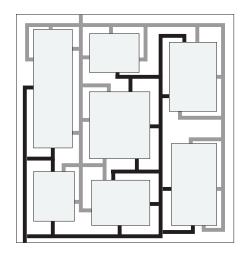

| 1.19 | 3-D H-trees with different topologies across tiers, where (a) is a 3-D H-tree with    |    |

|      | replicated 2-D H-trees on each tier [19], (b) is a 2-D H-tree with local rings in     |    |

|      | other tiers, and (c) is an H-tree with global rings in other tiers.                   | 20 |

| List | of | Figures |

|------|----|---------|

|------|----|---------|

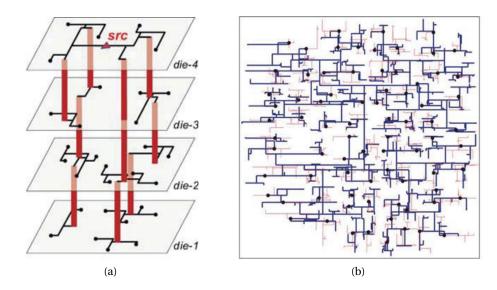

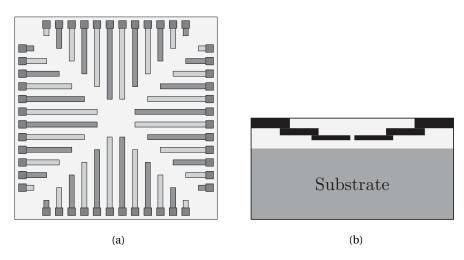

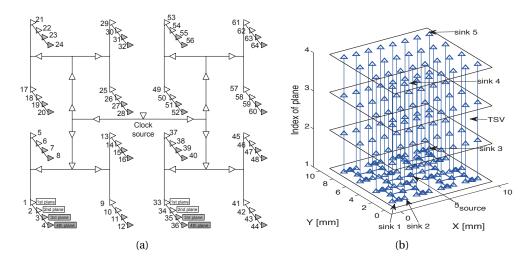

| 1.20 | 3-D clock trees from the CTS algorithm [20], where (a) is a clock tree in a four-<br>tier circuit and (b) is the top view of a clock tree in a two-tier circuit. TSVs are<br>denoted by dots in (b). | 21 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                                                                                      |    |

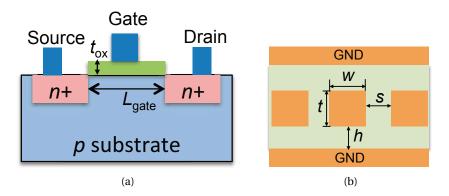

| 2.1  | Physical parameters of transistors and metal interconnects, where (a) and (b)                                                                                                                        |    |

|      | are the cross-sections of an NMOS transistor and a metal wire, respectively                                                                                                                          | 26 |

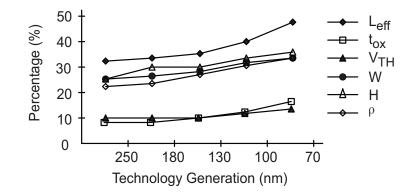

| 2.2  | The $3\sigma$ variation of several parameters <i>vs</i> . technology generations [21], [22]                                                                                                          | 26 |

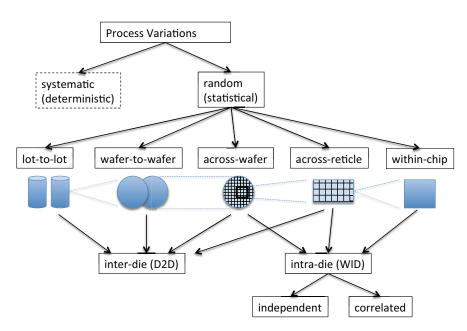

| 2.3  | The classification of process variations.                                                                                                                                                            | 28 |

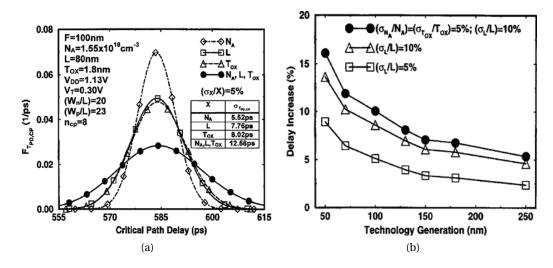

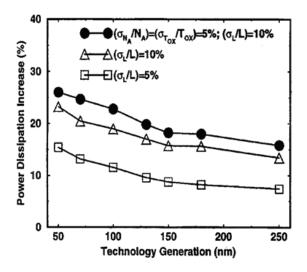

| 2.4  | The delay variation of critical paths due to process variations, where (a) is the                                                                                                                    |    |

|      | distribution of critical path delay for different parameter variations and (b) is                                                                                                                    |    |

|      | the increase in critical path delay corresponding to a $3\sigma$ delay deviation. [23] .                                                                                                             | 29 |

| 2.5  | The increase in dynamic power due to process variations corresponding to a $3\sigma$                                                                                                                 |    |

|      | critical-path delay deviation [23]                                                                                                                                                                   | 30 |

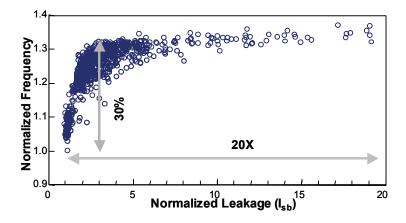

| 2.6  | Distribution of clock frequency and leakage current due to process variations [24].                                                                                                                  |    |

| 2.7  | An <i>RC</i> tree with two sinks.                                                                                                                                                                    | 32 |

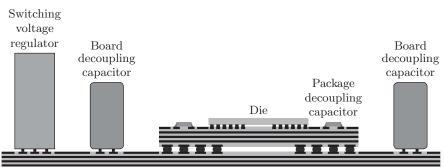

| 2.8  | Cross-section of the PDN hierarchy with decoupling capacitance [25].                                                                                                                                 | 34 |

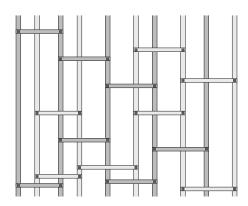

| 2.9  | Routed P/G networks [25,26]                                                                                                                                                                          | 34 |

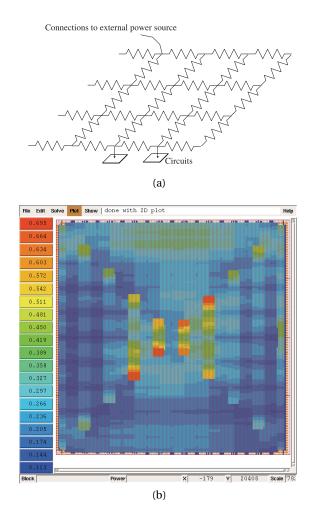

| 2.10 | A power and ground mesh [25]                                                                                                                                                                         | 35 |

| 2.11 | A power (VDD) and ground (GND) grid network, where (a) [25,27] and (b) are a                                                                                                                         |    |

|      | 3-D plot and a top-view of power grids, respectively.                                                                                                                                                | 35 |

| 2.12 | A PDN with P/G planes [25], where the power and ground planes are depicted in                                                                                                                        |    |

|      | dark and light gray, respectively.                                                                                                                                                                   | 36 |

| 2.13 | PDNs with P/G cascaded rings [25, 28], where (a) and (b) are the top-view and                                                                                                                        |    |

|      | cross-section of cascaded rings, respectively.                                                                                                                                                       | 37 |

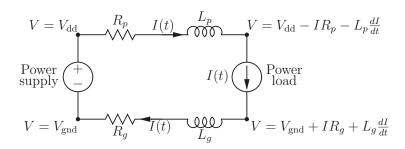

| 2.14 | Power supply noise caused by <i>IR</i> -drop and $L\frac{di}{dt}$ drop in a simplified PDN [25].                                                                                                     | 38 |

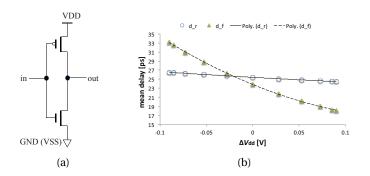

| 2.15 | Delay of a CMOS inverter <i>vs.</i> the fluctuation of supply voltage, where (a) is the                                                                                                              |    |

|      | schematic of a CMOS inverter. (b) is the change of the inverter delay, where both                                                                                                                    |    |

|      | the rise-fall (d_r) and fall-rise (d_f) delay are shown.                                                                                                                                             | 38 |

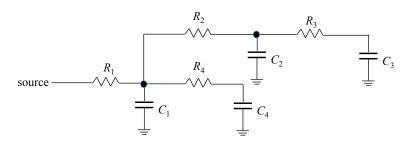

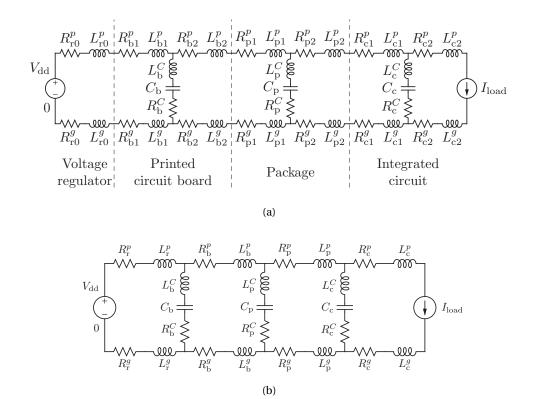

| 2.16 | A simplified one-dimensional circuit model for PDNs [25], where (a) models                                                                                                                           |    |

|      | both the upstream and downstream impedance of all levels of a PDN and (b) is a                                                                                                                       |    |

|      | compact version of (a)                                                                                                                                                                               | 39 |

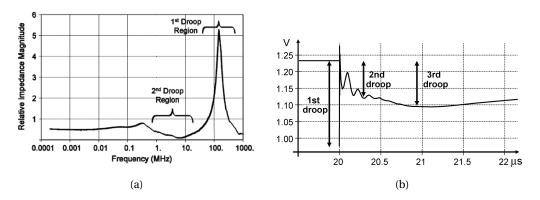

| 2.17 | Power supply noise in PDNs. (a) is the impedance of a PDN at different frequen-                                                                                                                      |    |

|      | cies [29] and (b) is the waveform of a resonant supply noise [30]                                                                                                                                    | 40 |

| 2.18 | Resistor network used to model the on-chip PDNs [27], where (a) and (b) are the                                                                                                                      |    |

|      | topology (not to scale) and voltage drop of the GND network                                                                                                                                          | 41 |

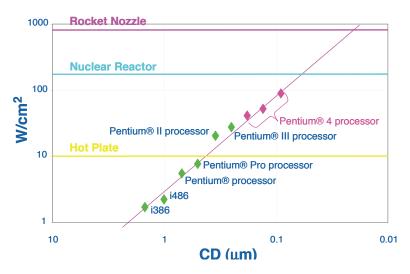

| 2.19 | The power density of Intel microprocessors vs. feature size of transistors [31, 32].                                                                                                                 | 42 |

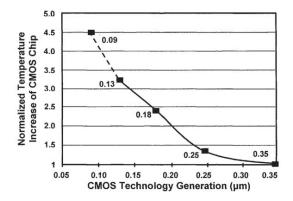

| 2.20 | The temperature increase in CMOS circuits <i>vs</i> . feature size of transistors [33].                                                                                                              | 42 |

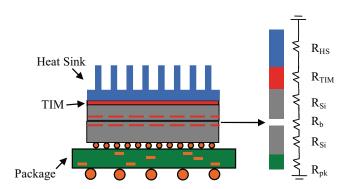

| 2.21 | One-dimensional steady-state heat transfer model for a two-tier 3-D IC [34],                                                                                                                         |    |

|      | where TIM is the abbreviation for thermal interface material.                                                                                                                                        | 43 |

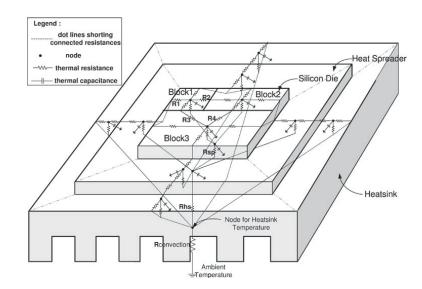

| 2.22 | A HotSpot <i>RC</i> model for a circuit with three architectural modules [35,36]                                                                                                                     | 45 |

|      |                                                                                                                                                                                                      |    |

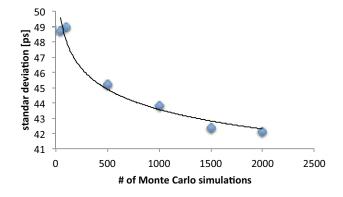

| 3.1  | The standard deviation of the delay of an inverter chain <i>vs</i> . the number of                                                                                                                   |    |

|      | Monte-Carlo simulations.                                                                                                                                                                             | 48 |

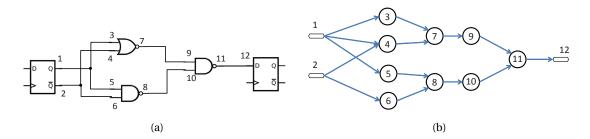

| 3.2 |                                                                                                           |      |

|-----|-----------------------------------------------------------------------------------------------------------|------|

|     | between two Flip-Flops and the corresponding timing graph, respectively. $\ldots$                         | 49   |

| 3.3 | i j                                                                                                       | 50   |

| 3.4 |                                                                                                           | 51   |

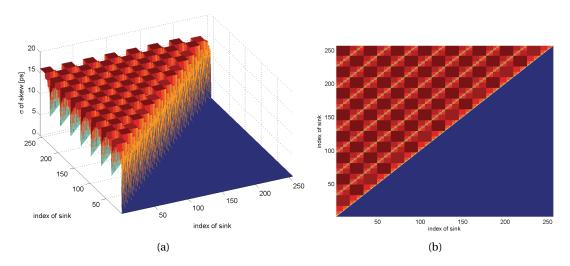

| 3.  | 5 The standard deviation of skew between each pair of clock sinks in a 2-D H-tree,                        |      |

|     | where (b) is the top-view of (a). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 52   |

| 3.  | 6 Modeling spatial correlations using quad-tree partitioning [37]                                         | 53   |

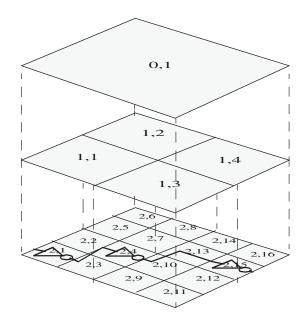

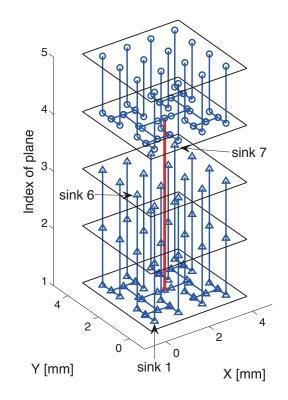

| 3.′ | 7 3-D H-trees spanning four planes, where (a) is the topology of a 3-D H-tree and                         |      |

|     | (b) is the 3-D view of a 3-D H-tree                                                                       | 55   |

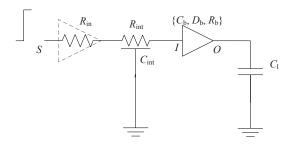

| 3.8 | An elemental circuit used to measure the variations in the buffer characteristics.                        | 56   |

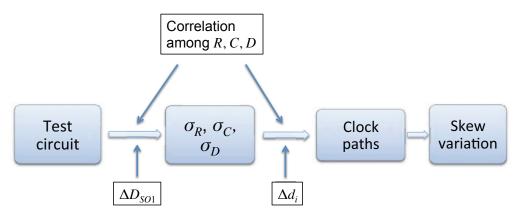

| 3.9 | 9 The flow to determine clock skew variation by using the parameters extracted                            |      |

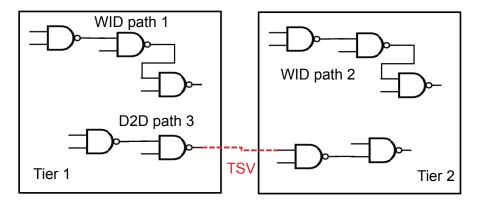

|     | from the test circuit.                                                                                    | 58   |

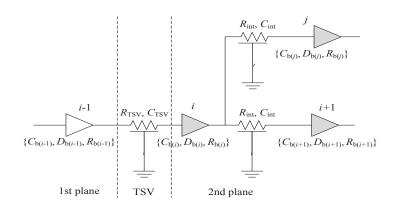

| 3.  | 10 The electrical model of a segment of a clock path                                                      | 59   |

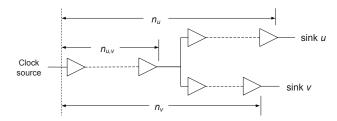

| 3.  | 11 The clock paths to sinks $u$ and $v$ where the paths share $n_{u,v}$ buffers                           | 63   |

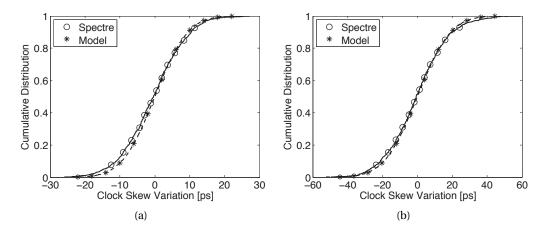

|     | 12 Comparison of skew variation between Spectre simulations and the analytic                              |      |

|     | skew model, where (a) and (b) are the CDFs of $\Delta s_{1,4}$ and $\Delta s_{1,5}$ , respectively.       | 65   |

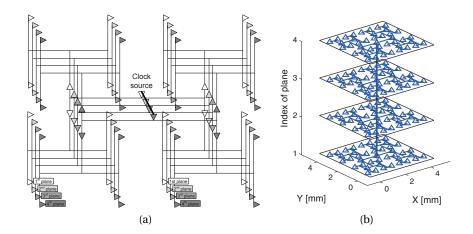

| 3.  | 13 A single-via 3-D clock H-tree, where 2-D view (a) and 3-D view (b) are illustrated                     | . 69 |

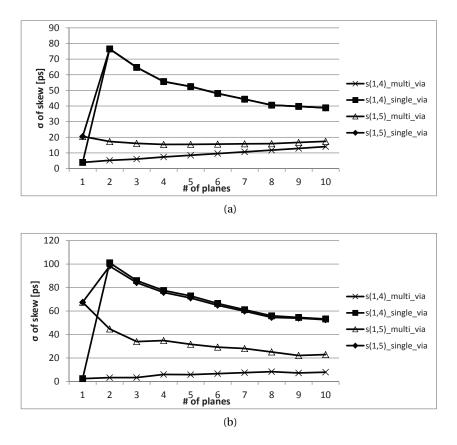

|     | 14 $\sigma$ of skew within the first plane for increasing number of planes, where the WID                 |      |

|     | variations are considered (a) independent and (b) multi-level correlated                                  | 70   |

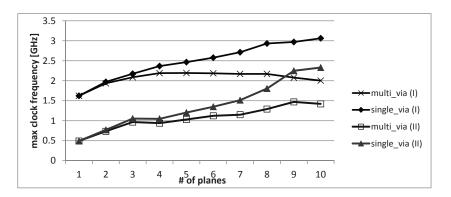

| 3.  | 15 The maximum supported clock frequency determined by the skew variation                                 |      |

|     | within one plane.                                                                                         | 72   |

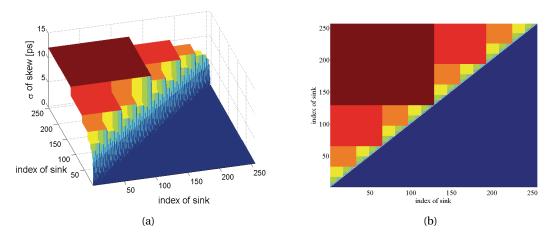

| 3.  | 16 The $\sigma$ of skew between each pair of clock sinks under the multi-via topology                     |      |

|     | where (a) is the 3-D view and (b) is the top view.                                                        | 72   |

| 3.  | 17 $\sigma$ of skew between the sinks in the first and the topmost plane for the single-via               |      |

|     | and multi-via topologies. The locations of the pairs of sinks defining $s_{1,4}$ and $s_{1,5}$            |      |

|     | are shown in Fig. 3.7(a). (a) is based on independent WID variations and (b) is                           |      |

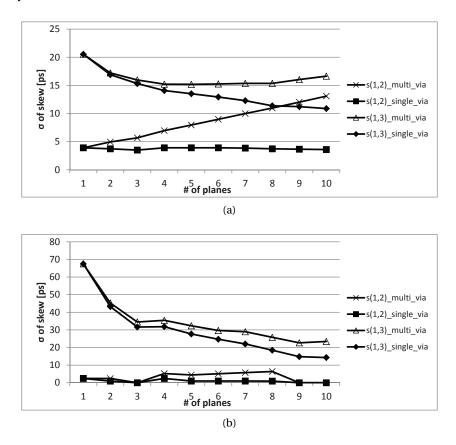

|     | based on multi-level correlated WID variations.                                                           | 73   |

| 3.  | 18 An example of the multi-group 3-D clock H-tree topology                                                | 76   |

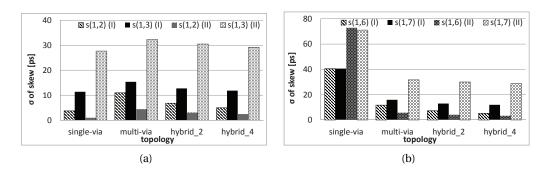

|     | 19 $\sigma$ of skew for three 3-D clock tree topologies. (a) Intra-plane skews $s_{1,2}$ and $s_{1,3}$ .  |      |

| 0.  | (b) Inter-plane skews $s_{1,6}$ and $s_{1,7}$ within a group of data-related planes                       | 77   |

| 3.3 | 20 An example of combining clock trees and grids, where (a) is the topology of a                          |      |

| 0.  | tree-grid structure [38] and (b) is the investigated global grid.                                         | 78   |

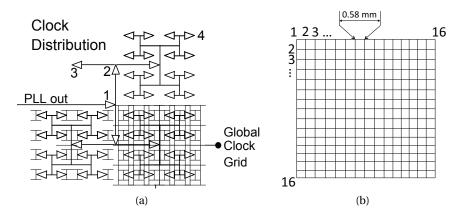

| 3   | 21 A four-plane 3-D IC with four clock domains. A PLL and an H-tree are used                              |      |

| 0.  | to generate and distribute, respectively, the clock signal within each domain                             |      |

|     | (plane). The clock sources are located at the center of each plane.                                       | 80   |

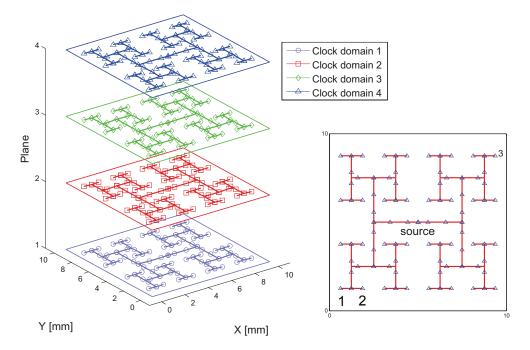

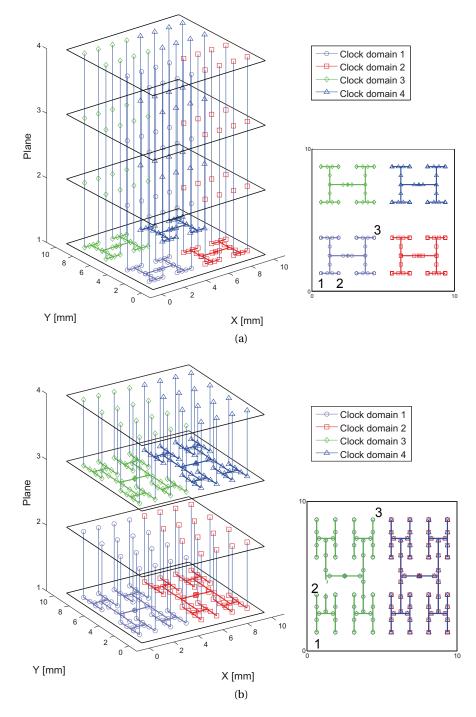

| 3   | 22 Different assignments of clock domains in a four-plane 3-D IC. (a) Four clock                          | 00   |

| 0.  | domains within each plane. (b) Two clock domains within each plane (a total of                            |      |

|     | four clock domains).                                                                                      | 81   |

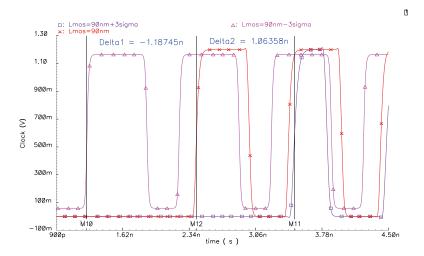

| 3   | 23 Waveform of the signal at $s_1$ with different gate lengths of MOSFET.                                 | 83   |

| 5.4 |                                                                                                           | 50   |

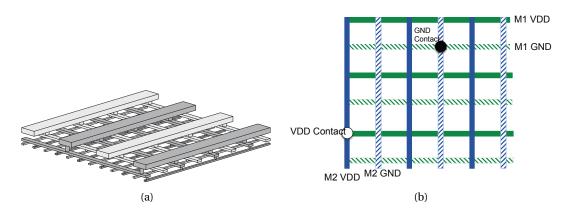

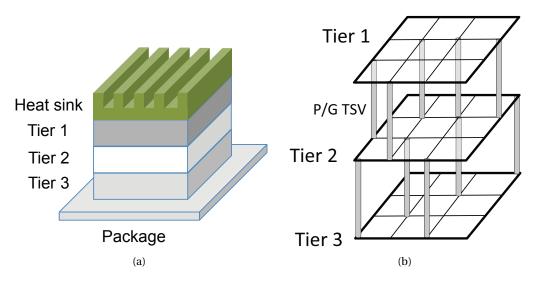

| 4.  | An example of a 3-D circuit where (a) is a schematic of a three-tier circuit and (b)                      |      |

|     | is the corresponding PDN.                                                                                 | 88   |

|     |                                                                                                           |      |

#### List of Figures

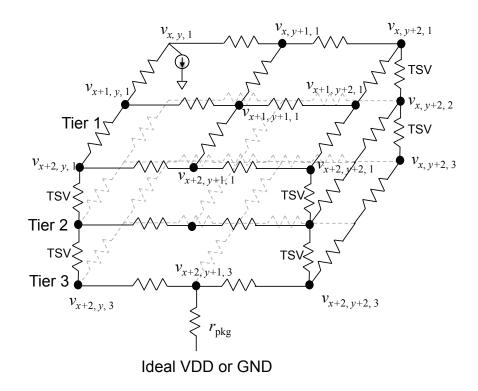

| 4.2  | A resistor network used to model a 3-D PDN for <i>IR</i> -drop analysis                              | 89  |

|------|------------------------------------------------------------------------------------------------------|-----|

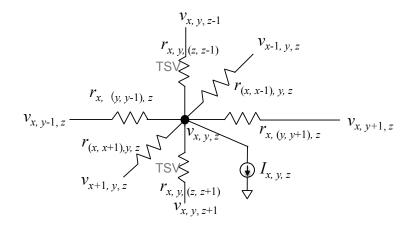

| 4.3  | A node of a power grid connected with four resistors in the same tier and two TSVs.                  | 90  |

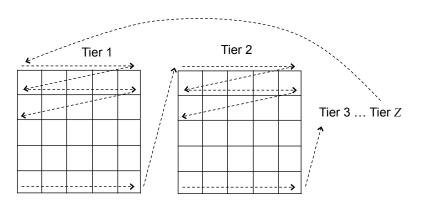

| 4.4  | The traversal direction of the row-based algorithm for a 3-D PDN with Z tiers.                       | 92  |

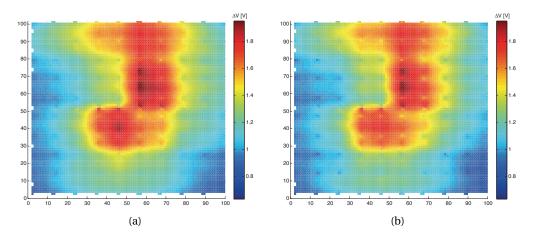

| 4.5  | <i>IR</i> -drop in a three-tier circuit based on ibmpg1, where (a) and (b) are the top-              |     |

|      | views of tiers 1 and 3 with 50 m $\Omega$ TSVs, respectively.                                        | 96  |

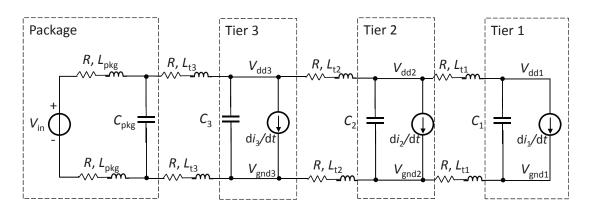

| 4.6  | A simplified circuit used to simulate the first-droop of the power supply noise.                     | 96  |

| 4.7  | Resonant noise in 3-D ICs due to different temporal separation of circuits switch-                   |     |

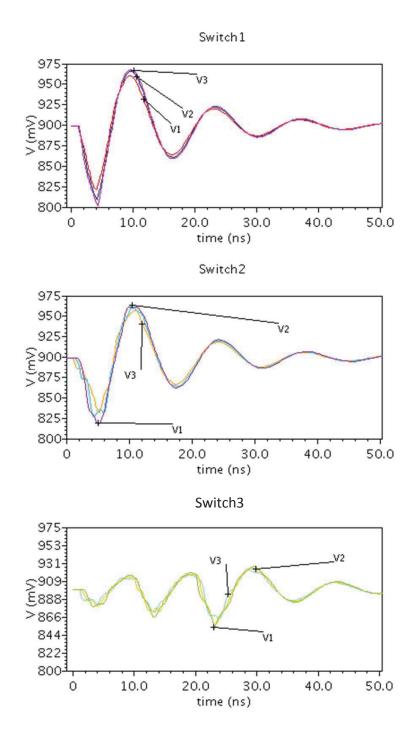

|      | ing within the three tiers.                                                                          | 98  |

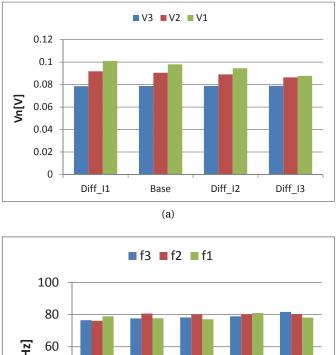

| 4.8  | Resonant noise vs. switching current in different tiers. The change of $V_{\rm n}$ and $f_{\rm n}$   |     |

|      | are illustrated in (a) and (b), respectively.                                                        | 99  |

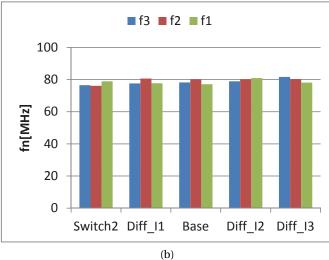

| 4.9  | Resonant noise <i>vs.</i> resistance of TSVs. The change of $V_n$ , <i>IR</i> -drop, and $f_n$ is    |     |

|      | illustrated in (a) to (c), respectively.                                                             | 100 |

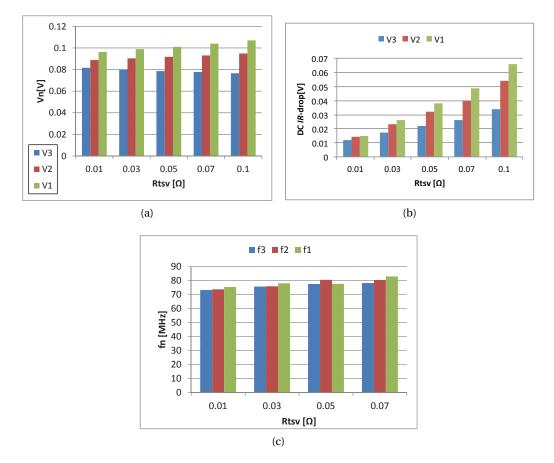

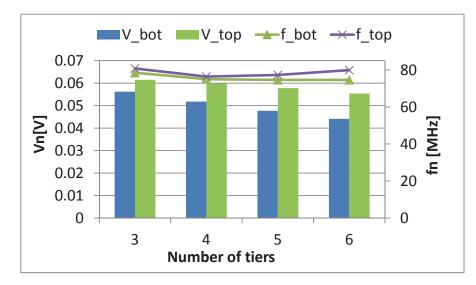

| 4.10 | Resonant noise <i>vs.</i> number of tiers. The changes in both $V_n$ and $f_n$ are depicted.         | 101 |

|      | A clock path affected by the first-droop supply noise, where (a) and (b) are the                     |     |

|      | clock path and path delay, respectively.                                                             | 102 |

| 4.12 | Different definitions of clock jitter.                                                               | 103 |

|      |                                                                                                      |     |

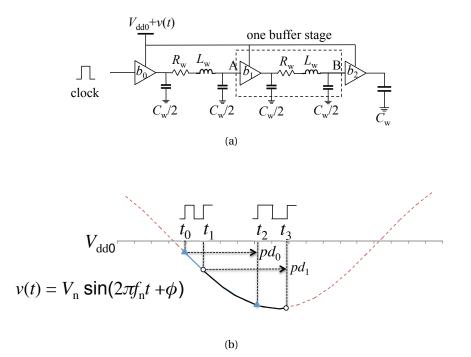

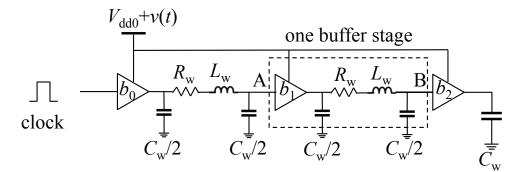

| 5.1  | A circuit used to measure the delay variation of one buffer stage due to process                     |     |

|      | variations and power supply noise                                                                    | 109 |

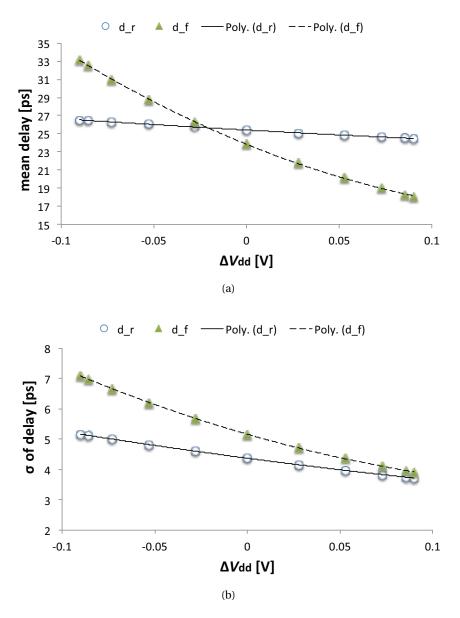

| 5.2  | The mean and standard deviation of the delay of a buffer stage                                       | 110 |

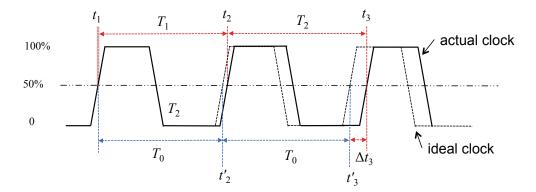

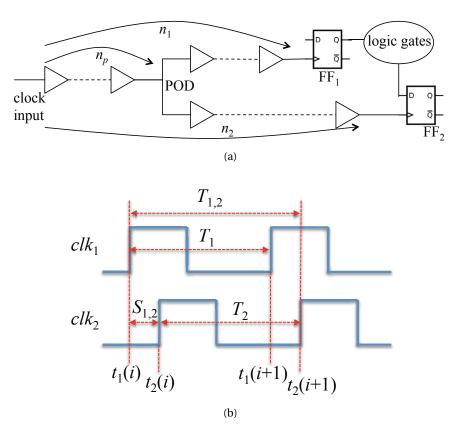

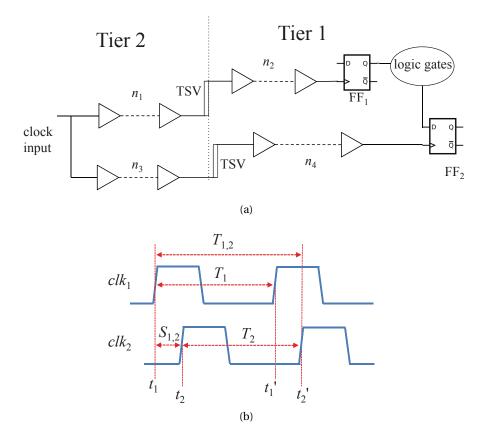

| 5.3  | Clock period jitter and skew between two clock paths. The clock paths and                            |     |

|      | FFs are illustrated in (a). The corresponding waveforms of the clock signal are                      |     |

|      | illustrated in (b)                                                                                   | 112 |

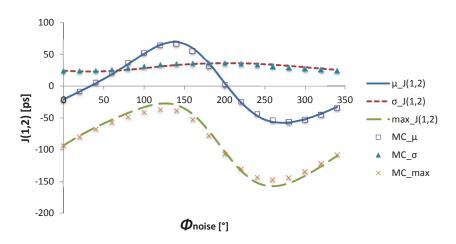

| 5.4  | $\mu_{J_{1,2}}$ and $\sigma_{J_{1,2}}$ from the proposed modeling method and Monte-Carlo simulations |     |

|      | (notated by "MC").                                                                                   | 115 |

| 5.5  | Mean slew rate for different buffer insertion under process variations and power                     |     |

|      | supply noise.                                                                                        | 116 |

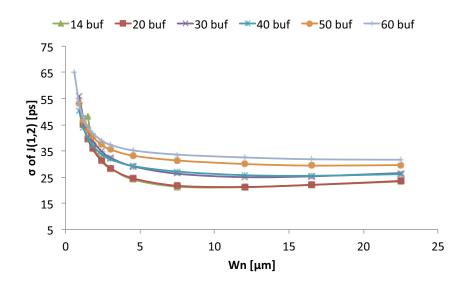

| 5.6  | $\sigma_{J_{1,2}}$ for different buffer insertion under process variations                           | 117 |

| 5.7  |                                                                                                      | 118 |

| 5.8  | $J_{1,2}$ for different buffer insertion under process variations and power supply                   |     |

|      | noise. (a) is the maximum $J_{1,2}$ . The max and min difference on $\sigma_{J_{1,2}}$ between PV    |     |

|      | only and PV&PSN is shown in (b).                                                                     | 119 |

| 5.9  | Skew and jitter with different length of clock paths.                                                | 120 |

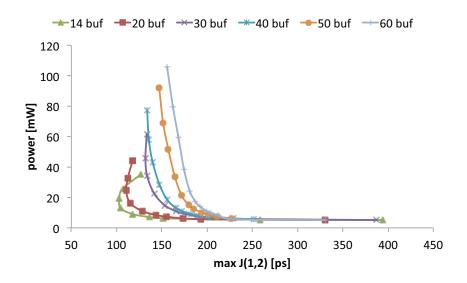

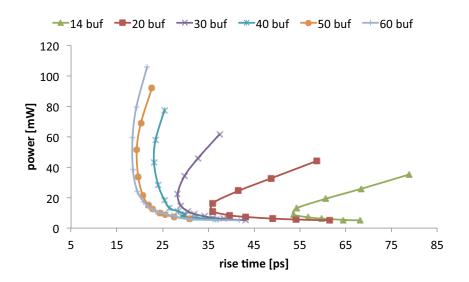

|      | Power consumption vs. $\max(J_{1,2})$ for different buffer insertions                                | 121 |

|      |                                                                                                      | 122 |

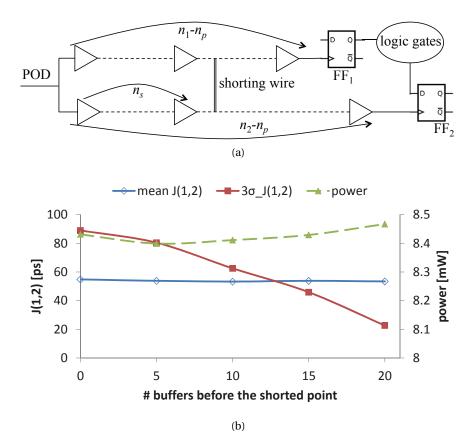

| 5.12 | Skitter and power with the shorted wire at different levels of clock paths. The                      |     |

|      | number of buffers before the shorted point is denoted by $n_s$                                       | 123 |

|      | Skitter between two branches vs. supply voltage.                                                     | 124 |

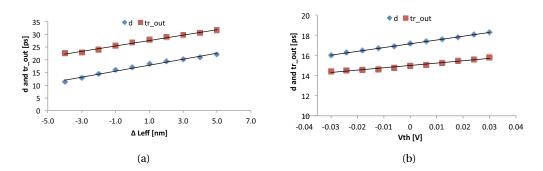

| 5.14 | Change of the delay and output transition time with (a) effective channel length                     |     |

|      | and (b) threshold voltage.                                                                           | 126 |

| 5.15 | Clock uncertainty between 3-D clock paths. Two paths and flip-flops are illus-                       |     |

|      | trated in (a). The corresponding clock signals are shown in (b)                                      | 128 |

#### List of Figures

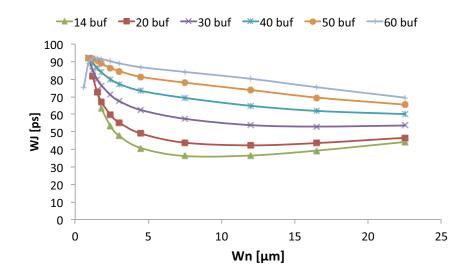

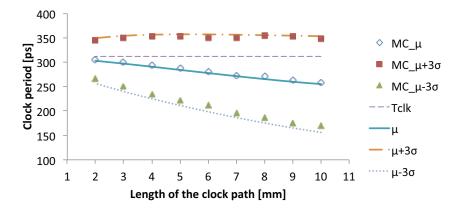

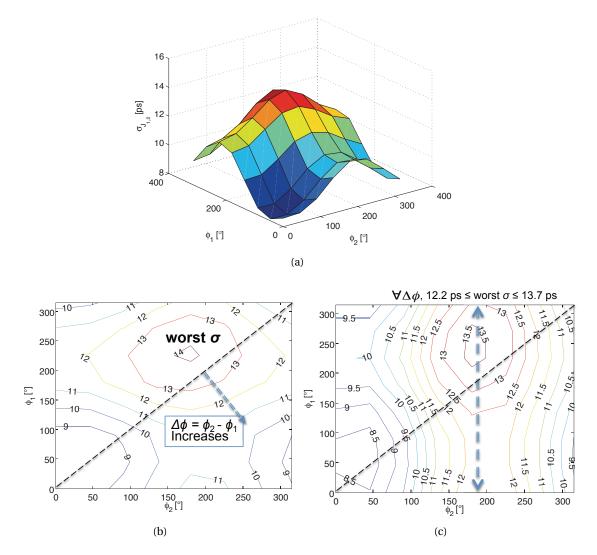

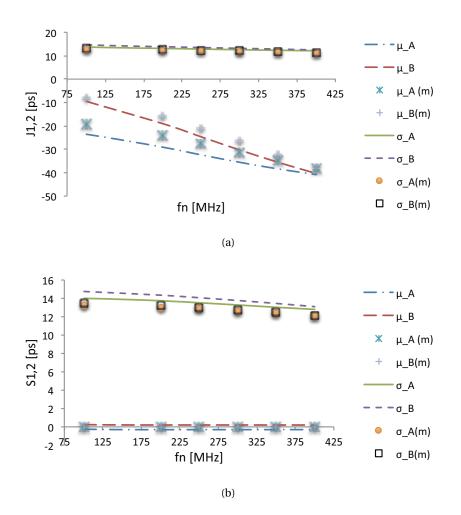

|      | Skitter <i>vs.</i> length of 3-D clock paths                                                                                                                                  | 132<br>133 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

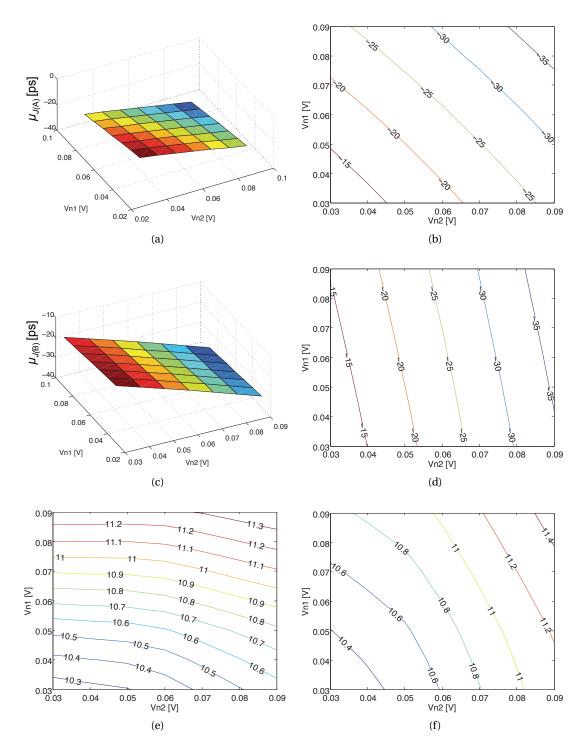

|      | Setup skitter <i>vs.</i> ( $V_{n2}$ , $V_{n1}$ ), where (a) and (b) are the 3-D plot and contour for                                                                          | 155        |

|      | $\mu_{J_{\rm A}}$ for distribution (A), respectively. (c) and (d) are the 3-D plot and contour for                                                                            |            |

|      | $\mu_{J_{\rm B}}$ for distribution (B), respectively. (e) and (f) are the contours of $\sigma_{J_{\rm A}}$ and $\sigma_{J_{\rm B}}$ ,                                         |            |

| - 10 | respectively.                                                                                                                                                                 | 134        |

| 5.19 | Hold skitter <i>vs.</i> ( $V_{n2}$ , $V_{n1}$ ), where (a) and (b) are the contours for $\sigma_{S_A}$ and $\sigma_{S_B}$ ,                                                   | 105        |

| F 20 | respectively                                                                                                                                                                  | 135        |

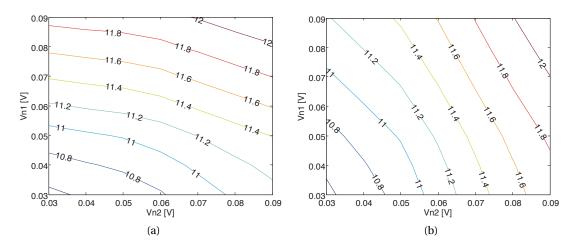

| 5.20 | Skitter <i>vs.</i> different $\phi$ ( $\phi_1 = \phi_2$ ), where (a) is the change of $\mu_{J_{1,2}}$ . (b) and (c) are the change of $\sigma_2$ and $\sigma_2$ respectively. | 136        |

| 5 21 | the change of $\sigma_{J_{1,2}}$ and $\sigma_{S_{1,2}}$ , respectively                                                                                                        | 130        |

| J.21 | map of $\sigma_{J_{1,2}}$ vs. ( $\phi_2$ , $\phi_1$ ) for distribution (A), respectively. (c) is the contour map                                                              |            |

|      | of $\sigma_{J_{1,2}}$ for distribution (B)                                                                                                                                    | 138        |

| 5 22 | Skitter <i>vs.</i> $f_n$ . The change of $J_{1,2}$ and $S_{1,2}$ are illustrated in (a) and (b), respectively                                                                 |            |

|      | The effect of the change of $f_n$ on delay variation, where (a) is the mean and                                                                                               |            |

|      | standard deviation of buffer delay vs. $V_{dd}$ . (b) is the supply voltage to a clock                                                                                        |            |

|      | path during the propagation of a clock edge.                                                                                                                                  | 140        |

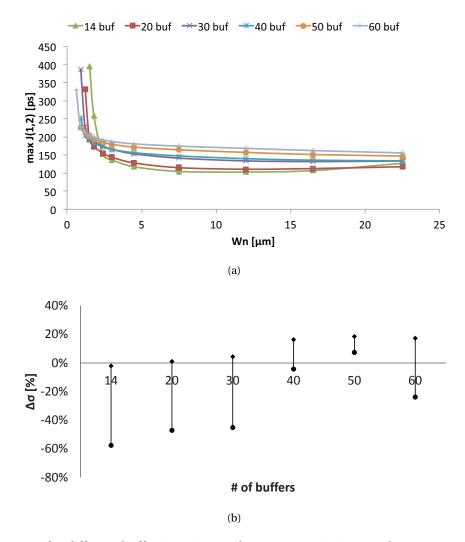

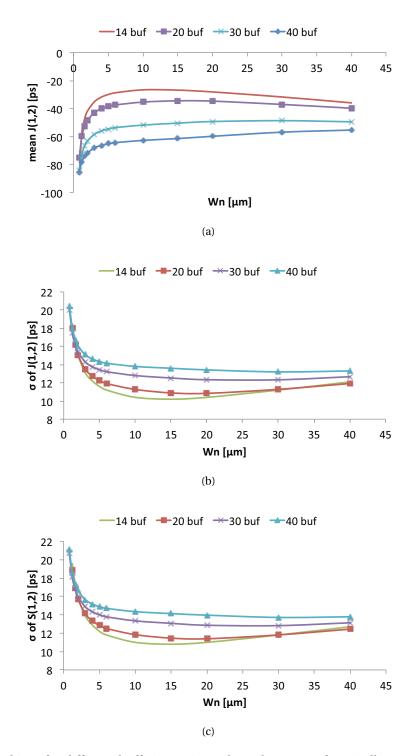

| 5.24 | Skitter for different buffer insertion, where the mean of $J_{1,2}$ is illustrated in (a)                                                                                     |            |

|      | and $\sigma_{J_{1,2}}$ and $\sigma_{S_{1,2}}$ are shown in (b) and (c), respectively.                                                                                         | 142        |

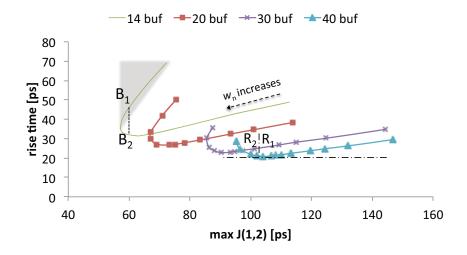

| 5.25 | Transition time <i>vs.</i> $\max(J_{1,2})$ for different buffer insertion                                                                                                     | 143        |

| 5.26 | Tradeoff between power and timing. Power <i>vs.</i> $max(J_{1,2})$ and $max(S_{1,2})$ are                                                                                     |            |

|      | illustrated in (a) and (b), respectively.                                                                                                                                     | 144        |

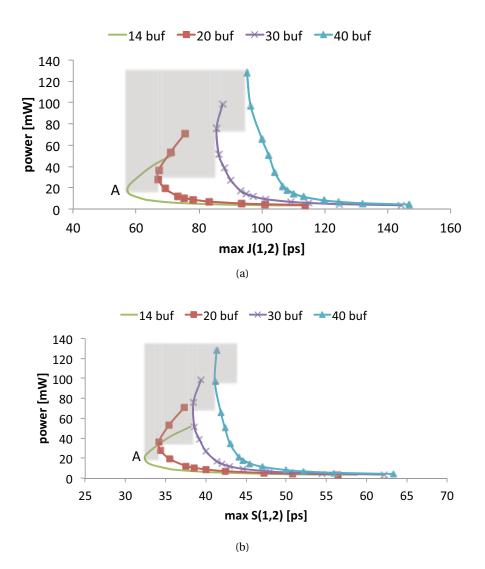

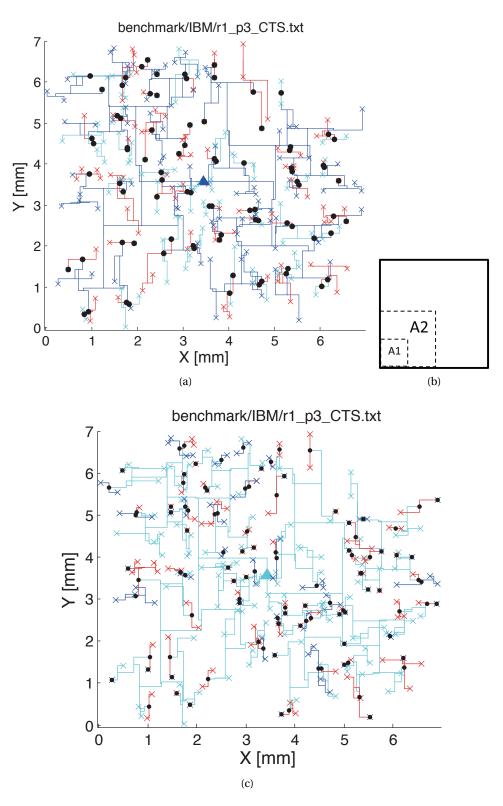

| 5.27 | An example of merging two nodes in 3D-DME algorithm, where (a) and (b) are                                                                                                    |            |

|      | the top and 3-D views of a 3-D circuit, respectively.                                                                                                                         | 146        |

| 5.28 | A synthesized 3-D clock tree with the majority of clock buffers in the first (a) and                                                                                          |            |

|      | third tier (c). The regions where the skitter is measured are illustrated in (b)                                                                                              | 148        |

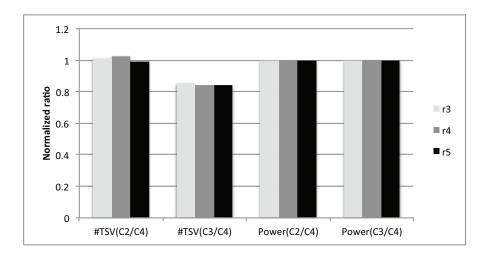

|      | Normalized number of TSVs and power for Cases 2 to 4                                                                                                                          | 152        |

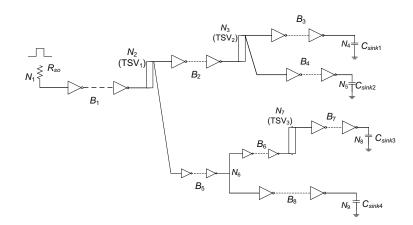

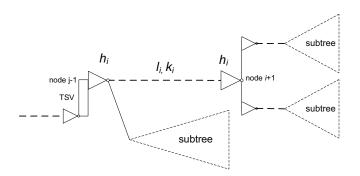

|      | A 3-D interconnect tree with buffers.                                                                                                                                         | 153        |

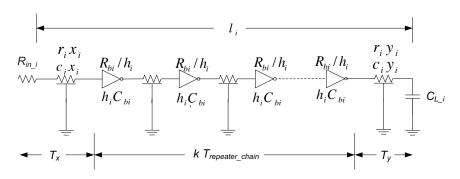

|      | The electrical model of a 2-D net with buffers.                                                                                                                               | 154        |

| 5.32 | A minimum size buffer exactly before the starting node is assumed. $C_{L_i}$ is                                                                                               |            |

| - 00 | determined by (5.41).                                                                                                                                                         | 157        |

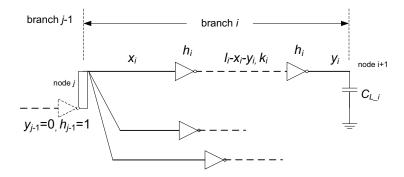

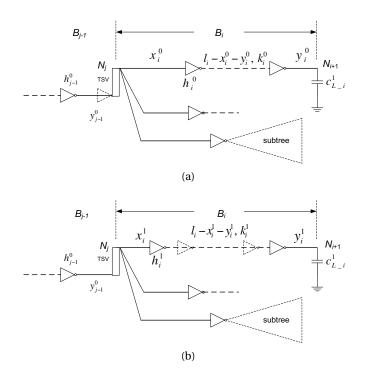

| 5.33 | Iterative procedure to insert buffers along a branch $B_i$ . (a) An initial solution for branch $B_i$ and (b) reference of the colution                                       | 150        |

| E 94 | branch $B_i$ and (b) refinement of the solution                                                                                                                               | 159        |

| 5.54 | Application of a conventional burlet insertion method [59], [40] in a 5-D free.                                                                                               | 160        |

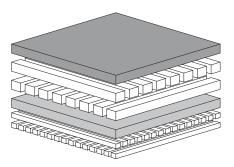

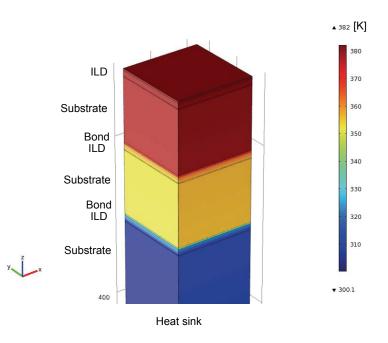

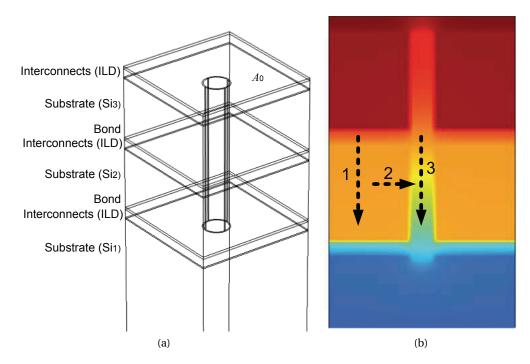

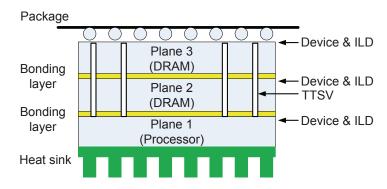

| 6.1  | A typical 3-D circuit with different layers.                                                                                                                                  | 166        |

| 6.2  | The maximum temperature of a 3-D circuit <i>vs</i> . the number of tiers                                                                                                      | 167        |

| 6.3  | A segment of a three-plane 3-D IC with a TTSV, where (a) is the geometric                                                                                                     |            |

|      | structure and (b) is the cross section. The footprint area of the circuit is denoted                                                                                          |            |

| ~    | by $A_0$ . Three paths of heat transfer are depicted with the dashed lines                                                                                                    | 168        |

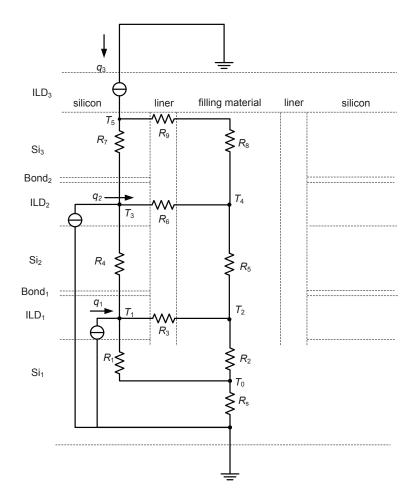

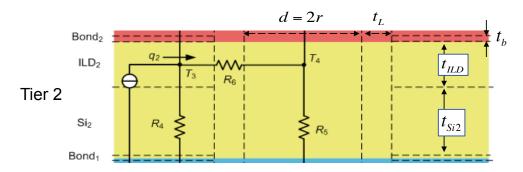

| 6.4  | Thermal model of a TTSV in a three-plane circuit (Model A).                                                                                                                   | 170        |

| 6.5  | Geometric parameters related to TTSVs in the second tier                                                                                                                      | 171        |

| 6.6  | Distributed thermal model of a TTSV in the second plane (Model B)                                                                                                          | 172 |

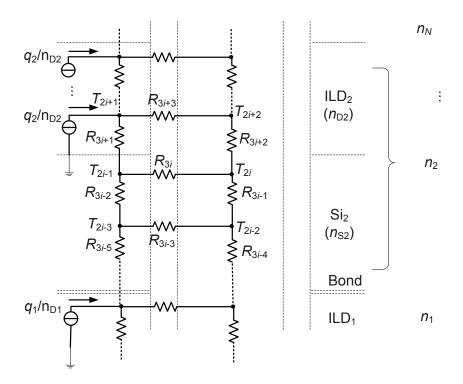

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

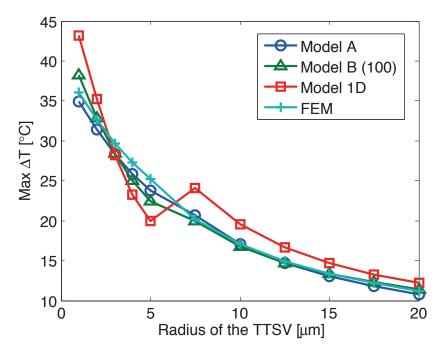

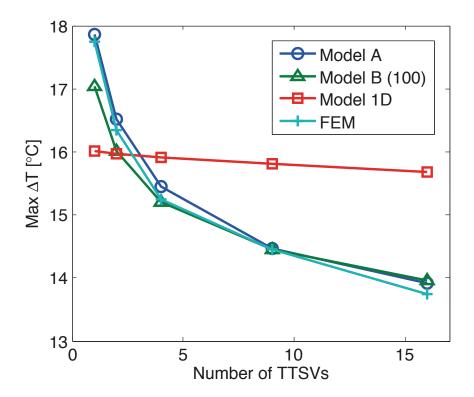

| 6.7  | Maximum temperature rise in a three-plane 3-D IC due to different TTSV radius.                                                                                             |     |

|      | $t_{\rm L} = 0.5\mu{\rm m}, t_{\rm D} = 4\mu{\rm m}, t_{\rm b} = 1\mu{\rm m}.$ For $1\mu{\rm m} \le r \le 5\mu{\rm m}, t_{{\rm Si}_2} = t_{{\rm Si}_3} = 5\mu{\rm m};$ for |     |

|      | $5\mu\text{m} < r \le 20\mu\text{m}, t_{\text{Si}_2} = t_{\text{Si}_3} = 45\mu\text{m}. k_1 = 1.3$ , and $k_2 = 0.55. \dots \dots \dots \dots$                             | 174 |

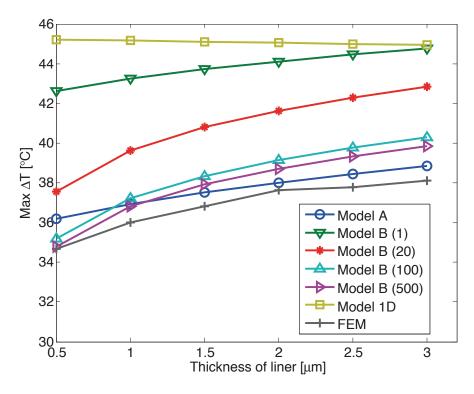

| 6.8  | Maximum temperature rise in a three-plane 3-D IC for different thickness of the                                                                                            |     |

|      | dielectric liner, where $r = 5 \mu$ m. The other parameters are $t_D = 7 \mu$ m. $t_b = 1 \mu$ m,                                                                          |     |

|      | $t_{\text{Si}_2} = t_{\text{Si}_3} = 45 \mu\text{m}.\ k_1 = 1.3 \text{ and } k_2 = 0.55.$                                                                                  | 175 |

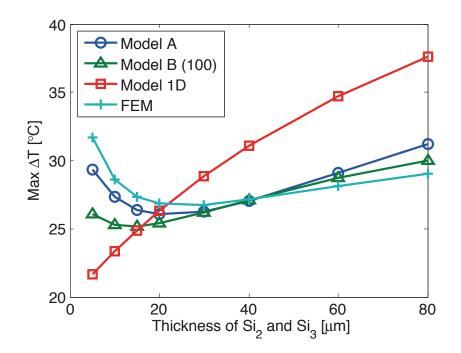

| 6.9  | Maximum temperature rise in a three-plane 3-D IC due to different thickness of                                                                                             |     |

|      | the silicon substrate. The other parameters are $t_{\rm L} = 1 \mu\text{m}$ , $t_{\rm D} = 7 \mu\text{m}$ , $t_{\rm b} = 1 \mu\text{m}$ ,                                  |     |

|      | $r = 8 \mu\text{m}, k_1 = 1.3 \text{ and } k_2 = 0.55$                                                                                                                     | 177 |

| 6.10 | Dividing a large TSV into four, nine, and 16 smaller TSVs                                                                                                                  | 177 |

| 6.11 | Maximum temperature rise in a three-plane 3-D IC due to different thickness                                                                                                |     |

|      | of the silicon substrate. $t_L = 1 \mu m$ , $t_D = 4 \mu m$ , $t_b = 1 \mu m$ , $t_{Si_2} = t_{Si_3} = 20 \mu m$ , $r_0 =$                                                 |     |

|      | $10 \mu\text{m},  k_1 = 1.3,  \text{and}  k_2 = 0.55. \dots \dots$         | 178 |

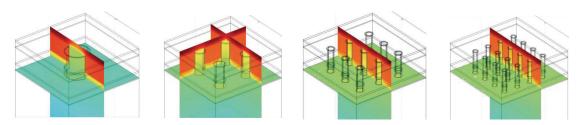

| 6.12 | A three-plane 3-D circuit with TTSVs. $t_{\rm L} = 1 \mu\text{m}, t_{\rm D} = 20 \mu\text{m}, t_{\rm b} = 10 \mu\text{m}, t_{\rm Si_1} =$                                  |     |

|      | $t_{\text{Si}_2} = t_{\text{Si}_3} = 300 \mu\text{m}, r = 30 \mu\text{m}, k_1 = 1.6, k_2 = 0.8, \text{ and } c_{1,2} = 3.5.$                                               | 179 |

## List of Tables

| 1.1  | Dimensions and resistances of TSVs from different technologies [7]                                       | 13  |

|------|----------------------------------------------------------------------------------------------------------|-----|

| 1.2  | Electrical characteristics of different TSVs.                                                            | 14  |

| 1.3  | Electrical characteristics of horizontal global interconnects [41].                                      | 14  |

| 3.1  | Device and Interconnect Parameters of the Investigated Circuit.                                          | 64  |

| 3.2  | Variations of the Electrical Characteristics of the Buffers                                              | 64  |

| 3.3  | $\sigma$ of Skew Variation of the 3-D Circuits Shown in Figs. 3.7 and 3.13                               | 65  |

| 3.4  | Parameters of Horizontal Interconnects.                                                                  | 67  |

| 3.5  | Skew Variation of the 3-D Circuits Considering Wire Variations                                           | 67  |

| 3.6  | The Number of Buffers Inserted into the 3-D Clock Trees.                                                 | 71  |

| 3.7  | The Maximum Clock Frequency Supported by Multi-Via and Single-Via Topologies.                            | 74  |

| 3.8  | $\sigma_{s_{1,7}}$ and Computational Time of three 3-D Clock Tree Topologies. $\ldots$ $\ldots$ $\ldots$ | 77  |

| 3.9  | Monte-Carlo Results of Different Clock Distribution Networks                                             | 79  |

| 3.10 | Electrical Characteristics of the Investigated Circuits.                                                 | 82  |

| 3.11 | Skew Variation Analysis of an Eight-Plane 3-D IC with Eight Clock Domains                                | 83  |

| 3.12 | Statistics of the Eight-Plane 3-D IC with Eight Clock Domains.                                           | 83  |

| 4.1  | IBM power grid benchmarks for IR-drop analysis                                                           | 94  |

| 4.2  | Simulation results for 2-D and 3-D power grids based on IBM benchmarks                                   | 95  |

| 4.3  | Electrical Characteristics of the Simplified Circuit.                                                    | 97  |

| 5.1  | Different Buffer Insertion Strategies for an Interconnect.                                               | 114 |

| 5.2  | Comparison between the Proposed Modeling Method and Monte-Carlo Simula-                                  |     |

|      | tions                                                                                                    | 115 |

| 5.3  | Comparison between the proposed modeling method and Monte-Carlo simula-                                  |     |

|      | tions for different numbers of buffers.                                                                  | 118 |

| 5.4  | Variations of Devices, Horizontal Wires, and TSVs                                                        | 131 |

| 5.5  | Effect of TSV Variations on Skitter                                                                      | 132 |

| 5.6  | 3-D ICs Based on IBM Clock Benchmarks                                                                    | 147 |

| 5.7  | Skitter in 3-D ICs Generated from the IBM Clock Distribution Network Benchmarks                          | 150 |

| 5.8  | Delay of 3-D interconnect trees after buffers are inserted.                                              | 161 |

| 5.9  | The improvement in total delay vs. number of iterations.                                                 | 162 |

| 5.10 | The improvement in delay and area under diverse area constraints                                         | 162 |

| 6.1 | The thermal conductivity of different materials used in 3-D ICs | 166 |

|-----|-----------------------------------------------------------------|-----|

| 6.2 | The Error and Run Time vs. # of Segments in Model B.            | 176 |

## **1** Introduction

*Three-dimensional* (3-D) integration emerges as a promising system integration approach to increase the density of devices, to shorten the interconnects of circuits, and, thus, to enhance the performance of circuits. Since multiple circuits are vertically stacked to form a 3-D system, the combined variations of these circuits significantly differ from traditional 2-D circuits. In addition, synchronizing devices across tiers becomes challenging. The modeling methods for different sources of variations and the design techniques to increase robustness in 3-D ICs, in particular 3-D clock distribution networks, are the focus of this dissertation.

The fundamentals of 3-D IC design and fabrication are introduced in the following section. The classification and manufacturing technologies of 3-D ICs are introduced in Sections 1.2 and 1.3, respectively. Clock distribution topologies for 3-D circuits are introduced in Section 1.4, where the synchronization approaches of digital circuits are discussed. The contributions of this dissertation are presented in Section 1.5. The assumptions and limitations of this work are summarized in Section 1.6. The organization of this thesis is listed in the last section.

#### 1.1 Background of 3-D ICs

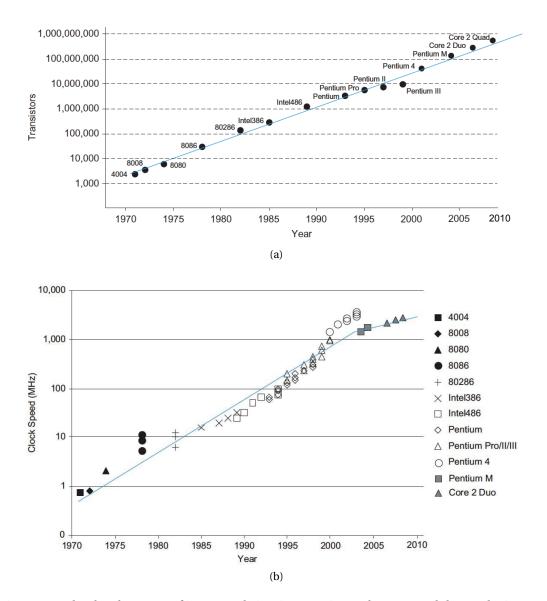

During the last decades, integrated circuits have experienced a tremendous increase in density, functionality, and speed. One of the most important driving forces for this continuous growth is the persistent downscaling of the size of transistors. The rapid development of electronic devices originated from 1947, where the first transistor was fabricated by J. Bardeen, W. Brattain, and W. Shockley [42]. After this first transistor with a size of over 10 cm, the size of transistors has fast scaled down to 22 nm for massive production in 2012 [43]. When the first integrated circuit was invented in 1958 by Jack Kilby [2], only two transistors were integrated within this circuit. In 2012, however, Intel Core i7-990X processor contains more than one billion transistors integrated within one chip [1]. The number of transistors within one circuit, the speed of circuit, and the functionality of integrated circuits all increase dramatically as technology scales , as illustrated in Fig. 1.1 [1,2].

Figure 1.1: The development of integrated circuits over time, where (a) and (b) are the increase in the number of transistors and the clock frequency of Intel processors, respectively [1,2].

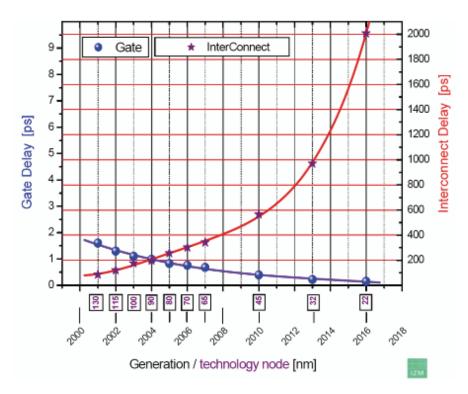

Nevertheless, as the feature size of transistors becomes smaller than 20 nm, traditional planar ICs have encountered new challenges. First, due to the limitation of manufacturing technologies and materials, it is extremely difficult and expensive to continue the scaling of feature size [44]. Second, the interconnect delay becomes dominant over the gate delay due to the increase in the interconnect length and *RC* delay, as depicted in Fig. 1.2 [3]. This increase is mainly due to the increase in the footprint size of circuits and the decrease in the width, space, and height of wires. Therefore, it is challenging for 2-D ICs to further enhance the density and speed of circuits simply by scaling. Consequently, new technologies are required to provide higher density, higher performance, and more functionalities for integrated systems.

Figure 1.2: The increase in interconnect delay with technology generations [3].

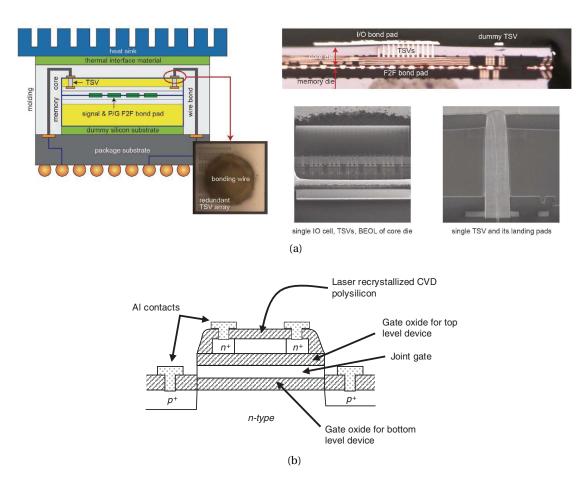

Three-dimensional integration provides a promising solution to continue improving the performance of integrated circuits. In 3-D ICs, vertical integration can be implemented at different levels. For instance, multiple chips/dies can be fabricated separately and then vertically stacked together. Each chip forms a plane or tier of the final circuit. An example of this type of 3-D circuits is illustrated in Fig. 1.3(a) [4], where a processor layer is stacked on top of a memory layer. At lower levels, devices (transistors) can be stacked together to provide higher density. For instance, the first vertically-stacked device was fabricated in early 1980s as illustrated in Fig. 1.3(b) [5]. By utilizing vertical integration, 3-D ICs exhibit three major advantages over traditional planar circuits: higher density, shorter interconnects, and easier heterogeneous integration.

Figure 1.3: Different levels of 3-D integration, where (a) is the cross-section of a 3-D circuit consisting of two dies [4] and (b) is a vertically stacked inverter [5].

#### **Higher density**

By vertically stacking devices or entire circuits, a larger number of transistors can be integrated with the same area as compared to a planar IC. Assuming that *n* dies with a similar number of transistors are vertically stacked in a 3-D circuit, the resulting density is *n* times that of the corresponding 2-D circuit. Consequently, the density of circuits can significantly be increased by 3-D integration. For instance, a 3-D DRAM fabricated by Samsung has achieved a capacity of 8 GB with a 50% increase in density [45, 46].

#### Shorter interconnects

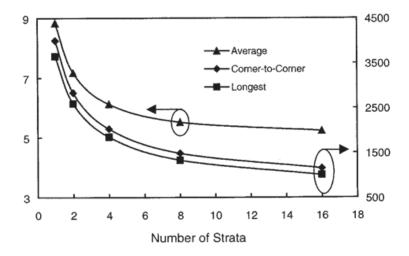

For the same number of transistors, 3-D ICs exhibit a smaller footprint than 2-D circuits due to the higher density. In addition, vertical interconnects are used in 3-D circuits. Consequently, the on-chip interconnect length can be greatly reduced. The decrease in the length of interconnects with the number of tiers is plotted in Fig. 1.4. As shown in this figure, the

Figure 1.4: Lengths of the longest and average interconnects vs. the number of tiers [6].

interconnect length decreases significantly as multiple circuits are vertically stacked. This reduction in interconnect length, consequently, decreases the interconnect delay. As shown in Fig. 1.2, since the interconnect delay dominates the overall delay of a circuit, decreasing the interconnect delay helps to enhance the speed of circuits.

#### Heterogeneous integration

There are currently three main application domains of 3-D ICs: memory stack, memoryon-microprocessor, and analog/digital mixed-signal circuits. A memory stack is a homogeneous 3-D circuit consisting of multiple memory dies [45]. Nevertheless, memory-onmicroprocessor [4] and analog/digital mixed-signal 3-D ICs are heterogeneous 3-D circuits. Heterogeneous integration, where different types of circuit blocks are integrated within one circuit, provides multiple functionalities within one system [47, 48]. In 2-D ICs, these different circuits have to be fabricated with the same technology. In 3-D ICs, however, these circuits can be located in different tiers and fabricated with different technologies. This feature greatly eases heterogeneous integration. Consequently, DRAM and processors can be fabricated separately with different technologies and stacked together [4]. Analog sensors and digital process units can also be designed and fabricated separately and then integrated into one 3-D circuit [48].

Several challenging issues of heterogeneous integration can be mitigated with 3-D ICs. For instance, analog and digital circuits can coexist in heterogeneous circuits. In 2-D ICs, since the same silicon substrate is shared by the entire circuit, substrate crosstalk can introduce large noise during the operation of these circuits. 3-D ICs, consequently, provides a novel way to mitigate this noise. As illustrated in Fig. 1.5 [7], the digital and analog parts of a 3-D circuit can be located in different tiers manufactured on different substrates. The substrate crosstalk,

therefore, can significantly be mitigated. In addition, due to the higher density, heterogeneous 3-D ICs provide several functions with a smaller footprint as compared to 2-D systems.

Figure 1.5: An example of a heterogeneous 3-D circuit containing both digital and analog circuitries [7].

Due to the significant advantages of 3-D ICs over conventional 2-D ICs, a strong research effort has been put in both academia and industry [7,49]. Currently, different types of 3-D circuits have been proposed and fabricated. The classification of 3-D systems is introduced in the following section.

#### 1.2 Classification of 3-D Circuits

Different types of 3-D integrated systems are introduced in this section. As previously mentioned, vertical integration can be implemented at different levels. Based on the integration level and the interconnection technologies among tiers, 3-D systems can roughly be classified into three primary categories: *System-in-Package* (SiP), *System-on-Package* (SoP), and fine-grain 3-D ICs [7].

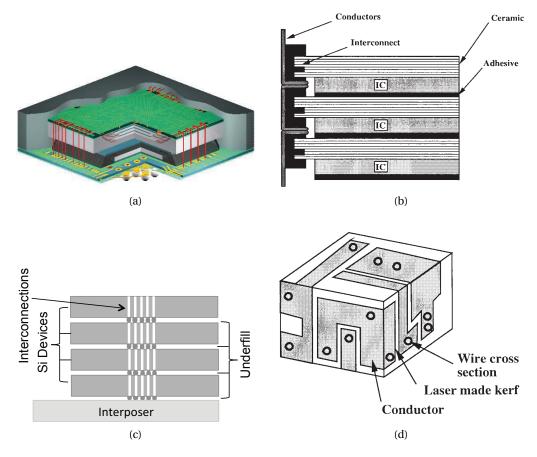

#### 1.2.1 System-in-Package

An SiP is a system assembling either bare or packaged dies along the vertical direction. The individual dies of an SiP are separately designed. Interconnections among dies are primarily implemented with four methods [7]:

Figure 1.6: System-in-Packages implemented with different methods: (a) wire bonding [8], (b) interconnects on the periphery of dies [9], (c) vertical interconnect array [10], and (d) interconnects on the faces of a 3-D stack [9].

- Wire bonding, as shown in Fig. 1.6(a)

- Vertical interconnects on the periphery of dies/packages, as illustrated in Fig. 1.6(b)

- Low aspect ratio (length over diameter) and low density vertical interconnects arranged in an array, as depicted in Fig. 1.6(c)

- Metallization on the faces of a 3-D stack, as illustrated in Fig. 1.6(d)

Due to the ease of design and fabrication, wire bonding is the most common inter-die communication mechanism used in SiPs [7]. SiPs significantly enhance the packaging efficiency and reduce the form factor. The dies within an SiP are integrated at the die or package level, where only coarse-grain interconnections can be achieved among the circuitries in different tiers. As shown in Fig. 1.6, due to the limited locations and low density of vertical interconnects, the advantage of 3-D integration to support shorter interconnects cannot be fully utilized in 3-D SiPs.

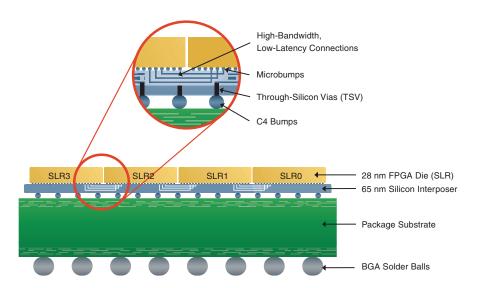

#### 1.2.2 System-on-Package

In SiPs, inter-die communication can only be implemented at specific locations. To facilitate the communication among dies, System-on-Packages have been proposed [50]. As illustrated in Fig. 1.7, a silicon interposer is used to host all the dies. Metal wires can be used in this interposer to interconnect different dies. TSVs are used to connect all the chips through the interposer with the package. SoPs are also referred as 2.5-D ICs, since multiple dies are located on a planar interposer. In 2.5-D SoPs, all the chips can be designed similar to conventional 2-D circuits. These chips are flipped down and bonded to the interposer. Consequently, 2.5-D SoPs are easier to design and fabricate as compared with fine-grain 3-D ICs. Industrial products of 2.5-D FPGAs have recently been released by Xilinx Inc. [11].

Figure 1.7: Xilinx Virtex-7 FPGA based on 2.5-D System-on-Package [11].

#### 1.2.3 Fine-grain 3-D ICs

To further decrease the interconnect length and delay, fine-grain 3-D ICs have been proposed. In general, fine-grain 3-D ICs refer to the circuits where the devices, gates, and circuit blocks can be vertically distributed among physical planes [51]. The interconnection among planes can be implemented (*e.g.*, by TSVs) at any "legal" location. To avoid confusion, the term "3-D IC" refers to fine-grain 3-D ICs in the remainder of this dissertation. Differently from the package-level integration in SiPs, 3-D ICs are integrated at lower levels. Depending on the fabrication process, 3-D ICs are classified into two main categories: monolithic and polylithic 3-D circuits [7].

#### **Monolithic 3-D ICs**

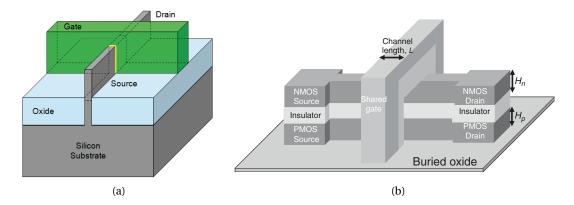

Monolithic 3-D ICs are fabricated in a batch process. Different planes of a monolithic 3-D circuit are successively fabricated. The devices in the upper planes are grown above the lower planes. Monolithic 3-D ICs can be further divided into two types: stacked 3-D ICs and 3-D *fin field effect transistors* (fin-FETs).

- In stacked monolithic 3-D ICs, multiple layers of planar transistors are successively grown on top of conventional CMOS or *Silicon-on-Insulator* (SOI) planes. As illustrated in Fig. 1.3(b), the transistor-level integration is achieved by stacking conventional transistors [52].

- A fin-FET is a nonplanar and multi-gate transistor built on an SOI substrate [53]. The conducting channel is surrounded by a silicon fin. Fin-FET-like transistors are successfully utilized in industrial products, *e.g.*, Intel Tri-Gate transistors [12] as illustrated in Fig. 1.8(a). The advantages of fin-FETs include the high driving current and the significant reduction in both the gate area and routing within one gate. 3-D fin-FETs are a novel transistor structure based on conventional fin-FETs. In 3-D fin-FETs, devices stacked together share the same gate [13, 54], as illustrated in Fig. 1.8(b). The density of devices is further increased as compared with conventional fin-FETs.

Figure 1.8: Different types of fin-FETs, where (a) and (b) are an Intel Tri-Gate [12] and a 3-D fin-FET [13], respectively.

#### **Polylithic 3-D ICs**

In polylithic 3-D ICs, different planes of a circuit are separately fabricated and then bonded together. In contrast to SiPs, in polylithic 3-D ICs, vertical interconnections are not limited to the periphery or in a fixed area array arrangement. These interconnections can be implemented in all possible locations (not occupied by transistors) by *Through Silicon Vias* (TSVs) [55], inductive coupling [56], or capacitive coupling [57], as illustrated in Fig. 1.9.

Figure 1.9: Communication mechanisms in different fine-grain 3-D ICs [7]: (a) TSVs, (b) inductive coupling, and (c) capacitive coupling.

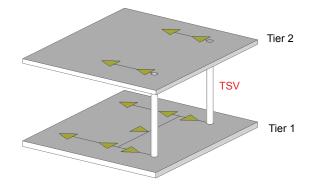

Wafer or die-level 3-D integration utilizing TSVs is the most attractive solution for fine-grain 3-D ICs [7,55]. First, TSVs can be inserted at any available location where vertical interconnection is required, fully exploiting the advantage of 3-D ICs in reducing interconnect length and delay. Second, different tiers of TSV-based 3-D ICs are separately fabricated, which shortens the manufacturing time as compared to monolithic 3-D ICs and allows integration of different technologies in different tiers. Consequently, TSV-based 3-D ICs are investigated in this dissertation. In the following context, 3-D ICs directly imply 3-D circuits using TSVs to communicate among tiers.

#### 1.3 Manufacturing Technologies for 3-D ICs

Manufacturing technologies and processes for 3-D ICs are introduced in this section. Different fabrication processes of TSVs are introduced in Section 1.3.1. The resulting physical and electrical characteristics of TSVs are presented in Section 1.3.2.

#### 1.3.1 TSV-based 3-D ICs

Although no standardized fabrication technique has yet been established, several types of fabrication processes have been used to manufacture TSV-based 3-D ICs [58, 59]. These processes, actually, share a similar sequence of fabrication stages [7], as depicted in Fig. 1.10. As the first step, CMOS or SOI wafers are separately fabricated, which provide the physical

Figure 1.10: Typical fabrication steps for 3-D ICs [7]: (a) wafer preparation, (b) TSV etching, (c) wafer thinning, bumping, and handle wafer attachment, (d) wafer bonding, and (e) handle wafer removal.

planes (tiers) for subsequent bonding, as shown in Fig. 1.10(a). In Fig. 1.10(b), vertical TSVs are etched and filled with a conductive material, such as tungsten (W), copper (Cu), or low-resistance polysilicon. To reduce the length of TSVs, wafers need to be thinned to different thickness depending on the techniques. To mechanically support the thinned wafers which are difficult to handle and bond, these wafers are attached to "handle" wafers, as shown in Fig. 1.10(c). The alignment and bonding between dies or wafers follow successively as in Fig. 1.10(d). Afterwards, the handle wafer is removed and the corresponding side of wafer is processed and bonded to another physical plane, if any.

Since all the inter-plane communication is implemented through TSVs, the fabrication of TSVs with high density is crucial to 3-D ICs. A fabrication technology for TSVs should provide reliable, inexpensive, low-impedance, and area-efficient vertical interconnections. Depending on which stage TSVs are fabricated at, there are presently three types of fabrication processes: via-first, via-middle, and via-last [43, 60–63]. In some other works, via-first and via-middle technologies are both designated as via-first technology [7]. To avoid confusion, via-first and via-middle are differentiated from each other in this dissertation.