### Multi-gate Si nanowire MOSFETs: Fabrication, strain engineering and transport analysis

THÈSE Nº 5507 (2012)

PRÉSENTÉE LE 2 NOVEMBRE 2012 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DES DISPOSITIFS NANOÉLECTRONIQUES PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

### Mohammad NAJMZADEH

acceptée sur proposition du jury:

Dr C. Dehollain, président du jury Prof. M. A. Ionescu, directeur de thèse Prof. S. Mantl, rapporteur Dr J.-M. Sallese, rapporteur Prof. A. Schenk, rapporteur

## Acknowledgements

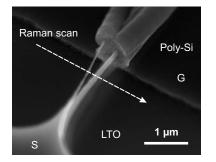

As a first step, I would like to thank Swiss Federal Institute of Technology in Lausanne-EPFL, the EDMI doctoral school and the Nanoelectronic Devices Laboratory (Nanolab) for doing this thesis in a competitive basis. It was a good opportunity to gain several knowledge in this thesis supported by extensive course works in microsystems and microelectronics as well, organized by EPFL, FSRM and MEAD Education SA. Thanks to Dr. Yoshishige Tsuchiya and Sheng Ye at Southampton University, UK, for the micro-Raman measurements (using a TERS setup) on deeply scaled cross-section Si nanowires and Dr. Di Wang and Dr. Robby Prang at Karlsruhe Institute of Technology (KIT), Germany, for the HRTEM cross-sections on my nanowires with 0.08 nm resolution. Thanks to Dr. Per-Erik Hellstrom at KTH Royal Institute of Technology, Stockholm, Sweden, for the poly-Si/SiO<sub>2</sub> gate stack, Dr. Sarah Olsen at Newcastle University, UK, for the micro-Raman measurement on sub-100 nm wide nanowires and Dr. Jean-Michel Sallese at EPFL to support the parameter extraction part of this thesis in the experiment, modeling and simulation steps. Thanks to Dr. Wladek Grabinski and Dr. Didier Bouvet (Dr. Paul Salet, Dr. Dimitrios Tsamados and Dr. Suyat Ayoz as well) for organizing the group meetings and providing feedbacks on the process, the electrical characterization and the simulation steps. Thanks to Matthieu Berthomé, for helps on the transport analysis steps in my nanowires, used for the three recent IEEE TED paper submissions (#1-3), and the other Ph.D. students, post-docs, all the secretaries and staff at Nanolab and EPFL for the happy moments.

Fabrication of bulk Si nanowires was pretty challenging, especially the isolation step, needing several process monitoring to minimize the process variation. Thanks to the CMi staff for the extensive technical supports during the various process steps, especially regarding several process issues for the first SOI Si nanowire run-card at EPFL including an ALD high-k/metal-gate stack. Note that we could fabricate the GAA sub-5 nm cross-sectional Si nanowires successfully and with 100% efficiency from our only two SOI wafers, dedicated to validate my first SOI Si nanowire run-card. Thanks to Mir-Enterprise Ltd., UK, and the Philips clean room at Eindhoven, the Netherlands, for performing the high-k/metal-gate ALD gate stack on mt 100 mm SOI wafers including suspended sub-5 nm cross-sectional Si nanowires. It was a pretty difficult task, performing all the steps in a few hours while monitoring and checking the actual process steps by EPFL at the same time as well. All the works went smoothly and with the highest possible quality and efficiency, only by perseverance, hardworking, precision and organization during the experiments, electrical characterization, publication and international conference presentations.

#### Acknowledgements

I would like to thank Prof. Andreas Schenk, the head of Nano-Device Physics Group at Swiss Federal Institute of Technology in Zurich-ETHZ, Dr. Jean-Michel Sallese from STI Scientists group at Swiss Federal Institute of Technology in Lausanne-EFPL, Prof. Adrian M. Ionescu, the head of Nanoelectronic Device Laboratory at Swiss Federal Institute of Technology in Lausanne-EFPL, the thesis director, Prof. Siegfried Mantl from Forschungszentrum Julich GmbH research center, Juelich, Germany, and finally, Dr. Catherine Dehollain, from the RFIC group, Swiss Federal Institute of Technology in Lausanne-EFPL, the jury director, for the high international level Ph.D. examination covering simulation, modeling and technology aspects in a competitive basis.

Performing the Ph.D. thesis at EPFL was an excellent opportunity to gain several experiences and knowledge on even the topics that I was not working directly considering various paper review requests from IEEE Transactions on Electron Devices (TED) and Institute Of Physics (IOP) e.g. Nanotechnology during my Ph.D. at EPFL. Thanks also to the Swiss National Science Foundation (SNSF) for the financial support to perform this project as well.

## Abstract

Multi-gate devices e.g. gate-all-around (GAA) Si nanowires and FinFETs are promising candidates for aggressive CMOS downscaling. Optimum subthreshold slope, immunity against short channel effect and optimized power consumption are the major benefits of such architectures due to higher electrostatic control of the channel. On the other hand, Si nanowires show excellent mechanical properties e.g. yield and fracture strengths of  $10\pm 2\%$  and  $30\pm 1\%$ in comparison to 3.7% and 4.0% for bulk Si, respectively, a strong motivation to be used as exclusive platforms for innovative nanoelectronic applications e.g. novel strain engineering techniques for carrier transport enhancement in multi-gate 3D suspended channels or local band-gap modulation using > 4 GPa uniaxial tensile stress in suspended Si channels to enhance the band-to-band tunneling current in multi-gate Tunnel-FETs, all without plastic deformation and therefore, no carrier mobility degradation in deeply scaled channels.

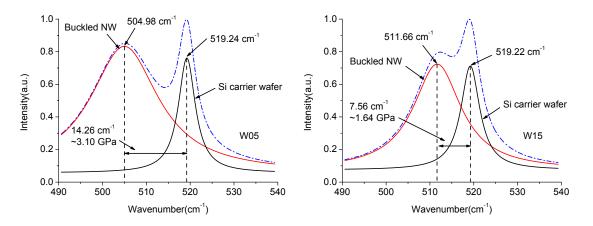

In this thesis and as a first step, a precise built-in stress analysis during local thermal oxidation of suspended Si NWs in the presence of a  $Si_3N_4$  tensile hard mask was done. Accumulation of up to 2.6 GPa uniaxial tensile stress in the buckled NWs is reported. The contribution of hard mask/spacer engineering on the stress level and the NW formation was studied and buckled self-aligned dual NW MOSFETs on bulk Si with two sub-100 nm cross-sectional Si cores including ~0.8 uniaxial tensile stress are reported. Micro-Raman spectroscopy was widely used in this thesis to measure stress in the buckled NWs on both bulk and SOI substrates.

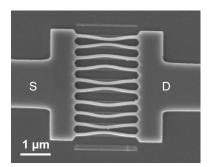

A process flow was designed to make dense array of GAA sub-5 nm cross-sectional Si NWs using a SOI substrate including a high level of stress. The NW stress level can be engineered simply using e.g. metal-gate thin film stress suitable for both NMOS and PMOS devices. Lately, highly and heavily doped architectures with a single-type doping profile from source to drain, called junctionless and accumulation-mode devices, are proposed to significantly simplify the fabrication process, address a few technical limitations e.g. ultra-abrupt junctions in order to fabricate shorter channel length devices. Therefore, in this process flow, a highly doped accumulation-mode was targeted as the operation mechanism.

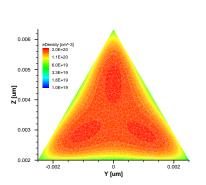

Finally, extensive TCAD device simulation was done on GAA Si NW JL MOSFETs to study the corner effects on the device characteristics, from subthreshold to strong accumulation, report the concept of local volume accumulation/depletion, quantum flat-band voltage, significant bias-dependent series resistance in junctionless MOSFETs and finally, support the experimental data to extract precisely the carrier mobility in sub-5 nm Si NW MOSFETs. **keywords: Si nanowire, multi-gate, stressor, mobility enhancement, micro-Raman, TCAD simulation, nano-transport, ALD gate stack, accumulation, inversion, junctionless.**

## Résumé

Les dispositifs à plusieurs grilles de contrôle, par exemple nanofils de silicium à grilles enrobantes et FinFETs sont des candidats prometteurs pour la réduction agressive des dimensions pour les dispositifs CMOS. Une pente sous le seuil optimale, l'immunité contre les effets de canaux courts et une consommation de puissance optimisée sont des bénéfices majeurs de ce genre de dispositifs, cela grâce à un meilleur contrôle électrostatique du canal. D'un autre côté , les nanofils de silicium présentent des propriétés mécaniques excellents , par exemple des limites d'élasticité et de fracture de  $10\pm 2\%$  et  $30\pm 1\%$  en comparaison à 3,7 et 4% pour du silicium massif, c'est une motivation forte pour les utiliser comme unique plateforme pour des applications nanoélectroniques innovantes comme par exemple des techniques nouvelles d'ingénierie du stress pour une amélioration des qualités de transport dans une architecture 3D à multiples grilles et canaux suspendus, ou bien une modulation de la bande interdite via une contrainte de tension uniaxiale supérieure à 4GPa, permettant d'augmenter le courant tunnel de bande-à-bande dans une architecture Tunnel-FET, tout cela sans modification plastique et par la même occasion sans dégradation de la mobilité des porteurs dans des canaux fortement réduits en dimension.

Dans cette thèse et dans un premier temps, nous analyserons précisément les contraintes intrinsèques accumulées lors d'oxydation thermiques locales de nanofils de silicium suspendus en présence d'un masque dur de nitrure de silicium. Une accumulation de contraintes de tension jusqu'à 2,6 GPa dans des nanofils avec une déformation de type flambage induite par la tension est rapportée. La contribution de la technologie de masques dus et d'ingénierie des espaceurs sur le niveau de contraintes et sur la formation des nanofils est étudiée et des transistors auto-alignés à nanofils de silicium jumeaux formés sur des plaques de silicium massif présentant un canal de dimension sub-100nm sont présentés. La spectroscopie micro-Raman a été souvent utilisée dans cette thèse pour mesurer les contraintes mécaniques dans des nanofils de silicium courbés, à la fois sur des substrats SOI ou bulk.

Un déroulement des procédés a été créé pour permettre la création de réseaux denses de nanofils à grilles enrobantes avec un diamètre sub-5nm, en utilisant un substrat SOI avec un haut niveau de contraintes. Le niveau de contraintes peut être modifié, pa exemple, par l'ajout d'une grille métallique à contrainte intrinsèque adaptés à l'architecture NMOS ou PMOS. Récemment une architecture à base de silicium très et hautement dopé présentant un type de dopage constant de la source au drain, appelées MOS à accumulation et MOS sans jonctions (junctionless) ont été proposées pour simplifier fortement le procédé de fabrication et éviter quelques limitations techniques, comme par exemple la nécessité de jonctions ultra abruptes,

#### Acknowledgements

dans le but de fabriquer des dispositifs avec des longueurs de canal encore plus petites. En conséquence, dans ce procédé de fabrication, un mode de fonctionnement à accumulation à base de silicium fortement dopé a été ciblé.

Enfin, une analyse du transport dans des transistors sans jonctions à base de nanofils de silicium à grille enrobantes a été effectuée, faisant usage de simulations TCAD complètes, pour rapporter l'effet des coins dans tous les modes d'opérations (depuis sous le seuil jusqu'à l'accumulation forte)., le concept d'accumulation/de déplétion de volume locale, le concept de tension de bandes plates quantique, l'importance de la résistance série et sa variation avec les tensions appliquées dans les architectures sans jonctions, et finalement une extraction précise de la mobilité des porteurs à faible champ dans des transistors à nanofils de silicium de dimensions sub-5nm.

Enfin, des simulations TCAD completes ont été faites sur des transistors MOS à nanofils de silicium à grille enrobante pour étudier l'effet des coins, depuis sous le seuil jusqu'en accumulation forte, décrire le concept d'accumulation et déplétion locales ainsi que la bande plate quantique, l'importance de la dépendance en biais des résistances parasites séries dans l'architecture de MOSFET sans jonctions, et enfin supporter les données expérimentales pour extraire précisément la mobilité des porteurs dans des MOSFET à nanofils de silicium de diamétre inférieur à 5nm.

Mots-cléfs : nanofils de silicium, multiples grilles, contraintes, augmentation de mobilité, micro-Raman, TERS, simulations TCAD, transport nanoélectronique, stack de grille ALD, accumulation, inversion, junctionless

# **Technical acronyms**

| Acronym | Description                                                         |

|---------|---------------------------------------------------------------------|

| AC      | alternative current                                                 |

| ALD     | atomic layer deposition                                             |

| AM      | accumulation-mode                                                   |

| AMOSFET | accumulation-mode metal-oxide semiconductor field effect transistor |

| BHF     | buffered hydro fluoric acid                                         |

| BOX     | buried oxide (in a SOI substrate)                                   |

| CE      | classical electron                                                  |

| CED     | classical electron density                                          |

| CESL    | contact etch stop layer                                             |

| CMOS    | complementary metal-oxide semiconductor                             |

| CMP     | chemical mechanical polishing                                       |

| CPD     | crytical point dryer                                                |

| CVD     | chemical vapor deposition                                           |

| DC      | direct current                                                      |

| DHF     | dilute hydrofluoric acid                                            |

| DIBL    | drain induced barrier lowering                                      |

| DM      | depletion-mode                                                      |

| EBL     | e-beam lithography                                                  |

| EM      | enhancement-mode                                                    |

| FB      | flat-band                                                           |

| FET     | field effect transistor                                             |

| FIB     | focused ion beam                                                    |

| GAA     | gate-all-around                                                     |

| HH      | heavy-hole band                                                     |

| HRTEM   | high resolution transmission electron microscopy                    |

| HSQ     | hydrogen silsesquioxane                                             |

| IM      | inversion-mode                                                      |

| IPA     | isopropanol (or 2-propanol)                                         |

| JL      | junctionless                                                        |

| LH      | light-hole band                                                     |

| LPCVD   | low pressure chemical vapor deposition                              |

| LS      | logic swing                                                         |

| LTO     | low temperature oxide                                               |

| MOS     | metal-oxide semiconductor                                           |

#### Technical acronyms

| Acronym | Description                                       |

|---------|---------------------------------------------------|

| MOSFET  | metal-oxide semiconductor field effect transistor |

| NEMS    | nano electromechanical systems                    |

| NW      | nanowire                                          |

| OIS     | Oxidation-induced stress                          |

| PMA     | post-metallization annealing                      |

| QE      | quantum electron                                  |

| QED     | quantum electron density                          |

| QM      | quantum mechanics                                 |

| RF      | radio frequency                                   |

| RTA     | rapid thermal annealing                           |

| SCE     | short channel effect                              |

| SEM     | scanning electron microscopy                      |

| SLO     | stress-limited oxidation                          |

| SMT     | stress memorization technique                     |

| SOI     | silicon on insulator                              |

| SS      | subthreshold swing                                |

| STI     | shallow trench isolation                          |

| TCAD    | technology computer aided design                  |

| TEM     | transmission electron microscopy                  |

| TERS    | tip-enhanced Raman spectroscopy                   |

| TH      | threshold                                         |

| TW      | transition width                                  |

| VTC     | voltage transfer characteristics                  |

# Physical constants and prefixes

### Metric prefixes

| Yotta (Y)             | $10^{24}$                |

|-----------------------|--------------------------|

| Zetta (Z)             | $10^{21}$                |

| Exa (E)               | $10^{18}$                |

| Peta (P)              | $10^{15}$                |

| Tera (T)              | $10^{12}$                |

| Giga (G)              | $10^{9}$                 |

| Mega (M)              | $10^{6}$                 |

| kilo (k)              | 10 <sup>3</sup>          |

| hecto (h)             | $10^{2}$                 |

| deca (da)             | $10^1$                   |

|                       | $10^{0}$                 |

| deci (d)              | $10^{-1}$                |

| centi (c)             | $10^{-2}$                |

| milli (m)             | $10^{-3}$                |

| micro ( $\mu$ )       | $10^{-6}$                |

| nano (n)              | $10^{-9}$                |

|                       |                          |

| pico (p)              | $10^{-12}$               |

| pico (p)<br>femto (f) | $10^{-15}$               |

|                       | $10^{-15}$<br>$10^{-18}$ |

| femto (f)             | $10^{-15}$               |

### Physical constants

| Avogadro's number ( $N_A$ )                 | $6.02 \times 10^{23} \text{ mol}^{-1}$          |

|---------------------------------------------|-------------------------------------------------|

| Boltzmann's constant (k)                    | 1.38×10 <sup>-23</sup> J/K                      |

| Electronic charge (q or e)                  | $1.60 \times 10^{-19} \text{ C}$                |

| Free electron rest mass (m <sub>0</sub> )   | $9.11 \times 10^{-31} \text{ kg}$               |

| Permittivity of free space ( $\epsilon_0$ ) | $8.85 \times 10^{-12} \text{ F/m}$              |

| Planck's constant (h)                       | $6.63 \times 10^{-34} \text{ J} \cdot \text{s}$ |

| Speed of light in vacuum (c)                | 3.00×10 <sup>8</sup> m/s                        |

# Contents

| Ac | knov    | wledge   | ments                                                                                           | iii   |

|----|---------|----------|-------------------------------------------------------------------------------------------------|-------|

| Ał | ostra   | ct (Eng  | lish/Français/Deutsch)                                                                          | v     |

| Те | chni    | cal acr  | onyms                                                                                           | ix    |

| Pł | ysic    | al cons  | tants and prefixes                                                                              | xi    |

| Li | st of : | figures  |                                                                                                 | xvi   |

| Li | st of   | tables   |                                                                                                 | xxiii |

| 1  | The     | sis ove  | rview                                                                                           | 1     |

| 2  | Intr    | oducti   | on                                                                                              | 5     |

|    | 2.1     | Aggre    | ssive CMOS downscaling                                                                          | 5     |

|    | 2.2     | Short    | -channel effects and multi-gate MOSFETs                                                         | 6     |

|    | 2.3     | Stress   | ors as CMOS boosters for carrier transport enhancement                                          | 8     |

|    |         | 2.3.1    | Physics of strained classical Si-based MOSFETs                                                  | 8     |

|    |         | 2.3.2    | Optimum channel strain engineering for NMOS and PMOS devices $\ldots$                           | 9     |

|    |         | 2.3.3    | Stress platforms for planar Si-based MOSFETs                                                    | 11    |

|    |         | 2.3.4    | Stress platforms for multi-gate MOSFETs                                                         | 12    |

|    | 2.4     | Si nan   | nowire platforms                                                                                | 12    |

|    |         | 2.4.1    | Samsung bulk top-down Si nanowire platform - horizontal NWs $\ldots$ .                          | 13    |

|    |         | 2.4.2    | IBM SOI top-down Si nanowire platform - horizontal NWs $\ldots \ldots \ldots$                   | 13    |

|    |         | 2.4.3    | IME-Singapore bulk top-down Si nanowire platform - vertical NWs                                 | 14    |

| 3  | Mul     | lti-gate | buckled Si NWs on bulk for high electron mobility and logic                                     | 21    |

|    | 3.1     | Local    | oxidation as a local stressor technology                                                        | 22    |

|    | 3.2     | Proce    | ss flow using $Si_3N_4$ hard mask and spacer $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 22    |

|    | 3.3     | Direct   | t stress measurement on buckled Si nanowires using micro-Raman spec-                            |       |

|    |         | trosco   | рру                                                                                             | 24    |

|    |         | 3.3.1    | Stress profile along the buckled nanowires                                                      | 26    |

|    | 3.4     | Built-   | in stress analysis during the process                                                           | 26    |

|    |         | 3.4.1    | Stress development during the oxidation step of W0.8 NWs                                        | 28    |

#### Contents

|   |                                                           | 3.4.2 Stress development during the hard mask and oxide stripping step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                         |

|---|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   |                                                           | 3.4.3 Stress development during the rest of the process steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                         |

|   |                                                           | 3.4.4 Stress development in W1.0 nanowires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                         |

|   |                                                           | 3.4.5 An additional oxidation step to shrink further the cross-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                         |

|   | 3.5                                                       | Local versus global carrier mobility in the Si nanowire channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                                         |

|   | 3.6                                                       | Scalability of local oxidation as a local stressor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                                         |

|   | 3.7                                                       | Multi-gate buckled self-aligned dual Si nanowires on bulk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                         |

|   | 3.8                                                       | Fabrication process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                         |

|   | 3.9                                                       | Strain analysis in the buckled Si nanowires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38                                                                         |

|   |                                                           | 3.9.1 stress measurement on the buckled dual Si NWs by micro-Raman spec-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|   |                                                           | troscopy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                         |

|   |                                                           | 3.9.2 Process-based stress optimization in the top-down Si nanowire platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                                         |

|   | 3.10                                                      | ) Electrical characterization and extraction of parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39                                                                         |

|   | 3.11                                                      | Si nanowires for low voltage digital logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                         |

|   |                                                           | 3.11.1 Electrical characterization of NMOS inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                                         |

|   |                                                           | 3.11.2 Small-signal analysis of multi-gate NMOS inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                         |

|   |                                                           | 3.11.3 Static analysis of the multi-gate suspended NMOS inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                                                                         |

|   | 3.12                                                      | 2 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                                                         |

|   | 3.13                                                      | 3 Future works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45                                                                         |

| 4 | Buc                                                       | ckled GAA deeply scaled cross-section Si nanowire MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                         |

| 4 | 4.1                                                       | Operation mode: Accumulation/junctionless vs. inversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                         |

|   |                                                           | Fabrication and stress development during the process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                                                                         |

|   | 4.2                                                       | 4.2.1 Uniaxial tensile stress development during the process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                                         |

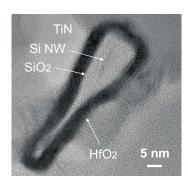

|   |                                                           | 4.2.1 Interfacial SiO <sub>2</sub> thin film layer between Si nanowire and HfO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55                                                                         |

|   | 4.3                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55                                                                         |

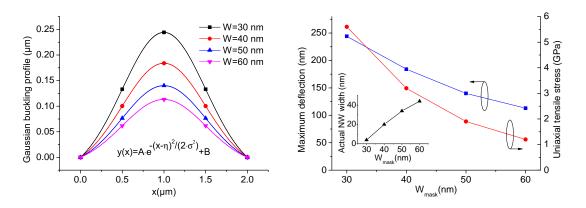

|   | - <del>1</del> .J                                         | Stress estimation for the buckled gate-all-around Si panowires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                         |

|   | 1 1                                                       | Stress estimation for the buckled gate-all-around Si nanowires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55<br>56                                                                   |

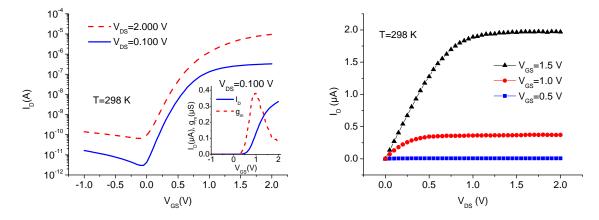

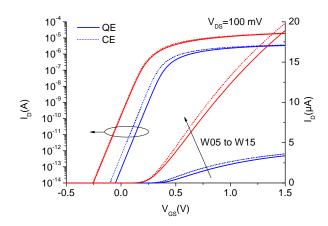

|   | 4.4                                                       | Electrical characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                         |

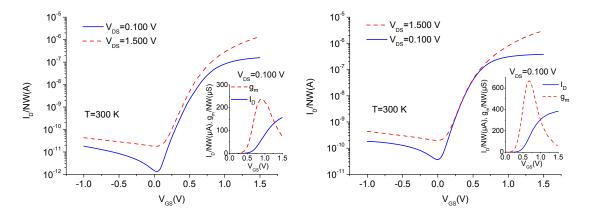

|   |                                                           | Electrical characterization    4.4.1      Room temperature (298 K)    4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56<br>56                                                                   |

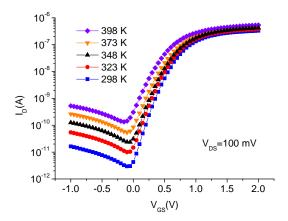

|   | 4.5                                                       | Electrical characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56<br>56<br>57                                                             |

|   |                                                           | Electrical characterization4.4.1Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                               | 56<br>56<br>57<br>57                                                       |

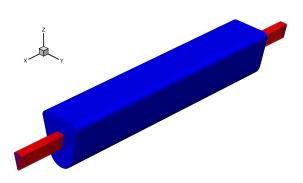

|   | 4.5                                                       | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation                                                                                                                                                                                                                                                                                                                                                                     | 56<br>56<br>57<br>57<br>57                                                 |

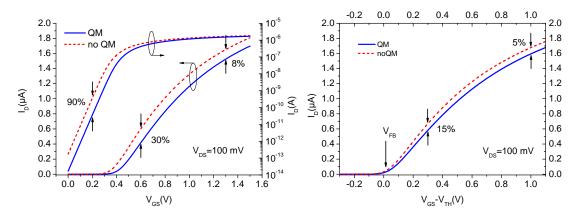

|   | 4.5                                                       | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect                                                                                                                                                                                                                                                                                                                       | 56<br>56<br>57<br>57<br>57<br>58                                           |

|   | 4.5                                                       | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect4.6.3 I-V analytical model in the strong accumulation regime                                                                                                                                                                                                                                                           | 56<br>57<br>57<br>57<br>57<br>58<br>59                                     |

|   | 4.5                                                       | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect4.6.3 I-V analytical model in the strong accumulation regime4.6.4 Subthreshold swing                                                                                                                                                                                                                                   | 56<br>57<br>57<br>57<br>57<br>58<br>59<br>61                               |

|   | 4.5<br>4.6                                                | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect4.6.3 I-V analytical model in the strong accumulation regime4.6.4 Subthreshold swing4.6.5 I_on/I_off ratio                                                                                                                                                                                                             | 56<br>56<br>57<br>57<br>57<br>58<br>59<br>61<br>61                         |

|   | 4.5<br>4.6                                                | Electrical characterization $4.4.1$ Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs $4.6.1$ 3D TCAD Sentaurus device simulation $4.6.2$ 3D quantum mechanical confinement effect $4.6.3$ I-V analytical model in the strong accumulation regime $4.6.4$ Subthreshold swing $4.6.5$ $I_{on}/I_{off}$ ratio $V_{TH}$ , $V_{FB}$ and low-field mobility extraction                                                                                                                               | 56<br>56<br>57<br>57<br>57<br>58<br>59<br>61<br>61<br>61                   |

|   | 4.5<br>4.6                                                | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect4.6.3 I-V analytical model in the strong accumulation regime4.6.4 Subthreshold swing4.6.5 $I_{on}/I_{off}$ ratioVTH, VFB and low-field mobility extraction4.7.1 Threshold voltage extraction                                                                                                                           | 56<br>56<br>57<br>57<br>57<br>58<br>59<br>61<br>61<br>61                   |

|   | 4.5<br>4.6<br>4.7                                         | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect4.6.3 I-V analytical model in the strong accumulation regime4.6.4 Subthreshold swing4.6.5 $I_{on}/I_{off}$ ratioVTH, VFB and low-field mobility extraction4.7.1 Threshold voltage extraction4.7.2 Low-field electron mobility extraction in accumulation regime                                                        | 56<br>56<br>57<br>57<br>58<br>59<br>61<br>61<br>61<br>61<br>61             |

|   | <ul><li>4.5</li><li>4.6</li><li>4.7</li><li>4.8</li></ul> | Electrical characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>58<br>59<br>61<br>61<br>61<br>61<br>62<br>63             |

|   | 4.5<br>4.6<br>4.7<br>4.8<br>4.9                           | Electrical characterization4.4.1 Room temperature (298 K)High temperature performance MOSFET demonstrationTransport mechanism in the AM/JL MOSFETs4.6.1 3D TCAD Sentaurus device simulation4.6.2 3D quantum mechanical confinement effect4.6.3 I-V analytical model in the strong accumulation regime4.6.4 Subthreshold swing4.6.5 $I_{on}/I_{off}$ ratioVTH, VFB and low-field mobility extraction4.7.1 Threshold voltage extraction4.7.2 Low-field electron mobility extraction in accumulation regimeVTH drift by temperature in the GAA sin anowire MOSFETs | 56<br>57<br>57<br>57<br>58<br>61<br>61<br>61<br>61<br>61<br>62<br>63<br>63 |

|   | 4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                   | Electrical characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56<br>57<br>57<br>58<br>59<br>61<br>61<br>61<br>61<br>62<br>63             |

| 5 | Loca | al volume depletion/accumulation in GAA Si NW junctionless nMOSFETs          | 71         |

|---|------|------------------------------------------------------------------------------|------------|

|   | 5.1  | Numerical simulation                                                         | 72         |

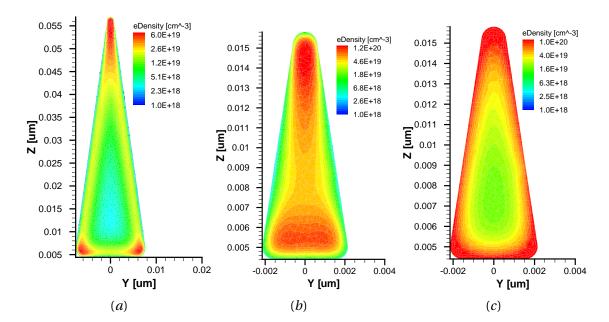

|   | 5.2  | From subthreshold to strong accumulation in a 20 nm wide Si nanowire MOSFET  | 73         |

|   |      | 5.2.1 Operation of accumulation-mode/junctionless MOSFETs                    | 73         |

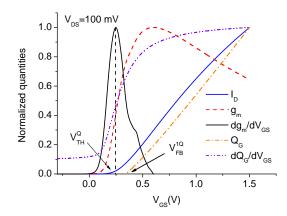

|   |      | 5.2.2 Threshold voltage extraction method                                    | 74         |

|   |      | 5.2.3 Flat-band voltage extraction method                                    | 74         |

|   |      | 5.2.4 Gate-channel capacitance and effective channel width                   | 75         |

|   |      | 5.2.5 Key MOSFET parameters at different channel doping levels               | 76         |

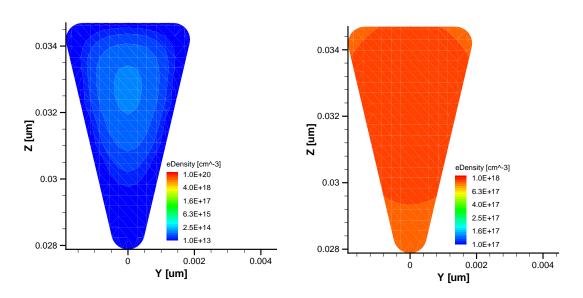

|   | 5.3  | Local electron density distribution across the channel from subthreshold to  |            |

|   |      | strong accumulation                                                          | 77         |

|   |      | 5.3.1 Origin of local depletion/local accumulation in AM/JL MOSFETs          | 77         |

|   |      | 5.3.2 Corner versus global accumulation electron densities in accumulation   |            |

|   |      | regime                                                                       | 79         |

|   | 5.4  | Cross-section shrinkage and corner effect                                    | 80         |

|   |      | 5.4.1 Local electron density for various cross-section dimensions            | 81         |

|   | 5.5  | Summary                                                                      | 83         |

|   | 5.6  | Future works                                                                 | 85         |

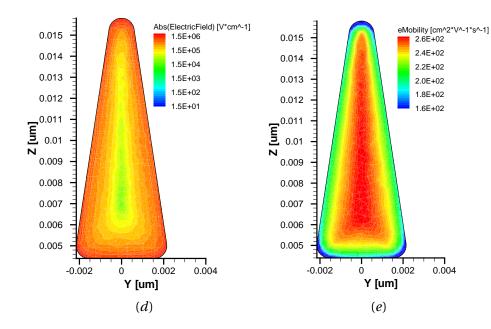

| 6 | Trat | nsport analysis in triangular GAA Si nanowire junctionless nMOSFETs          | 91         |

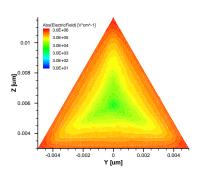

| U | 6.1  | Numerical simulation                                                         | 92         |

|   | 6.2  | Subthreshold to strong accumulation transport with a constant mobility model | 92         |

|   | 0.2  | 6.2.1 Operation of GAA Si nanowire junctionless nMOSFETs                     | 93         |

|   |      | 6.2.2 Threshold voltage extraction method                                    | 93         |

|   |      | 6.2.3 Flat-band voltage extraction method                                    | 94         |

|   |      | 6.2.4 Gate-channel capacitance and effective channel width                   | 94         |

|   |      | 6.2.5 Key MOSFET parameters for different cross-sections                     | 95         |

|   | 6.3  | Transport analysis in GAA Si nanowire MOSFETs with a constant mobility model |            |

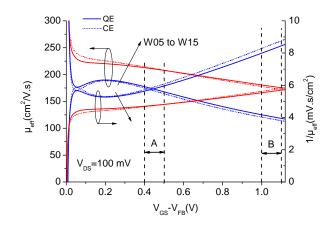

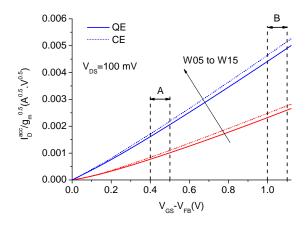

|   | 0.5  | 6.3.1 Transport analysis by split CV method                                  | 96         |

|   |      | 6.3.2 Series resistance and effective mobility attenuation                   | 97         |

|   |      | 6.3.3 Transport analysis using Y-function                                    | 99         |

|   | 6.4  | Transport analysis using Frunction                                           | 55         |

|   | 0.4  | ity model                                                                    | 99         |

|   |      | •                                                                            | 100        |

|   |      |                                                                              | 100        |

|   |      |                                                                              | 100        |

|   | 6.5  |                                                                              | 102        |

|   | 6.6  |                                                                              | 103<br>104 |

|   | 6.7  |                                                                              | 104<br>106 |

|   | 0.7  |                                                                              | 100        |

| 7 | Trar |                                                                              | 111        |

|   | 7.1  |                                                                              | 111        |

|   |      |                                                                              | 111        |

|   | 7.2  | Stress measurement via ALD gate stack using micro-Raman spectroscopy         | 112        |

#### Contents

|    | 7.3                | Numerical device simulation                                           | 112 |

|----|--------------------|-----------------------------------------------------------------------|-----|

|    | 7.4                | Extraction of key MOSFET parameters in an AMOSFET                     | 113 |

|    |                    | 7.4.1 Threshold voltage extraction method                             | 115 |

|    |                    | 7.4.2 Flat-band voltage extraction method                             | 115 |

|    |                    | 7.4.3 Product of gate-channel capacitance and channel width           | 117 |

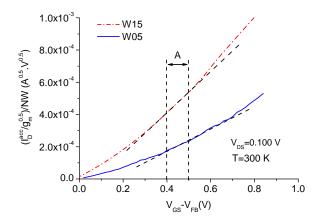

|    |                    | 7.4.4 Low-field electron mobility extraction by the split-CV method   | 117 |

|    |                    | 7.4.5 Low-field electron mobility extraction by the Y-function method |     |

|    | 7.5                | Electrical characterization                                           | 119 |

|    | 7.6                | Summary                                                               |     |

|    | 7.7                | Future works                                                          | 122 |

| 8  | Con                | nclusion                                                              | 127 |

|    | 8.1                | Summary                                                               | 127 |

|    | 8.2                | Future work perspectives                                              |     |

| A  | Pro                | cess flow of buckled NWs on bulk                                      | 133 |

| B  | Pro                | cess flow of self-aligned NWs on bulk                                 | 135 |

| С  | Pro                | cess flow of sub-5 nm SOI Si NWs                                      | 137 |

| D  | TCA                | AD simulations                                                        | 139 |

| Cu | Curriculum Vitae 1 |                                                                       | 141 |

# List of Figures

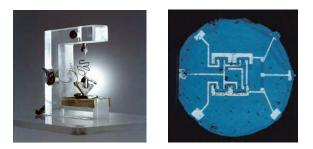

| 2.1      | The first transistor, a germanium-based PNP point-contact device (left), the first                                                                                     | -  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <u>.</u> | complementary MOSFET (CMOS) logic (right) [8].                                                                                                                         | 5  |

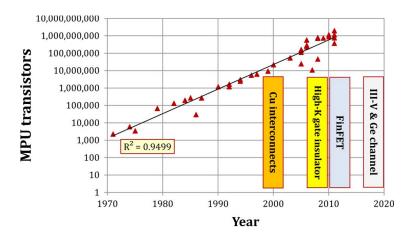

| 2.2      | The number of transistors per microprocessor chip vs. time [9].                                                                                                        | 6  |

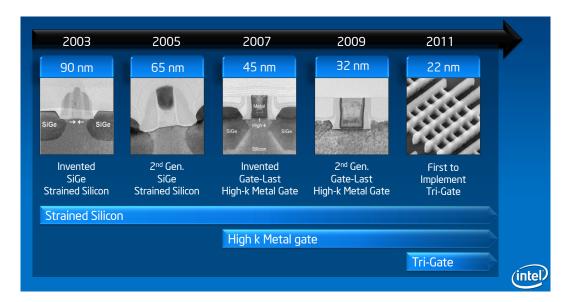

| 2.3      | Intel's 90 nm technology node and beyond to integrate stressor, high-k/metal-                                                                                          | _  |

|          | gate and a multi-gate architecture as CMOS boosters while downscaling [11].                                                                                            | 7  |

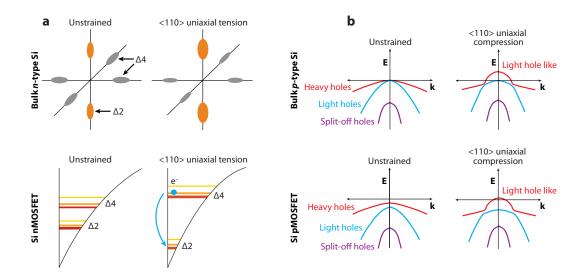

| 2.4      | Simplified conduction band engineering in n-type bulk Si and (100) Si nMOSFET                                                                                          |    |

|          | by <110> uniaxial tensile stress (a), simplified valence band engineering in p-                                                                                        |    |

|          | type bulk Si and (100) Si pMOSFET by <110> uniaxial compressive stress (b)                                                                                             | 0  |

| 0.5      |                                                                                                                                                                        | 9  |

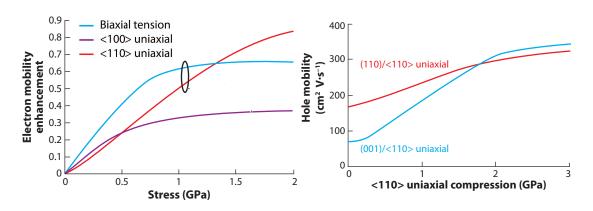

| 2.5      | Electron mobility enhancement factor for various tensile stress types in (100)                                                                                         |    |

|          | Si nMOSFET (left), hole mobility engineering in (100) and (110) Si pMOSFETs                                                                                            | 10 |

| 26       | using <110> uniaxial compressive stress (right) [13]                                                                                                                   | 10 |

| 2.6      | Samsung top-down bulk platform to make horizontal GAA twin circular Si                                                                                                 | 14 |

| 27       | nanowire MOSFETs using a damascene-gate process [44]                                                                                                                   | 14 |

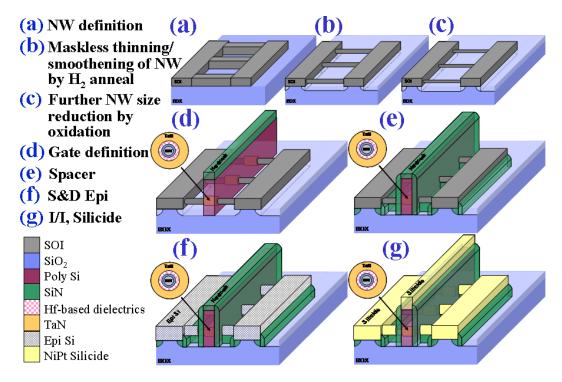

| 2.7      | FETs with a circular cross-section [46].                                                                                                                               | 15 |

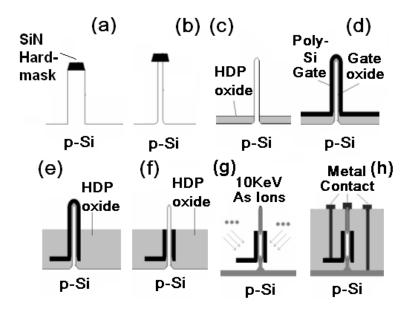

| 2.8      | IME-Singapore top-down bulk platform to make vertical GAA Si NW MOSFETs                                                                                                | 15 |

| 2.0      |                                                                                                                                                                        | 15 |

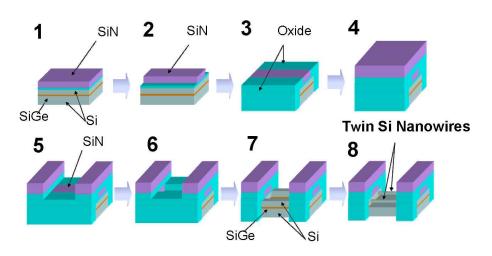

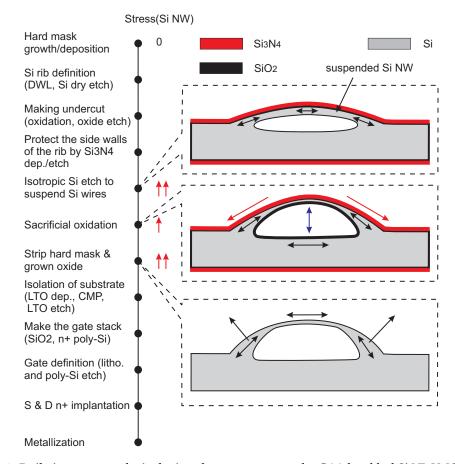

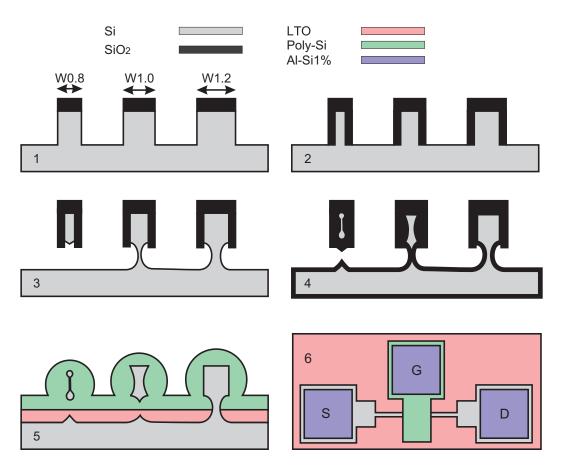

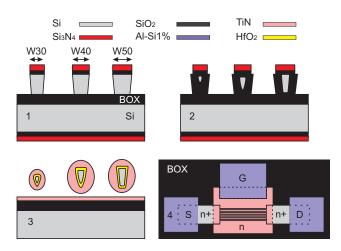

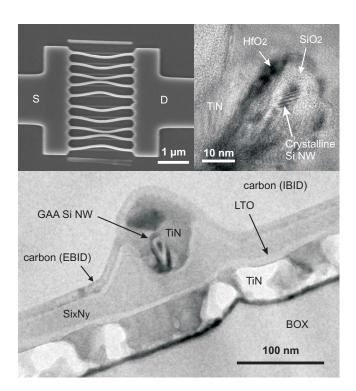

| 3.1      | Process flow to make GAA suspended buckled Si nanowire MOSFETs using a                                                                                                 |    |

|          | top-down Si nanowire platform. W08 and W10 represent the initial 0.8 and 1.0                                                                                           |    |

|          | $\mu$ m mask nanowire width, respectively                                                                                                                              | 23 |

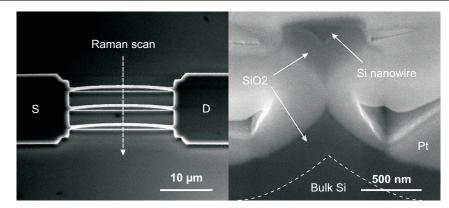

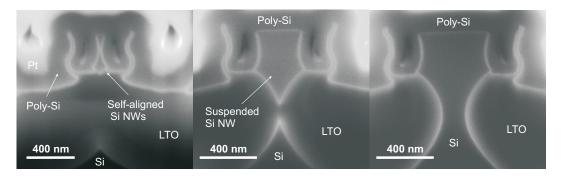

| 3.2      | SEM micrographs (tilted view) of suspended 20 $\mu m$ long W0.8 Si nanowires after                                                                                     |    |

|          | different process steps: a tensile hard mask on top before oxidation (left), after                                                                                     |    |

|          | sacrificial wet oxidation at 850 °C (middle) and after the stripping step (right),                                                                                     |    |

|          | representing reproducibility and controllability of the local strain technique.                                                                                        | 24 |

| 3.3      | SEM micrograph from an array of Si nanowires with a tensile nitride hard mask                                                                                          |    |

|          | on top after wet oxidation (left), the corresponding SEM nanograph cross-section                                                                                       |    |

|          | from the middle of the suspended Si nanowire (right).                                                                                                                  | 25 |

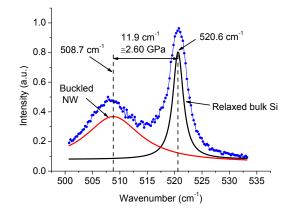

| 3.4      | Micro-Raman spectra at the middle of a buckled 20 $\mu$ m long naked W0.8 Si                                                                                           |    |

|          | nanowire on bulk Si (850 °C wet oxidation). Only two peaks could be detected                                                                                           |    |

|          | in the spectra (relaxed bulk Si and buckled Si nanowire), representing a pure<br>uniaxial tensile stress across the Si nanowire cross-section even at its bottom side. | 26 |

|          | umaxiai tensile suess across the si nanowire cross-section even at its bottom side.                                                                                    | 20 |

#### List of Figures

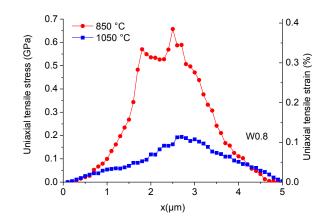

| 3.5   | Tensile strain profiles along two 5 $\mu$ m long W0.8 Si nanowires after wet oxidation (at 850°C and 1050°C) and stripping steps.                                  | 27 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6   | Built-in stress analysis during the process to make GAA buckled Si NW MOSFET                                                                                       |    |

|       | on bulk Si. The black arrows represent tensile stress in Si. The red arrows                                                                                        |    |

|       | represent restrictions on out-of-plane mechanical buckling due to a tensile hard                                                                                   |    |

|       | mask on top. The blue arrow represents upward vertical forces because of the                                                                                       |    |

|       | grown oxide layer underneath the NW.                                                                                                                               | 27 |

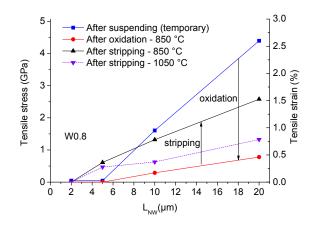

| 3.7   | The peak of tensile stress along W0.8 Si nanowires before/after wet oxidation                                                                                      |    |

|       | at 850 °C and after the stripping step vs. nanowire length. To obtain a highly                                                                                     |    |

|       | strained Si nanowire after the stripping step, oxidation should be performed                                                                                       |    |

|       | below $T_g(SiO_2) = 960^{\circ}C$ [4]                                                                                                                              | 28 |

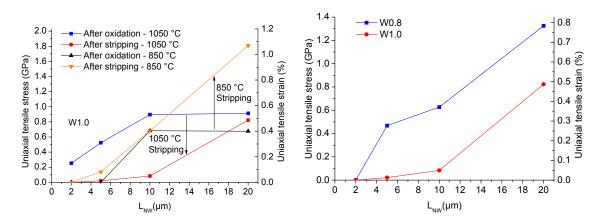

| 3.8   | The peak of tensile strain along two W10 Si NWs after wet oxidation at 1050°C                                                                                      |    |

|       | and after the stripping step (left). The peak of tensile strain along two W08 and                                                                                  |    |

|       | W10 Si NWs after wet oxidation at 1050 $^{\circ}\mathrm{C}$ and stripping steps (right). $\ldots$ .                                                                | 30 |

| 3.9   | SEM cross-section nanograph of a W1.0 Si nanowire after the oxidation step.                                                                                        |    |

|       | The remained Si between the Si nanowire and bulk was consumed during the                                                                                           |    |

|       | oxidation step and the nanowire will be released right after the stripping step                                                                                    | 30 |

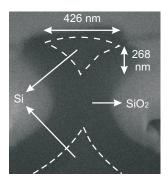

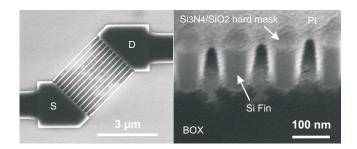

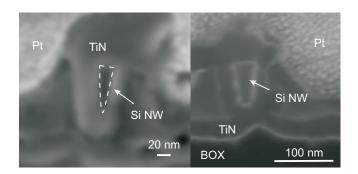

| 3.10  | SEM picture of a GAA Si NW nMOSFET (left); Cross-section of the GAA triangular                                                                                     |    |

|       | wire close to one of its anchors (right)                                                                                                                           | 31 |

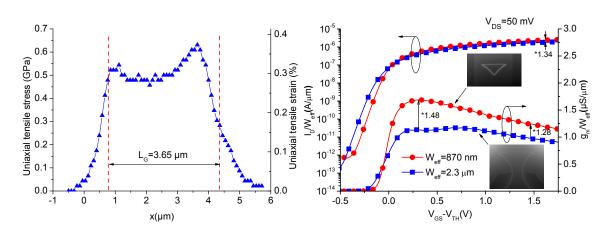

| 3.11  | Stress profile along the 5.0 $\mu$ m long Si nanowire, presented in Fig. 3.10, after the                                                                           |    |

|       | gate stack deposition step (left). Transfer and transconductance characteristics                                                                                   |    |

|       | of strained and non-strained 5.0 $\mu$ m long Si nanowire MOSFETs at $V_{DS}$ = 50 mV                                                                              |    |

|       | (right). The smaller $W_{eff}$ corresponds to the strained device (for the strained                                                                                |    |

|       | device: $V_T$ =-0.0384 V, SS=64 mV/dec; for the non-strained device: $V_T$ =+0.1525 V,                                                                             |    |

|       | SS=66 mV/dec.).                                                                                                                                                    | 32 |

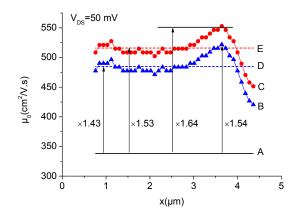

| 3.12  | Local electron mobility enhancement along the buckled Si nanowire channel:                                                                                         |    |

|       | Omega-gate non-strained Si nanowire MOSFET (A); nominal local electron mo-                                                                                         |    |

|       | <i>bility</i> estimation based on local stress profile in Fig. 3.11-left (B); <i>actual local</i>                                                                  |    |

|       | <i>electron mobility</i> along the suspended buckled Si nanowire channel (C); average                                                                              |    |

|       | of nominal local electron mobility estimation based on local stress profile along<br>the buelded element (D): the extracted low field electron mobility of the CAA |    |

|       | the buckled channel (D); the extracted low-field electron mobility of the GAA buckled suspended Si nanowire nMOSFET (E).                                           | 33 |

| 2 1 2 | The Si nanowires with strain peaks represented in Fig. 3.7 after the stripping step                                                                                | 55 |

| 5.15  | (up); the Si nanowires after about 25% prolongation of the isotropic Si etching                                                                                    |    |

|       | step and afterward the same oxidation and stripping steps (bottom). This Si                                                                                        |    |

|       | etching prolongation induces a higher buckling to the shorter devices, validating                                                                                  |    |

|       | the scalability potential of the local oxidation as a local stressor technique, while                                                                              |    |

|       | causing a complete consumption of the longer nanowires during the etching/ox-                                                                                      |    |

|       | idation steps as well. Such process variations can be minimized simply using a                                                                                     |    |

|       | SOI Si nanowire platform [10]-[13]                                                                                                                                 | 34 |

| 3.14  | Implementation of a short channel length Si nanowire MOSFET centered on the                                                                                        |    |

|       | highly strained nanowire region (e.g. sub-2.6 GPa lateral uniaxial tensile stress).                                                                                | 35 |

|       |                                                                                                                                                                    |    |

xviii

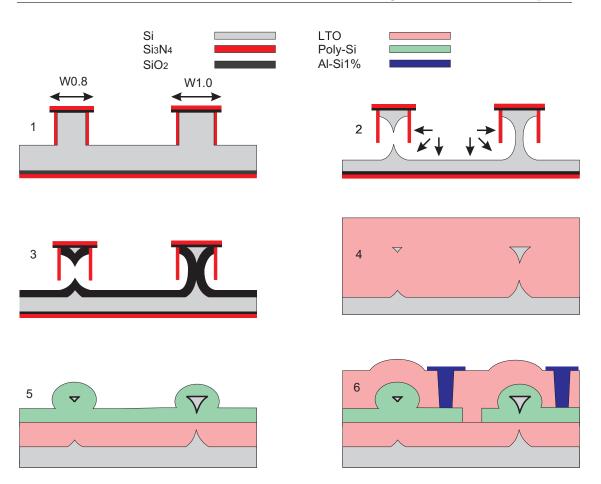

| 3.15 Process flow to obtain multi-gate Si nanowire MOSFETs on bulk. W0.8 corre-                                   | 26 |

|-------------------------------------------------------------------------------------------------------------------|----|

| sponds to the initial 0.8 $\mu$ m mask nanowire width.                                                            | 36 |

| 3.16 Tilted-view SEM micrograph of an array of 10 $\mu$ m long buckled dual Si nanowires                          |    |

| on bulk Si right after the SiO <sub>2</sub> stripping step, representing the reproducibility of                   |    |

| the process flow from strain engineering and dual Si nanowire formation aspects.                                  |    |

| The two sub-100 nm cross-section nanowire cores are connected to each other                                       |    |

| using a thin Si bridge. The out-of-plane buckling is the signature of uniaxial                                    |    |

| tensile stress in the nanowire.                                                                                   | 36 |

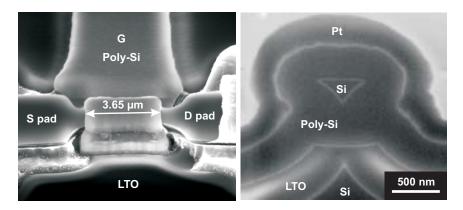

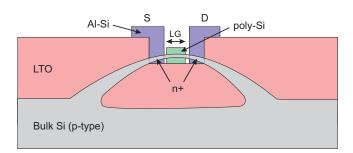

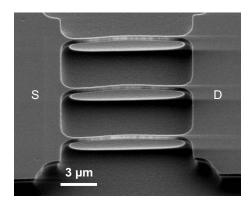

| 3.17 SEM nanograph from the cross-section of multi-gate MOSFETs on bulk Si: multi-                                |    |

| gate suspended dual self-aligned Si nanowires (W0.8, left), multi-gate suspended                                  |    |

| Si nanowire (W1.0, center) and omega-gate MOSFET (W1.2, right)                                                    | 37 |

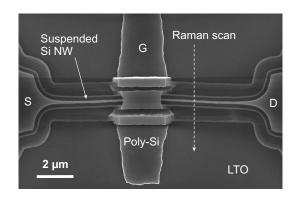

| 3.18 Top-view SEM micrograph of a multi-gate dual Si nanowire MOSFET on bulk                                      |    |

| Si. The in-plane nanowire buckling is a sign of uniaxial tensile stress in the                                    |    |

| channel. The arrow indicates the scan axis and direction of the laser spot in the                                 |    |

| micro-Raman measurement.                                                                                          | 37 |

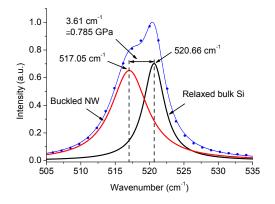

| 3.19 Micro-Raman spectrum taken on a 12 $\mu$ m long buckled dual Si NW on bulk Si                                |    |

| (SEM top-view in Fig. 3.18). The spectrum is well fitted with two Lorentzian                                      |    |

| peaks corresponding to the relaxed bulk Si at 520.66 $\text{cm}^{-1}$ and the strained Si                         |    |

| nanowire at 517.05 cm <sup><math>-1</math></sup> .                                                                | 38 |

| 3.20 Output (left) and input (right) characteristics of the multi-gate dual Si nanowire                           |    |

| MOSFET (W0.8, SEM cross-section in Fig. 3.17-left, $W_{eff}$ =0.713 $\mu$ m (top NW:                              |    |

| $0.273 \ \mu m$ , bottom NW: 0.440 $\mu m$ )). SS=62 mV/dec., V <sub>TH</sub> =-0.061 V, $\mu_0$ =468             |    |

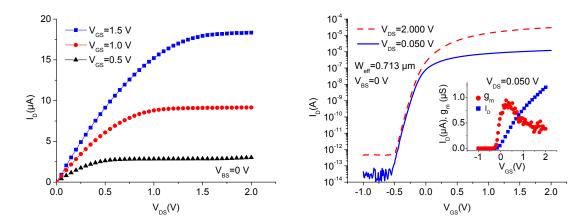

| $cm^2/V$ 's and $R_{SD}$ =18.7 k $\Omega$ , all at $V_{DS}$ =50 mV.                                               | 39 |

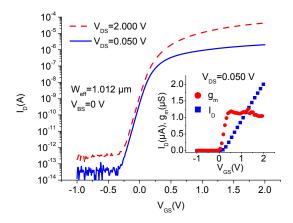

| 3.21 Input characteristics of the multi-gate Si nanowire MOSFET (W1.0, SEM cross-                                 | 33 |

| <b>_</b>                                                                                                          |    |

| section in Fig. 3.17-center, $W_{eff}$ =1.012 $\mu$ m). SS=64 mV/dec., $V_{TH}$ =0.213 V,                         | 40 |

| $\mu_0=353 \text{ cm}^2/\text{V}\cdot\text{s}$ and $R_{SD}=3.7 \text{ k}\Omega$ , all at $V_{DS}=50 \text{ mV}$ . | 40 |

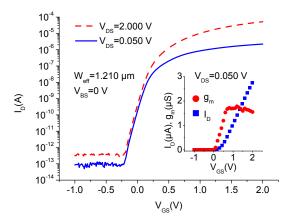

| 3.22 Input characteristics of the omega-gate MOSFET (W1.2, SEM cross-section in                                   |    |

| Fig. 3.17-right, $W_{eff}$ =1.210 $\mu$ m). SS=68 mV/dec., $V_{TH}$ =0.255 V, $\mu_0$ =329 cm <sup>2</sup> /V·s   |    |

| and $R_{SD}=0.8 \text{ k}\Omega$ , all at $V_{DS}=50 \text{ mV}$ .                                                | 41 |

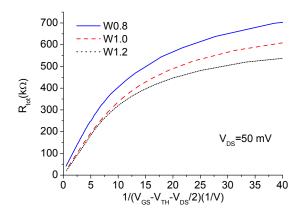

| 3.23 Total resistance ( $V_{DS}/I_D$ ; which is sum of series and channel resistances) vs.                        |    |

| $1/(V_{GS}-V_{TH}-V_{DS}/2)$ for the W0.8, W1.0 and W1.2 MOSFETs at $V_{DS}$ =50 mV. The                          |    |

| series resistance values can be approximately extracted from the y-intercept of                                   |    |

| each curve (least square approximation fitting e.g. below 2.5 $V^{-1}$ ) and reported                             |    |

| in Figs. 3.20-3.22, captions.                                                                                     | 42 |

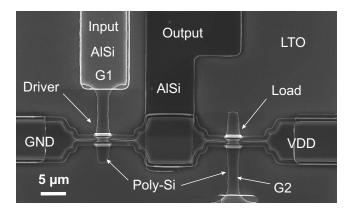

| 3.24 SEM picture of a NMOS inverter (W0.8). The nanowire length and gate length                                   |    |

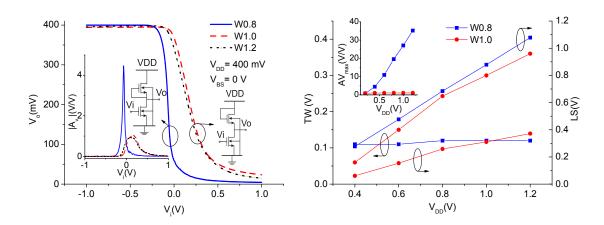

| are 12.0 and 2.0 $\mu$ m, repsectively                                                                            | 42 |

| 3.25 Voltage transfer characteristics (VTC) of the multi-gate W0.8, W1.0 and W1.2 Si                              |    |

| nanowire NMOS inverters (inset: absolute value of the voltage gain, $ A_v  =  dV_o/dV_b $                         | ], |

| vs. input voltage) (left). W0.8 has the DM architecture while the others with posi-                               |    |

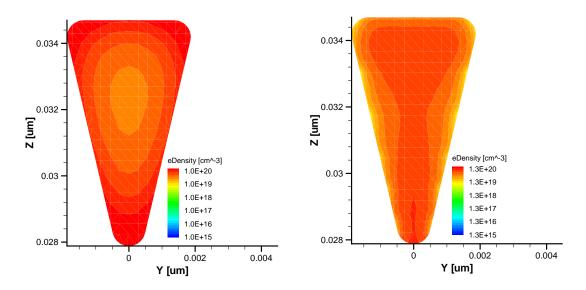

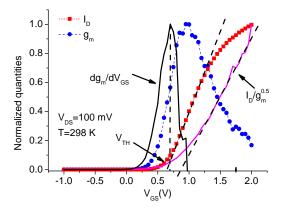

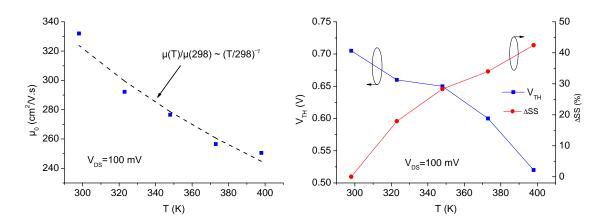

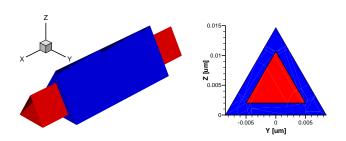

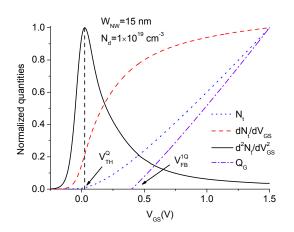

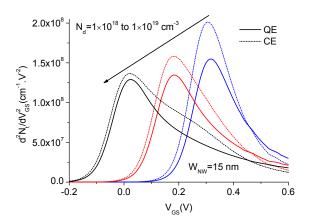

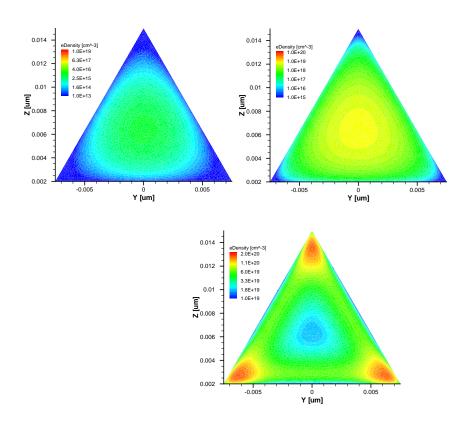

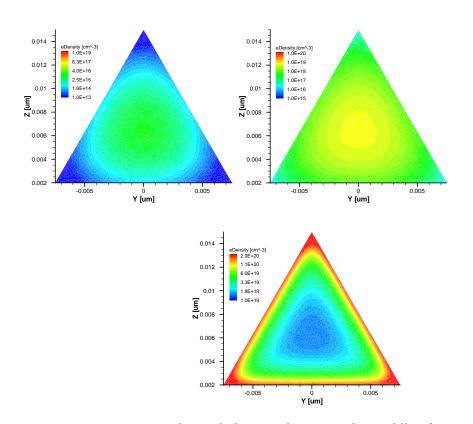

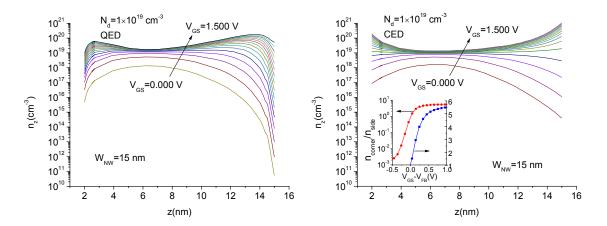

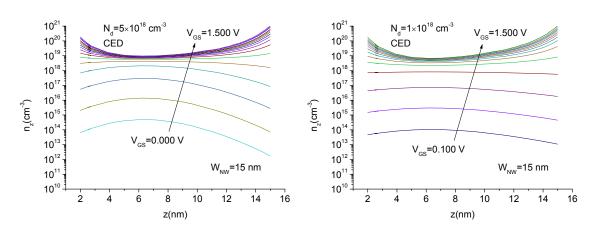

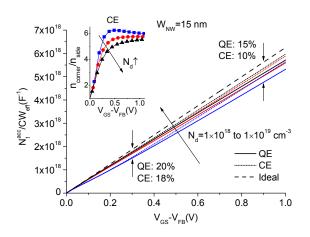

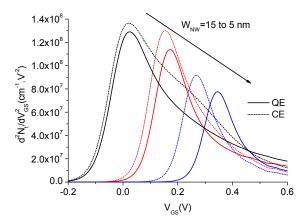

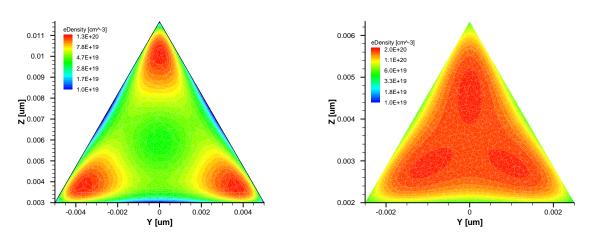

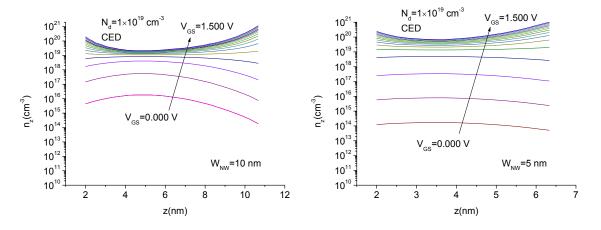

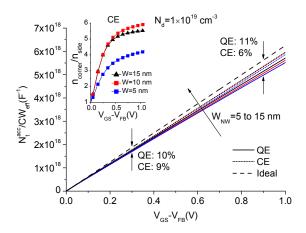

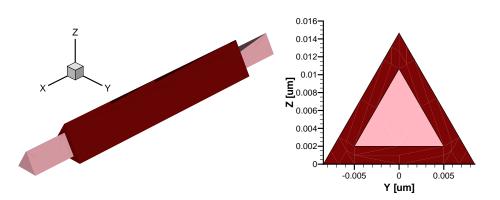

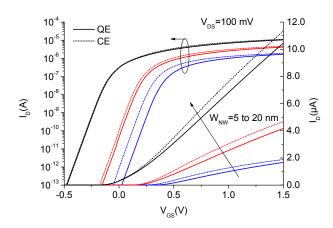

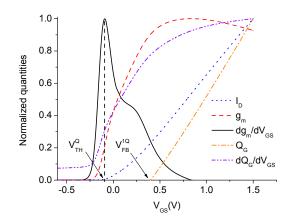

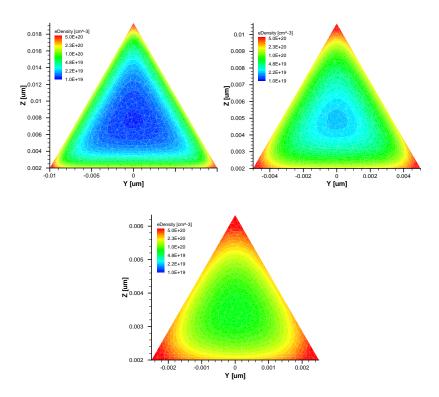

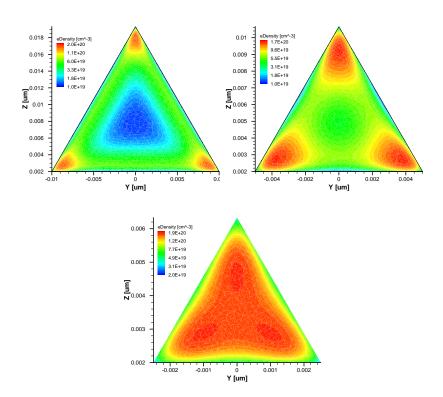

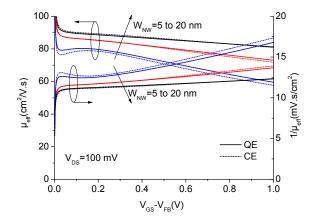

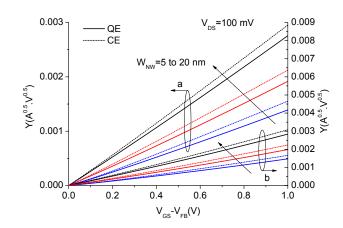

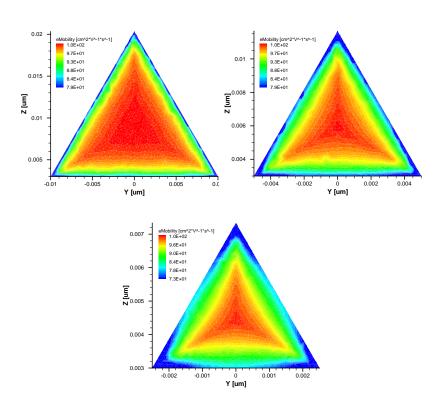

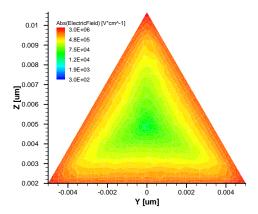

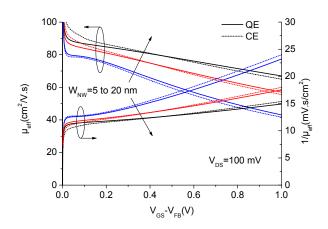

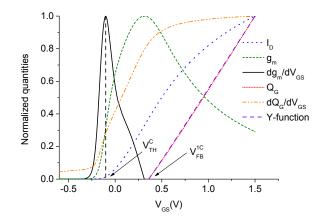

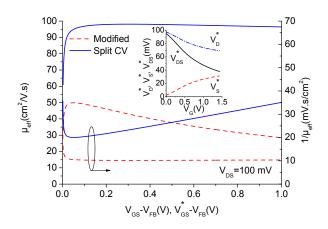

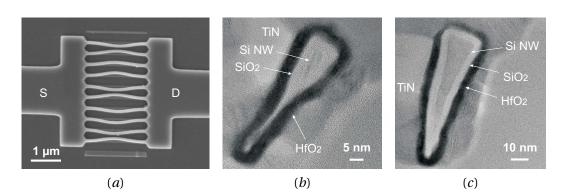

| tive threshold voltages have the EM architecture. Transition width (TW= $V_{iH}$ - $V_{iL}$ )                     |    |