## Design Methods and Tools for Application-Specific Predictable Networks-on-Chip

## THÈSE N° 5407 (2012)

PRÉSENTÉE LE 2 JUILLET 2012

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI)

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

## Ciprian SEICULESCU

acceptée sur proposition du jury:

Prof. B. Falsafi, président du jury Prof. G. De Micheli, Prof. L. Benini, directeurs de thèse Dr F. Angiolini, rapporteur Prof. D. Atienza Alonso, rapporteur Prof. A. Greiner, rapporteur

# **Abstract**

As the complexity of applications grows with each new generation, so does the demand for computation power. To satisfy the computation demands at manageable power levels, we see a shift in the design paradigm from single processor systems to *Multiprocessor Systems-on-Chip* (MPSoCs). MPSoCs leverage the parallelism in applications to increase the performance at the same power levels. To further improve the computation to power consumption ratio, MPSoCs for embedded applications are heterogeneous and integrate cores that are specialized to perform the different functionalities of the application. With technology scaling, wire power consumption is increasing compared to logic, making communication as expensive as computation. Therefore customizing the interconnect is necessary to achieve energy efficiency. Designing an optimal application specific *Network-on-Chip* (NoC), that meets application demands, requires the exploration of a large design space. Automatic design and optimization of the NoC is required in order to achieve fast design closure, especially for heterogeneous MPSoCs.

To continue to meet the computation requirements of future applications new technologies are emerging. *Three dimensional integration* promises to increase the number of transistors by stacking multiple silicon layers. This will lead to an increase in the number of cores of the MPSoCs resulting in increased communication demands. To compensate for the increase in the wire delay in new technology nodes as well as to reduce the power consumption further, multi-synchronous design is becoming popular. With multiple clock signals, different parts of the MPSoC can be clocked at different frequencies according to the current demands of the application and can even be shutdown when they are not used at all. This further complicates the design of the NoC. Many applications require different levels of guarantee from the NoC in order to perform their functionality correctly. As communication traffic patterns become more complex, the performance of the NoC can no longer be predicted statically. Therefore designing the interconnect network requires that such guarantees are provided during the dynamic operation of the system which includes the interaction with major subsystems (i.e., main memory) and not just the interconnect itself.

In this thesis, I present novel methods to design application-specific NoCs that meet perfor-

mance demands, under the constraints of new technologies. To provide different levels of *Quality of Service*, I integrate methods to estimate the NoC performance during the design phase of the interconnect topology. I present methods and architectures for NoCs to efficiently access memory systems, in order to achieve predictable operation of the systems from the point of view of the communication as well as the bottleneck target devices. Therefore the main contribution of the thesis is twofold: *scientific* as I propose new algorithms to perform topology synthesis and *engineering* by presenting extensive experiments and architectures for NoC design.

Keywords: MPSoC, NoC, topology, synthesis, real-time, simulation, DRAM memory

# Résumé

Comme la complexité des applications augmente avec chaque nouvelle génération, il en va de même pour les besoins en puissance de calcul. Pour satisfaire la demande en calculs tout en restant à des niveaux de puissance consommée acceptables, nous observons un changement dans le paradigme de conception depuis les systèmes monoprocesseurs aux systèmes sur puces multiprocesseurs (MPSoCs pour Multiprocessor Systems-on-Chip). Les MPSoCs reposent sur la parallélisation des applications pour augmenter les performances à un niveau de puissance consommée ciblé. Pour continuer à améliorer le rapport entre la puissance de calcul et la consommation d'énergie, les MPSoCs dédiés aux applications embarquées sont hétérogènes et intègrent des cœurs qui se sont spécifiques à certaines fonctionnalités de l'application. Avec l'évolution technologique et la réduction des dimensions, la consommation énergétique due aux interconnexions est en augmentation par rapport à la logique, ce qui rend la communication plus chére que le calcul. Par consèquent, l'utilisation de nouvelles structures d'interconnexions est nécessaire pour atteindre l'efficacité énergétique. La conception d'un Réseau sur Puce (NoC pour Network-on-Chip) optimal vis-à-vis des contraintes applicatives exige l'exploration d'un large espace de conception. La conception et l'optimisation automatique du NoC est nécessaire afin d'aboutir à un temps de conception tolérable, en particulier pour les MPSoCs hétérogènes.

Pour continuer à répondre aux exigences de calcul des futures applications, de nouvelles technologies font leur apparition. *L'intégration tri-dimensionelle* promet une augmentation du nombre de transistors grâce à l'empilement de multiples couches de silicium. Cela conduira à une augmentation du nombre de cœurs dans les MPSoCs et à des demandes accrues vis-à-vis des communications. Afin de compenser l'augmentation du délai du aux interconnexions dans les nouveaux nœuds technologiques mais aussi de continuer à réduire la consommation énergétique, la conception de systèmes multi-synchrones est devenu populaire. Avec plusieurs signaux d'horloge, les différentes parties du MPSoC peuvent être cadencées à des fréquences différentes selon le besoin immédiat de l'application et peuvent même être arrêtées lorsqu'elles ne sont

pas utilisées. Ceci complique encore la conception du NoC. Les applications exigent différents objectifs de performances du NoC afin d'assurer un fonctionnement correct. Or le trafic dans le réseau devenant de plus en plus complexes, la performance du NoC ne peut plus être prédite de façon statique. En conséquence, la conception du réseau d'interconnexion exige que ces objectifs soient tenus pendant le fonctionnement dynamique du système qui inclut l'interaction avec les principaux sous-systèmes (i.e, la mémoire principale) et non simplement l'interconnexion en elle-même.

Dans cette thèse, je présente de nouvelles méthodes pour concevoir des NoCs spécifiques à une application, qui répondent à des exigences de performance et respectent les contraintes des nouvelles technologies. Pour fournir différents niveaux de *qualité de service* (QoS pour Quality-of-Service), j'intègre des méthodes pour estimer la performance du NoC durant la phase de conception de la topologie d'interconnexion. Je présente des méthodes et des architectures pour les NoCs permettant d'accéder efficacement à la mémoire, dans le but d'obtenir un fonctionnement prévisible des systèmes du point de vue de la communication tout en considérant l'impact des périphériques les plus contraignants. Par conséquent, la thèse apporte une contribution originale sur deux fronts : *scientifique* en proposant de nouveaux algorithmes pour réaliser une synthèse topologique et *l'ingénierie* en présentant des expériences approfondies et des architectures pour la conception de NoCs.

**Mots-clés :** MPSoC, NoC, topologies, synthèse, temps réel, simulation, mémoire DRAM

# Riassunto

Con l'aumentare della complessità delle applicazioni ad ogni generazione, si assiste ad un aumento corrispondente dei requisiti di potenza di calcolo. Per soddisfare i bisogni computazionali mantenendo un livello di consumo di potenza ragionevole, assistiamo ad una transizione dai sistemi a singolo processore verso sistemi multiprocessore (Multiprocessor Systems-on-Chip o MPSoCs). Gli MPSoC sfruttano il parallelismo disponibile nelle applicazioni per aumentare le prestazioni a consumo di potenza costante. Per migliorare ulteriormente il rapporto tra potenza computazionale e requisiti energetici, gli MPSoC per applicazioni embedded sono eterogenei ed integrano processori specializzati per le varie funzioni delle applicazioni. Con lo scalare della tecnologia, il consumo di potenza per l'attraversamento dei fili è in aumento rispetto a quello della logica, rendendo la comunicazione costosa quanto la computazione. Di conseguenza, l'ottimizzazione dell'interconnessione è necessaria per raggiungere la massima efficienza energetica. Tuttavia, progettare una Networkon-Chip (NoC) specifica per un'applicazione, che soddisfi tutti i requisiti applicativi, richiede l'esplorazione di un vasto spazio di progetto. L'automazione della progettazione e ottimizzazione delle NoC è necessaria per ottenere una rapida convergenza, soprattutto per MPSoC eterogenei.

Nuove tecnologie stanno emergendo per continuare a soddisfare i requisiti di potenza di calcolo delle applicazioni future. L'*integrazione tridimensionale* promette un aumento del numero di transistori con la sovrapposizione di più strati di silicio. Questo porterà ad un aumento del numero di processori negli MPSoC, risultando anche in un aumento dei requisiti di comunicazione. Per compensare il deterioramento dei ritardi di propagazione sui fili nei nuovi nodi tecnologici e per ridurre ulteriormente i consumi di potenza, la progettazione multi-sincrona sta diventando sempre più comune. Usando più segnali di *clock*, ogni parte di un MPSoC può essere fatta lavorare a frequenze diverse secondo gli attuali requisiti applicativi, oppure addirittura spenta completamente quando non in uso. Questo però rende più complessa la progettazione della NoC. Inoltre, molte applicazioni si attendono livelli diversi di prestazioni

garantiti dalla NoC per svolgere correttamente i propri compiti. Tuttavia, al complicarsi degli schemi di traffico, queste prestazioni non possono più essere garantite staticamente. Quindi, progettare l'interconnessione richiede che queste garanzie siano fornite a *runtime* a sistema funzionante, quando vanno tenute in conto anche le interazioni con sottosistemi chiave (per esempio, la memoria esterna) e non più solo l'interconnessione in sè.

In questa tesi, presenterò dei metodi innovativi per progettare NoC ottimizzate per specifiche applicazioni, che rispettino i bisogni prestazionali e i nuovi vincoli tecnologici. Per poter fornire diversi livelli di servizio (*Quality of Service*), mostrerò l'integrazione di metodi per stimare le prestazioni della NoC già in fase di progettazione della topologia dell'interconnessione. Presenterò poi metodi ed architetture volte ad un efficiente accesso della NoC ai sottosistemi di memoria, per poter predire il funzionamento del sistema considerando sia l'interconnessione che i colli di bottiglia imposti dai dispositivi destinatari del traffico. In sintesi, il contributo principale della tesi comprende due assi principali: *scientifico*, riguardo agli algoritmi proposti per la sintesi delle topologie, e *ingegneristico*, con riferimento ad una vasta sezione sperimentale ed alle proposte architetturali per la progettazione di NoC.

**Parole chiave:** MPSoC, NoC, topologia, sintesi, tempo-reale, simulazione, memoria DRAM

# Acknowledgements

First of all I would like to thank Prof. Giovanni De Micheli for giving me the opportunity to do research under his supervision. Even though he gave me ample freedom to pursue my own ideas on the topic as well, his guidance was crucial for the completion of this work and for making sure that I would constantly focus on the overall goal. His advice was useful not only from the technical viewpoint, but also to help me refine other primary skills, such as technical writing and presentation. I am grateful also for the very friendly atmosphere that he creates in his laboratory, e.g. by way of the social events that he organizes.

I also need to thank Prof. Luca Benini for his continuous supervision and advice. He made sure that I would make constant progress, helping me reach the research milestone represented by this thesis. His careful review of my work was instrumental in improving the quality of my investigation and publications. His contacts with the industry and his broad scope of interests also helped make this work relevant from a practical perspective.

Then, I would like to thank Srinivasan Murali, the post-doctoral assistant supervising me, following my work and helping me from day one. I have learned a lot from him. Not only he inspired me to turn my ideas into publications from the very beginning of my PhD, he is also a very good friend. We have also spent quite a bit of time together outside of the laboratory and Srini is the one who got me started on several sportive activities in Lausanne.

I would like to thank my examination committee members, Prof. Babak Falsafi, Prof. Alain Greiner, Prof. David Atienza and Dr. Federico Angiolini for their comments and insightful advice on this thesis.

I would also like to thank my research collaborators, Dara Rahmati, Naser Khosro Pour and Stavros Volos for their contributions to some key publications, which are at the core of portions of this thesis.

I thank all my colleagues and friends at EPFL: Antonio, Pierre-Emmanuel, Jaime, Vasilis, Alena, Camilla, Shashi, Cristina, Andrea, Michele, Julien, Jacopo, Irene, Hu,

### Acknowledgements

Wenqi, Eleni, Francesca and all the others that I may have missed. They have created a very nice and friendly atmosphere in the lab and we have also spent many nice moments outside of it on hikes and dinners. I thank Jacopo and Shashi for their continuous efforts to provide entertainment during lunches. I thank Antonio for organizing a few extreme hikes, which I am proud to have completed, and Cristina for other nice ones - some of which we still need to complete. My gratitude goes to our administrative secretary Christina, whose efforts have spared us from the boring tasks of filling paperwork. A special mention goes to Abhishek, as TA of the course that inspired me to choose this laboratory for the PhD, and therefore also as one of my first colleagues. I would also thank Haykel, who was a very nice traveling companion during my first conferences overseas.

I also thank my parents for the inspiration they have provided, but also their help and support throughout these years. I thank all my family and friends for their support and I would like to give special thanks to Prof. Ioan Lie for the good collaboration I have had with him during my bachelors degree. Without his collaboration I would not have had the extra skills that enabled me to come to EPFL.

# **Contents**

| Al | ostra | t                                                                                 | ii    |

|----|-------|-----------------------------------------------------------------------------------|-------|

| Ac | knov  | ledgements                                                                        | ix    |

| Ta | ble o | contents                                                                          | xiv   |

| Li | st of | gures                                                                             | xviii |

| Li | st of | ables                                                                             | xix   |

| 1  | Intr  | duction                                                                           | 1     |

|    | 1.1   | Network-on-Chip a structured interconnect for Systems-on-Chip $\ldots$            | 3     |

|    | 1.2   | Interconnect design challenges                                                    | 5     |

|    | 1.3   | Tools for designing NoCs                                                          | 7     |

|    | 1.4   | Thesis contribution                                                               | 10    |

|    |       | 1.4.1 Assumptions and limitations                                                 | 10    |

|    | 1.5   | Thesis overview                                                                   | 11    |

|    |       | 1.5.1 NoC design in new technologies                                              | 12    |

|    |       | 1.5.2 Adding QoS to NoC synthesis                                                 | 13    |

| 2  | Bac   | ground                                                                            | 15    |

|    | 2.1   | NoC principles                                                                    | 15    |

|    |       | 2.1.1 NoC hardware                                                                | 15    |

|    |       | 2.1.2 NoC topology                                                                | 17    |

|    |       | 2.1.3 Switching and flow control                                                  | 18    |

|    |       | 2.1.4 Routing and arbitration                                                     | 20    |

|    | 2.2   | Three dimensional integration                                                     | 21    |

|    | 2.3   | Multi synchronous design                                                          | 25    |

|    | 2.4   | Quality-of-Service                                                                | 27    |

|    |       | 2.4.1 QoS at NoC level                                                            | 28    |

|    |       | 2.4.2 QoS in the presence of bottleneck devices                                   | 29    |

|    | 2.5   | Comparison with previous work and list of publications $ \ldots  \ldots  \ldots $ | 32    |

|    | 2.6   | Summary                                                                           | 33    |

### **Contents**

| 3 | Des | igning application specific NoCs for heterogeneous 3D-SoCs            | 35  |

|---|-----|-----------------------------------------------------------------------|-----|

|   | 3.1 | Architecture                                                          | 38  |

|   | 3.2 | Design approach                                                       | 40  |

|   | 3.3 | Methods to establish core to switch connectivity                      | 44  |

|   |     | 3.3.1 Phase 1                                                         | 44  |

|   |     | 3.3.2 Phase 2                                                         | 47  |

|   |     | 3.3.3 Pruning the search space                                        | 49  |

|   | 3.4 | Path computation                                                      | 50  |

|   | 3.5 | Switch Position Computation                                           | 51  |

|   | 3.6 | Experiments and case studies                                          | 55  |

|   |     | 3.6.1 Multimedia SoC case study                                       | 55  |

|   |     | 3.6.2 Comparison between Phase 1 and Phase 2                          | 60  |

|   |     | 3.6.3 2D vs. 3D comparison                                            | 60  |

|   |     | 3.6.4 Floorplanning study                                             | 62  |

|   |     | 3.6.5 Impact of inter-layer link constraint and comparisons with mesh | 62  |

|   | 3.7 | Summary                                                               | 64  |

| 4 | D   | South and a Na Office Cooperate Maria and about decomposite 1944.     |     |

| 4 |     | igning the NoC for SoCs with VFIs and shutdown capabilities           | 67  |

|   | 4.1 | Problem description                                                   | 69  |

|   |     | 4.1.1 Architecture Description                                        | 69  |

|   | 4.0 | 4.1.2 Synthesis problem                                               | 71  |

|   | 4.2 | Topology synthesis approach                                           | 72  |

|   | 4.3 | 3D architecture and design approach                                   | 76  |

|   | 4.4 | Experimental results                                                  | 77  |

|   |     | 4.4.1 Case study on mobile platform                                   | 77  |

|   |     | 4.4.2 Using intermediate NoC VFI                                      | 81  |

|   |     | 4.4.3 Comparisons on different benchmarks                             | 82  |

|   |     | 4.4.4 Comparison of 2D and 3D topologies                              | 83  |

|   |     | 4.4.5 Comparison for different number of VFIs                         | 83  |

|   |     | 4.4.6 Comparison with different design sizes                          | 88  |

|   |     | 4.4.7 Analysis of results                                             | 88  |

|   | 4.5 | Summary                                                               | 88  |

| 5 | Ren | noving deadlocks in application specific topologies                   | 91  |

|   | 5.1 | Background on deadlock avoidance techniques in NoCs                   | 93  |

|   | 5.2 | Problem formulation                                                   | 93  |

|   | 5.3 | Deadlock removal approach                                             | 97  |

|   |     | 5.3.1 Finding the edge to remove                                      | 99  |

|   |     |                                                                       | 102 |

|   |     |                                                                       | 102 |

|   | 5.4 |                                                                       | 103 |

|   | ~   |                                                                       |     |

|   |      | 5.4.1    | Comparison with resource ordering                                | 103 |

|---|------|----------|------------------------------------------------------------------|-----|

|   |      | 5.4.2    | Power comparison with VCs                                        | 105 |

|   |      | 5.4.3    | Area and power comparison with physical channels                 | 107 |

|   |      | 5.4.4    | Benefits of deadlock removal after topology synthesis for 3D-ICs | 107 |

|   | 5.5  | Sumn     | nary                                                             | 109 |

| 6 | Mee  | eting ha | ard latency constraints in best-effort NoCs                      | 111 |

|   | 6.1  | Real-t   | ime synthesis compared to mapping onto regular topologies        | 112 |

|   | 6.2  | Worst    | -case latency models                                             | 114 |

|   | 6.3  | Topol    | ogy design to meet worst-case constraints                        | 116 |

|   | 6.4  | Real-t   | ime network synthesis                                            | 117 |

|   |      | 6.4.1    | Real-time synthesis algorithm                                    | 118 |

|   |      | 6.4.2    | Cost calculation                                                 | 122 |

|   |      | 6.4.3    | Destination contention                                           | 123 |

|   |      | 6.4.4    | Path contention                                                  | 125 |

|   | 6.5  | Exper    | imental results                                                  | 126 |

|   |      | 6.5.1    | Effect on latency                                                | 129 |

|   |      | 6.5.2    | Effect on NoC components                                         | 132 |

|   |      | 6.5.3    | Effect on Power Consumption                                      | 134 |

|   | 6.6  | Sumn     | nary                                                             | 136 |

| 7 | A fa | st simu  | llation model for soft QoS                                       | 137 |

|   | 7.1  | Applio   | cation scenarios for fast simulation and contributions           | 138 |

|   |      | 7.1.1    | Simulations as part of topology synthesis                        | 138 |

|   |      | 7.1.2    | Simulations during design changes                                | 140 |

|   |      | 7.1.3    | Contributions                                                    | 141 |

|   | 7.2  | Partia   | l simulation                                                     | 143 |

|   |      | 7.2.1    | Assumptions                                                      | 145 |

|   |      | 7.2.2    | Pre-characterization phase                                       | 145 |

|   |      | 7.2.3    | Simulation phase                                                 | 148 |

|   |      | 7.2.4    | Traffic injection/ejection models                                | 150 |

|   |      | 7.2.5    | Latency estimation                                               | 153 |

|   | 7.3  | The u    | se of simulation during synthesis                                | 153 |

|   |      | 7.3.1    | Improving the accuracy of the estimated latency                  | 155 |

|   | 7.4  | Evalua   | ation                                                            | 156 |

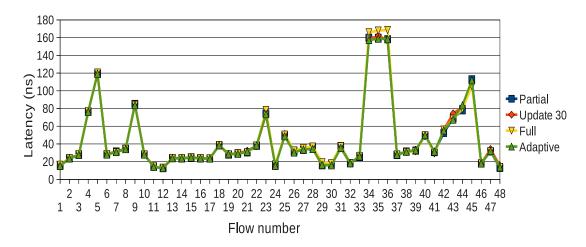

|   |      | 7.4.1    | Speedup                                                          | 156 |

|   |      | 7.4.2    | Accuracy                                                         | 158 |

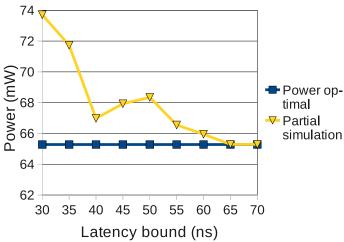

|   |      | 7.4.3    | Synthesis                                                        | 162 |

|   | 7.5  | Sumn     | nary                                                             | 163 |

### **Contents**

| 8  | Effic  | cient n | nemory a   | access                                               | 165 |

|----|--------|---------|------------|------------------------------------------------------|-----|

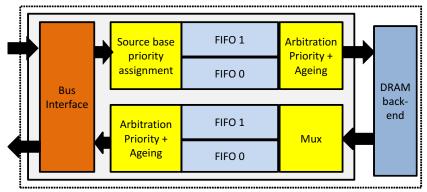

|    | 8.1    | Preve   | nting reg  | ular traffic to be blocked by DRAM traffic           | 169 |

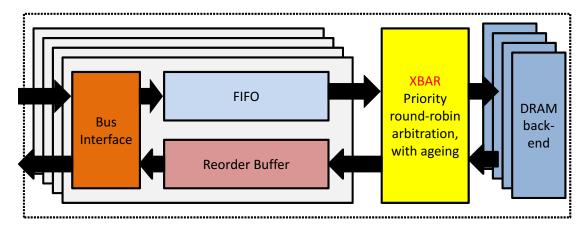

|    |        | 8.1.1   | System     | architecture                                         | 169 |

|    |        |         | 8.1.1.1    | Benchmark                                            | 170 |

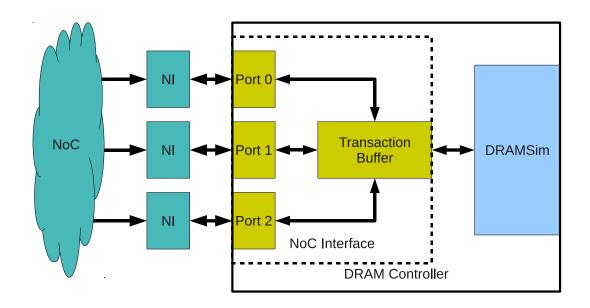

|    |        |         | 8.1.1.2    | Simulation infrastructure                            | 171 |

|    |        | 8.1.2   | Separat    | ed NoC vs. shared NoC                                | 171 |

|    |        |         | 8.1.2.1    | Power analysis                                       | 171 |

|    |        |         | 8.1.2.2    | Performance analysis for non-DRAM flows              | 174 |

|    |        |         | 8.1.2.3    | Performance analysis for DRAM flows                  | 176 |

|    |        |         | 8.1.2.4    | Observations                                         | 177 |

|    |        |         | 8.1.2.5    | DRAM buffer size impact on non DRAM flows            | 177 |

|    |        |         | 8.1.2.6    | Port count                                           | 178 |

|    |        | 8.1.3   | Networl    | k optimization for heterogeneous cores               | 178 |

|    |        |         | 8.1.3.1    | Proposed size converter architecture                 | 179 |

|    |        |         | 8.1.3.2    | Optimized NoC                                        | 180 |

|    | 8.2    | Acces   | sing mul   | tiple DRAM channels                                  | 180 |

|    |        | 8.2.1   | NoC and    | d controller architectures for multi-channel DRAM $$ | 180 |

|    |        |         | 8.2.1.1    | Distributed controller                               | 181 |

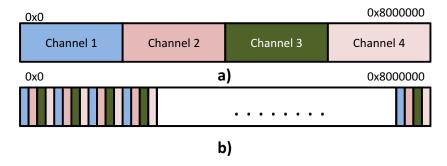

|    |        |         | 8.2.1.2    | Centralized controller with interleaving             | 182 |

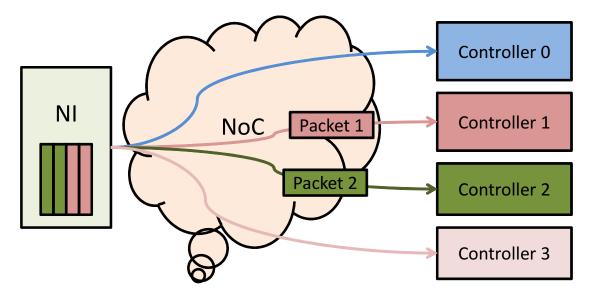

|    |        |         | 8.2.1.3    | Distributed controller with interleaving             | 184 |

|    |        |         | 8.2.1.4    | Simple reorder-buffer implementation                 | 185 |

|    |        | 8.2.2   | Explora    | tion environment                                     | 186 |

|    |        |         | 8.2.2.1    | Traffic generators and NIs                           | 187 |

|    |        |         | 8.2.2.2    | Benchmark and use-cases                              | 189 |

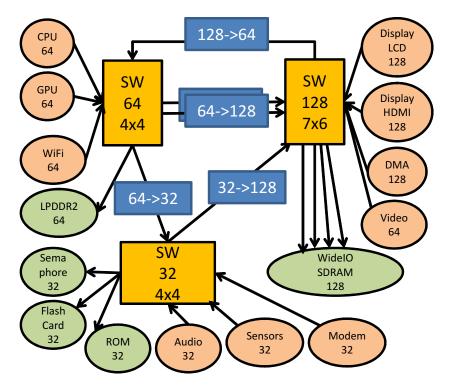

|    |        |         | 8.2.2.3    | Topology                                             | 191 |

|    |        | 8.2.3   | Experin    | nental results                                       | 192 |

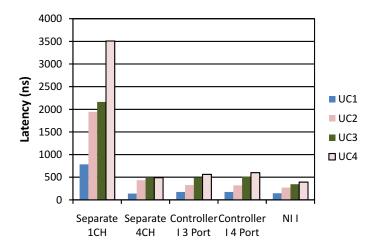

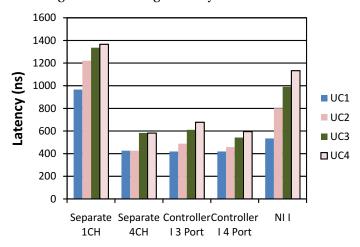

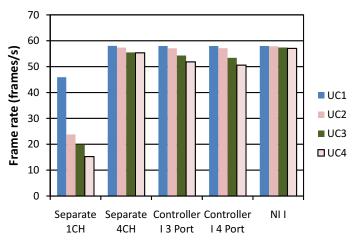

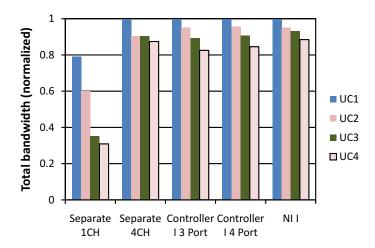

|    |        |         | 8.2.3.1    | Throughput oriented communication                    | 193 |

|    |        |         | 8.2.3.2    | Bandwidth analysis                                   | 197 |

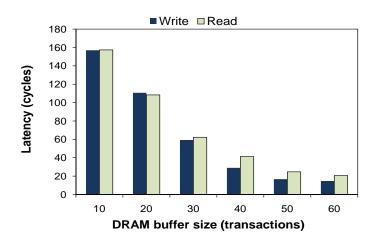

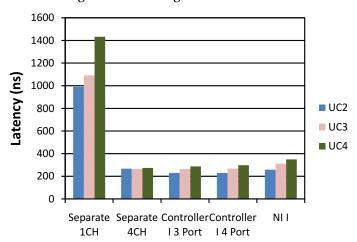

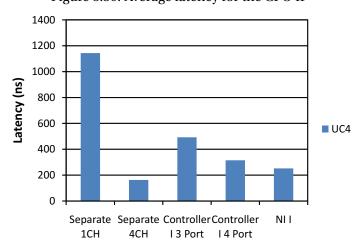

|    |        |         | 8.2.3.3    | Latency sensitive communication                      |     |

|    | 8.3    | Sumn    | nary       |                                                      | 199 |

| 9  | Con    | clusio  | ns and fu  | iture directions                                     | 201 |

|    | 9.1    | Sumn    | nary of th | ne thesis                                            | 201 |

|    | 9.2    | Sumn    | nary of th | ne main contributions                                | 202 |

|    | 9.3    | Futur   | e directio | ons                                                  | 202 |

| Bi | bliog  | raphy   |            |                                                      | 221 |

| Cı | arrici | ulum V  | 'itae      |                                                      | 223 |

# **List of Figures**

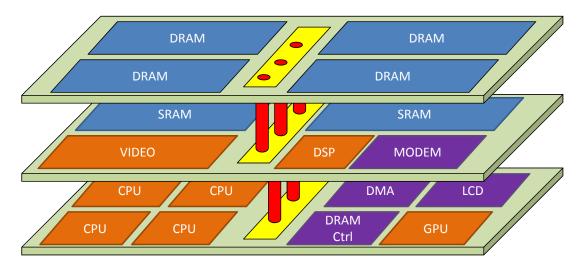

| 1.1  | Example of a 3D MPSoC with three stacked layers                          | 2  |

|------|--------------------------------------------------------------------------|----|

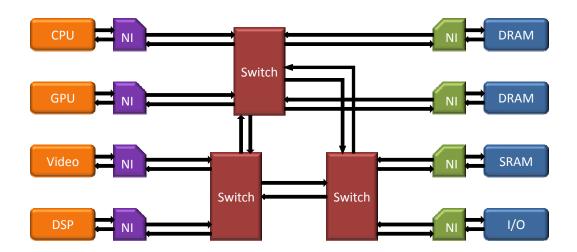

| 1.2  | Example of a topology showing: IP cores, NIs, Switches and Links         | 4  |

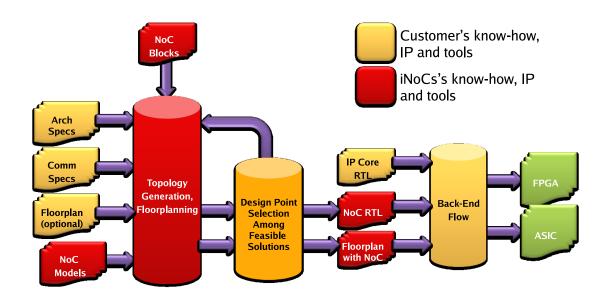

| 1.3  | iNoCs NoC design flow [73]                                               | 9  |

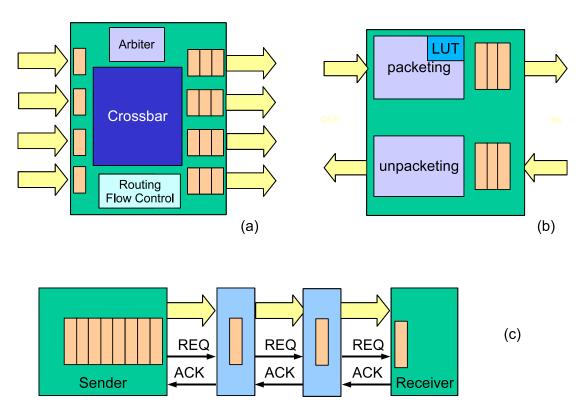

| 2.1  | ×pipes building blocks: (a) switch, (b) NI, (c) link                     | 16 |

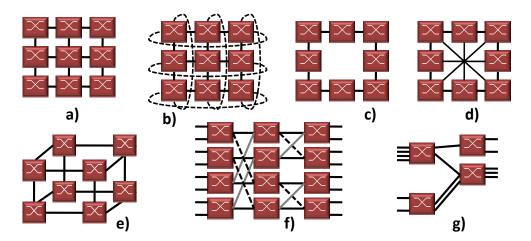

| 2.2  | Examples of topologies: a) mesh, b) torus, c) ring, d) spidergon, e) hy- |    |

|      | percube f) butterfly and g) application specific                         | 18 |

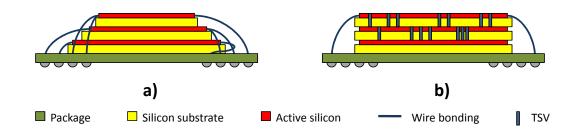

| 2.3  | Example of: a) System-in-Package technology and b) 3D-stacking with      |    |

|      | TSV connectivity                                                         | 22 |

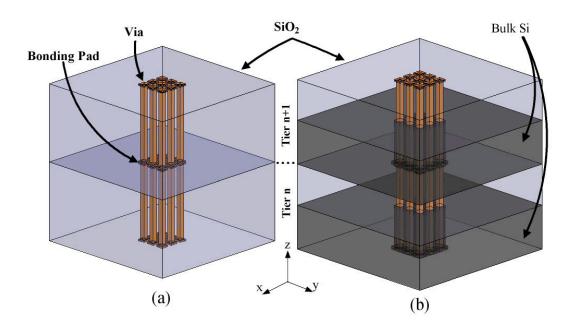

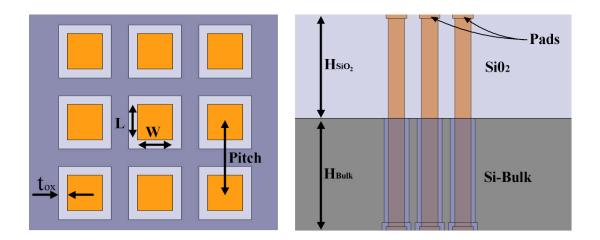

| 2.4  | An example set of 9 vertical links [72]                                  | 23 |

| 2.5  | 3D bundle cross-section [72]                                             | 24 |

| 2.6  | Floorplan example of an SoC with 6 clock domains                         | 26 |

| 2.7  | Intel Single Chip Cloud Computer [67]                                    | 30 |

| 2.8  | Texas Instruments OMAP 5 application platform [74]                       | 30 |

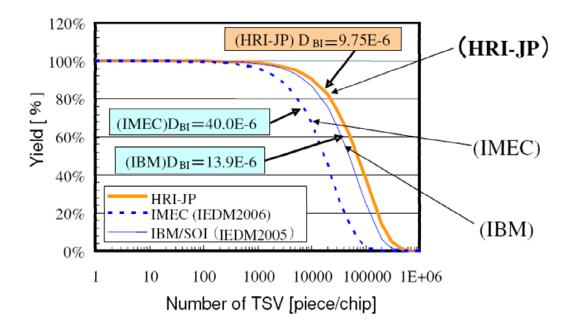

| 3.1  | Yield vs. TSV count [113]                                                | 36 |

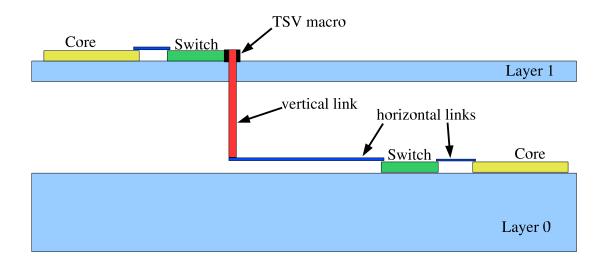

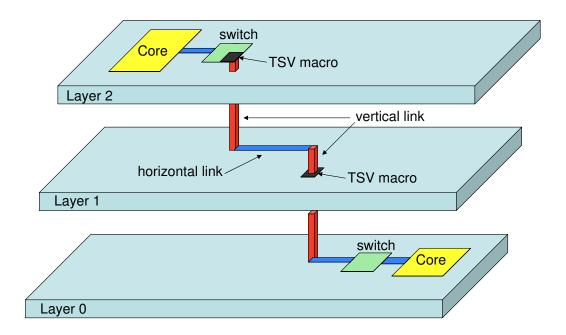

| 3.2  | Example vertical link                                                    | 38 |

| 3.3  | Example vertical link                                                    | 39 |

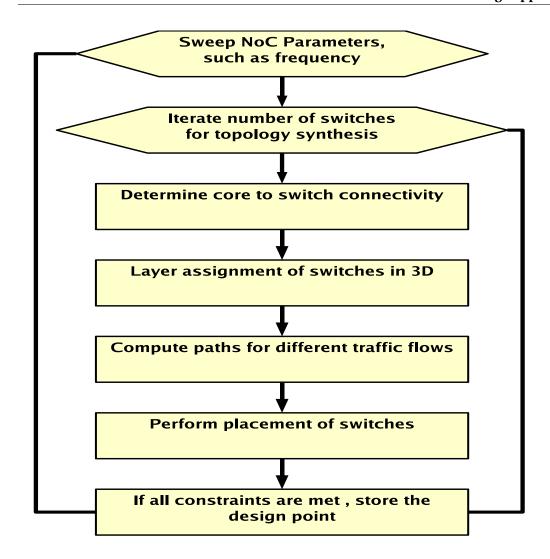

| 3.4  | Algorithm steps                                                          | 41 |

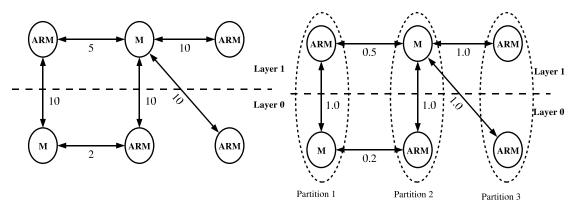

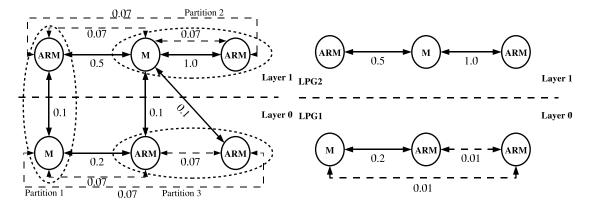

| 3.5  | Communication graph with bandwidth demands on the edges                  | 43 |

| 3.6  | PG and the min-cut partitions                                            | 43 |

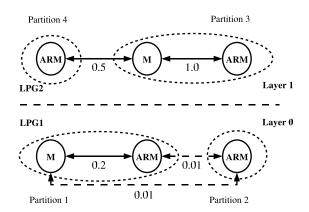

| 3.7  | SPG and the min-cut partitions                                           | 43 |

| 3.8  | LPGs for two layers                                                      | 43 |

| 3.9  | Two min-cut partitions of LPGs                                           | 45 |

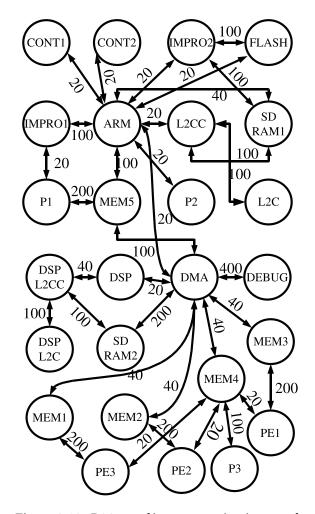

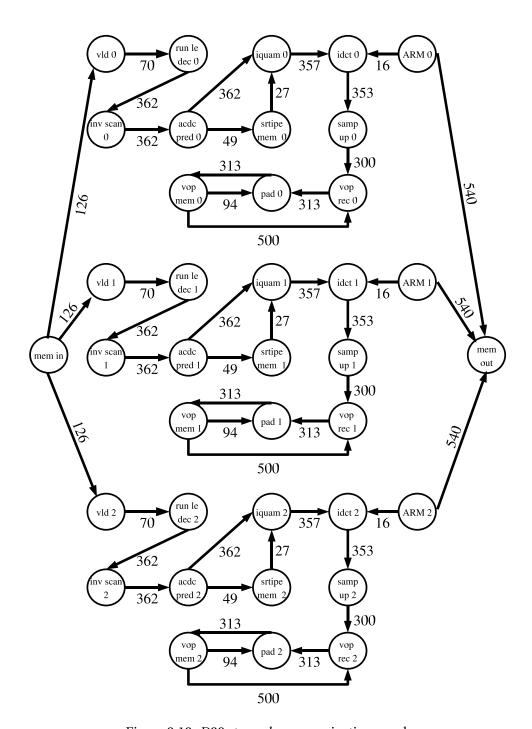

| 3.10 | <i>D</i> 26_ <i>media</i> communication graph                            | 53 |

| 3.11 | $D36\_4$ communication graph                                             | 53 |

| 3.12 | $D38\_tvopd$ communication graph                                         | 54 |

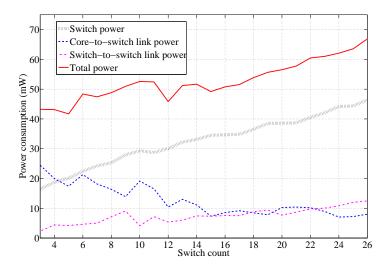

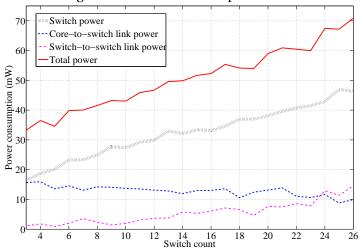

| 3.13 | Power consumption in 2D                                                  | 56 |

| 3.14 | Power consumption in 3D                                                  | 56 |

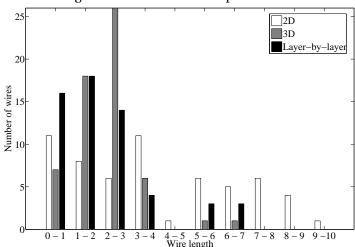

| 3.15 | Wire length distributions                                                | 56 |

| 3.16 | Most power-efficient topology ( <i>Phase</i> 1)                          | 57 |

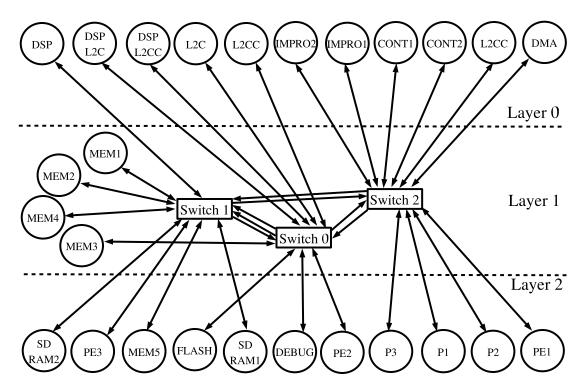

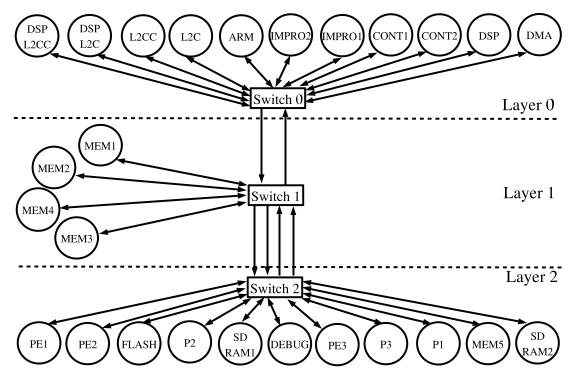

| 3.17 | Most power-efficient topology layer-by-layer ( <i>Phase</i> 2)           | 57 |

## **List of Figures**

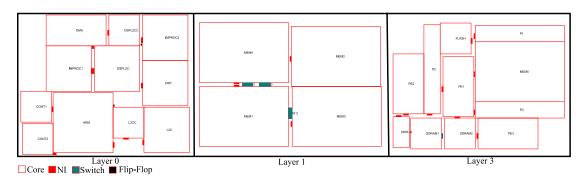

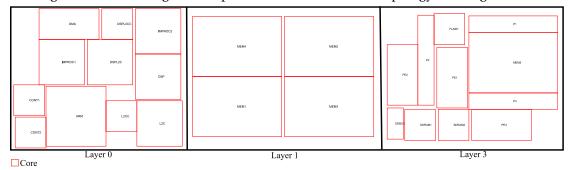

| 3.18 Resulting 3D floorplan with switches for the topology from Figure 3.16 | 58       |

|-----------------------------------------------------------------------------|----------|

| 3.19 Initial positions for $D26\_media$                                     | 58       |

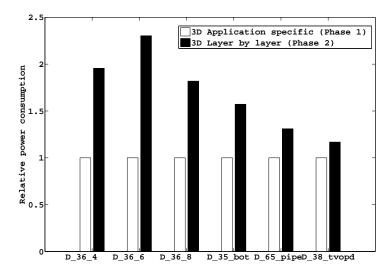

| 3.20 Comparison with layer-by-layer                                         | 59       |

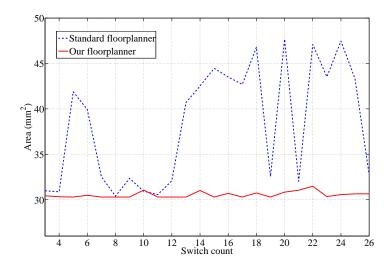

| 3.21 Area plot for different switch counts                                  | 61       |

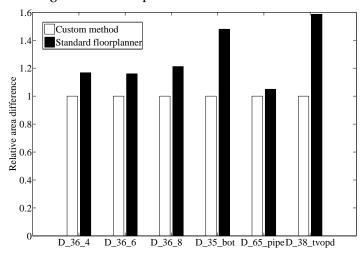

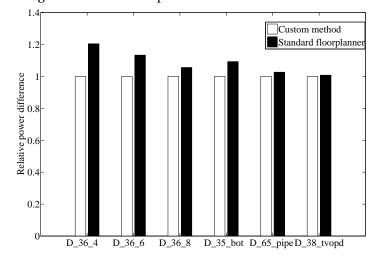

| 3.22 Area comparison for different benchmarks                               | 61       |

| 3.23 Power comparison for different benchmarks                              | 61       |

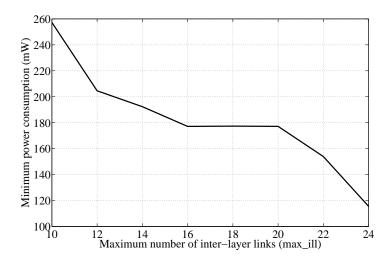

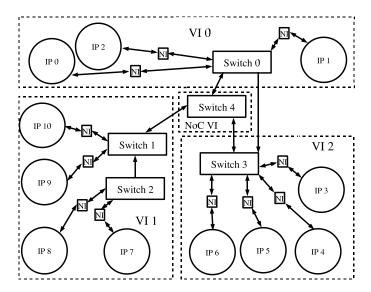

| 3.24 Impact of $max_ill$ on power                                           | 63       |

| 3.25 Impact of $max_ill$ on latency                                         | 63       |

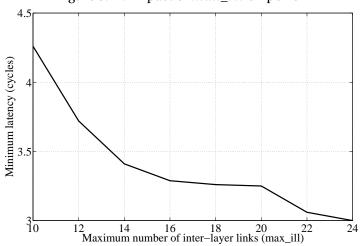

| 3.26 Comparisons with mesh                                                  | 63       |

|                                                                             | 00       |

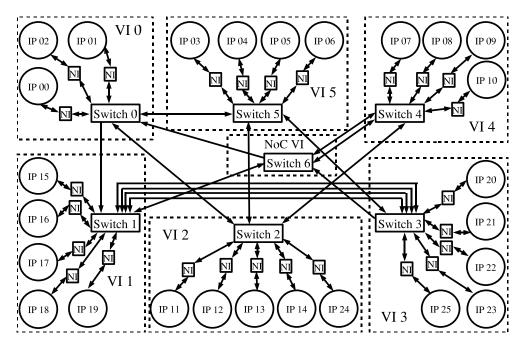

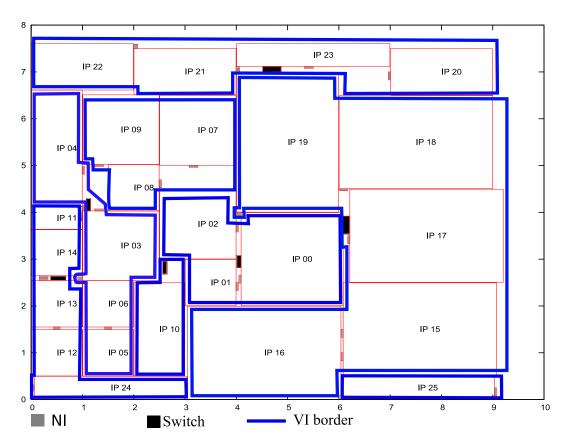

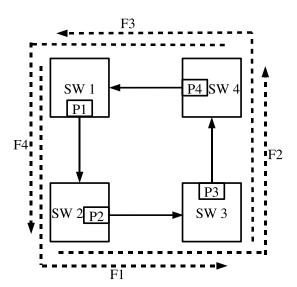

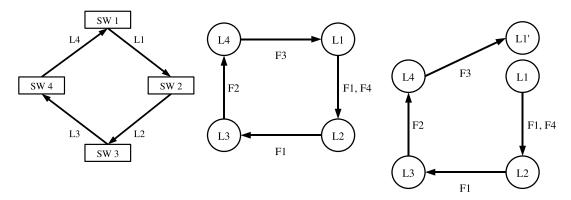

| 1 1                                                                         | 69<br>70 |

| 1                                                                           | 70<br>70 |

| 1                                                                           | 78<br>70 |

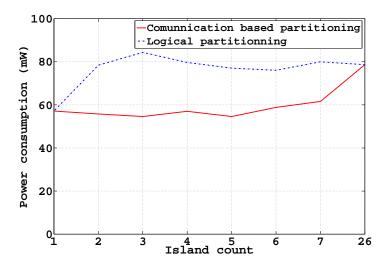

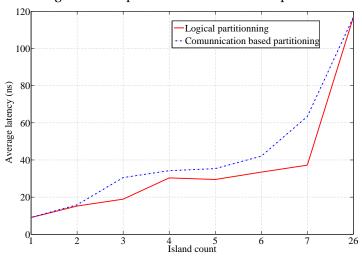

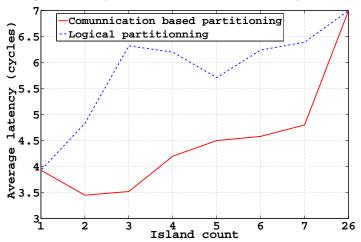

| ı                                                                           | 78<br>70 |

| r                                                                           | 78       |

| 1 07 1                                                                      | 80       |

| 1                                                                           | 80       |

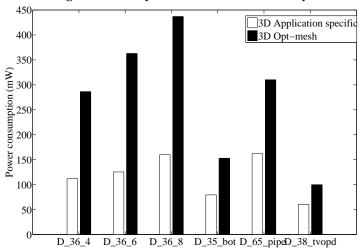

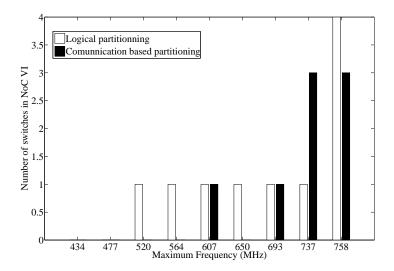

| 1 1 3                                                                       | 82       |

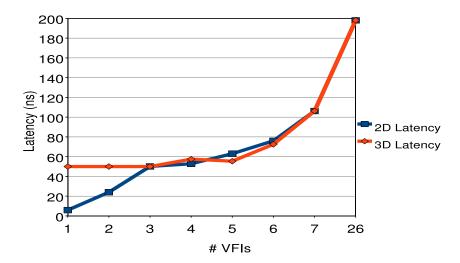

| o .                                                                         | 84       |

| 8                                                                           | 84       |

| o o                                                                         | 84       |

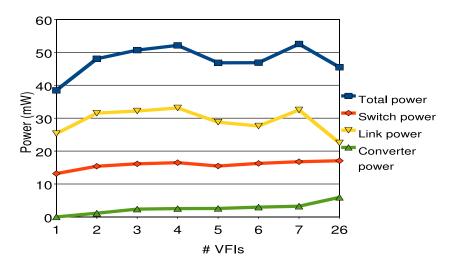

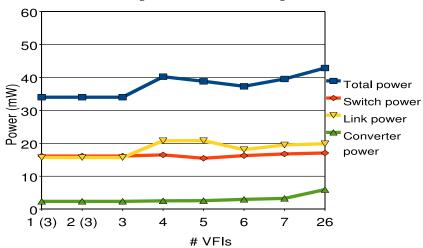

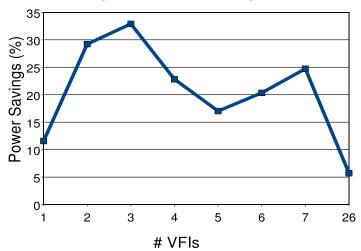

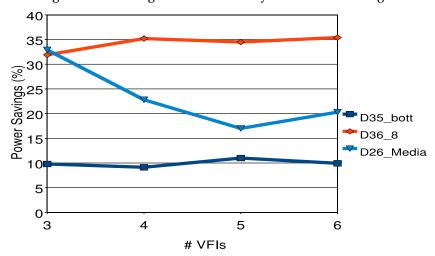

| 3                                                                           | 87       |

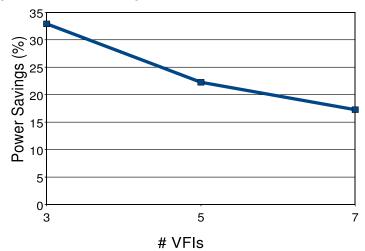

| O                                                                           | 87       |

| 4.14 Power savings of 3D vs. 2D for different core areas                    | 87       |

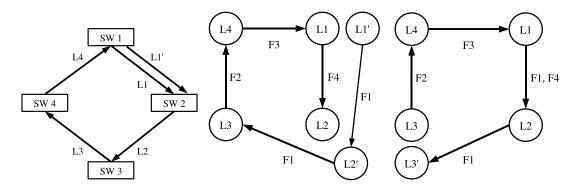

| 5.1 Deadlock example                                                        | 94       |

|                                                                             | 95       |

| 1 07 1                                                                      | 95       |

| -                                                                           | 95       |

|                                                                             | 96       |

|                                                                             | 96       |

|                                                                             | 96       |

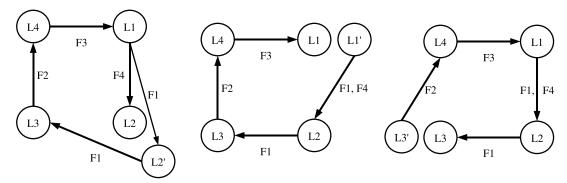

|                                                                             | 99       |

|                                                                             | 99       |

|                                                                             | 99       |

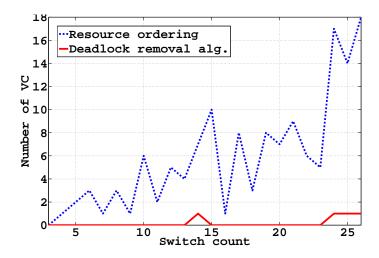

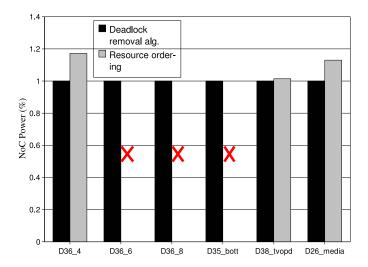

| _                                                                           | 04       |

|                                                                             | 04       |

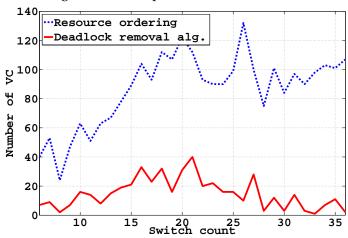

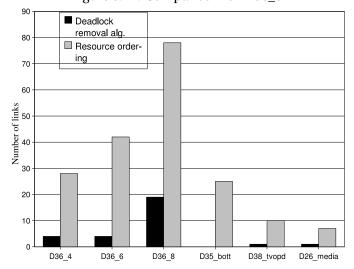

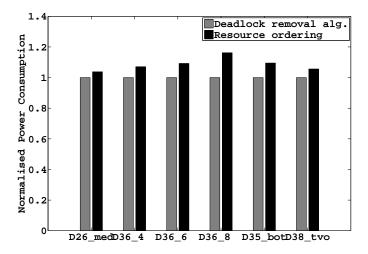

| <del>-</del>                                                                | 04       |

|                                                                             | 06       |

| _                                                                           | .06      |

|                                                                             | .06      |

| <u>.</u>                                                                    |          |

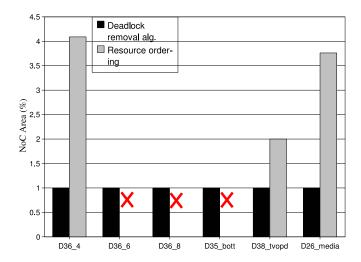

| 5.17       | Minimum number of TSVs for topologies to be synthesized with the two methods                                                                             | 108  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

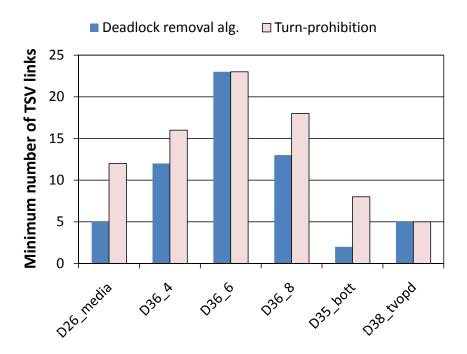

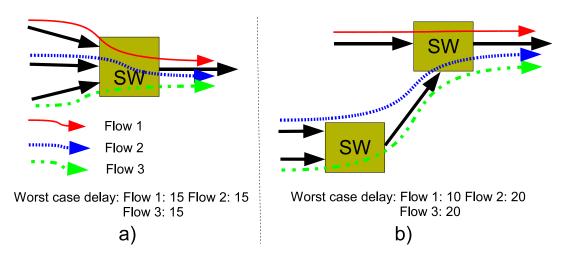

| 6.1<br>6.2 | Algorithm flow: a) Task mapping with QoS, b) Real-time topology synthesis Example of topologies with worst case delays: a) single switch (crossbar);     | s113 |

| 0.2        | b) multi-switch                                                                                                                                          | 118  |

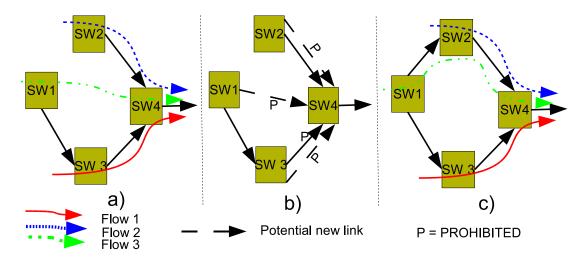

| 6.3        | Destination contention example: a) initial topology; b) link status anno-                                                                                | 110  |

|            | tation; c)final topology                                                                                                                                 | 124  |

| 6.4        | Path contention example: a) initial topology; b) link status annotation;                                                                                 |      |

|            | c)final topology                                                                                                                                         | 125  |

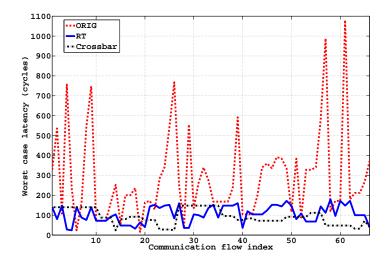

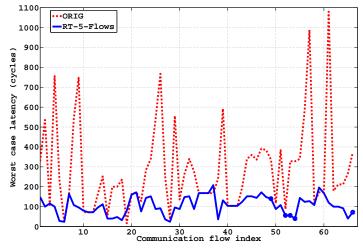

| 6.5        | Worst case latency on each flow                                                                                                                          | 127  |

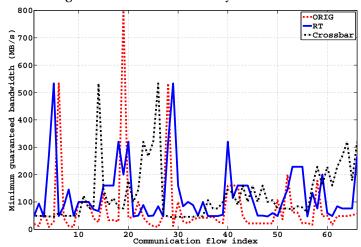

| 6.6        | Minimum guaranteed bandwidth for each flow                                                                                                               | 127  |

| 6.7        | Worst case latency when only 5 flows are constrained                                                                                                     | 127  |

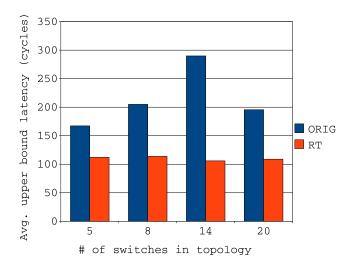

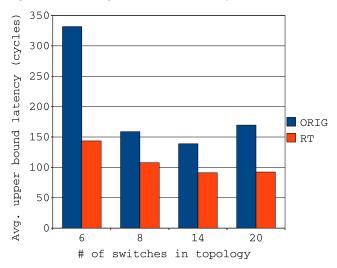

| 6.8        | Average worst case latency for <i>D26_media</i>                                                                                                          | 128  |

| 6.9        | Average worst case latency for $D36_4$                                                                                                                   | 128  |

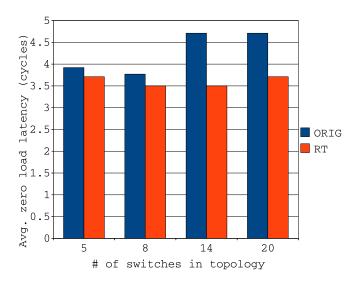

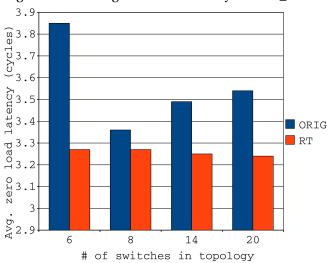

| 6.10       | Average zero load latency for <i>D26_media</i>                                                                                                           | 129  |

|            | Average zero load latency for $D36\_4$                                                                                                                   | 129  |

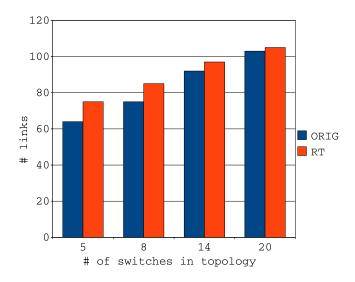

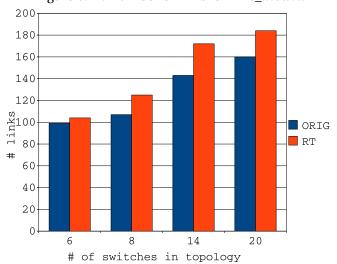

| 6.12       | Number of links for <i>D26_media</i>                                                                                                                     | 131  |

| 6.13       | Number of links for $D36_4$                                                                                                                              | 131  |

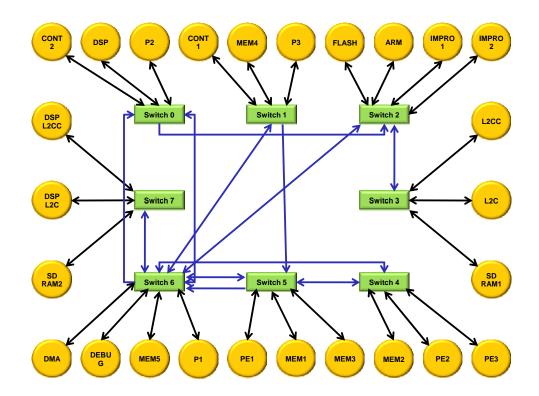

| 6.14       | Topology with 8 switches for <i>D26_media</i> designed with the original                                                                                 |      |

|            | algorithm                                                                                                                                                | 133  |

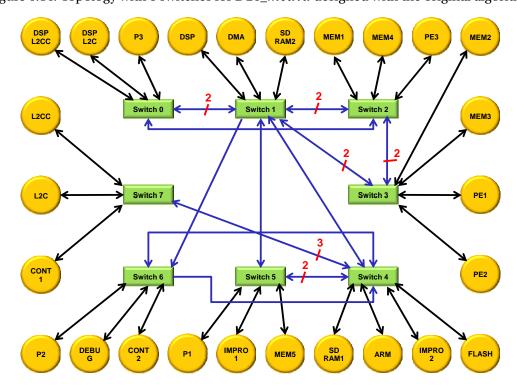

| 6.15       | Topology with 8 switches for <i>D26_media</i> designed with the real-time                                                                                |      |

|            | algorithm                                                                                                                                                | 133  |

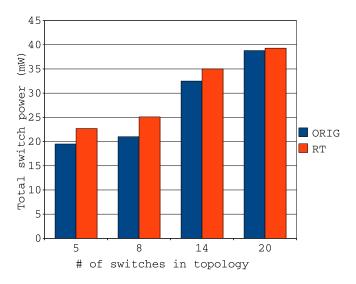

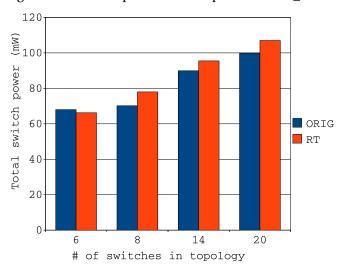

| 6.16       | Switch power consumption for <i>D26_media</i>                                                                                                            | 134  |

| 6.17       | Switch power consumption for $D36\_4$                                                                                                                    | 134  |

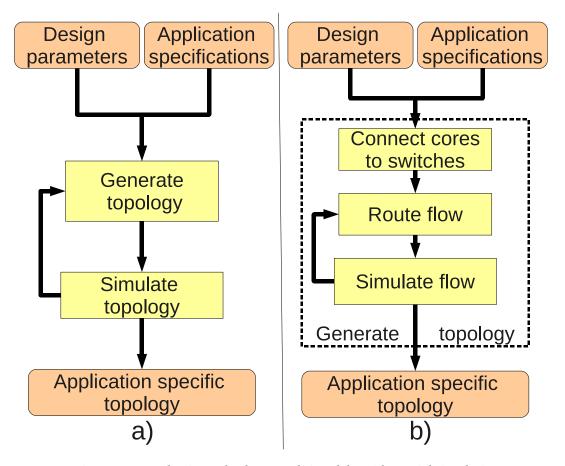

| 7 1        | Crosthogic mothodo, a) traditional h) with partial simulation                                                                                            | 120  |

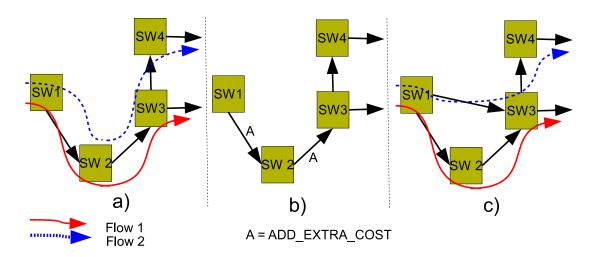

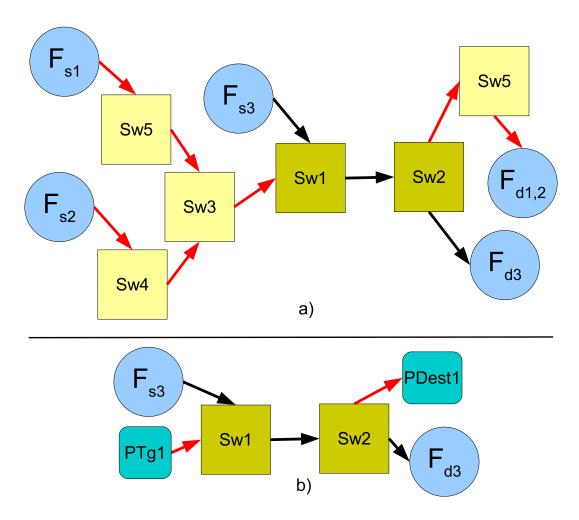

| 7.1        | Synthesis methods: a) traditional, b) with partial simulation Example of: a) topology where a new flow has been added from $F_{s3}$ to                   | 139  |

| 7.2        | Example of. a) topology where a flew flow has been added from $F_{s3}$ to $F_{d3}$ depicted by the black arrow and the state of the previous topology is |      |

|            | $T_{d3}$ depicted by the black arrow and the state of the previous topology is know depicted by the red arrows; b) partial simulation setup for the new  |      |

|            | flow with the corresponding partial traffic generators and destinations                                                                                  |      |

|            | that replace the rest of the topology                                                                                                                    | 141  |

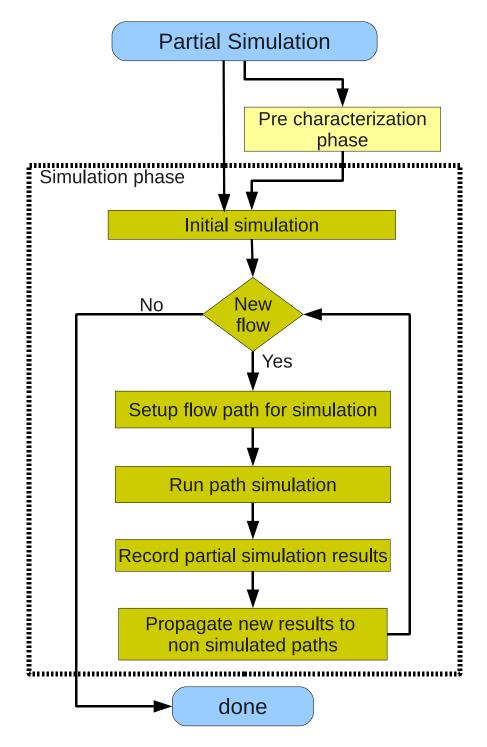

| 7.3        | Partial simulation steps                                                                                                                                 | 144  |

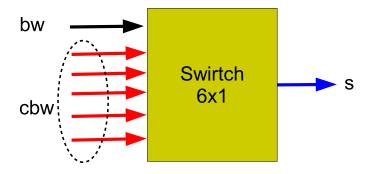

| 7.4        | Single switch model                                                                                                                                      | 146  |

| 7.5        | Traffic characterization                                                                                                                                 | 151  |

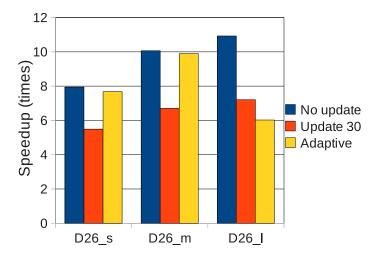

| 7.6        | D26_media speedup                                                                                                                                        | 157  |

| 7.7        | D36_4 speedup                                                                                                                                            | 157  |

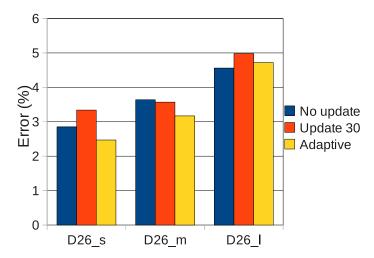

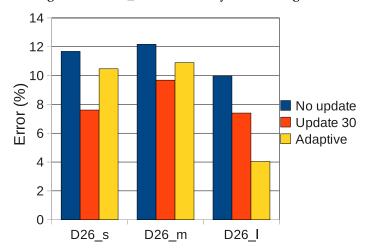

| 7.8        | D26_media flow-by-flow average error                                                                                                                     | 158  |

| 7.9        | D26_media average error at the end                                                                                                                       | 158  |

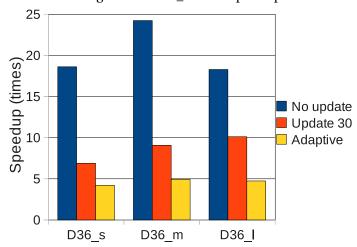

|            | D36_4 flow-by-flow average error                                                                                                                         | 159  |

|            | D36_4 average error at the end                                                                                                                           | 159  |

|            |                                                                                                                                                          |      |

## **List of Figures**

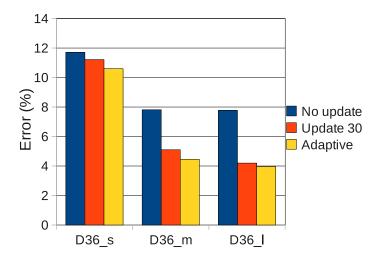

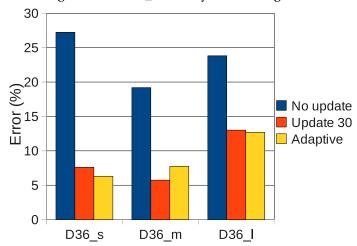

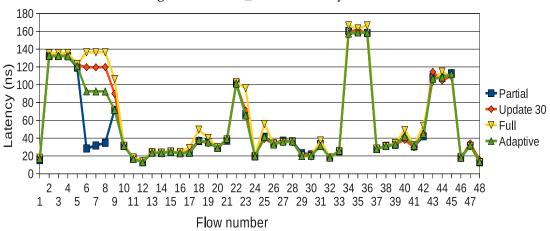

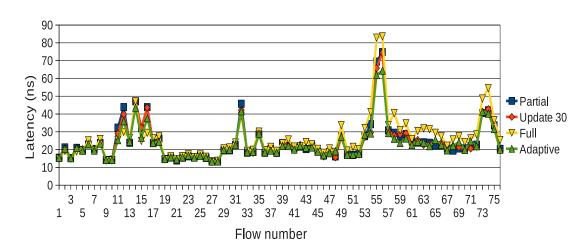

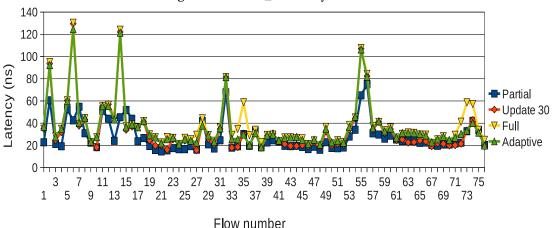

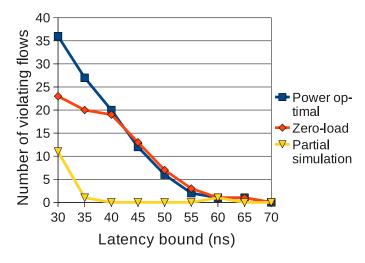

| 7.12 <i>D</i> 26_ <i>media</i> flow-by-flow error                                                 | 160 |

|---------------------------------------------------------------------------------------------------|-----|

|                                                                                                   | 160 |

| 7.14 <i>D</i> 36_4 flow-by-flow error                                                             | 161 |

|                                                                                                   | 161 |

| 7.16 <i>D</i> 26_ <i>media</i> synthesis evaluation                                               | 162 |

|                                                                                                   | 162 |

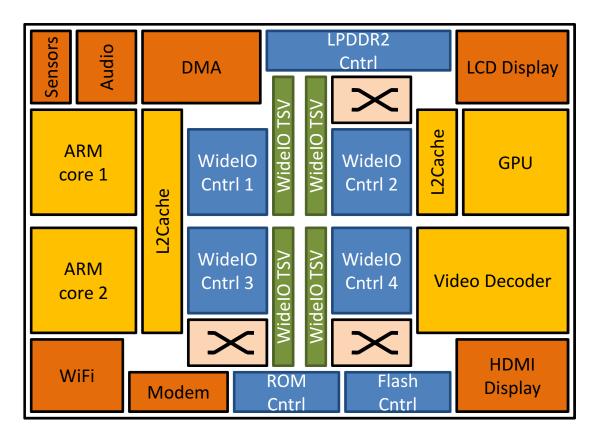

| 8.1 Example of SoC floorplan with WideIO TSV interfaces                                           | 168 |

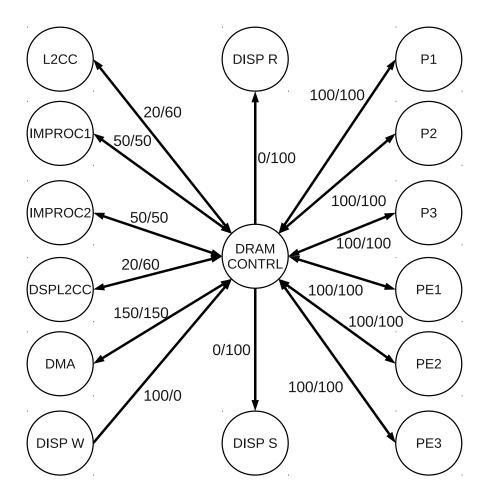

| 8.2 Communication specifications to DRAM                                                          | 170 |

| 8.3 Example of DRAM controller connection                                                         | 172 |

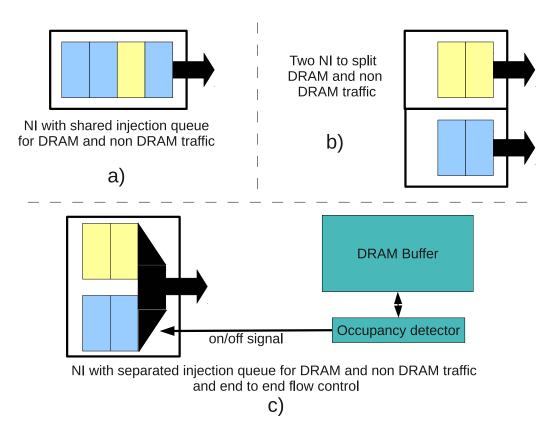

| 8.4 NI injection queues: a) <i>shared</i> b) <i>split</i> and c) <i>end-to-end flow control</i> . | 172 |

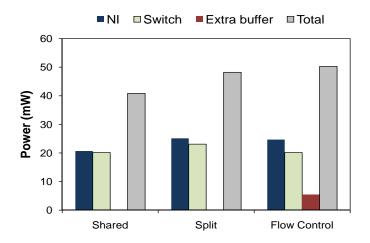

| 8.5 Power consumption for shared and separated NoCs                                               | 173 |

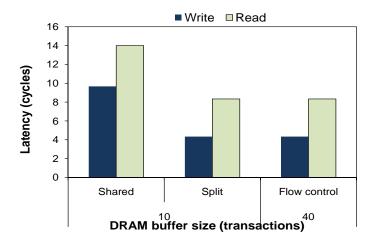

| 8.6 Average latency for non DRAM flows                                                            | 173 |

| 8.7 Maximum latency for non DRAM flows                                                            | 173 |

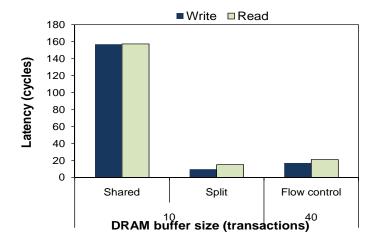

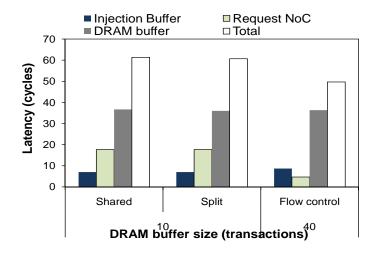

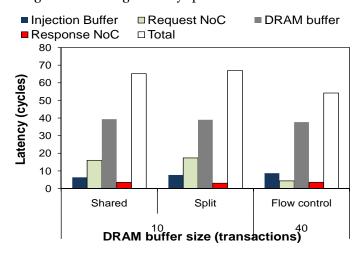

| 8.8 Average latency split for write DRAM flows                                                    | 175 |

| 8.9 Average latency split for read DRAM flows                                                     | 175 |

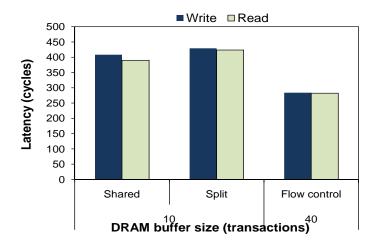

| 8.10 Maximum latency for DRAM flows                                                               | 175 |

| 8.11 Average latency for non DRAM flows in shared NoC                                             | 176 |

| 8.12 Maximum latency for non DRAM flows in shared NoC                                             | 176 |

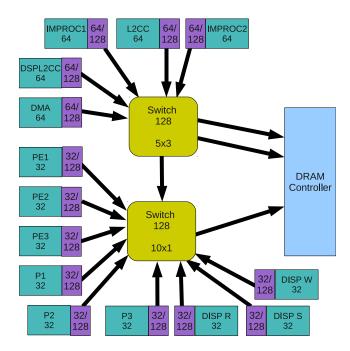

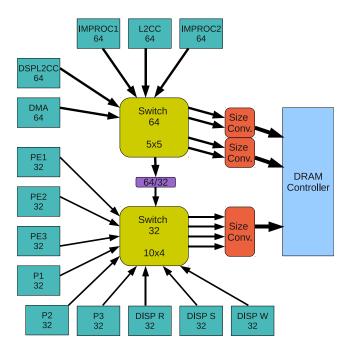

| 8.13 Original topology                                                                            | 178 |

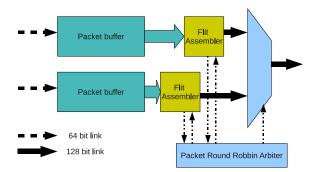

| 8.14 Data size converter architecture                                                             | 179 |

| 8.15 Optimized topology                                                                           | 180 |

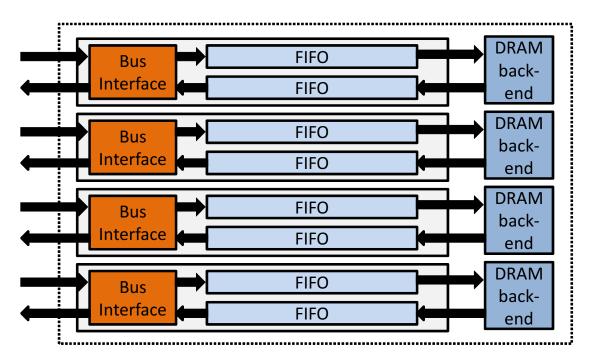

| 8.16 Distributed DRAM controller with 4 separate channels                                         | 182 |

| 8.17 Centralized DRAM controller with interleaving at the controller side                         | 183 |

| 8.18 Example of a) partitioned- and b) interleaved address space                                  | 183 |

| 8.19 Example of distributed interleaving where the NI sends out a 4 beat                          |     |

| burst transaction in 2 packets on different routes                                                | 185 |

| 8.20 DRAM controller port with priority                                                           | 185 |

| 8.21 Simple reorder buffer schematic                                                              | 186 |

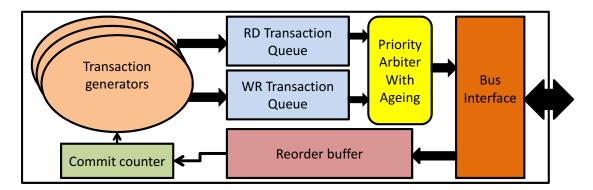

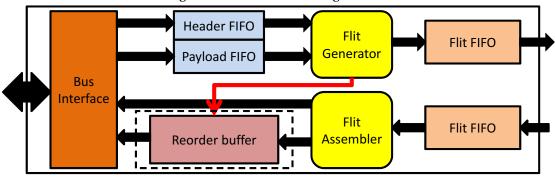

| 8.22 Initiator traffic generator                                                                  | 187 |

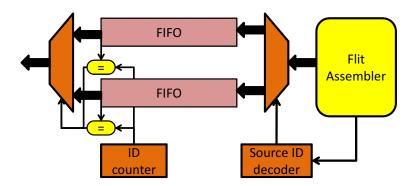

| 8.23 Initiator network interface                                                                  | 187 |

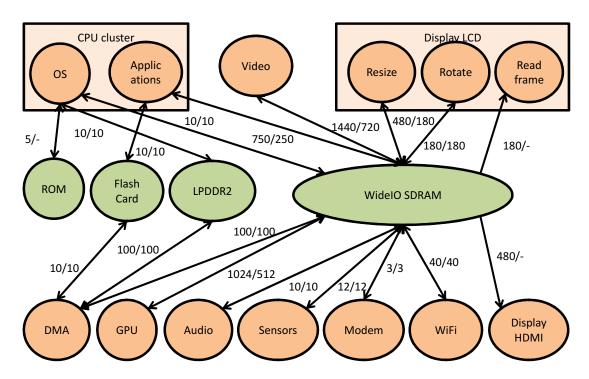

| 8.24 Benchmark communication graph                                                                | 190 |

| 8.25 Topology                                                                                     | 191 |

| 8.26 Average latency for the Video IP                                                             | 195 |

| 8.27 Average latency for the HDMI IP                                                              | 195 |

| 8.28 Average frame-rate                                                                           | 195 |

| _                                                                                                 | 198 |

|                                                                                                   | 198 |

|                                                                                                   | 198 |

# **List of Tables**

| 3.1 | 2D vs 3D NoC Comparison                                            | 60  |

|-----|--------------------------------------------------------------------|-----|

|     | NoC component figures                                              |     |

|     | Cost table in forward direction                                    |     |

|     |                                                                    |     |

|     | Results summary                                                    |     |

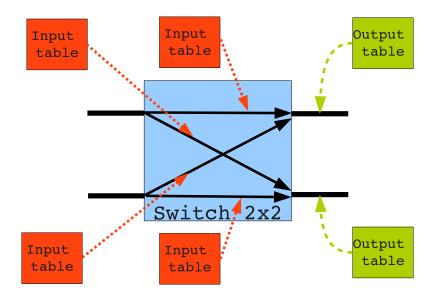

|     | Input table data structure                                         |     |

| 8.1 | Average and maximum read latency from DRAM for different number of |     |

|     | ports                                                              | 177 |

| 8.2 | Description of the use-cases                                       | 190 |

| 8.3 | Simulation parameters for the ITGens                               | 194 |

# 1 Introduction

The field of embedded and even general purpose computing has evolved considerably as it is driven by increasingly more demanding application requirements. A look at todays applications for consumer electronics shows a great demand for computation power and high flexibility, but with great constraints on the power consumption and device size. With the introduction of *High Definition (HD)* television, video decoding alone, requires 70 to 80 *Giga Instructions Per Second (GIPS)* [33]. However TV platforms today provide much more functionality than just simple video decoding which can range from browsing the Internet or running voice over IP applications, to fetching the video stream from WiFi enabled storage server. Similarly mobile communication devices have evolved from simple phones to full-fledged computation platforms with multimedia capabilities, high-bandwidth data communication connections and even navigation capabilities. Future applications like 3D-enabled displays and high bandwidth wireless communication like 4G will increase the requirements for computation even further.

Traditionally computation power was increased by raising the operating frequency as transistors in new technology nodes were faster. The power consumption was managed by scaling the supply voltage. As supply voltage scaling is leveling off in new technology nodes, computation power can only be increased at manageable power densities by exploiting the application-level parallelism. Therefore we see a design paradigm shift from single processor systems to *Multi Processor Systems-on-Chip (MPSoCs)*. MPSoCs are communication centric as the processors communicate over a global interconnect in order to cooperatively complete the parallel application. As such the MPSoC performance is directly influenced by the efficiency of the communication infrastructure. Recent MPSoCs prototype chips [162], [166], [67] and even products [164] have adopted *Networks-on-Chip (NoCs)* as the global on-chip interconnect. NoCs originate from general networks, but have been adapted to take advantage of the locality and silicon technology. NoCs have been proposed as a solution to

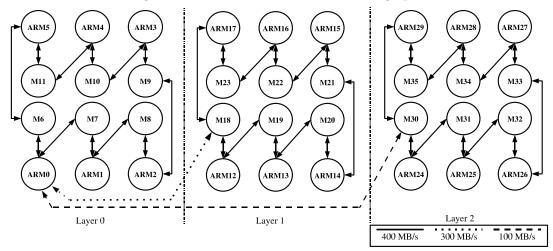

Figure 1.1: Example of a 3D MPSoC with three stacked layers

the interconnect design challenge due to predictability of design and the intrinsic scalability of the networks.

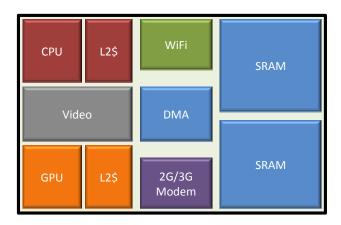

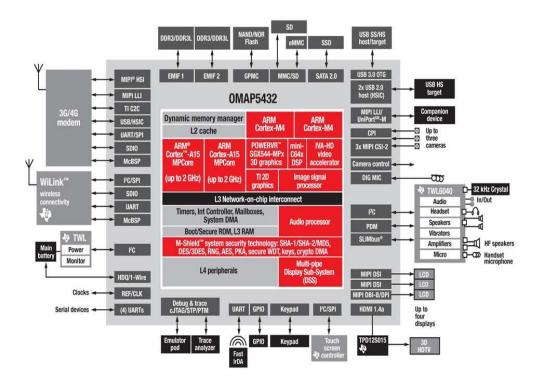

In power-constrained systems, like mobile platforms where increasing the autonomy is an important design challenge we see that programmability is traded for efficiency. Therefore the SoCs are customized for the required applications and many of the cores specialized to provide a specific functionality. The global interconnect can also be tailored according to the demands of the application. Customizing the interconnect is a must, as it can be responsible for as 30% of the SoC power consumption [162]. Already in the new-generation mobile platform chips [74] we can find NoCs as the global interconnect, not only for their scalability, but also because their modularity provides great opportunities for customization.

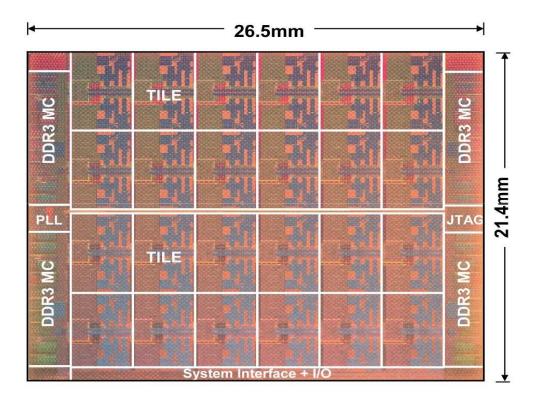

CMOS scaling is projected to continue at least until the end of this decade [14]. However the cost of designing and manufacturing integrated circuits in the new technology nodes is becoming prohibitive even for high-end systems. *Three Dimensional Integration* is emerging as a promising alternative for increasing the number of on-chip transistors, by stacking multiple dies in the same package. Unlike existing *Systems-on-Package*, *Three Dimensional Integrated Circuits* (3D-ICs) provide less restrictive vertical connectivity in the form of *Through Silicon Vias (TSVs)*. An example of a 3D SoC is shown in Figure 1.1. As it will be possible to integrate more cores in 3D-ICs to provide increased functionality, Three Dimensional Integration provides further challenges and opportunities to design an optimized on-chip interconnect. However to be able to explore all the degrees of freedom when customizing the interconnect and to improve the design productivity, tools are needed to perform architectural level exploration as well as synthesis.

### 1.1 Network-on-Chip a structured interconnect for Systems-on-Chip

Early MPSoC chips with few cores used a single bus for on-chip communication. However as the bus is a shared medium of communication, it cannot scale as the number of integrated cores is increased. As a consequence more complex design started using hierarchies of shared busses to exploit the parallelism in communication and to reduce collisions among cores that desire to communicate at the same time. As wire delay increases in new technology nodes due to the increased coupling capacity caused by the tall aspect ratio of the wires [5], [64], busses are becoming unpredictable from the timing point of view. The timing of the bus can only be estimated correctly after the place and route and this increases the time for achieving design closure. The introduction of crossbars in designs solves the problem of parallel access to different cores and also eliminates the long wires form the buses. Crossbar based designs do not scale though, as the crossbar is a centralized device. To solve both the problem of predictability as well as the scalability of the interconnect infrastructure, a networkbased interconnect inspired from general networks designed for the super computes has been proposed as early as the year 2000 [60]. Many of the current high-end SoCs employ NoC as the global interconnect [74], [67] and even products [164].

The use of packet-switched networks to interconnect components in a computing systems has been proposed by Seitz and co-workers [152]. Networks have then been studied and used in multi processor super computes and an overview of the interconnect networks is presented in [41]. As MPSoCs became more complex integrating more cores on the same chip the use of *Networks-on-Chip (NoCs)* was first advocated by Greiner in [60] and within the Scalable Programmable Integrated Network (SPIN) project [2] and elaborated in its various facets by Benini et al. [23], [42], and Dally et al. [40] in the early part of the previous decade.

One of the most important characteristic on NoC is that they are modular. An example showing the NoC components is presented in Figure 1.2. The three basic modules to build an NoC are:

- Network Interfaces (NIs)

- Switches

- Links

Most components of the SoCs are *Intellectual Property* (IP) cores which use standard bus-like communication protocols. The role of the Network Interface is to convert the bus protocol used by the IP cores to the network protocol used by the switches. One NI is needed to connect each IP core to the NoC. NIs convert the transaction

Figure 1.2: Example of a topology showing: IP cores, NIs, Switches and Links

into packets that are then sent though the network and then reassembled back into transactions by the destination NI. Packets usually contain more information bits than the number of wires that connect the NoC components. So the packets are serialized into a sequence of *FLow control unITS (flits)* before transmission, to decrease the physical wire parallelism requirements. Even though there are no standards NoC protocols for intra-network communication and are implementation dependent, most NI support standard protocols (e.g., OCP, AHB, AXI, Wishbone, OPB, PLB) toward the IP cores. Existing IPs to be connected easily to the network without requiring any modifications. The NI translation layer provides greater flexibility in connecting IPs using different protocols to the same system interconnect.

Switches provide the main infrastructure for the NoC in order to route packets from source to destination. Switches can have any number of inputs and outputs and a crossbar that allows for arbitrary connectivity between several inputs and several outputs. Of course the number of inputs and outputs is restricted by the desired operation frequency and the available area. Switches can be connected in different topologies in order to provide connectivity for many IP cores. Apart from the crossbar switches also provide buffering resources to lower congestion and improve performance. The buffers could be placed at the input ports (input-queued router), output ports (output-queued router) or at both places. In many NoCs with regular topologies where one or few cores are connected to a switch, the functionality of the NI is integrated in the switch itself. In such topologies it is common to call as a *router* the combination of the NI with the switch.

Links are used to connect NI to switches as well as provide the switch to switch connectivity. As links are point to point connections between NoC components their timing characteristics are more predictable than those of busses. Links can represent more than just groups of parallel physical wires as they can provide pipelining in order to achieve the required timing and provide full throughput. Other components can also be added like frequency converters or size converters to further increase the flexibility of designing the interconnect in SoCs use multiple clock signals.

To summarize the NoC provide the following main advantages over bus-based design:

- Scalability to accommodate more bandwidth, more switches can be added to increase the size of the topology.

- Predictability as switches segment the wires and the connections are point to point, the timing characteristics can be estimated. Pipelining of the long links can be performed in order to preserve timing and throughput.

- Flexibility the modularity of NoCs enables for the design of arbitrary topologies that can be customized to application requirements. Frequency and size converters can be seamlessly integrated to support multiple clock domains and heterogeneous IP cores.

- Interoperability the NI protocol translation enables the connectivity of IP cores that use different communication protocols.

- Increased reliability protocols for error detection and retransmission at link connection level within the NoC can be used to increase the reliability in critical systems or systems that are susceptible to faults.

As such NoC based design of the interconnect can result in faster design closure. In large systems there are still many parameters that need to be explored, however since the NoC design is predictable tools can be used for automatic exploration of the design space in order to achieve design closure.

## 1.2 Interconnect design challenges

Even though NoCs provide the scalability and predictability to design an efficient interconnect for large SoCs, there are many parameters that can be tuned. To design an efficient NoC based interconnect a vast design space needs to be explored. The main problems that need to be solved are:

- Choosing the IP cores and profiling the application to characterize the traffic.

- Decide on the technology design parameters: number of layers for a 3D-IC, the number of clock domains, the possibility to shutdown some clock domains.

- The assignment of IPs to clock domains and layers.

- Synthesis of a topology or mapping of the IPs onto a regular topology.

- Sizing the network parameters for the given application.

- Verifying correctness and performance.

- Generating the Register Transfer Logic (RTL) code.

- Perform RTL synthesis place and route, and post layout simulation and validation.

One of the most important challenges to design the interconnect customized for a given application is to determine the traffic characteristics. Once the IP cores and the algorithms that are to be implemented are known, architectural level simulation has to be performed in order to profile the application and to determine the traffic characteristics. The main parameters that describe the traffic patterns include: i) the average and pick bandwidth between cores, ii) the latency constraints required to offer a certain *Quality of Service (QoS)*, iii) the burstiness of the traffic, iv) the size of the transactions and v) a potential address trace. Along with the traffic characteristics the technology constraints have to be decided before the interconnect can be designed. The technology used (2D planar, 3D integration), the assignment of IP cores to clock domains or silicon layers in a 3D-IC, generate certain constraints that the interconnect has to fulfill for the SoC to function correctly. Therefore when building a customized interconnect, the analysis of the application is crucial as any mistake at this point can lead (in the best case) to a suboptimal design of the interconnect.

Designing the topology of NoC is the step that can make the most significant difference with regard to the power consumption and performance of the NoC. The parameters that have to be decided during synthesis are: choosing the number of switches, deciding the assignment of IP cores to switches, deciding the switch to switch connectivity and routing the flow such that the power is minimized under performance and technological constraints. As the design space is large there may be no optimal solution for all the criteria, but rather a set of trade-off points. *Computer Aided Design (CAD)* tools have been designed in order to explore the potential trade-off solutions and find the most suited NoC topology for the given application. For SoCs that are homogeneous and the functionality is implemented using the same IP core, mapping the tasks to IP cores on different regular topologies can also be used. However provided that the application does not change significantly and does not require the flexibility of a regular topology, synthesis of a customized topology will most likely yield a better result.

Apart from the topology other parameters can be customized like the buffer sizes, link widths, arbitration policies, routing method that also influence the performance, power consumption and area of the NoC. To efficiently tune all these parameters a combination of CAD tools, simulation tools, designer input and iteration may be needed. To reduce the time to market the automation of as many of the design steps as well as the seamless integration with simulation tools is desired, with the designer interacting only at a high level (e.g. solution evaluation).

To reduce further the design time automatic generation of the RTL code for the NoC topology is also needed. Integration with standard synthesis and back-end tools and verification and post layout simulation is also required in order to ensure that there is no performance loss between the estimation of the synthesis topology synthesis tool and the final result after place and route. In the past years much research has been perform in automatizing several is not all the steps of the NoC based interconnect design.

### 1.3 Tools for designing NoCs

For general purpose SoC the traffic patterns are not known at design time as they are dependent on the variety of applications that will run on the system. The topology has to provide full connectivity in such systems. As such many regular topologies have been proposed and explored. Designing the interconnect for such systems is simply a matter of choosing the topology that has the properties which best suite the SoC and sizing it using simulation and general traffic patterns that are expected to be produced. For application-dedicated SoCs on the other hand, the traffic patterns are known at design time and this enables the customization of the interconnect according to the application demands in order to reduce area and power while maximizing performance. Therefore much research has been done on tools and algorithm for automating the different steps of NoC design for application specific MPSoCs.

There are three major directions in which tools have been developed:

- architectural exploration and mapping or synthesis;

- simulation and evaluation;

- automatic RTL code generation and synthesis.

One advantage of NoCs is the ease to design regular structures by simply replicating the IP cores along with the NIs and switches. Such homogeneous SoCs are useful for applications that require greater programmability as the specifications and requirement can change during the design time. For these reason a lot of research has

focused on algorithms and tools to map tasks to IP cores interconnected by regular topologies [68], [69], [122], [123]. Murali et al. also propose in [120] a tool to map tasks considering QoS constraints as well. In systems where the application is known at design time or the traffic can be characterized well even without an explicit implementation of the application, programmability can be traded for improved efficiency. This requires the use of customized IP cores (e.g. audio accelerators, video decoders, WiFi modules) as well a customized interconnect tailored to the application requirements. Several research works propose algorithms and methods to design application specific NoC topologies [134], [65], [8], [158], [62], [181], [177], [121].

To validate the output of the synthesis tools under dynamic load or to further adjust some other parameters of the NoC components (e.g. buffer sizes), simulation tools are also needed. Alternatively analytical models have been proposed in order to estimate the NoC performance faster than simulation. Analytical models however tend to trade-off runtime for accuracy so in many cases simulation is still required for the final solution validation. Simulation as well can be done at different levels of abstraction. Architectural-level simulators like GARNET [4], SICOSYS [136], NOXIM [130] abstract away some of the details of the RTL implementation like the method for packetization or ignore the time to generate the packet. This may result in some loss of accuracy, but overall can give a good performance evaluation and verify most notwork properties faster. To close the gap between the accuracy of RTL simulation and the speed of architectural simulation or of the analytical models, there have been several proposals for emulation of the NoC hardware on Field Programmable Gate Arrays (FPGAs) [16]. In some cases, analytical models can evaluate properties (e.g. worst case latency) that would require extensive simulation. Several research papers have proposed models for estimating worst case latencies for real-time system implementation [139], [92]. In [61], [124], the authors present methods for application-level performance analysis and data-flow based NoC performance analysis, respectively. A data-flow based analysis can also be used to speed-up network performance estimation when the traffic patterns can be modeled accurately to fit the models.

The research and development of ×pipesCompiler [76] and NoC library [160] addressed both the support for the automatic implementation of heterogeneous NoC topologies. Both a parametrized library ×pipes and a NoC hardware compiler were presented to address the problem of synthesis and optimization for heterogeneous NoCs by means of highly-configurable network building blocks, customizable at instantiation time for a specific application domain.

In order to handle the design complexity and meet the tight time-to-market constraints, it is not sufficient to automate most of these NoC design phases. To achieve design closure, the different phases should also be integrated in a seamless manner. Several such integrated design flows have been proposed in the research commu-

Figure 1.3: iNoCs NoC design flow [73]

nity [25], [140]. Some companies like: Arteris [170], iNoCs [73], Silistix [171] are also providing some commercial design automation tools for NoCs. As an example Figure 6 depicts the design flow from iNoCs. The tool flow starts from the application architecture, application constraints (e.g. number of IP cores) and the application communication constraints (e.g. the average bandwidth of communication between the different cores, average latency constraints). The design flow uses the provided tools to go from input specifications all the way to the RTL description of the topology. Also scripts are provided such that in conjunction with other commercial tools the RTL code can be synthesized for deployment onto *Field Programmable Gate Arrays* (FPGAs) or *Application Specific Integrated Circuits* (ASICs).

For the synthesis and architectural exploration phase there are still many opportunities that can be explored in order to improve the outcome of synthesis tools. The exiting tools do not take in to account the constraints that surface in new technologies. For example as wire delay grows in relation with the area of the die as technology continues to scale, it is not possible to design a fully synchronous SoC. Most design use multiple clock domains. To reduce the idle power IP cores in a clock domain can also be shutdown when not used. The interconnect must function correctly regardless so a synthesis tool must be aware of these properties and design the NoC accordingly. If 3D integration technology is used, further challenges need to be addressed like: limiting the number of vertical connections, assigning the NoC components to layers. Another problem with existing tools is that synthesis and performance evaluation are two decoupled steps. As such it may require many iterations before the required

*Quality of Service* (QoS) is achieved by the designed interconnect. By integration the performance evaluation during synthesis the number of design iteration could be dramatically reduced leading to faster design closure.

### 1.4 Thesis contribution

I present in this thesis methods for automatic design of NoCs considering the constraints of new technologies as well as QoS constraints. On one hand the thesis brings a strong engineering contribution as all the presented methods are oriented to solve real problems related to NoC design. The integration of the proposed algorithms into tools to automate the high level NoC design phase as well as the experimental results provided have direct applicability for designing NoCs. On the other hand the thesis has a scientific contribution as well as new algorithms are presented for NoC topology synthesis and deadlock removal.

There are two main technical contributions that this thesis brings:

- 1. I present methods to design efficient NoC to be used as global interconnect in SoC designed in new technologies (3D integration and multi synchronous domain) and

- 2. I integrate methods to evaluate the NoC performance within the synthesis algorithms such that different levels of QoS can be provided with an automated flow.

Finally I also present new architecture and methods to efficiently access bottleneck devices with high latency devices like DRAM memories.

### 1.4.1 Assumptions and limitations

For the rest of this work I made the following realistic assumptions:

- Three dimensional integration adoption: I assume that 3D integration technology will be adopted in the design of future SoC. As technology scaling is becoming more expensive with each technology node, 3D integration is a promising alternative to increase the number of on-chip transistors. This is a realistic assumption as we can already find some products (e.g. memories) that have adopted 3D integration.

- *Multi synchronous design:* Another assumption is that 3D SoCs will use multiple clock domains. Already in existing SoC designed in 2D technology it is not

possible to distribute one synchronous clock throughout the chip. It has been projected in [5] that in 35nm technologies less than 2% of the chip area can be reached in a single clock cycle at a frequency of 5GHz. Therefore it is likely that multiple clock domains will be needed in 3D as well. Also it may not even be possible to power all the cores at the same time as well [49] and considering that many IP cores provide specific functionality it is desirable to shut them down when they are not needed to save power.

- Computation can be decoupled from communication: The thesis focuses on designing the interconnect according to the application specifications. The application traffic characteristics can be evaluated through profiling of the applications that are executed on the IP cores. The interconnect can be designed using the obtained traffic characteristics without having the need for an explicit description of the computation IP cores. Therefore the design of the interconnect can be decoupled from the actual computation that is performed by the SoC cores.

- *NoC components are predictable:* The synthesis algorithm evaluate the NoC performance based on models of the NoC components. Therefore to decouple the high-level topology synthesis from the silicon implementation, models of the NoC components are used. The models are built from post place and route results for the given technology. The assumption is that the NoC components are predictable such that even after integration with the whole systems the NoC components will maintain the properties that they had when the models were built. This assumption is realistic as synthesis tools enables the hierarchical design, so the NoC components can be synthesized as if they were stand-alone modules. Also the links are point-to-point so their properties are easier to predict.

### 1.5 Thesis overview

The thesis focuses on two main aspects of NoC design. First, Chapters 3, 4 and 5 present methods for NoC design considering 3D integration technology and the use of multiple clock domains. Then in Chapters 6, 7 and 8 the thesis focuses on the integration of performance evaluation during synthesis and on design aspects to improve the Quality of Service. In the remainder of this section a detailed overview of this thesis is presented.

### 1.5.1 NoC design in new technologies

In Chapter 3, I present two algorithms for designing application-specific NoCs for 3D-ICs. The first algorithm is designed to produce power optimal topologies for SoCs with less restrictive constraints on vertical connections. The second algorithm is designed to produced results with small numbers of vertical connections and to guarantee direct connection only between adjacent layers in the case of more restrictive 3D integration technologies. The two algorithms are integrated in a tool together with methods to assign the NoC components to layers and to insert them in a valid floorplan. The two algorithms are fully integrated in a single tool and the tool automatically switches between the two to produce good results even under tight constraint on the number of vertical wires that can be used. As 3D integration promises to increase the heterogeneity of cores by stacking dies created with different technological processes, 3D SoCs could greatly benefit by customizing the interconnect according to the application demands. Therefore the chapter also presents an evaluation of the generated 3D topologies with respect to 2D topologies required for a similar sized 2D SoC. The benefits of application specific topologies with respect to 3D regular topologies are also explored.

As in advanced technologies it may take several clock cycles for an electrical signal to traverse the length of a chip on global wires [24], it also very expensive to distribute a synchronous clock throughout the die. Designing SoCs in new technology nodes require the use of either multiple clock domains or asynchronous global communication. In many application-oriented SoCs the IP cores are specialized for a specific functionality. When that functionality is not required, then those IP cores along with the clock domain can be shutdown to reduce the idle power consumption. Therefore the communication infrastructure must be aware of clock domain crossing and be able to provide the required functionality even when parts of the chip are turned off. In Chapter 4, I present an algorithm to design NoC topologies in the presence of multiple clock domains that have the possibility of shutting down. The algorithm is first described for designing 2D topologies and later extended to support multiple clock domains in 3D SoCs. An evaluation of the overhead of the NoC topology due to the partitioning the cores in different clock domains is described. Also a comparison of topologies for 2D and 3D SoC implementations in the presence of multiple clock domains is presented.

One important property for a NoC topology is to ensure deadlock freedom. If traffic flows are not routed with care, they could block by creating circular dependencies when reserving NoC resources. If deadlocks appear they would lead to the catastrophic failure of the communication infrastructure. In regular topologies deadlocks are prevented by restricting the routing function from using certain combinations of links. Similarly, by restricting the routing of flows from using certain sequences of