**TECHNICAL PAPER**

# High quality factor copper inductors integrated in deep dry-etched quartz substrates

C. Leroy · M. B. Pisani · C. Hibert · D. Bouvet · M. Puech · A. M. Ionescu

Received: 3 August 2006/Accepted: 4 December 2006/Published online: 24 January 2007 © Springer-Verlag 2007

**Abstract** This paper reports on an inductor fabrication method capable to deliver high quality factor (Q)and high self-resonance frequency (SRF) devices using quartz insulating substrates and thick high-conductivity copper lines. Inductors are key devices in RF circuits that, when fabricated on traditional semiconductor substrates, suffer from poor RF performances due to thin metallization and substrate related losses. Many previous works revealed that RF performances are strongly dependent on the limited metallization thickness and on the conductivity of the substrate. In this paper we demonstrate a new fabrication process to improve the Q factor of spiral inductors by patterning thick high conductive metal layers directly in a dielectric substrate. Moreover, we develop and validate accurate equivalent circuit modeling and parameter extraction for the characterization of the fabricated devices.

C. Leroy  $\cdot$  M. B. Pisani ( $\boxtimes$ )  $\cdot$  D. Bouvet  $\cdot$  A. M. Ionescu Electronics Laboratory (LEG), Institute of Microelectronics and Microsystems (IMM), Ecole Polytechnique Federale de Lausanne (EPFL), Station 17, Lausanne 1015, Switzerland e-mail: marcelo.pisani@epfl.ch

M. B. Pisani · C. Hibert Center of Micro and Nanotechnology (CMI), Institute of Microelectronics and Microsystems (IMM), Ecole Polytechnique Federale de Lausanne (EPFL), Station 17, Lausanne 1015, Switzerland

M. Puech

Alcatel Vacuum Technology, 98 av. de Brogny, Annecy 74000, France

#### **1** Introduction

Modern applications using RF ICs demand higher working frequencies, low noise and low power consumption, which require high quality factor (Q) and high self-resonance frequency (SRF) passive components.

Our study concerns integrated inductors for which low RF performances limit their application in RF ICs. Typical values are  $Q_{max} < 10-15$ , with a peak below 2 GHz and self resonance frequencies below 3–5 GHz (Yue 2000). The origin of their limited performances is well known and reported: inductors mainly suffer from substrate related RF losses due to low-resistivity underneath substrate, low metal tracks conductivity due to thin layers resistive losses and capacitive parasitics due to inter-spiral tracks/substrate coupling.

Many works have already been done and a lot of solutions have been investigated to increase these performances. For reducing substrate-related losses, high-resistivity silicon (Reyes 1996) or SOI substrates (Kim 1995) have been used, insulating the inductor from the silicon substrate. Etching a cavity underneath the inductor has also been investigated (Ozgur 1999).

Even if inductors with reasonable Q factors and resonance frequencies can be manufactured on top of low-resistivity silicon wafers (Lakdawala 2002), covering most of the telecommunication applications, the nature of the substrate remains a recurrent limitation. Yoon et al. (1999) investigated the RF performances of the same inductor design fabricated on both silicon and glass substrates. On-glass inductor provided a significant increase in both quality factor (45%) and SRF (2.5 times higher) due to a relatively large decrease in the parasitic capacitance to the substrate. We used new inductive coupled plasma (ICP) etcher dedicated to dielectrics anisotropic deep dry etching in order to explore a new technique based on patterning the inductor directly in a quartz substrate. The main advantage of this technique is the high resistivity of the quartz ( $2 \times 10^{14} \Omega$  cm at 20°C), which reduces dramatically the substrate-related RF losses.

### 2 Fabrication process

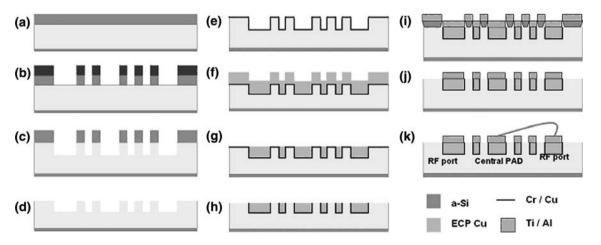

Figure 1 shows a schematic cross section view of the technology steps used to fabricate thick copper spiral inductors embedded in a quartz substrate. A 2 µm sputtered amorphous silicon film is used as hard mask for the etching of the quartz (Fig. 1a). This a-Si hard mask is patterned by thin-resist photolithography followed by a SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub> dry plasma etching step (Fig. 1b). The quartz substrate is then patterned by C<sub>4</sub>F<sub>8</sub>/CH<sub>4</sub>/Ar plasma etching step performed in a state-of-the-art Alcatel AMS 200 DSE ICP dry etcher (Fig. 1c). After stripping off the amorphous silicon mask (Fig. 1d), the quartz mould is cleaned in a piranha bath  $(H_2SO_4/H_2O_2)$  and receives 0.1 µm sputtered chromium as adhesion layer and a 0.2 µm sputtered copper as seed layer (Fig. 1e). The mould is filled out with 4.8 µm of high conductive electrocopper (resistivity =  $2.0 \ \mu \ \Omega \ cm$ , Fig. 1f). plated Copper lines are then defined by a damascene approach using a high-removal rate chemical-mechanical polishing receipt (CMP) (Pisani 2004) (Fig. 1g). The CMP stops at the top chromium layer which is cleared in very selective chromium to copper wet etch bath (Fig. 1h).

A protection layer is then defined in order to avoid copper oxidation and to have good electrical contacts to the devices. The protection is composed of 0.2  $\mu$ m titanium and 0.6  $\mu$ m of aluminum layers deposited successively in the same multi-target evaporator system, which avoids the first film to be exposed to air (Fig. 1i). The protection layer is patterned by lift-off process, using reversal thin-resist (Fig. 1j). Finally, connections are established by bonding a 25  $\mu$ m diameter gold wire between the inductor central pad and the lateral RF port (Fig. 1k).

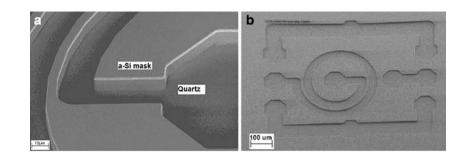

Figure 2 shows scanning electron microscopy (SEM) pictures of a quartz etched mould.  $C_4F_8/CH_4/Ar$  plasma etching is a very selective process (>20) that provides very vertical walls (Pavius 2004). Quartz mould is also very well defined.

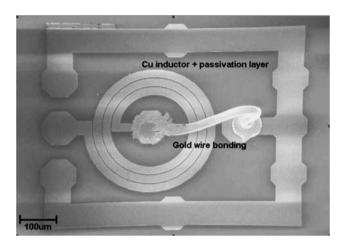

A SEM photo of a final fabricated (passivated and bonded) device can be seen in Fig. 3.

## **3 Results**

RF electrical characterization was performed using full 2-port *S*-parameter measurements in a microprober equipped with an HP 8719D vector network analyzer and Cascade Microtech RF ground-signal-ground probes (GSG). The RF setup is calibrated in the range of frequencies from 0.05 to 13.5 GHz using an Impedance Standard Substrate with SOLT references (short-circuit, open, load and thru). Measured *S*-parameter data are transformed into *Y*-parameters and inductance and quality factor of the devices are calculated from the equivalent 1-port impedance of the device as (Yue 2000):

Fig. 1 Schematic cross section view of the coil fabrication process flow: **a** a-Si deposition (PVD), **b** a-Si dry etching, **c** quartz dry etching, **d** a-Si mask strip, **e** adhesion and seed layers

deposition (Cr/Cu, PVD), **f** Cu electroplating, **g** chemical mechanical polishing, **h** top Cr wet etching, **i** lithography and protection layer deposition (Ti/Al), **j** lift-off, **k** gold wire bonding

Fig. 3 View of a fabricated 3-turn circular spiral inductor (400  $\mu$ m outer diameter, 40  $\mu$ m track width, 8  $\mu$ m track spacing)

$$L = \frac{\operatorname{imag}\left(1/y_{11}\right)}{2\pi f},\tag{1}$$

and

$$Q = \frac{\mathrm{imag}(1/y_{11})}{\mathrm{real}(1/y_{11})},$$

(2)

where L is the inductance, Q is the quality factor, f is the measurement frequency and 1/y11 is the equivalent complex impedance of port 1 when port 2 is connected to the ground (Yue 2000). These formulas are commonly used for isolated inductors working below the resonance frequency. The resonance frequency is defined when the expression for Q (Eq. 2) goes to 0.

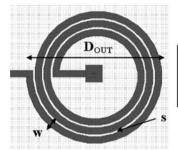

In this paper, we analyze two devices of 3.8 and 9.0 nH nominal inductances that have been fabricated and characterized in the 0.05–13.5 GHz frequency range. Dimensions and calculated inductance of each device are summarized in Fig. 4 and Table 1. Expected inductance values are calculated following the current sheet method presented in (Moham 1999). The thicker layer used in this work with respect to (Moham 1999) explains a reduction of a few percent in the inductance

D<sub>OUT</sub>: outer diameter w: track width s: track spacing

**Fig. 4** Schematic view of a 3-turn circular inductor and its main geometrical parameters

values with respect to the predicted ones (inductance decreases with both increasing track width and thickness, but must of practical formulae neglect the thickness dependency).

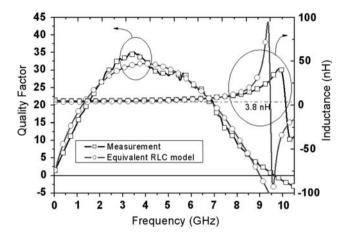

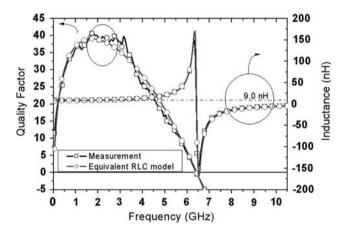

Figures 5 and 6 show respectively the extracted L-values (Eq. 1) and Q-factors (Eq. 2) for these two inductors.

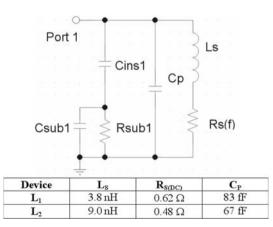

We have used a broadband RLC equivalent circuit of a spiral inductor in order to model the measured parameters. Figure 7 shows the equivalent 1-port circuit (Yue 2000) and the values of the parameters extracted from the measurements using a dedicated procedure (non-linear least squares fit on S-parameters and on impedance data). The L-Q plots for this model are also shown in Figs. 5 and 6.

In the model of Fig. 7,  $R_s$  accounts for the series resistance of the metal tracks and is dependent of the frequency in the form  $R_s(f) = R_{DC} + a\sqrt{f} + b_f$  where

Table 1 Dimensions and inductances of the two analyzed inductors

|                          | $L_1$     | $L_2$    |

|--------------------------|-----------|----------|

| $D_{\rm OUT}$ (µm)       | 800       | 800      |

| w (µm)                   | 20        | 40       |

| $s (\mu m)$              | 12        | 12       |

| Forms                    | Octagonal | Circular |

| No. of turns             | 1.5       | 3        |

| $L_{(\text{PREDICTED})}$ | 4.3 nH    | 9.3 nH   |

| $L_{(\text{MEASURED})}$  | 3.8 nH    | 9.0 nH   |

**Fig. 5** Extracted inductance (Eq. 1) and *Q*-factor (Eq. 2) versus frequency for the 3.8-nH device  $(L_1)$

**Fig. 6** Extracted inductance (Eq. 1) and Q-factor (Eq. 2) versus frequency for the 9.0 nH circular inductor  $(L_2)$

**Fig. 7** Equivalent broadband RLC model of a spiral inductor [1] and extracted values for  $L_1$  and  $L_2$  devices ( $C_{\text{INS1}}$ ,  $R_{\text{SUB1}}$  and  $C_{\text{SUB1}}$  substrate parameters are negligible)

$R_{\rm DC}$  is the low frequency resistance and a and b are constants depending on the device geometry that accounts for the skin and proximity effects. These effects increase the resistance as function of the frequency (Bahl 2003).  $C_{\rm P}$  is the parasitic parallel capacitance that comes mainly from the capacitive coupling between adjacent inductor tracks.  $C_{INS1}$  and  $C_{SUB1}$  accounts for the parasitic capacitances between the measurement ports and between the spiral tracks and the backside ground of the wafers.  $R_{SUB1}$  accounts for the resistive losses in the substrate, due to the substrate conductivity as well as to eddy currents induced in the substrate by the magnetic field of the inductor. Its value ranges from typically some ohms to hundreds of ohms when the spiral is designed on top of low-resistivity substrates. This resistance decreases the peak quality factor as well as the SRF. For our devices, the contribution of the substrate is reduced to its minimum by the use of the insulating quartz substrate, and only the  $C_{\rm P}$  value needs to be considered to produce an accurate equivalent circuit model.

Figure 5 shows the electrical performance and RLC fit for the 3.8-nH inductor. We observed a peak quality factor of 35 at 3.5 GHz and a SRF of 9 GHz. Figure 6 shows the electrical performances and RLC fit for the 9.3-nH inductor. Measured peak quality factor is 40 at 2.1 GHz and resonance frequency is 6.5 GHz.

It should be pointed that the fabricated devices exhibit a broadband Q-behavior, with Q exceeding 20 in the range of 1–5 GHz, enabling the use of such devices in multiband circuits, covering a significant number of telecommunication standards, including GSM, UMTS and WLAN. The achieved performances in terms of  $Q_{\rm PEAK}$  and SRF are in the current state-of-the-art for integrated inductors (Lakdawala 2002; Carchon 2004).

## 4 Conclusion

We developed an innovative fabrication process of passive devices directly embedded in an insulating substrate. This technique uses a state-of-the-art Alcatel AMS 200 DSE ICP dry etcher that enables to pattern deep trenches in quartz substrates and to fabricate devices using a reduced number of masks. The major advantage of this technique is to significantly decrease the RF losses due to parasitic capacitance by using a dielectric as substrate. We fabricated and characterized integrated spiral inductors with high RF performances (peak quality factor in excess of 30 around 2 GHz and self resonance frequency superior to 6 and 9 GHz) using a thick high conductivity copper/quartz fabrication process. The broadband Q-behavior of the fabricated components enables the use of them in telecommunication applications, particularly in multi-standard circuits that can operate at different standards in the 1–6 GHz range (GSM, UMTS and WLAN).

Acknowledgments The authors thank the IST Wide-RF project (IST-2001-33286), the Swiss OFES project 01.0308 and the IST MIMOSA project (IST-2002-507045) for funding. We thank Mr. Giancarlo Corradini from the EPFL-LPM (Laboratoire de Production Microtechnique) for providing the gold wire-bonding services. Many thanks are due to the EPFL-CMI staff for the clean room facilities access and supplied technical support.

## References

- Bahl I (2003) Lumped elements for RF and microwave circuits. Artech House, Boston

- Carchon GJ, de Raedt W, Beyne E (2004) Wafer-level packaging technology for high-*Q* on-chip inductors and transmission lines. IEEE Trans Microw Theory Tech 52:1244–1251

- Kim BK, Ko BK, Lee KK (1995) Monolithic planar RF inductor and waveguide structures on silicon with performance comparable to those in GaAs MMIC. IEDM Tech Digest pp 717–720

- Lakdawala H, Zhu X, Luo H, Santahannan S, Carley LR, Fedder GK (2002) Micromachined high-*Q* inductors in a 0.18-μm copper interconnect low-k dielectric CMOS process. IEEE J Solid State Circuits 37:394–403

- Mohan SS, M.M. Hershenson MM, S.P. Boyd SP, T.H. Lee TH (1999) Simple accurate expression for planar spiral inductances. IEEE J Solid State Circuits 34:1419–1424

- Ozgur M, Zaghloul M, Gaitan M (1999) High *Q* backside Micromachined CMOS inductors. IEEE Int Symp Circuits Syst 2:577–580

- Pavius M, Hibert C, Flückiger P, Renaud P (2004) Profile angle control in SiO2 deep anisotropic dry etching for MEMS fabrication. In: Proceedings of MEMS 2004, pp 669–672

- Pisani MB, Hibert C, Bouvet D, Beaud P, Ionescu AM (2004) Copper/polyimide fabrication process for above-IC integration of high quality factor inductors. Microelectron Eng 73– 74:474–479

- Reyes AC, El-Ghazaly SM, Dorn S, Dydyk M, Schroder DK, Patterson H (1996) High-resistivity silicon as a microwave substrate. In: Proceedings of electronic components and technology conference, pp 382–391

- Yoon JB, Kim BK, Han CH, Yoon E, Kim CK (1999) Surface micromachining solenoid on-Si and on-glass inductors for RF applications. IEEE Electron Devices Lett 20(9):487–489

- Yue CP, Wong SS (2000) Physical modeling of spiral inductors on silicon. IEEE Trans Electron Devices 47:560–568