# Closing the Gap between FPGA and ASIC: Balancing Flexibility and Efficiency

## THÈSE N° 5339 (2012)

PRÉSENTÉE LE 27 MARS 2012

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE D'ARCHITECTURE DE PROCESSEURS

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

### PAR

## Hadi PARANDEH AFSHAR

acceptée sur proposition du jury:

Prof. E. Sanchez, président du jury Prof. P. Ienne, directeur de thèse Prof. G. De Micheli, rapporteur Prof. G. Lemieux, rapporteur Dr A. Mishchenko, rapporteur

# Acknowledgements

Foremost, I would like to thank my wonderful advisor, **Prof. Paolo Ienne**, for all his effective supports and his patience. He is not only a good advisor, but also a great teacher and manager. I hope to be lucky enough to work with such a professional manager in my future career. His comments and guidance always improved my work, and the result is a thesis that includes two *Best Paper Awards* received from top international conferences.

I would like to appreciate my committee members, **Prof. Giovanni De Micheli**, **Prof. Guy Lemieux**, and **Dr. Alan Mishchenko**, for having accepted this demanding task, reading this dissertation, and providing constructive feedbacks. I would like to thank **Prof. Eduardo Sanchez** for serving as the president of my jury.

Parts of this thesis have been published in some conferences and journals, in which many of my colleagues contributed over the years. I have had the privilege of interacting with some of present and past members of Processor Architecture Laboratory (LAP) including Prof. Philip Brisk, Dr. David Novo, Dr. Madhura Purnaprajna, Dr. Ajay K. Verma, Alessandro Cevrero, Grace Zgheib, Arkosnato Neogy, Panagiotis Athanasopoulos, and Hind Benbihi. I would like to thank all these colleagues and friends for their incredible collaborations.

The members of the LAP group provided a wonderful work environment in which it was hard not to be productive, in particular I would like to thank **Chantal Schneeberger** whose constant support and encouragement has been an important factor in the completion of this thesis. Additionally, her contribution in editing the thesis also cannot be ignored. I would like to express my special thanks to Xavier Jimenez, my office mate, for all his useful tips and also his contribution in editing the thesis. Also, I would like to thank René Beuchat for his contribution in editing the thesis and his feedbacks on my research.

I am grateful to **Prof. Babak Falsafi** for his supports, fruitful guidances, and inspiring feedbacks. I learnt many concepts related to computer architecture from him in the two courses that I had with him.

I am thankful to Dr. Alan Mishchenko for his kind supports in connecting me with various FPGA companies, which enabled to present my ideas and receive practical feedbacks that improved my work. Also, I would like to thank Alan for providing his wonderful synthesis and verification tool, ABC. This open source tool had a key role in our research advances.

Needless to mention that without financial support from Swiss National Science Foundation (SNSF), it was impossible to make such a progress in the field. The SNSF fund provided the opportunity to concentrate on the research and attend several international conferences all over the world.

### Acknowledgements

Finally, I would like to thank my lovely wife, Mahboobeh Karamian, for her patience and supports during our extended and long student life. She, with her patience and encouragement, gave me the flexibility to work overtime and during the weekends to meet all tough deadlines. It is my great pleasure to dedicate this thesis to my wife, Mahboobeh, and my little daughter, Helen. Also, I would like to appreciate our parents for their support, understanding and endurance that helped us to live happily, although we were thousands of miles away from them.

Lausanne, 12 March 2011

Hadi P. Afshar

# **Abstract**

Despite many advantages of *Field-Programmable Gate Arrays (FPGAs)*, they fail to take over the IC design market from *Application-Specific Integrated Circuits (ASICs)* for high-volume and even medium-volume applications, as FPGAs come with significant cost in area, delay, and power consumption. There are two main reasons that FPGAs have huge efficiency gap with ASICs: (1) FPGAs are extremely flexible as they have fully programmable *soft-logic* blocks and routing networks, and (2) FPGAs have *hard-logic* blocks that are only usable by a subset of applications. In other words, current FPGAs have a heterogeneous structure comprised of the flexible soft-logic and the efficient hard-logic blocks that suffer from inefficiency and inflexibility, respectively. The inefficiency of the soft-logic is a challenge for any application that is mapped to FPGAs, and lack of flexibility in the hard-logic results in a waste of resources when an application can not use the hard-logic.

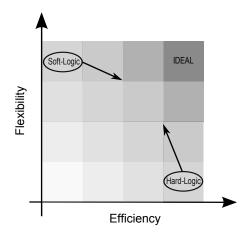

In this thesis, we approach the inefficiency problem of FPGAs by bridging the efficiency/flex-ibility gap of the hard- and soft-logic. The main goal of this thesis is to compromise on efficiency of the hard-logic for flexibility, on the one hand, and to compromise on flexibility of the soft-logic for efficiency, on the other hand. In other words, this thesis deals with two issues: (1) adding more generality to the hard-logic of FPGAs, and (2) improving the soft-logic by adapting it to the generic requirements of applications.

In the first part of the thesis, we introduce new techniques that expand the functionality of FPGAs hard-logic. The hard-logic includes the dedicated resources that are tightly coupled with the soft-logic—i.e., adder circuitry and carry chains—as well as the stand-alone ones—i.e., DSP blocks. These specialized resources are intended to accelerate critical arithmetic operations that appear in the pre-synthesis representation of applications; we introduce mapping and architectural solutions, which enable both types of the hard-logic to support additional arithmetic operations. We first present a mapping technique that extends the application of FPGAs carry chains for carry-save arithmetic, and then to increase the generality of the hard-logic, we introduce novel architectures; using these architectures, more applications can take advantage of FPGAs hard-logic.

In the second part of the thesis, we improve the efficiency of FPGAs soft-logic by exploiting the circuit patterns that emerge after logic synthesis, i.e., connection and logic patterns. Using these patterns, we design new soft-logic blocks that have less flexibility, but more efficiency than current ones. In this part, we first introduce *logic chains*, fixed connections that are integrated between the soft-logic blocks of FPGAs and are well-suited for long chains of logic that appear post-synthesis. Logic chains provide fast and low cost connectivity, increase the

#### Abstract

bandwidth of the logic blocks without changing their interface with the routing network, and improve the logic density of soft-logic blocks.

In addition to logic chains and as a complementary contribution, we present a non-LUT soft-logic block that comprises simple and pre-connected cells. The structure of this logic block is inspired from the the logic patterns that appear post-synthesis. This block has a complexity that is only linear in the number of inputs, it sports the potential for multiple independent outputs, and the delay is only logarithmic in the number of inputs. Although this new block is less flexible than a LUT, we show (1) that effective mapping algorithms exist, (2) that, due to their simplicity, poor utilization is less of an issue than with LUTs, and (3) that a few LUTs can still be used in extreme unfortunate cases.

In summary, to bridge the gap between FPGAs and ASICs, we approach the problem from two complementary directions, which balance flexibility and efficiency of the logic blocks of FPGAs. However, we were able to explore a few design points in this thesis, and future work could focus on further exploration of the design space.

**Keywords**: FPGA, Efficiency Gap, ASIC, FPGA Logic Block, FPGA Mapping Algorithm, Logic Chains, Carry Chains, And-Inverter Graph, And-Inverter Cone, DSP Block, Carry Save Arithmetic, Look-Up Table.

# Résumé

Malgré leurs nombreux avantages, les *Field-Programmable Gate Arrays (FPGAs)* ne parviennent pas à s'emparer du marché de conception de circuits intégrés pour des applications à hauts ou même moyens volumes, actuellement contrôlés par les *Application-Specific Integrated Circuits (ASICs)*, car les FPGAs ont des coûts importants en terme de surface, délai et consommation d'énergie. Il y a deux raisons principales expliquant le large écart de rendement entre les FPGAs et les ASICs : (1) les FPGA sont extrêmement flexibles, grâce aux routage programmables et des blocs de logique programmables, et (2) les FPGAs ont des blocs spécialisés, à logique non-programmable, utilisables seulement par un sous-ensemble d'applications. En d'autres termes, les FPGAs actuelles ont une structure hétérogène, composée de logique programmable flexible et de logique spécialisée efficace qui souffrent respectivement d'inefficacité et d'inflexibilité. L'inefficacité de la logique programmable est un défi pour n'importe quelle application implementeé sur FPGA. Le manque de flexibilité dans la logique spécialisée entraîne un gaspillage de ressources lorsque l'application ne peut en bénéficier.

Dans cette thèse, nous proposons d'am'eliorer l'inefficacité des FPGAs en équilibrant la performance et la flexibilité de la logique spécialisée et programmable des FPGAs. L'objectif principal de cette thèse est d'une part, de faire des concessions sur la performance de la logique spécialisée pour plus de la flexibilité, et d'autre part de faire des concessions sur la flexibilité de la logique programmable pour gagner en performance. En d'autres termes, cette thèse traite de deux questions : (1) ajouter plus de généralité à la logique spécialisée des FPGAs, et (2) l'améliorer la logique programmable en l'adaptant aux besoins des applications.

Dans la première partie de la thèse, nous introduisons de nouvelles techniques qui élargissent les fonctionnalités de la logique spécialisée des FPGAs. La logique spécialisée comprend les ressources dédiées qui sont étroitement couplées avec la logique programmable—par exemple, circuits additionneurs et chaînes de retenue—ainsi que les cellules autonomes—par exemple, les blocs DSP. Ces ressources ciblent généralement les opérations arithmétiques avec l'intention de les utiliser avant la synthèse; nous introduisons des solutions de synthèse et architecturales, qui permettront aux deux types de logique spécialisée de faciliter des opérations arithmétiques supplémentaires. Nous présentons d'abord une technique de synthèse qui permet l'utilisation des chaînes de retenue des FPGAs pour des applications sans propagation de retenue, puis afin d'augmenter encore la généralité de la logique spécialisée, nous introduisons de nouvelles architectures; en utilisant ces architectures, un plus grand nombre d'applications peut tirer avantage de la logique spécialisée des FPGAs.

Dans la deuxième partie de la thèse, nous améliorons l'efficacité de la logique programmable

des FPGAs en exploitant des motifs de circuits qui émergent après la synthèse logique, comme des motifs d'interconnection et de logique. En utilisant ces modèles, nous concevons de nouveaux blocs à logique programmable qui ont moins de flexibilité, mais sont plus performant que ceux actuels. Dans cette partie, nous présentons d'abord les *logic chains*, des connexions fixes qui sont intégrées entre les blocs à logique programmable des FPGAs et sont bien adaptées aux longues chaînes logiques qui apparaissent après synthèse. Les *logic chains* fournissent une connectivité rapide et à faible coût, augmentent la bande passante des blocs logiques sans changer leur interface avec le réseau de routage, et améliorent la densité logique du bloc à logique programmable.

En plus des *logic chains*, nous vous présentons un bloc à logique programmable sans *Loo-kUp Table (LUT)* qui comporte des cellules simples et pré-connectées. La structure de ce bloc logique est inspirée des motifs logiques qui apparaissent après synthèse. Ce bloc a une complexité qui n'est linéaire que dans le nombre d'entrées, il peut potentiellement avoir de multiples sorties indépendantes, et le délai est uniquement proportionel au logarithmique du nombre d'entrées. Bien que ce nouveau bloc est extrêmement moins flexible que les LUTs traditionnels, nous montrons (1) que des algorithmes de synthèse efficaces existent, (2) qu'en raison de leur simplicité, une faible utilisation est moins un problème que pour les LUTs, et (3) que quelques LUTs peuvent toujours être utilisés dans des cas extrêmes.

En résumé, pour combler le fossé entre les FPGAs et les ASICs, nous abordons le problème par deux directions complémentaires, lesquelles équilibrent la flexibilité et la performance des blocs logiques des FPGAs. Seuls quelques points du problème ont pu être couverts par la présente thèse et des travaux futurs pourraient continuer sur une exploration plus poussée du problème dans sa totalité.

**Mots-clés**: FPGA, Écart de Rendement, ASIC, Blocs de Logique Programmables, Algorithmes de Synthèse, Logic Chains, Chaînes de Retenue, And-Inverter Graph, And-Inverter Cone, Bloc DSP, Applications sans Propagation de Retenue, Look-Up Table.

# **Contents**

| A  | cknov | vledgements                                                | iii |

|----|-------|------------------------------------------------------------|-----|

| Al | ostra | ct (English/Français)                                      | v   |

| Li | st of | figures                                                    | x   |

| Li | st of | tables                                                     | xix |

| 1  | Intr  | oduction                                                   | 1   |

|    | 1.1   | Thesis Motivation                                          | 2   |

|    | 1.2   | Thesis Organization                                        | 5   |

| 2  | Bac   | kground and Preliminaries                                  | 9   |

|    | 2.1   | FPGAs Introduction                                         | 9   |

|    |       | 2.1.1 FPGAs Architecture                                   | g   |

|    |       | 2.1.2 FPGAs CAD Flow                                       | 11  |

|    | 2.2   | State-of-the-art FPGAs                                     | 12  |

|    |       | 2.2.1 Altera Stratix-III                                   | 13  |

|    |       | 2.2.2 Xilinx Virtex-5                                      | 15  |

|    | 2.3   | Computer Arithmetic Preliminaries                          | 17  |

|    |       | 2.3.1 Full- and Half-Adders                                | 17  |

|    |       | 2.3.2 Ripple-Carry and Carry-Save Adders                   | 18  |

|    |       | 2.3.3 Parallel Counters                                    | 19  |

|    |       | 2.3.4 Compressors                                          | 19  |

|    |       | 2.3.5 Adder and Compressor Trees                           | 20  |

|    |       | 2.3.6 Parallel Multipliers                                 | 23  |

| 3  | Maj   | oping using Carry Chains                                   | 25  |

|    | 3.1   | Introduction                                               | 26  |

|    | 3.2   | Hybrid Design Methodology                                  | 27  |

|    | 3.3   | Developing Compressor Tree Primitives for FPGAs            | 28  |

|    |       | 3.3.1 GPC Libraries                                        | 30  |

|    |       | 3.3.2 Efficiently Packing Adjacent GPCs Along Carry Chains | 33  |

|    | 3.4   | Compressor Tree Synthesis Heuristic                        | 34  |

|    |       | 3.4.1 GPC Library Characterization                         | 34  |

### **Contents**

|   |      | 3.4.2 Compressor Tree Synthesis Heuristic         |

|---|------|---------------------------------------------------|

|   | 3.5  | Experimental Results                              |

|   |      | 3.5.1 Experimental Methodology                    |

|   |      | 3.5.2 Benchmarks                                  |

|   |      | 3.5.3 Results: Stratix-III                        |

|   |      | 3.5.4 Results: Virtex-5                           |

|   |      | 3.5.5 Integer Linear Programming (ILP)            |

|   | 3.6  | Related Work                                      |

|   |      | 3.6.1 Compressor Tree Synthesis for FPGAs         |

|   |      | 3.6.2 Compressor Tree Synthesis for ASICs         |

|   | 3.7  | Conclusion                                        |

| 4 | Non  | propagating Carry Chains 4                        |

|   | 4.1  | Introduction                                      |

|   | 4.2  | Compressors                                       |

|   |      | 4.2.1 Compression Ratio                           |

|   | 4.3  | Logic Block Design                                |

|   | 4.4  | Compressor Tree Synthesis on the New Logic Block  |

|   | 4.5  | Experimental Setup                                |

|   |      | 4.5.1 VPR                                         |

|   |      | 4.5.2 Packing                                     |

|   |      | 4.5.3 Benchmarks                                  |

|   | 4.6  | Experimental Results                              |

|   |      | 4.6.1 Overview of Experimental Comparison         |

|   |      | 4.6.2 Critical Path Delay                         |

|   |      | 4.6.3 Critical Path Analysis                      |

|   |      | 4.6.4 Area Utilization                            |

|   |      | 4.6.5 Wire-length and Routability                 |

|   | 4.7  | Related Work                                      |

|   | 4.8  | Conclusion                                        |

| 5 | Vers | atile DSP Blocks 6                                |

|   | 5.1  | Introduction                                      |

|   | 5.2  | Overview of DSP Blocks for Multi-input Addition 6 |

|   |      | 5.2.1 FPCA Architecture Overview                  |

|   |      | 5.2.2 FPCT Architecture Overview 6                |

|   | 5.3  | Proposed Versatile DSP Block                      |

|   |      | 5.3.1 Architecture of the Base DSP Block          |

|   |      | 5.3.2 Supporting Various Multiplier Bit-widths    |

|   |      | 5.3.3 Supporting Multi-input Addition             |

|   |      | 5.3.4 Multi-input Addition Mapping Algorithm      |

|   | 5.4  | Experiments                                       |

|   |      | 5.4.1 Results 7                                   |

|    | 5.5    | Related Work                               | 80  |

|----|--------|--------------------------------------------|-----|

|    | 5.6    | Conclusion                                 | 81  |

| 6  | Log    | ic Chains                                  | 83  |

|    | 6.1    |                                            | 84  |

|    |        | 6.1.1 Key Idea                             | 85  |

|    |        | 6.1.2 Carry Chain Option                   | 86  |

|    | 6.2    | New Logic Chain                            | 88  |

|    | 6.3    | Chaining Heuristic                         | 90  |

|    | 6.4    | Tool Chain Flow                            | 92  |

|    | 0.1    | 6.4.1 DAG Generator                        | 92  |

|    |        | 6.4.2 Placement and Routing                | 93  |

|    |        | 6.4.3 Timing Analysis                      | 95  |

|    |        | 6.4.4 Power Estimation                     | 96  |

|    | 6.5    | Experimental Results                       | 97  |

|    | 6.6    | Related Work                               | 101 |

|    | 6.7    |                                            |     |

|    | 0.7    | Conclusion                                 | 105 |

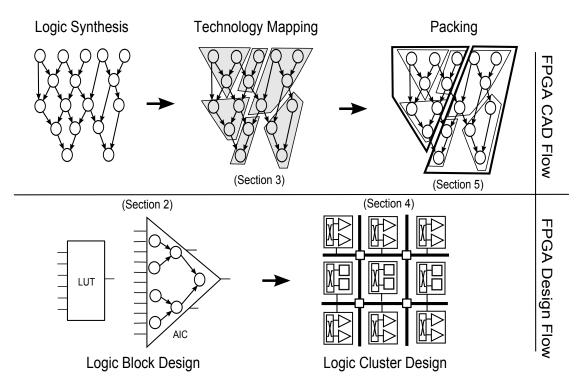

| 7  | ANI    | D-Inverter Cones                           | 105 |

|    | 7.1    | Introduction                               | 105 |

|    | 7.2    | Logic Block Design                         | 108 |

|    |        | 7.2.1 An AIG-inspired logic block          | 108 |

|    |        | 7.2.2 AND-Inverter Cone (AIC) Architecture | 109 |

|    | 7.3    | Technology Mapping                         | 109 |

|    |        | 7.3.1 Definitions and Problem Formulation  | 110 |

|    |        | 7.3.2 Generating All Cones                 | 111 |

|    |        | 7.3.3 Forward Traversal                    | 112 |

|    |        | 7.3.4 Backward Traversal                   |     |

|    |        | 7.3.5 Converting Cones to LUTs and AICs    |     |

|    | 7.4    | Logic Cluster Design                       |     |

|    | 7.5    | Packing Approach                           |     |

|    | 7.6    | Experimental Methodology                   |     |

|    |        | 7.6.1 Area Model                           |     |

|    |        | 7.6.2 Delay Model                          |     |

|    | 7.7    | Results                                    | 118 |

|    | 7.8    | Related Work                               |     |

|    | 7.9    | Conclusions                                |     |

|    | 1.3    | Conclusions                                | 144 |

| 8  | Con    | iclusions and Future Work                  | 125 |

|    | 8.1    | Future Work                                | 128 |

| Ri | hlino  | graphy                                     | 138 |

|    | 21108  | >- mk·1                                    | 100 |

| Cı | ırricı | ulum Vitae                                 | 139 |

# **List of Figures**

| 1.1 | FPGA versus ASIC. FPGA is highly flexible and less efficient, while ASIC is highly             |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | efficient and less flexible. The flexibility of FPGA comes at a price, which is the            |    |

|     | delay, area and power gap between FPGAs and ASICs [50]                                         | 2  |

| 1.2 | Effect of using hard-logic in FPGAs in narrowing their area and delay gaps with                |    |

|     | ASICs [50]. Although the hard-logic can significantly reduce the area gap, its                 |    |

|     | effect on the delay gap is not considerable for three reasons: (1) Underutilization            |    |

|     | of the hard-logic, (2) high routing cost to the stand-alone hard-logic, and (3) the            |    |

|     | presence of the FPGAs soft-logic in critical-paths                                             | 3  |

| 1.3 | Thesis roadmap for improving FPGAs. To bridge the FPGAs and ASICs efficiency                   |    |

|     | gap, two complementary steps are required: (1) increasing the generality of the                |    |

|     | hard-logic such that more applications benefit from it, and (2) improving the                  |    |

|     | soft-logic efficiency, which impacts all applications, through novel logic blocks.             | 4  |

| 1.4 | Ideal FPGA and how the roadmap of Figure 1.3 helps to get closer to this ideal                 |    |

|     | FPGA                                                                                           | 5  |

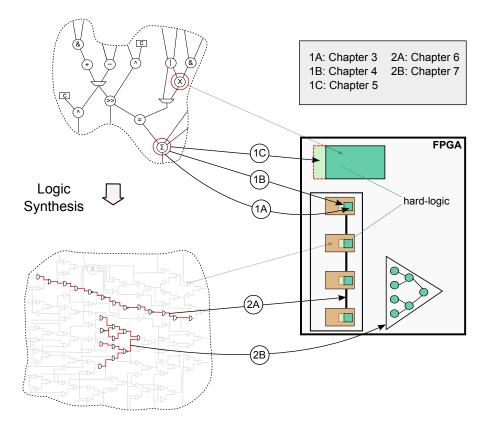

| 1.5 | Thesis organization. Based on the thesis roadmap, shown in Figure 1.3, we                      |    |

|     | approach the gap problem from two complementary directions: (1) Improving                      |    |

|     | the generality of the hard-logic blocks through synthesis (1A) and architectural               |    |

|     | (1B, 1C) methods, and (2) lightening the stress on the expensive routing network               |    |

|     | through locally connected (2A) and synthesis-inspired (2B) logic blocks                        | 6  |

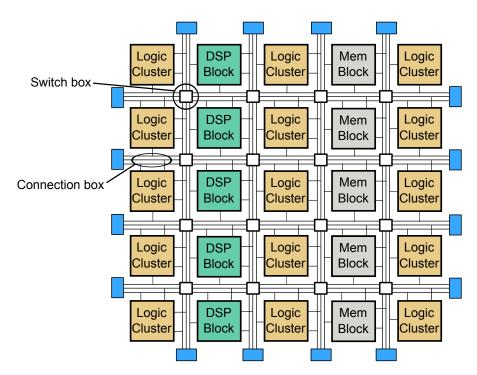

| 2.1 | An island-style FPGA with heterogeneous structure. Different types of FPGA                     |    |

|     | blocks, including <i>soft-logic</i> and <i>hard-logic</i> blocks, interconnected through a two |    |

|     | dimensional routing network consisted of routing switches                                      | 10 |

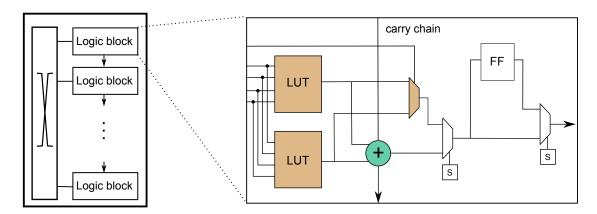

| 2.2 | Generic structure of logic cluster (left) and logic block (right) in current FPGAs.            |    |

|     | Logic cluster is an array of logic blocks with a local routing network that is                 |    |

|     | mainly a crossbar. Logic block has a fracturable LUT structure and supports fast               |    |

|     | arithmetic addition using the dedicated circuitry and hard-wired carry chains.                 | 11 |

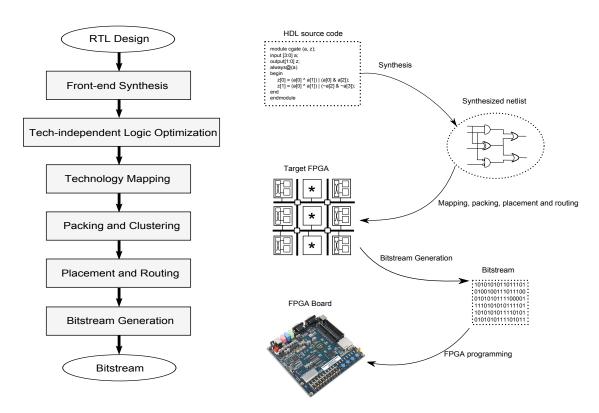

| 2.3 | Typical CAD and design flow in current FPGAs                                                   | 12 |

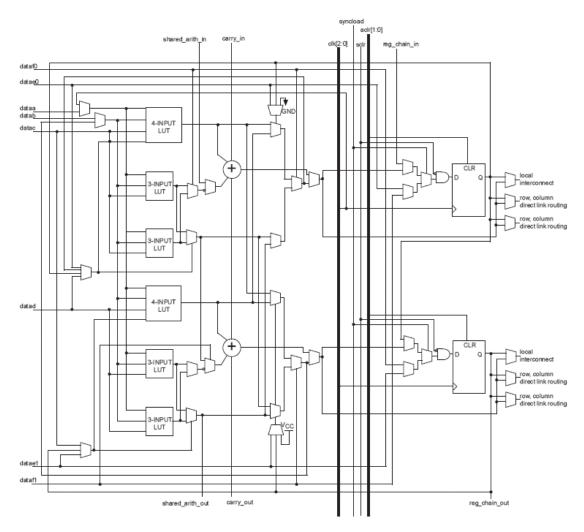

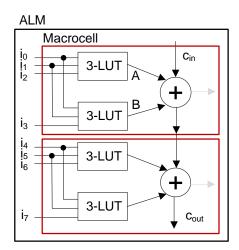

| 2.4 | Logic block (ALM) structure of Altera Stratix II-V [7]                                         | 13 |

| 2.5 | Modes of the ALM that use the carry chain [7]. <i>Arithmetic</i> mode is used for              |    |

|     | binary addition and subtraction and <i>shared arithmetic</i> mode is used for ternary          |    |

|     | addition                                                                                       | 14 |

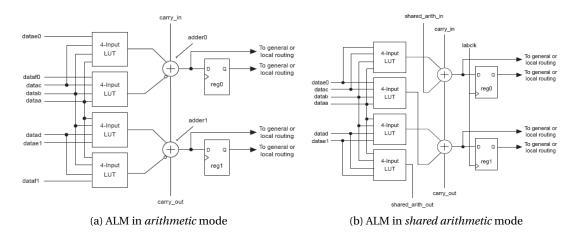

| 2.6 | The DSP block structure of Altera Stratix-III [7]                                              | 15 |

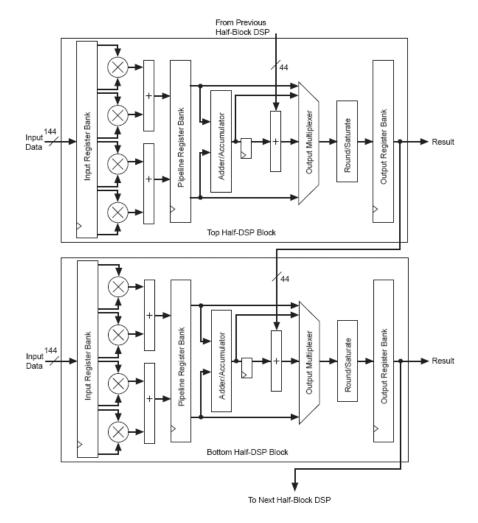

| 2.7  | Structure of logic cluster in Xilinx Virtex-5 [92]. The adder circuitry is composed of multiplexers and XOR gates. This logic cluster has four logic blocks that are equivalent to the Altera ALM                                                                                                                                                                              | 16 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

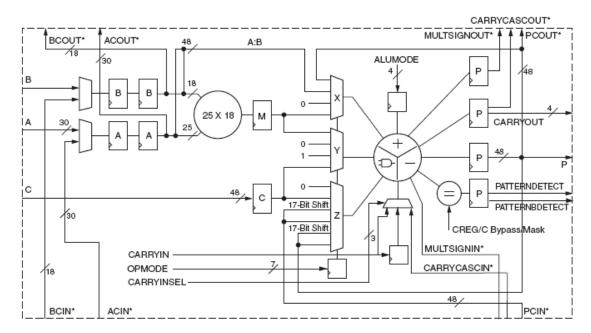

| 2.8  | The DSP block structure of Xilinx Virtex-5 [92]                                                                                                                                                                                                                                                                                                                                | 17 |

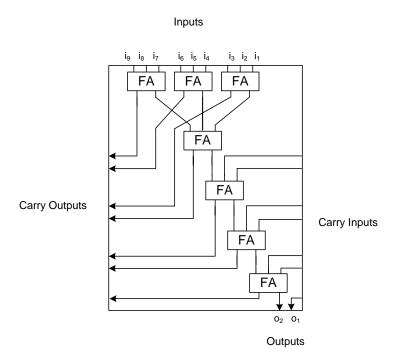

| 2.9  | Ripple carry adder (RCA) versus carry save adder (CSA). In RCA, carry propagates                                                                                                                                                                                                                                                                                               |    |

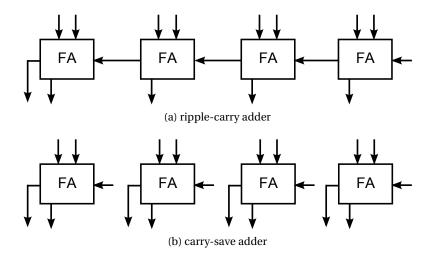

|      | through the full-adders, while in CSA, no carry propagation occurs. $\ \ldots \ \ldots$                                                                                                                                                                                                                                                                                        | 18 |

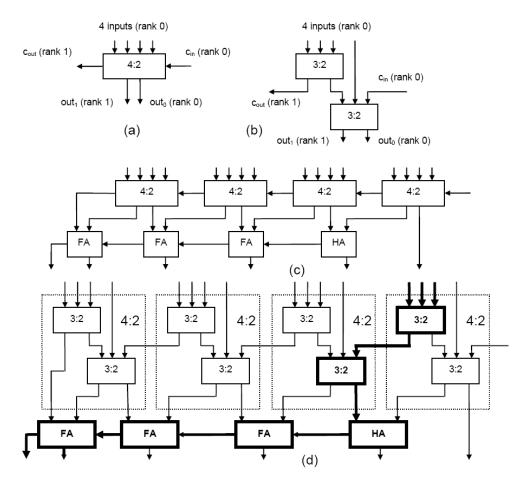

| 2.10 | Example of an arithmetic compressor. (a) 4:2 compressor I/O diagram; (b) 4:2 compressor architecture; (c) 4-ary adder built from an array of 4:2 compressors followed by an RCA; (d) illustration of the interconnect between consecutive 4:2 compressors: although the array has the appearance of an RCA in Figure 2.10c, the carry chain only goes through two compressors. | 21 |

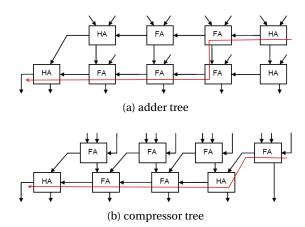

| 2.11 | Adder tree versus compressor tree. Two implementations of a 4-bit ternary adder using (a) an adder tree, i.e., two RCAs; and (b) a compressor tree, i.e., a CSA followed by an RCA. The compressor tree implementation eliminates the delay of two XOR gates from the critical path                                                                                            | 22 |

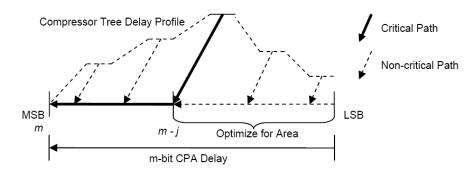

| 2.12 | Illustration of the critical path delay through a compressor tree of a multiplier, including that of the final CPA. The critical path typically includes the $j$ most significant bits of the final CPA; the portion of the final CPA that computes the $m-j$ least significant bits can be optimized for area rather than for speed, as long as it does not become critical   | 22 |

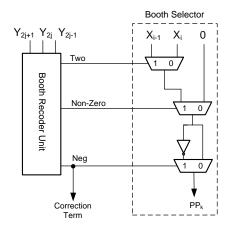

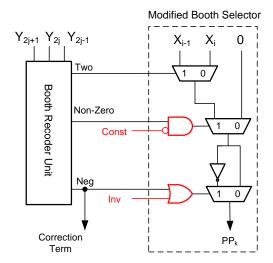

| 2.13 | The PPG unit of the Radix-4 Booth multiplier. Based on the output of the booth encoder, the right PP is generated by the Booth selector. The input to the Booth encoder is the multiplier, $Y$ , and the input to the Booth selector is the multiplicand, $X$ .                                                                                                                | 23 |

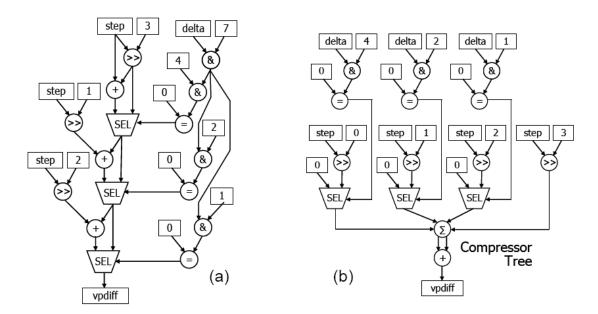

| 3.1  | A kernel of the adpcm benchmark, originally written in C [53]. (a) a dataflow graph of the circuit is shown following if-conversion [2]; and (b) rewritten to merge three addition operations into a compressor tree [86]                                                                                                                                                      | 26 |

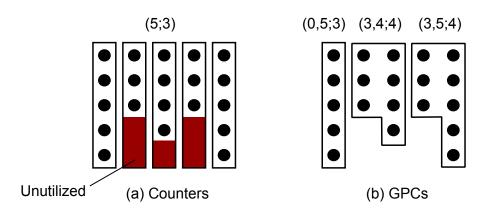

| 3.2  | In the FPGA implementation, GPCs are more flexible and efficient than parallel counters for compressing bits. Fewer blocks are required to map the same bits, using GPCs as the mapping blocks. Here, we assume that the GPCs and counters have the same area and delay, when they are mapped on FPGAs                                                                         | 28 |

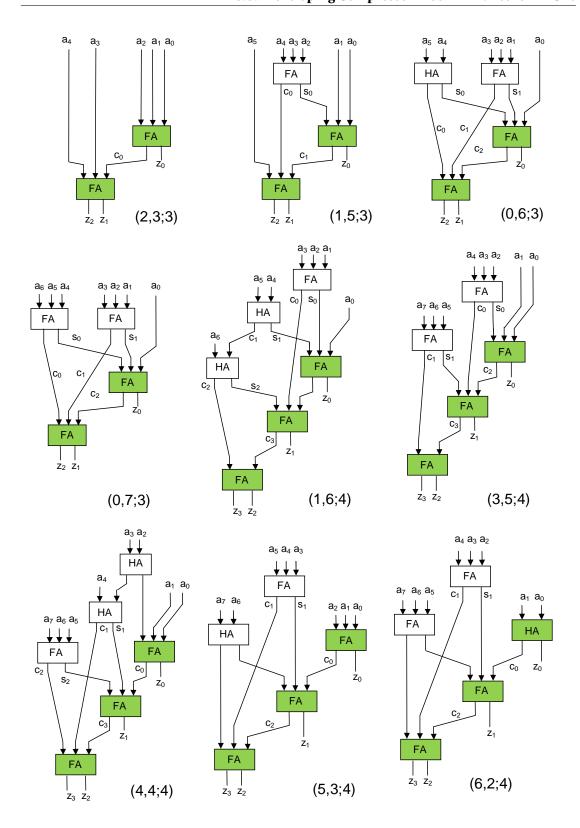

| 3.3  | The covering GPCs listed in Tables 3.1 and 3.2 as networks of full- and half-adders. The shaded full- and half-adders are synthesized on the carry chains                                                                                                                                                                                                                      | 29 |

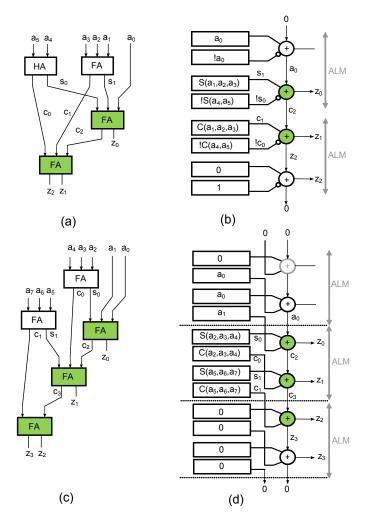

| 3.4  | A (0,6;3) GPC implemented at the circuit level (a) and synthesized on ALMs and carry chains using Arithmetic Mode (b). A (3,5;4) GPC implemented at the circuit level (c) and synthesized on ALMs and carry chains using Shared Arithmetic Mode (d)                                                                                                                            | 30 |

| 3.5  | Arithmetic Mode (d)                                                                                                                                                                                                                                                                                                                                                            | 30 |

| 5.5  | Slice (b) using the carry chain.                                                                                                                                                                                                                                                                                                                                               | 32 |

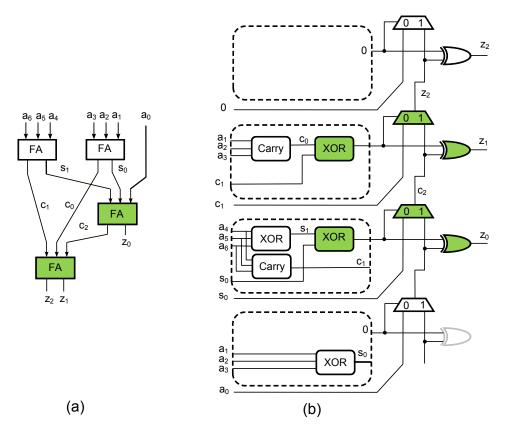

| 3.6   | Example of abutting GPCs on the carry chains of FPGAs. (a) By abutting two (0,6;3) GPCs on Stratix-III, which are implemented using the same (Arithmetic) mode, an ALUT can be shared between two GPCs. (b) Two (0,7;3) GPCs on Virtex-5 are abutted by sharing on LUT. Only portions of both GPCs are shown |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                      | 34 |

| 3.7   | •                                                                                                                                                                                                                                                                                                            | 36 |

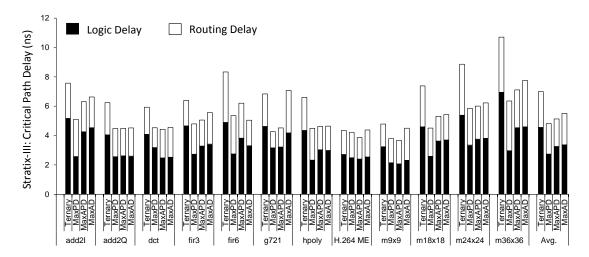

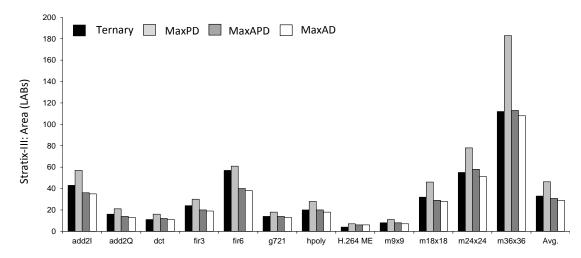

| 3.8   | The critical path delay of Ternary, MaxPD, MaxAPD, MaxAD decomposed into                                                                                                                                                                                                                                     | 38 |

| 3.9   |                                                                                                                                                                                                                                                                                                              | 39 |

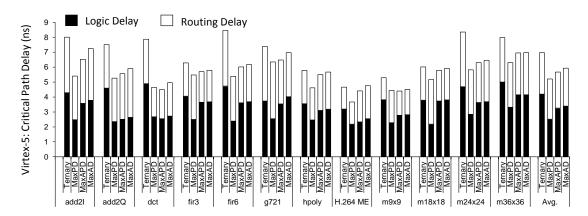

|       | The critical path delay of Ternary, MaxPD, MaxAPD, MaxAD decomposed into                                                                                                                                                                                                                                     | 40 |

| 2 1 1 |                                                                                                                                                                                                                                                                                                              |    |

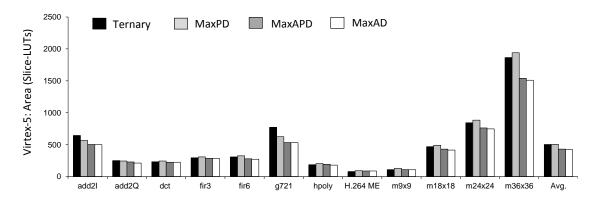

| 3.11  | Area usage (LUTs) of the four synthesis methods on Virtex-5                                                                                                                                                                                                                                                  | 40 |

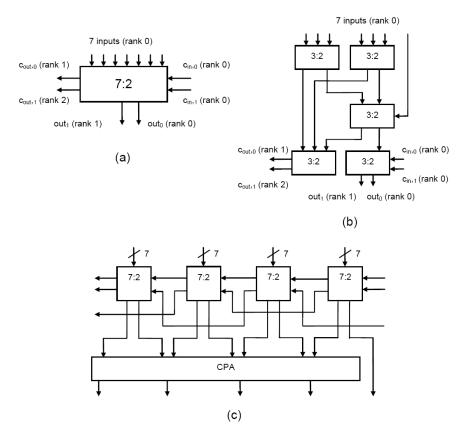

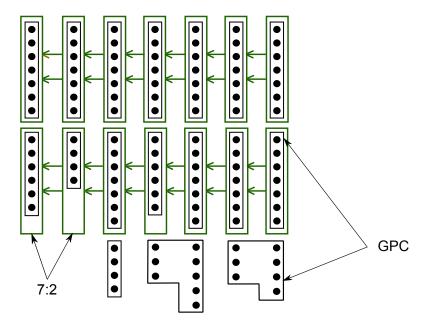

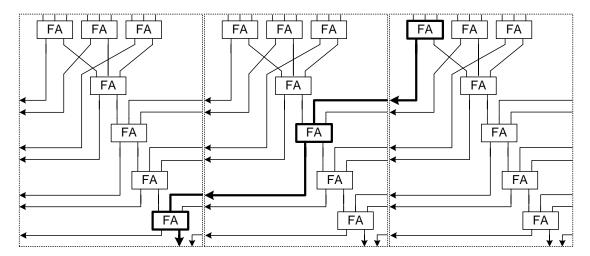

| 4.1   | (a) 7:2 compressor I/O diagram; (b) 7:2 compressor architecture; (c) illustration                                                                                                                                                                                                                            |    |

|       | of the interconnection pattern between consecutive 7:2 compressors                                                                                                                                                                                                                                           | 47 |

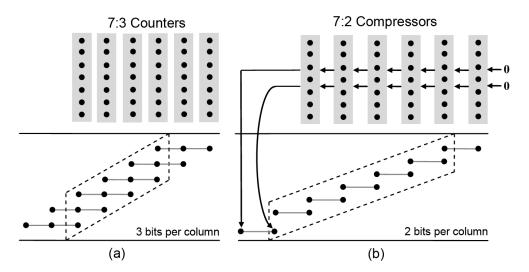

| 4.2   | Compression ratio difference between counters and compressors. (a) Covering                                                                                                                                                                                                                                  |    |

|       | a set of columns with 7:3 counters yields three bits per column in the output;                                                                                                                                                                                                                               |    |

|       | (b) using 7:2 compressors reduces the number of bits per column to two. Con-                                                                                                                                                                                                                                 |    |

|       | tiguous columns covered with 7 : 3 counters can be converted to 7 : 2 compressors.                                                                                                                                                                                                                           | 48 |

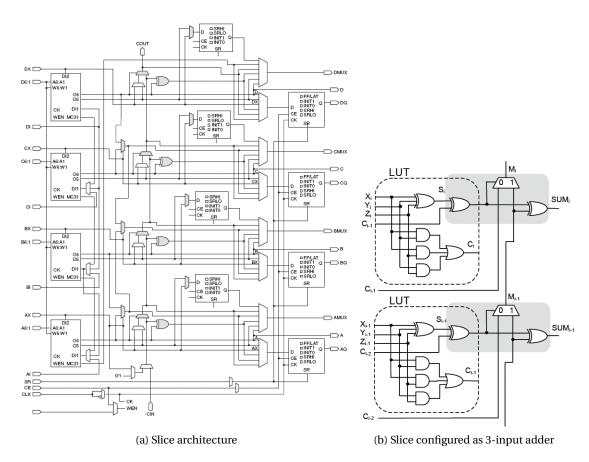

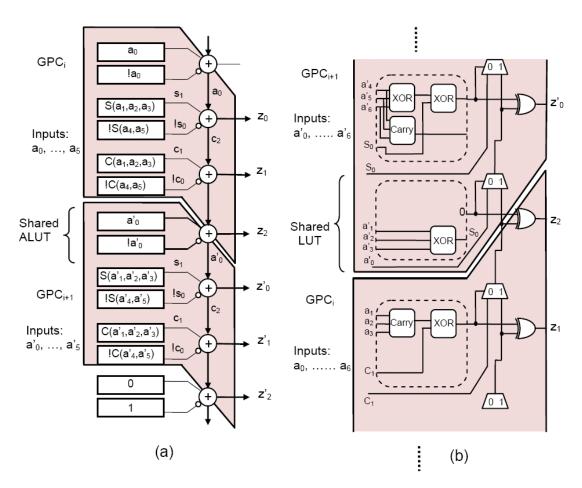

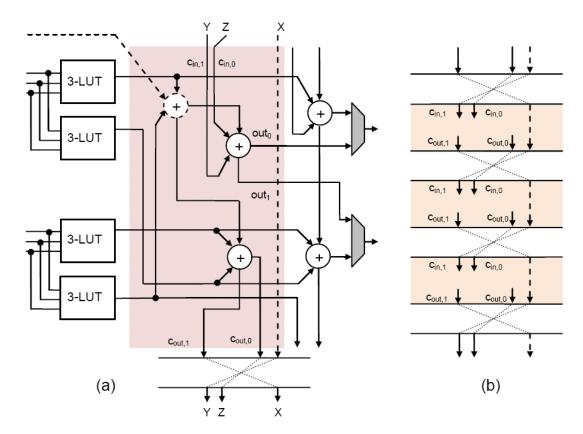

| 4.3   | Logic block architecture with new hard-logic.(a) Enhanced version of the Shared                                                                                                                                                                                                                              |    |

|       | Arithmetic Mode of the Altera ALM; new carry chains, shown in gray, allow the                                                                                                                                                                                                                                |    |

|       | ALM to be configured as a 7:2 compressor. Two additional multiplexers are                                                                                                                                                                                                                                    |    |

|       | required to select between the two <i>sum</i> outputs of the 7:2 compressor and                                                                                                                                                                                                                              |    |

|       | ternary adder—already present in the ALM; (b) pattern of carry-propagation for                                                                                                                                                                                                                               |    |

|       | the 7:2 compressor                                                                                                                                                                                                                                                                                           | 49 |

| 4.4   | Mapping to the logic block of Figure 4.3a. The <i>first</i> step is to cover the bits with                                                                                                                                                                                                                   |    |

|       | the GPCs, using the mapping heuristic of Chapter 3. The <i>second</i> step is to replace                                                                                                                                                                                                                     |    |

|       | contiguous single column GPCs with 7:2 compressors                                                                                                                                                                                                                                                           | 51 |

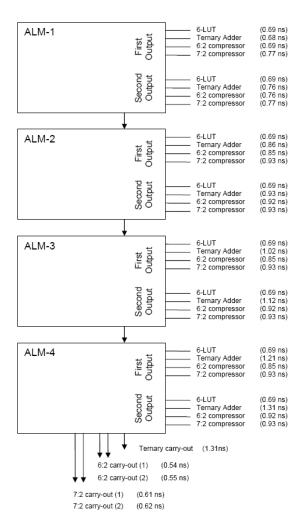

| 4.5   | Combinational delays of the ALM outputs in a LAB, including propagation delays                                                                                                                                                                                                                               |    |

|       | along the carry chains                                                                                                                                                                                                                                                                                       | 53 |

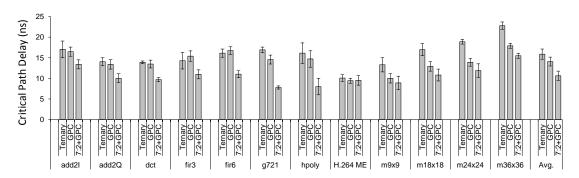

| 4.6   | The critical path delay for each benchmark and compressor tree synthesis                                                                                                                                                                                                                                     |    |

|       | methodology, shown with a 95% confidence interval                                                                                                                                                                                                                                                            | 55 |

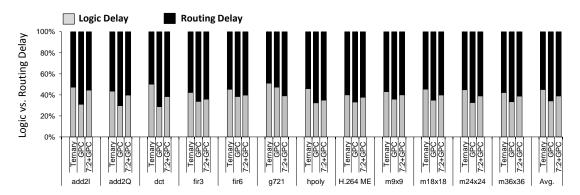

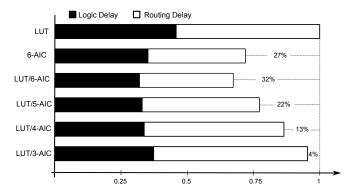

| 4.7   | On average, the percentage of critical path delay due to logic and routing for                                                                                                                                                                                                                               |    |

|       | each benchmark                                                                                                                                                                                                                                                                                               | 56 |

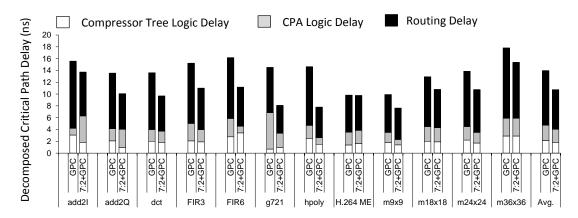

| 4.8   | The minimum critical path for each benchmark and synthesis method, decom-                                                                                                                                                                                                                                    |    |

|       | posed into logic delays within the compressor and CPA, and routing delay                                                                                                                                                                                                                                     | 58 |

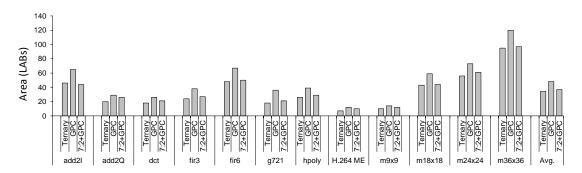

| 4.9   | The area (LABs) required for each benchmark and compressor tree synthesis                                                                                                                                                                                                                                    |    |

|       | method                                                                                                                                                                                                                                                                                                       | 59 |

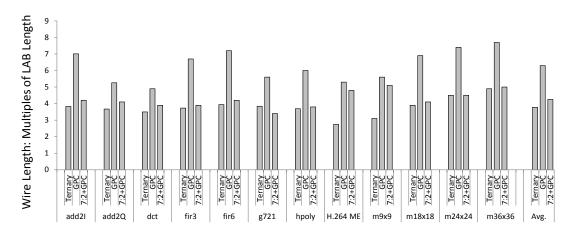

| 4.10  | Average wirelength per net for each benchmark and compressor tree synthesis                                                                                                                                                                                                                                  |    |

|       |                                                                                                                                                                                                                                                                                                              | 60 |

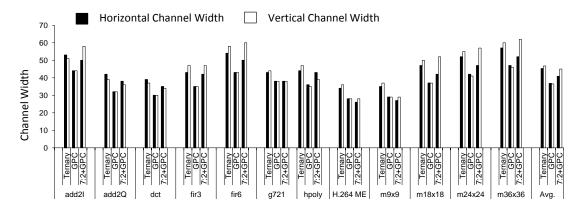

| 4.11  | The minimum channel width in the $x$ and $y$ directions for which each benchmark                                                                                                                                                                                                                             |    |

|       | is routable for each compressor tree synthesis method                                                                                                                                                                                                                                                        | 61 |

|       |                                                                                                                                                                                                                                                                                                              |    |

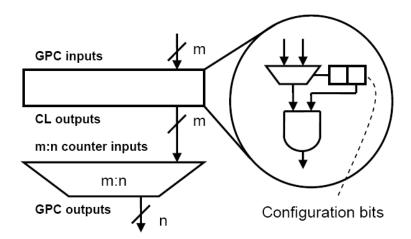

| 5.1  | Architecture of an m-input, n-output programmable GPC. The programmable GPC is the building logic block of FPCA                                                                                                                                                                                                                                  | 65 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

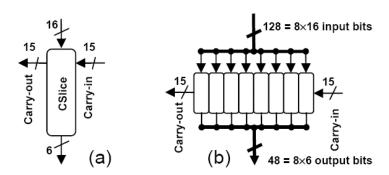

| 5.2  | FPCT structure, consisted of 8 CSlices. (a) I/O interface to a CSlice (b) and an 8-CSlice FPCT                                                                                                                                                                                                                                                   | 66 |

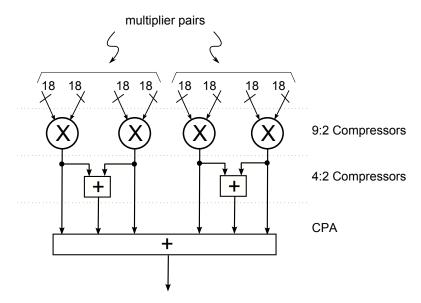

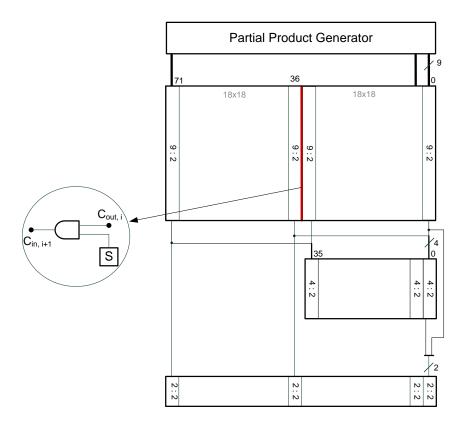

| 5.3  | Conceptual illustration of the reference DSP block architecture. Four $18 \times 18$ multiplies along with the adders that are required for either constructing larger multipliers or complex arithmetic multipliers                                                                                                                             | 68 |

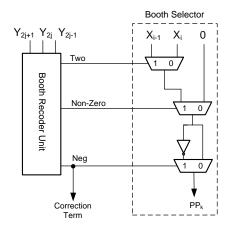

| 5.4  | The Radix-4 Booth PPG unit. Booth encoder is shared between all PPs bits, but each bit of PP needs a separate Booth Selector unit                                                                                                                                                                                                                | 69 |

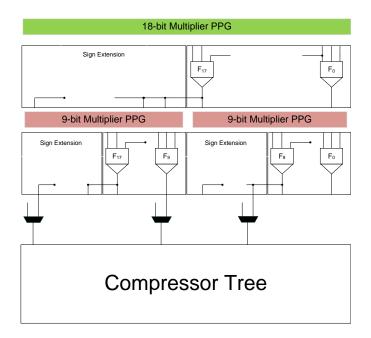

| 5.5  | Structure of the 9:2 compressor in the proposed DSP block. This compressor has nine inputs and two outputs, in addition to the carry inputs and outputs. All the inputs, including the carry inputs, have the same rank.                                                                                                                         | 70 |

| 5.6  | A chain of three 9:2 compressors. The longest path that a carry output can propagate includes two compressors, as shown in this figure. Hence, the delay of a 9:2 compressor layer remains constant when the number of compressors in the layer varies                                                                                           | 71 |

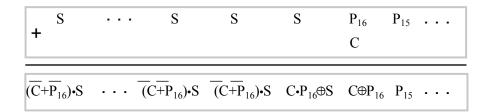

| 5.7  | Merging the ninth carry bit with the first PP. MSB bits of the PP from bit 16 are modified                                                                                                                                                                                                                                                       | 71 |

| 5.8  | The compressor tree structure of each multiplier pair in Figure 5.3. The compressor tree includes one layer of 9:2 compressors followed by one layer of 4:2 compressors and the final CPA adder. The 9:2 layer can be split into independent 9:2 layers at the multipliers boundaries by disconnecting the carry paths using the shown AND gates | 72 |

| 5.9  | Overlap between the PPG of two different multiplier configurations. Since the same PPRT is used for both configurations, several multiplexers are required to select between either the encoded or the sign bits of the two configurations                                                                                                       | 73 |

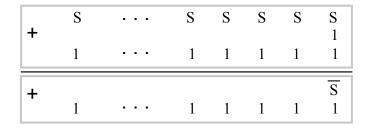

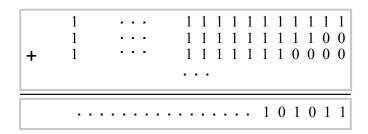

| 5.10 | Reducing the repetitive sign bits by adding with $\pm 1$                                                                                                                                                                                                                                                                                         | 73 |

| 5.11 | Reducing the constant numbers to one number                                                                                                                                                                                                                                                                                                      | 74 |

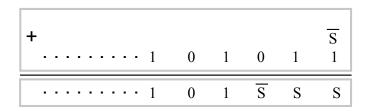

| 5.12 | Merging the constant number into first partial product                                                                                                                                                                                                                                                                                           | 74 |

| 5.13 | The modified Radix-4 Booth PPG encoder for resolving the conflicts of PPG parts of various multiplier bit-widths.                                                                                                                                                                                                                                | 75 |

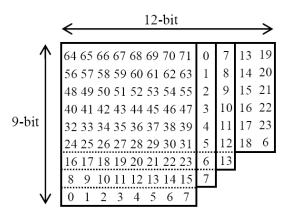

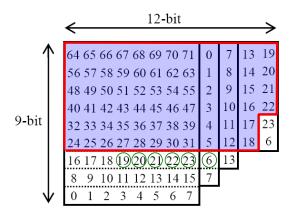

| 5.14 | The indices of the DSP Block inputs that are connected to each <i>Rectangular (RC)</i> block. RC-blocks are aligned for maximum input sharing, and each RC-block is connected to distinct DSP block inputs                                                                                                                                       | 76 |

| 5.15 | Block refinement. The underutilized column in the RC-block provides the opportunity to cover more bits in other columns. The circled indices are the mapping candidates, from which two can be covered.                                                                                                                                          | 77 |

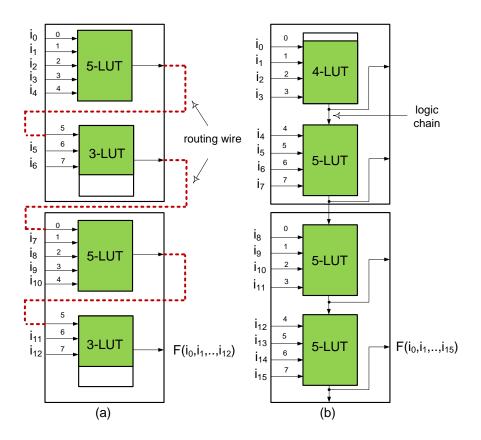

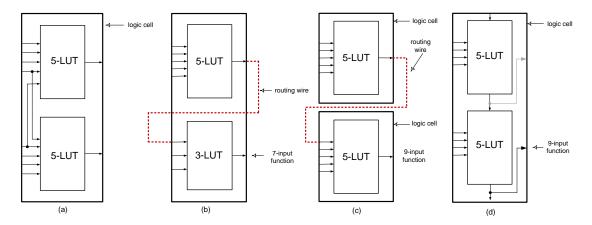

| 6.1  | Key idea. (a) Two logic blocks, each has eight inputs and two base 5-LUTs. Many 13-input logic functions can be mapped to a linear cascade of the base LUTs; routing resources are required to connect adjacent LUTs in the cascade. (b) A dedicated logic chain between adjacent LUTs eliminates the overhead due to routing resources and increases the input bandwidth of logic block. Many                                                                                                                                                                                                                                                |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

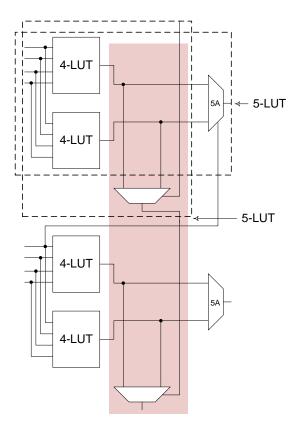

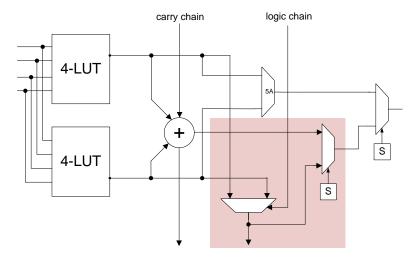

| 6.2  | 16-input logic functions can be mapped with the same number of available LUTs. Proposed configuration for the ALM, using the adder and the carry chain for generic logic synthesis. Each ALM can implement two chained 5-input functions                                                                                                                                                                                                                                                                                                                                                                                                      | 85 |

|      | with non-shared inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86 |

| 6.3  | (a) The Altera's ALM configured to implement two 5-input logic functions; ALM imposes the constraint that the two functions must share two inputs. (b) Using fracturable LUTs, a subset of 7-input logic functions can be synthesized on an ALM, but this requires routing a signal from one sub-LUT to the next. (c) To implement two cascaded 5-input functions with no common inputs, two ALMs are required. (d) All three of the preceding logic functions can be synthezed on the proposed logic block using the logic chain and without using the global routing network; moreover, the proposed cell can implement a subset of 9-input |    |

| 6.4  | logic functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88 |

| 6.5  | cascaded 5-LUTs with no shared inputs can be mapped to the new cell The logic chain integrated with the carry chain. In addition to the vertical multiplexer, a horizontal multiplexer is added to select between the sum output of the full-adder and the logic chain fanout; this multiplexer gives access to any point of the logic chain                                                                                                                                                                                                                                                                                                  | 90 |

| 6.6  | (a) Two chains intersecting at a shared node. (b) The shared node is assigned to one of the chains, breaking the other chain into two smaller sub-chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92 |

| 6.7  | The depths of different nodes in a sample DAG. The shaded nodes are part of other chains and hence not chainable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94 |

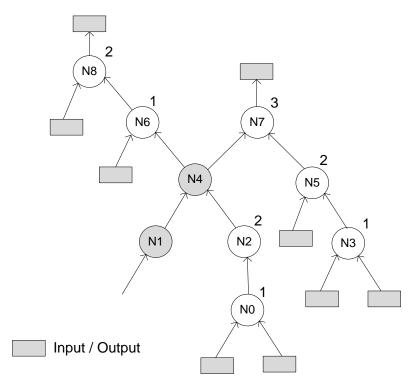

| 6.8  | Tool chain flow used for the experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95 |

| 6.9  | Number of logic blocks (ALMs) that are used in each method. On average, the introduction of our logic chain reduces the ALM usage by 4%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97 |

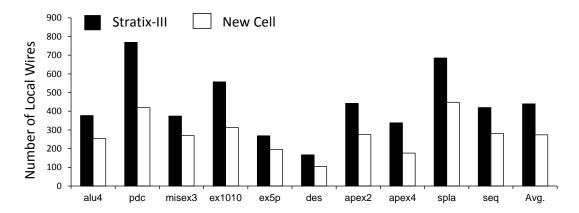

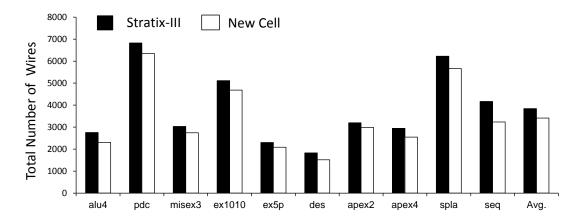

| 6.10 | The number of local interconnection wires—i.e., within a LAB—used for each benchmark. On average, the introduction of the logic chain reduces the number of local wires used by 37%                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98 |

| 6.11 | The number of global and local interconnection wires used for each benchmark, scaled by the length of the wires. On average, the introduction of the logic chain reduces the total number of wires used by 12%                                                                                                                                                                                                                                                                                                                                                                                                                                | 98 |

|      | reduces the total frumber of wifes used by 12/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

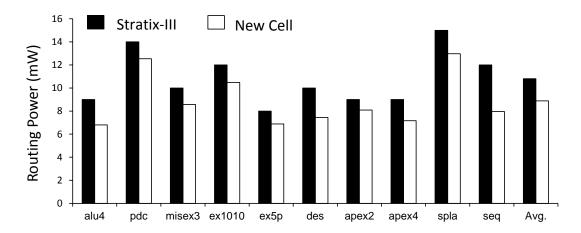

| 6.12 | Dynamic power consumption estimates for the routing network; as the logic chain reduces the number of programmable wires used, an average savings of 18% is obtained                                                                                                                                                                                                                                                                                                                                                                                               | 99  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

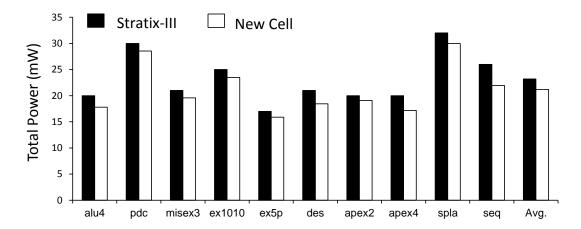

| 6.13 | Total (logic plus routing network) power consumption estimates; the logic chain reduces total power consumption by 10%, on average                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

| 6.14 | Critical path delay of each benchmark; the introduction of the logic chain marginally improves the critical path delay of most benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 |

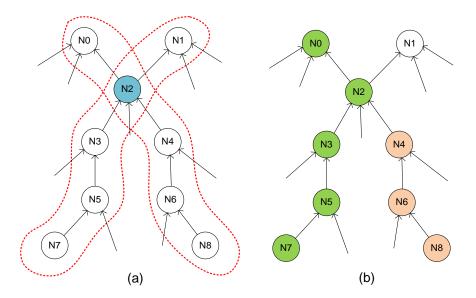

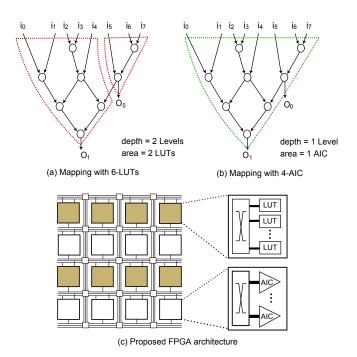

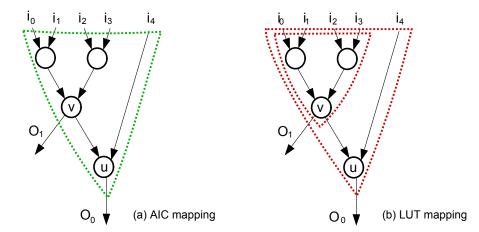

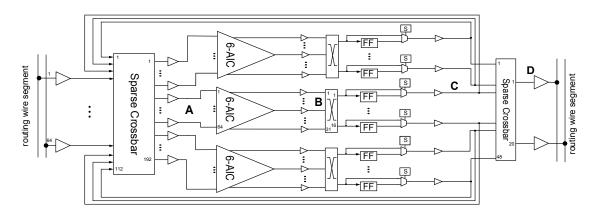

| 7.1  | Flexibility, bandwidth, cost, and delay. (a)–(b) <i>And-Inverter Cones (AICs)</i> can map circuits more efficiently than LUTs, because AICs are multi-output blocks and cover more logic depth due to their higher input bandwidth. (c) A possible integration of AIC electors in an EPCA architecture.                                                                                                                                                                                                                                                            | 100 |

| 7.2  | integration of AIC clusters in an FPGA architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 106 |

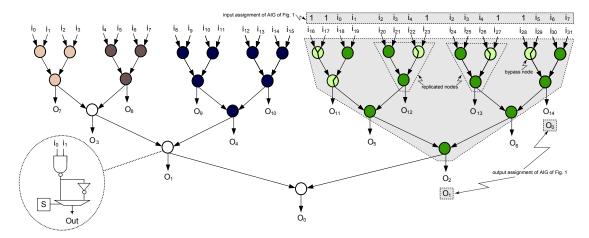

| 7.3  | Architecture of 5-AIC (AND-Inverter Cone), which has five levels of cells that are programmable to either AND or NAND gates. The 5-AIC can also be configured to 2-, 3-, and 4-AICs in many ways (highlighted cells show one possibility), without any need for extra hardware. The AIG of Figure 7.1 is mapped onto the right-hand side. To propagate a signal, we can configure a cell to the bypass mode (e.g., forcing one input to 1 when this is operated as an AND). Moreover, some AIG nodes need to be replicated when the fanout of an internal value is |     |

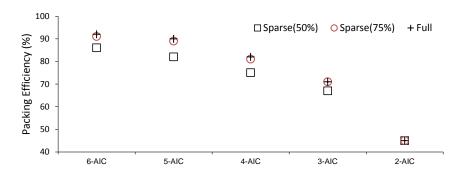

| 7.4  | larger than one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 109 |

| 7.5  | of $v$ , while in LUT mapping, no common cone exist for any two nodes (b) The packing efficiency of three crossbar connectivity scenarios: 50%, 75%, and 100%. The allowed cone depth in technology mapping is varied to study the effect of AIC size on the packing quality                                                                                                                                                                                                                                                                                       |     |

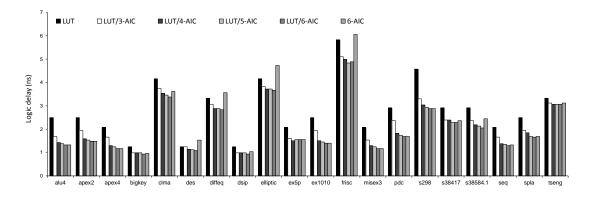

| 7.6  | Structure and delay paths of an AIC cluster with three 6-AICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 117 |

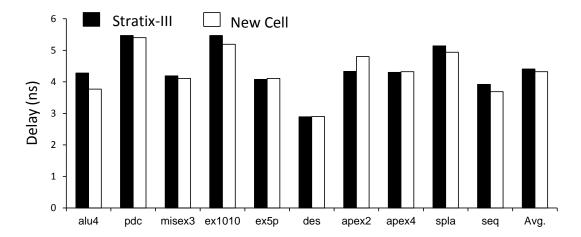

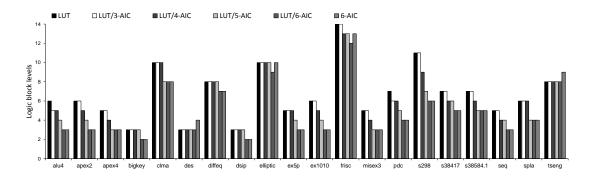

| 7.7  | Logic delay of all benchmarks in the original FPGA (LUT), for the FPGA composed only of AIC (6-AIC), and for a hybrid FPGA (LUT/6-AIC)                                                                                                                                                                                                                                                                                                                                                                                                                             | 118 |

| 7.8  | Number of logic blocks (both LUTs and AICs) on the critical path. $\ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 119 |

| 7.9  | Geometric mean of normalized total logic and routing delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 120 |

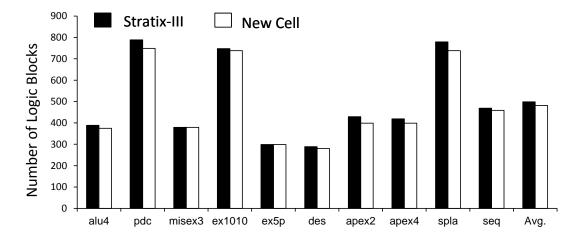

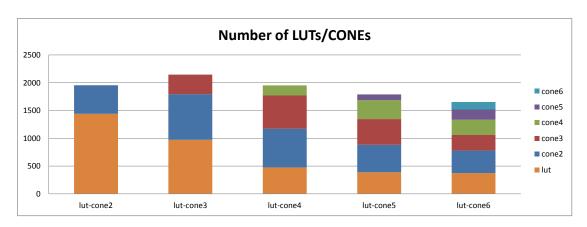

| 7.10 | Number and type of logic blocks used in the various architectures and with the various mapping strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120 |

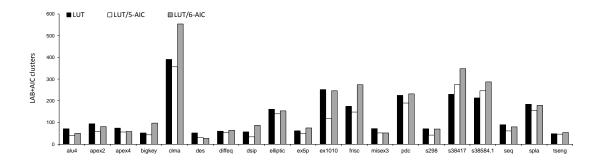

| 7.11 | Area measured as the total number of clusters used, completely or partially. LABs and AIC clusters occupy approximately the same area. On average, LUT/5-AIC                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | uses 16% less resources than LUT-only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 121 |

| 8.1 | Achievements of this thesis in closing the delay and area gaps between FPGAs     |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | and ASICs. By increasing the flexibility of the hard-logic, we improved the per- |     |

|     | formance of carry-save-based arithmetic circuits. Moreover, we enhanced both     |     |

|     | performance and area of generic logic implementation on FPGAs, by introducing    |     |

|     | novel architectures for the soft-logic                                           | 129 |

|     |                                                                                  |     |

# **List of Tables**

| 3.1 | Covering GPC libraries for the Stratix-III (left) and Virtex-5 (right) FPGAs. The                      |     |

|-----|--------------------------------------------------------------------------------------------------------|-----|

|     | delay unit is <i>ns</i> and the area unit for Stratix-III is <i>ALM</i> and for Virtex-5 is <i>LUT</i> | 33  |

| 3.2 | The CD value for each GPC, and the PD, AD, and APD values for the Stratix-III                          |     |

|     | and Virtex-5 GPC libraries listed in Table 3.1. The GPC with the highest priority                      |     |

|     | in each case has been highlighted                                                                      | 35  |

| 3.3 | Benchmark summary.                                                                                     | 38  |

| 4.1 | Description of the three synthesis methodologies used in the experiments                               | 55  |

| 5.1 | Operation modes of the modified Radix-4 Booth PPG                                                      | 74  |

| 5.2 | Different rectangular blocks that are used for the mapping of the inputs bits of                       |     |

|     | the adder tree                                                                                         | 75  |

| 5.3 | Overhead of adding new features to the base DSP block. The delay numbers                               |     |

|     | show the $18 \times 18$ multiplier delay in each case                                                  | 79  |

| 5.4 | Delay comparison of the multipliers in our DSP block with the Stratix-II DSP                           |     |

|     | block. For our DSP block, these numbers are achieved when all features pre-                            |     |

|     | sented in Table 5.3 are included                                                                       | 79  |

| 5.5 | Delays (ns) of multi-input addition benchmarks, when they are mapped on                                |     |

|     | different logic blocks                                                                                 | 80  |

| 5.6 | Areas of multi-input addition benchmarks, when they are mapped on different                            |     |

|     | logic blocks.                                                                                          | 80  |

| 6.1 | Distribution of LUT sizes in different benchmarks                                                      | 96  |

| 6.2 | Chaining heuristic statistics for different benchmarks                                                 | 97  |

| 7.1 | AICs have less configuration bits than LUTs, while they can implement circuits                         |     |

|     | with a much greater number of inputs (e.g., a 6-AIC includes eight times more                          |     |

|     | inputs than a typical 6-LUT)                                                                           | 110 |

| 7.2 | Areas of different components in an AIC cluster and in a LAB, measured in units                        |     |

|     | of minimum-width transistor area                                                                       | 117 |

| 7.3 | Delays of different of paths in the AIC cluster of Figure 7.6                                          | 118 |

| 7.4 | Average ratio of intra cluster wires for the different mapping scenarios                               | 119 |

| 7.5 | Average wire length in units of one CLB segments.                                                      | 122 |

# 1 Introduction

With the increase of *Application-Specific Integrated Circuit (ASIC)* design costs and the pressure of time-to-market, *Field-Programmable Gate Arrays (FPGAs)* continue to replace ASICs in many low- and mid-volume products. The cost of designing ASICs, including *Non-Recurring Engineering (NRE)*, mask, and development costs, is increasing every year as Moore's law progresses and applications get extremely complicated. Issues such as power, signal integrity, clock tree synthesis, and manufacturing defects can add significant risk and time-to-market delays. FPGAs offer a viable and competitive option to ASIC development by reducing the risk of re-spins, high NRE costs, and time-to-market delays, as an off-the-shelf FPGA has already been fabricated and verified.

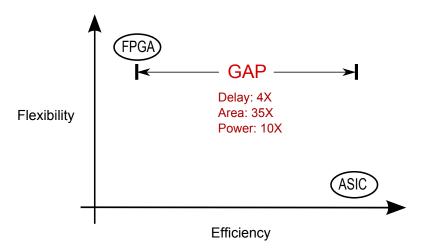

Although they outperform traditional software, FPGAs have a significant *gap* in performance, power consumption, and area utilization with ASICs. A recent research by Kuon and Rose [50] indicate that FPGAs require approximately 20 to 35 times more area, have a speed roughly three to four times slower, and consume roughly 10 times more dynamic power than standard-cell ASICs. Figure 1.1 pictorially illustrates the FPGA and ASIC gaps in the flexibility and efficiency design space. As shown, FPGAs are the most flexible choice for implementing applications, but their efficiency is low; ASICs offer the best efficiency, but they are not flexible. This is the reason that ASICs are still the first choice for implementing high-volume applications, in which the unit cost remains low.

In the past, many researchers have attempted to enhance FPGAs, but despite more than 20 years of research, FPGAs are way behind ASICs in efficiency, as described in the previous paragraph. Previous studies have shown that without innovations in FPGA architecture, advances in device technology, alone, cannot noticeably shrink this gap between FPGAs and ASICs. In this thesis, we introduce a *roadmap* for improving FPGAs, and we show how each contribution of the thesis fits into the roadmap. In the next section, we first describe the motivation of this thesis, and then we introduce the mentioned roadmap and the thesis contributions.

Figure 1.1: FPGA versus ASIC. FPGA is highly flexible and less efficient, while ASIC is highly efficient and less flexible. The flexibility of FPGA comes at a price, which is the delay, area and power gap between FPGAs and ASICs [50].

### 1.1 Thesis Motivation

Early FPGAs were created with the purpose of implementing any possible digital circuit; hence, they had a highly flexible structure consisting of fully programmable logic blocks—*Look-Up Tables (LUTs)*—and a routing network. This flexibility and its consequent advantages do not come for free: logic blocks and routing resources tend to be large and slow. Later, FPGA vendors embedded ASIC-like logic blocks into FPGAs to soften the inefficiency problem of FPGAs. These new blocks have little flexibility and are dedicated to critical arithmetic operations that occur frequently in many signal processing applications. As a result, the FPGA structure became heterogeneous, comprised of the original flexible logic blocks and new dedicated blocks, which are called *soft-* and *hard-logic* in this thesis, respectively.

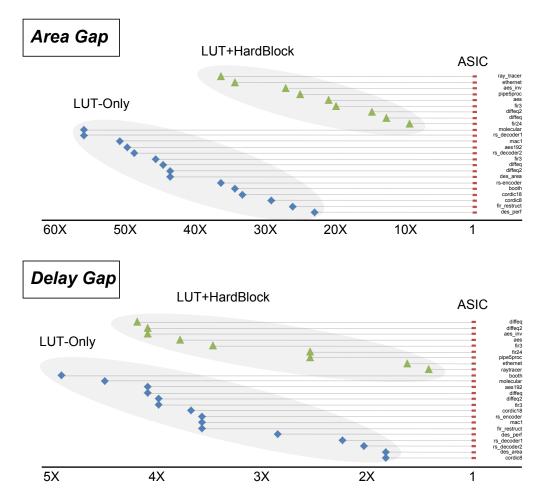

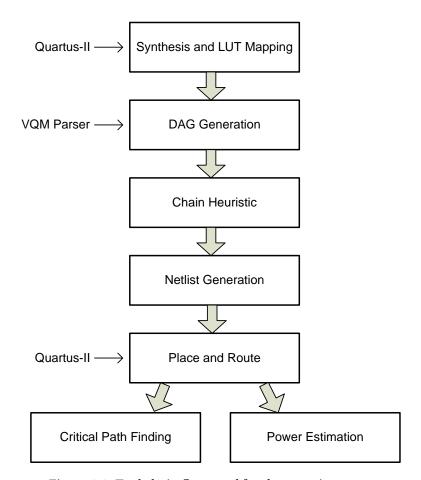

Although the hard-logic can improve FPGAs when it is utilized efficiently, due to its inflexible nature, many applications cannot take advantage of it. In [50], Kuon and Rose have evaluated the impact of the hard-logic on narrowing the gaps between FPGAs and ASICs. The results of this study for the area and delay gaps are illustrated in Figure 1.2. As shown, the area gap can be improved substantially when the hard-logic is actually used. In principle, operations that are implemented by the hard-logic are also implementable by the soft-logic. But, the area that is consumed by the soft-logic is much larger than the area of the dedicated implementation. Though, due to the inflexible nature of the dedicated blocks, it is quite possible that these blocks are not utilized in many applications, which makes the area efficiency problem even worse.

On the other hand, the impact of the hard-logic on delay improvement is little compared to the area improvement. Kuon and Rose [50] give three reasons for that: (1) the hard-logic is less flexible and it might be underutilized, (2) some parts of applications still need to be mapped to the soft-logic, which is inherently slow, and (3) the cost of routing to the (stand-alone)

Figure 1.2: Effect of using hard-logic in FPGAs in narrowing their area and delay gaps with ASICs [50]. Although the hard-logic can significantly reduce the area gap, its effect on the delay gap is not considerable for three reasons: (1) Underutilization of the hard-logic, (2) high routing cost to the stand-alone hard-logic, and (3) the presence of the FPGAs soft-logic in critical-paths.

hard-logic is high and the interconnection delay can be considerable. This implies that the impact of the hard-logic on delay improvement of an application is highly dependent on how the rest of the application is implemented by the soft-logic.

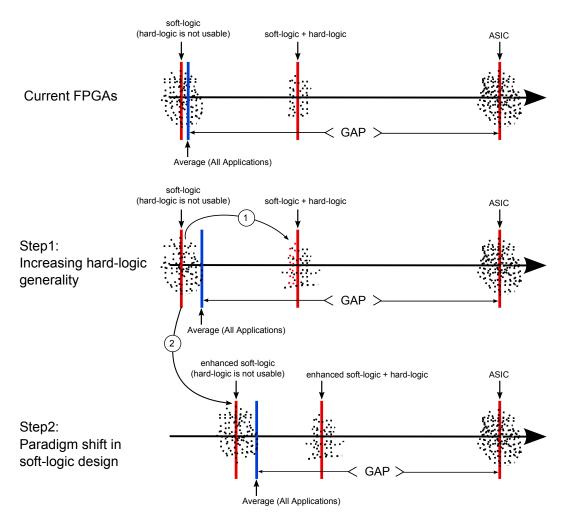

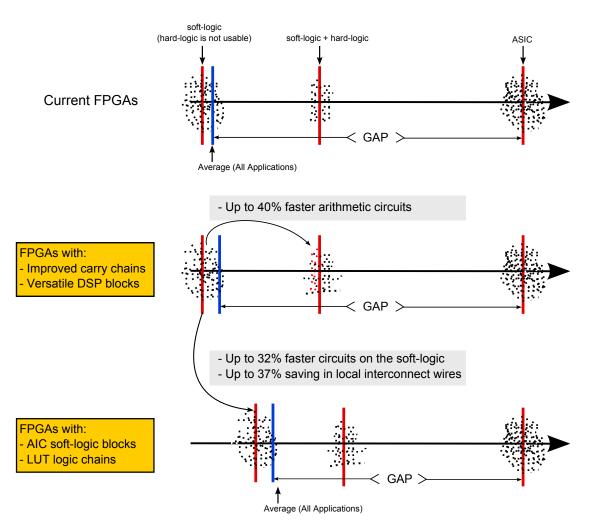

In summary, current heterogeneous FPGAs have logic blocks that suffer from either *inflex-ibility* or *inefficiency*, which both limit the enhancement of FPGAs. This fact motivated us to approach the gap problem from two perspectives, as shown in Figure 1.3. The top plot in this (conceptual) figure illustrates the current efficiency gap between FPGAs and ASICs. In this figure, it is assumed that the same applications are used for comparing FPGAs against ASICs, but for FPGAs, these applications are categorized into two sets: (1) the first set contains the applications that can exclusively use the soft-logic for their implementation, and (2) the second set contains the ones that use a mixture of the soft- and hard-logic. Typically, more applications fall into the first set compared to the second. Hence, the overall average of the

Figure 1.3: Thesis roadmap for improving FPGAs. To bridge the FPGAs and ASICs efficiency gap, two complementary steps are required: (1) increasing the generality of the hard-logic such that more applications benefit from it, and (2) improving the soft-logic efficiency, which impacts all applications, through novel logic blocks.

FPGAs efficiency tends to be closer to the average efficiency of the applications in the first set.