### Design of a Discrete-Component Impulse-Radio Ultra Wide-Band (IR-UWB) Testbed and Design of a Very Low-Power IR-UWB Transmitter in CMOS Technology

THÈSE Nº 5307 (2012)

PRÉSENTÉE LE 9 MARS 2012 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR GROUPE SCI STI CD PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

### Edmund James COLLI-VIGNARELLI

acceptée sur proposition du jury:

Prof. A. Skrivervik Favre, présidente du jury Dr C. Dehollain, Prof. J.-Y. Le Boudec, directeurs de thèse Prof. M. Green, rapporteur Dr N. Jöhl, rapporteur Dr B. Kawkabani, rapporteur

# Abstract

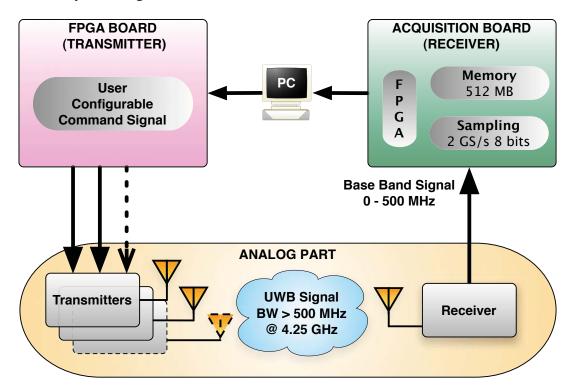

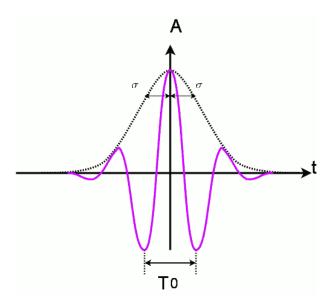

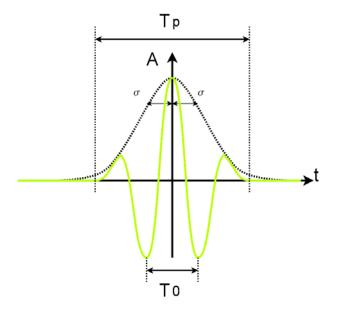

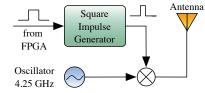

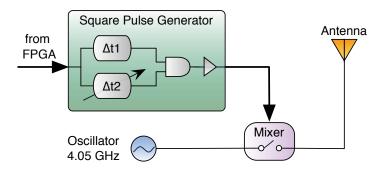

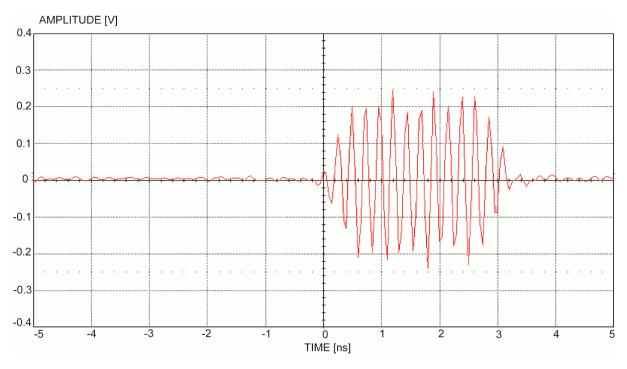

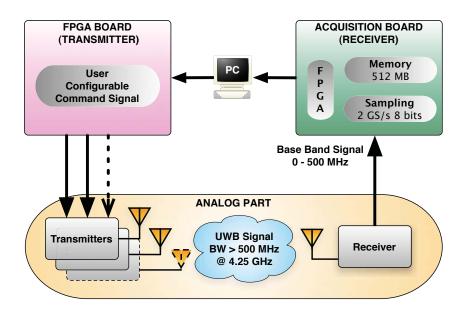

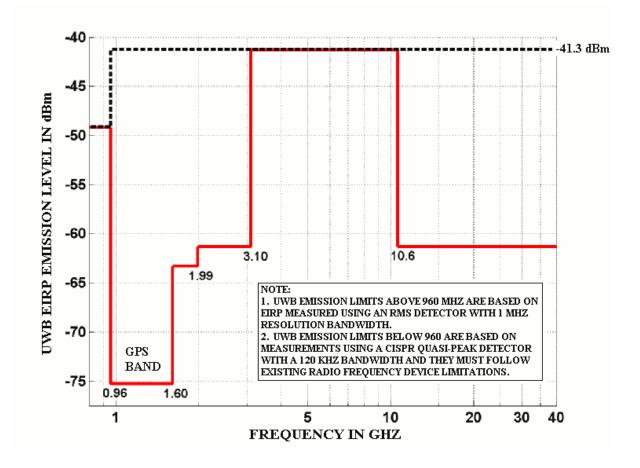

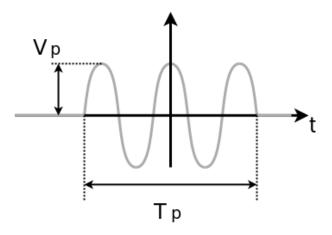

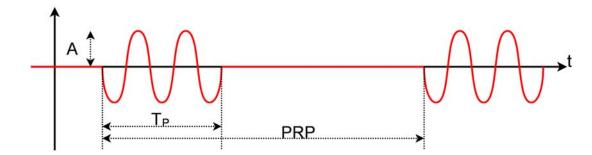

This work presents, in a first part, a testbed for Impulse-Radio Ultra-Wideband (IR-UWB) communication for validating the possibility to do such radio communications. The UWB radio is a radio technique that consists to send extremely short impulses (few nano-seconds) which have a rich spectral content over several hundreds of MHz. The UWB radio we consider here works in the 4.0 to 4.5 GHz frequency range.

The IR-UWB radio allows high datarates and small power consumption. In addition, it allows localising precisely a mobile transmitter because UWB signal are similar to those of radar.

As UWB radio is different than conventional narrow-band radio, the algorithms used for communication and synchronisation between UWB devices need to be reconsidered. The UWB testbed presented here allows validating and experimenting these algorithms in order to improve and publish them with significant results.

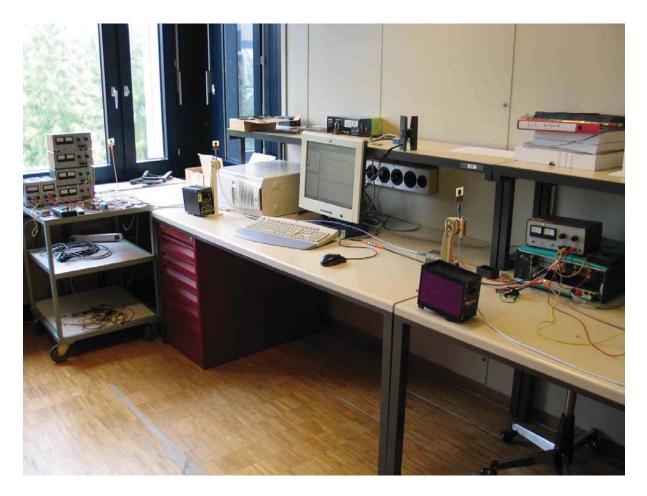

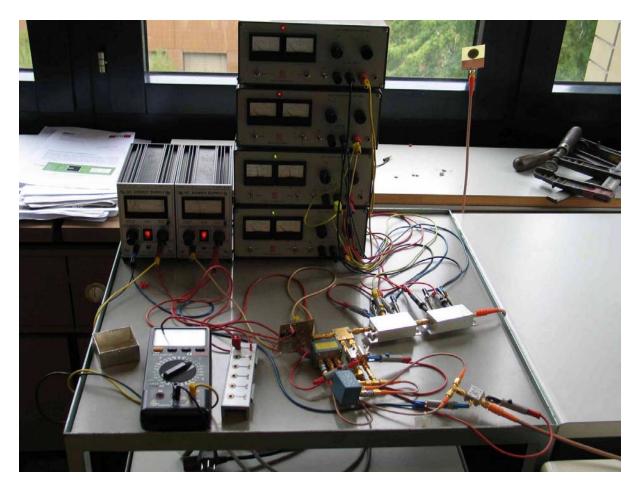

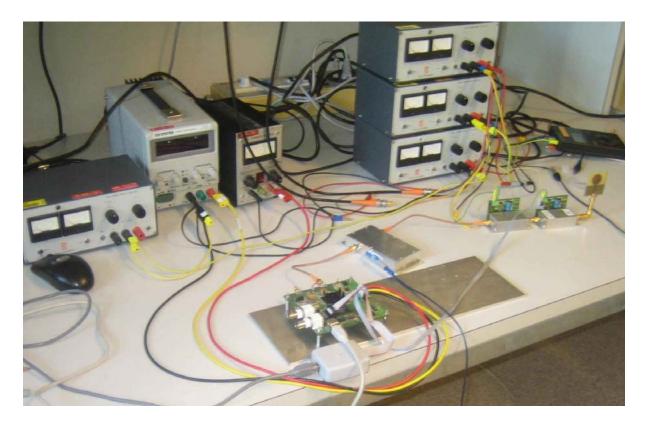

There are several already published UWB testbed but few of them are described with enough details to be rebuilt as they are by other researchers or scientists in order to reproduce an experiment. In addition, building such a testbed requires an advanced knowledge not only in electronics and microwave theory but also on practical aspects of building such devices. However, many researchers have not this knowledge because they work on another field and thus, we provide a detailed description about the design and construction of the parts of the testbed in order to help anyone who wants to build the testbed. It is also possible to modify the design of the testbed in order that it works in another frequency range by following the methodology of design we used. The testbed is entirely designed with off-the-shelf discrete components and can be built at a relatively low price. We begin our work by presenting first a very simple but viable UWB testbed in order to understand the principles of UWB radio and to justify further design consideration made later in the work. We also present a mathematical study of UWB signals that allows to rapidly determine their specifications in order to generate a true well shaped UWB signal.

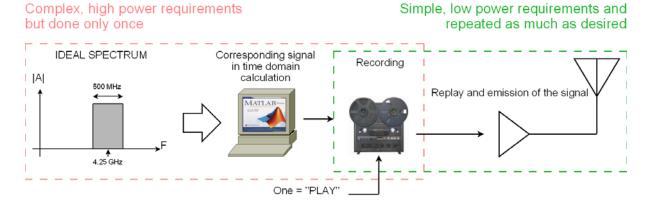

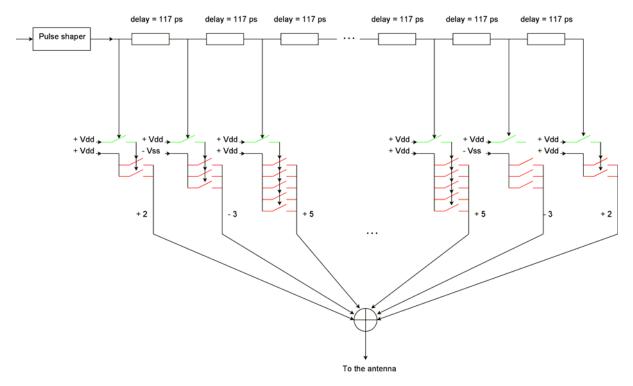

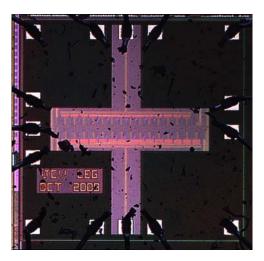

This work presents, in a second part, the design and construction of an integrated lowpower UWB transmitter in CMOS 0.18um technology. As UWB radio is by nature low-power, we present a novel architecture for generating an arbitrary signal by consuming the smaller as possible amount of energy. We use this architecture for generating the UWB impulse that we determined mathematically in order to have a shape that optimize the spread of energy in the available frequency range (4.0 to 4.5 GHz as for the testbed). We present three prototypes of the architecture where one is patented.

**Keyworks** UWB, Ultra-Wideband, IR, Impulse-Radio, testbed, discrete-components, low-power transmitter, CMOS 0.18um

# Abrégé

Cette thèse présente, dans un premier temps, une plate-forme de test pour radio impulsionnelle à très large bande (ULB) afin de valider expérimentalement la faisabilité d'un tel type de communication. La radio impulsionnelle ULB est une technique radio qui consiste à envoyer des signaux impulsionnels très courts (quelques nano-secondes) ayant un contenu spectral riche et large de plusieurs centaines de MHz. La radio considérée ici émet dans la bande 4.0 à 4.5 GHz.

La radio ULB permet d'obtenir des débits élevés avec une faible consommation d'énergie. Elle permet en outre, la possibilité de localiser précisément la position de l'émetteur car la nature de ses signaux est proche de ceux du radar.

Comme la radio ULB est de nature différente de la radio conventionnelle à bande étroite centrée sur une porteuse, les algorithmes utilisés pour communiquer et synchroniser les émetteurs et récepteurs de ce type de radio doivent être entièrement revisités. La plate-forme de test que nous présentons ici permet justement de valider et expérimenter ces algorithmes afin de les améliorer et les publier.

De nombreuses plate-formes de test pour radio ULB sont décrites dans les publications mais peu d'entre-elles le sont de manière suffisamment précise pour que d'autres équipes de chercheurs puissent la reconstruire à l'identique afin de refaire ou d'améliorer une expérience. De plus, construire une telle plate-forme demande des connaissances avancées en électronique, et ce également en ce qui concerne la réalisation pratique des éléments de cette plate-forme. Or, à cause de leur spécialisation dans un autre domaine, de nombreux chercheurs n'ont pas forcément l'expertise ni l'équipement pour construire de telles plate-formes, c'est pourquoi nous avons veillé à donner tous les détails relatifs à la conception et la construction de cette plate-forme afin de guider quiconque souhaite la reproduire. Ainsi, il est également possible de modifier la conception électronique de la plate-forme pour la faire fonctionner dans une autre gamme de fréquences en suivant la méthodologie indiquée. La plate-forme est entièrement conçue avec des composants discrets disponibles dans le commerce et peut être construite pour un coût relativement bas. En préambule, nous présentons un premier prototype de plate-forme de test rudimentaire afin de comprendre les enjeux et difficultés et ainsi de justifier les choix de conception qui ont étés appliqués dans la plate-forme de test définitive. Nous présentons également une étude mathématique des signaux ULB permettant de calculer rapidement les caractéristiques que doit avoir un signal ULB pour être considéré comme tel.

Cette thèse présente, dans second temps, la conception et la réalisation d'un émetteur ULB en technologie intégrée CMOS 0.18um à très basse consommation. La radio ULB étant par nature à basse consommation, nous présentons une architecture originale permettant de générer un signal arbitraire en utilisant le moins possible d'énergie. Nous utilisons cette architecture pour la génération d'un signal ULB que nous avons déterminé mathématiquement pour avoir une forme qui optimise la répartition de la puissance dans le spectre dans la gamme de fréquence considérée (de 4.0 à 4.5 GHz comme pour la plate-forme). Nous présentons trois variantes de l'architecture dont l'une constitue un brevet.

**Mots-clé** ULB, Ultra-Large Bande, IR, Radio Impulsionelle, plate-forme de test, composants discrets, émetteur basse consommation, technologie intégrée CMOS 0.18um

## Remerciements

Ce travail n'aurait pas été possible sans la collaboration et le soutien de nombreuses personnes que je souhaite remercier ici :

- Je remercie d'abord mes directeurs de thèse, Dr Catherine Dehollain et Prof Jean-Yves Le Boudec, pour la qualité de leur encadrement et toutes les discussions que nous avons eues ensemble pour faire avancer ce travail. Leur disponibilité et leur soutien m'ont été précieux.

- Je remercie également Prof Anja Skrivervik, Dr Norbert Joehl, Prof Michael Green et Dr Basile Kawkabani qui ont accepté d'être membre du jury de thèse. Je les remercie en particulier d'avoir pris du temps durant les fêtes de fin d'année pour lire attentivement le manuscrit et pour les corrections et propositions d'amélioration qui ont suivi.

- Je remercie mes collègues pour leur disponibilité et leur aide dans ce travail: Altug Oz, Prakash Thoppay, Enver Kilinc, Oguz Atasoy, Mithat Silay, Francesco Mazilli, Paulo Augusto Dal Fabro, Adil Koukab, Nicolas Pillin et André Décurnex. J'adresse un merci tout particulier à Marc Pastre qui n'a pas compté ses heures pour dépanner les bugs des logiciels de conception de circuits integrés et autres problèmes informatiques.

- Je remercie aussi toutes les personnes responsables d'administrer notre laboratoire et sans qui le travail serait impossible : Isabelle Buzzi, Karin Jaymes, Roland Jaques et Raymond Sutter. Merci aussi à Joseph Guzzardi pour sa disponibilité et ses conseils pratiques toujours plein de bon sens notamment sur la sécurité du travail.

- Je remercie également les personnes des autres laboratoires qui ont collaboré avec notre groupe : Dr Ruben Merz pour m'avoir fait découvrir la radio UWB; Jérôme Vernez pour son travail remarquable sur la carte d'acquisition et la plate-forme; Dr Marcin Poturalski, Dr Hai Zhan, Dr Alexander Feldman et Dr Alexander Bahr pour avoir utilisé et valorisé notre plate-forme UWB; Holly Cogliati pour ses relectures et corrections d'articles

en anglais, John Gerrits pour ses idées créatives sur l'émetteur UWB en composants discrets; et enfin Jean-François Zürcher pour ses connaissance encyclopédique sur les circuits radio, les antennes ainsi que la maniÃ<sup>..</sup>re de les construire.

- Cette thèse n'aurait jamais pu se faire sans les ateliers de fabrication de circuit imprimés ACI-ACORT. Je remercie chaleureusement MM. Philippe Vosseler, Mose Silvestri, Pierre-André Joly, Manuel Leitos, Jose Luis Garciacano, André Badertscher et Peter Bruehlmeier pour la qualité de leur travail et le temps qu'il m'ont consacré pour transmettre leur savoir. De nombreux chapitres et l'annexe C de cette thèse leur doit beaucoup.

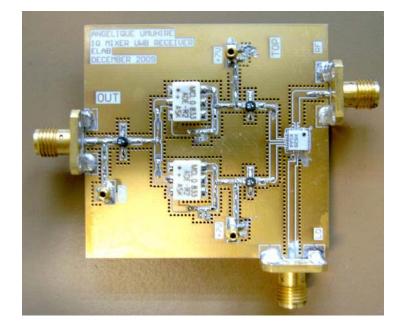

- Je remercie aussi les étudiants qui ont travaillé avec moi durant toutes ces années et qui ont chacun contribué de manière directe ou indirecte à ce travail : Yasmine Akhertouz Moreno, Angélique Umuhire, Jaskaranjeet Singh, Karim Jaber, Anurag Mangla, Haisong Wang, Aravinthan Athmanathan, Vincent Praplan, Fabio Da Cunha, Axel Murguet et Gilbert Conus.

- Enfin je remercie mes amis et ma famille qui m'ont soutenu et encouragé dans mon travail, ainsi que tout autre personne que j'aurais éventuellement oublié de citer ici.

# Contents

| A | bstract i |          |                                                                                                                                      |     |  |  |

|---|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| A | brégé     |          |                                                                                                                                      | iii |  |  |

| R | emerc     | eiement  | 5                                                                                                                                    | v   |  |  |

| I | Int       | roduc    | tion to UWB                                                                                                                          | 1   |  |  |

| 1 | Intr      | oductio  | n                                                                                                                                    | 3   |  |  |

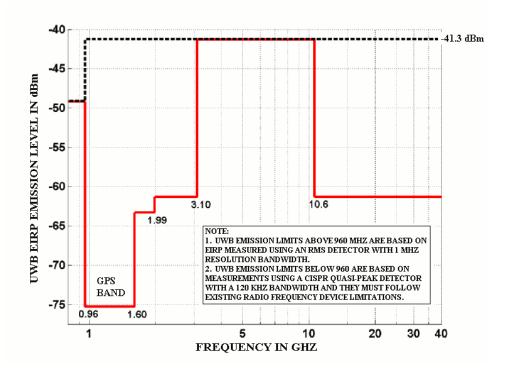

|   | 1.1       | Introd   | uction to UWB                                                                                                                        | 3   |  |  |

|   |           | 1.1.1    | UWB and conventional (narrow-band) Radio                                                                                             | 4   |  |  |

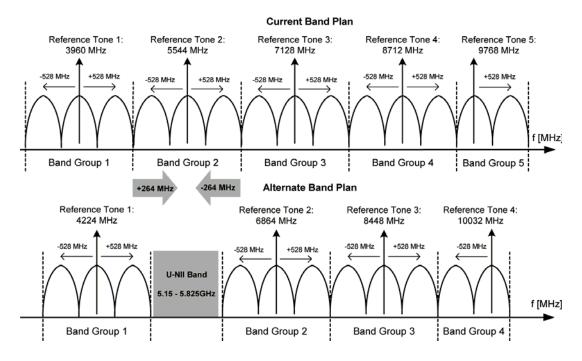

|   |           | 1.1.2    | UWB OFDM                                                                                                                             | 5   |  |  |

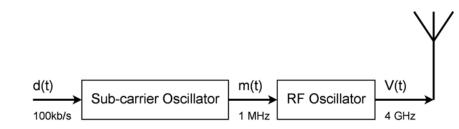

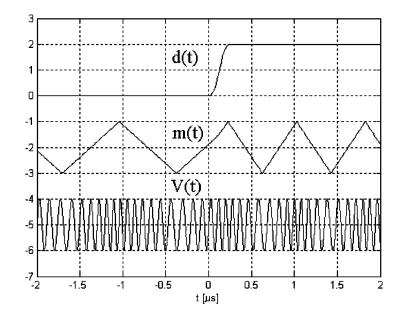

|   |           | 1.1.3    | UWB FM                                                                                                                               | 7   |  |  |

|   |           | 1.1.4    | UWB IR                                                                                                                               | 8   |  |  |

|   |           | 1.1.5    | Physical layer for IR-UWB as done in our system                                                                                      | 9   |  |  |

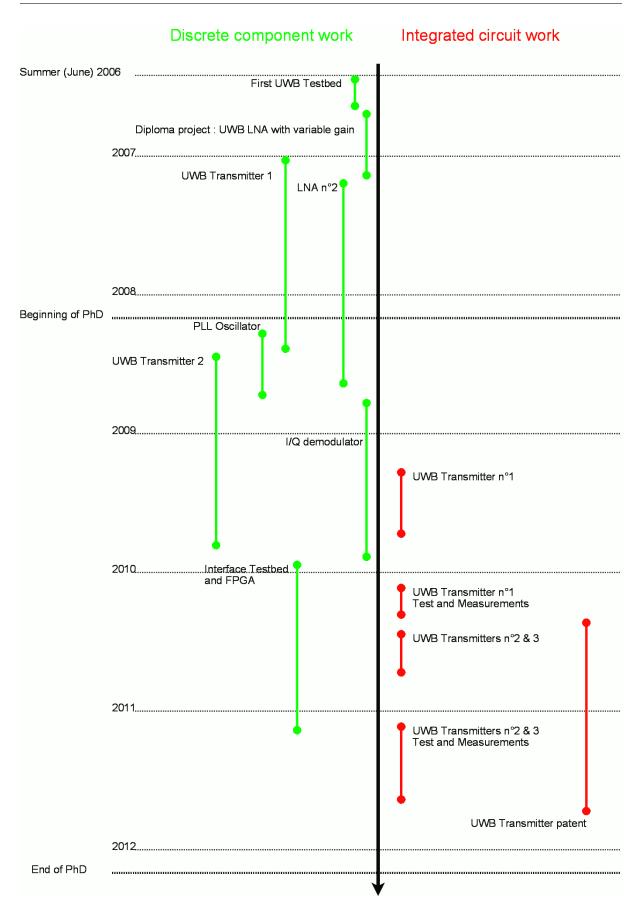

|   | 1.2       | About    | this work                                                                                                                            | 11  |  |  |

|   |           | 1.2.1    | The early beginning                                                                                                                  | 11  |  |  |

|   |           | 1.2.2    | Organisation and objectives of the work                                                                                              | 12  |  |  |

| 2 | A fi      | rst prot | otype of UWB testbed                                                                                                                 | 17  |  |  |

|   | 2.1       | Introd   | uction                                                                                                                               | 17  |  |  |

|   | 2.2       | UWB      | Transmitter (or Pulser)                                                                                                              | 19  |  |  |

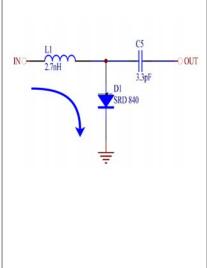

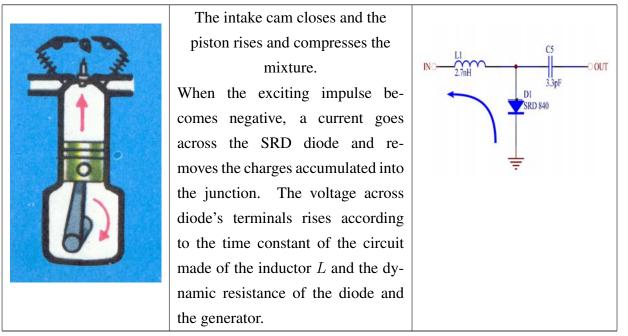

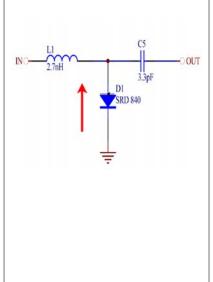

|   |           | 2.2.1    | Working principle - analogy with the engine                                                                                          | 19  |  |  |

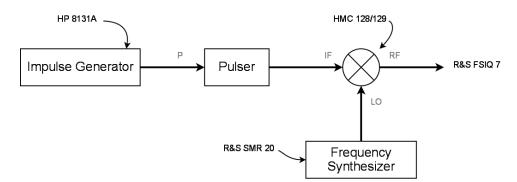

|   |           | 2.2.2    | Prototype $n^{\circ} 1 \dots $ | 22  |  |  |

|   |           | 2.2.3    | Prototype $n^{\circ} 2 \ldots \ldots$            | 24  |  |  |

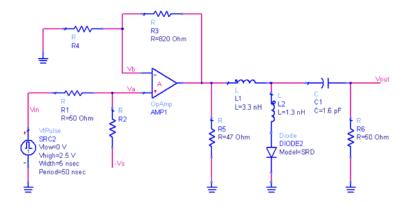

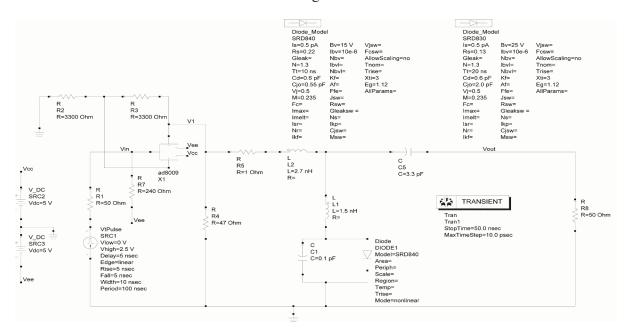

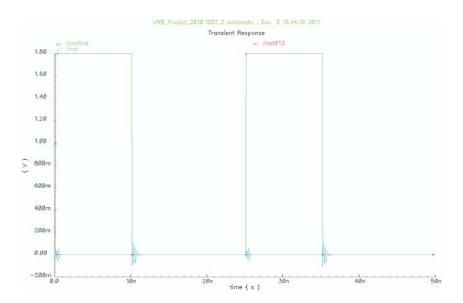

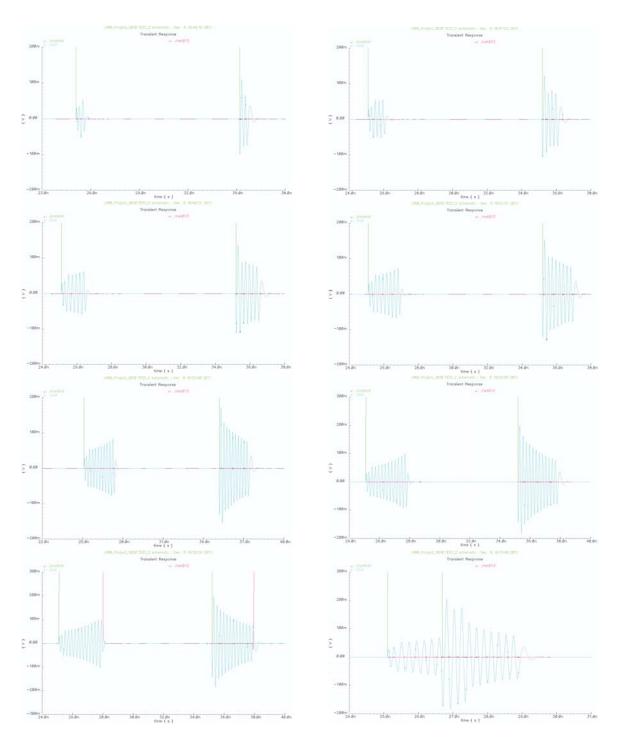

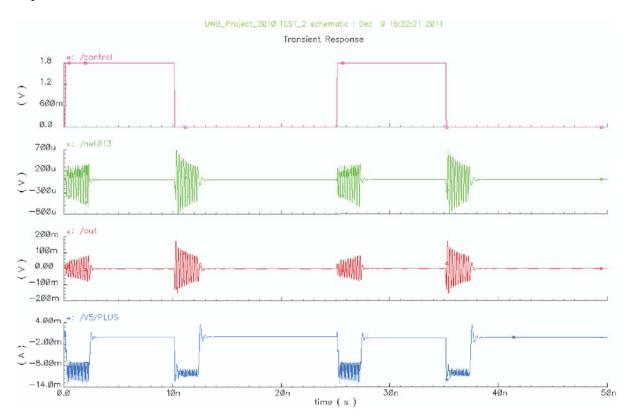

|   |           | 2.2.4    | Simulations                                                                                                                          | 26  |  |  |

|   |                                               | 2.2.5                                                                                                   | Choice of components                                        | 27                                                       |

|---|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|

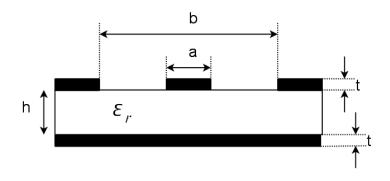

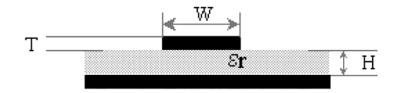

|   |                                               | 2.2.6                                                                                                   | Stripline calculations                                      | 27                                                       |

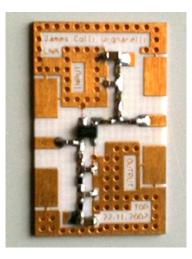

|   |                                               | 2.2.7                                                                                                   | PCB of the pulser                                           | 28                                                       |

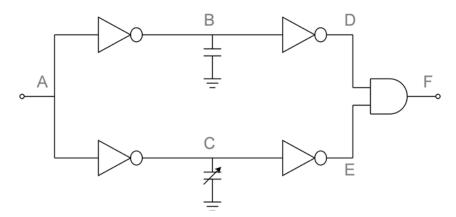

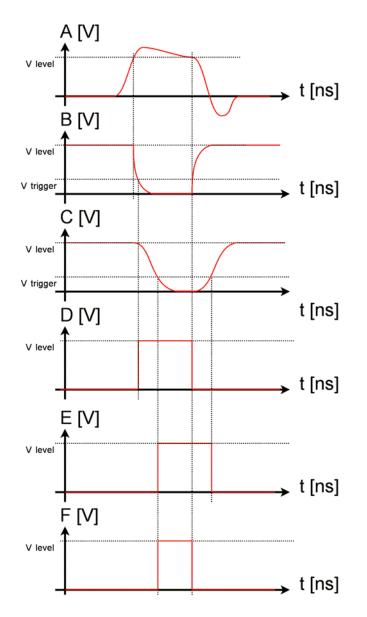

|   |                                               | 2.2.8                                                                                                   | Driving circuit                                             | 29                                                       |

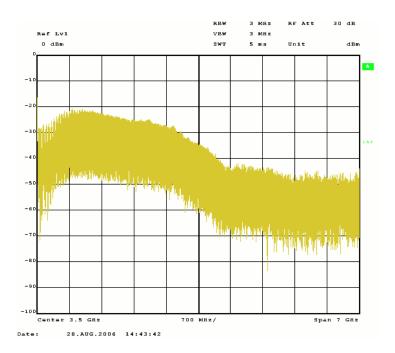

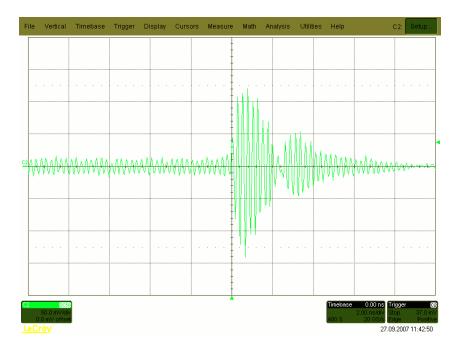

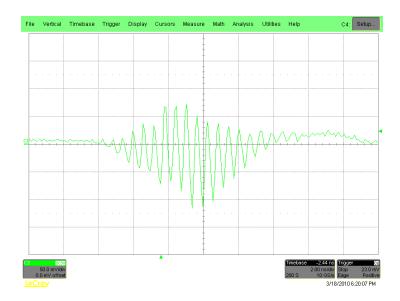

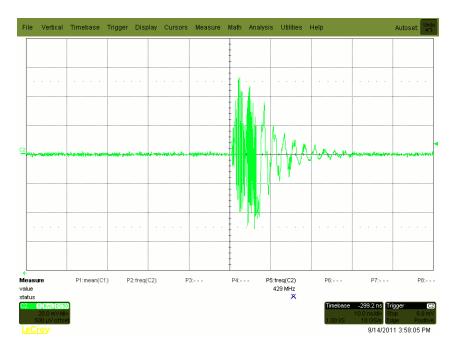

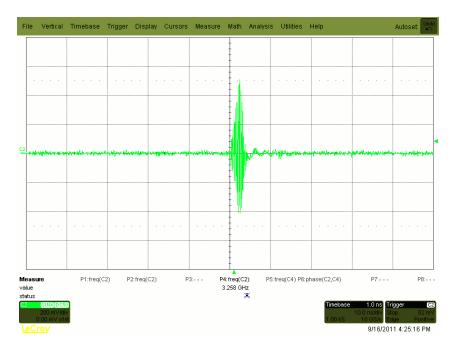

|   |                                               | 2.2.9                                                                                                   | Measurements                                                | 30                                                       |

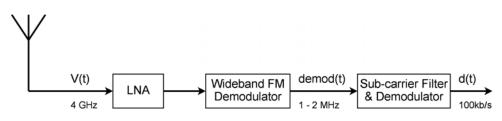

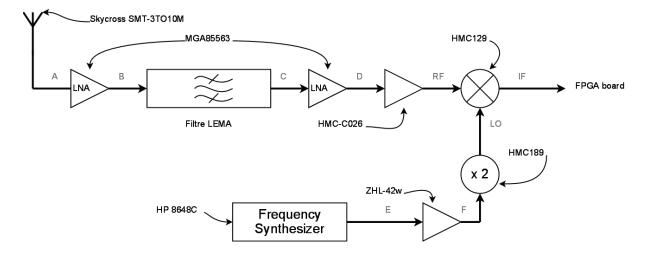

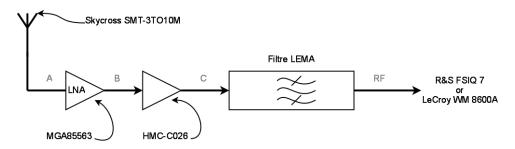

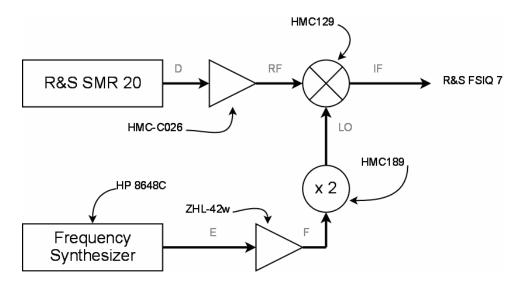

|   | 2.3                                           | UWB                                                                                                     | receiver                                                    | 33                                                       |

|   |                                               | 2.3.1                                                                                                   | Receiver description                                        | 33                                                       |

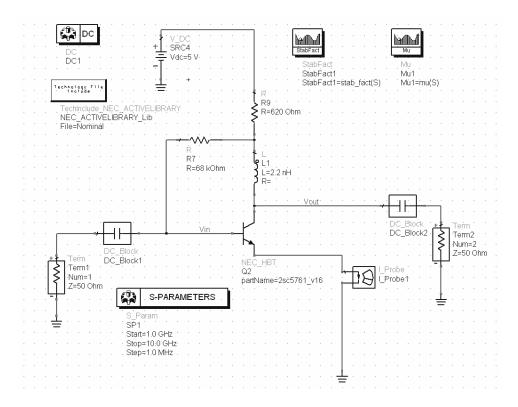

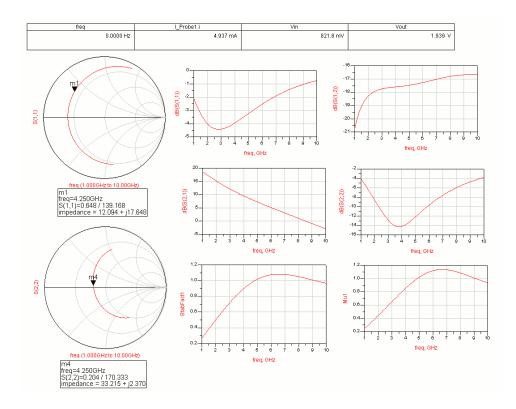

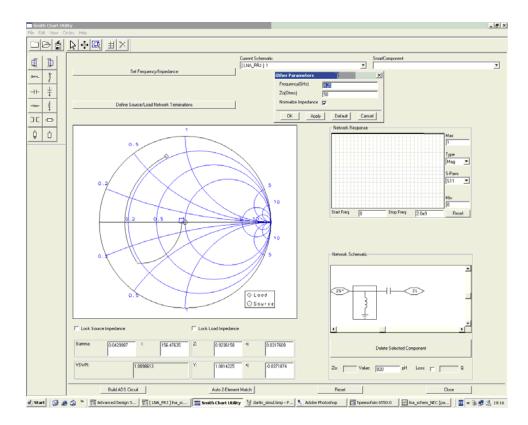

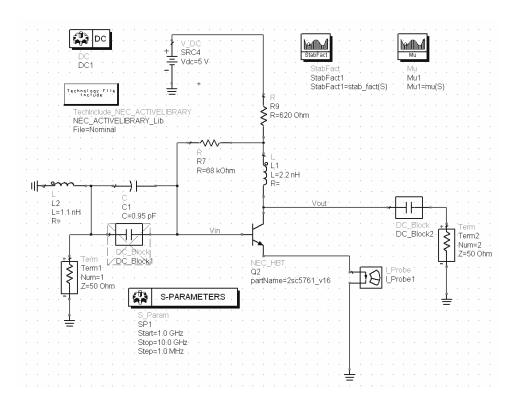

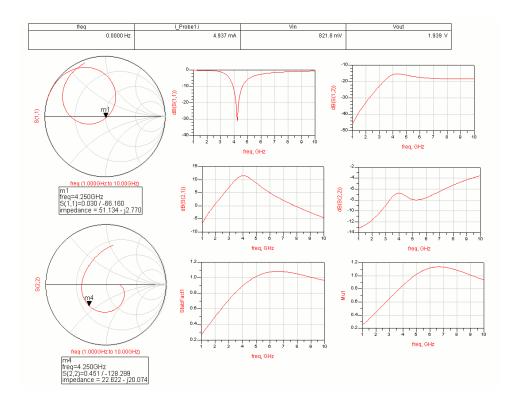

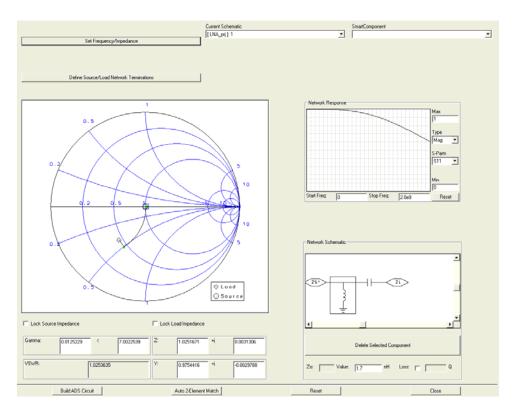

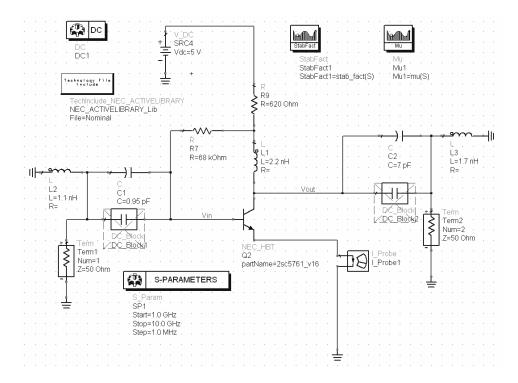

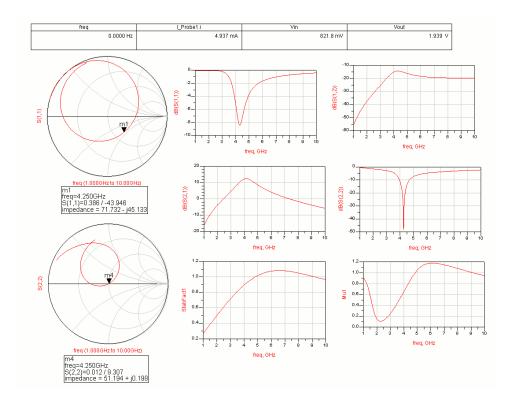

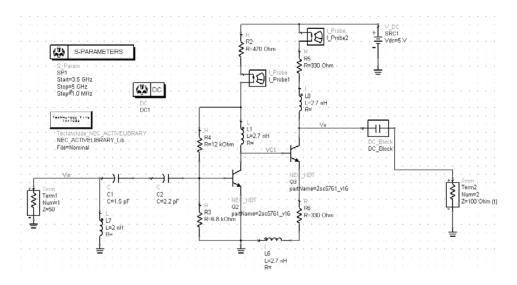

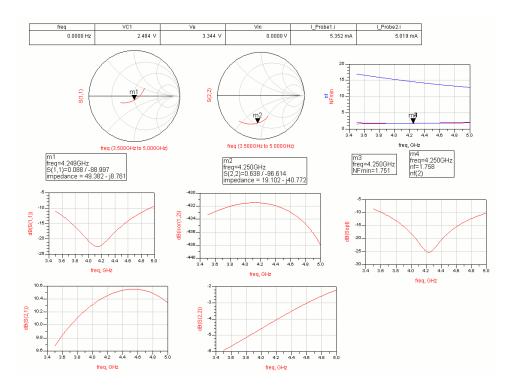

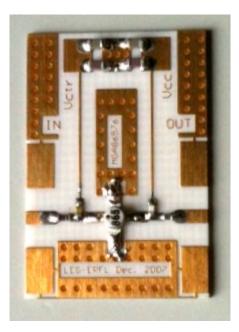

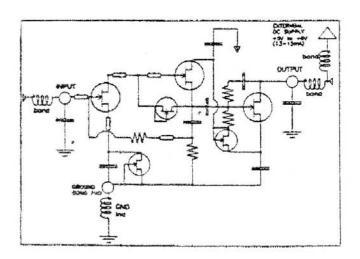

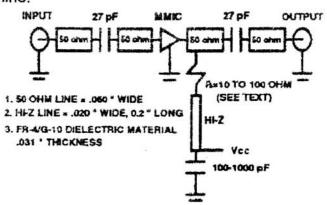

|   |                                               | 2.3.2                                                                                                   | Low Noise Amplifier (LNA)                                   | 35                                                       |

|   |                                               | 2.3.3                                                                                                   | Choice of components                                        | 37                                                       |

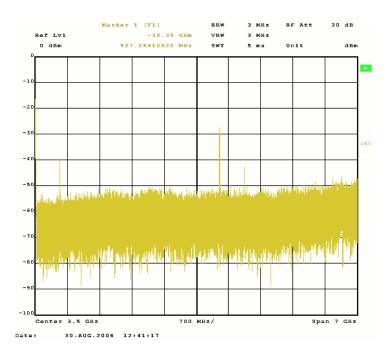

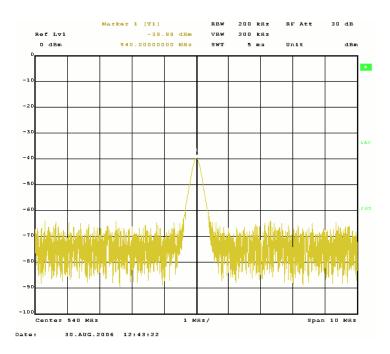

|   |                                               | 2.3.4                                                                                                   | Measurements                                                | 37                                                       |

|   | 2.4                                           | Improv                                                                                                  | vements                                                     | 44                                                       |

|   |                                               | 2.4.1                                                                                                   | Improvement nº 1                                            | 44                                                       |

|   |                                               | 2.4.2                                                                                                   | Improvement nº 2                                            | 45                                                       |

|   |                                               | 2.4.3                                                                                                   | $Improvement \ n^o \ 3 \ . \ . \ . \ . \ . \ . \ . \ . \ .$ | 45                                                       |

|   |                                               | 2.4.4                                                                                                   | Improvement nº 4                                            | 45                                                       |

|   | 2.5                                           | Conclu                                                                                                  | usion                                                       | 46                                                       |

| 2 |                                               |                                                                                                         |                                                             |                                                          |

| 3 | UW                                            | B Math                                                                                                  | ematical foundations                                        | 47                                                       |

| 3 | <b>UW</b><br>3.1                              |                                                                                                         | tion of the generic signals                                 | <b>4</b> 7<br>48                                         |

| 5 |                                               |                                                                                                         |                                                             |                                                          |

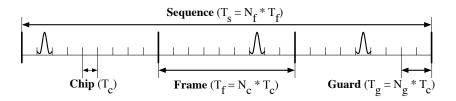

| 3 |                                               | Definit                                                                                                 | tion of the generic signals                                 | 48                                                       |

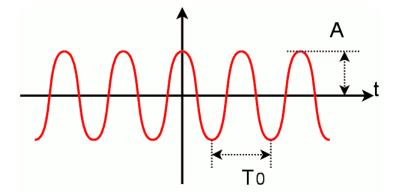

| 3 |                                               | Definit<br>3.1.1                                                                                        | tion of the generic signals                                 | 48<br>48                                                 |

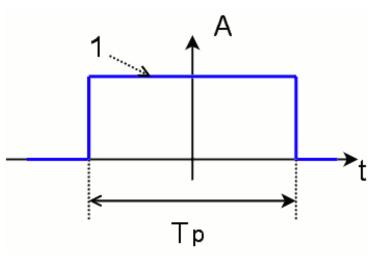

| 3 |                                               | Definit<br>3.1.1<br>3.1.2<br>3.1.3                                                                      | tion of the generic signals                                 | 48<br>48<br>49                                           |

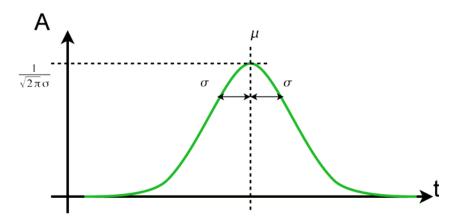

| 3 | 3.1                                           | Definit<br>3.1.1<br>3.1.2<br>3.1.3                                                                      | tion of the generic signals                                 | 48<br>48<br>49<br>49                                     |

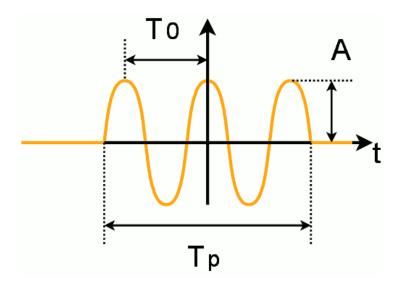

| 3 | 3.1                                           | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin                                                           | tion of the generic signals                                 | 48<br>48<br>49<br>49<br>50                               |

| 3 | 3.1                                           | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin<br>3.2.1<br>3.2.2                                         | tion of the generic signals                                 | 48<br>48<br>49<br>49<br>50<br>51                         |

| 3 | <ul><li>3.1</li><li>3.2</li></ul>             | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin<br>3.2.1<br>3.2.2                                         | tion of the generic signals                                 | 48<br>48<br>49<br>49<br>50<br>51<br>54                   |

| 3 | <ul><li>3.1</li><li>3.2</li></ul>             | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin<br>3.2.1<br>3.2.2<br>The sin                              | tion of the generic signals                                 | 48<br>49<br>49<br>50<br>51<br>54<br>55                   |

| 3 | <ul><li>3.1</li><li>3.2</li></ul>             | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin<br>3.2.1<br>3.2.2<br>The sin<br>3.3.1<br>3.3.2            | tion of the generic signals                                 | 48<br>49<br>49<br>50<br>51<br>54<br>55<br>55             |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin<br>3.2.1<br>3.2.2<br>The sin<br>3.3.1<br>3.3.2            | tion of the generic signals                                 | 48<br>49<br>49<br>50<br>51<br>54<br>55<br>55<br>60       |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Definit<br>3.1.1<br>3.1.2<br>3.1.3<br>The sin<br>3.2.1<br>3.2.2<br>The sin<br>3.3.1<br>3.3.2<br>The sin | tion of the generic signals                                 | 48<br>49<br>49<br>50<br>51<br>54<br>55<br>55<br>60<br>60 |

| 4 | Pres | entatio         | n of the discrete-components UWB Testbed  | 67  |  |  |  |  |

|---|------|-----------------|-------------------------------------------|-----|--|--|--|--|

| - | 4.1  |                 | isation of Part II                        |     |  |  |  |  |

|   | 4.2  | Overv           | iew of the <i>U-Lite</i> Testbed          | 69  |  |  |  |  |

| 5 | Osci | illator         |                                           | 75  |  |  |  |  |

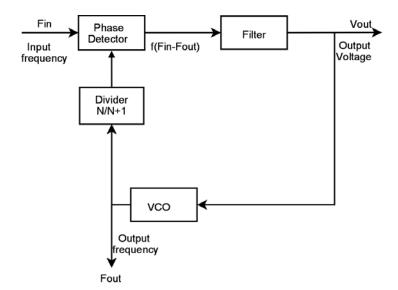

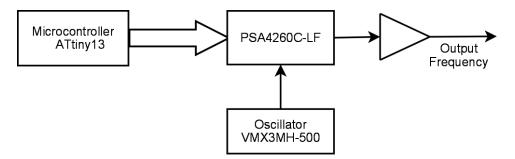

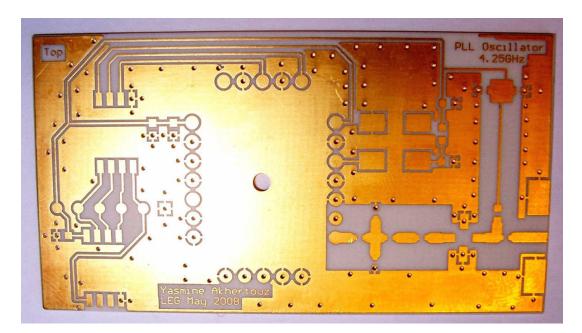

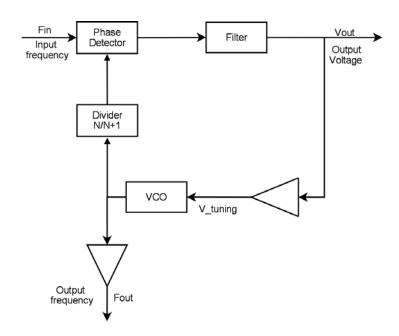

|   | 5.1  | The Pl          | LL synthesizer                            | 76  |  |  |  |  |

|   |      | 5.1.1           | The microcontroller                       | 77  |  |  |  |  |

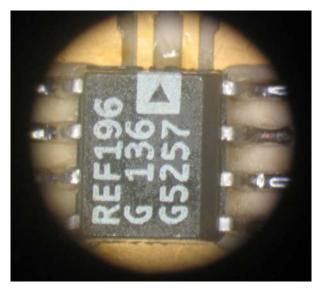

|   |      | 5.1.2           | The reference oscillator                  | 78  |  |  |  |  |

|   |      | 5.1.3           | The RF amplifier                          | 78  |  |  |  |  |

|   |      | 5.1.4           | Summary                                   | 79  |  |  |  |  |

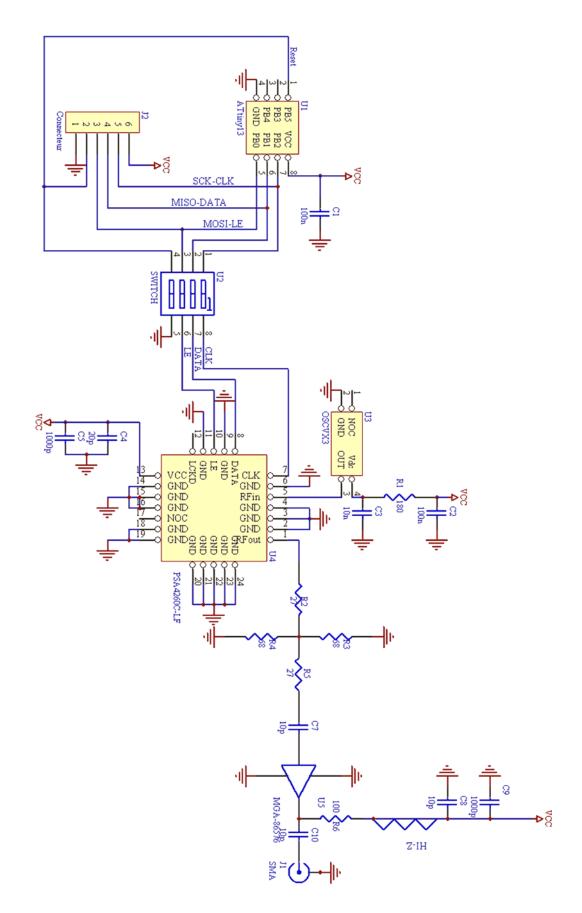

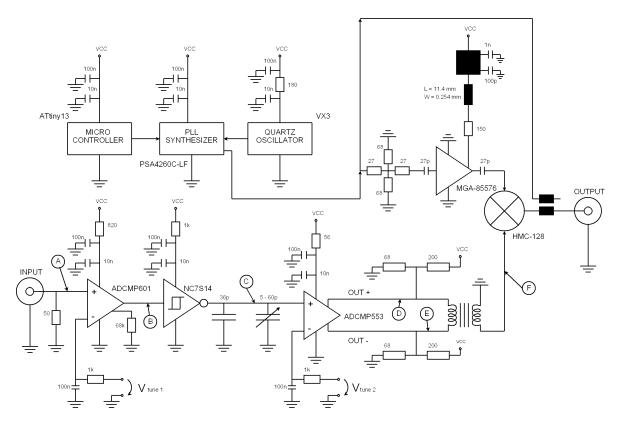

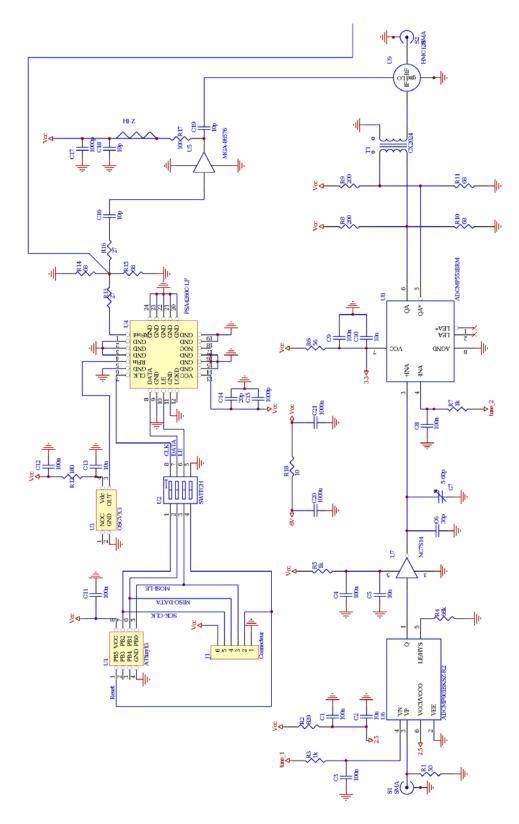

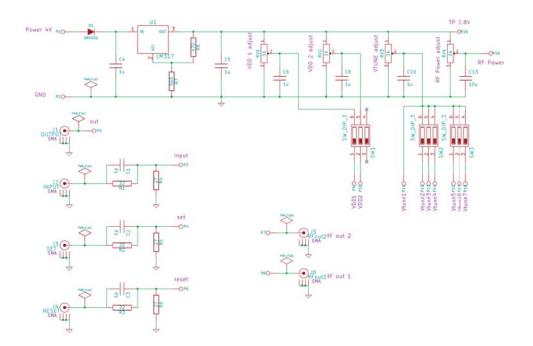

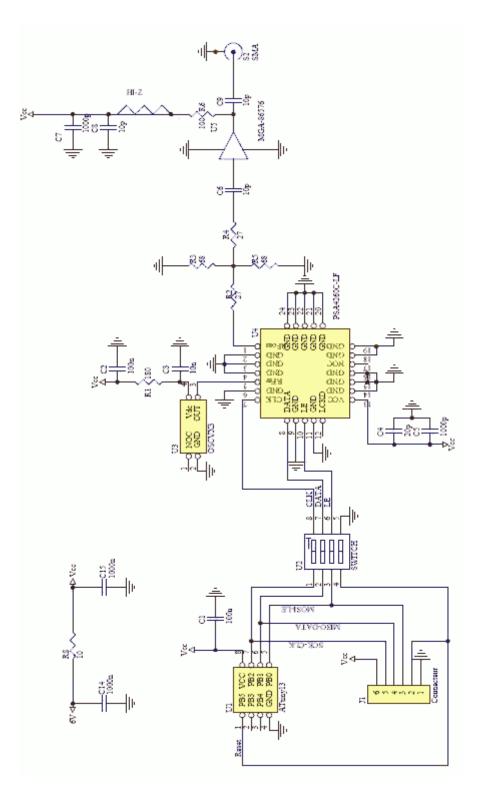

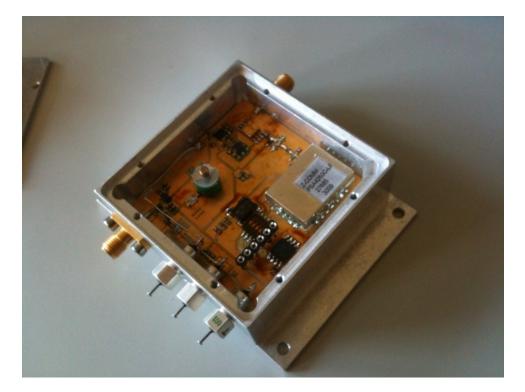

|   | 5.2  | The sc          | hematic                                   | 79  |  |  |  |  |

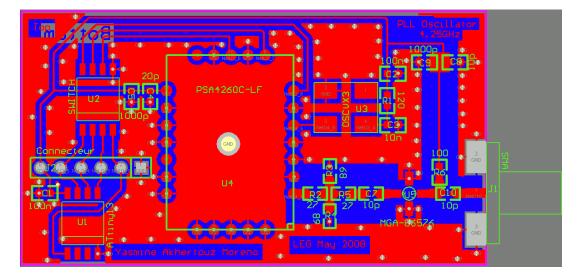

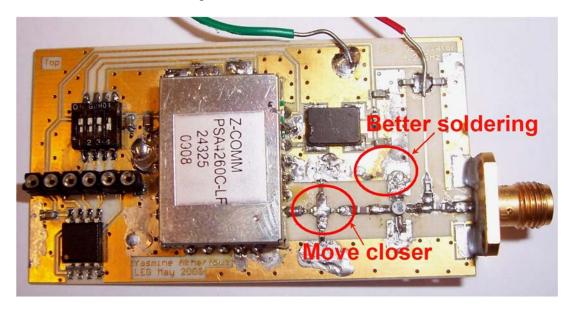

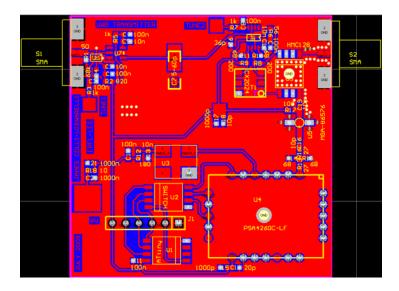

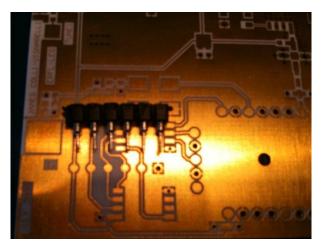

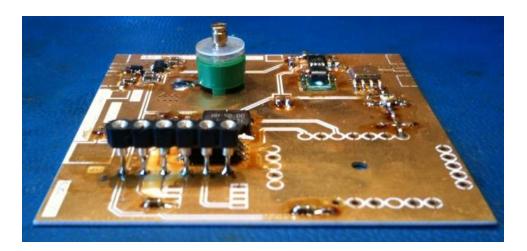

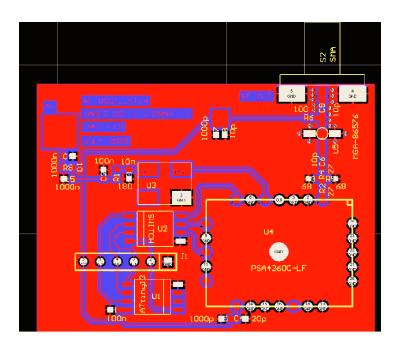

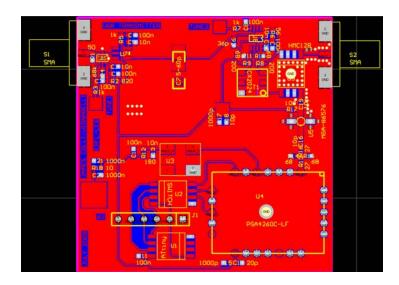

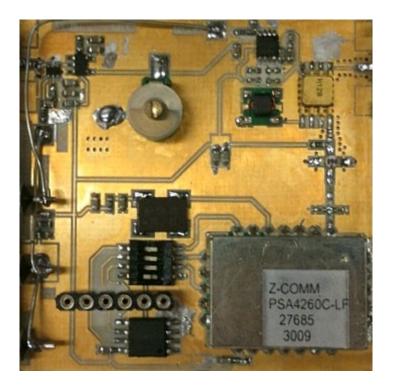

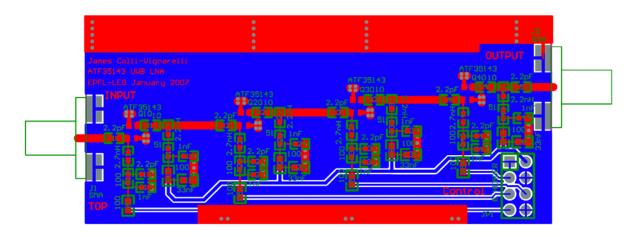

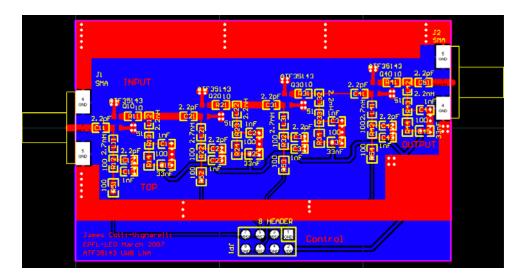

|   | 5.3  | The PO          | CB layout                                 | 83  |  |  |  |  |

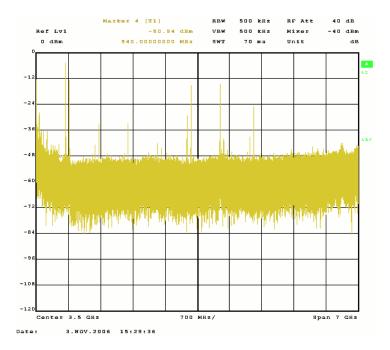

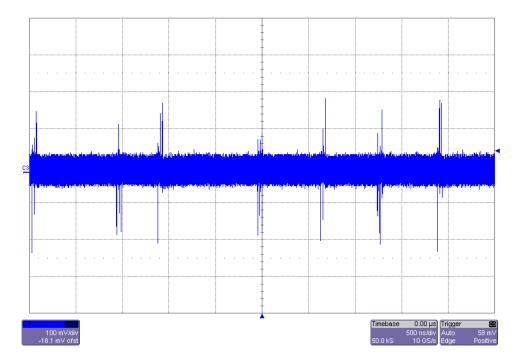

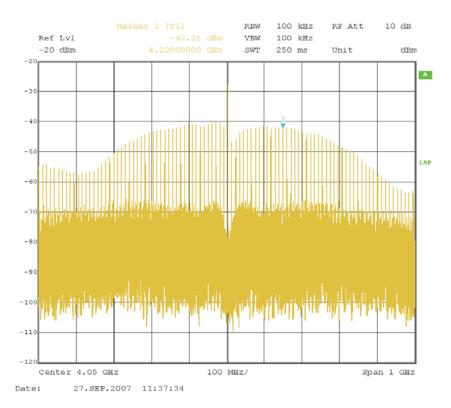

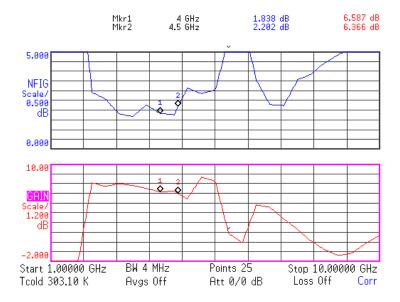

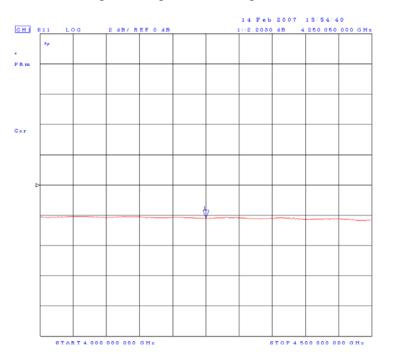

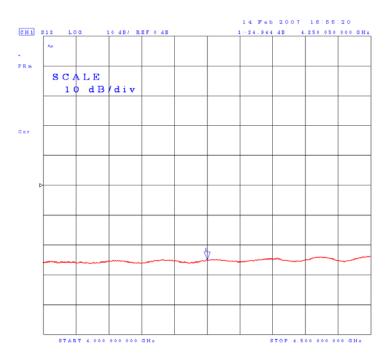

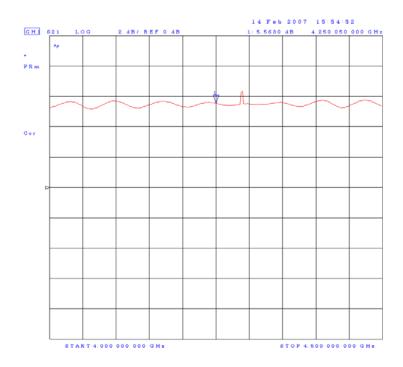

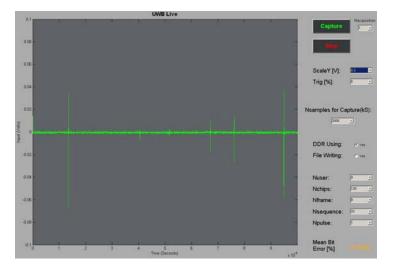

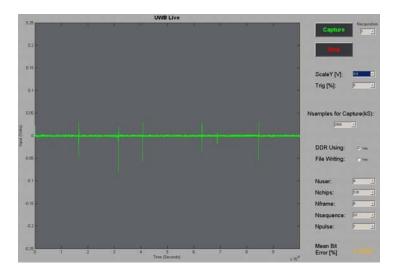

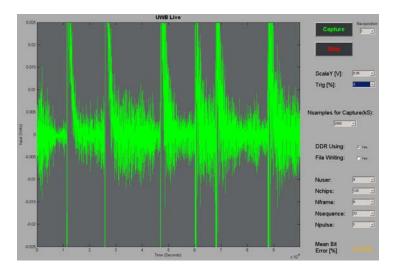

|   | 5.4  | Measu           | rements                                   | 85  |  |  |  |  |

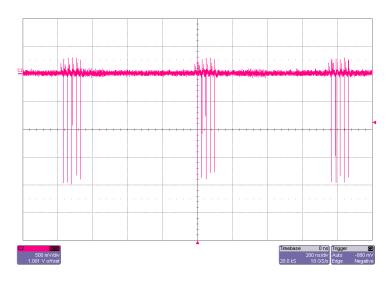

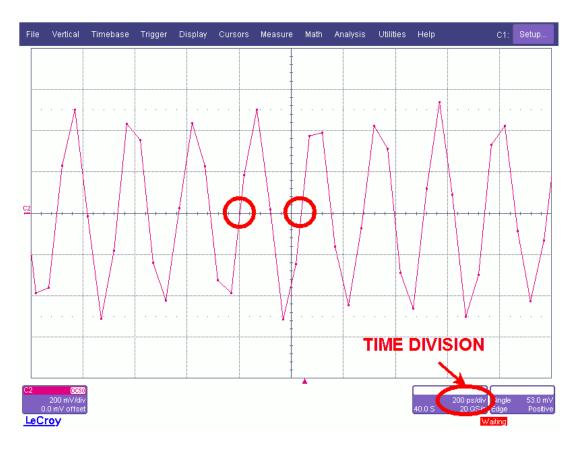

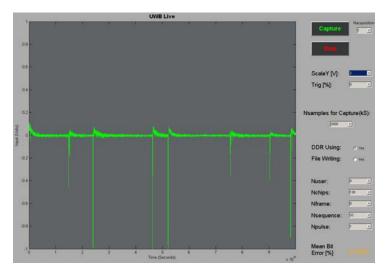

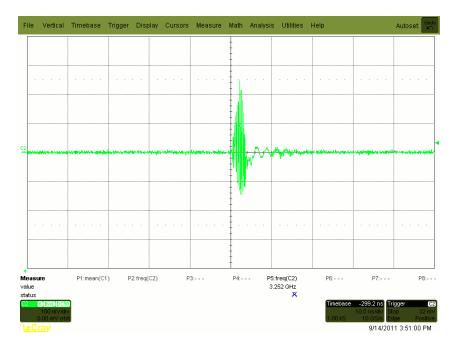

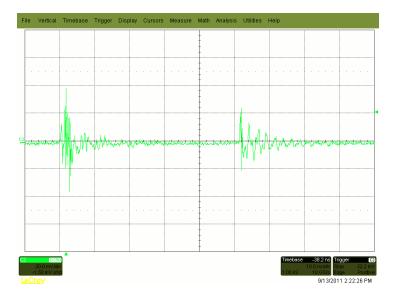

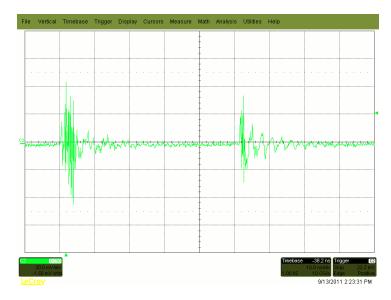

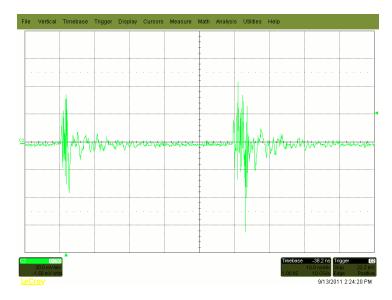

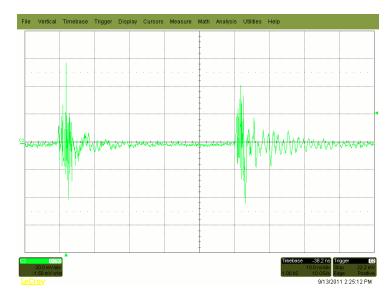

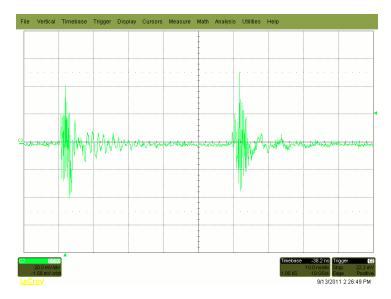

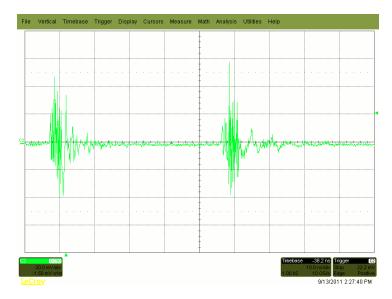

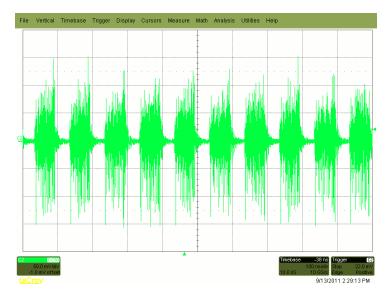

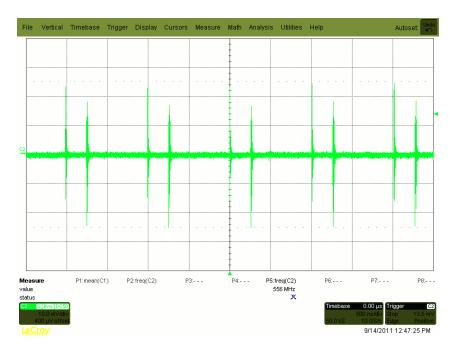

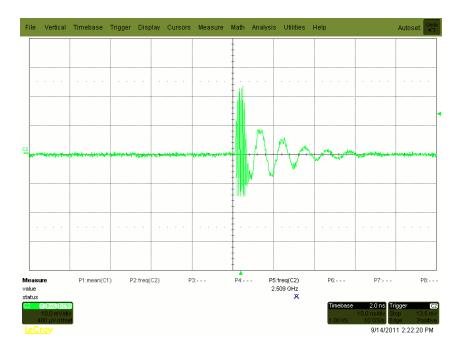

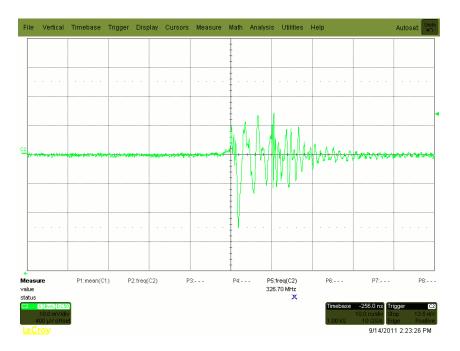

|   |      | 5.4.1           | Time measurement                          | 85  |  |  |  |  |

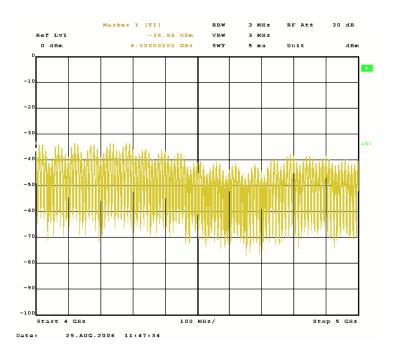

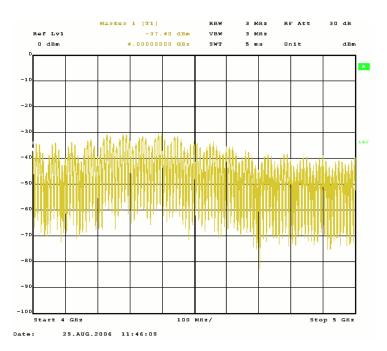

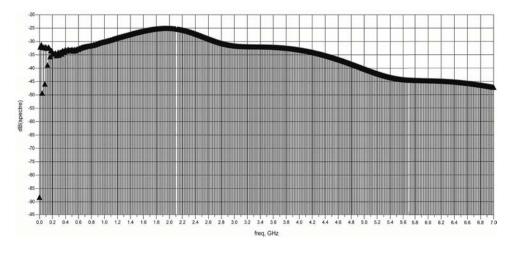

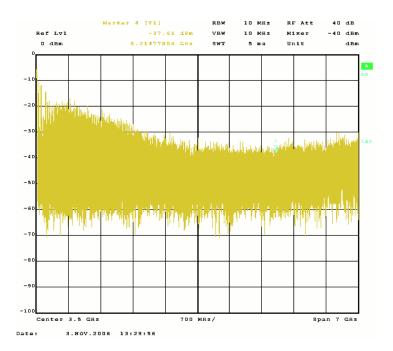

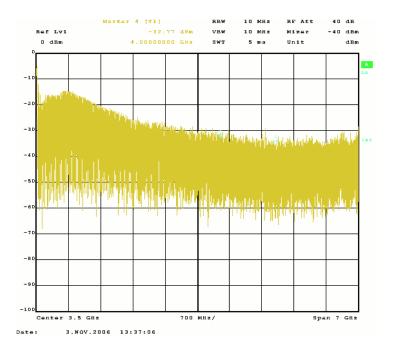

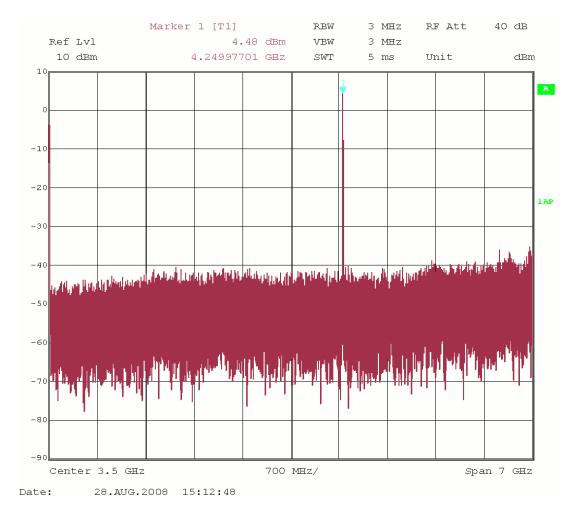

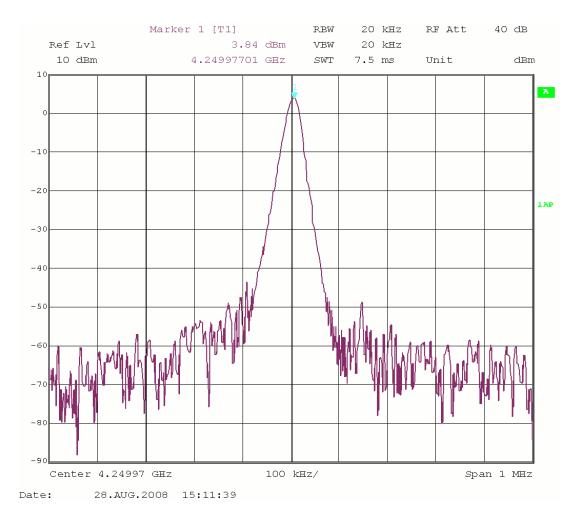

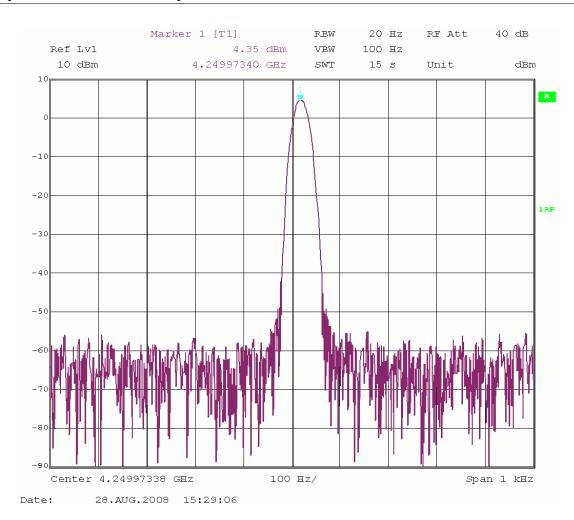

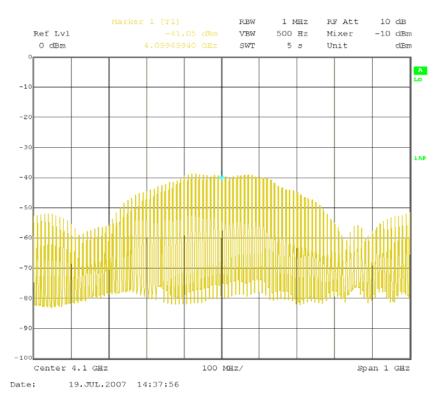

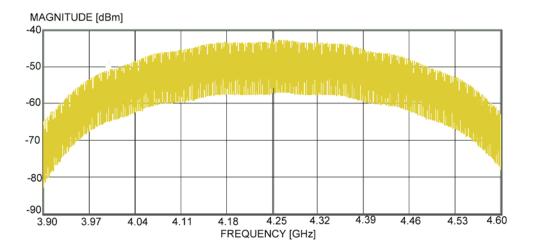

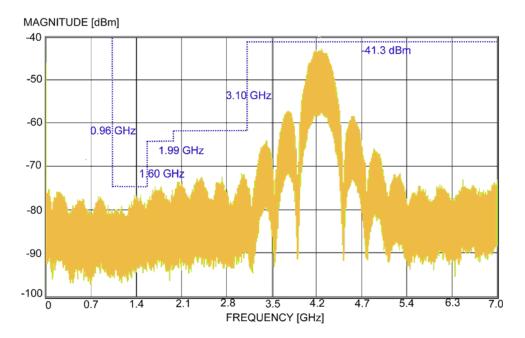

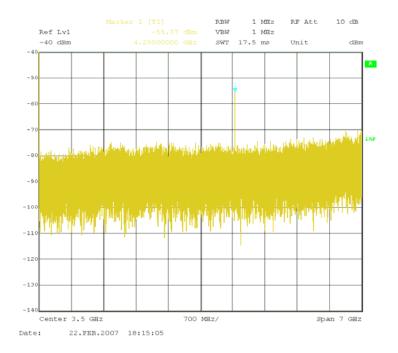

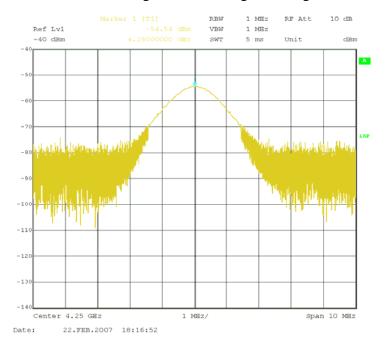

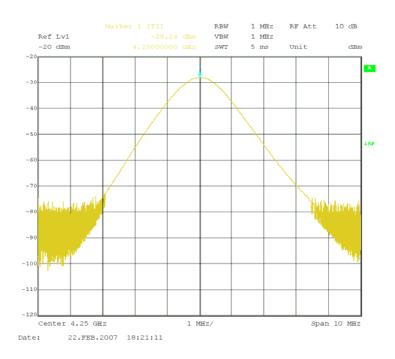

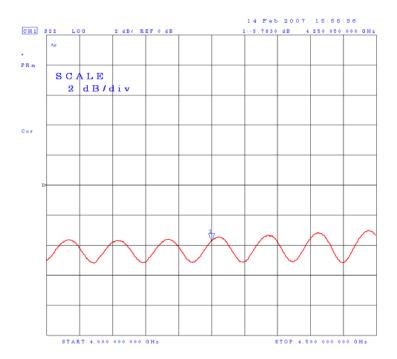

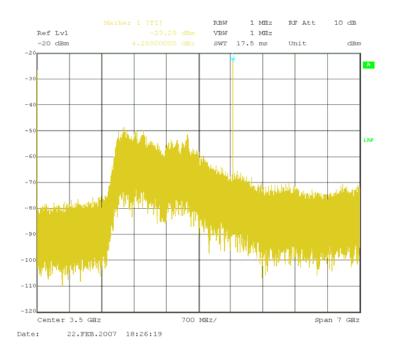

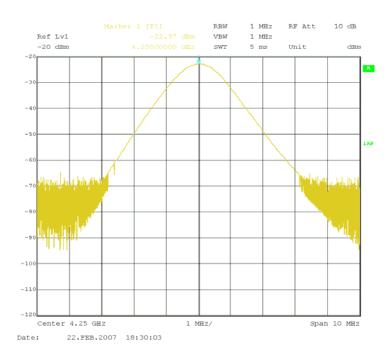

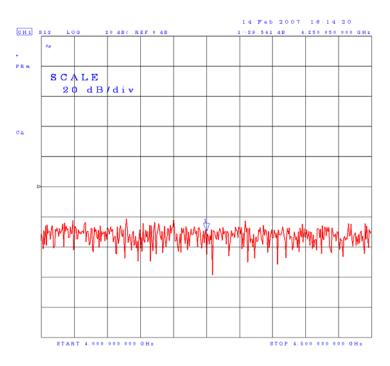

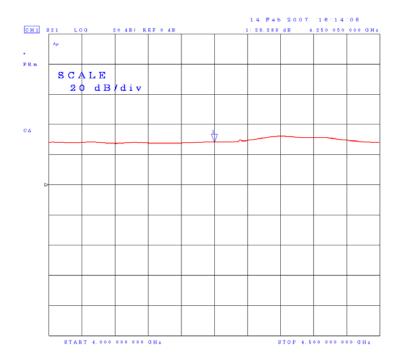

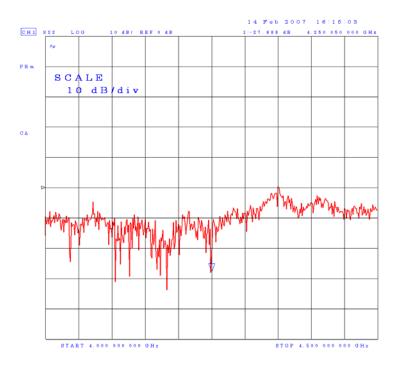

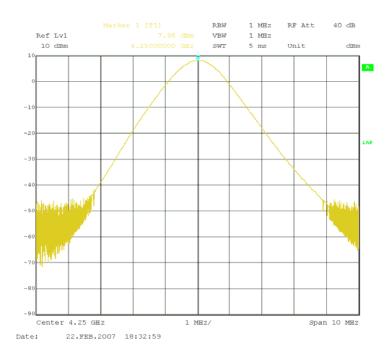

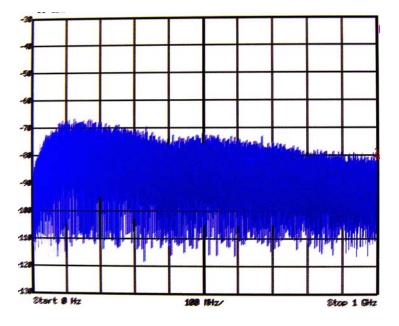

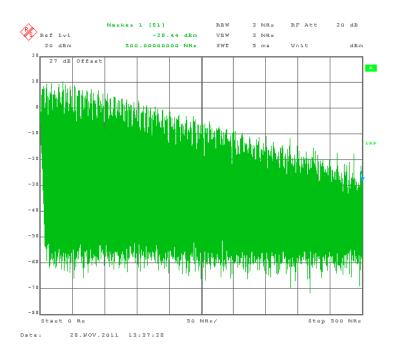

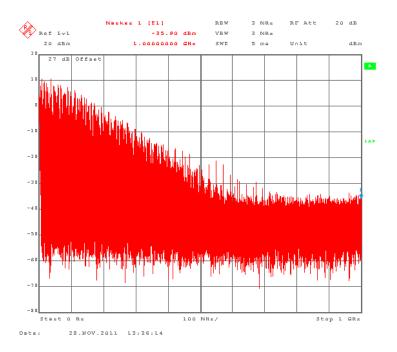

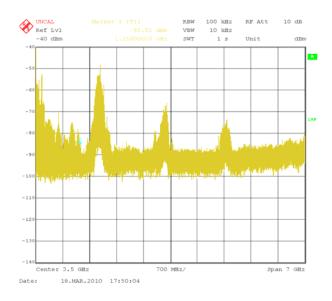

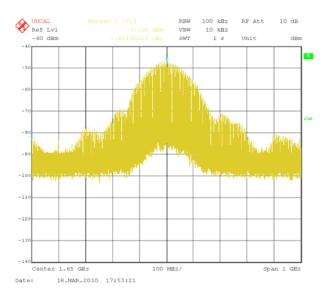

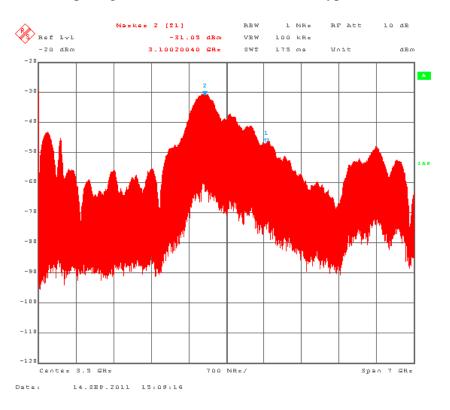

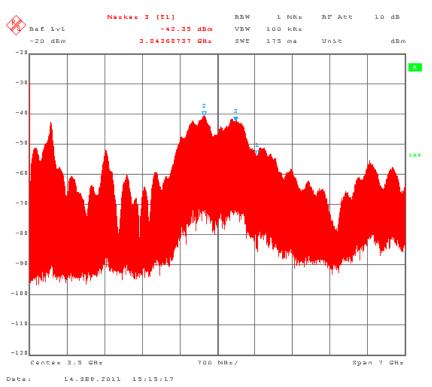

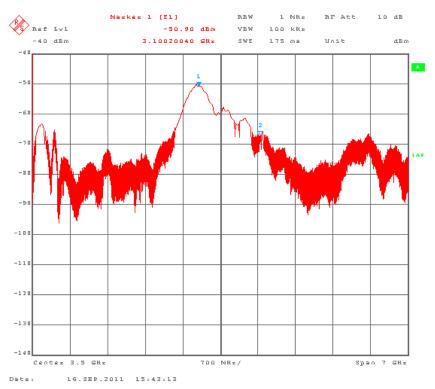

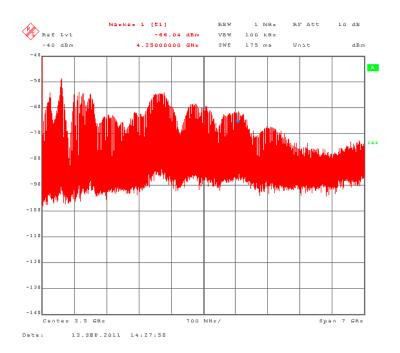

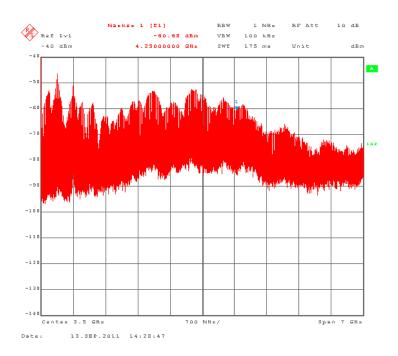

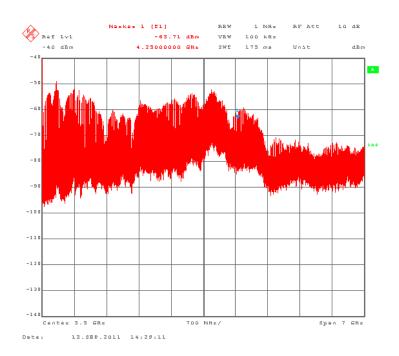

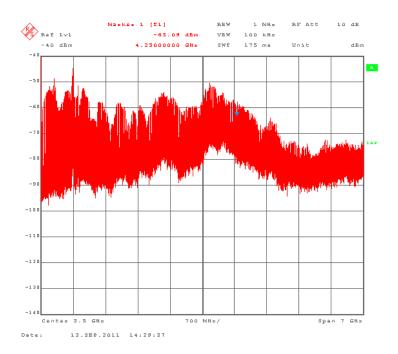

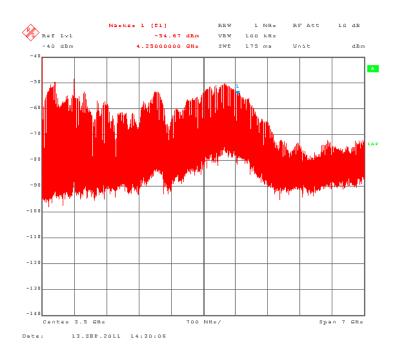

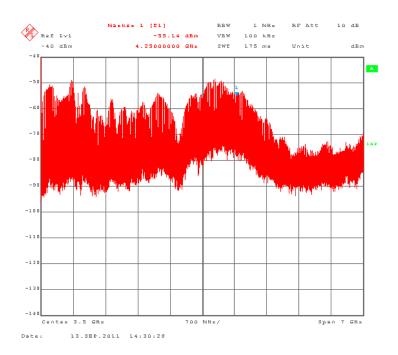

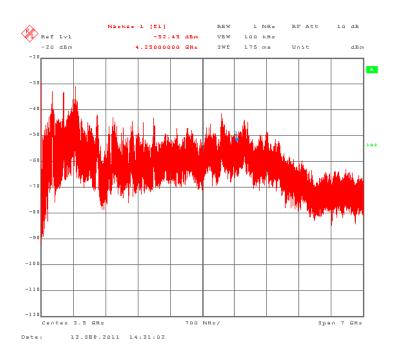

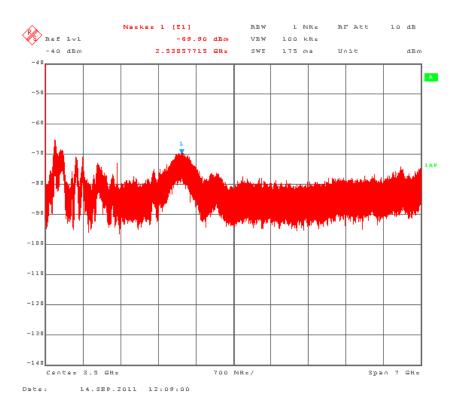

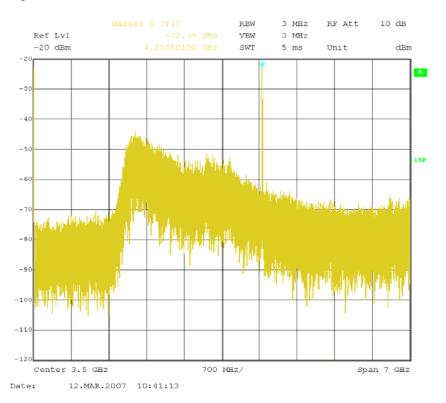

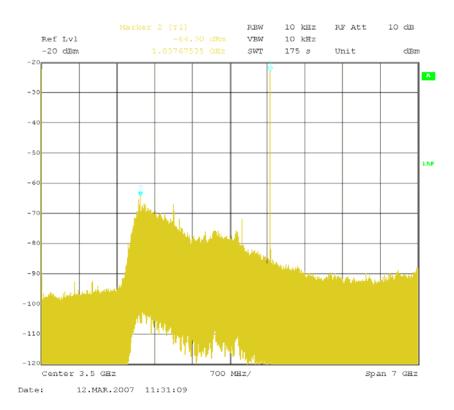

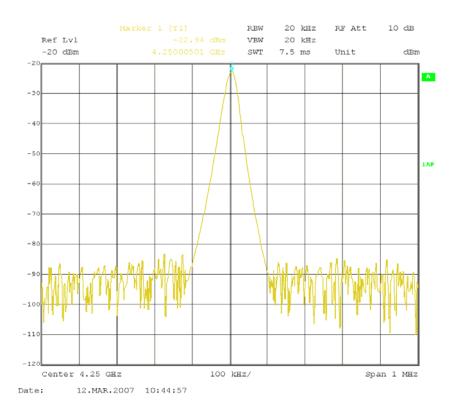

|   |      | 5.4.2           | Spectrum measurement                      | 85  |  |  |  |  |

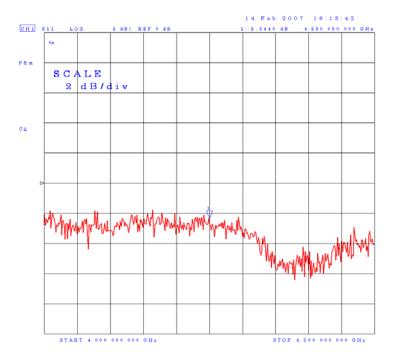

|   |      | 5.4.3           | Noise floor                               | 86  |  |  |  |  |

|   | 5.5  | Improv          | vements and further implementations       | 86  |  |  |  |  |

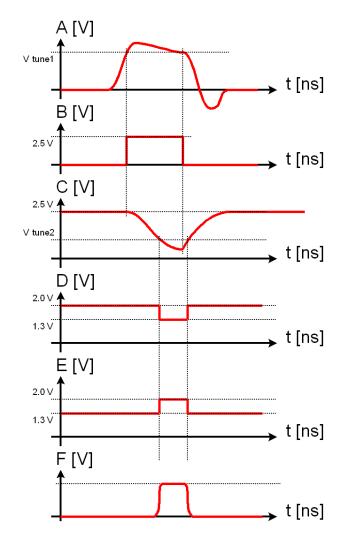

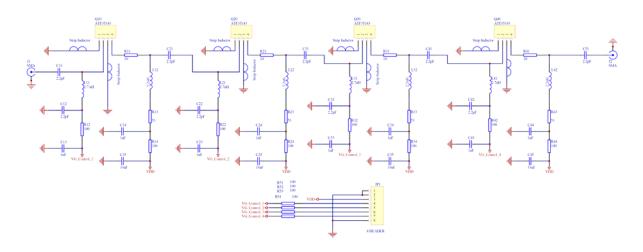

| 6 | UW   | UWB Transmitter |                                           |     |  |  |  |  |

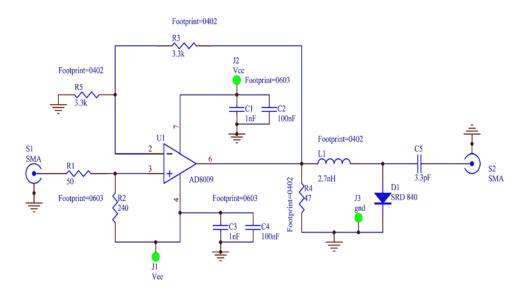

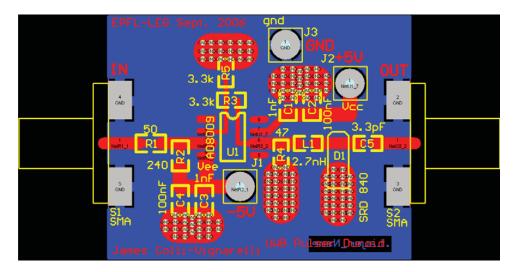

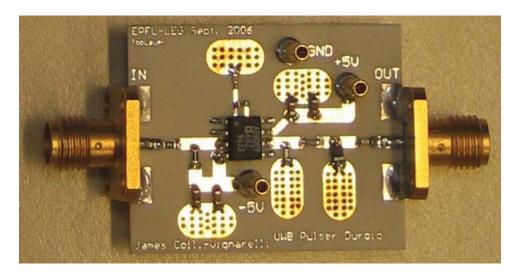

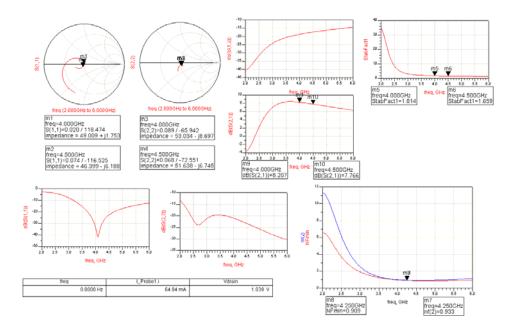

|   | 6.1  | UWB             | Transmitter prototype nº 1                | 93  |  |  |  |  |

|   |      | 6.1.1           | UWB Transmitter prototype nº 1, version 1 | 93  |  |  |  |  |

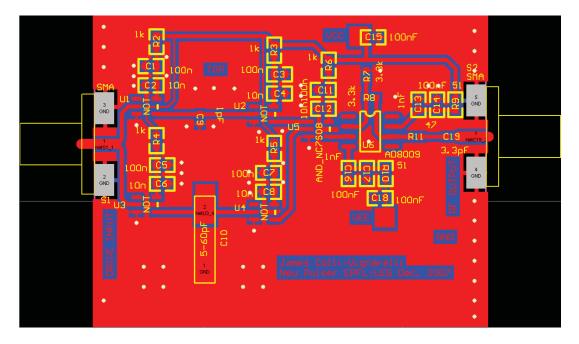

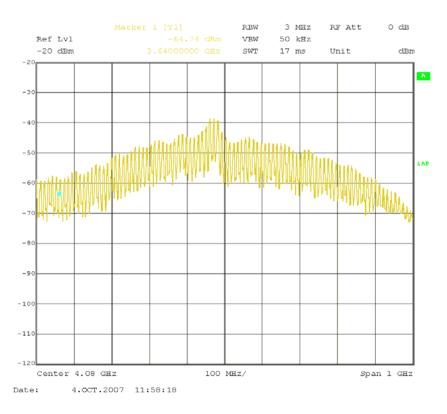

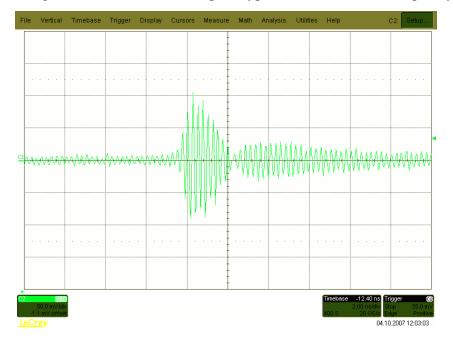

|   |      | 6.1.2           | UWB Transmitter prototype nº 1, version 2 | 96  |  |  |  |  |

|   |      | 6.1.3           | UWB Transmitter prototype nº 1, version 3 | 98  |  |  |  |  |

|   |      | 6.1.4           | Conclusion about Prototype nº 1           | 100 |  |  |  |  |

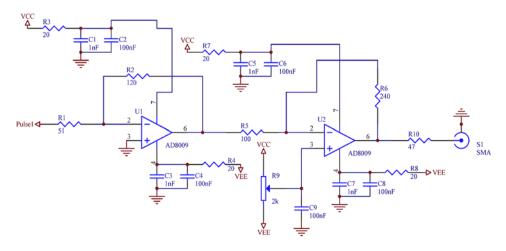

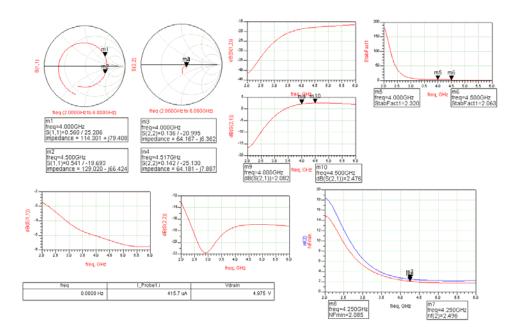

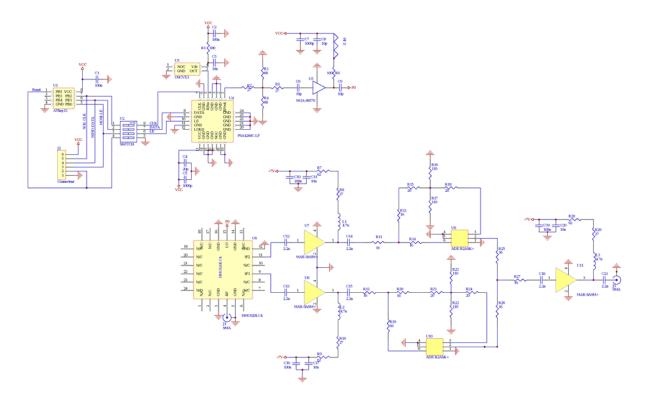

|   | 6.2  | UWB             | Transmitter prototype nº 2                | 102 |  |  |  |  |

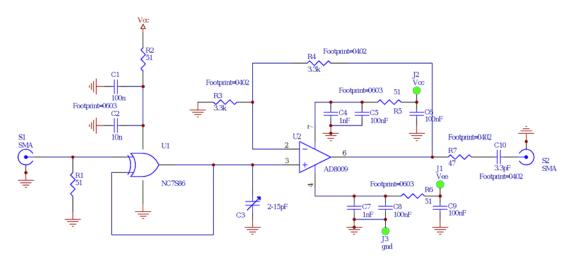

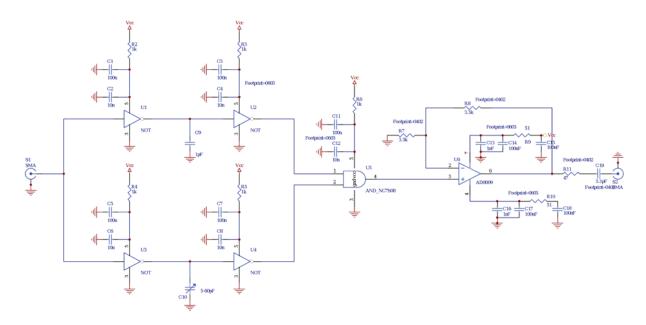

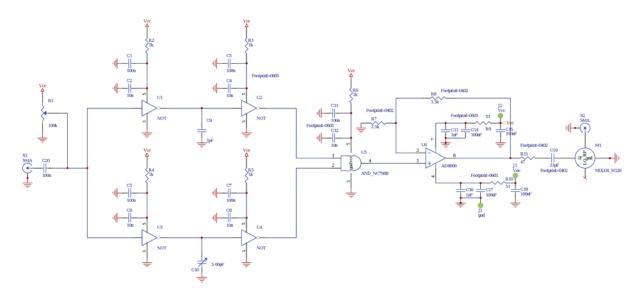

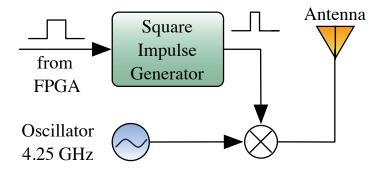

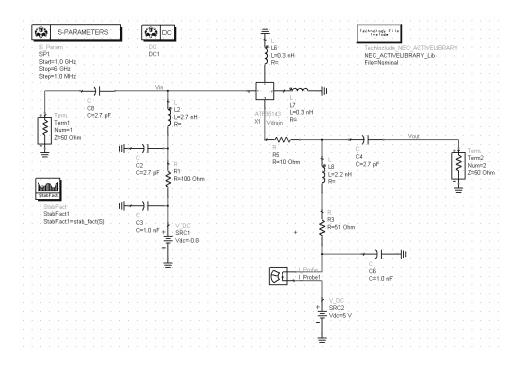

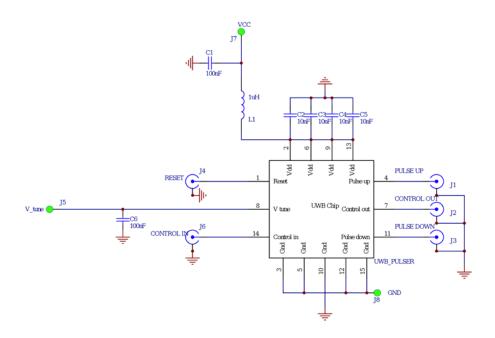

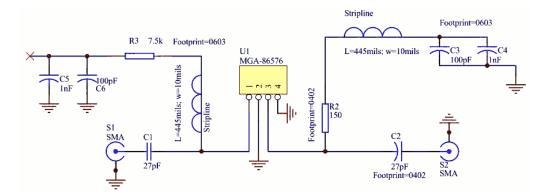

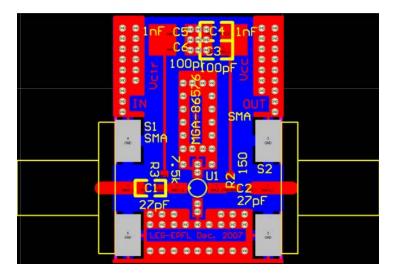

|   |      | 6.2.1           | Schematic of the Transmitter              | 102 |  |  |  |  |

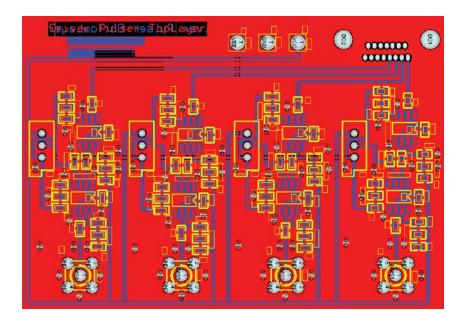

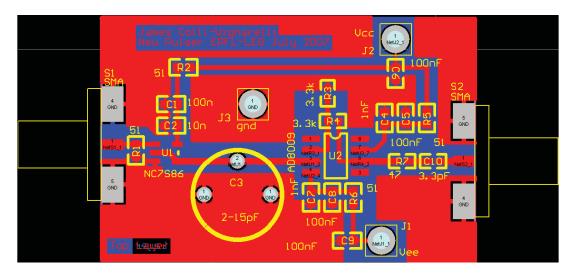

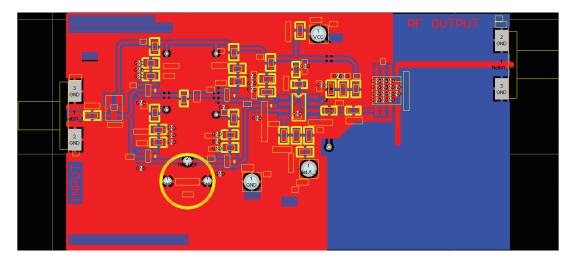

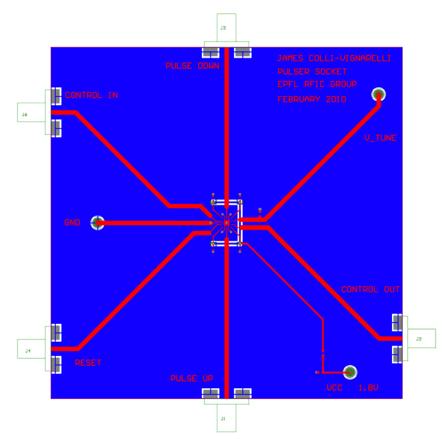

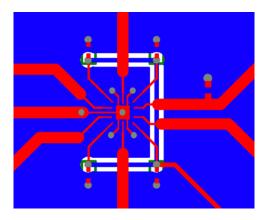

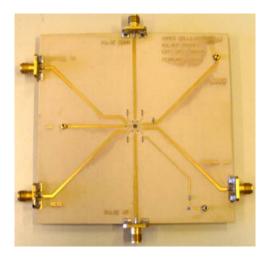

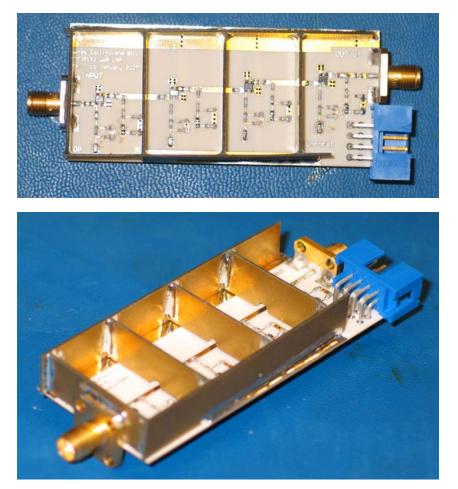

|   |      | 6.2.2           | Construction of the IR-UWB Transmitter    | 105 |  |  |  |  |

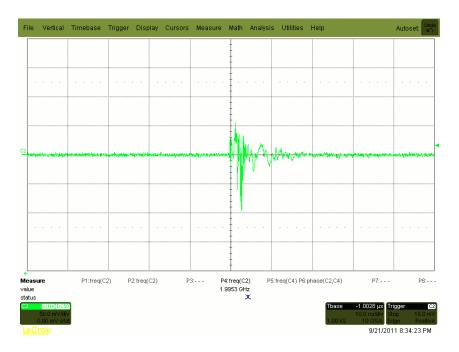

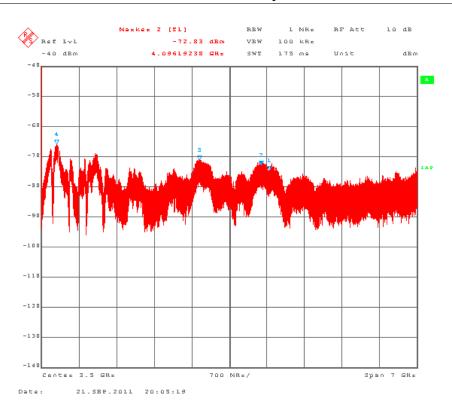

|   |      | 6.2.3           | Measurement on the IR-UWB Transmitter     | 108 |  |  |  |  |

|   | 6.3  | Conclu          | usion                                     | 110 |  |  |  |  |

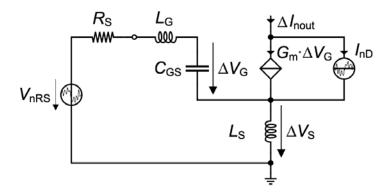

| 7 | LNA  | A proto         | type nº 1                                 | 111 |  |  |  |  |

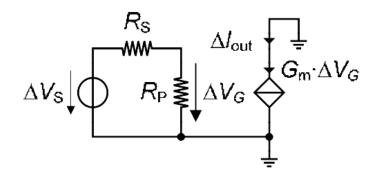

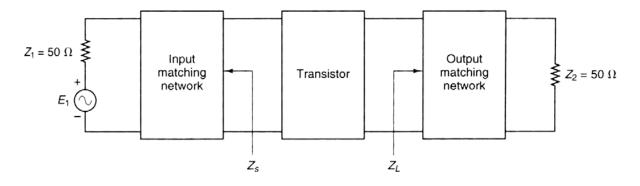

|   | 7.1  | Princip         | ples of LNAs with MOS transistor          | 112 |  |  |  |  |

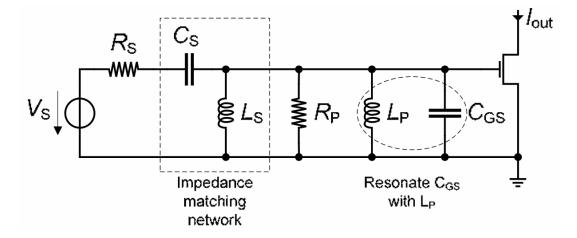

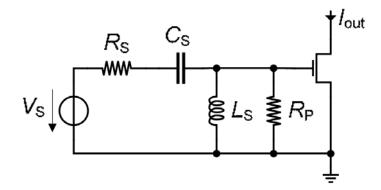

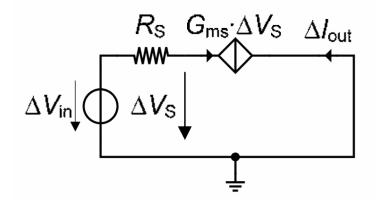

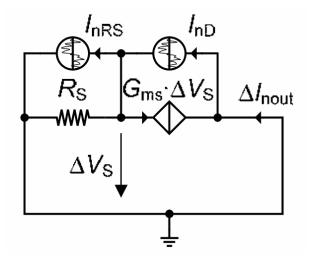

|   |     | 7.1.1    | LNA $n^{\circ} 1$ : Common source without matching network                                                       |

|---|-----|----------|------------------------------------------------------------------------------------------------------------------|

|   |     | 7.1.2    | LNA $n^{\circ} 2$ : Common source with matching network                                                          |

|   |     | 7.1.3    | LNA n° 3 : Common gate without matching network $\ldots \ldots \ldots \ldots \ldots 120$                         |

|   |     | 7.1.4    | LNA $n^{\circ} 4$ : Common gate with matching network                                                            |

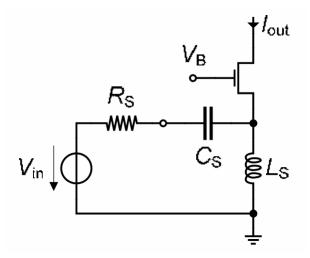

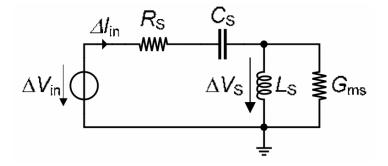

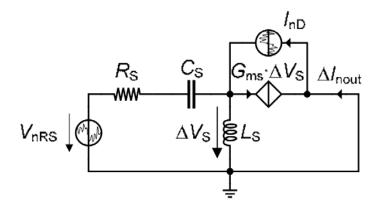

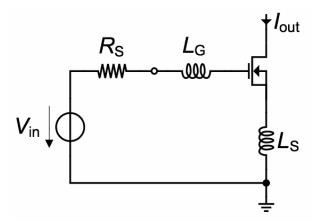

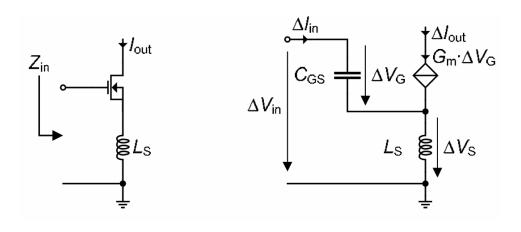

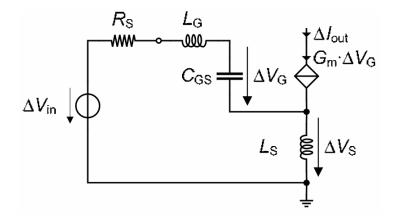

|   |     | 7.1.5    | LNA $n^{\circ} 5$ : Common source inductively degenerated $\ldots \ldots \ldots \ldots \ldots 127$               |

|   |     | 7.1.6    | Conclusion on LNA architectures                                                                                  |

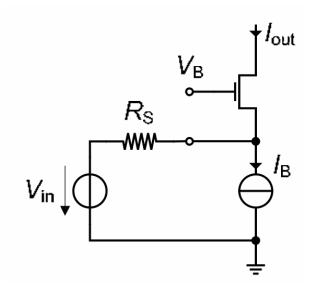

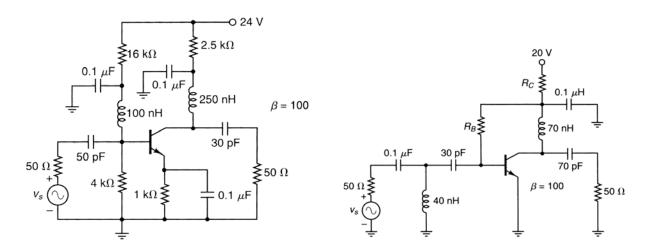

|   | 7.2 | Bipola   | r transistor LNA                                                                                                 |

|   |     | 7.2.1    | The basic principles of bipolar-based LNA                                                                        |

|   |     | 7.2.2    | Architecture $n^{\circ} 1$ : The common emitter                                                                  |

|   |     | 7.2.3    | Architecture $n^{\circ} 2$ : The cascode amplifier $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 146$ |

|   |     | 7.2.4    | Architecture nº 3 : The Darlington amplifier                                                                     |

|   |     | 7.2.5    | Conclusion on bipolar transistor                                                                                 |

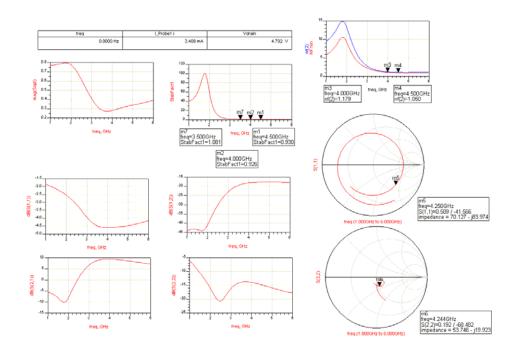

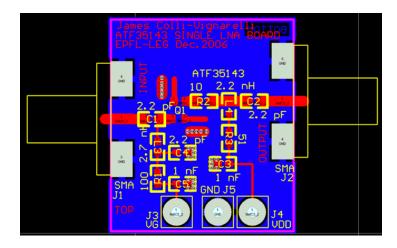

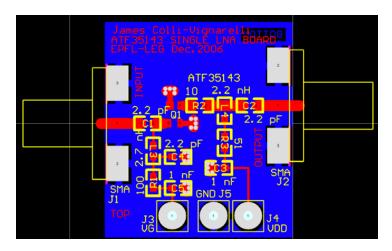

|   | 7.3 | pHEM     | T transistor LNA                                                                                                 |

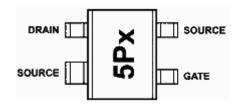

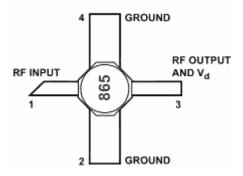

|   |     | 7.3.1    | What is a pHEMT transistor                                                                                       |

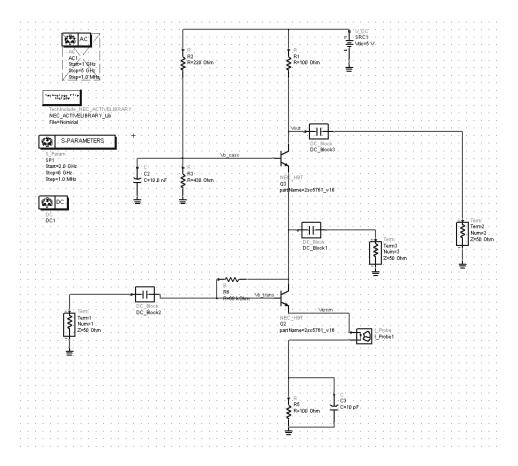

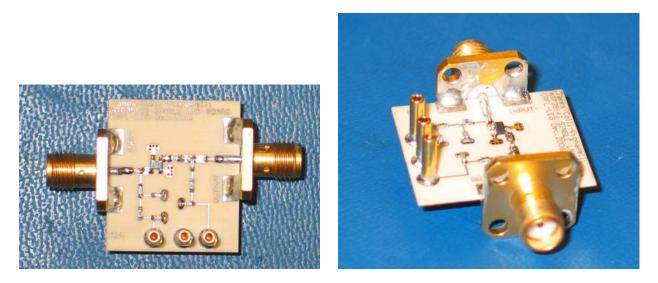

|   |     | 7.3.2    | The single LNA                                                                                                   |

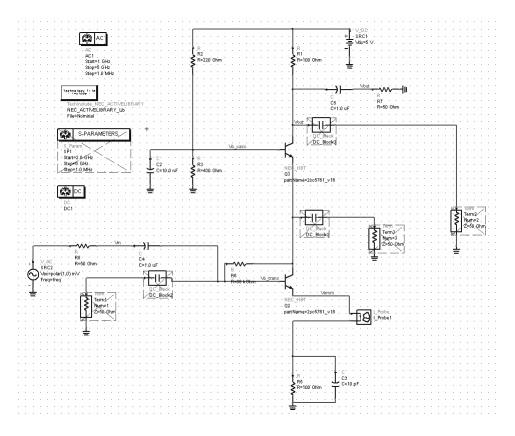

|   |     | 7.3.3    | The complete LNA                                                                                                 |

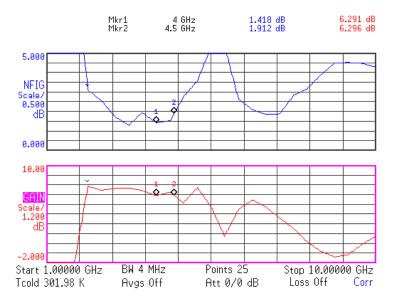

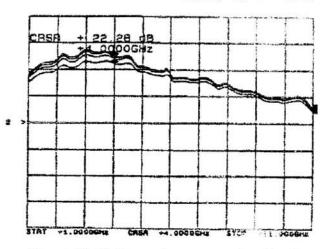

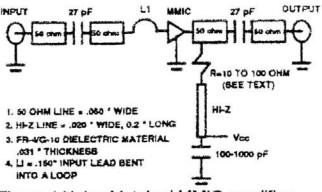

|   | 7.4 | Measu    | rements and improvements                                                                                         |

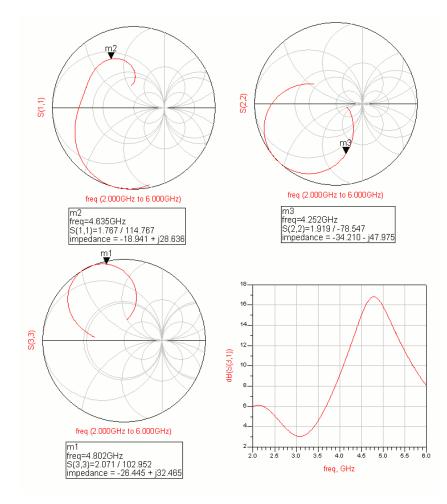

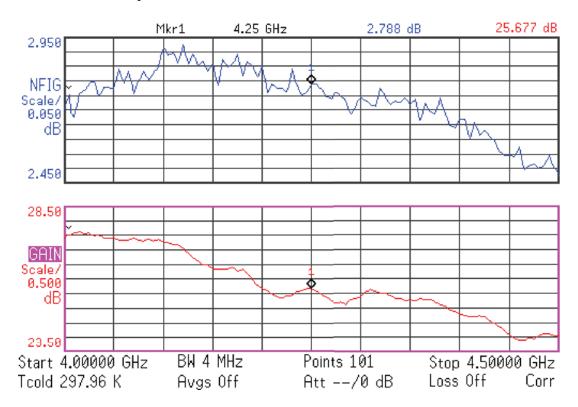

|   |     | 7.4.1    | Single LNA                                                                                                       |

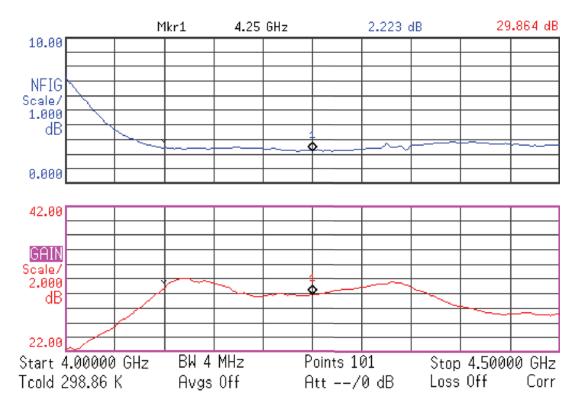

|   |     | 7.4.2    | Complete LNA                                                                                                     |

|   |     | 7.4.3    | Improvements                                                                                                     |

|   | 7.5 | Conclu   | usion                                                                                                            |

| 8 | LNA | a protot | ype nº 2 175                                                                                                     |

|   |     | Introdu  |                                                                                                                  |

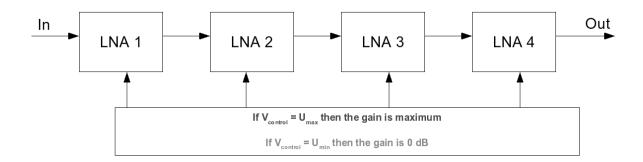

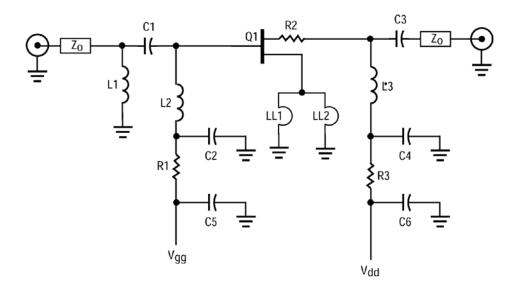

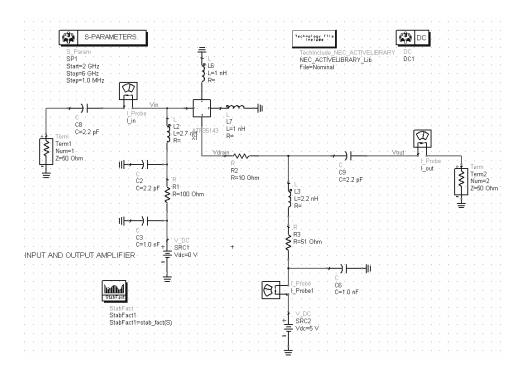

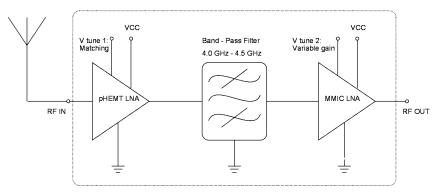

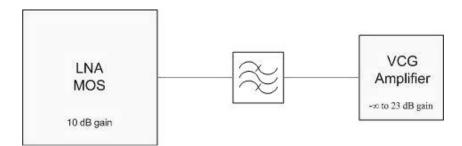

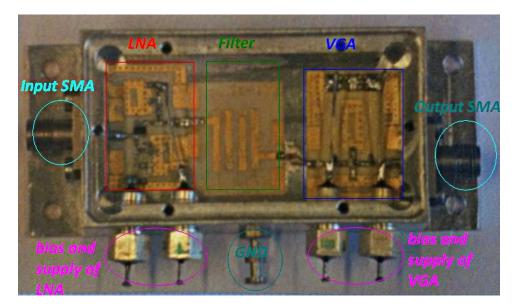

|   | 8.2 | Archite  | ecture of the UWB LNA                                                                                            |

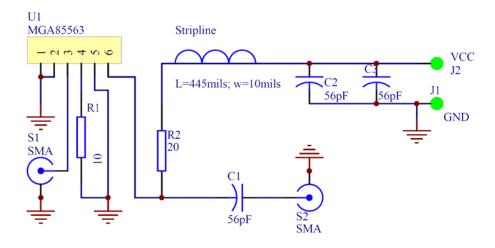

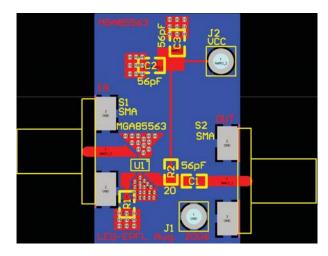

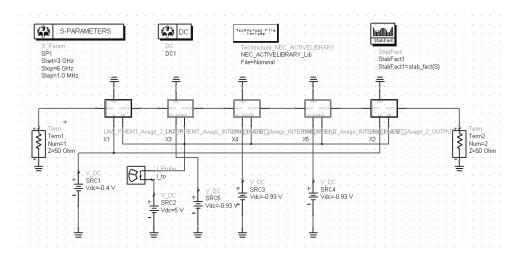

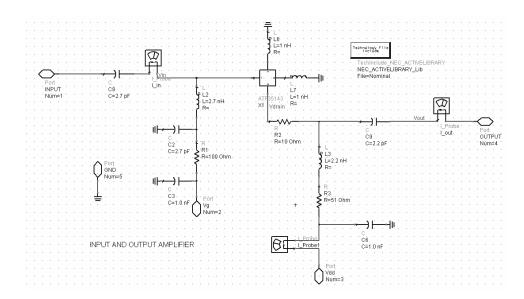

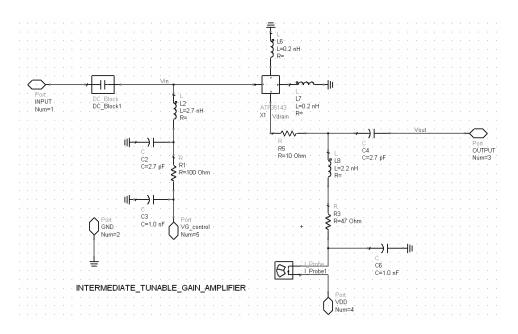

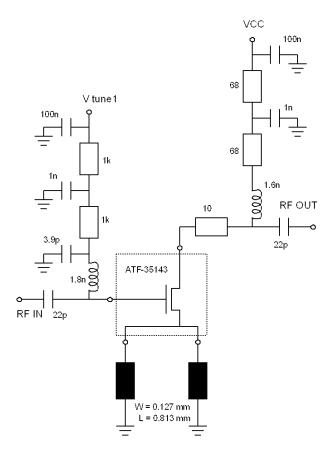

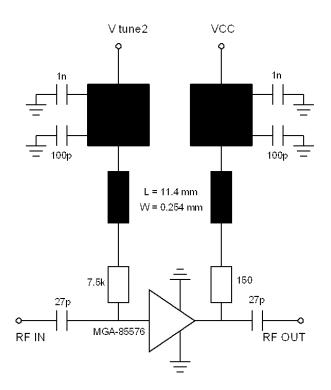

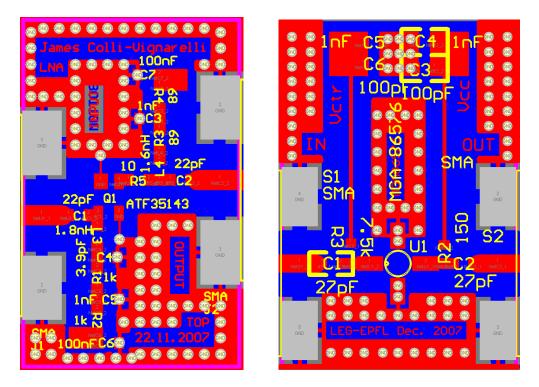

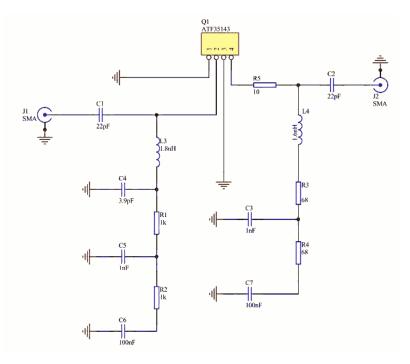

|   | 8.3 |          | atic of the UWB LNA                                                                                              |

|   |     | 8.3.1    | The pHEMT LNA Input Stage                                                                                        |

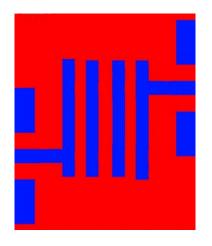

|   |     | 8.3.2    | The UWB Band-Pass Filter                                                                                         |

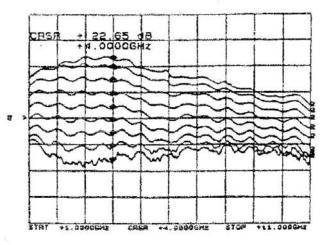

|   |     | 8.3.3    | The Variable-Gain Output Power-Stage                                                                             |

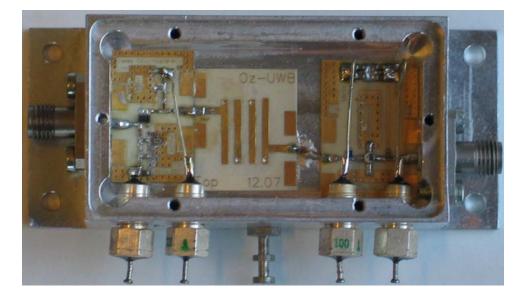

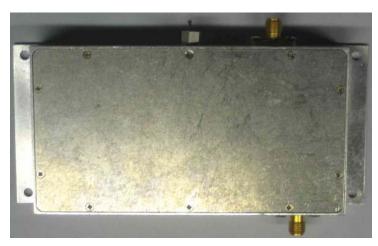

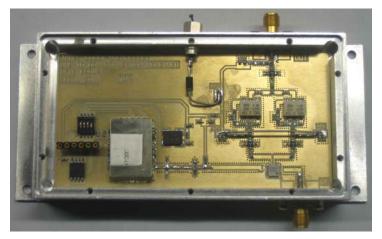

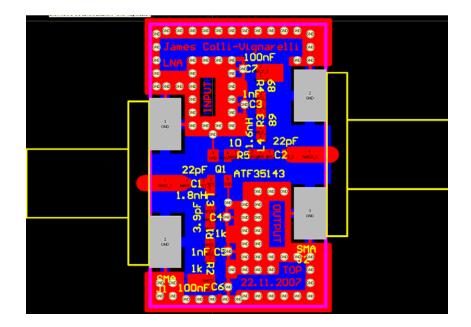

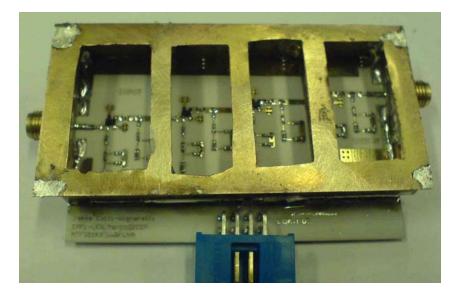

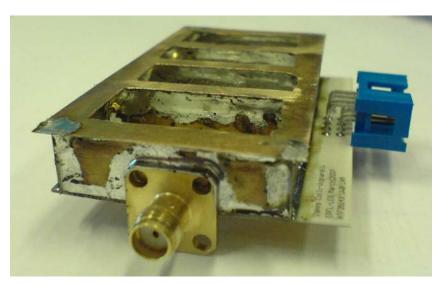

|   | 8.4 | Constr   | uction of the UWB LNA                                                                                            |

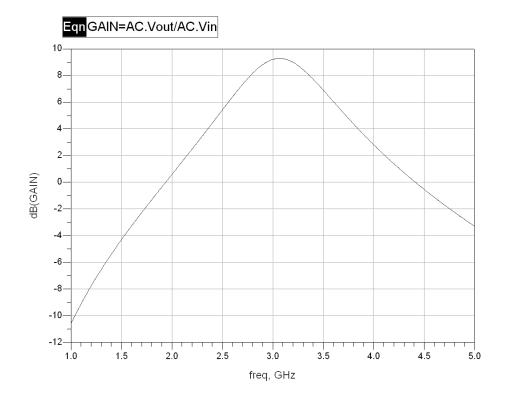

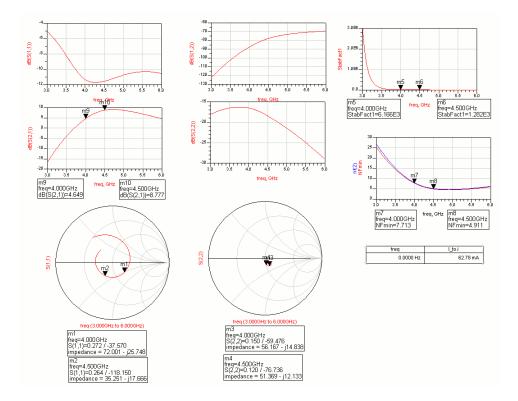

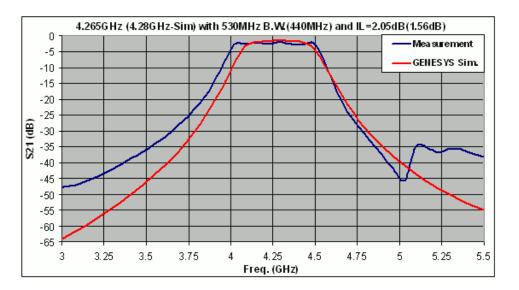

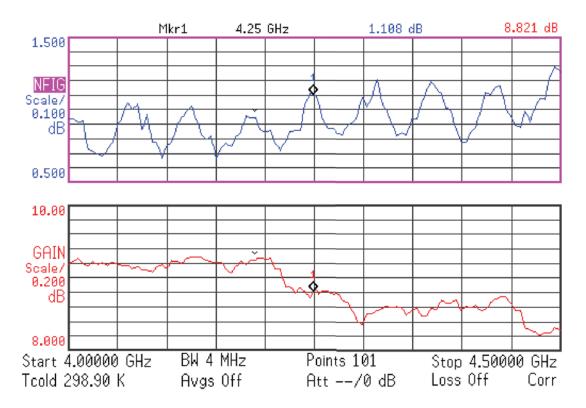

|   | 8.5 |          | rement on the UWB LNA                                                                                            |

|   |     | 8.5.1    | The pHEMT LNA Input Stage                                                                                        |

|   |     | 8.5.2    | The UWB Band-Pass Filter                                                                                         |

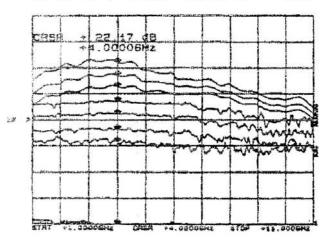

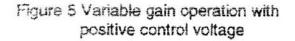

|   |     | 8.5.3    | The Variable-Gain Output Power-Stage                                                                             |

|   |     |          | · ·                                                                                                              |

|    |       | 8.5.4   | The Whole Chain of the UWB LNA with Variable Gain             | 184 |

|----|-------|---------|---------------------------------------------------------------|-----|

|    | 8.6   | Conclu  | sion                                                          | 186 |

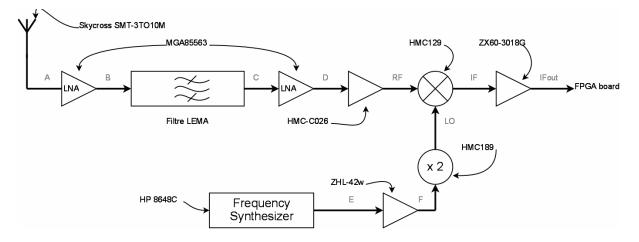

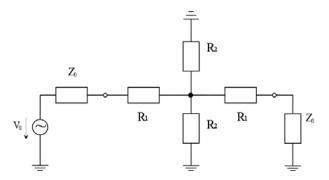

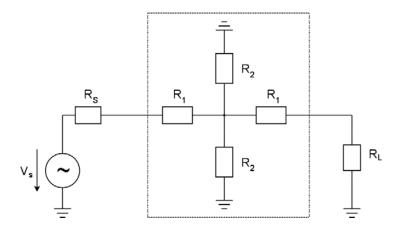

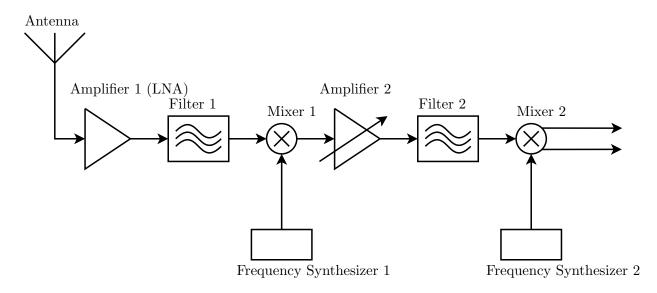

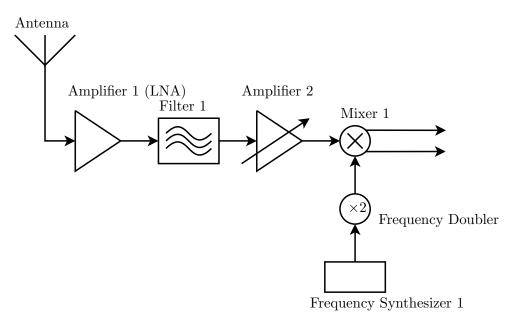

| 9  | I/Q I | Demodu  | ilator                                                        | 187 |

|    | 9.1   | Introdu | iction                                                        | 187 |

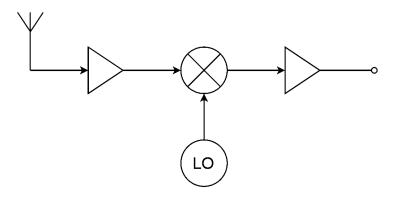

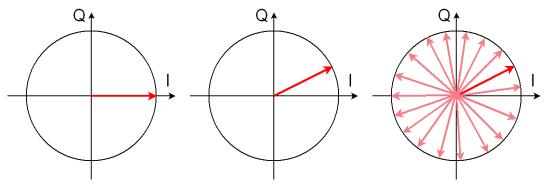

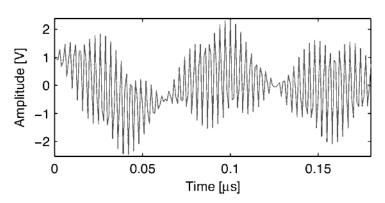

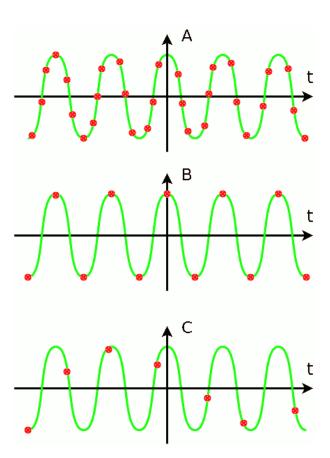

|    |       | 9.1.1   | Frequency down-conversion                                     | 188 |

|    |       | 9.1.2   | The importance of I/Q demodulation in our Testbed             | 188 |

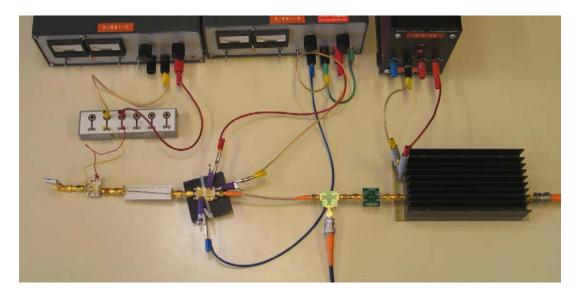

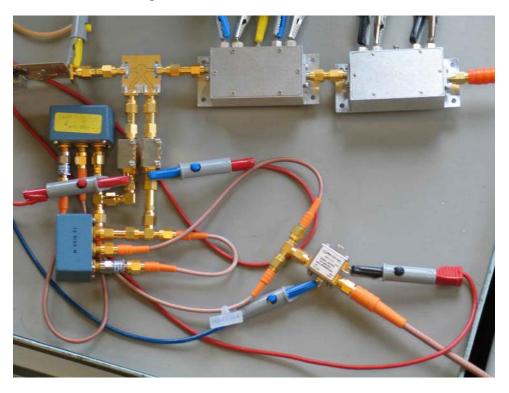

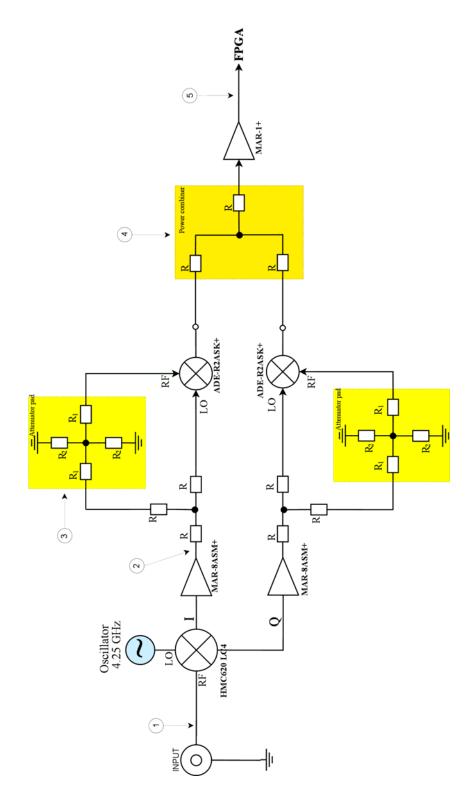

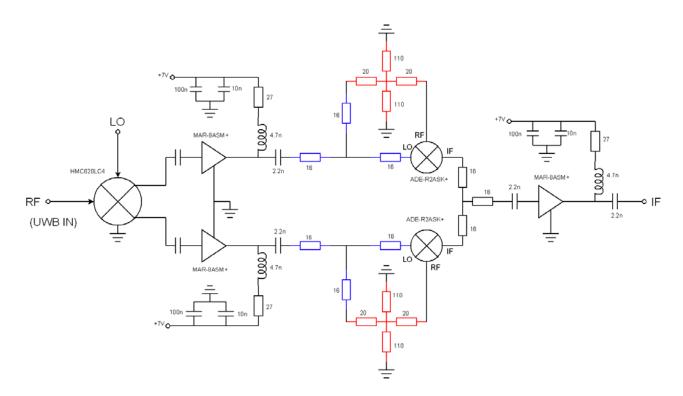

|    | 9.2   | I/Q der | nodulator architecture                                        | 192 |

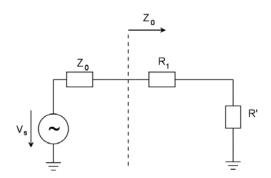

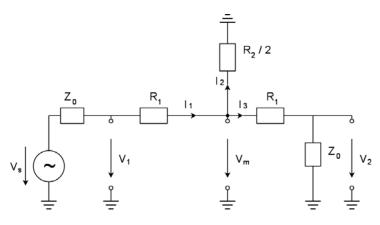

|    | 9.3   | Schem   | atic of the receiver                                          | 195 |

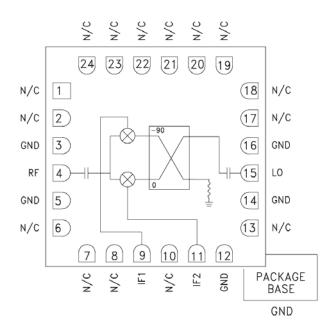

|    |       | 9.3.1   | The I/Q mixer                                                 | 195 |

|    |       | 9.3.2   | Amplifiers                                                    | 195 |

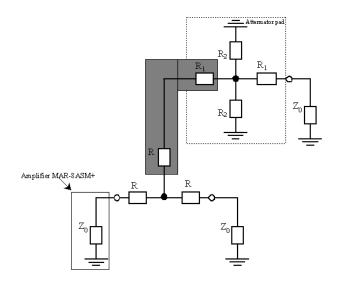

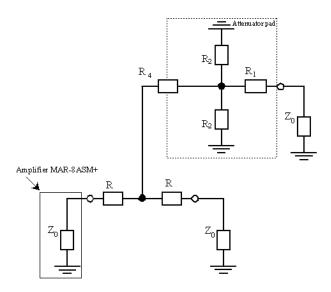

|    |       | 9.3.3   | The squaring circuit                                          | 197 |

|    |       | 9.3.4   | Resistive network                                             | 197 |

|    |       | 9.3.5   | Decoupling elements                                           | 201 |

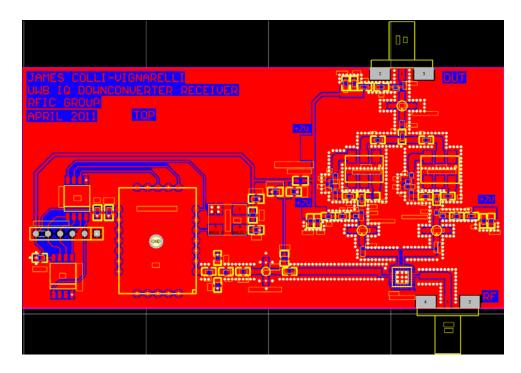

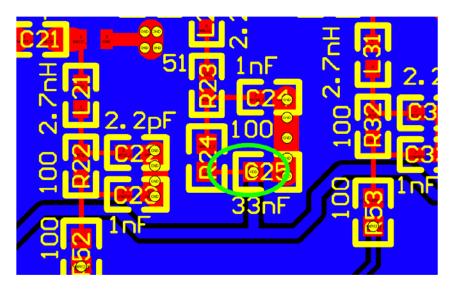

|    | 9.4   | PCB la  | yout - Prototype $n^{\circ}$ 1                                | 202 |

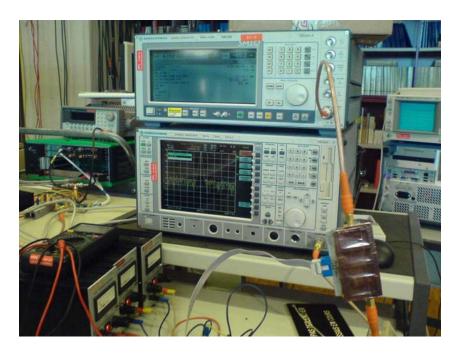

|    | 9.5   | Measu   | rements and tests                                             | 203 |

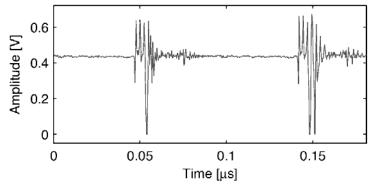

|    |       | 9.5.1   | The receiver board without the I/Q mixer                      | 204 |

|    |       | 9.5.2   | The receiver board with the I/Q mixer                         | 206 |

|    |       | 9.5.3   | Conclusion on prototype nº 1                                  | 209 |

|    | 9.6   | Improv  | vement - Prototype n° 2                                       | 211 |

|    | 9.7   | Conclu  | sion                                                          | 212 |

| 10 | Fvn   | rimont  | al validation and performance evaluation with the UWB testbed | 217 |

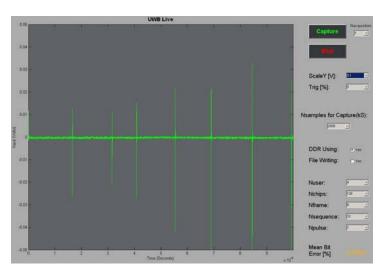

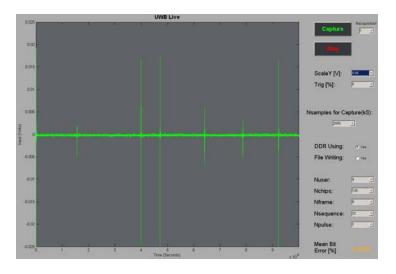

| 10 | -     |         | mental validation of PID synchronisation algorithm            |     |

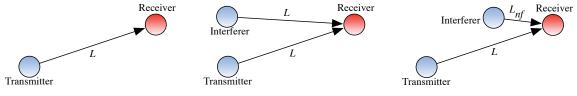

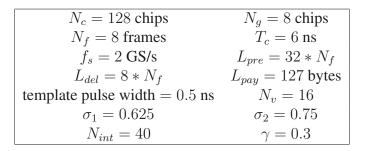

|    | 10,1  | -       | System presentation                                           |     |

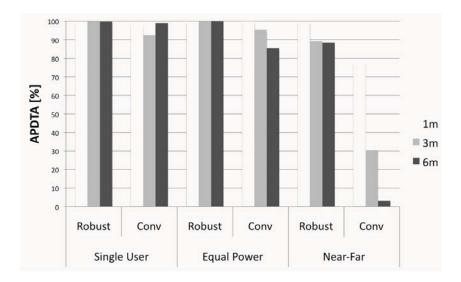

|    |       |         | Performance Evaluation                                        |     |

|    |       |         | Conclusion about PID algorithm                                |     |

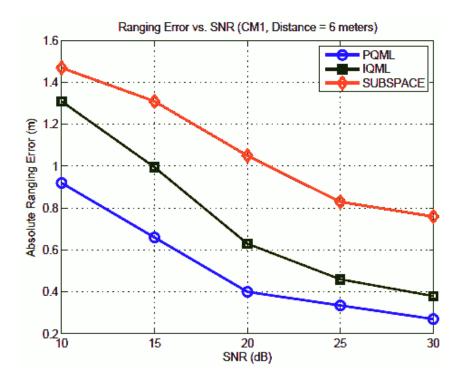

|    | 10.2  |         | mental validation of ranging algorithm                        |     |

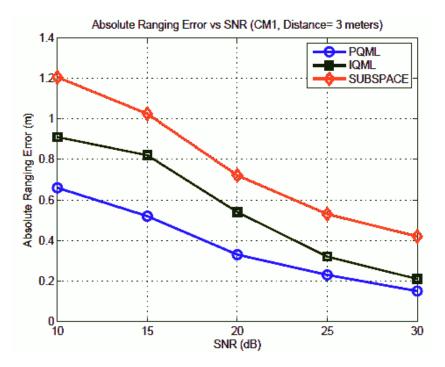

|    | 10.2  | _       | Experimental validation of the PQML algorithm                 |     |

|    |       |         | Statistical Analysis of IR-UWB MUI                            |     |

|    | 10.3  |         | mental validation of security algorithm                       |     |

|    |       | -       |                                                               |     |

|    | 10.4  | CONCIU  | 101011                                                        | ()  |

| III | Design and realisation of integrated low power IR-UWB transmi | t-  |

|-----|---------------------------------------------------------------|-----|

| ter |                                                               | 229 |

| 11 | Low  | -nower  | transmitter architectures                                              | 231 |

|----|------|---------|------------------------------------------------------------------------|-----|

|    |      | -       |                                                                        |     |

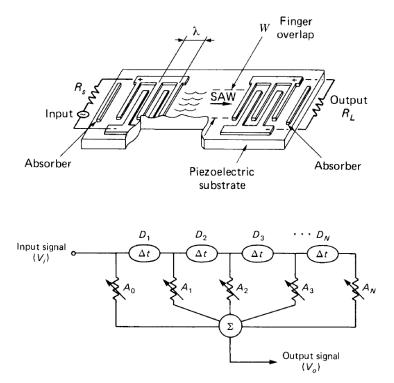

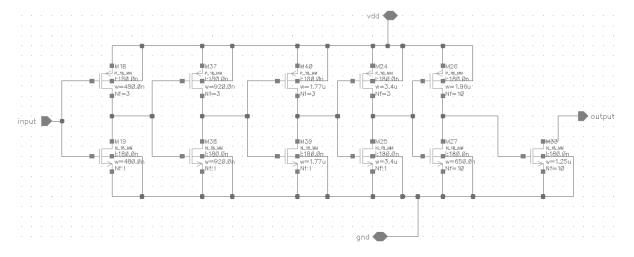

|    |      |         | bw power transmitter architecture                                      |     |

|    | 11.2 | •       | Specifications                                                         |     |

|    |      |         | Minimal power estimation for a pulse                                   |     |

|    |      |         | Minimal voltage estimation for a pulse                                 |     |

|    |      |         | Overview of actual solutions for very low power UWB transmitter        |     |

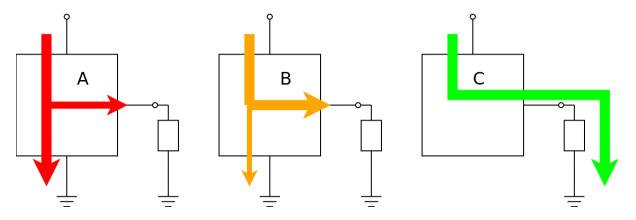

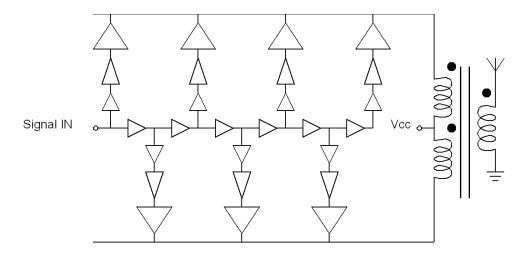

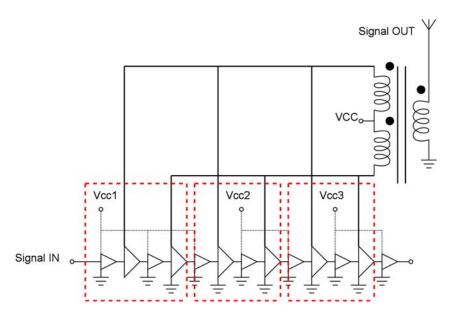

|    |      |         | Solution retained for this work                                        |     |

|    | 112  |         |                                                                        |     |

|    | 11.3 |         |                                                                        |     |

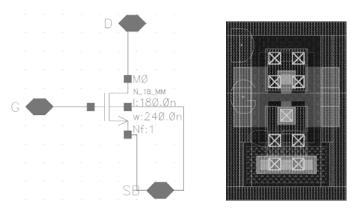

|    |      |         | The technology                                                         |     |

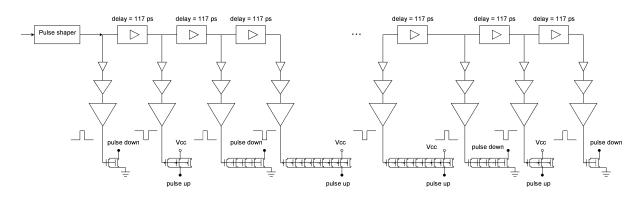

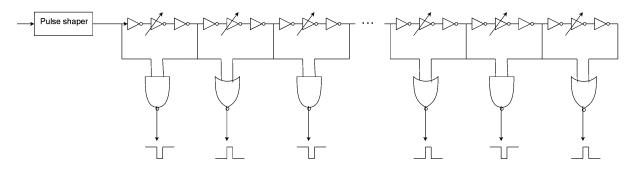

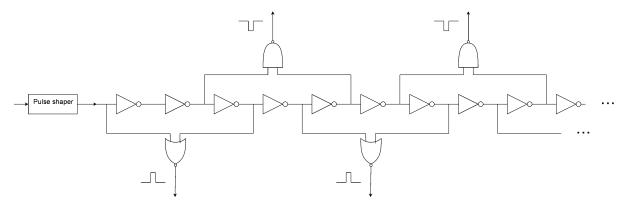

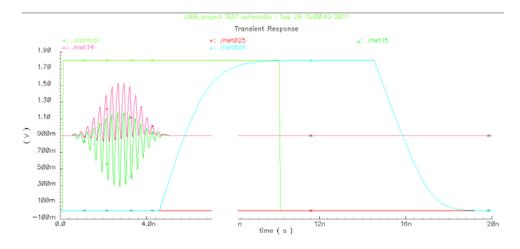

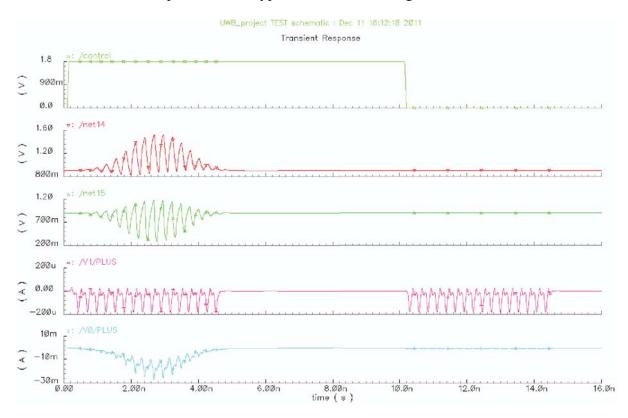

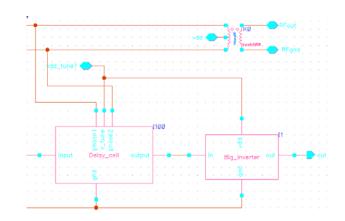

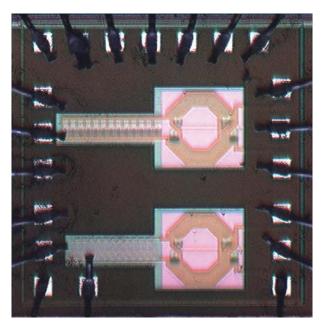

|    |      |         | The design of a prototype: prototype $n^{\circ} 1$                     |     |

|    |      | 11.3.3  | Improvement of prototype $n^{\circ}$ 1: prototypes $n^{\circ}$ 2 and 3 | 250 |

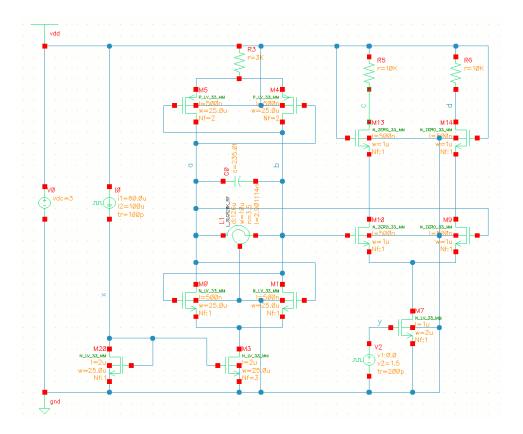

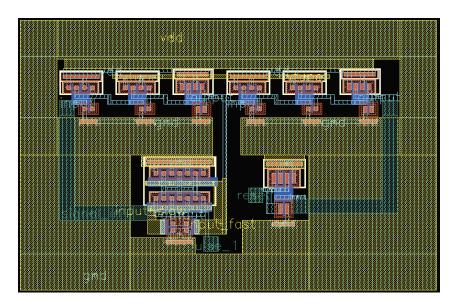

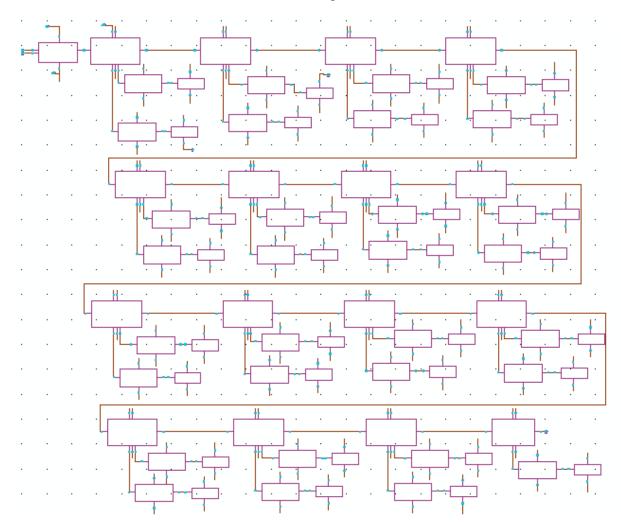

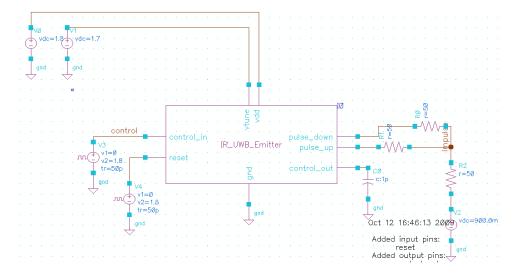

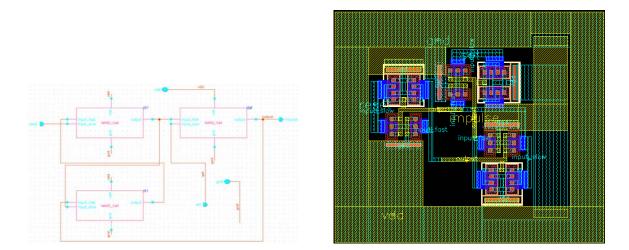

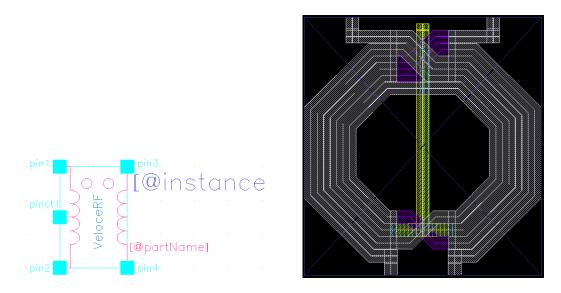

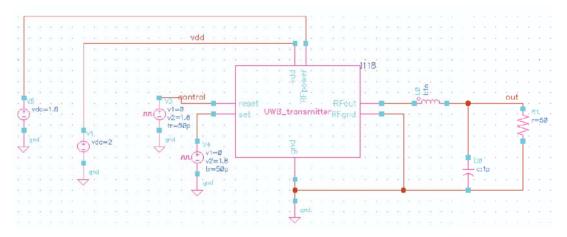

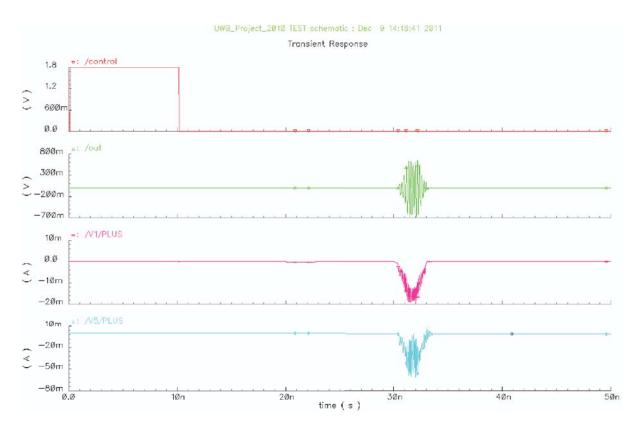

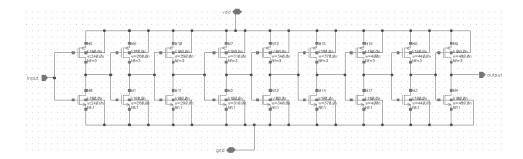

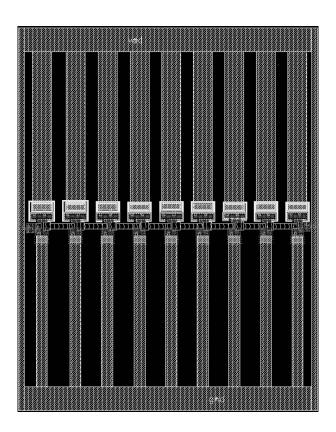

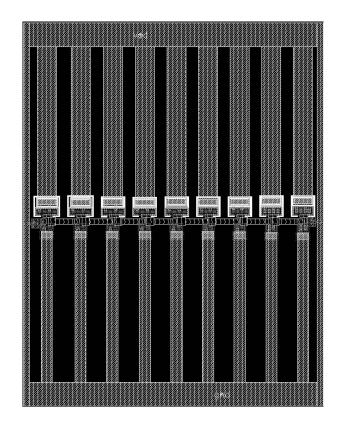

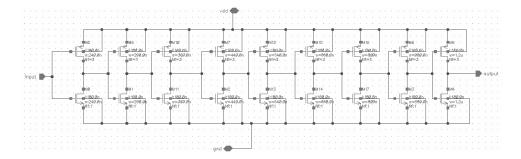

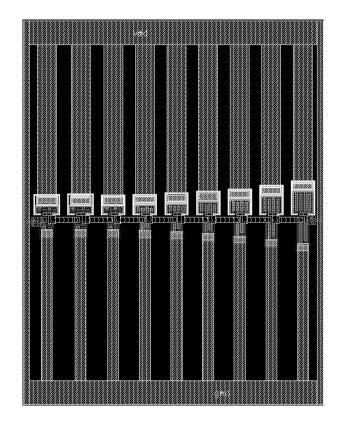

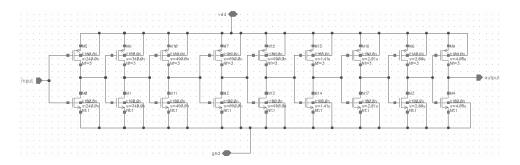

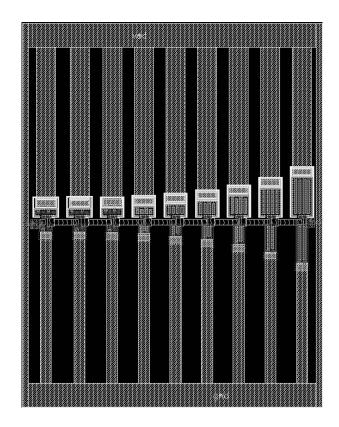

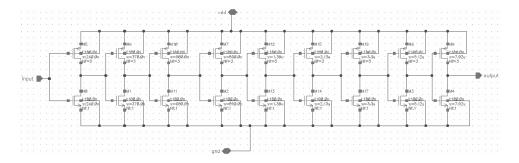

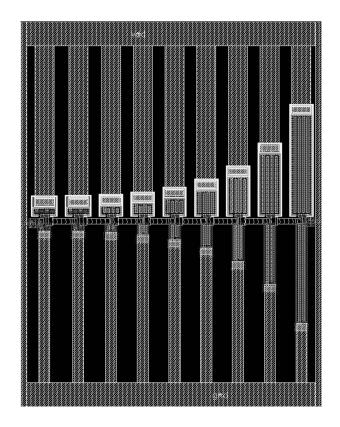

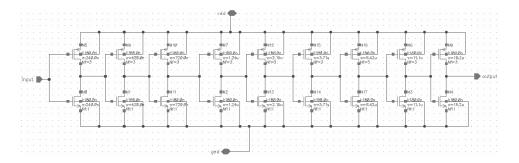

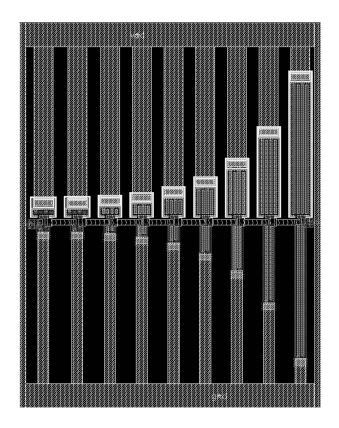

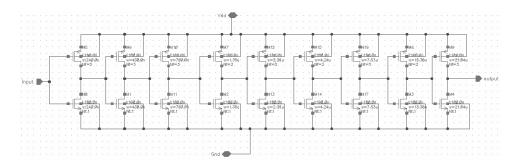

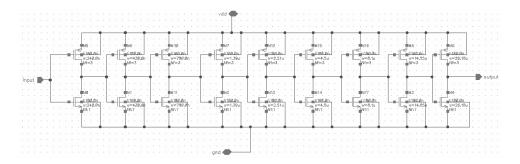

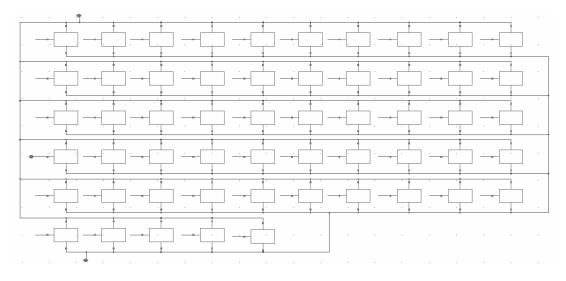

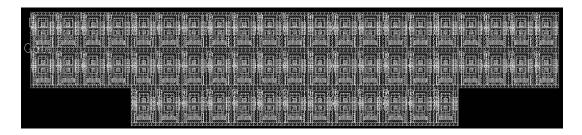

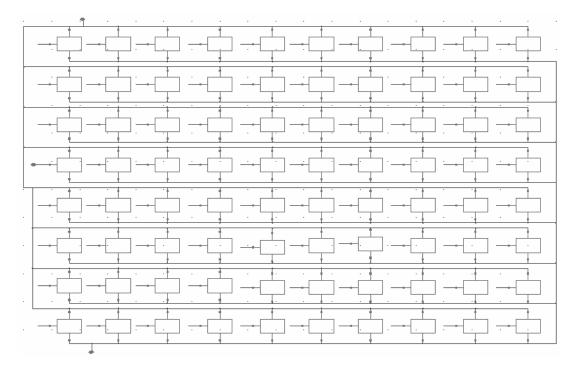

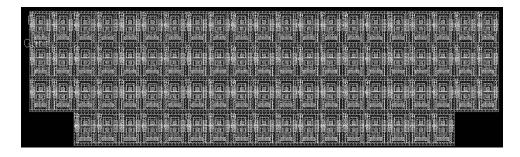

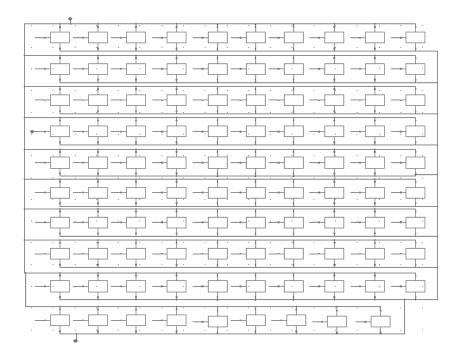

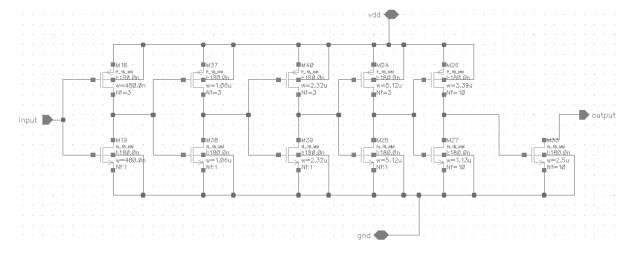

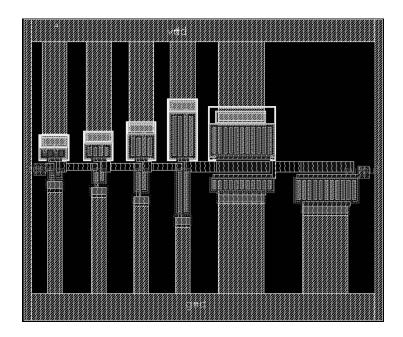

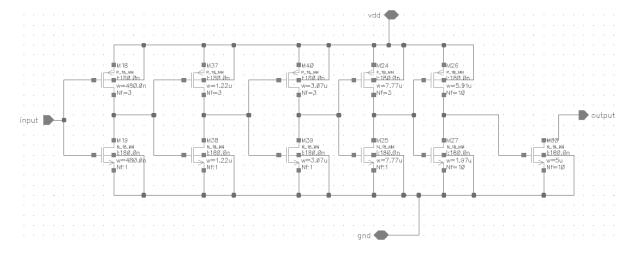

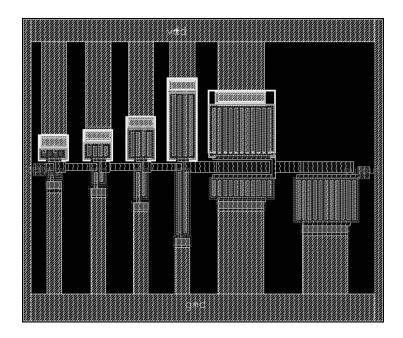

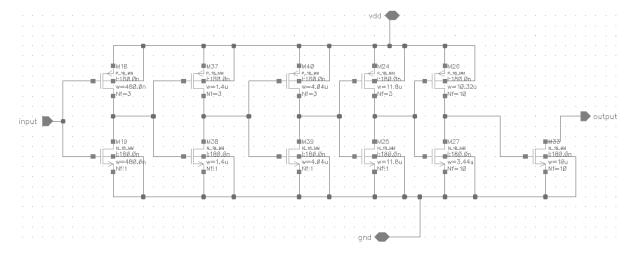

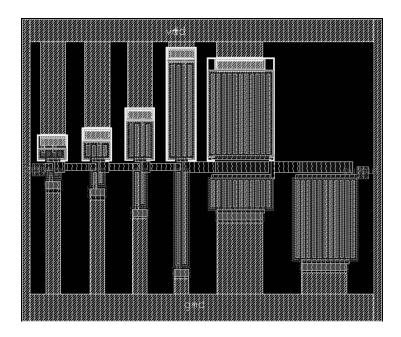

| 12 | The  | Cadenc  | e schematics and layouts of prototype nº 1                             | 251 |

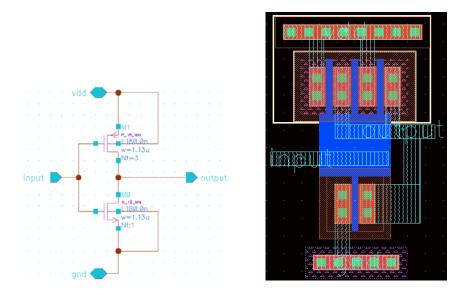

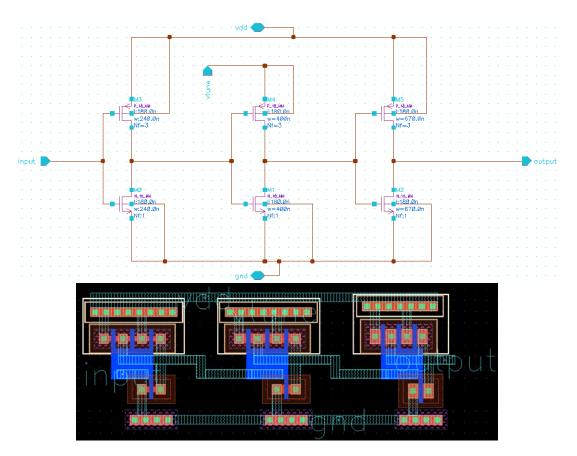

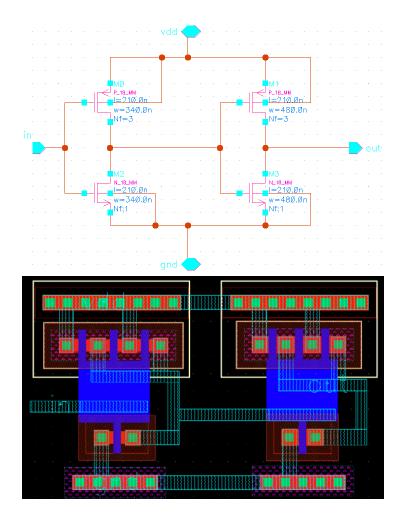

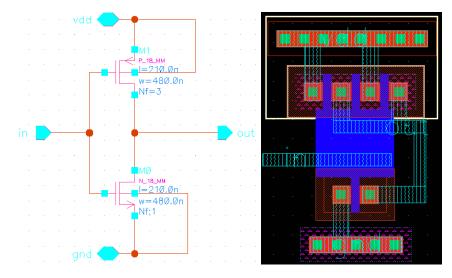

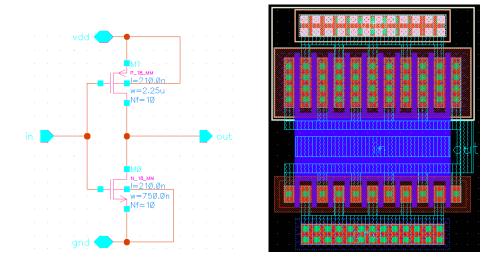

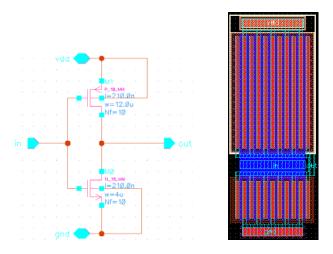

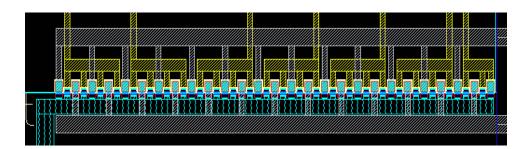

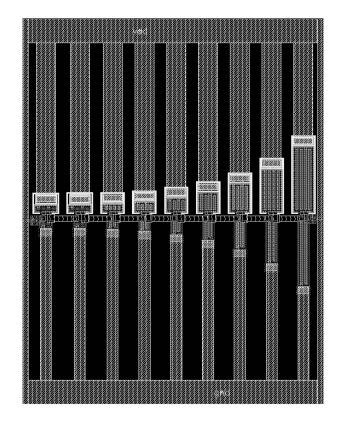

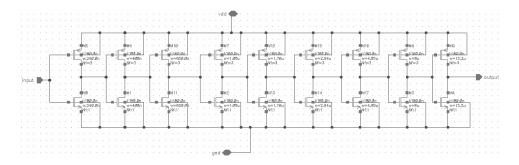

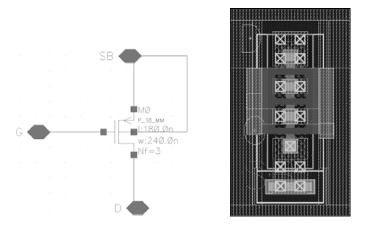

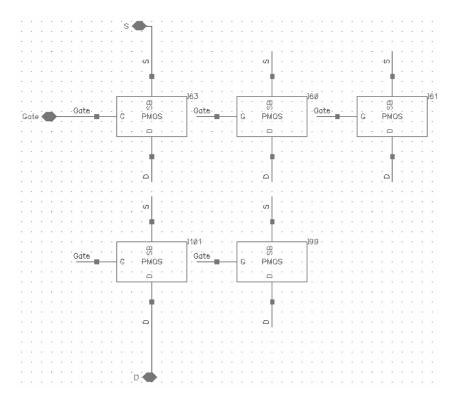

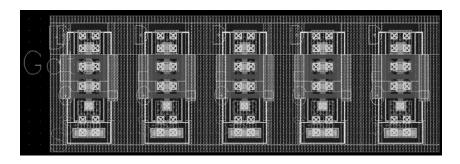

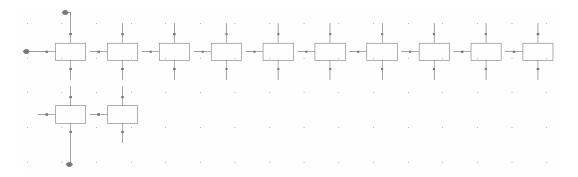

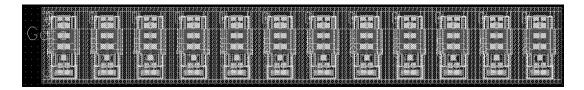

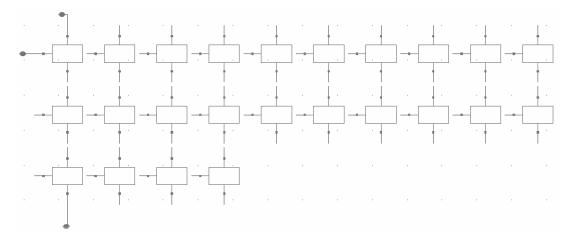

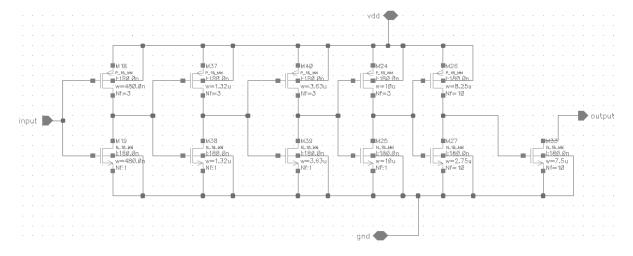

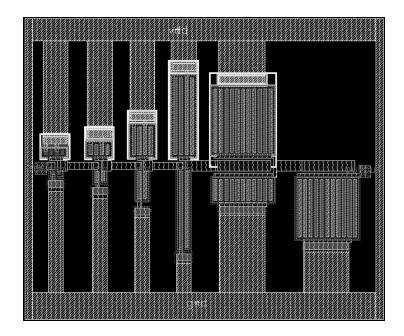

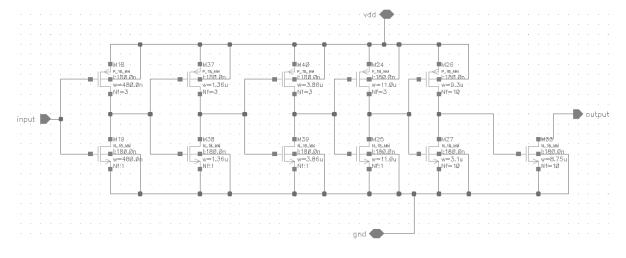

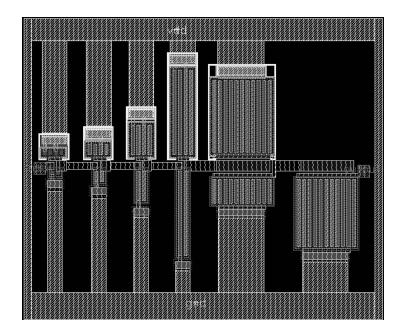

|    | 12.1 | The ele | ementary cells                                                         | 253 |

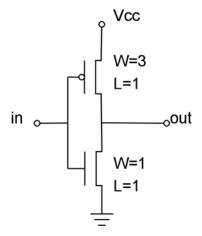

|    |      | 12.1.1  | The reference inverter                                                 | 253 |

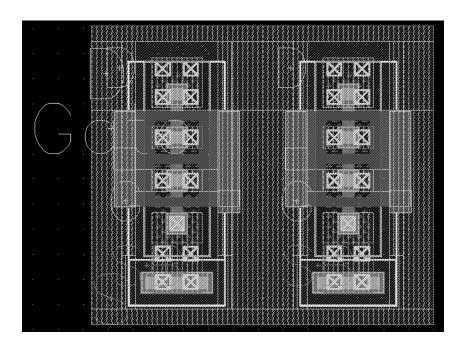

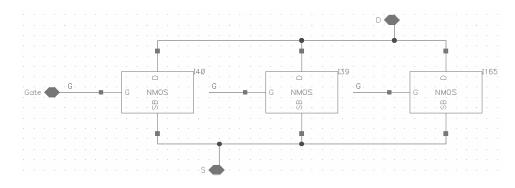

|    |      |         | The NAND gate                                                          |     |

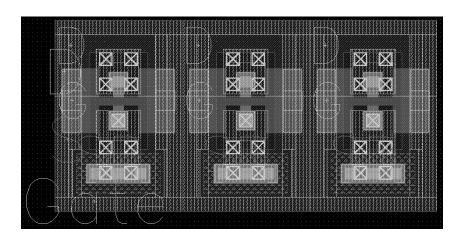

|    |      |         | The NOR gate                                                           |     |

|    |      |         | The (real) inverter                                                    |     |

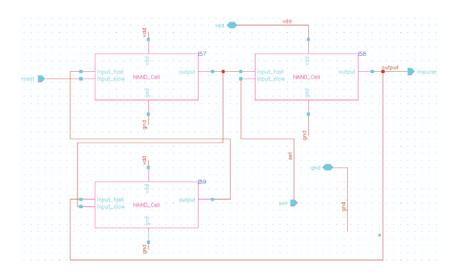

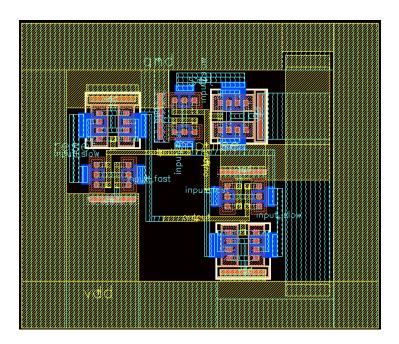

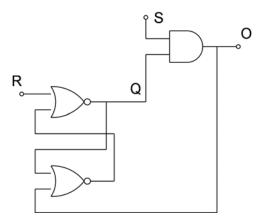

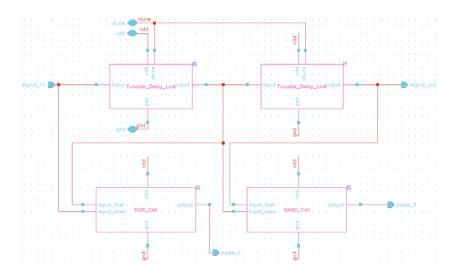

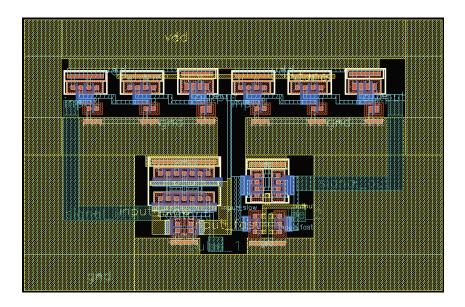

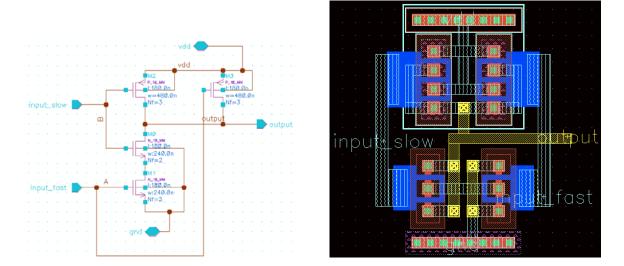

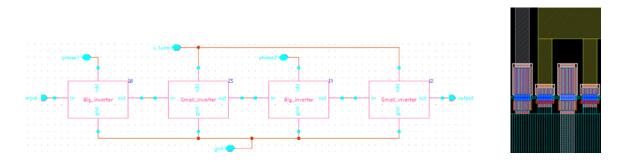

|    | 12.2 |         | mplex cells                                                            |     |

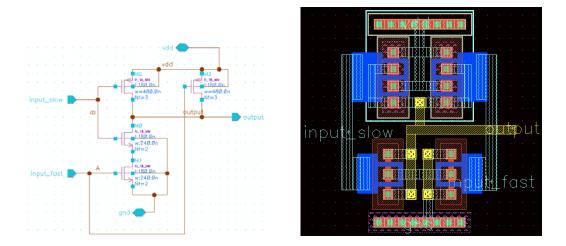

|    |      | 12.2.1  | -                                                                      |     |

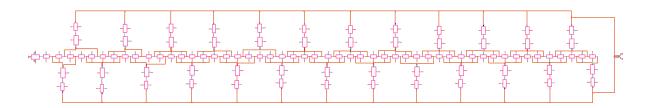

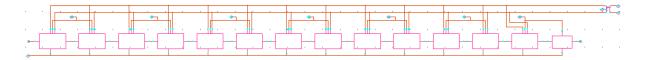

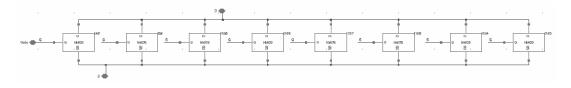

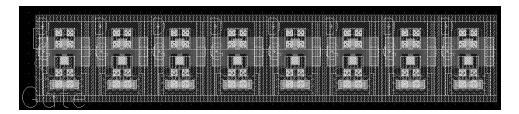

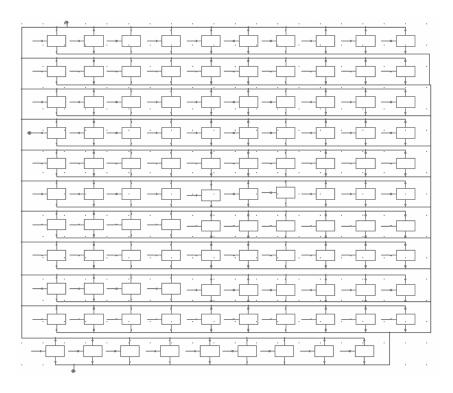

|    |      | 12.2.2  | The tunable delay line                                                 |     |

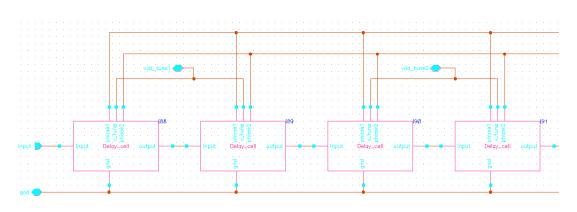

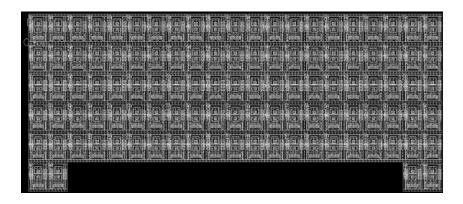

|    |      |         | The delay line macrocell                                               |     |

|    |      |         | The delay line macrocell - the ending cell                             |     |

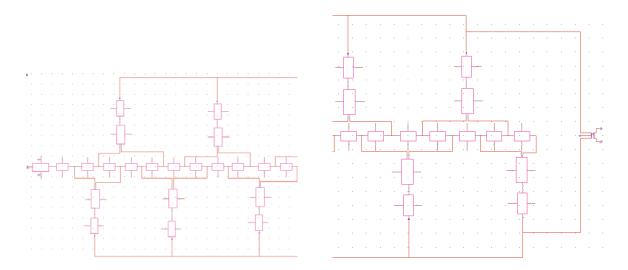

|    | 12.3 |         | ffers and switches                                                     |     |

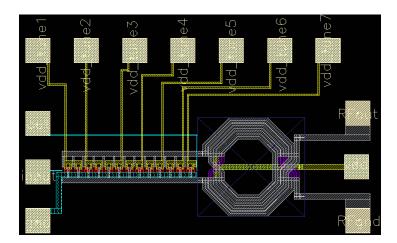

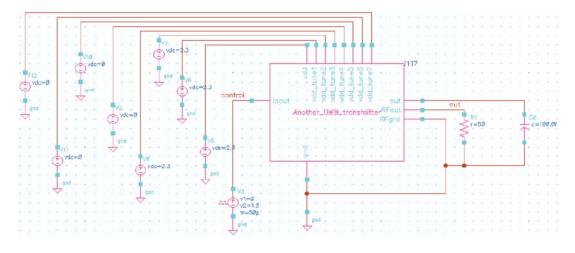

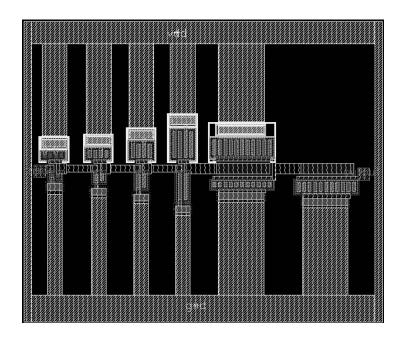

|    |      |         | mplete circuit                                                         |     |

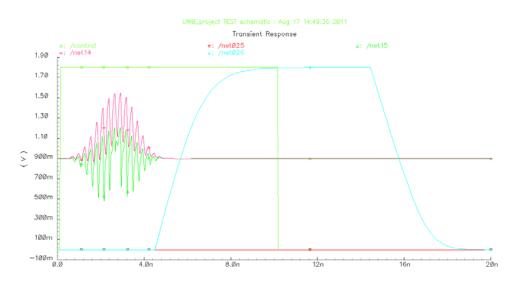

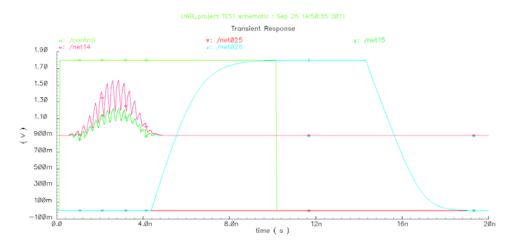

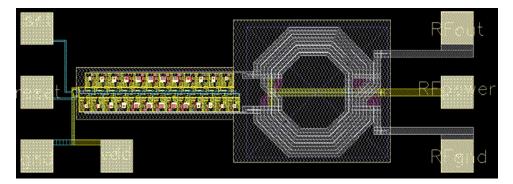

|    |      |         | Prototype $n^{\circ}$ 1                                                |     |

|    | 12.0 | 1050 01 |                                                                        | 200 |

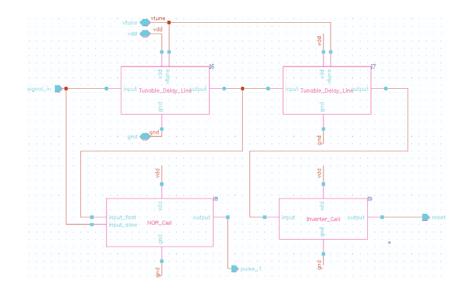

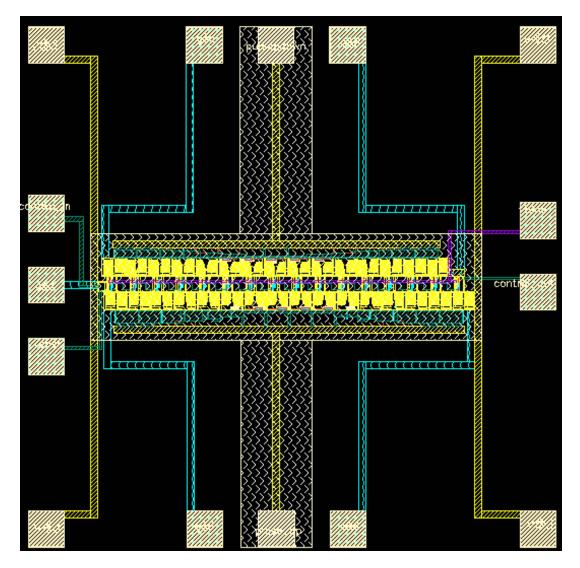

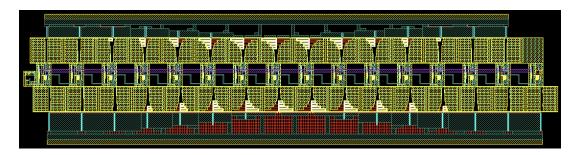

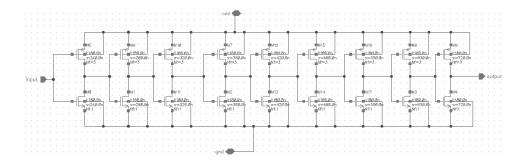

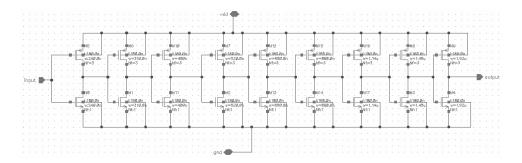

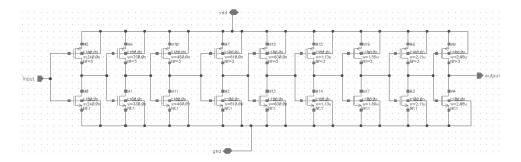

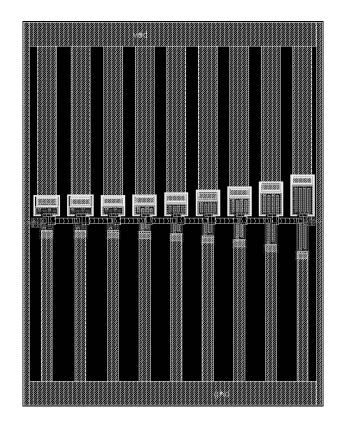

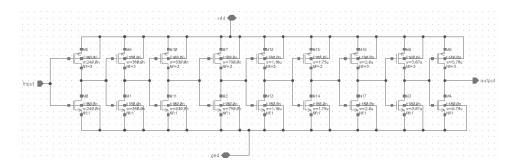

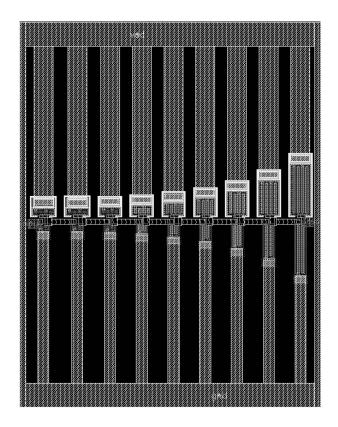

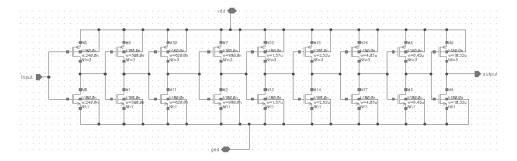

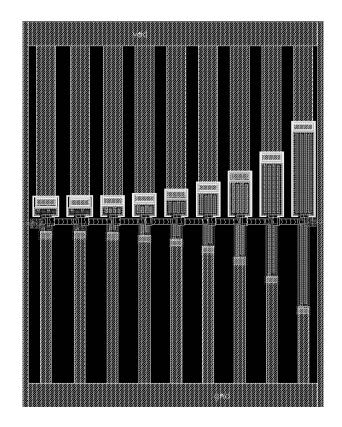

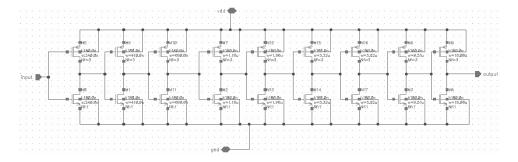

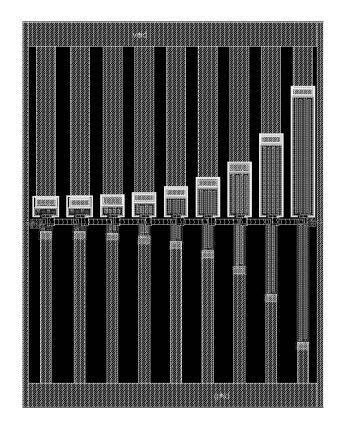

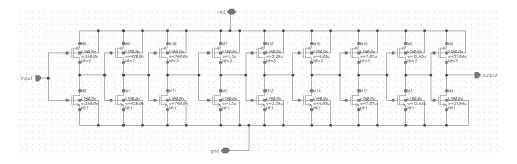

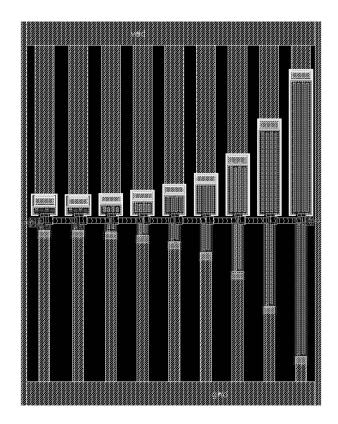

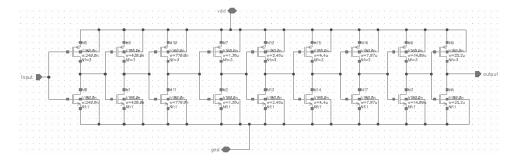

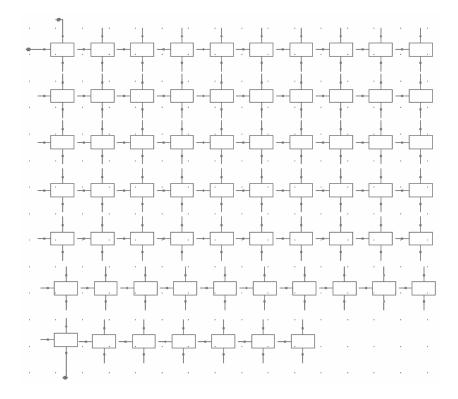

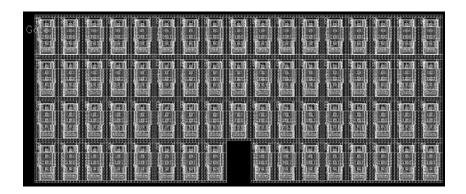

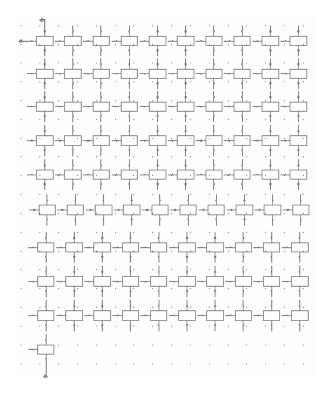

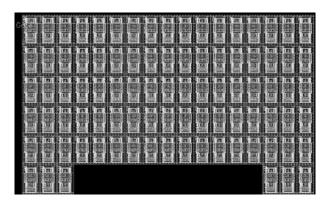

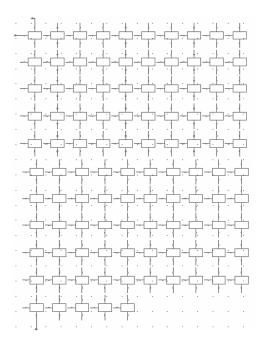

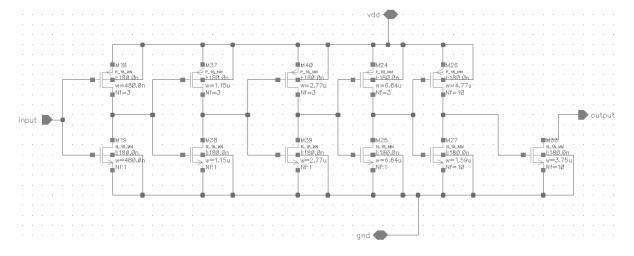

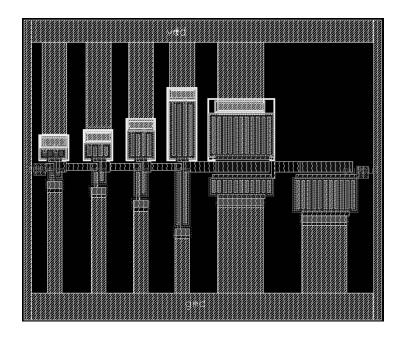

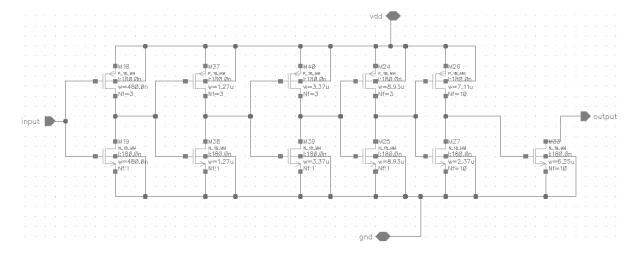

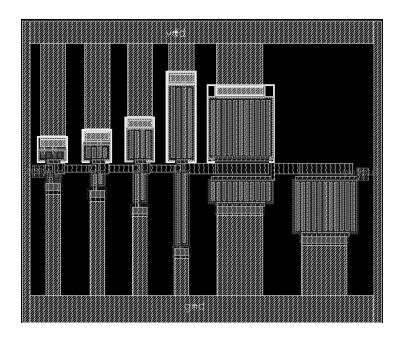

| 13 | The  | Cadenc  | e schematics and layout of prototypes nº 2 and nº 3                    | 271 |

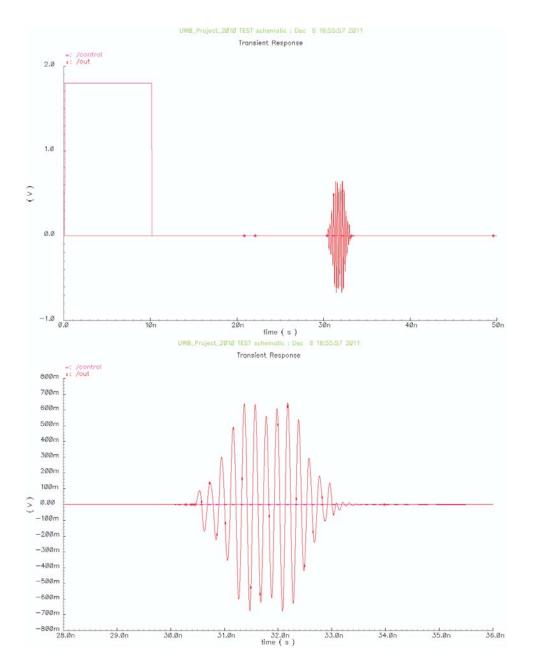

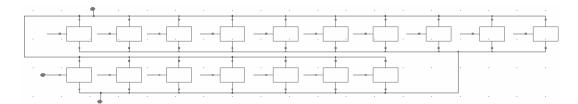

|    | 13.1 | The pro | ototype $n^{\circ} 2$                                                  | 273 |

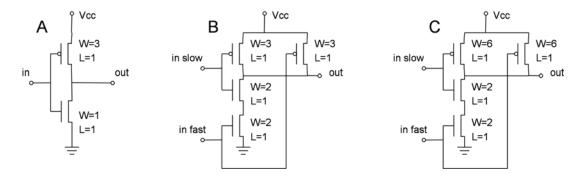

|    |      | 13.1.1  | The impulse generator                                                  | 273 |

|    |      | 13.1.2  | The NAND gate                                                          | 273 |

|    | 15.2         | Future work and perspective                                                                                                                                                                         | 320 |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 15.1         | Contributions made in this work                                                                                                                                                                     | 319 |

| 15 | Conc         | lusion                                                                                                                                                                                              | 319 |

|    | 14.7         | Conclusion and perspective                                                                                                                                                                          | 315 |

|    | <del>-</del> | 14.6.3 Tests with Khepera modulator                                                                                                                                                                 |     |

|    |              | 14.6.2 Tests with current consumption optimization                                                                                                                                                  |     |

|    |              | 14.6.1 Tests with the function generator                                                                                                                                                            |     |

|    | 14.6         | Prototype n° 3 validation                                                                                                                                                                           |     |

|    |              | 14.5.2 Tests with the Khepera modulator                                                                                                                                                             |     |

|    |              | 14.5.1 Tests with the function generator                                                                                                                                                            |     |

|    | 14.5         | Prototype $n^{\circ}$ 2 validation                                                                                                                                                                  |     |

|    |              | Prototypes $n^{\circ} 2$ and $n^{\circ} 3$ measurement board $\ldots \ldots \ldots$ |     |

|    | 14.3         | Prototype nº 1 validation                                                                                                                                                                           | 294 |

|    | 14.2         | Prototype nº 1 measurement board                                                                                                                                                                    | 291 |

|    | 14.1         | Current measurements                                                                                                                                                                                | 289 |

| 14 | Expe         | rimental validation and measurements                                                                                                                                                                | 289 |

|    |              | 13.2.0 Tests of the Flototype II <sup>-</sup> 5                                                                                                                                                     | 200 |

|    |              | 13.2.5 The complete transmitter    2      13.2.6 Tests of the Prototype nº 3    2                                                                                                                   |     |

|    |              | 13.2.4 The balun transformer                                                                                                                                                                        |     |

|    |              | 13.2.3 The delay cell                                                                                                                                                                               |     |

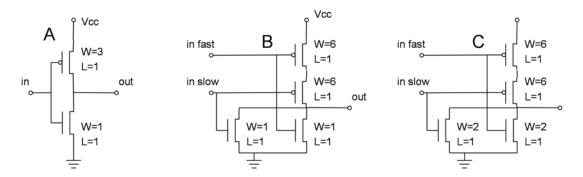

|    |              | 13.2.2 The big inverter                                                                                                                                                                             |     |

|    |              | 13.2.1 The small inverter                                                                                                                                                                           |     |

|    | 13.2         | The prototype n° 3                                                                                                                                                                                  |     |

|    |              | 13.1.8 Tests of the Prototype $n^{\circ} 2$                                                                                                                                                         |     |

|    |              | 13.1.7 The complete circuit of prototype $n^{\circ} 2 \dots 2$                                                                                                                                      |     |

|    |              | 13.1.6 The balun transformer                                                                                                                                                                        |     |

|    |              | 13.1.5 The buffers                                                                                                                                                                                  | 276 |

|    |              | 13.1.4 The inverter cell 2                                                                                                                                                                          | 274 |

|    |              | 13.1.3 The inverter cell 1                                                                                                                                                                          | 273 |

## **IV** Appendices

| A | Mat          | lab sour  | ce codes                                                                                                                   | 325 |

|---|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------|-----|

|   | A.1          | RF line   | e design                                                                                                                   | 325 |

|   |              | A.1.1     | Stripline calculation                                                                                                      | 325 |

|   |              | A.1.2     | Coplanar Waveguide calculation                                                                                             | 326 |

|   |              | A.1.3     | RFC stripline calculation                                                                                                  | 328 |

|   |              | A.1.4     | Microstrip inductance calculation                                                                                          | 329 |

|   | A.2          | Numer     | ic applications                                                                                                            | 330 |

|   |              | A.2.1     | Matlab code for $\alpha$ calculation $\ldots \ldots \ldots$ | 330 |

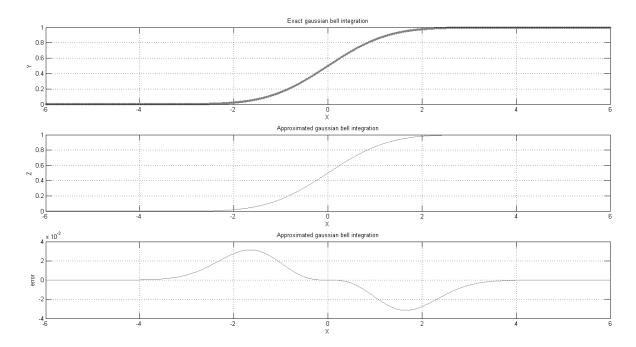

|   |              | A.2.2     | Matlab code for Gauss integral error estimation with Chu estimation                                                        | 330 |

|   |              | A.2.3     | Matlab code for weight calculation                                                                                         | 331 |

|   |              | A.2.4     | Matlab code for weight verification                                                                                        | 333 |

| B | The          | oscillato | or's firmware                                                                                                              | 339 |

| - | B.1          |           | nthesizer's registers                                                                                                      |     |

|   |              | B.1.1     | The Shift register                                                                                                         |     |

|   |              | B.1.2     | The Initialisation Latch register                                                                                          |     |

|   |              | B.1.3     | The R counter register                                                                                                     |     |

|   |              | B.1.4     | The N counter register                                                                                                     |     |

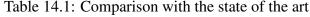

|   | B.2          | Code d    | lescription                                                                                                                |     |

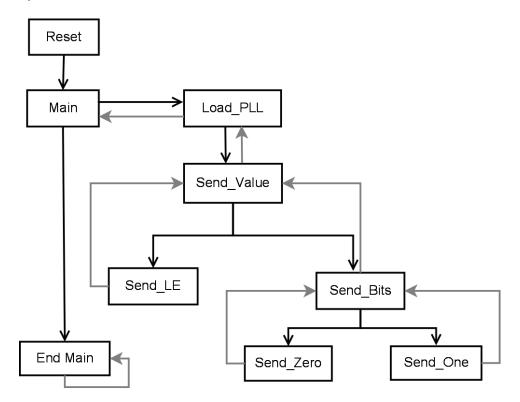

|   |              | B.2.1     | The reset                                                                                                                  |     |

|   |              | B.2.2     | The reset part                                                                                                             |     |

|   |              | B.2.3     | The loadData part                                                                                                          |     |

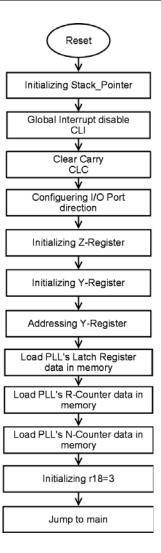

|   |              | B.2.4     | The main                                                                                                                   |     |

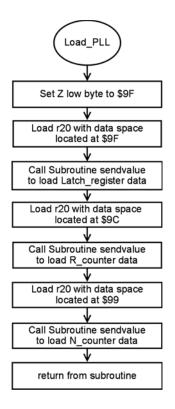

|   |              | B.2.5     | Load_PLL                                                                                                                   |     |

|   |              | B.2.6     | Sendvalue                                                                                                                  |     |

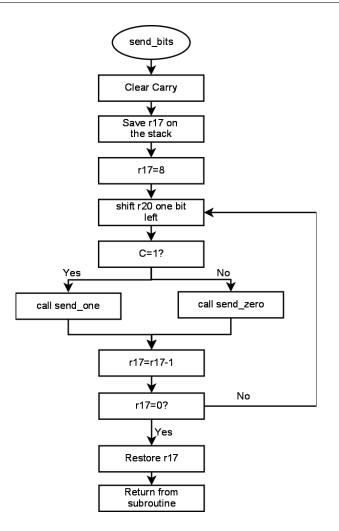

|   |              | B.2.7     | Send_bits                                                                                                                  |     |

|   |              | B.2.8     | Send_one                                                                                                                   | 351 |

|   |              | B.2.9     | Send_zero                                                                                                                  |     |

|   |              | B.2.10    | Send_LE                                                                                                                    | 354 |

|   | B.3          |           | <br>cript                                                                                                                  |     |

| C | <b>D</b> - 1 |           |                                                                                                                            | 2/1 |

| U |              |           | truction                                                                                                                   | 361 |

|   | C.1          | About     | This Project                                                                                                               | 361 |

|   | C.2  | Genera   | ll Constraints in RF PCB Design                                       | 362 |

|---|------|----------|-----------------------------------------------------------------------|-----|

|   | C.3  | Genera   | l Considerations About Soldering Components on Printed Circuit Boards |     |

|   |      | (PCB)    |                                                                       | 363 |

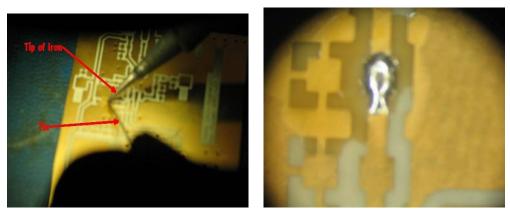

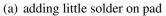

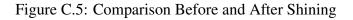

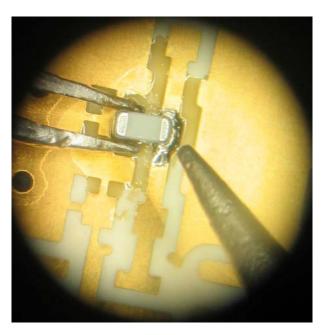

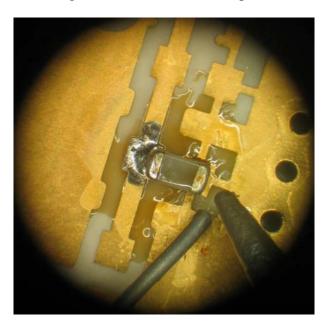

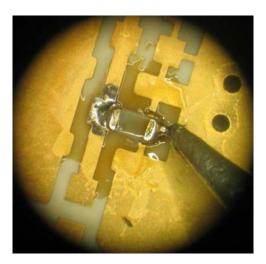

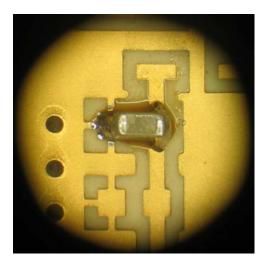

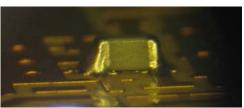

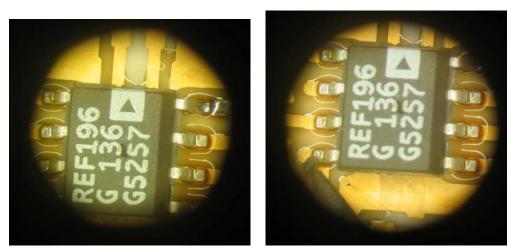

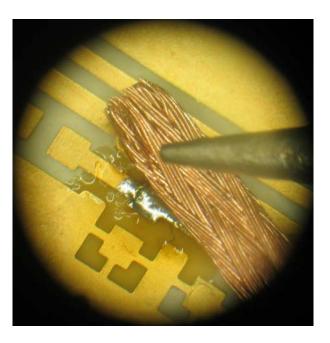

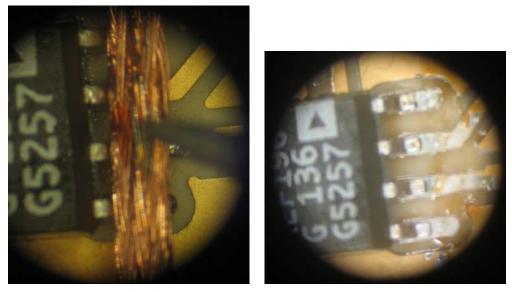

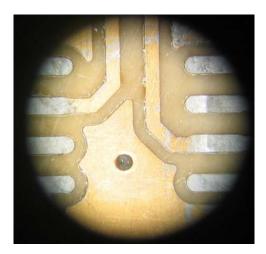

|   |      | C.3.1    | Soldering Surface Mounted Devices (SMD)                               | 363 |

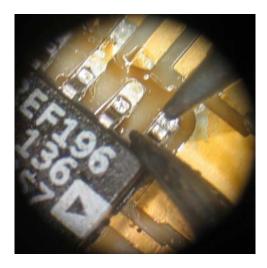

|   |      | C.3.2    | Desoldering                                                           | 370 |

|   |      | C.3.3    | Key points to bear in mind                                            | 372 |

|   | C.4  | System   | Building Blocks                                                       | 374 |

|   | C.5  | Low N    | oise Amplifier (LNA)                                                  | 376 |

|   |      | C.5.1    | Schematic and PCB Layout                                              | 376 |

|   |      | C.5.2    | Soldering Guidelines                                                  | 376 |

|   | C.6  | Variabl  | le Gain Amplifier (VGA)                                               | 379 |

|   |      | C.6.1    | Schematic and PCB Layout                                              | 379 |

|   |      | C.6.2    | Soldering Guidelines                                                  | 380 |

|   | C.7  | Oscilla  | tor                                                                   | 382 |

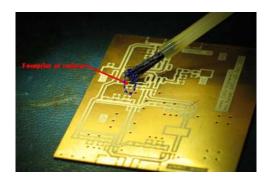

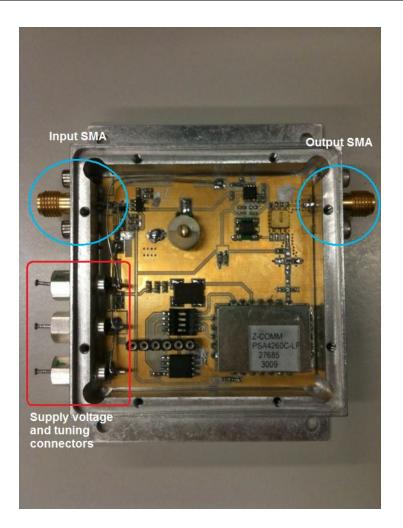

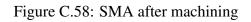

|   | C.8  | Oscilla  | tor construction                                                      | 385 |

|   | C.9  | Transm   | nitter                                                                | 391 |

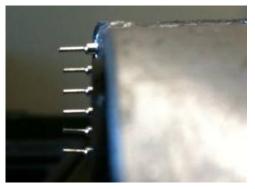

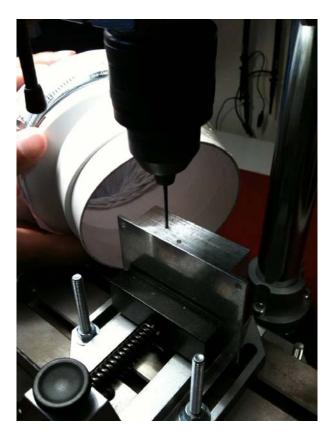

|   | C.10 | Custon   | nizing the shielding boxes                                            | 394 |

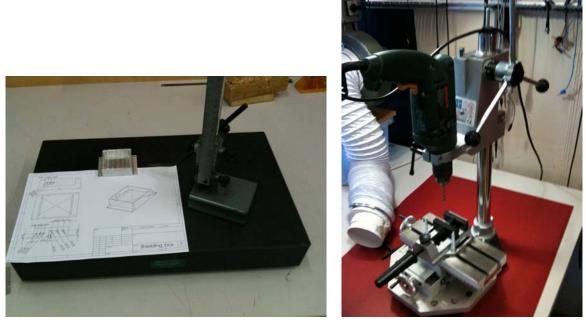

|   |      | C.10.1   | Equipment Required                                                    | 395 |

|   |      | C.10.2   | Marking the boxes                                                     | 395 |

|   |      | C.10.3   | Drilling the holes                                                    | 397 |

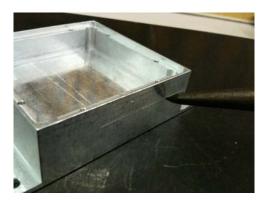

|   |      | C.10.4   | Threading the screw holes                                             | 398 |

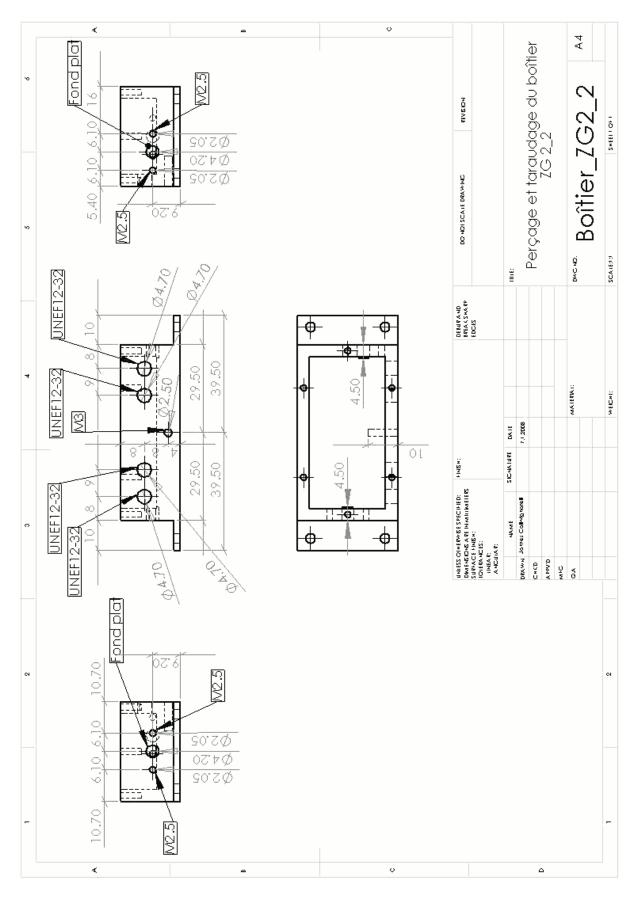

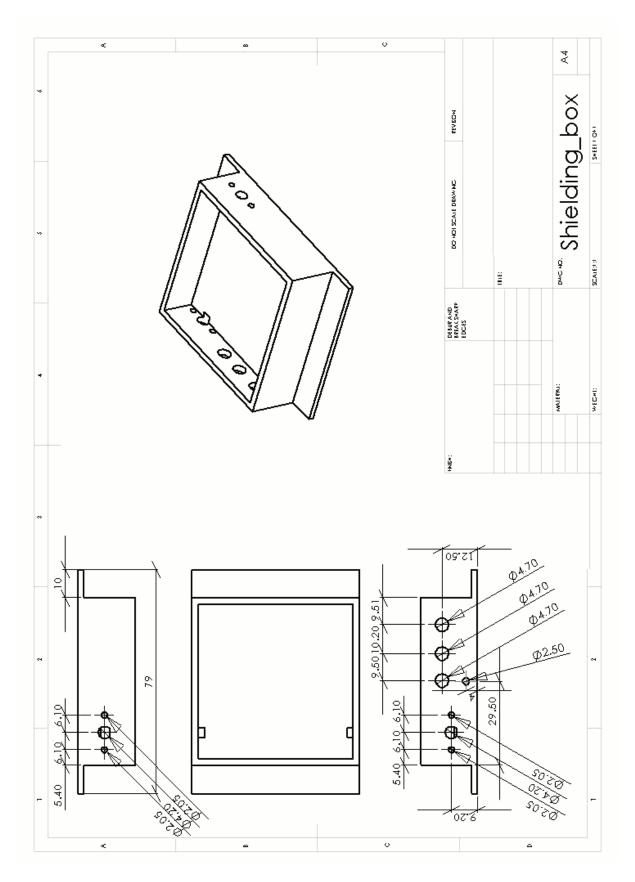

|   |      | C.10.5   | LNA shielding box                                                     | 398 |

|   |      | C.10.6   | Transmitter shielding                                                 | 400 |

|   | C.11 | Finaliz  | ing the circuits                                                      | 402 |

| D | TATA | 0.1      |                                                                       | 405 |

| D |      |          | addendum                                                              | 407 |

|   | D.1  |          | uction of LNA prototype $n^{\circ} 1$                                 |     |

|   |      | D.1.1    | The printed circuit board design                                      |     |

|   |      | D.1.2    | The printed circuit board construction                                |     |

|   | D.2  | Improv   | vements of the LNA prototype n° 1 construction                        | 415 |

| E | Resi | stive Ne | tworks                                                                | 423 |

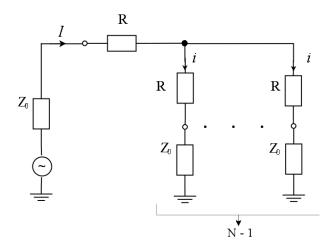

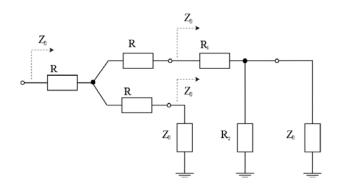

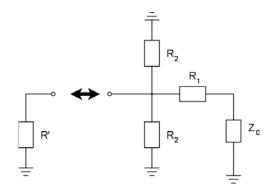

|   | E.1  | Power    | splitter/combiner                                                     | 423 |

|   |      | E.1.1    | Calculation of $R$                                                    |     |

|   |      |          |                                                                       |     |

|   |      | E.1.2         | Calculation of the attenuation                                                        | . 425 |

|---|------|---------------|---------------------------------------------------------------------------------------|-------|

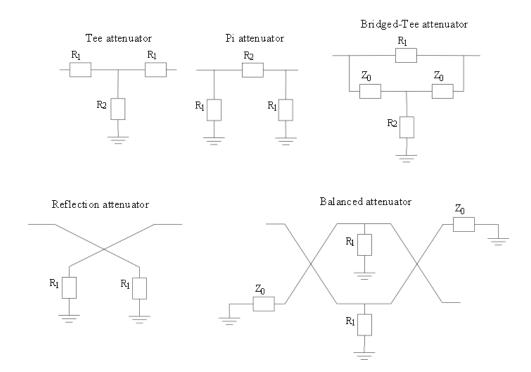

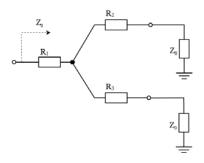

|   | E.2  | Power         | splitter as an attenuator                                                             | . 426 |

|   |      | E.2.1         | Case $n^o 1$ : Power splitter with at input port a Tee-type attenuator $\ldots$       | . 427 |

|   |      | E.2.2         | Case $n^{\circ} 2$ : Power splitter with at input port a Tee-type attenuator $\ldots$ | . 428 |

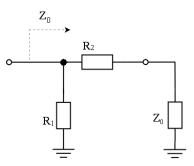

|   |      | E.2.3         | Case $n^{o} 3$ : Power splitter/combiner with T-type attenuator at one out-           |       |

|   |      |               | put port                                                                              | . 429 |

|   |      | E.2.4         | Case nº 4 : Power splitter/combiner with attenuator-pad at one output                 |       |

|   |      |               | port                                                                                  | . 430 |

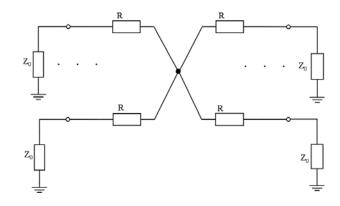

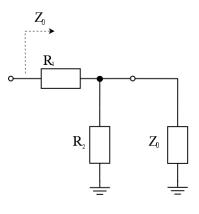

|   | E.3  | Cross A       | Attenuator                                                                            | . 431 |

|   |      | E.3.1         | Calculation of $R_2$ with $R_1$ known in order to match $Z_0$                         | . 432 |

|   |      | E.3.2         | Calculation of the attenuation                                                        | . 433 |

|   |      | E.3.3         | Design methodology                                                                    | . 435 |

|   |      | E.3.4         | Conclusion                                                                            | . 437 |

| F | C    |               |                                                                                       | 420   |

| F |      | -             | s market exploration                                                                  | 439   |

|   | F.1  |               | cillator components                                                                   |       |

|   |      | F.1.1         | PLL synthesizer                                                                       |       |

|   |      | F.1.2         | VCO                                                                                   |       |

|   |      | F.1.3         | PLL synthesizer-VCO                                                                   |       |

|   | F.2  |               | Q demodulator components                                                              |       |

|   |      | F.2.1         | I/Q Mixer                                                                             |       |

|   |      | F.2.2         | Conventional mixer                                                                    |       |

|   |      | F.2.3         | Amplifier                                                                             | . 457 |

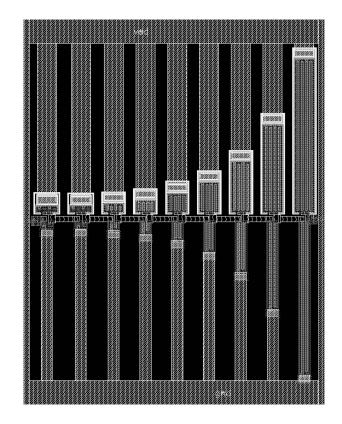

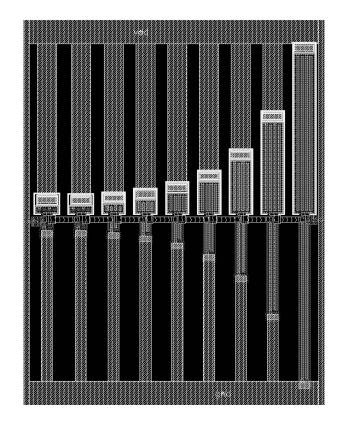

| G | Buff | ers and       | Switches schematics and layouts for Prototype n <sup>o</sup> 1                        | 467   |

|   | G.1  |               | iffers                                                                                | . 468 |

|   |      | G.1.1         | Buffer 2                                                                              | . 468 |

|   |      | G.1.2         | Buffer 3                                                                              |       |

|   |      | G.1.3         | Buffer 5                                                                              |       |

|   |      | G.1.4         | Buffer 8                                                                              |       |

|   |      | G.1.5         | Buffer 12                                                                             |       |

|   |      | G.1.6         | Buffer 17                                                                             |       |

|   |      | G.1.7         | Buffer 24                                                                             |       |

|   |      |               | Buffer 33                                                                             |       |

|   |      | <b>U</b> .1.0 |                                                                                       |       |

|    |            | G.1.9 Buffer 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 476        |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    |            | G.1.10 Buffer 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 477        |

|    |            | G.1.11 Buffer 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 478        |

|    |            | G.1.12 Buffer 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 479        |

|    |            | G.1.13 Buffer 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 480        |

|    |            | G.1.14 Buffer 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 481        |

|    |            | G.1.15 Buffer 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 482        |

|    |            | G.1.16 Buffer 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 483        |

|    | G.2        | The switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 484        |