### On the Cryptanalysis of Public-Key Cryptography

### THÈSE N° 5291 (2012)

PRÉSENTÉE LE 24 FÉVRIER 2012

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE DE CRYPTOLOGIE ALGORITHMIQUE

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Joppe Willem BOS

acceptée sur proposition du jury:

Prof. B. Falsafi, président du jury Prof. A. Lenstra, directeur de thèse Dr P. C. Leyland, rapporteur P. L. Montgomery, rapporteur Prof. S. Vaudenay, rapporteur

| Dit proefschrift is opgedragen aan mijn ouders<br>Jaap & Bettien |  |

|------------------------------------------------------------------|--|

|                                                                  |  |

|                                                                  |  |

|                                                                  |  |

|                                                                  |  |

## Acknowledgements

First and foremost I would like to thank my supervisor Arjen K. Lenstra for his guidance and advice during my PhD. I don't think there are many supervisors who give such detailed and constructive feedback to their PhD students. After the invitation to come and visit his laboratory for cryptologic algorithms (LACAL) at EPFL I quit my job in the Netherlands and came to Switzerland to start my PhD. My first year at EPFL I spent at the mathematics institute of geometry and applications at the chair of algebraic and geometric structures led by Eva Bayer-Fluckiger. I would like to thank all members of this laboratory for their help during my first year at EPFL.

I would like to thank all the post-doctoral researchers from LACAL who helped me during these years: Nicolas Gama, Dimitar P. Jetchev, Marcelo E. Kaihara, Thorsten Kleinjung, and Martijn Stam. Especially Thorsten, who was always patient and able to answer all my questions and acted as my second supervisor. Furthermore, I would also like to thank all the other PhD-students at LACAL: Maxime Augier, Alina Dudeanu, Andrea Miele, Seyyd Hasan Mirjalili, Alexandre Karlov, Shahram Khazaei, Dag Arne Osvik, Onur Özen, and Juraj Šarinay. Besides all the interesting discussions we also had a lot of fun during and after work and I discovered many great movies during the LACAL lunch-entertainment sessions. A special thanks goes out to the secretary of our lab: Monique Amhof. She was always available to help and assist if I had trouble with the local language or sort out any administrative troubles. Besides my colleagues I would like to thank Eline, which I married during my PhD, for all her support and love during this period. Especially when I was working from home and she noted that I was still looking at the "boring screen" (Linux terminal).

Part of this work was supported by the Swiss National Science Foundation under grant numbers 200021-119776, 206021-117409 and 206021-128727 and by the European Commission through the ICT programme under contract ICT-2007-216676 ECRYPT II.

## Abstract

Nowadays, the most popular public-key cryptosystems are based on either the integer factorization or the discrete logarithm problem. The feasibility of solving these mathematical problems in practice are studied and techniques are presented to speed-up the underlying arithmetic on parallel architectures.

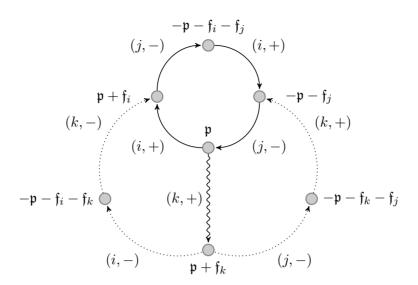

The fastest known approach to solve the discrete logarithm problem in groups of elliptic curves over finite fields is the Pollard rho method. The negation map can be used to speed up this calculation by a factor  $\sqrt{2}$ . It is well known that the random walks used by Pollard rho when combined with the negation map get trapped in fruitless cycles. We show that previously published approaches to deal with this problem are plagued by recurring cycles, and we propose effective alternative countermeasures. Furthermore, fast modular arithmetic is introduced which can take advantage of prime moduli of a special form using efficient "sloppy reduction." The effectiveness of these techniques is demonstrated by solving a 112-bit elliptic curve discrete logarithm problem using a cluster of PlayStation 3 game consoles: breaking a public-key standard and setting a new world record.

The elliptic curve method (ECM) for integer factorization is the asymptotically fastest method to find relatively small factors of large integers. From a cryptanalytic point of view the performance of ECM gives information about secure parameter choices of some cryptographic protocols. We optimize ECM by proposing carry-free arithmetic modulo Mersenne numbers (numbers of the form  $2^M-1$ ) especially suitable for parallel architectures. Our implementation of these techniques on a cluster of PlayStation 3 game consoles set a new record by finding a 241-bit prime factor of  $2^{1181}-1$ .

A normal form for elliptic curves introduced by Edwards results in the fastest elliptic curve arithmetic in practice. Techniques to reduce the temporary storage and enhance the performance even further in the setting of ECM are presented. Our results enable one to run ECM efficiently on resource-constrained platforms such as graphics processing units.

**Keywords**: cryptanalysis, public-key cryptography, integer factorization, elliptic curve discrete logarithm problem, arithmetic

### Résumé

De nos jours, les cryptosystèmes à clef publique les plus populaires sont basés soit sur le problème de la factorisation des entiers, soit sur celui du logarithme discret. La faisabilité de la résolution pratique de ces problèmes mathématiques est étudiée, et des techniques pour l'accélération de l'arithmétique sous-jacente sur des architectures parallèles sont présentées.

La plus rapide approche connue pour la résolution du problème du logarithme discret sur les groupes des courbes elliptiques sur corps finis est la méthode du Rho de Pollard. L'application de négation permet d'accélérer le calcul par un facteur  $\sqrt{2}$ . Il est communément reconnu que les marches aléatoires utilisées par le Rho de Pollard, en combinaison avec l'application de négation, s'égarent dans des cycles infructueux. Nous montrons que les approches précédentes pour éviter cette difficulté sont pénalisées par des cycles récurrents, et nous proposons des contre-mesures efficaces. De plus, nous introduisons une arithmétique modulaire rapide, qui tire avantage de modules premiers de forme spéciale, en utilisant l'efficace "réduction hâtive". Nous montrons l'efficacité de ces techniques en résolvant un problème de logarithme discret sur une courbe elliptique de 112 bits, sur un cluster de consoles de jeu PlayStation 3, cassant ainsi un standard de chiffrement à clef publique, et réalisant un nouveau record mondial.

La méthode des courbes elliptiques (ECM) pour la factorisation des entiers est la méthode la plus rapide asymptotiquement pour identifier de relativement petits facteurs de grands entiers. D'un point de vue cryptanalytique, la performance d'ECM fournit des informations sur la sûreté du choix des paramètres de certains protocoles cryptographiques. Nous optimisons ECM en proposant une arithmétique modulo un nombre de Mersenne quelconque (nombres de la forme  $2^M-1$ ) sans retenues, particulièrement adaptée aux architectures parallèles. Notre implémentation de ces techniques sur un cluster de consoles de jeu PlayStation 3 réalise un nouveau record en identifiant un facteur premier de 241 bits de  $2^{1181}-1$ .

Une forme normale pour les courbes elliptiques, introduite par Edwards, donne en pratique l'arithmétique la plus rapide pour les courbes elliptiques. Nous présentons des techniques pour réduire le stockage temporaire et améliorer encore plus la performance dans le contexte d'ECM. Nos résultats permettent d'utiliser ECM efficacement sur des plateformes aux ressources limitées comme les GPU (processeurs graphiques).

Mots-clefs: cryptanalyse, cryptographie à clef publique, factorisation des entiers, problème de logarithme discret sur une courbe elliptique, arithmétique

## Zusammenfassung

Die gebräuchlichsten Public-key Kryptosysteme beruhen heutzutage entweder auf dem Faktorisierungsproblem oder dem diskreten Logarithmus-Problem. In dieser Arbeit wird zum einen untersucht, inwieweit es möglich ist, diese mathematischen Probleme zu lösen, und zum anderen werden Techniken zur Beschleunigung der zugrundeliegenden Arithmetik auf parallelen Architekturen vorgestellt.

Pollard's rho Verfahren ist der schnellste bekannte Ansatz, das diskrete Logarithmus-Problem in der Gruppe der Punkte einer elliptischen Kurve über einem endlichen Körper zu lösen. Dieses Verfahren kann mittels der Negationsabbildung um einen Faktor  $\sqrt{2}$  beschleunigt werden. Bekanntlich können dabei die Zufallswege aus Pollard's rho Methode in fruchtlosen Zyklen enden. Wir zeigen, dass die bisherigen Ansätze, dieses Problem zu lösen, mit dem Problem der wiederkehrenden Zyklen zu kämpfen haben, und schlagen effektive Alternativen vor. Ausserdem stellen wir für Primmoduli einer speziellen Form eine schnelle modulare Arithmetik vor, die effiziente "saloppe Reduktion" benutzt. Mit der Lösung eines 112-Bit elliptischen diskreten Logarithmus-Problems auf einem Verbund von PlayStation 3 Spielkonsolen, was einen Public-key Standard bricht und einen neuen Weltrekord aufstellt, wird die Effektivität dieser Techniken unter Beweis gestellt.

Die asymptotisch schnellste Methode, relativ kleine Faktoren grosser Zahlen zu finden, ist die elliptische Kurven Methode (ECM). Für die Kryptographie ist sie wichtig, um Informationen über sichere Parameter für einige kryptographische Protokolle zu erhalten. Wir haben ECM mit einer übertragsfreien Arithmetik optimiert, die für Arithmetik modulo Mersennezahlen (Zahlen der Form  $2^M-1$ ) auf parallelen Architekturen besonders geeignet ist. Mit unserer Implementierung dieser Techniken haben wir auf einem Verbund von PlayStation 3 Spielkonsolen mit einem 241-Bit Primfaktor von  $2^{1181}-1$  einen neuen Rekord aufgestellt.

Eine von Edwards eingeführte Normalform für elliptischen Kurven führt zur schnellsten Arithmetik auf elliptische Kurven in der Praxis. Im Falle der Anwendung auf ECM stellen wir Techniken vor, die den temporären Speicherbedarf reduzieren und die Laufzeit noch weiter verbessern. Dies erlaubt uns, ECM auf ressourcenbeschränkten Plattformen wie Graphikprozessoren laufen zu lassen.

**Schlagwörter**: Kryptanalyse, Public-key Kryptographie, Primfaktorzerlegung, diskretes Logarithmus-Problem für elliptische Kurven, Arithmetik

### Riassunto

Al giorno d'oggi, i sistemi crittografici a chiave pubblica più popolari, sono basati sul problema della fattorizzazione di numeri interi o su quello del logaritmo discreto. Verrà presentato lo studio relativo alla risoluzione di tali problemi matematici nella pratica e saranno presentate tecniche per accelerare l'aritmetica utilizzata su architetture parallele.

L'approccio più veloce per risolvere il problema del logaritmo discreto in un un gruppo di punti su una curva ellittica è il metodo rho di Pollard. L'utilizzo della "mappa di negazione" può essere adottato per velocizzare l'elaborazione di un fattore  $\sqrt{2}$ . E' ben noto che le passeggiate aleatorie usate da Pollard, combinate con la mappa di negazione, possono entrare in cicli infruttuosi. Mostreremo che, gli approcci pubblicati precedentemente in letteratura per affrontare questo problema, sono affetti da cicli ricorrenti e proporremo contromisure alternative efficaci. Inoltre, verrà introdotta un'aritmetica modulare veloce, per moduli dalla forma speciale, basata su una tecnica di riduzione efficiente denominata "riduzione pigra". L'efficacia di tali tecniche è stata dimostrata risolvendo un'instanza del problema del logaritmo discreto su una curva ellittica a 112-bit usando un cluster di console PlayStation 3: uno standard crittografico a chiave pubblica è stato attaccato con successo ed un nuovo record mondiale è stato stabilito.

Il metodo delle curve ellittiche (ECM) per la fattorizzazione di interi è asintoticamente il metodo più veloce per trovare fattori piccoli (relativamente) di interi molto grandi. Dal punto di vista della crittanalisi le prestazioni di ECM influiscono sulla scelta dei parametri di sicurezza di alcuni protocolli crittografici. Noi abbiamo ottimizzato ECM, proponendo un'aritmetica senza resti particolarmente adatta ad architetture parallele e moduli definiti da numeri di Mersenne: numeri della forma  $2^M-1$ . La nostra implementazione di queste tecniche, su un cluster di console PlayStation 3, ha stabilito un nuovo record: è stato trovato un fattore di 241-bit del numero  $2^{1181}-1$ .

Una forma normale per le curve ellittiche introdotta da Edwards consente di lavorare, nella pratica, con l'aritmetica delle curve ellittiche più veloce in assoluto. Verrano presentate tecniche pratiche per ridurre l'occupazione di memoria e per migliorare le prestazioni di tale aritmetica. I nostri risultati consentono di eseguire ECM in maniera efficiente su piattaforme dalle risorse limitate come i processori grafici.

Termini di indicizzazione: crittanalisi, crittografia a chiave pubblica, fattorizzazione di numeri interi, problema del logaritmo discreto su una curva ellittica, aritmetica

## Samenvatting

Tegenwoordig zijn de populairste asymmetrische cryptosystemen gebaseerd op het probleem van de ontbinding van een geheel samengesteld getal in priemfactoren of op het discrete logaritme probleem. De praktische mogelijkheden om deze wiskundige problemen op te lossen worden bestudeerd en technieken worden gepresenteerd om de berekeningen te versnellen op parallelle computerarchitecturen.

De snelste manier om het discrete logaritme probleem in groepen van elliptische krommen over een eindig lichaam op te lossen is het Pollard rho algoritme. Spiegelbeelden kunnen worden gebruikt om de berekening met een factor  $\sqrt{2}$  te versnellen, tenzij de toevalsbewegingen erdoor in nutteloze cycli terecht komen. We tonen aan dat eerder gepubliceerde methoden om dit probleem op te lossen door terugkerende cycli niet werken en we laten zien hoe ook dit probleem kan worden opgelost. Verder introduceren we "slordige reductie" om modulair rekenen met getallen van een speciale vorm te versnellen. We laten zien dat dit in de praktijk werkt door een 112-bit elliptische kromme asymmetrische standaard te kraken. De berekening werd gedaan op een cluster bestaande uit PlayStation 3 spelcomputers en zette een nieuw wereldrecord.

De elliptische kromme methode (ECM) is de asymptotisch snelste methode om kleine priemfactoren te vinden. De grootte van de factoren die ermee gevonden kunnen worden geeft aan hoe de parameters van sommige cryptosystemen gekozen moeten worden. Voor toepassing van ECM op Mersenne getallen (getallen van de vorm  $2^M-1$ ) hebben we een snelle overdrachtsvrije rekenmethode ontwikkeld die zeer geschikt is voor parallelle computerarchitecturen. Op het spelcomputercluster hebben we er een nieuw ECM record mee gevestigd door een 241-bit priemfactor te vinden van  $2^{1181}-1$ .

Een paar jaar geleden heeft Edwards de tot nu toe snelste manier bedacht om met elliptische krommen te rekenen. We laten zien hoe de voor toepassing op ECM vereiste hoeveelheid geheugen drastisch kan worden verminderd. Dit maakt het mogelijk ECM te versnellen op architecturen met beperkt geheugen zoals grafische kernen (GPUs).

**Sleutelwoorden**: cryptanalyse, asymmetrische cryptografie, ontbinden in factoren, rekenkunde, discrete logaritme probleem voor elliptische krommen

# Contents

| A            | Acknowledgements |                                                    |    |  |  |  |

|--------------|------------------|----------------------------------------------------|----|--|--|--|

| $\mathbf{A}$ | bstra            | act (English/Français/Deutsch/Italiano/Nederlands) | v  |  |  |  |

| 1            | Intr             | Introduction                                       |    |  |  |  |

|              | 1.1              | Publications and Thesis Outline                    | 3  |  |  |  |

| <b>2</b>     | $\mathbf{Pre}$   | liminaries                                         | 7  |  |  |  |

|              | 2.1              | Radix Representation and Bit Lengths               | 7  |  |  |  |

|              | 2.2              | Parallel Architectures                             | 7  |  |  |  |

|              |                  | 2.2.1 The Cell Broadband Engine                    | 8  |  |  |  |

|              |                  | 2.2.2 Integer and Bit Arithmetic on the SPU        | 9  |  |  |  |

|              |                  | 2.2.3 Compute Unified Device Architecture          | 10 |  |  |  |

|              | 2.3              | Multiplication                                     | 12 |  |  |  |

|              |                  | 2.3.1 Montgomery Modular Multiplication            | 13 |  |  |  |

|              | 2.4              | Elliptic Curves                                    | 14 |  |  |  |

|              |                  | 2.4.1 The Elliptic Curve Method                    | 16 |  |  |  |

|              |                  | 2.4.2 Elliptic Curve Scalar Multiplication         | 18 |  |  |  |

|              | 2.5              | The Pollard Rho Method                             | 20 |  |  |  |

| 3            | Hig              | h-Performance Arithmetic on Parallel Architectures | 23 |  |  |  |

|              | 3.1              | Fast Reduction using Special Primes                | 24 |  |  |  |

|              |                  | 3.1.1 NIST Primes                                  | 24 |  |  |  |

|              |                  | 3.1.2 Curve25519                                   | 25 |  |  |  |

|              | 3.2              | Applications                                       | 26 |  |  |  |

|              |                  | 3.2.1 Cryptography                                 | 26 |  |  |  |

|              |                  | 3.2.2 Cryptanalysis                                | 27 |  |  |  |

|              | 3.3              | Representation of Long Integers                    | 27 |  |  |  |

|              |                  | 3.3.1 Representation of Long Integers on the SPU   | 27 |  |  |  |

|              |                  | 3.3.2 Representation of Long Integers on the GPU   | 29 |  |  |  |

|          | 3.4               | Finite Field Arithmetic                          |

|----------|-------------------|--------------------------------------------------|

|          |                   | 3.4.1 Modular Addition and Subtraction           |

|          |                   | 3.4.2 Modular Multiplication                     |

|          |                   | 3.4.3 Fast Reduction                             |

|          |                   | 3.4.4 Montgomery Multiplication on the SPU       |

|          | 3.5               | Elliptic Curve Arithmetic on the GPU             |

|          | 3.6               | Performance Results and Discussion               |

|          |                   | 3.6.1 Results on the Cell                        |

|          |                   | 3.6.2 Results on Various GPUs                    |

|          | 3.7               | Conclusions                                      |

| 4        | Doll              | ard Rho – Using the Negation Map 45              |

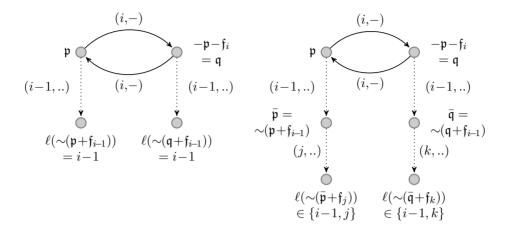

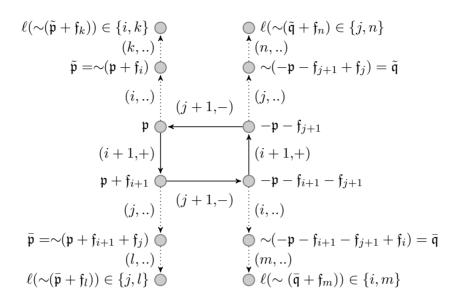

| 4        | 4.1               | r-Adding and $r + s$ -Mixed Walks                |

|          | 4.2               | Parallelized Random Walks                        |

|          | 4.3               | Unique Point Representation                      |

|          | 4.4               | Simultaneous Inversion                           |

|          | $\frac{4.4}{4.5}$ | Using Automorphisms                              |

|          | 4.6               | •                                                |

|          | $\frac{4.0}{4.7}$ | 9 9                                              |

|          | 4.7               |                                                  |

|          | 4.8               | 1 0                                              |

|          |                   | 4.8.1 Short Fruitless Cycle Reduction            |

|          |                   | v I                                              |

|          | 4.0               |                                                  |

|          | 4.9               | Comparison                                       |

|          |                   | Conclusion                                       |

|          | 4.11              | Follow-Up Work                                   |

| <b>5</b> | Solv              | ring ECDLPs on the Cell 65                       |

|          | 5.1               | A 112-bit Prime Field ECDLP                      |

|          | 5.2               | Pollard's Rho Method on the PS3                  |

|          |                   | 5.2.1 4-way SIMD Long Integer SPU-Arithmetic 67  |

|          |                   | 5.2.2 SIMD Modular Inversion on the SPU 72       |

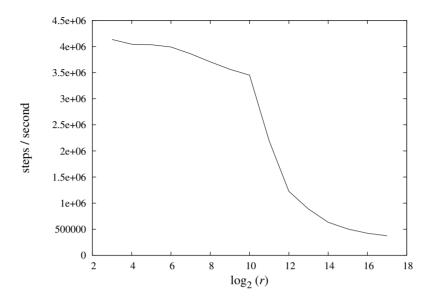

|          | 5.3               | Timings and Solution of the Prime Field ECDLP    |

| 5.       | 5.4               | An Approach to Solve ECC2K-130                   |

|          |                   | 5.4.1 ECC2K-130 and Choice of Iteration Function |

|          |                   | 5.4.2 Computing the Iteration Function           |

|          |                   | 5.4.3 Polynomial or Normal Basis?                |

|          | 5.5               | The Non-Bitsliced Implementation                 |

|          |                   | 5.5.1 Multiplication                             |

|          |                   | 5.5.2 Squaring                                   |

|          |                   | 5.5.3 Basis Conversion and $m$ -Squaring 81      |

|          |                   | 5.5.4 Modular Inversion                          |

|          |                   | 5.5.5 Results 82                                 |

| 6                      | Effi  | cient S | SIMD arithmetic modulo a Mersenne number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 85  |

|------------------------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                        | 6.1   | Arithr  | metic Modulo $2^M - 1$ on the SPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86  |

|                        |       | 6.1.1   | Related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|                        |       | 6.1.2   | Representation of 4-tuples of Integers Modulo $N 	cdots 	$ | 87  |

|                        |       | 6.1.3   | Addition and Subtraction Modulo $N$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|                        |       | 6.1.4   | Multiplication Modulo $N$ using Radix Conversions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88  |

|                        |       | 6.1.5   | Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                        |       | 6.1.6   | Further Speedups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92  |

|                        |       | 6.1.7   | Multiplication Modulo $N$ using Signed Radix- $2^{13}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94  |

|                        |       | 6.1.8   | Comparison with other SPE Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95  |

|                        | 6.2   | Applie  | cation to ECM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95  |

|                        |       | 6.2.1   | ECM on the Cell Applied to $2^M - 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97  |

|                        |       | 6.2.2   | Comparison Between Cell and Regular Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

|                        | 6.3   | Concl   | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 |

| 7                      | EC    | M at V  | Vork                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101 |

|                        | 7.1   | ECM     | in Practice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102 |

|                        | 7.2   | Ellipti | ic Curve Constant Scalar Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 103 |

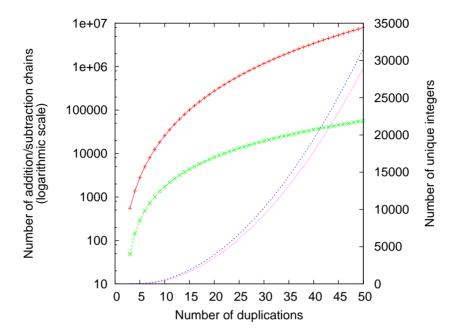

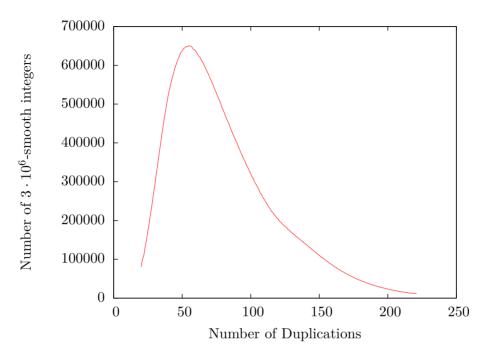

|                        |       | 7.2.1   | Addition/Subtraction Chains With Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104 |

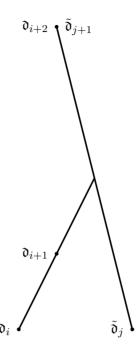

|                        |       | 7.2.2   | Generating Addition/Subtraction Chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106 |

|                        |       | 7.2.3   | Combining Addition/Subtraction Chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109 |

|                        |       | 7.2.4   | Additional Multiplications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 112 |

|                        | 7.3   | Result  | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 113 |

|                        | 7.4   |         | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| $\mathbf{C}^{\dagger}$ | urric | ulum '  | Vitae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 117 |

### Introduction

Obtaining the original meaning of encrypted data without using the corresponding secret material is part of the research area known as *cryptanalysis*. Cryptanalysis, often referred to as the practice of code breaking, together with cryptography, the science of hiding information, are the two branches of the larger research area known as cryptology. Within cryptology one can (roughly) distinguish three different research fields, each fulfilling a different practical need: cryptographic hash functions, symmetric-key and asymmetric-key cryptography. The latter is also known as *public-key* cryptography, here the methods used to hide the information use different keys, a public and a private, for hiding and revealing the message respectively. This thesis is concerned with both the theoretical and practical aspects of *public-key crypt-analysis*.

In the late 1970s, Rivest, Shamir and Adleman proposed an approach to realize public-key cryptography in practice which is known as the RSA algorithm [174]. The core idea described in their paper is still valid today and resisted many years of cryptanalysis [28]. The RSA algorithm is, without doubt, currently the most widely used public-key cryptosystem and has been standardized in the public-key cryptography standard [112]. The mathematical foundation of the RSA scheme is the *integer factorization problem*, this problem can be defined as follows [201, (Integer Factoring, p. 290)].

**Definition 1.1** (The Integer Factorization Problem). Integer factoring is the following problem: given a positive integer n, find positive integers v and w, both greater than 1, such that  $n = v \cdot w$ .

Another approach to realize public-key cryptography is based on the algebraic structure of elliptic curves over finite fields. Elliptic curve cryptography (ECC) [124,143] enjoys increasing popularity since its invention in the mid 1980s. The attractiveness of small key-sizes [131,135] has placed this public-key cryptosystem as the preferred alternative to RSA. This is emphasized by the current migration away from 80-bit to 112-bit security where, for instance, the United States' National Security Agency restricts the use of public key cryptography in "Suite B" [151] to ECC. Popular ECC based schemes are based on the ElGamal cryptosystem [75]

2 INTRODUCTION

and the digital signature algorithm [199]. The mathematical problem used as the theoretical foundation in these systems is known as the *discrete logarithm problem* and can be defined as follows [201, (Discrete Logarithm Problem, p. 164)].

**Definition 1.2** (The Discrete Logarithm Problem). Let g be a generator for a cyclic group G. Given an element  $y \in G$ , the discrete logarithm problem is to find an integer x such that  $g^x = y$ .

Note that not all public-key schemes are based on these two problems; examples of other mathematical problems used are the hardness of decoding a general linear code (used in the McEliece cryptosystem [141]) and lattice based problems (used in the Goldreich-Goldwasser-Halevi encryption [90] and NTRU [106]) but the use of such schemes in practice is limited.

Although the integer factorization and discrete logarithm problems are not proven to be hard, many people believe that this is the case; e.g. there exists no polynomial time integer factorization method (or (sub)exponential but feasible in practice) on a classical computer (polynomial in the number of bits of the number to be factored). On a quantum computer, however, one *can* factor (and compute discrete logarithms) in polynomial time due to Shor's algorithm [183]. This thesis is only concerned with methods and algorithms running on classical (non-quantum) computers. To make the situation even worse, it is not even known if breaking RSA is equivalent to factoring; there are results pointing in different directions [1,29].

This thesis studies how efficiently one can solve the mathematical problems stated in Definition 1.1 and Definition 1.2. Obtaining the secret information by other means than solving these problems is not considered. Examples of such other methods can be found in the research area related to *side channel attacks* [126, 127]: attacks which use information gained from the physical implementation of a certain scheme to break its security; e.g. the elapsed time or power consumption.

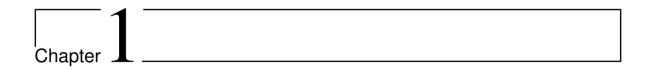

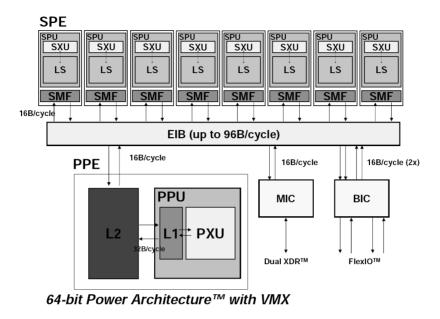

A common approach to study to what extent these mathematical problems can be solved in practice is combining the state-of-the-art algorithms and resources. It might be necessary to adopt the algorithms to a specific architecture or to build a machine specifically designed for such tasks. As an example, the world's first programmable, digital, electronic, computing device known as the Colossus [79] was designed for cryptanalytic purposes<sup>1</sup>. A current shift in architecture design is to move towards many-core processors [159]. From a practical point of view this thesis aims to present and optimize algorithms which are specifically suitable to run on such parallel architectures (just as in the early 1990s, e.g. [70,71]). The prime candidates considered are the heterogeneous, multi-core, single-instruction, multiple data Cell broadband engine (Cell) architecture and the single-instruction, multiple thread graphics processing unit (GPU) architecture families. We think that the techniques described in this thesis, and the implementation of these algorithms on parallel architectures, can be used to better understand what practical parameters should be used to provide a sufficient level of confidence in the security used in modern public-key cryptosystems. These fast (parallel)

$<sup>^{1}</sup>$ The Colossus machine was used to break the codes produced by the Lorenz SZ40/42 cipher machine in the second world war.

arithmetic routines also find their application in cryptography by enhancing the performance of asymmetric cryptographic primitives.

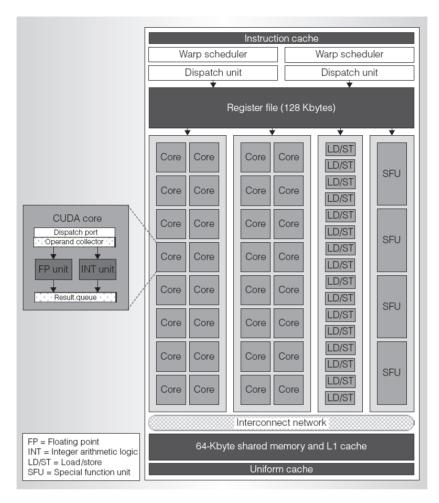

From a theoretical point of view, we adopt and optimize arithmetic procedures to these architectures to lower the required run-time. We also study some problems when using the negation map optimization, an approach which results in a constant factor speedup when solving the elliptic curve discrete logarithm problem, and give solutions to circumvent them. In the factorization setting we study methods to reduce the runtime and space (memory) requirement when using Edwards curves to accelerate the elliptic curve factorization method.

### 1.1 Publications and Thesis Outline