# CONTRIBUTION TO THE ACTIVE GENERATOR PRINCIPLE: The Gate-Commutated Polyphased Matrix Converter

## THÈSE N° 5258 (2012)

PRÉSENTÉE LE 13 JANVIER 2012

À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE D'ÉLECTRONIQUE INDUSTRIELLE

PROGRAMME DOCTORAL EN ENERGIE

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

## Antoine BÉGUIN

acceptée sur proposition du jury:

Prof. M. Paolone, président du jury Prof. A. Rufer, directeur de thèse Prof. J. C. Clare, rapporteur Dr B. Kawkabani, rapporteur Dr K.-D. Walli, rapporteur

## **Acknowledgments**

A thesis cannot be accomplished without the precious help of other people. Many contributed to my work, on various levels and in various ways.

First, I want to express my gratitude to the industrial partner, who has funded my four years of research. It has been a pleasure to work with this partner and I hope to have positively contributed to its R&D program.

During a research project there are moments of doubts about the current development, but fortunately there is always the thesis director that leads s the candidate towards the right track. Hence I specially thank my thesis director, Prof. A. Rufer. It has been a pleasure for me that you provided me with the opportunity to work in your very motivating laboratory.

My colleagues contributed to excellent working conditions for four years. Here I would like to thank all my colleagues for the stimulating discussions during coffee breaks and their willingness to always helps me. Thank you to Dr. Philippe Barrade, who provided me with my first pink Bible to guide my research. Thank you to Roberto Zoia for all his help with the informatics tools. A special "Thank you" to both of my office mates, Irma Villar and Stefan Kenzelmann, who made me think differently about my projects, entertained me and took care of the plants of the office. I also have to address special thanks to Christian Rod, Simon Delalay, Mahbod Heidari and Gael Katuku, who helped me cabling and soldering my experimental set-up. Special thanks also to Dr. Sébastien Wasterlain, who quit his post doc status for a few hours to help me mounting connectors and who also found a cinematographic utility to my experimental set-up. Thank you also to Yves Birbaum, who contributed with his legendary efficiency to debug my experimental set-up, sparing me some weeks of head scratching. A general thank to all other colleagues, whose names don't appear here, but yet contributed with their presence to my thesis.

Thanks to the staff of the *ACI* workshop of the EPFL, who manufactured the Printed Circuit Boards and gave me smart advices for the soldering. In particular, I thank M. André Badertscher.

Thank you to all my friends, who have provided comfortable lifeboats during storms and deckchairs for the sunny weather.

Last but not least, I wish to thank my family from the bottom of my heart. You strongly supported me during those four years, so I finally reached the goal of the race.

### **Abstract**

This work is part of the innovative « Active Generator » (AG) project. AG is a concept that suggests a new arrangement of the turbine-generator line of a high power utility (a few hundred of MW) in order to de-synchronize the rotation speed of the turbine-generator group from the fixed grid frequency (50Hz or 60Hz). This de-synchronization has essentially two advantages. First, the variable speed of the group enables the operation of the turbine at its best available efficiency in function of the delivered power. Second, the de-synchronization allows to eliminate the gearbox between the turbine and the generator without losing the important degree of freedom in the choice of optimal nominal rotation speed of the turbine. The latter advantage is particularly interesting for high power utilities, whose prime mover is a gas turbine, because for this power range the gearbox constitutes a heavy burden. The de-synchronization is realized with a static frequency converter which is a power electronics circuit composed of silicon power devices. The converter must ensure the same nominal frequency ratio than the gearbox it replaces, which can go above 50%. For such ratio the converter must be inserted between the stator windings of the generator and the grid. There are numerous different frequency converters. Some of them are available as industrial products and others are still in a development state. Not all of these different frequency converters are well adapted to high power applications. In the AG literature, a few recommendations suggest to use a low frequency commutation sequence, combined with a high number of input phases. The high number of input phases ensures a sufficient resolution of the converter's output voltage. Compared to others, this sequence is supposed to decrease the commutation losses of the converter, avoid the usual overdesign of the nominal power of the generator, and, finally, does not require the converter to include bulky intermediary DC storage components (capacitor or inductor). This sequence is a variant of the "Cosine Waveform Crossing" (CWC) method used for Naturally Commutated Cyclo-converters (NCC) and is named slowCWC. However, up till now, there is no converter that is able to run properly with this sequence. Thus a new converter is needed.

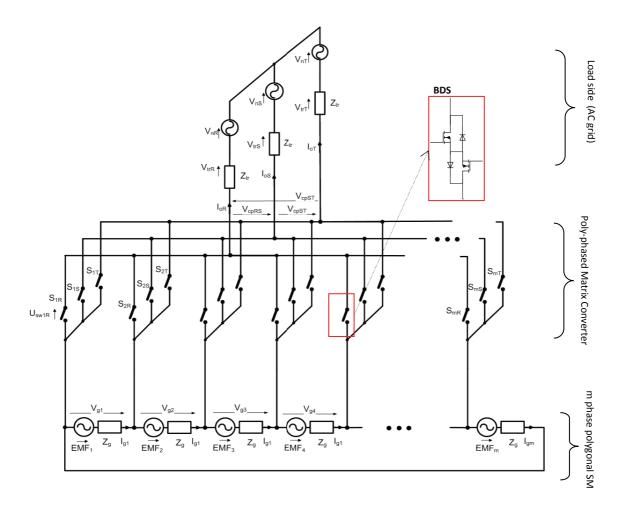

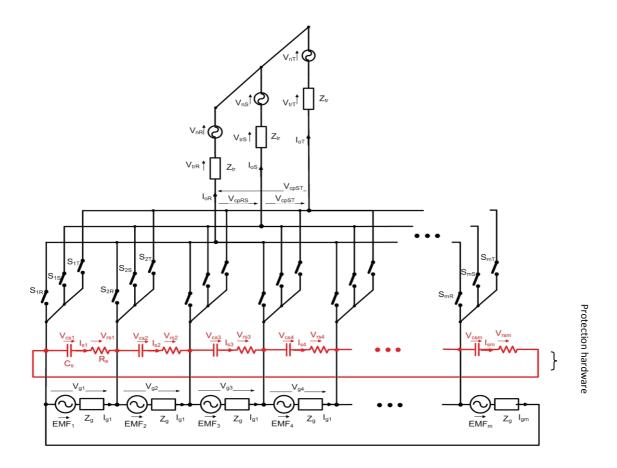

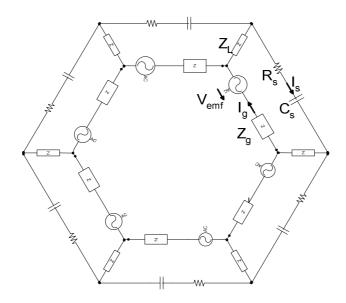

This PhD work introduces a new converter that is able to fulfill the *slowCWC* sequence. It is derived from a slight modification of an existing topology (NCC) and is called "gate-commutated Polyphased Matrix Converter" (PPMC). It is a direct frequency converter with a high number of input phases, generally greater than twenty, and a matrix structure of the valves that allows to connect each of the three output phases to each of the generator (input) phases. The valves are bi-directional in voltage and current and are transistor-based to achieve the turn-off capability required by the commutation sequence. The PPMC requires to add protection circuits across each generator stator winding. These circuits protect the stator windings from overvoltages which appear during some forced commutations.

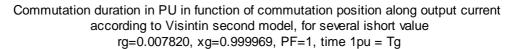

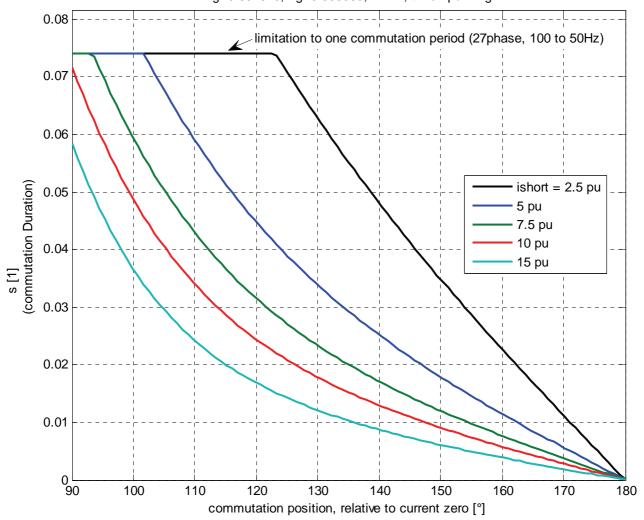

In its first part this PhD work uses an analytical approach and the results are expressed in a per unit system that is also adequate to describe the electrical machines. In this first part, it is about the development of design rules for the components of the protection circuits. In addition the energy losses linked to these circuits are evaluated. Those losses strongly depend on the commutation type, which is itself influenced by the presence of the protection circuits. The expression of the duration of natural commutations in the per unit system is also developed in this first part and it constitutes a key parameter in the determination of the commutation type. These theoretical developments are illustrated with numerical simulations.

In its second part this PhD work presents the realization of a small-scale experimental set-up with reduced power (1kW) but a high input phase number (27). The aim of the experimental set-up is to implement and experiment in real-time the command and control algorithm of the PPMC as well as to verify the theoretical predictions developed in the first part. The results of those developments lead to the quantitative assessment of the efficiency of the PPMC. Besides the key parameters that can help to improve this efficiency are pointed out. In certain cases the efficiency of the PPMC is acceptable under the condition that a generator parameter (its leakage reactance) remains under a

given limit. This work ends with a list of suggestions for future works related to the improvement of the PPMC and related to the AG project.

**Keywords:** frequency conversion, power electronics, power generation utility, gas turbine, variable speed, gearbox, efficiency, overvoltage, protection circuit, natural commutations, forced commutations, commutation duration, cosine waveform crossing.

#### Résumé

Ce travail s'inscrit dans le contexte d'un projet d'innovation nommé «the Active Generator » (AG). AG est un concept proposant un nouvel arrangement de la ligne turbine-générateur d'une centrale de production d'électricité de grande puissance (quelques centaines de MW) afin de désynchroniser la fréquence fixe du réseau électrique (50Hz ou 60Hz) de la fréquence de rotation du groupe turbinegénérateur. La désynchronisation amène principalement deux avantages. Premièrement, la vitesse variable du groupe permet d'utiliser la turbine de manière efficace en fonction de la puissance délivrée. Deuxièmement la désynchronisation permet d'éliminer le réducteur mécanique, généralement inséré entre la turbine et le générateur, sans perdre la liberté du choix de la vitesse de rotation nominale optimale pour le dimensionnement de la turbine. Ce dernier avantage est particulièrement intéressant pour les centrales de grande puissance, dont la source mécanique est une turbine à gaz, car le réducteur pour ces puissances est un fardeau incontournable. Le rapport de transformation des vitesses de ces engrenages est d'environ 2:1 ou supérieur. La désynchronisation et le remplacement du réducteur peuvent être réalisés par le biais d'un convertisseur statique de fréquence, c'est-à-dire un circuit électronique composé d'éléments à semi-conducteurs de puissance. La valeur du rapport des fréquences impose un convertisseur statique de fréquence de puissance nominale égale au groupe turbine-générateur. En plus, ce convertisseur doit être placé entre le stator du générateur et le réseau. Il existe aujourd'hui une multitude de convertisseurs de fréquence différents, certains fonctionnant déjà sous forme de produits industriels d'autres sont encore au niveau expérimental. Ces différents convertisseurs peuvent plus au moins bien être adaptés à des grandes puissances. Dans la littérature au sujet de AG, une série de recommandations proposent une séquence de commutation à basse fréquence avec un nombre de niveaux d'entrée élevé afin de garantir une résolution suffisante de la tension de sortie du convertisseur en se passant de filtre. Cette séquence est une variante de celle qui est utilisée pour les Cyclo-convertisseurs à commutations naturelles (CCN). Cette séquence aurait comme avantage, par rapport aux autres solutions, de diminuer les pertes du convertisseur, d'éviter un surdimensionnement de la puissance nominale du générateur, et enfin, de se passer de gros éléments passifs de stockage intermédiaires (condensateur ou inductance). Cependant il n'existe à ce jour aucun convertisseur capable d'exécuter cette séquence correctement. Un nouveau convertisseur est donc nécessaire.

C'est ainsi que ce travail propose une modification d'un convertisseur déjà existant (CCN) afin de réaliser un système compatible avec la séquence proposée dans la littérature. Cette solution est nommée « Polyphased Matrix Converter » (PPMC). Il s'agit d'un convertisseur de fréquence direct avec un nombre de phases d'entrée élevé, généralement supérieur à vingt, et une structure matricielle permettant de relier chacune des trois phases de sorties à chacune des phases du générateur d'entrée. Les interrupteurs sont de type bidirectionnels en tension et en courant, au pouvoir d'interruption contrôlable, une qualité imposée par la séquence de commutation utilisée. Le PPMC nécessite l'ajout de circuits d'aide à la commutation aux bornes de chaque phase statorique du générateur afin de protéger celles-ci contre des surtensions apparaissant lors de certaines commutations forcées. La première partie de ce travail est théorique et est constituée de développements algébriques qui expriment les résultats par des grandeurs adimensionnelles compatibles avec le système usuellement utilisé pour la description des machines électriques. Il s'agit de dimensionner les éléments du circuit de protection en fonction des contraintes données et d'évaluer les pertes supplémentaires occasionnées par ceux-ci. Ces pertes dépendent fortement du type de commutation qui est lui-même influencé par la présence des éléments de protection. Le développement du calcul de la durée relative des commutations naturelles est aussi donné dans cette première partie et constitue la clef de voûte dans la détermination du type de commutation. Ces résultats théoriques sont appuyés par des exemples de simulations numériques. Une deuxième partie de ce travail consiste en la réalisation et la mise en œuvre d'un modèle physique de PPMC à échelle réduite (puissance nominale 1kW) mais avec un nombre de phases d'entrée élevé (27) afin de tester la commande et le contrôle du PPMC en temps réel et aussi de vérifier les calculs théoriques donnés en première partie de ce travail. Les développements amenés tout au long de ce travail

permettent de donner une appréciation quantitative du rendement énergétique du PPMC et de mettre en évidence les paramètres clés par lesquels il est possible d'améliorer ce rendement. Dans certains cas, le rendement du PPMC est admissible pour l'application sous la condition qu'un paramètre du générateur (la réactance de fuite) reste au-dessous d'une valeur critique. Le travail est ponctué par une liste de propositions de développements futurs relatifs au PPMC et au projet d'innovation AG.

**Mots clefs:** conversion de fréquence, électronique de puissance, centrale électrique, turbine à gaz, vitesse variable, train d'engrenages, rendement énergétique, surtension, circuit de protection, commutations naturelles, commutations forcées, temps de commutation.

## **Table of contents**

| Chapter 1 - Introduction                                             | 1    |

|----------------------------------------------------------------------|------|

| 1.1 Context and structure of the work                                | 2    |

| 1.2 Active Generator principle overview                              | 4    |

| 1.3 Towards the proposed new converter                               | 10   |

| Chapter 2 - Poly-phased direct frequency conversion                  | 13   |

| 2.1 Introduction                                                     | 14   |

| 2.2 Basic commutation cell                                           | 15   |

| 2.3 Minimum error sequence                                           | 19   |

| 2.4 Cosine Waveform Crossing (CWC) sequence                          | 21   |

| 2.5 The slowCWC sequence                                             | 27   |

| 2.6 Input and output waveforms properties                            | 32   |

| Chapter 3 - The Poly-Phased Matrix Converter (PPMC)                  | 41   |

| 3.1 Introduction to the PPMC                                         | 42   |

| 3.2 The forced commutation issue                                     | 48   |

| 3.3 Case study - introduction                                        | 51   |

| 3.4 Commutation cell within the PPMC                                 | 55   |

| 3.5 The duration of natural commutation                              | 64   |

| 3.6 Existence of natural commutation                                 | 70   |

| 3.7 Conduction losses                                                | 78   |

| 3.8 Switching losses                                                 | 81   |

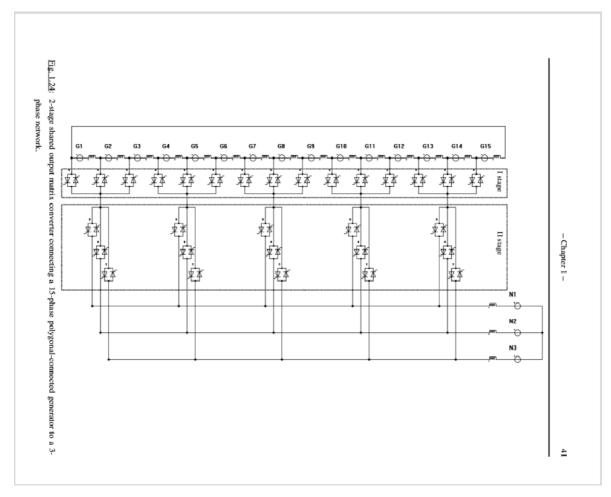

| 3.9 The two stages topology                                          | 84   |

| Chapter 4 – Design and properties of the snubber circuits            | 87   |

| 4.1 Introduction                                                     | 88   |

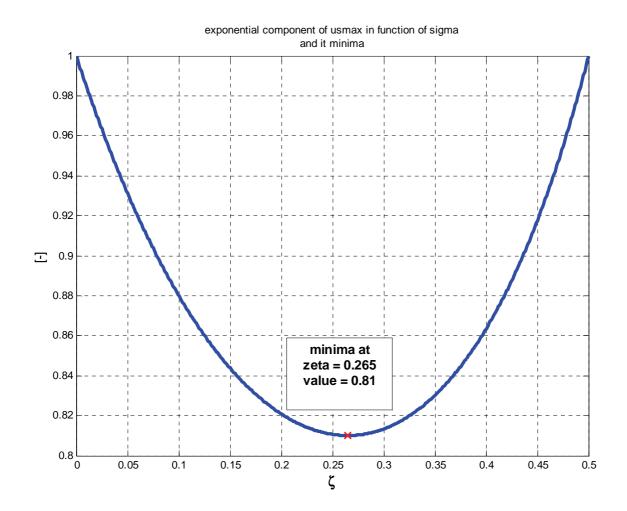

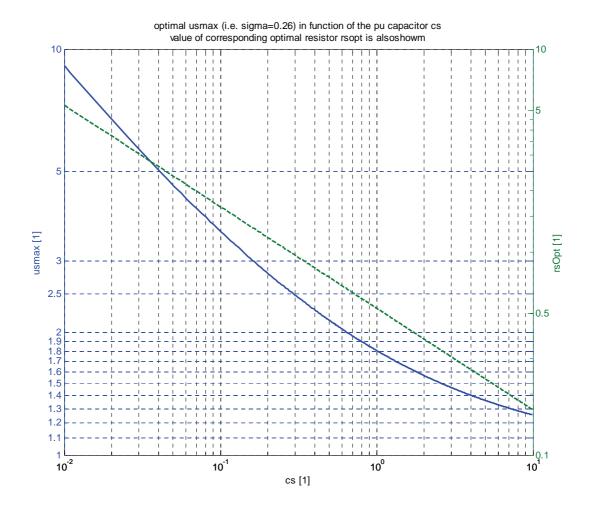

| 4.2 Design of RC snubber circuits                                    | 88   |

| 4.3 The effect of the forced commutations at the output of converter | 101  |

| 4.4 Evaluation of the dimensions of snubber capacitors               | 103  |

| 4.5 Energy and efficiency considerations                             | 104  |

| 4.6 Case study to illustrate the snubber design rules                | 123  |

| 4.7 Case study to illustrate the energetic properties of the snubber | 131  |

| 4.8 Alternative solution for snubber circuits                        | 138  |

| Chapter 5 – Command and control of the PPMC                          | 145  |

| 5.1 Introduction                                                     | 1/16 |

| 5.2 Command algorithm of the PPMC            | 147 |

|----------------------------------------------|-----|

| 5.3 Current control                          | 159 |

| Chapter 6 – Small scale experimental set-up  | 163 |

| 6.1 Experimental set-up principle            | 164 |

| 6.2 Realization of the experimental set-up   | 169 |

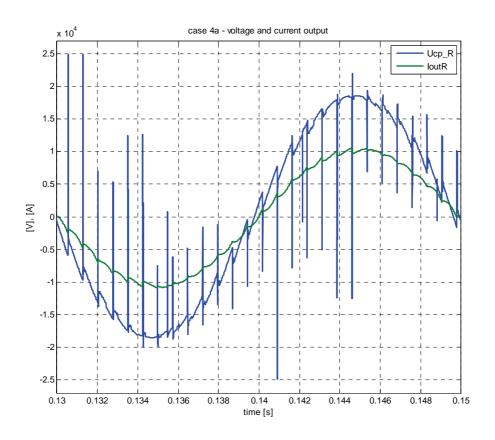

| 6.3 Experimental results                     | 171 |

| Chapter 7 – Conclusion and perspectives      | 177 |

| 7.1 Conclusions on the new proposed topology | 178 |

| 7.2 Perspectives                             | 179 |

| Nomenclature                                 | 181 |

| Bibliography                                 | 185 |

| List of figures                              | 189 |

| List of tables                               | 193 |

## **Chapter 1 - Introduction**

#### 1.1 Context and structure of the work

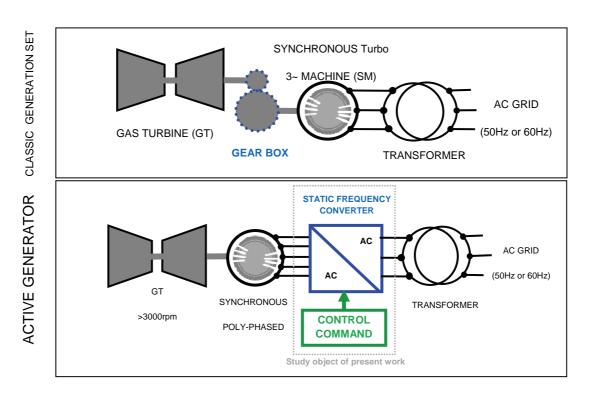

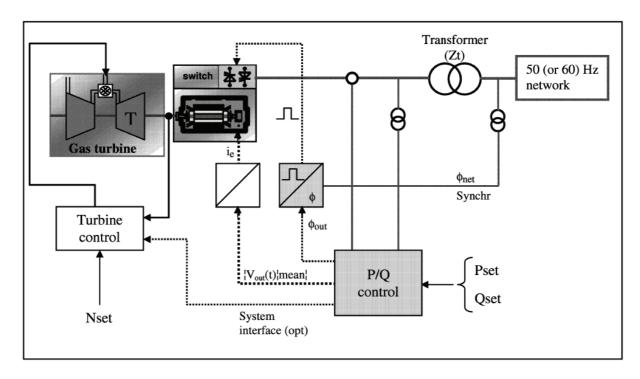

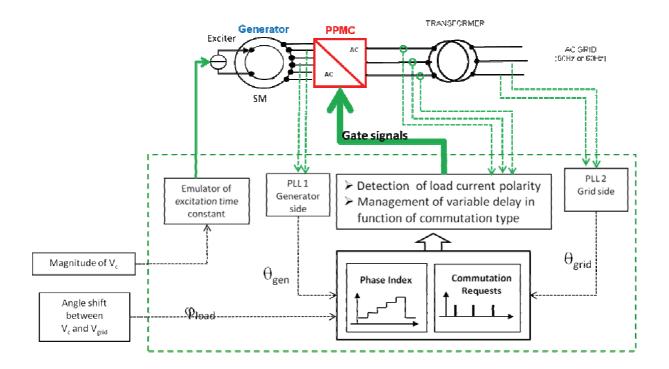

The "Active Generator" (AG) provides the framework of this PhD thesis. The AG principle, as shown in Fig. 1.1, describes a non-classical arrangement of a power generation utility, which consists in the insertion of a static frequency converter between the electrical generator and the electrical 50Hz (or 60Hz) grid. In general, the AG principle is associated installation of a power range of several hundreds of MW per generation group. The AG principle was first mentioned in [1], [2] and [3] where the prime mover is a gas turbine. At EPFL's LEI, two PhD thesis have been dedicated to the AG principle [13] and [14], both of them focus on the analysis of a specific converter topology in order to assess the feasibility of the given topology for the AG application. Similarly, in this PhD work, a new static frequency converter is proposed and its feasibility is analyzed. This new converter is derived from existing converters and is called gate-commutated "Poly-Phased Matrix Converter" (PPMC).

Fig. 1.1- Classical vs. Active Generator layout of a power utility

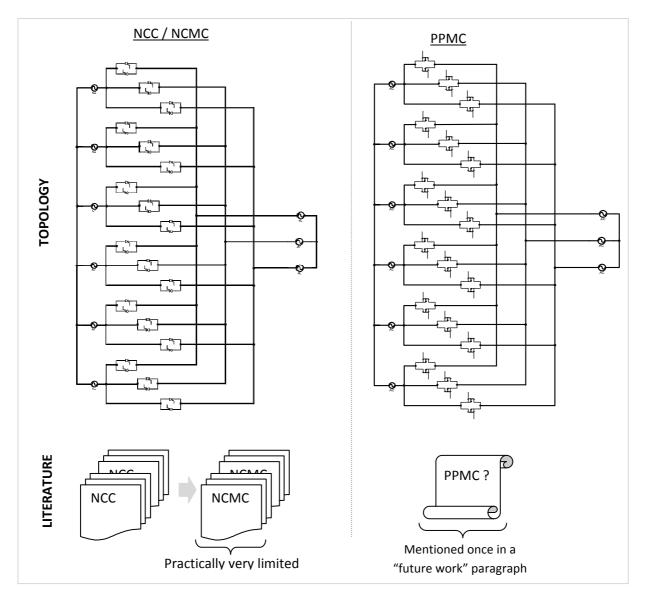

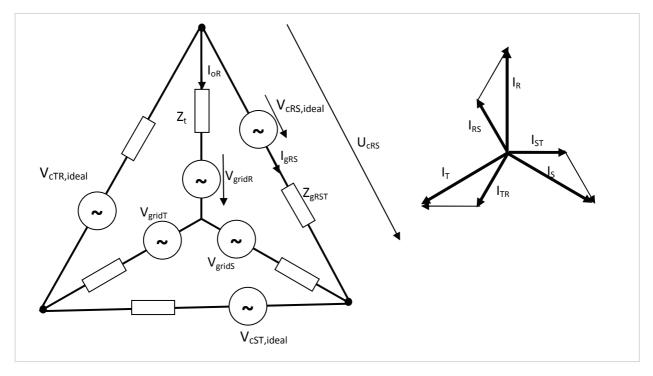

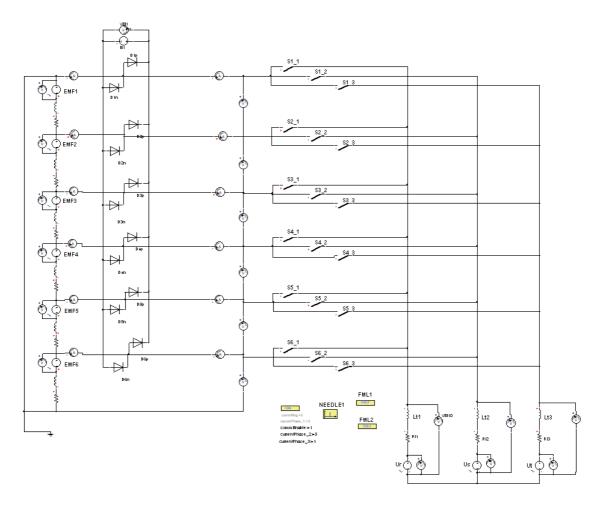

The next section of this introductory chapter presents an overview of the AG principle and a review of the literature related to this topic. This review leads to the presentation and justification of the proposed new converter. Fig. 1.2 (right) shows a simple schematic of the PPMC, which is a direct frequency converter, gate-commutated as opposed to the line-commutated converters proposed in the literature (Fig. 1.2, left). The PPMC is linked to an interesting and advantageous commutation sequence previously mentioned in the literature [1] but never used efficiently because of the limitations of natural commutations. This commutation sequence is renamed slow "Cosine Waveform Crossing" (slowCWC) in this thesis, as a result of a detailed analysis and comparison with the better known CWC (Cosine Waveform Crossing) sequence, as defined in [5]. As this sequence plays a key role in the proposed new topology, chapter 2 presents the theory about commutation sequences for poly-phased direct frequency conversion application.

Chapter 2 details the steps that, from the existing commutation sequence, lead to the commutation sequence *slowCWC*. The interesting input and output properties of the *slowCWC* sequence are highlighted with frequency spectrum of ideal waveforms. Those properties are important because they have a strong influence on the elements connected on each side of the converter. This chapter also introduces the basic commutation cell which will be used extensively throughout this work. In particular, to achieve the *slowCWC* sequence, the basic commutation cell shows that the PPMC must be able to perform natural and forced commutations. By appropriated command algorithm, one can choose to operate the PPMC only with forced commutations or with a mix of forced and natural commutations, i.e., the full forced or the mix mode.

Fig. 1.2 - State of the art of Topology and literature for AG principle

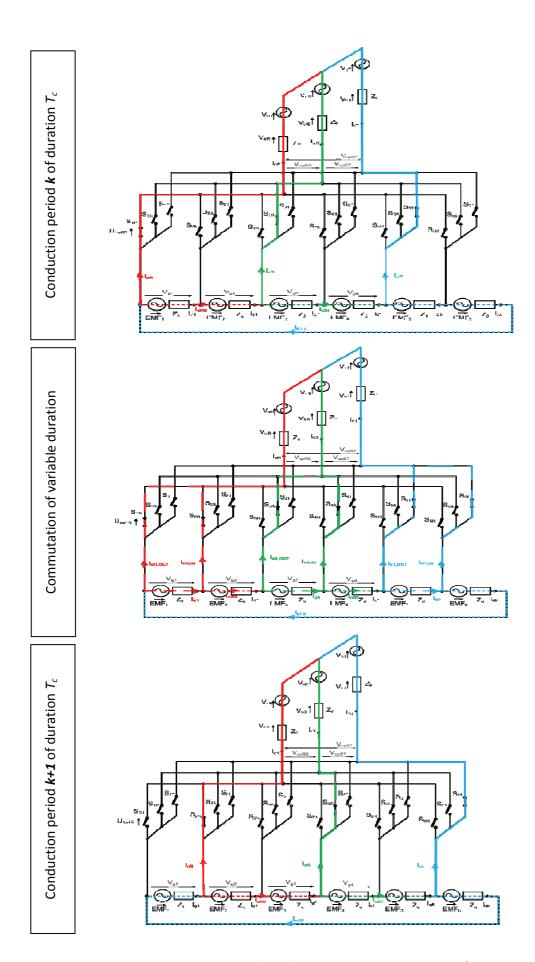

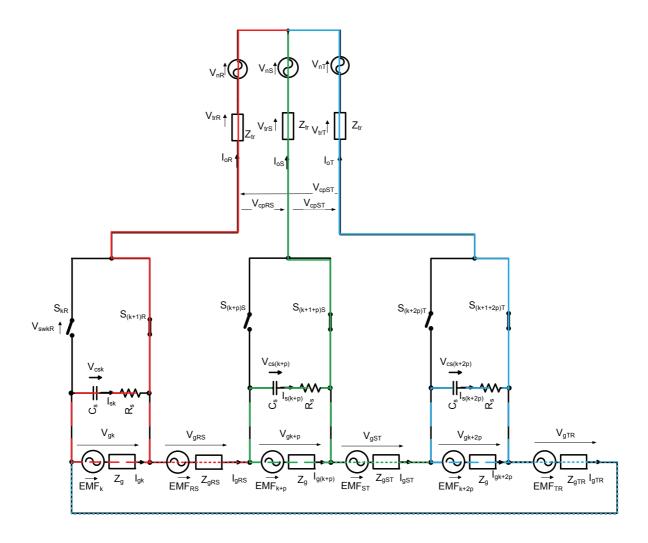

Chapter 3 and chapter 4 are the core of this work. Chapter 3 presents in details the new proposed static frequency converter, the PPMC. Because the PPMC operates with the *slowCWC* sequence, some of its commutations must be forced, which requires to add a passive protection circuit (or free-wheeling path) across each input phases to avoid destructive overvoltages. The presence of this free-

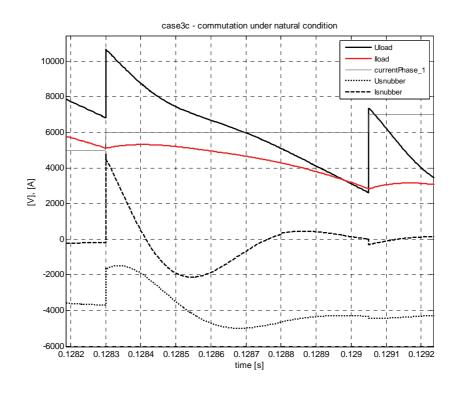

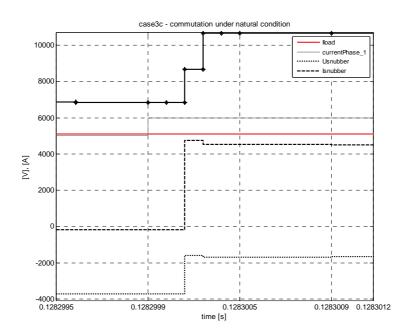

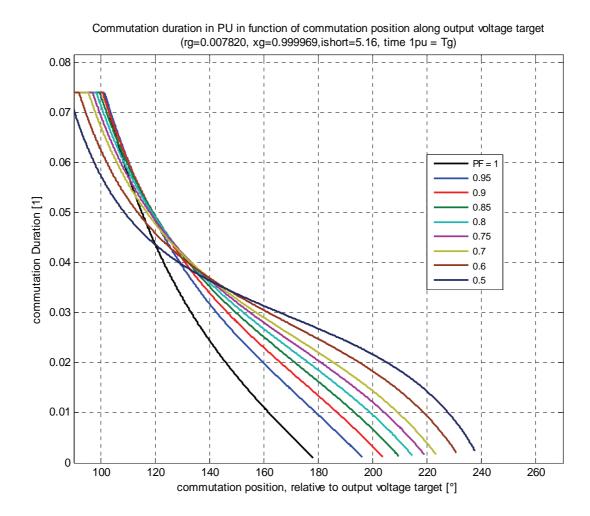

wheeling path modifies the basic commutation cell. Chapter 3 gives a detailed analysis of the modified commutation cell. This detailed analysis is essential in order to understand the PPMC operation, in order to evaluate its energetic properties and in order to select a suitable mode of operation, i.e. full forced mode or mix mode. The particularity of the analysis of the modified commutation cell is that it expresses the results in a per unit system where the relative parameters of the generator and of the protection circuit also appear. The relative system allows to highlight how each parameter influences the studied properties. Chapter 3 gives an original analysis of the duration of natural commutation expressed in the per unit system. The relative duration of the natural commutation is a key parameter that influences the type of commutations and their distribution along one period of the output of the converter. The false natural commutation and the early cut-off are phenomena that are directly influenced by the duration of the natural commutation. Chapter 3 gives an extensive study of both of those phenomena because they can have a significant influence on the energetic properties of PPMC. Also, chapter 3 gives an assessment of the conduction and switching losses of the PPMC.

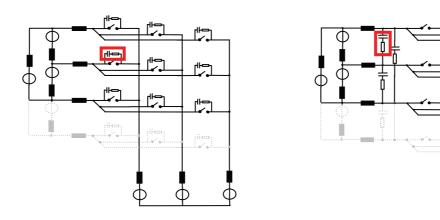

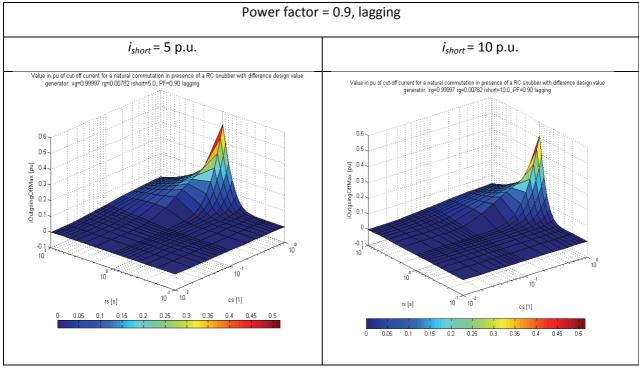

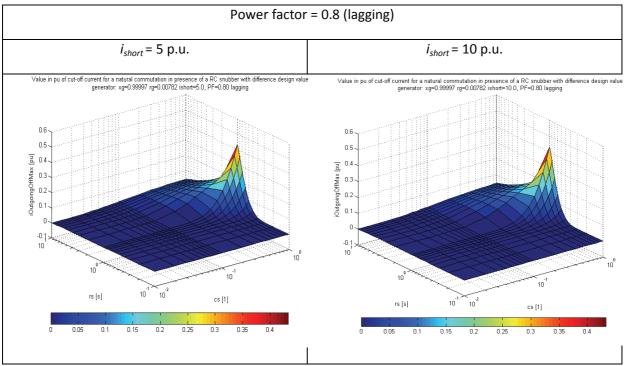

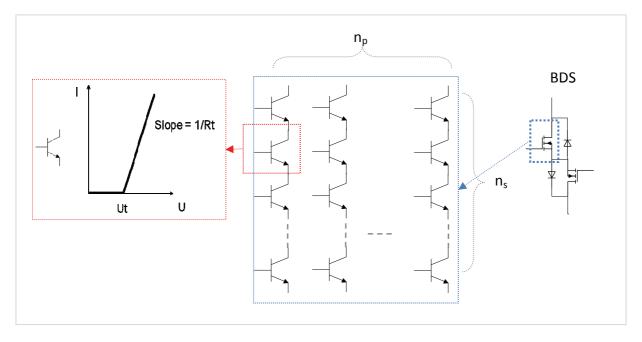

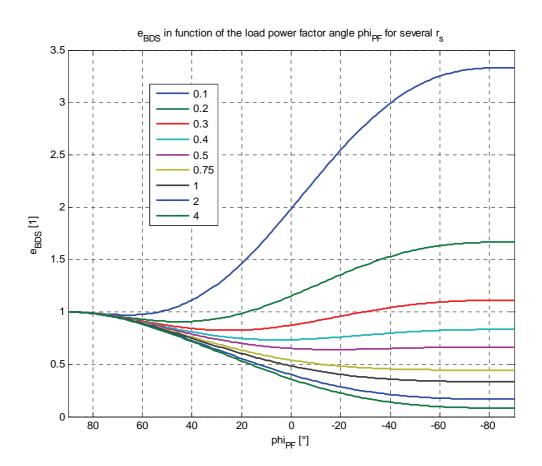

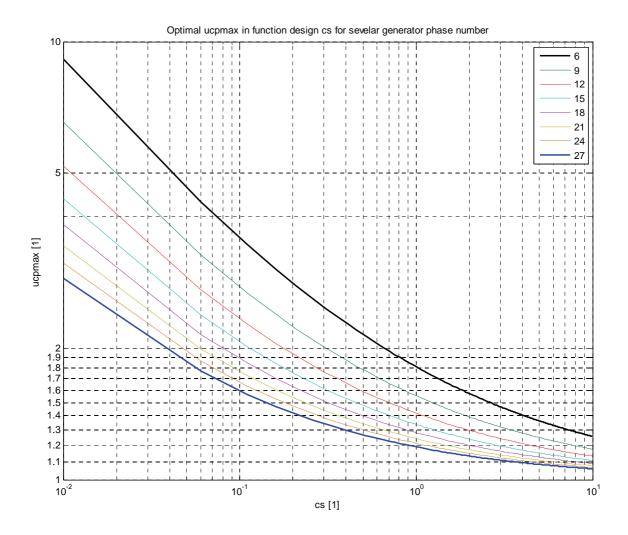

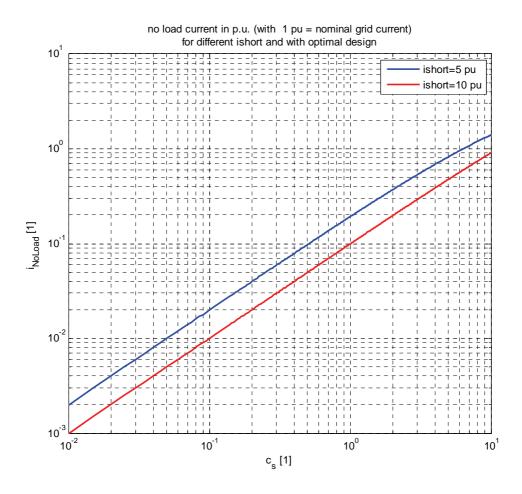

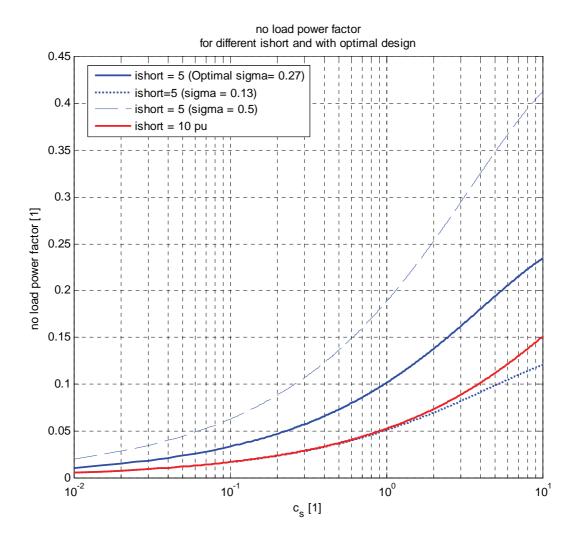

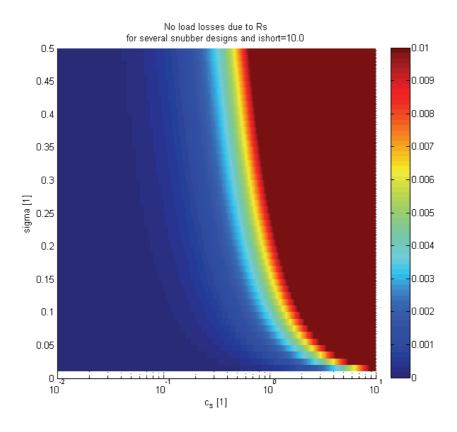

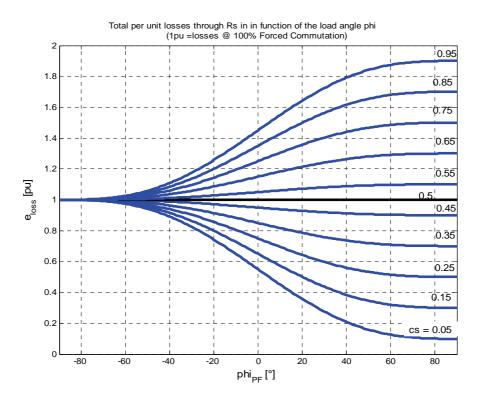

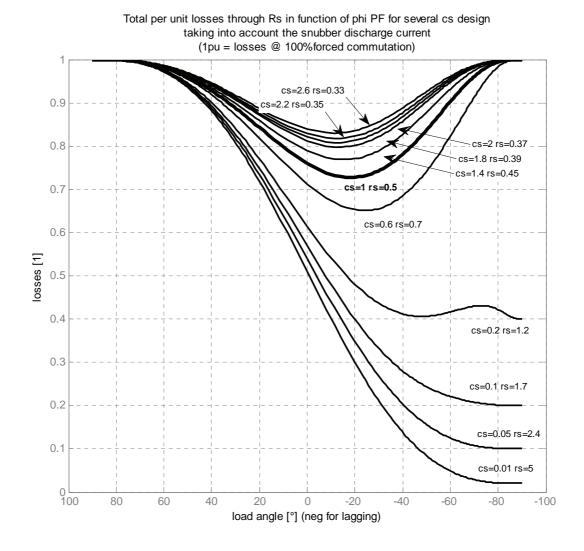

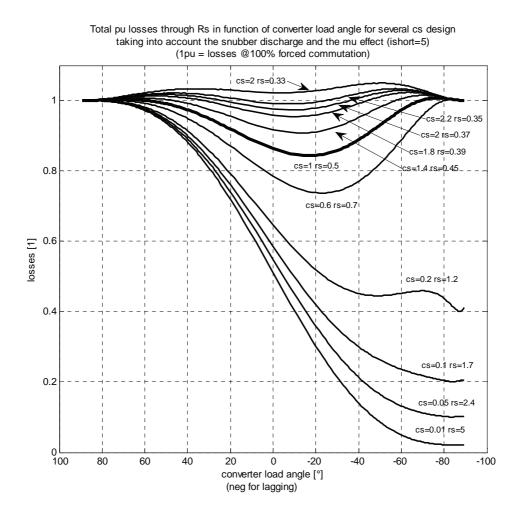

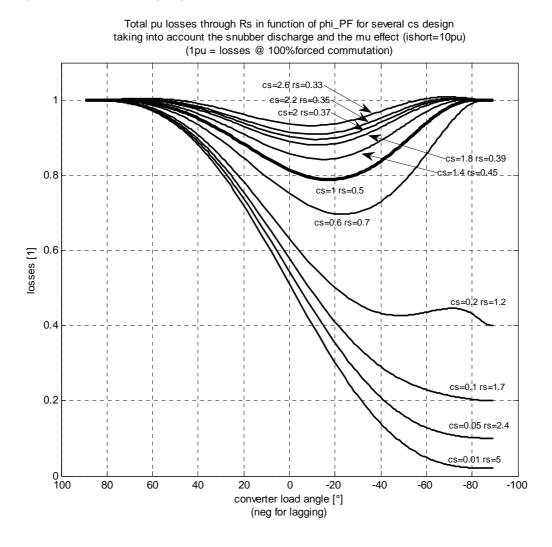

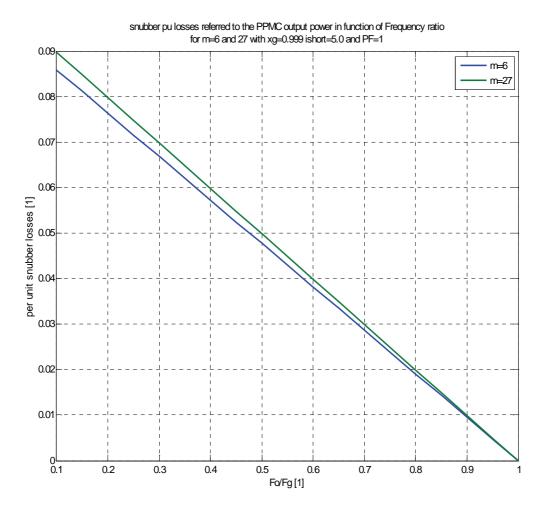

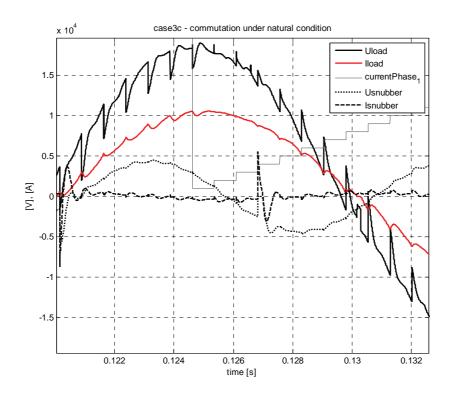

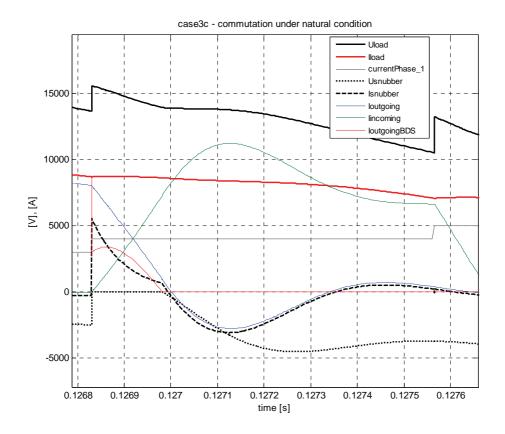

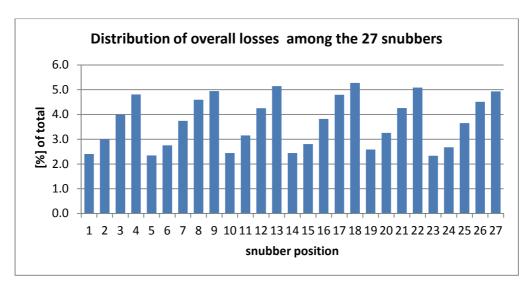

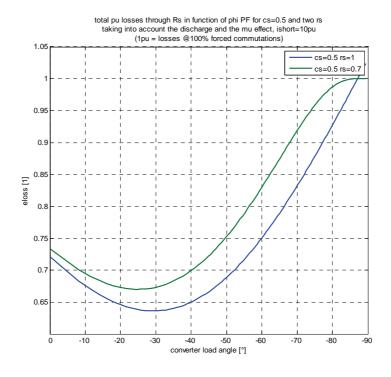

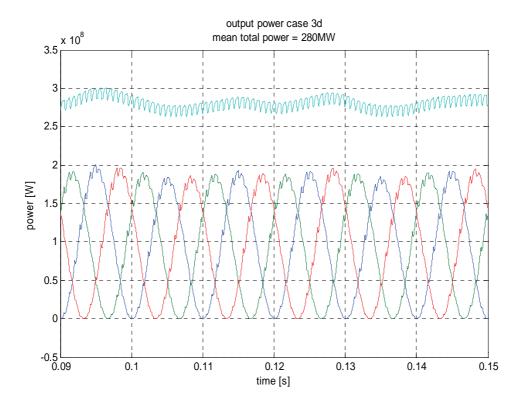

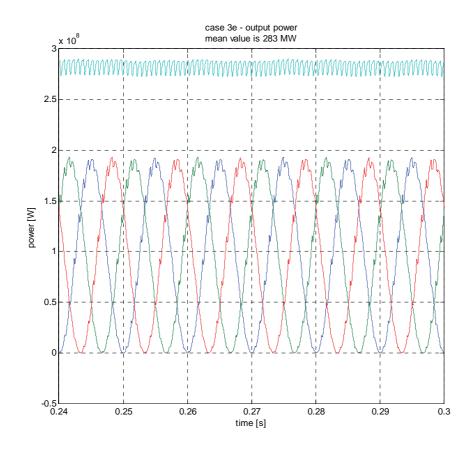

Chapter 4 first develops a design method of the protection circuit that is based on algebraic equations, expressed in the per unit system defined in chapter 3. The design method gives the optimal values of the components of the protection circuit from a single design abacus, where the optimum corresponds to the minimum value of installed passive component for a given overvoltage constraint. Second, on the basis of result of chapter 3, chapter 4 develops algebraic formula that describe the energetic properties of the protection circuit and its role in the global efficiency of the PPMC. This energetic analysis takes into account two phenomena of the modified commutation cell, which are the false natural commutation and the early cut-off. This energetic analysis of the protection circuit helps to conclude on the advantage of running the PPMC with a mix of forced and natural commutations. In chapter 3 and 4, simulation results are presented in order to illustrate and verify the theoretical calculations.

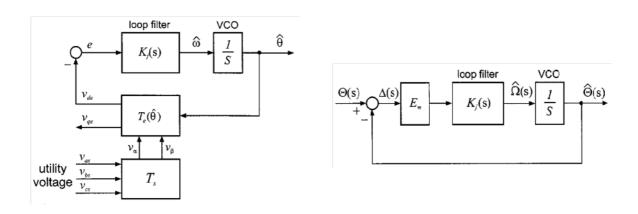

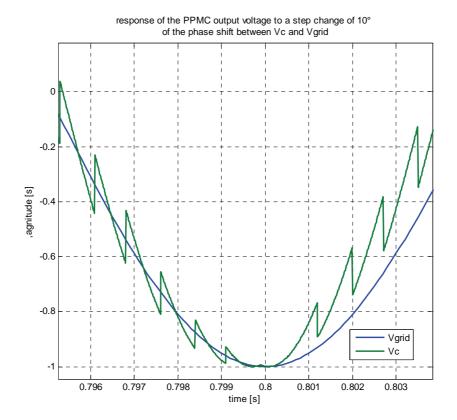

Chapter 5 gives the details of the command algorithm of the PPMC. In particular, the method for the synchronization of the PPMC with the AC grid is explained. The understanding of the command algorithm of the PPMC is very important to design its power control. In this regard, chapter 5 also sets the basis for the design of a current control for the PPMC and presents some preliminary results. In particular chapter 5 highlights the dynamics limitations that are intrinsic to the *slowCWC* commutation sequence.

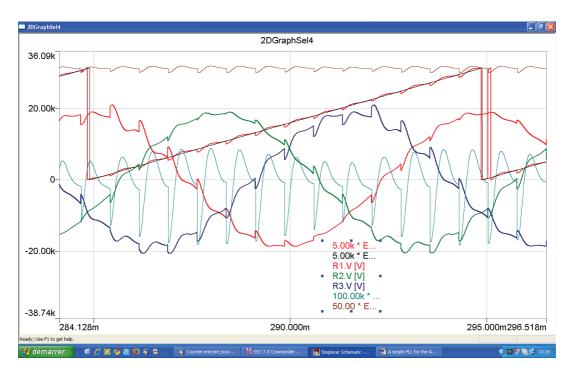

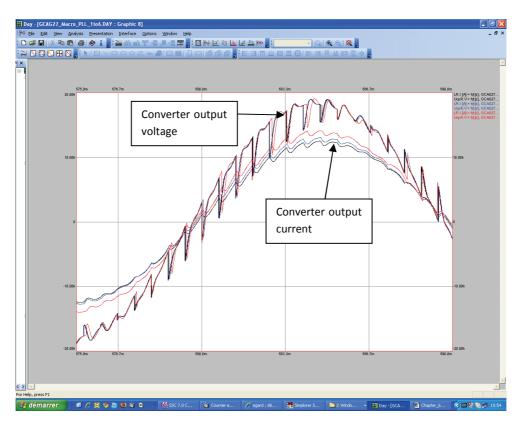

Chapter 6 presents the experimental set-up that has been realized during this PhD work and first experimental results. Finally, chapter 7 summarizes the obtained results to obtain a global picture of the new proposed converter. Besides, the conclusion gives a generous list of perspectives and future developments related to the PPMC and to the AG principle.

#### 1.2 Active Generator principle overview

The Fig. 1.1 describes the AG principle. It consists in the insertion of a static frequency converter inbetween the generator and the AC grid in order to de-synchronize the rotational speed of the generator and the stiff AC grid 50Hz (or 60Hz). The AG concept also recommends to use a direct static frequency converter with a naturally commutated sequence. Likewise it recommends the use of a poly-phased generator, i.e. a synchronous machine (SM) that has a number of stator windings

higher than three. To be noted that the generator is still referred to as a "Synchronous Machine" (SM) because its basic operation principle is identical to a standard three-phase SM. The converter topology and the commutation sequence will be described in detail in chapter 2 and 3. The next paragraph presents the main advantages of the de-synchronization, or variable speed feature of the AG.

#### 1.2.1 Motivation for de-synchronization (or variable speed)

For power generation utilities connected to an AC grid, like wind turbine, hydro power plants or even gas/steam turbine driven generators, the variable speed feature can offer several advantages that are listed below.

- part load efficiency optimization

- elimination of gear box

- unique prime mover design for several grid frequencies

- control of power flow through the static converter (FACTS functionality)

- elimination of the auxiliary converter for start-up

Without the variable speed feature, the prime mover's rotational speed is linked to the grid frequency by a factor that depends on the number of poles of the electrical machine and on the ratio of the mechanical gearbox, if any. For a SM with two poles, the rotational speed of the shaft is 3000rpm,. For a SM with four poles, the rotational speed decreases to 1500rpm. The prime mover is designed for a given nominal rotational speed and delivers a nominal power at this speed with the nominal efficiency, assumed to be the best one. If the optimal rotating speed does not match 3000rpm or 1500rpm, a gear box is inserted between the prime mover and the generator. In general, the efficiency curve of the prime mover in function of the delivered/absorbed power with a fixed rotational speed has the shape of a bell. This means that the part load operation of the prime mover degrades the efficiency. Briefly, the reasons for this bell shape efficiency curve are to be found in the mechanical and thermal laws governing those machines (e.g. a fixed orientation angle of runner blades). Examples of bell-shape efficiency curves can be found in [40] for gas turbines and in [48] and [59] for hydro turbines. The variable speed feature, achieved with a frequency converter, allows adapting the speed to operate the prime mover on its maximum efficiency point for whatever the load is. Usually, this requires a relatively small speed variation, in the range ±30% of nominal speed.

The gear box inserted between the prime mover and the generator allows an optimal design of the mechanical prime mover but becomes a drawback for high power installation (maintenance, noise, efficiency, space and cost). For high power, if no gear box is used, the fixed rotational speed of 3000rpm or 1500rpm forces design trade-off of the rotating machines, and often compromises the efficiency of those machines. In this case, the replacement of the gear box by a static frequency converter allows to design the prime mover with the desired rotational speed without the burden of the gear box. However, the frequency ratio could then easily reach the value of 50% or more, which represents a speed variation greater than the one required for the function of maximizing the efficiency point, described above. The required frequency ratio for the frequency converter will strongly influence the converter-machine arrangement, as discussed below.

FACTS functionality: The power control will be achieved through control of the converter output in terms of phase shift and magnitude. This strategy will surely change the rules for the design of the

SM in term of internal impedance. The presence of the converter between the machine and the network considerably redefine the dynamic of the power plant and all the issue around the tripping of the group in case of short circuit on the network side.

#### 1.2.2 Converter-machine arrangement

Before power electronics and converters were available on the level of industrial products, frequency conversion was realized by the use of back to back and cascaded rotating electrical machines and playing with the windings connections and voltage levels. Discussing this arrangement here is beyond the scope of this thesis. Today, the advances in the power electronics field allow to build satisfying frequency static converters. There are two possibilities to de-synchronize the electrical machine. Either the converter is placed between the grid and stator of the machine or it is placed between the grid and the rotor of the machine. In the latter case, this requires an asynchronous machine with an accessible three phase wound rotor (through brushes usually). This arrangement is often referred to as Doubly Fed Induction Machines (DFIM). The DFIM arrangement is very efficient and the nominal power of the converter is only in the order of  $s*P_N$  where s is the slip speed and  $P_N$  is the nominal power of the fed machine. In practice, s ranges between 0 and 0.3 in order to keep the eddy current losses in the rotor low. Unfortunately, in the AG principles because the frequency converter replaces the gear box, the sliding speed s would be too large and the elegant DFIM solution must be discarded. That is why, in Fig. 1.1, the static frequency converter is inserted between the grid and the stator of the SM. The nominal power of the converter is equal to the nominal power of the SM.

### 1.2.3 Variable speed power generators applications in the world

Variable speed applications are wide spread in the field of hydraulic pump/turbine storage machinery (mostly in a DFIM configuration) in order to run the hydraulic machines with the best efficiency whatever power is demanded. In case of a pumped storage plant, the optimal rotational speed of both pump and turbine mode are usually different. With variable speed, pump and turbine mode can both work at their best efficiency for a range of operating points. For large gas turbines power utilities, no realization has been reported in the literature with the exception of the starting devices. Table 1.1 gives some examples of real applications of variable speed.

Table 1.1 – A few samples of variable speed power generation applications in the world

| Place                           | Year      | Mechanical mover        | Configuration | Nominal Power                          | Speed range    |

|---------------------------------|-----------|-------------------------|---------------|----------------------------------------|----------------|

| Ukraine                         | 1985/1991 | Turbine (steam)         | DFIM          | 200MW                                  | -              |

| USSR                            | 1960-1962 | Hydro (turbine)         | DFIM          | 50MVA                                  | -              |

| Japan                           | 1980      | Hydro<br>(Pump/turbine) | DFIM          | 360MVA                                 | +8/-10%        |

| Japan<br>(Ohkawachi)            | 1993      | Hydro<br>(Pump/turbine) | DFIM<br>(NCC) | 400MVA                                 | 330 to 390 rpm |

| Germany<br>(Goldisthal)         | 2004      | Hydro<br>(Pump/turbine) | DFIM<br>(NCC) | 2x265MW<br>(1060MW<br>total installed) | +4%/-10%       |

| Japan<br>(Yagisawa)             | 1991      | Hydro<br>(Pump/turbine) | DFIM<br>(NCC) | 82MW                                   | 130 to 156 rpm |

| Germany<br>(GROWIAN<br>project) | 1983      | Wind                    | FSC           | 3MW                                    | +30%/-90%      |

Sources: [12], [18], [42], [44], [45], [48] to [54]

#### 1.2.4 Converter and Generator requirements

As written above, the variable speed features should also be applied for large Gas Turbines (GT) power gen sets. This would remove the gear box, eliminate the start up converter but add the main frequency converter.

In the AG literature, a converter topology and its associated sequence are recommended. The precise choice of the best converter topology needs criteria in order to compare topologies among them. Most of these criteria are technical and are listed in Table 1.2 and commented hereafter. The economical criterion is also important but won't be taken into account in this thesis, because it relies on cost functions that can widely vary with time and the politico-economical situation.

Table 1.2 - Criteria for AG frequency converter

| Criterion         | Importance for AG |

|-------------------|-------------------|

| Weight            | Not critical      |

| Space             | Not Critical      |

| Efficiency        | Critical          |

| Output quality    | Critical          |

| Dynamic Behaviour | Critical          |

Weight: the weight of the converter is not critical because it is not a mobile application.

**Space**: the required room to build the converter is not critical because in the context of a high power generator set, the GT already requires a large room and there are no high constraints on available room.

**Current and voltage quality**: as the converter is connected to the grid and is part of a generation utility, the requirements in terms of THD of the output voltage and currents are severe. For example the THD requirements for a 110kV connection point are 2.5% for voltage and current [15]. There are also harmonics not to be over passed. On the side of the generator, the THD of the stator current should be limited to avoid heating losses.

**Dynamic behavior**: Power generation installations must fulfill a set of given conditions during transient behavior when connected to the grid. It also helps maintaining the grid. The kind of transient behavior that he power generation set must be able to manage correctly will not be discussed in this thesis.

**Efficiency**: in the context of power generation, the efficiency of the converter is critical for obvious ecological and economical reasons. However, one should above all consider the global efficiency of the power plant. In this respect, there could be special power plant configurations where the relevance of the converter's efficiency is relatively low. This could be the case if a combined cycle power plant configuration is used, where the losses of the converter could be used as heat source in a CHP system.

If the role of the converter is only to replace the gear box, then in order not to alter the overall efficiency, the converter must have a similar efficiency as the gearbox. To be more accurate, the converter effect on the generator must also be taken into account. The waveform of the currents in the generator windings will have to be defined in detail in order to assess this effect.

Table 1.3 provides examples of efficiencies of the components of the power generation set. The efficiency of the generator is given for two configurations: connected to a converter or directly to the grid. The efficiency of the gas turbine is given for two cases: in variable speed or fixed speed mode. Each efficiency value is given for a nominal point and for a 50% part load. These are only approximation and only the order of magnitude is to be considered here. Those values are taken from [15] in which the static converter is a NCMC from which the PPMC is derived. For the full load, it is important that the effect of the converter on the generator efficiency is reduced, and the converter itself must have comparable efficiency with the gear box, or even slightly higher to compensate for the reduction of the generator efficiency. Overall, it is clear that for full load, the gain in efficiency of the AG is not a key motivation. To be noted in the values presented in Table 1.3 the classical configuration contains a gear box, so in the design of the Gas turbine its nominal rotational speed is a freedom degree. It could be that for high power, the use of a gear box is discarded which cancels this freedom degree which in turn would affect the GT efficiency. In this case the AG configuration would be advantageous.

Table 1.3 - Numerical examples of efficiencies of the components involved in an AG generation set

| Device                         | Efficiency                                    |                             |                     |

|--------------------------------|-----------------------------------------------|-----------------------------|---------------------|

|                                | Symbol                                        | Typical<br>nominal<br>value | 50% load efficiency |

| Gas turbine without var. speed | $\eta_{\text{GT}}$                            | 40                          | 20 to 30            |

| Gas turbine with var speed     | η' <sub>GT</sub>                              | 40                          | 40                  |

| Gear box                       | $\eta_{GB}$                                   | 98.5                        | 97                  |

| Generator without converter    | $\eta_{Gen}$                                  | 98.2                        | 97.6                |

| Generator with converter       | η' <sub>Gen</sub>                             | 97.8                        | 96.4                |

| Converter                      | $\eta_c$                                      | 99.6                        | 99.5                |

| Overall Classical solution     | $\eta_o = \eta_{GT} * \eta_{GB} * \eta_{Gen}$ | 38.7                        | 18.9 to 28.4        |

| Overall AG solution            | $\eta = \eta'_{GT} * \eta'_{Gen} * \eta_{C}$  | 38.9                        | 38.4                |

Sources [15]

For the part load, the increased efficiency of the GT with variable speed largely compensates for the negative effect of the converter on the generator and for the converter the own part load efficiency decreases.

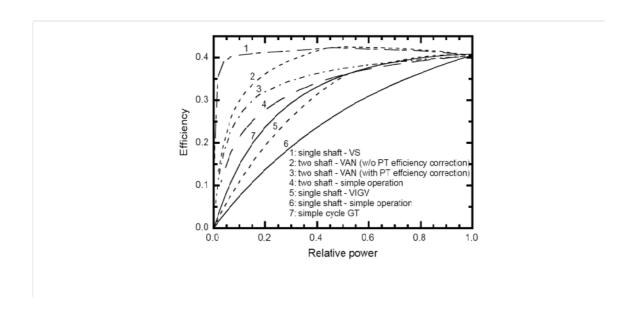

In the literature of thermo-dynamical engineering, GT efficiency in different configurations has been discussed. Fig. 1.3 from [40] shows examples of GT efficiency in function of relative delivered power, from no load to full load, for different configurations. There are several means to enhance the efficiency of a GT, which constitute a purely thermo-dynamical solution. Besides, there is the variable speed solution, which is the curve #1 in Fig. 1.3. Although Fig. 1.3 is given for medium power GT, we assume similar tendencies for higher power GT. This clearly shows the high potential of variable speed for increasing the part load efficiency of a GT.

Fig. 1.3 - Example of different configurations and various part load operation strategies of GT (source [40])

Even if the overall efficiency is mainly affected by the GT efficiency, it is important for electrical engineering to keep the high efficiency converter and make all possible effort to gain a few efficiency points in order not to cancel out the effort from the mechanical engineering part to gain a few efficiency points. But it is clear that most improvements are in the hands of mechanical engineers.

#### 1.2.5 Frequency converter topology

The literature about AG principle, as said earlier in this section, has already recommended a converter topology and a respective commutation sequence. Here, a brief review of frequency converter topologies is provided to understand the recommendations made in the literature about the AG principle.

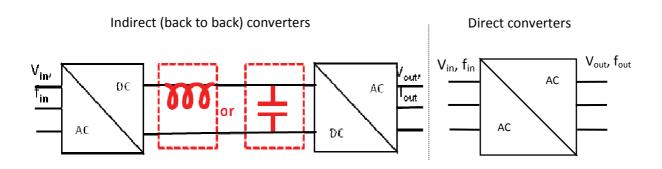

#### **Indirect Converters vs. Direct**

A frequency converter is a power electronic circuit that permits to interconnect two AC power sources which have different frequencies and optionally different voltage levels. There are two main categories of frequency converters: indirect and direct converters that are depicted in Fig. 1.4. Both categories can perform frequency conversion along with voltage adaptation. They also can both deal with bidirectional power flow.

Fig. 1.4 – Two main AC/AC converter categories

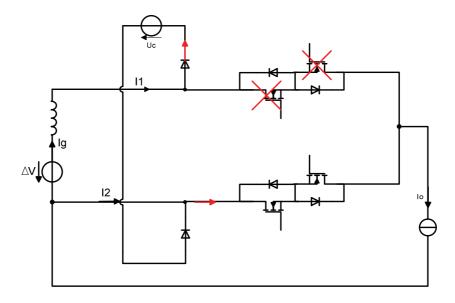

The indirect converters process the conversion in two steps: a rectifying step followed by an inverting step. Those converters absolutely need a DC energy storage unit for their DC link, either a large capacitor or a large inductor. The load current has to go through two silicon stages. This technology is very well known and practically used. Back to back Voltage Source Converter (VSC) or Current Source Inverter (CSI) are practical implementations of the indirect conversion.

The direct frequency converters process the conversion in a single step. They skip the rectifying process and do not store energy inside. They take portions of the input sine waves to build the output wave with the desired frequency (lower) and possibly desired harmonic contents. This solution does not require any device for energy storage but has a strong influence on both sides in terms of frequency content. The load current flows through two stages of silicon devices. For direct converters, there is abundant literature and practical realizations on Naturally Commutated Cycloconverters (NCC) [5], [16] and [18] or Matrix Converter [19], [55] to [57]. Another argument in favor of the direct converters is the advantage of avoiding a double conversion that results in a cascade of partial efficiencies.

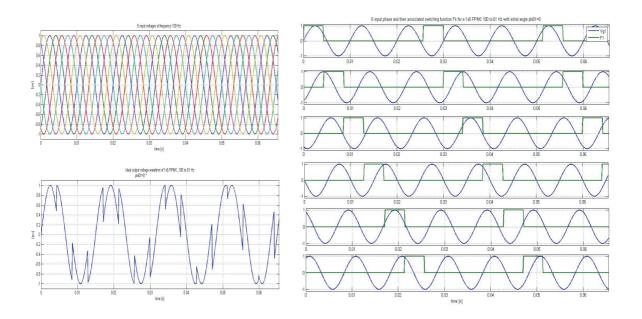

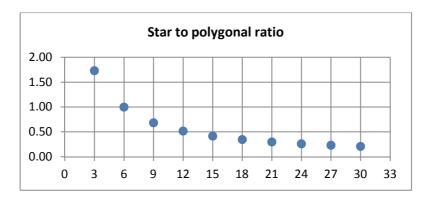

#### Switching frequency

Both categories of frequency converters can be operated with a high switching frequency ( $F_{switching} >> F_{out}$ ) or a low switching frequency ( $F_{switching} >= F_{out}$ ), where the switching frequency is the frequency of use of one switch. Both categories can be run with high or a low number of levels. The number of levels directly influences the resolution of the quantification of the ideal output waveform the converter should produce. To obtain the desired ideal output waveform (a pure sinus), it is required to place an output filter that selects the fundamental or wanted component. Usually, in order to keep the size of the output filter reasonable, a low number of levels implies to operate the converter with a high switching frequency, whereas a low switching frequency implies a high number of levels. The THD of the output voltage of low commutation frequency switching converters can be improved by increasing the number of input phases, as suggested in [1] and [6]. The needed number of input phases depends mainly on the THD requirements on the output waveforms. To comply with the grid codes' constraints, the number of input phases is usually set to 20 and higher.

For direct converters, a high number of levels is obtained by increasing the number of input phases. In general, on the side of the source of the converter, it is not acceptable to have high frequencies in the spectrum of the current. A high switching frequency requires an additional input filter which might not be necessary with a low switching frequency combined with high number of levels.

### 1.3 Towards the proposed new converter

Most of the literature of the AG principle recommends using a direct frequency converter in order to get rid of the supposedly costly and dangerous DC storage component. In some applications this DC storage component plays a second role of energy reserve for a short duration. In the AG case, this short reserve is available from the inertia of the generator rotor. However reference [14] presents a back to back configuration in the frame of AG principle. The reference [14] suggests a special back to back three or five levels NPC in a low switching frequency (square mode), which shows excellent efficiency. However it requires a DC intermediary capacitor and an output filter. The AG literature about AG assumes here that a high switching frequency is not suitable for high power applications

because of too high commutation losses and because of the necessary input filter to decrease high frequency current harmonics that the generator cannot accept. The modeling of a poly-phased generator has been newly covered in detail by [43]. This reference will certainly help in assessing the constraints to observe in terms of current harmonics allowed into the generator stator to keep damper cage losses low and torque ripple in a reasonable frame.

With the given recommendation of direct conversion, no input filter and slow switching frequency, the NCC topology would be an eligible solution, provided that the input phase number is high enough. Usual NCC count up to 12 input phases (12 pulses NCC). The NCC is attractive and suitable for high power since it uses thyristors as valves. However, the NCC and its associated switching scheme, the Cosine Waveform Crossing (CWC), present one big disadvantage, i.e. reactive power consumption. More precisely, the CWC makes the input displacement factor of the input sources more reactive than the power factor of the grid. This usually implies an over sizing of the generator in term of apparent power. To get rid of this issue, it is suggested in [1], [2] and [3] to use a switching scheme, derived from CWC, which makes the input displacement factor equal to the load angle and, by the way, reduces the commutation number per output period compared to the CWC. In particular, [4], [7], [8], [9], [10] and [15] studies the implementation of this scheme using thyristors and only natural commutations. In the literature, this converter is called the NCMC (Naturally Commutated Matrix Converter) where the reference to the matrix converters is due to the matrix configuration of the valves of the NCMC (Fig. 1.2 top left). The natural commutations imply delaying some of the commutation instants, which limits the real application of the suggested slow switching scheme. The practical implementation of the NCMC is restricted to some lagging operating points only, which is of course not compatible with the requirement set by the AG principle. Indeed, a power plant must be able to deliver power with leading and lagging operating points, even within a restricted range, but at least unity power factor must be achievable. For those reasons, the NCMC should be discarded.

It comes out that recommendations about converter topologies are made and a certain direction is privileged but there are no satisfying practical converters for this direction that is studied, nor available. In response to the recommendations to use a direct converter with a given slow switching scheme and a high number of levels, a straightforward converter topology would be to replace the thyristors of the NCMC with transistors in order to get rid of the natural commutation limitations. This idea is indeed briefly mentioned in [15] as a future work. This leads to the proposed new converter, named gate-commutated "Poly-Phased Matrix Converter" (PPMC), which is shown in Fig. 1.2 (right) in a simplified schematic. The aim of the thesis is to investigate the PPMC topology and highlight its pros and cons. The detailed structure of this work is given earlier, in section 1.1. This work aims at clarifying the recommendations found in the literature about the converter topology choice, but does not pretend to be a tool to select the best converter topology for the AG application.

## **Chapter 2 - Poly-phased direct frequency conversion**

#### 2.1 Introduction

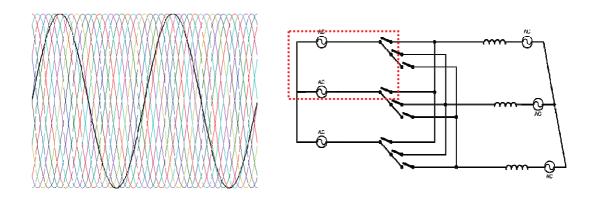

It has been said in the previous chapter that a new switching method was suggested in the literature, denoted here *slowCWC*. In order to give more insight and to show how to derive the slowCWC sequence this chapter addresses the synthesis of a sine waveform of a given amplitude and frequency from a set of *m* sine waveforms input with different, generally higher, frequency and amplitude. This is the poly-phased direct frequency conversion. Fig. 2.1 (left) illustrates the general problem of curve synthesis. Which input curve is to be selected at what time to follow a given target curve, and how to select it, are the basic questions to answer to perform the synthesis of the target curve (black curve). The possible sequences to synthesize the target are:

- Venturini's PWM modulation and its multiple derivate forms

- Minimum error sequence

- Cosine Waveform Crossing (CWC)

- slowCWC

The PWM and the *CWC* sequence belongs to the state of the art and are largely used in industrial applications. As stated in chapter 1, the PWM commutation sequences are discarded for the AG application and will not be exposed here. *CWC* and *slowCWC* are exposed and detailed in two sections of this chapter.

Fig. 2.1 – Illustration of direct frequency conversion and associated converter structure

The general structure of converter used for direct frequency conversion is given in Fig. 2.1 (right). Each output phase can be connected to any input phase. Generally the output is considered as a current source that should not be interrupted and the input is considered as voltage sources that should not be short-circuited. A PWM sequence does not require more than three input phases since the resolution of the output voltage or current is ensured by appropriated filters made feasible by the high switching frequency. The 'line-commutated'-like commutation sequences (CWC, slowCWC), i.e. sequences with commutation frequency being a close multiple of the input frequency, ensure the resolution of the output waveform by a sufficient input phase number, noted *m*. Whatever commutation sequence is used, PWM or line-commutated, the output current has to be commutated from one input phase (outgoing) to another (incoming). The commutation cell, the part of the circuit that contains both outgoing and incoming input phases, as highlighted in Fig. 2.1 (right), is a key concept to understand in order to say if a commutation sequence is feasible and working

properly. As a reminder or for clarity of this chapter, the next section briefly exposes the basic commutation cell principle and properties.

#### 2.2 Basic commutation cell

#### 2.2.1Transient response of commutation cell

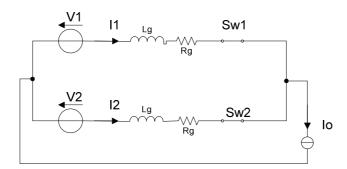

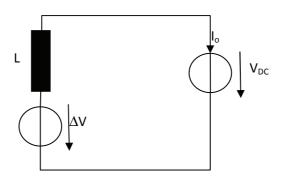

The commutation cell highlighted in Fig. 2.1 (right) is isolated from the whole converter circuit and drawn in Fig. 2.2. Again, the nature of the input and output source is considered voltage and current resp. They are real sources and have an internal impedance. This impedance will help the commutation process in some situations, in other situations it will be a problem to be addressed. As can be seen in Fig. 2.2, DC sources are used in this basic cell to represent the circuit during the commutation. For this approximation to be valid, the commutation duration must be short compared to the period of the input period. No precise numerical limits are given here since it depends on a lot of parameters.

Fig. 2.2 – Basic commutation cell with outgoing  $(V_1)$  and incoming  $(V_2)$  input phases

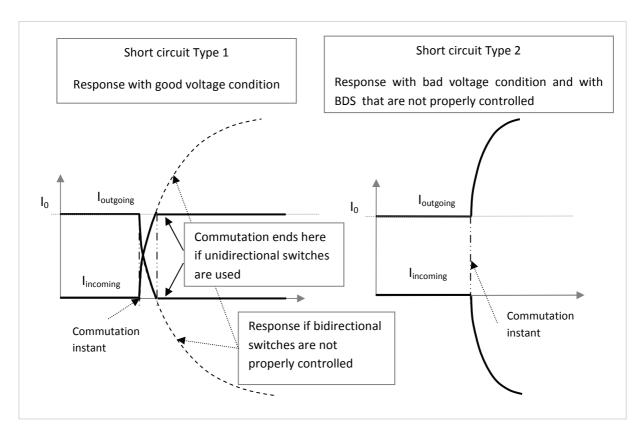

The closing of one switch does not lead to any violation of the basic rules of power electronics. However, when opening a switch which was conducting a current, one must ensure that there is a free-wheel path for this current, otherwise we do not respect one interconnection law. This free-wheeling path is normally ensured by closing the incoming switch (SW<sub>2</sub>, new generator phase). As switching (on and off) duration is not instantaneous both outgoing and incoming sources are short-circuited. The short-circuit between two real voltage sources composed of one ideal voltage source plus one series internal impedance (resistive inductive), lead to a short circuit current  $I_c$ = $\Delta V/(2R)$ . Generally R is such that  $I_c$ >> $I_o$  The time constant of the transient phenomena just after the short circuit of both input phases is L/R.  $\Delta V$  is the voltage difference  $V_1$ - $V_2$ . There are two possible responses to this short-circuit, which are illustrated in Fig. 2.3 and commented here.

If  $\Delta V$  and  $I_o$  are both positive or negative, then the situation is not helping the commutation (increase of current in outgoing phase, decrease of current in incoming phase). However if  $\Delta V$  and  $I_o$  are of opposite signs, the outgoing current decreases and the incoming current increases. Hence, the current in the outgoing phase will cross zero. If using unidirectional switch with a blocking capability at current zero crossing, this process will automatically stops and the desired commutation is done. It is called a **natural commutation** which is largely used in NCC. The basic commutation cell is a very simple model of the input source with a given fixed internal impedance (L and R). In reality, especially

if the input source is a SM or ASM, the internal impedance to consider is not necessarily constant and can vary with time. In this regard there is a more detailed analysis about proper conditions for natural commutations in [3] but for the present study in this work, the above condition will be considered as good enough for the case studied.

Fig. 2.3 – Types of short circuit between two input phases of the basic commutation cell

#### 2.2.2 Nature of switches

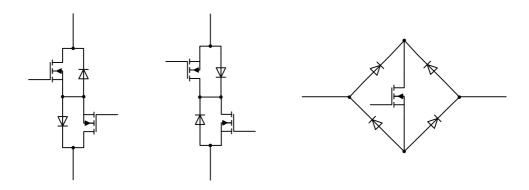

Historically, the high voltage switches were only achievable with thyristors. When thyristors are employed, the blocking capability during current reversal is intrinsic. Thus natural commutation is possible without control. it is besides not necessary for security of the commutation to know the sign of  $\Delta V$  before starting the commutation. When  $\Delta V$  is positive, nothing will happens since the thyristor cannot start conducting a negative current and it is negative bias. However when thyristors are used it is required to implement a management of the zero-crossing of the load current (circulating or circulating-free current are two possibilities). Nowadays, it is more and more possible for high power to build turn-off capable bidirectional switches (BDS). They are build from transistors, usually, IGBT or IGCT arranged with power diodes as depicted in Fig. 2.4. There are several combinations which all have advantages and disadvantages. To choose the appropriate combination, one should assess the main trade-off of number of switches vs. number of pn junctions in the current path, which influences the conduction losses. When such transistor-based BDS are used as valves for the frequency converter, the control must be appropriated to avoid short circuit of type 2 (see Fig. 2.3) between both input phases involved in commutation cell . Besides, depending on the gating signals

control, the reverse blocking capability is not guaranteed. It is however not necessary to control the zero crossing of the load current.

The two left most composition of transistor-based BDS of Fig. 2.4 (common source and common drain) offer the possibility to independently control each direction of the current however the control of the firing signals is more complicated than the diode bridge composition (right most in Fig. 2.4). For the common source or drain configuration, a special gating signals control can guaranty the automatic blocking capability at current reversal, which secures the commutation and avoids short circuits of type 2 (see Fig. 2.3). Control of commutation with real BDS in matrix converters are well described in [20], [21] and [24]. The common source configuration is mostly used in matrix converters. With this BDS configuration, there are four gating signals involved in one commutation which are described in the next paragraph.

Fig. 2.4 – Transistor-based BDS: common source or emitter, common drain or collector, diode bridge (left to right)

#### 2.2.3 Four steps commutation rule

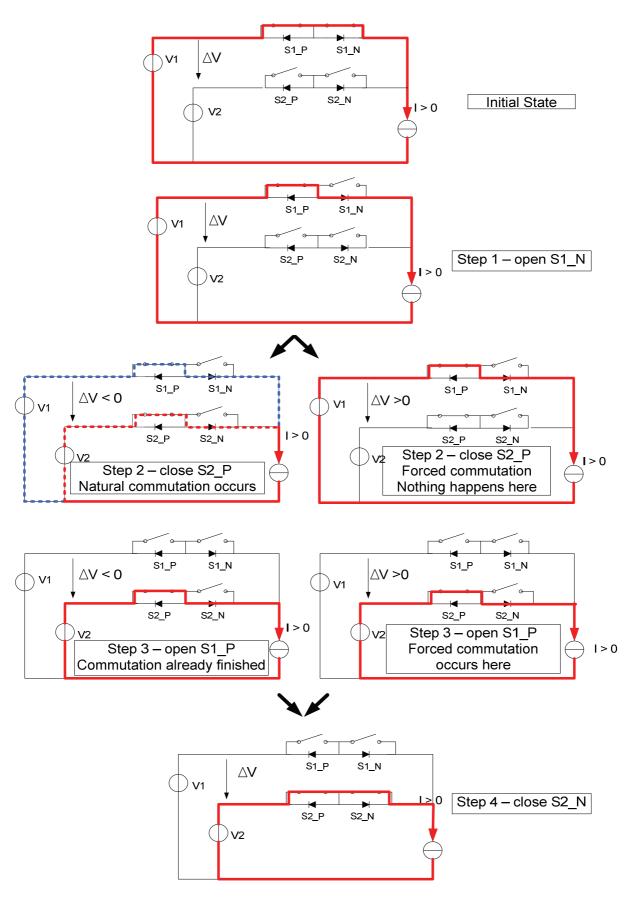

Fig. 2.5 describes the four steps commutation rule, as described in [21] that will be used later in this work. The first step ensures blocking capability at current zero crossing. Step 2 prepares the free-wheeling path and commutation starts at this step if the conditions for natural process are met. If not, nothing happens. Step 3 finishes the commutation. In case of natural commutation, noting happens here provided that the delay between step 2 and step 3 was long enough to let the natural process finish. In case of forced commutation, the current is cut off by the switch itself. Consideration of the source impedance is mandatory here for practical implementation of forced commutation. Step 4 ensures the automatic current reversal through the switch in case the load current crosses zero during the conduction period of the phase  $U_2$  of Fig. 2.5.

Fig. 2.5 – Four steps commutation rule of the basic commutation cell

## 2.3 Minimum error sequence

Before presenting already existing commutation sequences or modulation for direct AC conversion, this section shows one possibility which is very intuitive. Switches are assumed to be ideal, bidirectional and have turn-off capability.

### Minimum error principle

Very intuitively, one would recommend to build the target curve from segment of the whole set of available input voltages, by each time, selecting the curve that is the closest to the target one. If the number of input phases is high enough we can get a quite good approximation of the target curve.

Fig. 2.6 - Output waveform of the minimum error sequence

Fig. 2.6 shows the output (bold blue) obtained when synthesizing the target curves (black) with the "minimum error" sequence from a set of twelve input phases. This algorithm delivers at first sight a quite good output curve, with a good shape. However, for further qualification of curve quality within this work, it is necessary to have criteria on which to base the assessment. Here are a few criteria for quality of a commutation sequence:

#### Assessment criteria

#### - Output THD

The output THD is acceptable, compared to the other similar sequence presented later. The THD is independent of the frequency ratio, as can be observed in Table 2.1. There is no mathematical proof of this independency to frequency ratio for this minimum sequence. Only the numerical analysis of this sequence's waveforms shows this independency. The THD values are computed with a Matlab® script that generates the theoretical waveforms and then computes the frequency spectrum of the ideal output waveforms with an FFT algorithm. THD are deduced from the frequency spectrum. Table 2.1 gives a few numerical values:

Table 2.1 - Output THD of minimum error sequence

|                 | 98Hz to 50Hz | 62Hz to 50Hz |

|-----------------|--------------|--------------|

| 12 input phases | 11%          | 11%          |

| 24 input phases | 5%           | 5%           |

## Degree of freedom

The degree of freedom here is complete, both frequency and magnitude can be modulated

## - Commutation frequency Higher than a line-commutated sequence but lower than a PWM sequence

- Type of commutation (hard/soft)

Mix of both, statistically 50% each

- Complexity of algorithm

Easy. It is a comparison between the set of input curves and the target.

#### - Input THD

Fig. 2.7 represents the time evolution of the index of the input phase connected to the output. There are different commutation frequencies and the index jumps is always a different value, jumping forward and backward. In practice, the input is either multi-phase transformer or a generator, hence the input source has limitation in the acceptable frequency of the input current to guarantee its proper working. As can be qualitatively deduced from Fig. 2.7, the spectrum of an input current would contain some high frequency harmonics that are surely not acceptable for a generator as input source. High input current harmonics lead to high circulating currents in the damper cage and high ripple torque.

Fig. 2.7 - Input phase index evolution of minimum error sequence

## 2.4 Cosine Waveform Crossing (CWC) sequence

Historically, the only switches available for high power, which usually means also high voltage, were thyristors. As seen in section 2.2, with thyristors it is only possible to perform natural commutations. The *Cosine Waveform Crossing (CWC)* sequence has been then especially developed for thyristor-based line commutated converters, named Naturally Commutated Cyclo-converter (NCC). The *CWC* is presented here because the commutation sequence that will be under study along this work, called *slowCWC*, is very near to the *CWC*. A very well known reference about *CWC* can be found in [5]. Fig. 2.8 (top and bottom) shows two ideal waveforms of the *CWC* sequence for two different output power factors. Intuitively, one can observe that the *CWC* is the minimum error sequence with restriction to natural commutation only.

Fig. 2.8 – Output waveform of CWC sequence with unity power factor (top) and 0.85 lagging power factor (bottom)

## CWC principle

The CWC sequence is itself derived from the phase-controlled rectifiers control sequence. The DC mean output voltage of such a phase-controlled rectifier depends on the angle  $\alpha$  (the phase of the control) and is given by Equ. 2.1.

Equ. 2.1

$$V_{omean} = Acos(\alpha)$$

where A is the magnitude of the generator phase scaled down by a coefficient smaller than one, that depends on the number of input phases. Fig. 2.9 shows the output of a phase controlled rectifier and the place of the angle  $\alpha$ .

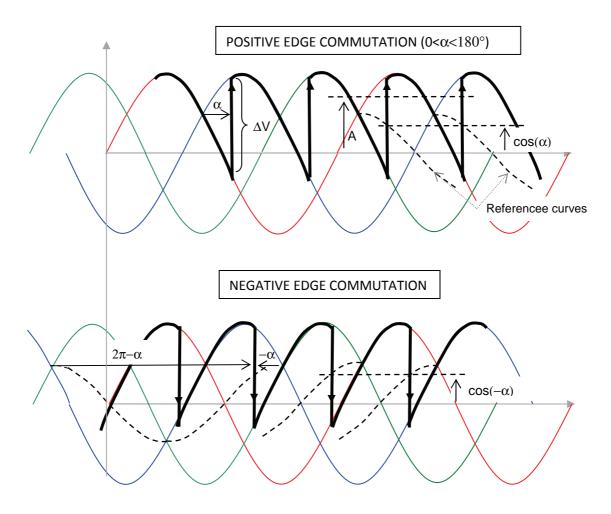

Fig. 2.9 – Positive and negative edge type waveform of a phase-controlled rectifier

As can be seen in Fig. 2.9, for the same  $V_{Omean}$  there are two possible waveforms types denoted by positive edge and negative edge, where the edge refers to the jumps from the outgoing phase to the incoming phase. As this rectifier works with natural commutation, as exposed in section 2.2, the requirement is that  $\Delta V$  and the load current have opposite sign, hence depending on the load current sign, either the positive or the negative edge must be used to produce the desired  $V_{Omean}$ . For a similar  $V_{Omean}$ , Equ. 2.2 (left) gives the relation between the  $\alpha$  of the positive edge  $(\alpha_{pos})$  and the alpha of the a negative edge  $(\alpha_{neg})$ . The idea to create a sinusoidal waveform at the output is simply to modulate the phase angle  $\alpha$  along the time. If  $\alpha$  increases linearly with the time, as given by Equ. 2.2 then  $V_{Omean}$  is a sine waveform of desired frequency  $F_o$ . Theoretically there are no limitation on  $F_o$ , but in practice, the fundamental of the output waveform should remain the dominant component, hence usually  $F_o < \frac{1}{3}F_{in}$ , with  $F_{in}$  being the input frequency.

Equ. 2.2

$$lpha_{neg} = 2\pi - lpha_{pos}$$

$lpha(t) = 2\pi F_o t$

As the current is also be sinus, half of the output waveform will be of positive edge type and the other half of negative edge type. In practice, there are two half bridges, one being dedicated to the positive load current and the other to the negative load current. As visible in Fig. 2.9 for the same  $V_{omean}$ , instantaneous voltage of both bridges are not equal. Both positive and negative bridges are commanded to have the same mean output voltage but only one has its firing pulses enabled, depending on the sign of the output current (target value). There is also the possibility to use a midpoint inductor that reduces the circulating current between both bridges if their firing pulses are simultaneously enabled. With the circulating current mode, the zero crossing management of the load current is not necessary.

According to Fig. 2.9, a commutation must occur each time that the target output voltage  $V_{omean}$  crosses a reference voltage, which is  $(v_{in,k}+v_{in,k+1})/2$ , which is the mean between the conducting input phase and the next one. Fig. 2.10 (top and center) shows half a period of a target output waveform  $V_{omean}$  waveform with superimposed portion of the real converter output waveform with positive edge and negative edge type for both possibility of load current polarity (here output power factor is unity). To produce this output waveform  $\alpha$  must vary linearly back and forth between 90° ( $V_{omean}=0$ ) and 0° ( $V_{omean}=A$ ), as depicted in Fig. 2.10 (top). As a consequence of the back and forth modulation of the phase angle  $\alpha$ , the output waveform of the CWC has two distinct commutation rates, that can be easily observed in the ideal waveform of Fig. 2.8. The construction of the CWC output waveform can be translated into a spatial vector diagram where the reason for those two commutations frequencies becomes very clear.

Fig. 2.10 - Type of edge and commutation frequency of CWC sequence

Normally, there should be m vectors representing the m input phases which vectors are rotating in the counter-clock wise direction with a given speed  $\omega_g$ . The spatial vector diagrams of Fig. 2.10 (bottom) are however drawn for two distinct commutation instants, denoted by  $t_1$  and  $t_2$  and only the involved two input phases are represented. The target output voltage  $V_{omean}(\alpha_{pos})$  can be represented by a spatial vector too. Now depending on the sign of the derivative of  $\alpha_{pos}$ , this spatial vector rotates in a counter-clock-wise or clock-wise direction, for an increasing or decreasing slope of  $\alpha$  resp. The rotating speed of this target vector is the desired output pulsation  $\omega_o$ . According to the

CWC sequence, a commutation occurs at a crossing of the reference curve and the target, as depicted in Fig. 2.9. In the spatial vector diagram, this means that a commutation occurs each time the angle difference between the target and the conducting input phase is greater than  $\pi/m$  because the reference vector is in the middle of the conducting input phase and the next one. This is illustrated in the bottom left diagram of Fig. 2.10. Hence depending on the direction of the rotation of the target spatial vector which is similar or opposite of the input vector rotation, those crossings will occurs either proportionally to the sum or the difference of  $\omega_{\rm g}$  and  $\omega_{\rm o}$ . This gives rise to both commutation frequencies of the CWC sequence as expressed in Equ. 2.3.

Equ. 2.3

$$F_{C,fast} = m(F_{in} + F_{out}) \qquad F_{C,slow} = m(F_{in} - F_{out}) \quad [Hz]$$

The development is similar for negative edge type, see Fig. 2.10 (bottom right). The proportion between fast and slow depends on the power factor. One can then deduce the mean commutation frequency as expressed in Equ. 2.4.

Equ. 2.4

$$F_{C,mean} = m(F_{in} - (1 - pf)F_{out})$$

where *pf*, the power factor of output, is accounted positive if the load current lags the output voltage.

#### Assessment criteria

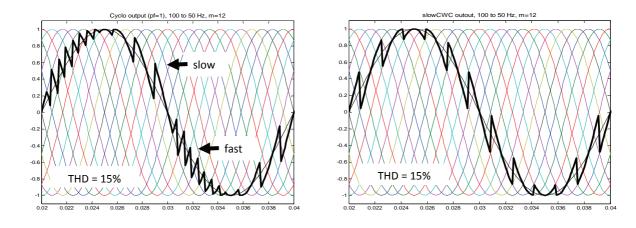

#### - Output THD

The output THD is also acceptable, compared to the other similar sequence presented later. The THD is independent of the frequency ratio. Table 2.2 gives a few numerical values, also computed with the similar Matlab® script as for the minimum error sequence:

98Hz to 50Hz 62Hz to 50Hz

12 input 15% 15% phases

24 input 7% 7% phases

Table 2.2 – THD of CWC output waveform

Compared to the minimum error sequence, those THD values are a bit higher for equivalent number of input phases.

#### Input THD

Fig. 2.11 represents the time evolution of the index of the input phase connected to the output. Here also, the two distinct commutation frequencies can be observed. Indeed, there are two distinct slopes of the index time evolution. The index normally jumps forward with unity steps except when switching from one bridge to the other (positive to negative or vice versa). Compared to the minimum error sequence, the input quality is better and there are surely less harmonics. The increase of the output THD is compensated here with better input quality. However it will be shown later that the input displacement factor is not satisfying.

Fig. 2.11 - Input phase index evolution of the CWC sequence

- Degree of freedom

The degree of freedom here is complete, both frequency and magnitude can be modulated.

- Commutation frequency

Fully determined. It depends on the output power factor, on the difference between input and output frequency. Lower than the minimum error sequence.

- Type of commutation (hard/soft)

100% soft because restrictions to natural commutations

- Complexity of algorithm

In principle easy but there are technical issues that are listed below

## Technical issues of CWC

The CWC sequence is used for NCC which uses thyristors as valves. There are some technical difficulties for practical realization of a NCC that are to be mentioned here:

- Zero crossing or bank Selection

- The valves are composed of two anti-parallel thyristors acting like two half bridges, one for each half cycle of the load current (no circulating current configuration). It is not an easy task to find the right moment when to select the time to switch from one bridge to the other. It is especially difficult if the ripple in the current is strong or in case of a leading power factor. The usual dead time at the zero crossing leads to distortion of the load current. Method and handling of that problem can be found in [5].

- Unsuccessful commutations

- In reality, a natural commutation lasts a certain time or angle, often denoted as  $\mu$  overlapping angle. An unsuccessful commutation is a commutation that starts in correct conditions but during which, or shortly after, the driving voltage  $\Delta V$  changes its sign. The current derivatives in each active phase reverse as well. Consequently, the current of the outgoing thyristor will not cross zero and the commutation cannot finish properly. The supposed outgoing phase will then continue to conduct the load current until a proper action is taken to mitigate this phenomenon. Proper action to take when entering a short circuit state will not be discussed here but are described in [5] and especially [13]. The location of commutation for which this danger could appear starts with  $\alpha_{\text{pos}}$  near the 180° limits, that is, when the converter acts as a inverter. For this risk to appear, the power factor has to reach

low values (lagging) near 0. Of course the precise determination of this depends on numerical values of  $\mu$ . It is usual to find a practical limit to  $\alpha_{pos}$  of 150°, which correspond to a limitation of power factor of 0.5 lagging. Similarly the limit imposed on  $\alpha_{neg}$  to avoid unsuccessful commutation is 210°.

- Reverse recovery phenomenon of thyristors

- Thyristors do not turn-off as soon as the current reverses but need a recovery time from the instant of zero crossing to eliminate accumulated charges in their pn junction. The consequence is that they effectively turn off when the current is already negative. The precise determination of that value is complex and beyond the scope of this chapter but it is usually not negligible and the current can reach a non negligible opposite value when the device turns off. There is usually an inductive component involved in the leg where the device turns off and this leads to voltage surge. Snubber is required to limit the dv/dt and the peak value of the surge. Also, the thyristor after having turned off needs to be impressed a negative voltage for a given duration before a forward can be reapplied otherwise the thyristor might fire again itself. This is usually ensured in normal operating mode of a NCC but this is not the case of leading power factor operating mode. Particular care must be paid for leading power factor when using a NCC.

- Unsymmetrical input phase connection & multiple feeding of network phase

With the CWC sequence, for a three phase load, there are instants when a given input phase

is selected to feed two load phases simultaneously. The issue is an overload of the given

input phase which could be a problem. Also, the input source is never connected in a

symmetrical configuration. For a generator, this unbalanced mode might be a drawback and

might inject current harmonics that lead to losses in the damping cage.

# 2.5 The *slowCWC* sequence

# 2.5.1 Principle of the slowCWC sequence

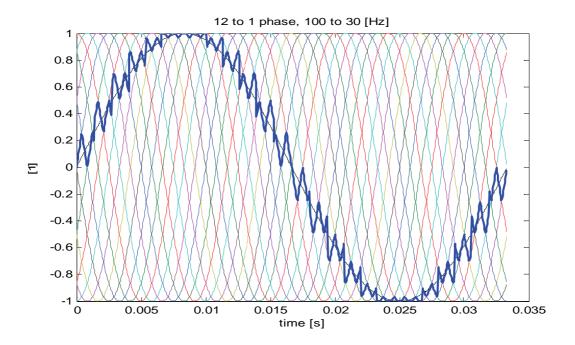

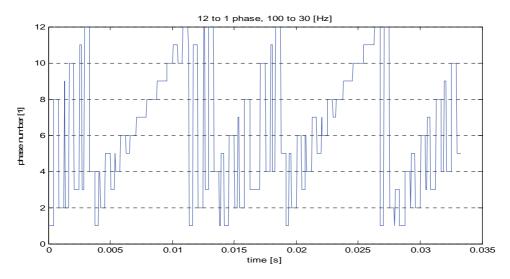

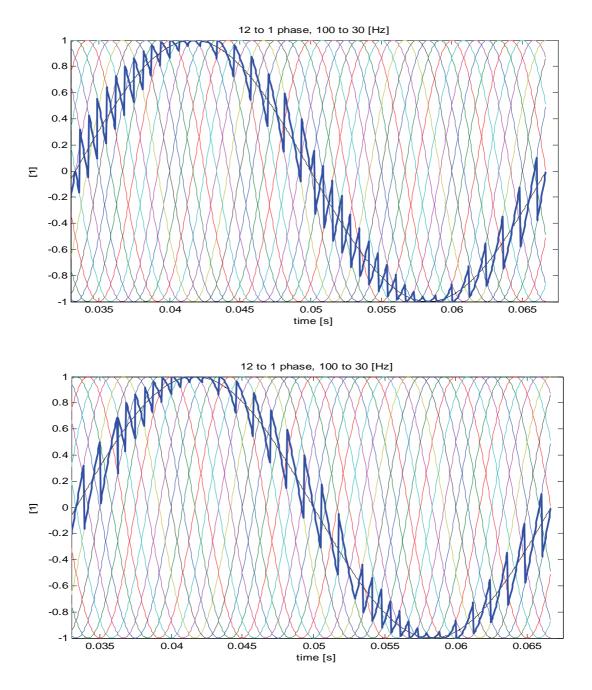

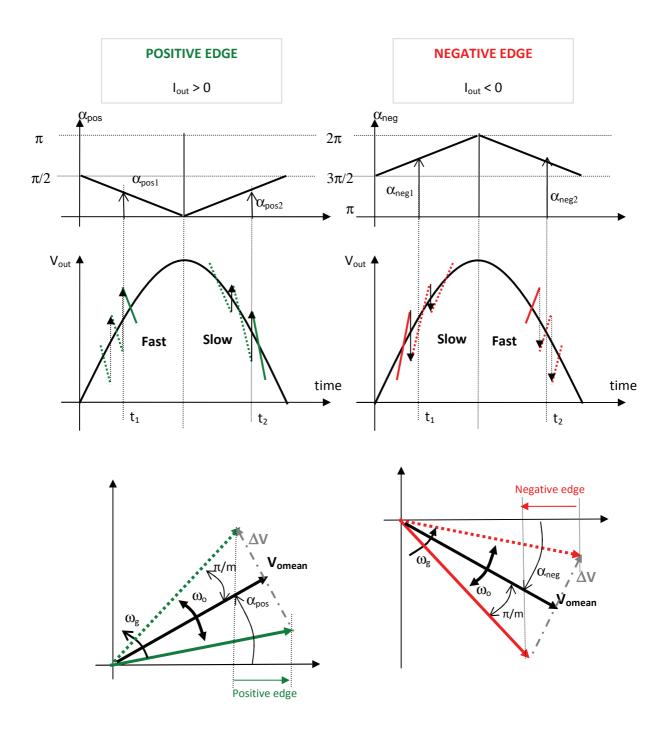

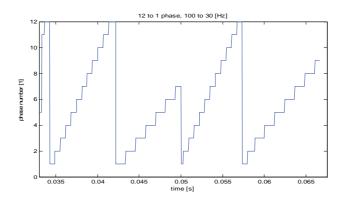

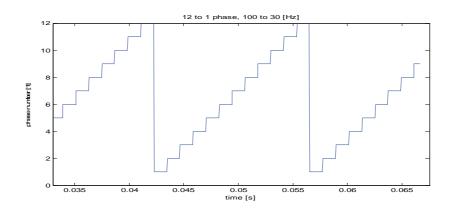

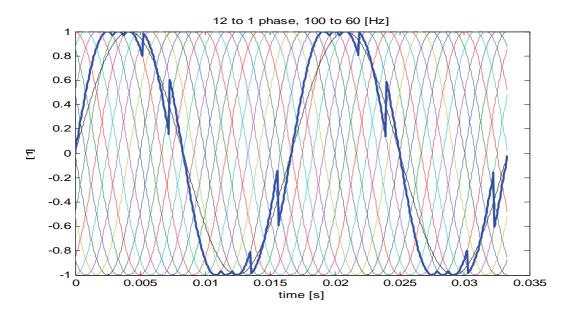

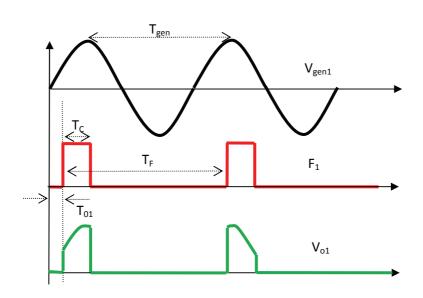

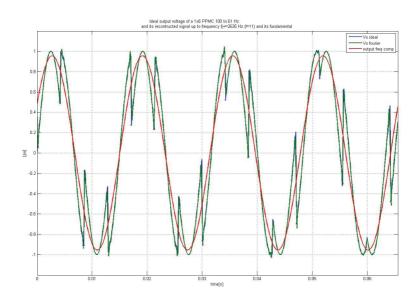

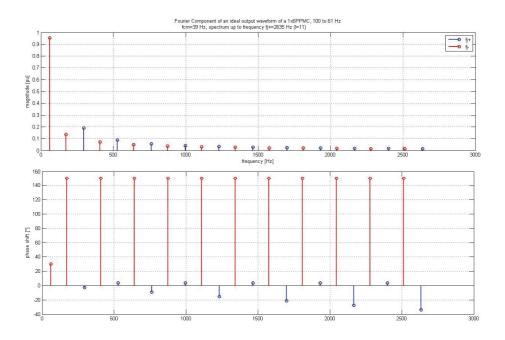

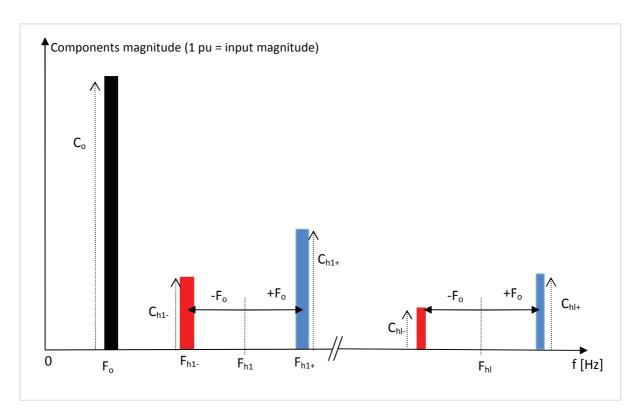

The *slowCWC* sequence is very similar to the CWC presented in the previous section. The *slowCWC* sequence, as introduced in [1] and [2], suggests to follow the output wanted component **only** with the slow switching rate of the CWC scheme, that is  $F_{C,slow}$ . Fig. 2.12 compares a waveform of CWC (left) and a waveform of the *slowCWC* sequence, in order to clearly and intuitively understand the similarities of both types. In Fig. 2.13, shows the time evolution of the input phase index. Here also, the unique switching frequency can be observed when compared to Fig. 2.11.

Fig. 2.12 - Ideal output voltage (bold) of cyclo-converter (left) and slow switching scheme (right)

Fig. 2.13 – Input phase index evolution of the slowCWC sequence

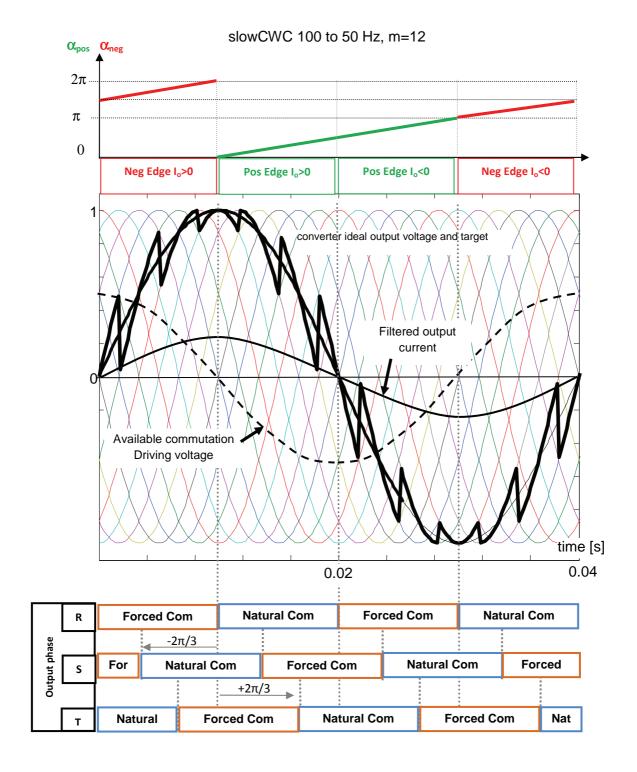

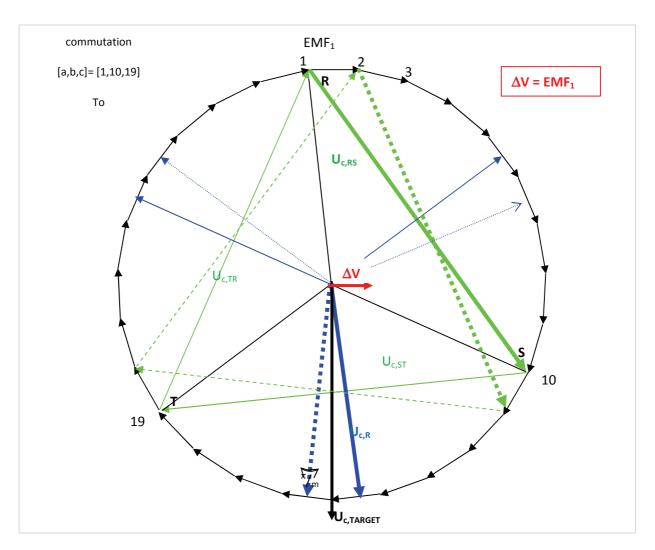

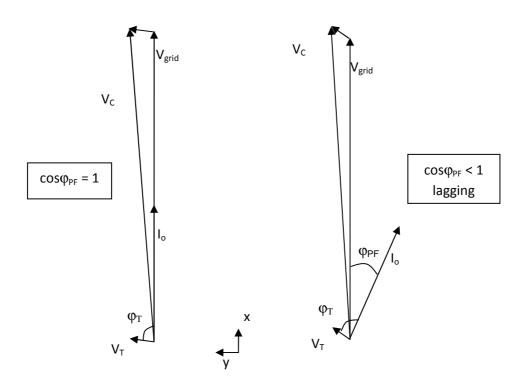

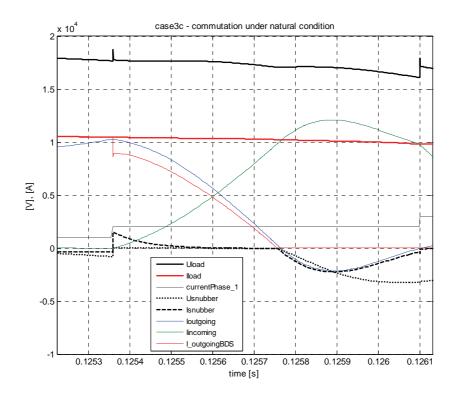

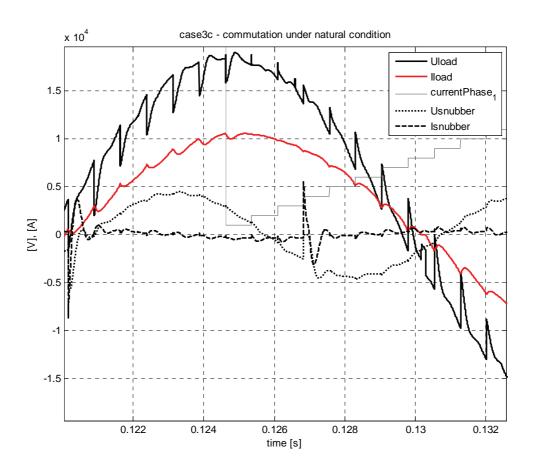

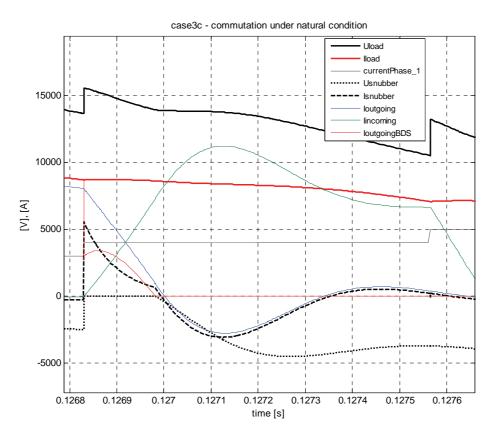

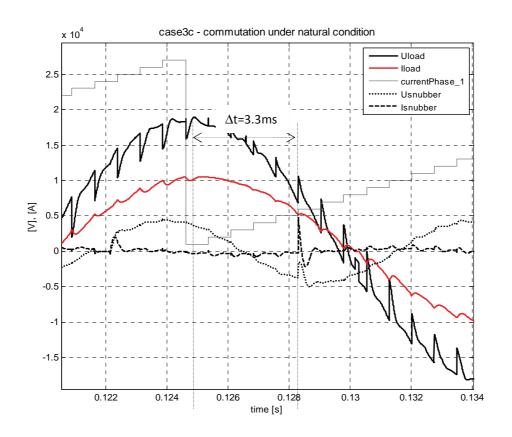

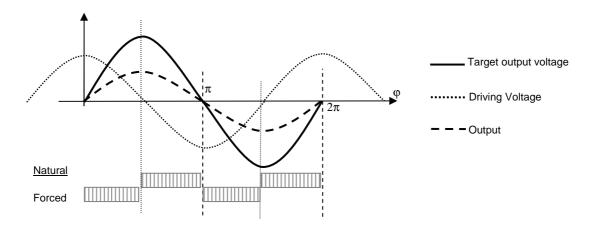

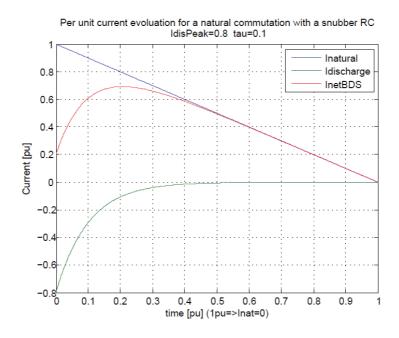

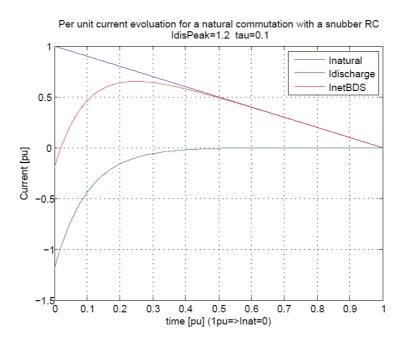

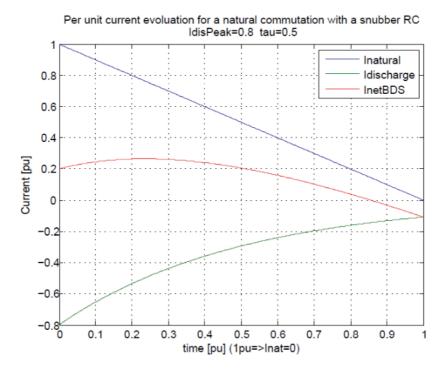

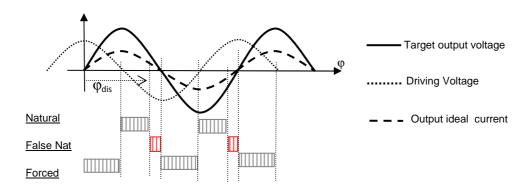

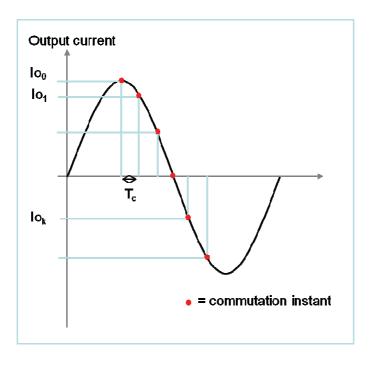

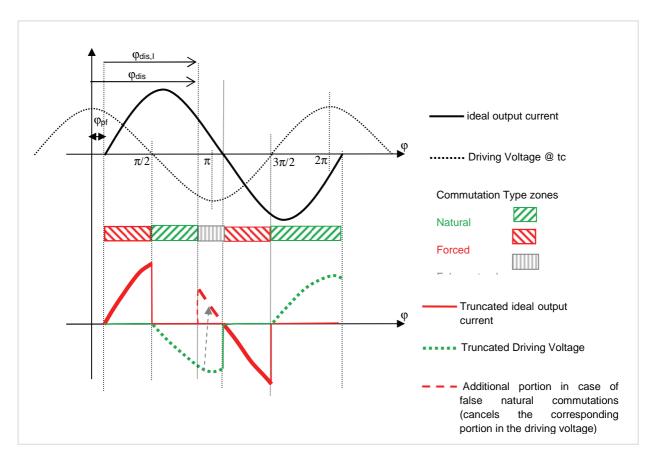

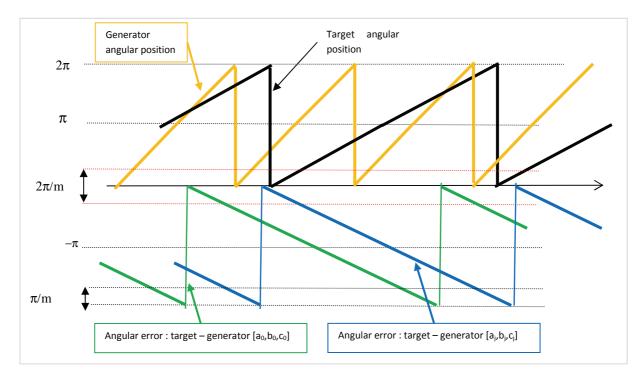

Determination of commutation instant can be done similarly as CWC with the phase angle  $\alpha$  or in the spatial vector plane. As can be observed in Fig. 2.14, only positive slopes of  $\alpha_{pos}$  and  $\alpha_{peg}$  are used for the slowCWC, which guarantees the slow commutation frequency. Consequently, the edge type (positive or negative) is not always compatible with the sign of the output current which implies that some commutations do not respect the power requirement to be natural and must be forced. This sequence is only feasible if the available valves are turn-off capable. Fig. 2.14 shows the zones of forced and natural commutations for a unity power factor. The forced commutation zones appear where the sign of the edge type (positive or negative) does not correspond to the load current sign. For other power factor, the width of the commutation and natural zone will vary in a complementary manner. This varies linearly with the power factor angle  $\varphi_{PE}$ . For a 90° lagging phase angle, there will be 100% of natural commutation. Similarly, for a 90° leading phase angle, there will be 100% forced commutations. In Fig. 2.14, the target output voltage is a sine waveform with a frequency  $F_{out}$ . The commutation driving voltage,  $\Delta V$ , is the voltage between two generator phases that allows commuting the currents from the outgoing to the incoming phase. From the spatial vector representation of Fig. 2.10 it can be shown that  $\Delta V$  at commutation instant  $t_c$  can be represented by a sine waveform of same pulsation as the target curve, but with a phase shift of  $+\pi/2$ . The magnitude of  $\Delta V$  depends on the input phase number. The trigonometric relation that links  $\Delta V$  and input phase magnitude will be presented in chapter 3. In Fig. 2.14, the commutation type zone of the corresponding two other output phase S and T of the converter are also represented. This shows that, for this unity power factor, there are moments during which there are two forced commutations and one natural commutation, and some other moments where there are two natural commutations and one forced. For this to be valid, natural commutations must be enabled by the control of the gating signals, i.e. delay between step 2 and step 3 must be set long enough to let the natural commutation proceed.

Fig. 2.14 - Driving voltage in function of commutation instant along the target output voltage

# 2.5.2 Pros and cons of the *slowCWC* sequence

Advantages of slowCWC over CWC

• Lower commutation rate with equivalent output THD For the slow switching scheme, the mean switching frequency is obviously  $F_{C,mean} = F_{C,slow}$ . The gain in commutation number per output period between CWC and slowCWC can be relevant. For example at unity power factor with a frequency ratio  $F_o/F_{in} = 0.5$ , slowCWC uses 50% less commutation than CWC for a similar output THD.

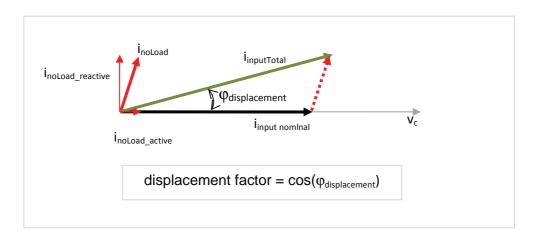

#### • Zero input displacement factor of the converter

As will be shown in the next section about waveform spectrum properties, the converter is transparent in term of reactive power. It means that the input displacement factor of the converter is identical to the load power factor. The converter with *slowCWC* does not introduce an additional lag between the voltage and current fundamental of the input phases, as opposed to the NCC which can introduce up to an additional lagging angle of 30°.

#### Technical benefits

Technical benefits will be detailed when introducing the PPMC in chapter 3 but the main advantages compared to the NCC is that there is no bank selection or zero crossing management (or much easier) and there are no danger of unsuccessful commutation because the BDS are and must be fully controllable (on and off).

#### Drawbacks of slowCWC

#### Forced commutation

As will be detailed in chapter 3 and 4, the forced commutation introduces commutation losses in the switches and requires protection hardware to limit voltage surge due to inductive components in the commutation loop.

#### No modulation depth

Due to the nature of *slowCWC* sequence there is no choice in the magnitude of the output voltage whereas with CWC this one can be varied by varying the magnitude of the target curve in the waveform crossing algorithm. However in our application, the voltage magnitude will be controlled via the excitation of the generator. This will imposes dynamic limitation when it comes to current control and difficulties in designing the current controller.

#### Technical issues

Availability and price of turn-off capable switches (IGBT's, IGCT's) for equivalent voltage/current rating with thyristors. Chapter 4 will analyze the consequences of additional losses due to the use of snubber circuits.

# 2.5.3 Note about slowCWC limited to natural commutations

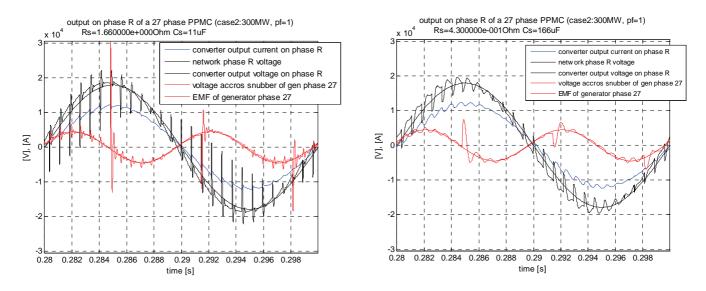

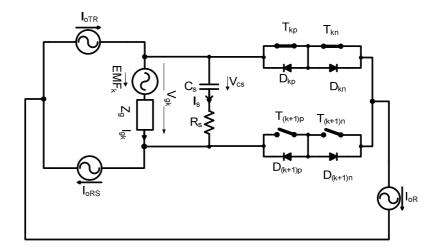

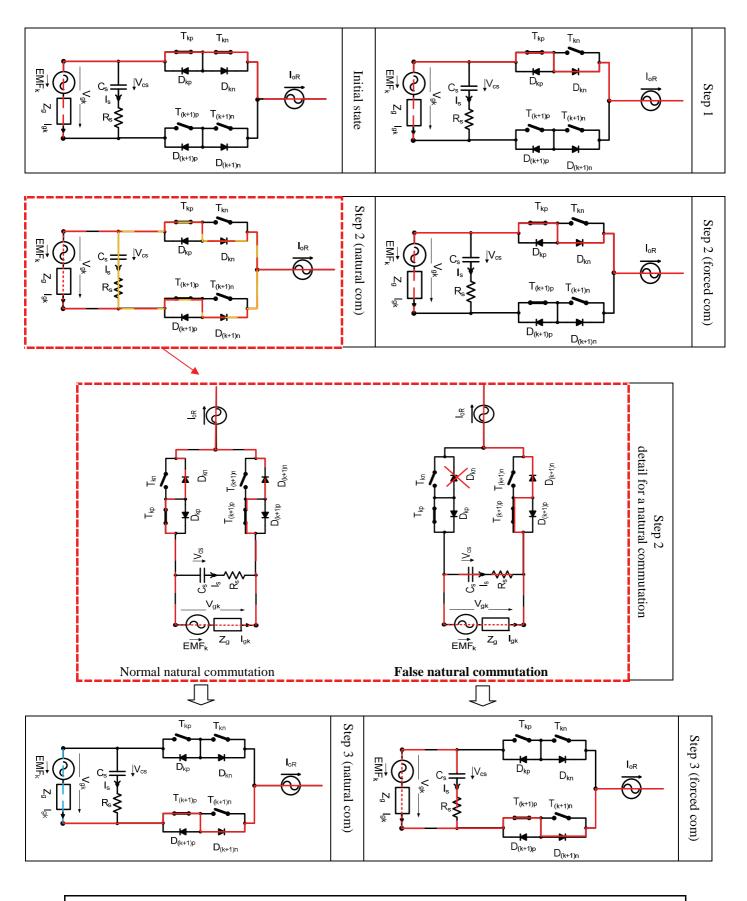

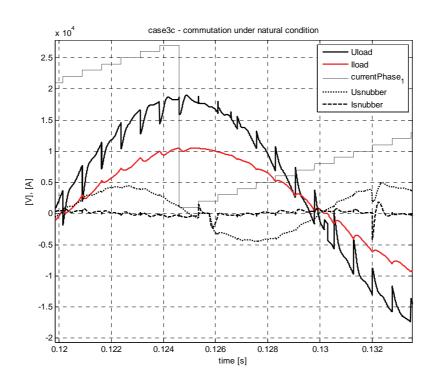

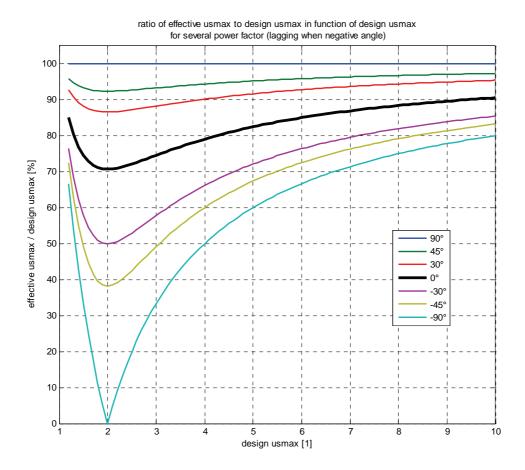

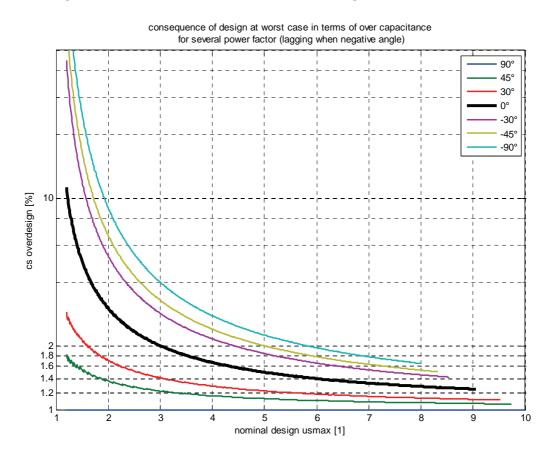

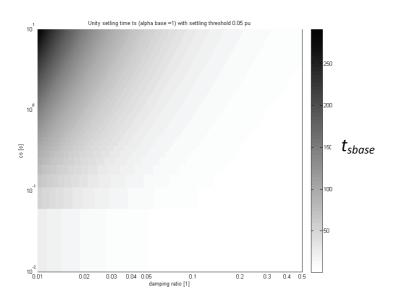

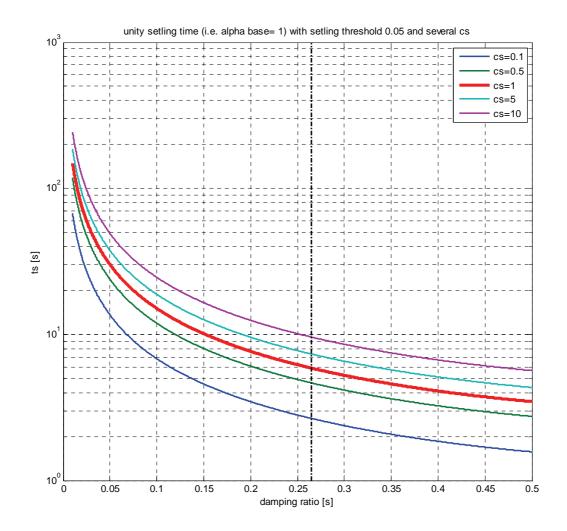

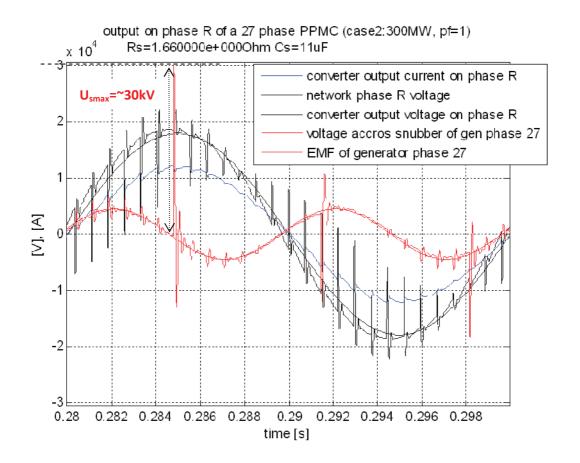

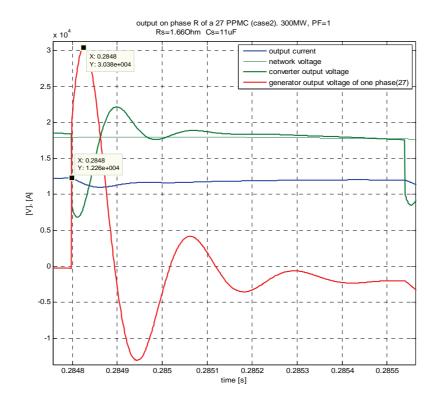

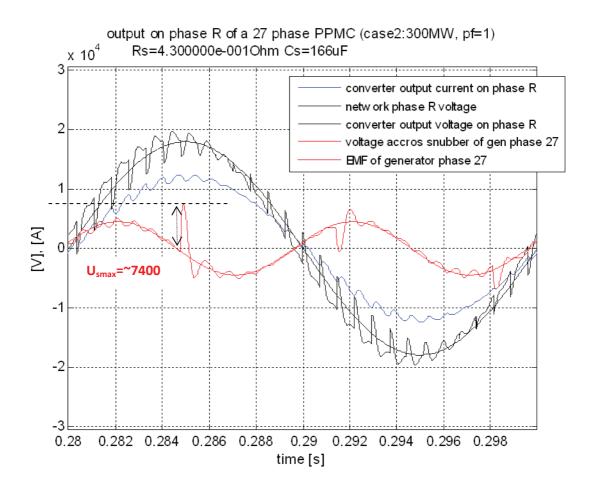

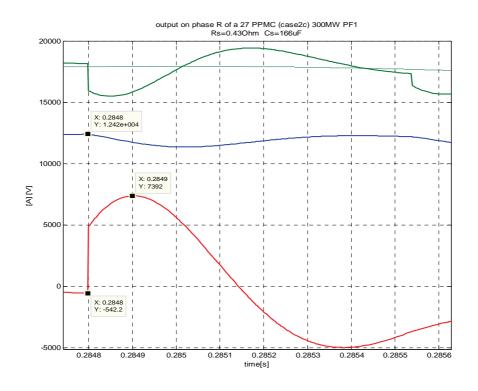

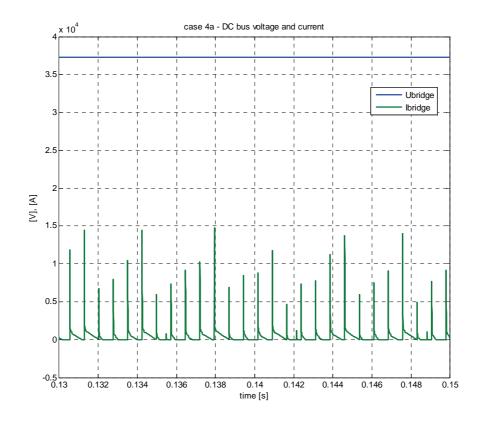

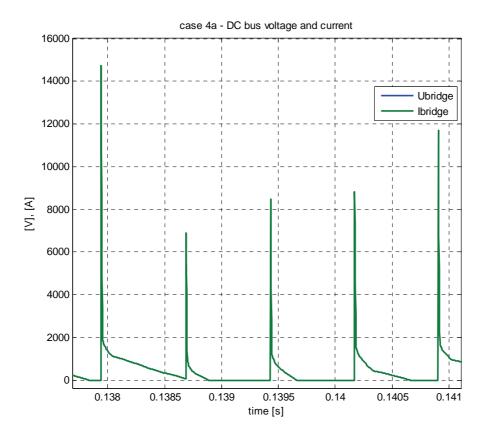

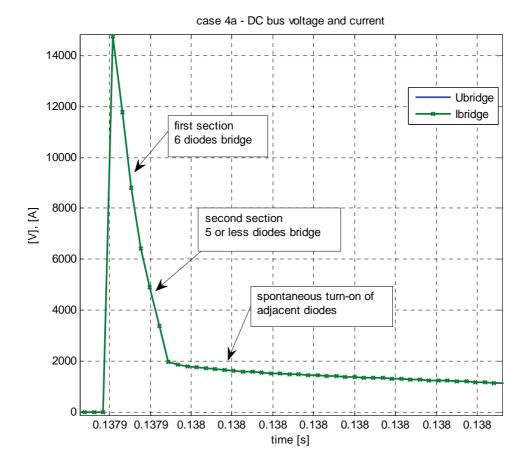

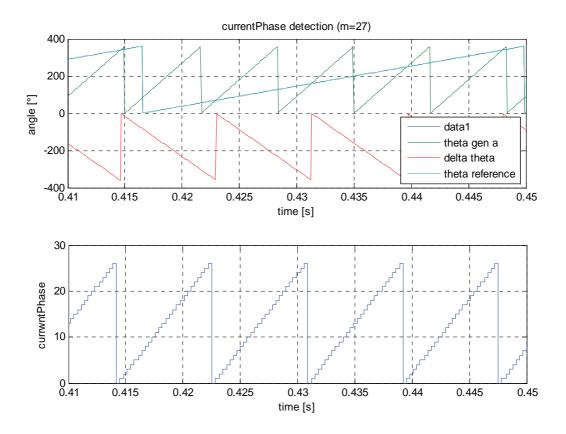

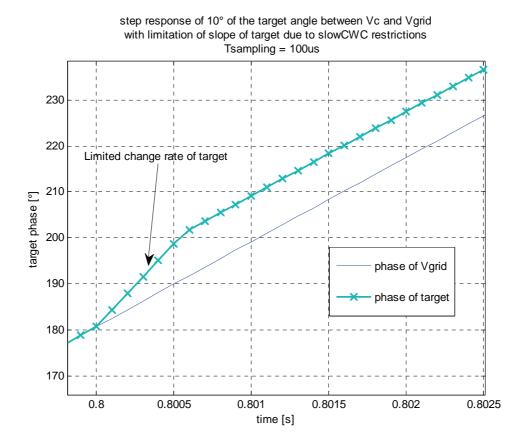

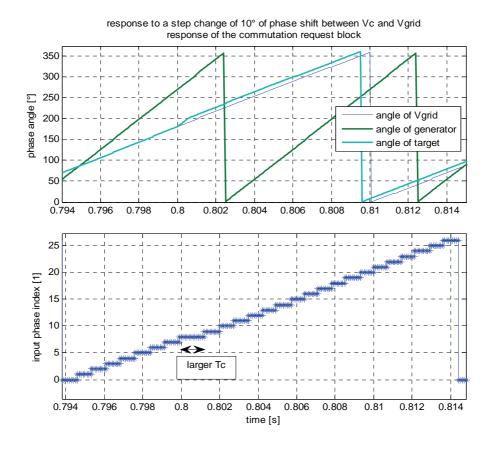

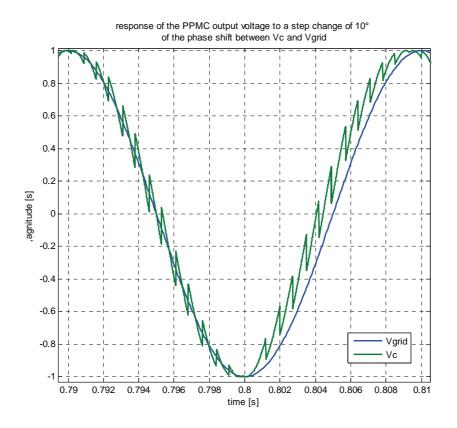

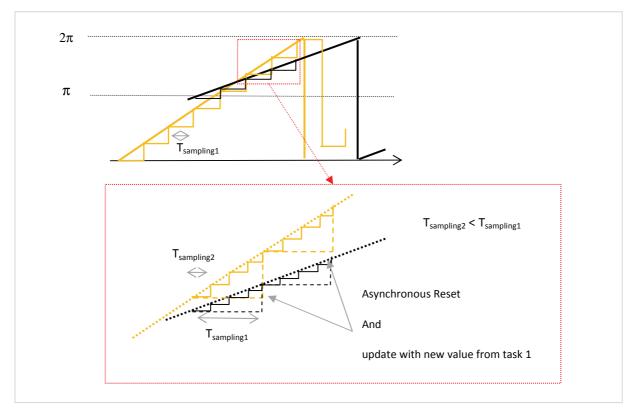

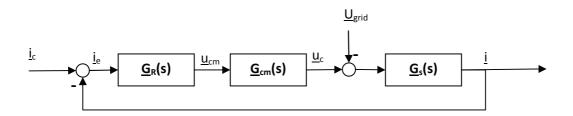

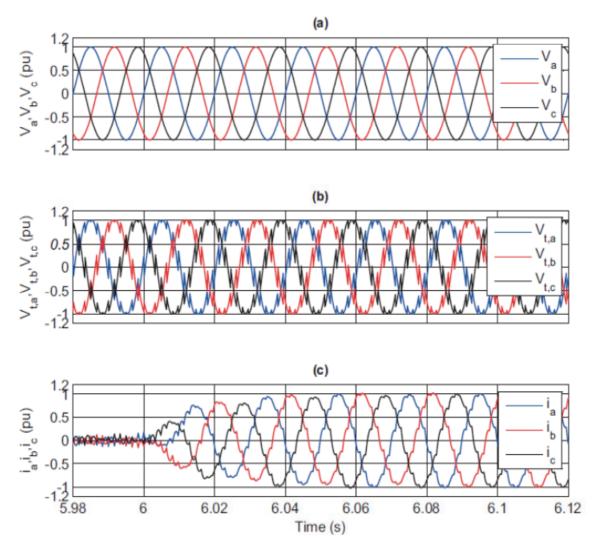

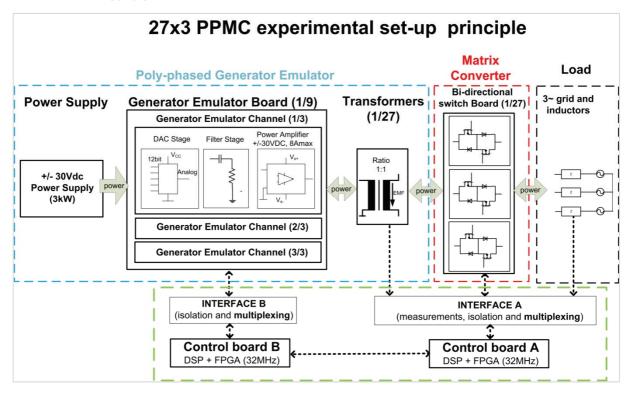

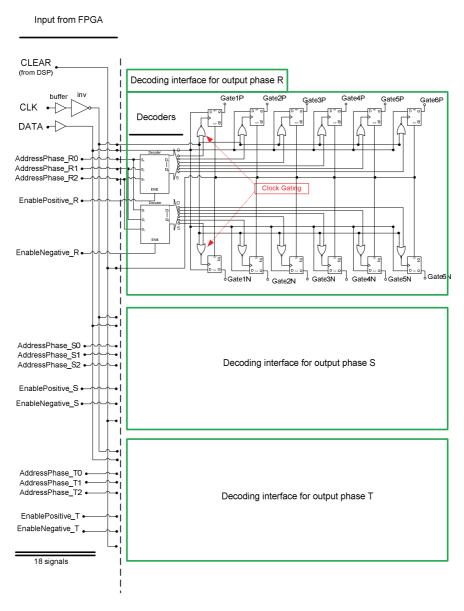

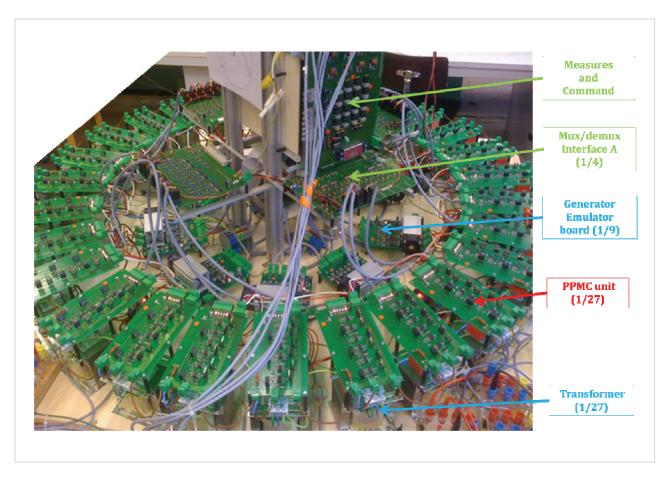

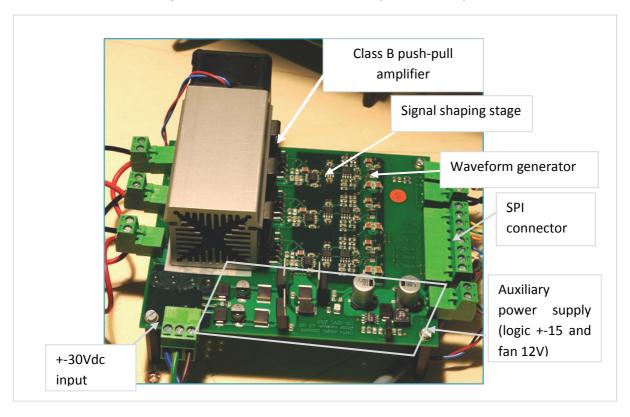

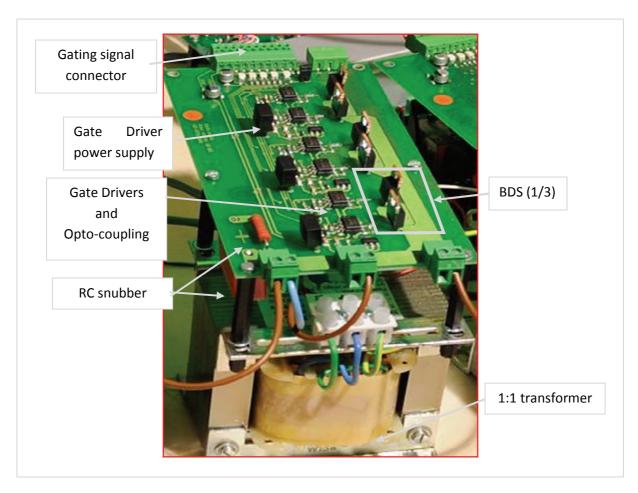

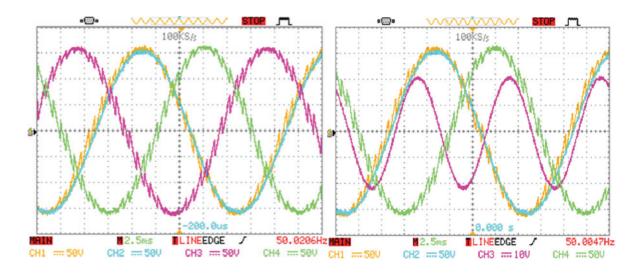

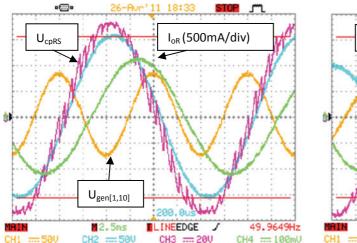

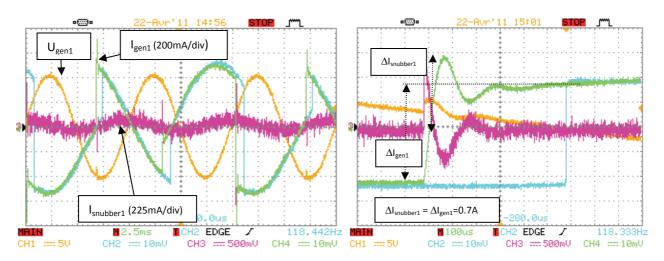

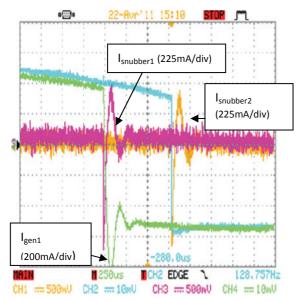

The *slowCWC* sequence, as written in chapter 1, has been suggested several times in the literature. However, the *slowCWC* has always been suggested along with a matrix converter using thyristors (NCMC) restricted to natural commutations (no additional circuitry to force off thyristors). As shown above, the *slowCWC* sequence cannot be executed entirely with natural commutations except for specific output power factor (lagging 0). If it is still required to work with natural commutations, then some commutations must be delayed, leading to a distorted output waveform. Reference [13] gives an exhaustive study of such a converter and especially the procedure to avoid unsuccessful