### Self-Aligned 3D Chip Integration Technology and Through-Silicon Serial Data Transmission

### THÈSE N° 5182 (2011)

PRÉSENTÉE LE 29 SEPTEMBRE 2011

À LA FACULTÉ SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

GROUPE DE SCIENTIFIQUES STI

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Fengda SUN

acceptée sur proposition du jury:

Prof. M. A. Ionescu, président du jury Dr J.-M. Sallese, directeur de thèse Prof. J. Brugger, rapporteur Dr W. Escher, rapporteur Prof. C. Lallement, rapporteur

## **Acknowledgements**

With thanks to the great mind of science, Swiss beautiful landscape and École Polytechnique Fédérale de Lausanne, my lovely mother school, I finished my dissertation. My thanks are boundless. At first, I would like to express my great appreciation to Prof. Jacques Giovanola, the dean of the doctoral school, for his strong supports to help me complete my PhD study. Through the communications with Prof. Giovanola, I felt not only the warm and kind understanding, but also the high requirement of a prestigious university has on his graduates. And I would like to thank Dr. Jean-Michel Sallese for accepting me as his student and guiding me through the final tough months to complete this thesis. Without his confidence, encouragement and patience, I can image how much more difficult it will be. This is a most precious experience.

I thank Prof. Mihai Adrian Ionescu for helping me arrange the administrative issues and would like to be the president of my PhD defense. I would like to extend my gratitude and thanks to Dr. Werner Escher, Prof. Christophe Lallement and Prof. Jürgen Brugger for accepting to be the jury members, reading and evaluating this thesis.

The cooperation with Dr. Thomas Brunschwiler is an unforgettable beautiful memory in my life. I admire his passion for science, his devotion to work, his fairness and sincerity. He encouraged me to make progress and firmed my confidence in studies. The colleagues in IBM, Zurich offered me happiness and support as well during my visits. I especially thank Ute Drechsler and Martin Witzig for their precious help on the process.

I greatly thank Prof. Vijaykrishnan Narayanan, Prof. Yuan Xie for the guidance and the cooperation of Asit K. Mishra, Guangyu Sun, Jin Ouyang, and Cong Xu during my visit in Pennsylvania State University. And I thank all the team mates and friends, Hsiang-Yun Cheng, Jishen Zhao, Qiaosha Zou, Jing Xie, Dimin Niu, Wenhui Hu, Tao Zhang, Yibo Chen, Matt Poremba in Penn State University for sharing an interesting short semester with me.

I thank Dr. Deniz Tezcan for giving me the chance to visit IMEC, Belgium. I thank Philip Normans for sharing his knowledge on microfabrication which was really in need for a beginner like me at that time. I thank Dr. Fabrice Duval for sharing his precious experience on polymers. And I enjoyed a lot the exciting travels with Dr. Iaci Pereira during the three months in Belgium, the ice skating and museum visits with Dr. Koen De Munck, Dr. Minoglou Kiki, Arno Aarts, and the happy time with Dr. Pham Nga, Dr. Majeed Bivragh, Goedele Potoms and Rita Verbeeck.

I thank the clean room staff in CMI for the support during my work and I would like to thank Yvan Deillon for the help on dicing and Boris Lunardi for configuring the coating system which ensured the success of the work in the extremely tight schedule. I thank Dr. Harald Van Lintel for sharing the grinding machine and doing the grinding experiment with me. I thank Dr. Sandro Carrara for letting me use their fume hood and offering some chemicals for trial. I also would like to thank Dr. Marc Pastre, Dr. Alex Schmid, Dr. Alain Vachoux and Joseph Guzzardi for helping me with the PC and Linux configuration.

Alessandro Cevrero, Panagiotis Athanasopoulos and I had a busy, productive and happy night together in the office until 3am to catch a deadline. And I enjoyed the days with Andrea Cavallini and Cristina Boero when we shared some experimental tools. I thank Massimo Spina for kindly offering his expertise on AFM, although in the end, the two fine images are not used in this thesis.

I thank Yin Yuan for accompanying me and providing valuable suggestions since we became friends. And I thank all my Chinese friends in EPFL and University of Lausanne, especially Dr. Meng Shen, Yan Yan, Yu Lu, Dr. Hongyan Bi, Hui Yang, Dr. Li Jin, Dr. Hua Zhang, Dr. Peng Xu, Liang Qiao, Hui Chen, Yu Chen, Cheng Yu, Shenqi Xie, Ji Cao, Xiaoqing Zhou, Dr. Lina Huang, Dr. Tiankai Zhu, Dr. Yu Bai, Dr. Zhanbin He, Qunzi Zhang, Chenxiu Lin and many more, for sharing their colorful and exciting lives.

I would like to thank Marie Halm, the secretary of my doctoral program. Moved by her kindness and consideration when I was looking for an advisor four years ago, I decided to come to this beautiful city for my PhD study. Throughout my study here, she offered excellent guidance on the doctoral school formalities and real warm help on my living. I would like to thank Ms. Marie Ligier and Ms. Marianne Wannier for their support as well.

Along the way, many of my teachers in all levels of training and shaping my mind with great hands that I greatly appreciate and wish to acknowledge, especially Ms. Huiyun Ni, Ms. Rong Cao, Ms. Hong Shen, Mr. Fengyi Sun, Mr. Zhenzhen Song, Prof. Jinming Dong, Prof. Bingru Yang, Prof. Dezheng Zhang and etc.

I owe my thanks to my father Dr. Gangbo Sun and mother Jingbo Cao, for giving me a family full of love, trust and devotion to each other. I thank my dad for opening a beautiful world well-connected in all aspects for me through his history study and teaching me the depth and length of a life. My lovely mom, being so serene, tender, organized, diligent and wise, is a life-long example for me, and I thank her. You are also my mentors I cherish forever.

## **Abstract**

The emerging three-dimensional (3D) integration technology is expected to lead to an industry paradigm shift due to its tremendous benefits. Intense research activities are going on about technology, simulation, design, and product prototypes. This thesis work aims at fabricating through-silicon vias (TSVs) on diced processor chips, and later bonding them into a 3D-stacked chip. How to handle and process delicate processor chips with high alignment precision is a key issue. The TSV process to be developed also needs to adapt to this constraint.

Four TSV processes have been studied. Among them, the ring-trench TSV process demonstrates the feasibility of fabricating TSVs with the prevailing dimensions, and the whole-through TSV process achieves the first dummy chip post-processed with TSVs in EPFL although the dimension is rather large to keep a reasonable aspect ratio (AR).

Four self-alignment (SA) techniques have been investigated, among which the gravitational SA and the hydrophobic SA are found to be quite promising. Using gravitational SA, we come to the conclusion that cavities in silicon carrier wafer with a profile angle of 60 ° can align the chips with less than 20  $\mu$ m inaccuracies. The alignment precision can be improved after adopting more advanced dicing tools instead of using the traditional dicing saws and larger cavity profile angle. Such inaccuracy will be sufficient to align the relatively large TSVs for general products such as 3D image sensors. By fabricating bottom TSVs in the carrier wafer, a 3D silicon interposer idea has been proposed to stack another chip, e.g. a processor chip, on the other side of the carrier wafer.

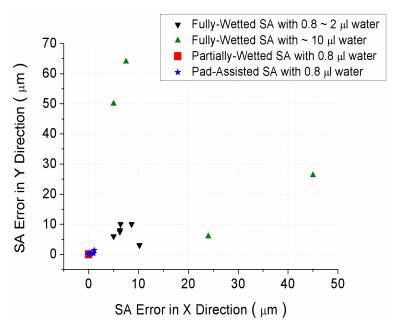

But stacking microprocessor chips fabricated with TSVs will require higher alignment precision. A hydrophobic SA technique using the surface tension force generated by the water-to-air interfaces around the pads can greatly reduce the alignment inaccuracy to less than 1  $\mu$ m. This low-cost and high throughput SA procedure is processed in air, fully-compatible with current fabrication technologies, and highly stable and repeatable. We present a theoretical meniscus model to predict SA results and to provide the design rules. This technique is quite promising for advanced 3D applications involving logic and heterogeneous stacking.

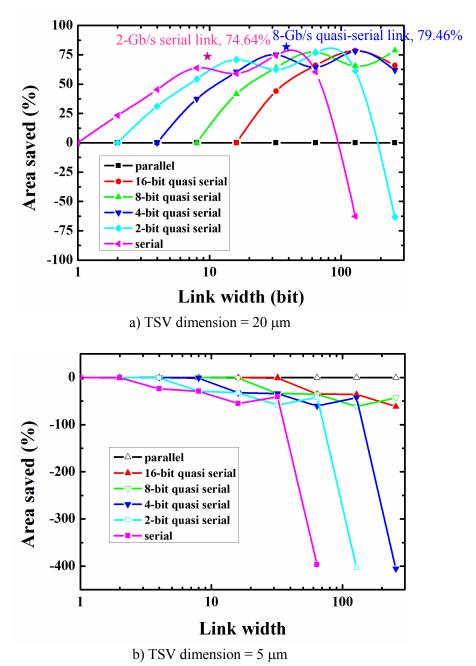

As TSVs' dimensions in the chip-level 3D integration are constrained by the chip-level processes, such as bonding, the smallest TSVs might still be about 5  $\mu$ m. Thus, the area occupied by the TSVs cannot be neglected. Fortunately, TSVs can withstand very high bandwidths, meaning that data can be serialized and transmitted using less numbers of TSVs. With 20  $\mu$ m TSVs, the 2-Gb/s 8:1 serial link implemented saves 75% of the area of its 8-bit parallel counterpart. The quasi-serial link proposed can effectively balance the inter-layer bandwidth and the serial links' area consumption. The area model of the serial or quasi-serial links working under higher frequencies provides some guidelines to choose the proper serial link design, and it also predicts that when TSV diameter shrinks to 5  $\mu$ m, it will be difficult to keep this area benefit if without some novel circuit design techniques.

As the serial links can be implemented with less area, the bandwidth per unit area is increased. Two scenarios are studied, single-port memory access and multi-port memory access. The expanded inter-layer bandwidth by serialization does not improve the system

performance because of the bus-bottleneck problem. In the latter scenario, the inter-layer ultra-wide bandwidth can be exploited as each memory bank can be accessed randomly through the NoC. Thus further widening the inter-layer bandwidth through serialization, the system performance will be improved.

Keywords: 3D integration, 3D chip integration, memory-on-logic stacking, through silicon via (TSV), post-processing, self-alignment (SA), gravitational SA, hydrophobic SA, surface tension force, self-assembled monolayer (SAM), serial transmission, inter-layer bandwidth, serial link, Network on chip (NoC), chip multi-processor (CMP), serializer and deserializer (SerDes), multiplexer (MUX), demultiplexer (DEMUX)

## Résumé

L'émergence de la technologie d'intégration 3D devrait repousser les limites technologiques suite aux avantages que promet celle-ci. Des recherches poussées sont en cours portant sur divers aspects, tels que la simulation, le design et les prototypes en tant que produits. Dans ce contexte, le sujet de cette thèse réside dans la fabrication de connections (TSV) réalisées à travers le silicium afin de fusionner en un seul empilement 3D des puces électroniques déjà découpées. Optimiser la manipulation et l'intégration de ces puces électroniques avec une grande précision demeure un défi majeur qui doit être pris en compte par le procédé de fabrication de ces "TSV".

Quatre procédés ont été étudiés. Parmi ceux-ci, le "ring-trench" est celui qui a permis de démontrer qu'il était possible de fabriquer ces "TSV" avec les dimensions requises. Ainsi a pu être réalisée à l'EPFL la première connexion à travers le silicium sur un échantillon témoin, et ceci bien que les dimensions étaient relativement grandes pour obtenir un rapport géométrique raisonnable.

D'autres parts, quatre techniques d'auto alignement de ces puces ont été évaluées, parmi lesquelles l'alignement par gravité et l'alignement obtenu sous l'effet de la tension superficielle. Tous deux très prometteurs. L'alignement par gravité démontre qu'il est possible d'atteindre une précision inférieure à 20 micromètres lorsque l'angle de la cavité, qui sert d'alignement dans le "wafer" de silicium, est de 60 °. Une meilleure précision pourrait être obtenue si des outils de découpes plus évolués étaient utilisés, ainsi qu'avec des angles plus verticaux. Cependant, de telles imprécisions restent compatibles pour aligner des "TSV" relativement larges qui sont destinés à des applications telles que les capteurs d'images. Par ailleurs, en fabricant des "TSV" sur la face arrière du "wafer" en silicium qui sert d'intermédiaire pour ces placements, nous avons proposé l'idée d'interposer un autre film de silicium afin d'empiler une puce sur l'autre face, telle que par exemple un processeur.

Toutefois, empiler des microprocesseurs nécessite une plus grande précision dans l'alignement. Celui ci peut être réalisé avec la technique d'auto alignement basé sur la tension superficielle qui apparait en présence de surfaces hydrophiles et hydrophobes. Dans ce cas, la précision devient meilleure que le micromètre. Cette technique, à bas coût et à fort rendement, est compatible avec les technologies standards. Elle est en outre stable et reproductible. Nous présentons également une étude théorique qui permet de prédire l'alignement des puces et qui pourrait être utilisée pour définir des règles de "design". Il est à noter que cette approche est prometteuse dans le sens où elle permettrait de combiner des circuits assez hétérogènes.

Etant donné que les dimensions de ces TSV dépendent également des procédés de fabrication de la puce elle-même, tels que la connexion, leurs dimensions minimales devraient être de 5 micromètres, pas moins. Ainsi, la surface qui leur est associée pourrait ne plus être négligeable. Mais un des avantages de ces "TSV" est qu'ils offrent une bande passante extrêmement large, ce qui implique que des données peuvent être transmises en série à travers un nombre réduit de ces éléments. Si l'on considère des "TSV" de 20 micromètres de diamètre, une transmission série de type 2-Gb/s 8:1 réduirait de 75% la surface occupée par une transmission équivalente de 8-bit sous un format parallèle. Il s'avère que la transmission partielle en série peut compenser de manière efficace la surface occupée par cette technologie,

tout en restant compatible avec des bandes passantes réalistes. Ainsi, le calcul de la surface utilisée pour la transmission série ou pseudo-série à plus haute fréquence permet de choisir la meilleure topologie. Il permet aussi de souligner que lorsque les "TSV" atteindront 5 micromètres, cet avantage sera difficile à conserver en termes de gain en surface sans devoir introduire de nouvelles techniques de "design" de ce genre de circuit.

Par ailleurs, étant donné que les connections de type série demandent moins de surface, la largeur de bande par unité de surface en sera augmentée. Deux scénarios sont étudiés, à savoir un accès mémoire "single port" ou bien "multiple-port".

Mais nous avons mis en évidence que l'accroissement de la largeur de bande entre les différentes couches obtenue par la transmission série n'améliore pas forcément les performances du système, ceci à cause de l'engorgement provenant du bus de transmission lui-même.

Finalement, dans une dernière analyse, nous mentionnons que la transmission entre les différentes couches à ultra haute fréquence pourrait être exploitée dans le cas de la mémoire qui serait accessible de manière aléatoire à travers le "Network on Chip". Ainsi, les performances du système seraient améliorées en augmentant la bande passante au moyen de la transmission série entre les couches

**Mots clefs**: 3D integration, 3D chip integration, memory-on-logic stacking, through silicon via (TSV), post-processing, self-alignment (SA), gravitational SA, hydrophobic SA, surface tension force, self-assembled monolayer (SAM), serial transmission, inter-layer bandwidth, serial link, Network on chip (NoC), chip multi-processor (CMP), serializer and deserializer (SerDes), multiplexer (MUX), demultiplexer (DEMUX)

# **Glossary**

| Acronym | Signification                                       |

|---------|-----------------------------------------------------|

| 2EH     | 2-ethyl-1-hexanol                                   |

| ALD     | Atomic Layer Deposition                             |

| AR      | Aspect Ratio                                        |

| BARC    | Bottom-Layer Anti-Reflective Coating                |

| BCB     | Benzocylcobutene                                    |

| BEOL    | Back End of Line                                    |

| BHF     | Buffered Hydrofluoric Acid                          |

| CMI     | Center of Micronanotechnology                       |

| CML     | Current Mode Logic                                  |

| CMP     | Chemical Mechanical Polishing                       |

| CMP     | Chip Multiprocessor (in Chapter 6)                  |

| CSCM    | Chip Scale Camera Module                            |

| C-to-W  | Chip-to-Wafer                                       |

| CTE     | Coefficient of Thermal Expansion                    |

| CVD     | Chemical Vapor Deposition                           |

| DEMUX   | Demultiplexer                                       |

| DMA     | Distributed Memory Architecture                     |

| DRAM    | Dynamic Random Access Memory                        |

| DRIE    | Deep Reactive Ion Etching                           |

| DSC     | Differential Scanning Calorimetry                   |

| FEOL    | Front End of Line                                   |

| FIB     | Focused Ion Beam                                    |

| F-W SA  | Fully-Wetted Self-Alignment                         |

| HAR     | High Aspect Ratio                                   |

| HPIMS   | High Power Impulse Magnetron Sputtering             |

| HVM     | High Volume Manufacturing                           |

| ICP     | Inductive Coupled Plasma                            |

| ICV     | Inter Chip Via                                      |

| IMP     | Ionized Metal Plasma                                |

| ITRS    | International Technology Roadmap for Semiconductors |

| LPCVD   | Low Pressure Chemical Vapor Deposition              |

| KGD     | Known Good Die                                      |

| KOD     | Keep Out Distance                                   |

| KOZ     | Keep Out Zone                                       |

| MEK     | Methylethyl                                         |

| MEOL    | Middle End of Line                                  |

| MOCVD   | Metal Organic Chemical Vapor Deposition             |

| MUX     | Multiplexer                                         |

| NoC     | Network on Chip                                     |

| NUCA    | Non-Uniform Cache Access                            |

| P-A SA  | Pad-Assisted SA                                     |

| PECVD   | Plasma Enhanced Chemical Vapor Deposition           |

| PGMEA   | Propylene Glycol Monometryl Ether Acetate           |

| PVD     | Physical Vapor Deposition                           |

| P-W SA  | Partially-Wetted SA                                 |

| Acronym | Signification                             |

|---------|-------------------------------------------|

| RC      | Routing Computation                       |

| RDL     | ReDistribution Layer                      |

| RIE     | Reactive Ion Etching                      |

| RMS     | Root Mean Square                          |

| SA      | Self-Alignment                            |

| SACVD   | Sub Atmospheric Chemical Vapor Deposition |

| SAM     | Self-Assembled Monolayer                  |

| SEM     | Scanning Electron Microscope              |

| SerDes  | Serializer and Deserializer               |

| SMA     | Shared Memory Architecture                |

| S-NUCA  | Static Non-Uniform Cache Access           |

| SOI     | Silicon on Insulator                      |

| SOD     | Spin-On Dielectrics                       |

| TCV     | Through Chip Via                          |

| TSV     | Through Silicon Via                       |

| UCA     | Uniform Cache Access                      |

| VC      | Virtual Channel                           |

| W-to-W  | Wafer-to-Wafer                            |

# Content

| Chapter 1 Introduction                                                               |    |

|--------------------------------------------------------------------------------------|----|

| 1.2 Key Technologies of 3D Integration                                               |    |

| 1.2.1 Through Silicon Via                                                            |    |

| 1.2.2 Thinning                                                                       | 11 |

| 1.2.3 Bonding                                                                        | 13 |

| 1.2.4 3D Integration Schemes                                                         | 13 |

| 1.3 3D Applications                                                                  | 14 |

| 1.4 3D Circuit Design and System Architecture                                        | 15 |

| 1.5 Outline of This Thesis                                                           | 15 |

| Reference                                                                            | 16 |

| Chapter 2 TSV Fabrication Technologies                                               |    |

| 2.2 Core-Hole TSV Process                                                            | 21 |

| 2.2.1 Process Flow                                                                   | 21 |

| 2.2.2 Silicon Dry Etch                                                               | 21 |

| 2.2.3 Spray Coating in High Aspect Ratio (HAR) Topography                            | 31 |

| 2.2.4 Core-Hole TSV Detailed Process                                                 | 33 |

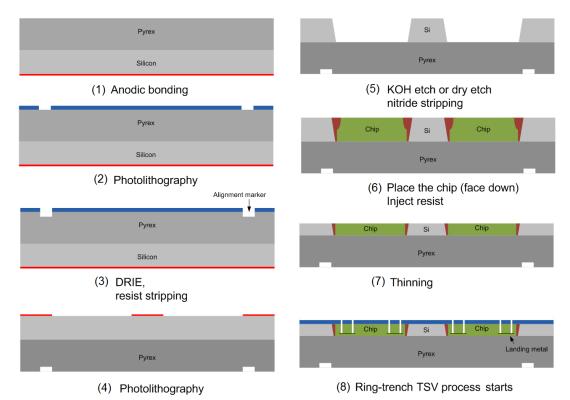

| 2.3 Ring-Trench TSV Process                                                          | 36 |

| 2.3.1 Process Flow                                                                   | 36 |

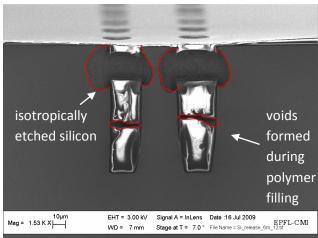

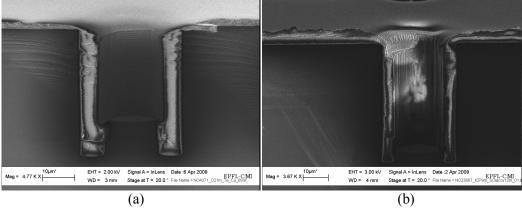

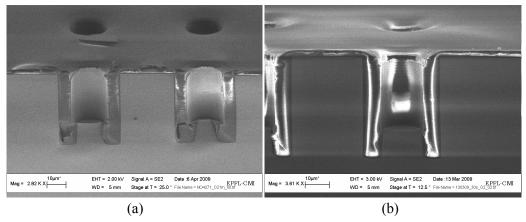

| 2.3.2 Filling Polymer in HAR Microstructures and Pattern Transfer                    | 37 |

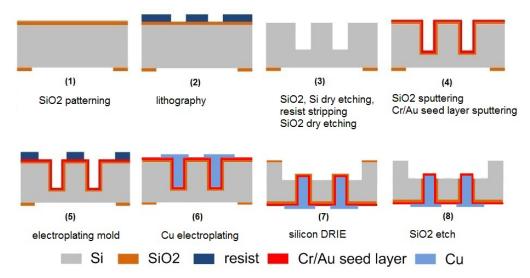

| 2.3.3 Electroplating Mold for Cu Electroplating.                                     | 42 |

| 2.3.4 Ring-Trench TSV Detailed Process                                               | 45 |

| 2.3.5 A Modified Ring-Trench TSV Process                                             | 49 |

| 2.4 Step TSV Process: An Alternative Solution                                        | 53 |

| 2.4.1 Process Flow                                                                   | 53 |

| 2.4.2 Step TSV Detailed Process                                                      | 53 |

| 2.5 Whole-Through TSV Process: A Feasible Solution to TSV Post-Processing on Dies    | 54 |

| 2.5.1 Introduction                                                                   | 54 |

| 2.5.2 Parylene C on Through-Wafer Holes and Double-Side Sputtering of Al on Parylene | 55 |

| 2.5.3 Die Thinning                                                                   |    |

| 2.5.4 BEOL Metal (Al) as Dry Etch Hard Mask                                          | 57 |

| 2.5.5 Whole-Through TSV Detailed Process                                             |    |

| 2.6 Summary                                                              | 60 |

|--------------------------------------------------------------------------|----|

| Reference                                                                | 62 |

| Chapter 3 Alignment and Stacking Techniques for Die-Level 3D Integration |    |

| 3.1.1 Materials for Temporary Die Attachment                             | 65 |

| 3.1.2 Precise Die Attachment/Stacking                                    | 66 |

| 3.2 Picturing SA Techniques for 3D                                       | 67 |

| 3.2.1 Gravitational SA                                                   | 67 |

| 3.2.2 Electrostatic SA                                                   | 68 |

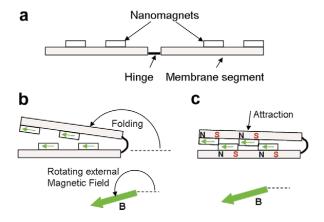

| 3.2.3 Magnetic SA                                                        | 68 |

| 3.2.4 Hydrophobic SA                                                     | 69 |

| 3.3 Silicon Interposer and Gravitational SA Technique                    | 69 |

| 3.3.1 The Idea                                                           | 69 |

| 3.3.2 Proof of Concept                                                   | 73 |

| 3.3.3 Discussion of the Process, Further Improvements and Conclusion     | 74 |

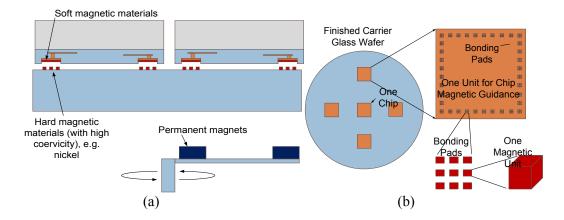

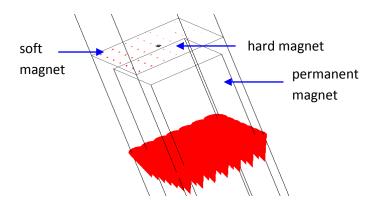

| 3.4 Magnetic SA Technique                                                | 76 |

| 3.4.1 The Idea                                                           | 76 |

| 3.4.2 Theoretical Analysis                                               | 76 |

| 3.4.3 Initial Experiment Results and Summary                             | 77 |

| Reference                                                                | 77 |

| Chapter 4 Hydrophobic SA for Heterogeneous 3D Integration                |    |

| 4.1.1 The Advantage of Hydrophobic SA over the Other SA Techniques       | 79 |

| 4.1.2 Hydrophobic SA                                                     | 80 |

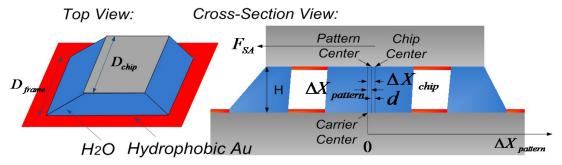

| 4.2 Our Method                                                           | 81 |

| 4.3 Experiment Evaluation                                                | 82 |

| 4.3.1 Experimented Self-Alignment Processes                              | 82 |

| 4.3.2 Sample Preparation                                                 | 83 |

| 4.3.3 Experiment Results                                                 | 85 |

| 4.4 Meniscus Model                                                       | 89 |

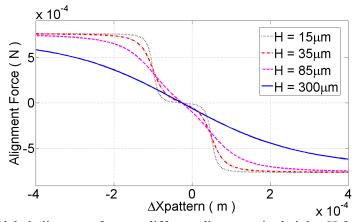

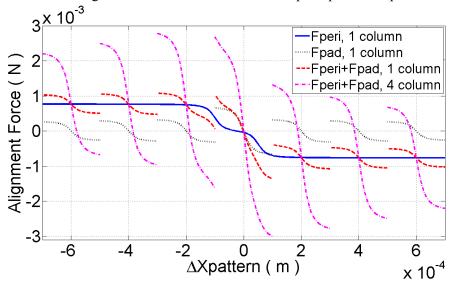

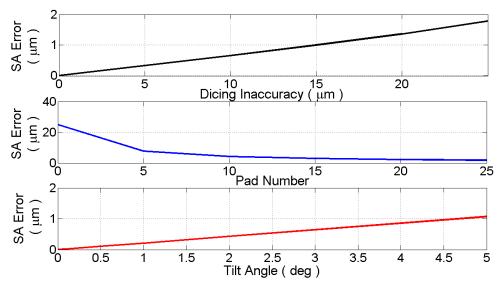

| 4.4.1 Analytical Model of SA                                             | 89 |

| 4.4.2 Modeling Results                                                   | 90 |

| 4.5 A Revisit of Magnetic SA in Comparison of Hydrophobic SA             | 93 |

| 4.6 Summary                                                              | 94 |

| Reference                                                                | 95 |

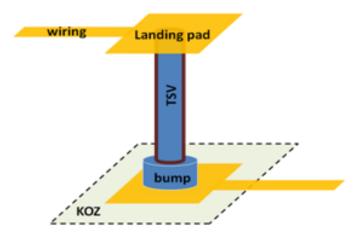

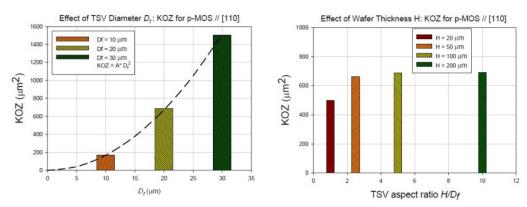

| 5.1 Introduction                                                      | 97  |

|-----------------------------------------------------------------------|-----|

| 5.2 TSV Characteristics and Performance                               | 97  |

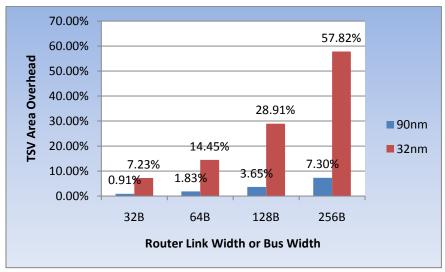

| 5.2.1 TSV Area                                                        | 97  |

| 5.2.2 TSV Electrical Performance                                      | 99  |

| 5.2.3 TSV I/O Power Estimation                                        | 104 |

| 5.2.4 Summary                                                         | 105 |

| 5.3 A 2-Gb/s Inter-Layer Serial Link                                  | 105 |

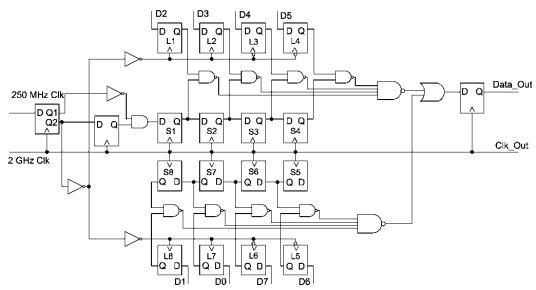

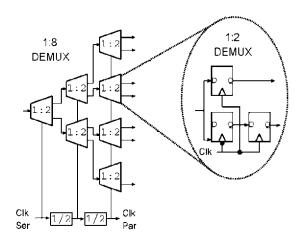

| 5.3.1 Circuit Design for Each Tier                                    | 105 |

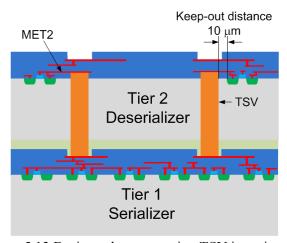

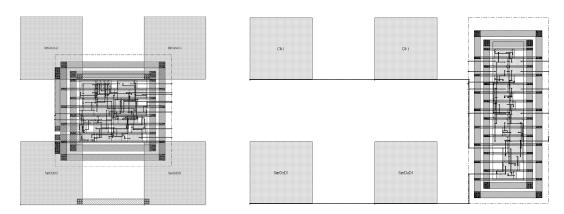

| 5.3.2 TSV Insertion and Layout Simulation                             | 107 |

| 5.3.3 Results                                                         | 108 |

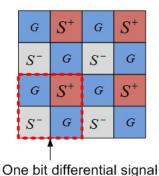

| 5.4 A 8-Gb/s Inter-Layer Quasi-Serial Link                            | 109 |

| 5.5 Inter-Layer Serial Link Design Methodology                        | 110 |

| 5.6 Summary                                                           | 113 |

| Reference                                                             | 114 |

| Chapter 6 System-Level Exploration of Inter-Layer Serial Transmission |     |

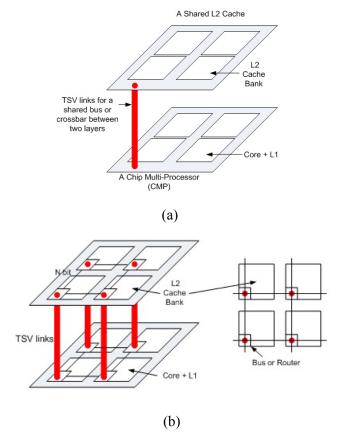

| 6.1.1 Memory-on-Logic 3D Stacking and Our Research Region             | 117 |

| 6.1.2 Networks-on-Chip (NoCs)                                         | 118 |

| 6.1.3 UCA cache and NUCA Cache                                        | 118 |

| 6.1.4 3D Memory-on-Core System Architectures                          | 119 |

| 6.2 Proofs for Inter-Layer Serialization                              | 120 |

| 6.2.1 Area Considerations                                             | 120 |

| 6.2.2 Power Consumption Considerations                                | 121 |

| 6.3 Serialized Inter-Layer Transmission in 3D SMA                     | 122 |

| 6.3.1 Simulation Platform.                                            | 122 |

| 6.3.2 Simulation Results                                              | 123 |

| 6.4 Serialized Inter-Layer Transmission in 3D DMA                     | 123 |

| 6.4.1 Simulation Platform                                             | 123 |

| 6.4.2 Simulation Results                                              | 124 |

| 6.5 Summary                                                           | 126 |

| Reference                                                             | 127 |

| Chapter 7 Conclusion and Outlook                                      |     |

| 7.1.1 Technology Aspects                                              | 129 |

| 7.1.2 Through-Silicon Serial Data Transmission Issues                 | 130 |

| 7.2 Outlook                                                           | 131 |

# Chapter 1

## Introduction

#### 1.1 History

The invention of transistor by John Bardeen, Walter Brattain and William Shockley in 1947 and the integrated circuit by Jack Kilby in 1959 were great innovations. Since the Moore's Law was postulated in 1965, the semiconductor industry continuously followed these scaling rules. In 1980's, people saw the possible end of the Moore's Law. Although this limit has always been postponed, the end of the Moore's law is becoming a reality: we are facing atomic scale issues in ultra deep miniaturization. Researchers have been working hard to find replacement solutions. Intensive research is going not only on "exotic" semiconductor materials, like diamond and graphene, but also on computing technologies such as quantum and bio-inspired computation. However, among all the solutions, exploring the 3D vertical space using existing semiconductor infrastructures is surely the most natural and prospective choice. This is known as "3D integration". It is truly not a new idea. William Shockley made a technology patent entitled "Semiconductive Wafer and Method of Making the Same" in 1965 [1]. It is actually what we call "Through Silicon Vias (TSV)" or "3D vias" now, which is the key of the recent 3D technology. But no one really paid attention to this idea at that time.

In 1985, a Noble Physics laureate, Richard Feynman, said in his address "the Computing machines in the Future" and I quote, "Another direction of improvement (of computing power) is to make physical machines three dimensional instead of all on a surface of a chip. That can be done in stages instead of all at once - you can have several layers and then add many more layers as time goes on." In the following year, Yoichi Akasaka published a paper in Proceedings of IEEE with a title "Three-Dimensional IC Trends" [2]. Since then, 3D research has been world-wide popular in different levels for the past 20 years. Today its era has come.

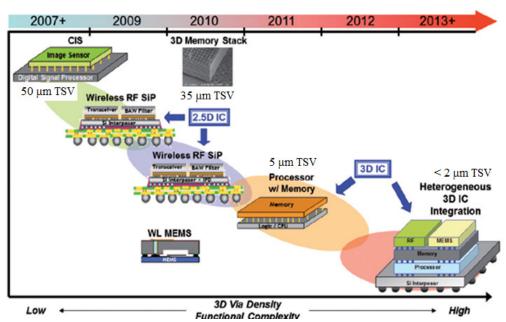

The Advanced Semiconductor Engineering Group (ASE Group, the world's largest provider of independent semiconductor manufacturing services in assembly and test) has proposed a 3D roadmap in Fig. 1.1, showing the aimed 3D applications with the predicted time to market.

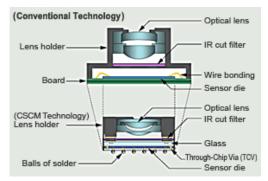

Consumer electronics, for example, cell phones, digital cameras, PDAs audio players and mobile gaming, demand innovative form factors and styling. By removing the on-board connections by vertical interconnections in the chip stack, the form factor is greatly reduced. Toshiba's commercialized Chip Scale Camera Module (CSCM) equipped with a Dynastron® CMOS image sensor manufactured with Through-Chip Via (TCV) technology. A downsizing of approximately 64% compared to conventional module has been achieved (Fig. 1.2) [3].

Now, considering computing performance, for a uni-core processor, 3 GHz clocking is almost the upper limit and represents the end of the line in clock speed improvements. In one third of a nanosecond, light moves about 4 inches or 10 cm, not much distance when the chips have miles of internal wiring.

Instead of pursuing higher clock frequency, more cores are stuffed into one chip. But the number of cores we can put in a single chip is an issue. From the application point of view, except for some critical ones like scientific calculation and videos that multi-core architectures will gain efficiency, other applications like web surfing certainly do not require so many cores. Making multi-core chips workable is not only very challenging with respect to the technology itself, but also making the memory wall problem even more difficult, since larger on-chip caches are then required to improve the performances. But inevitably, cache hit ratio declines with size, and so does the performance. What is required is a system-level solution, higher memory capacity with new memory architectures. Directly stacking memory on core or distributing cores and memories into several layers creates more design possibilities with higher system performance.

People also put hope on 3D integration to enable the super stacking of heterogeneous chips with different functions such as MEMS, RF, CPU, memories and etc. Without 3D, the one-plane implementation is form factor prohibitive or even not functional.

Great potential and significance of 3D integration have been clearly demonstrated. However, to get the enabling technologies and to achieve successful 3D systems, circuit designers and system architects should have a good understanding of the technology. In the next sections, we will introduce the key technologies in 3D integration, the upper levels of the 3D ecological systems including the EDA tool support and 3D circuit and system study.

Figure 1.1 3D Roadmap. Courtesy of ASE Group.

Figure 1.2 Toshiba commercialized CSCM with TCV (= TSV) technology [3].

#### 1.2 Key Technologies of 3D Integration

#### 1.2.1 Through Silicon Via

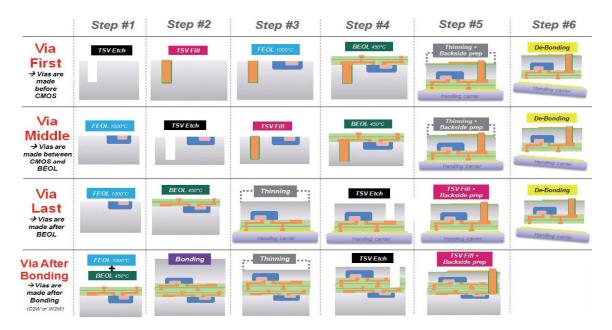

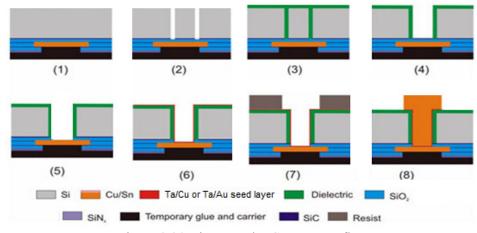

TSV is the soul of 3D technology. It is the interconnection penetrating the wafer or chip that transmits signals from one stratum to another. Basically, to get a TSV, we need to first open some via holes, then form an isolation layer around the sidewall and finally deposit conducting materials inside the holes. Two main stream TSV processes exist, front end of line (FEOL) TSV process and back end of line (BEOL) TSV process. Later, a middle end of line (MEOL) TSV process has been proposed. TSVs can also be processed after bonding. As it is not as popular as the other three TSV processes, it will be introduced as the last solution. The four processes are illustrated in Fig. 1.3.

Figure 1.3 Main TSV integration scenarios [3]. Courtesy of Yole Development.

#### FEOL TSV or Via-First Approach

For FEOL TSV process, TSV holes are etched prior to CMOS transistor or MEMS microstructure fabrications. For TSV used in CMOS chips, the materials need to be CMOS-compatible. Thermal oxidation of silicon for TSV isolation can be used, which is a big advantage since it achieves conformal lining without the limitation of topography, while other methods such as plasma enhanced chemical vapor deposition (PECVD) and sputtering processes cannot.

An early trial was presented by Chow *et al.* in 2000 [4]. In this process, 20 µm circular holes were etched by double-side DRIE process through a 400 µm thick wafer. Through-hole insulation and conduction layer were achieved by thermal oxidation of silicon and Low Pressure Chemical Vapor Deposition (LPCVD) of polysilicon. Next, phosphorus diffusion at 1000 °C rendered the polysilicon conducting.

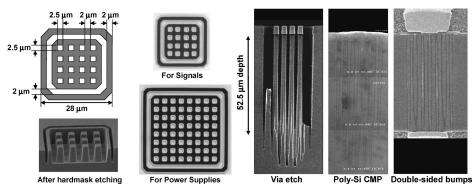

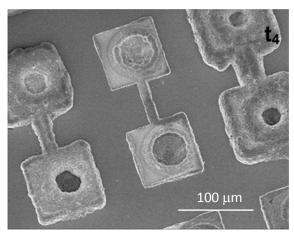

In 2008, Kawano *et al.* presented polysilicon TSVs, with 18 µm diameter and 140 µm depth, working in a 8-layer dynamic random access memory (DRAM) stack [5] (Fig. 1.4). In the future, it is expected that tiny and dense TSVs will have less than 1 µm diameter and only a few micron height. Only polysilicon can be used as conducting material for FEOL TSV since metal cannot withstand high temperatures. Thus, via resistivity will be higher compared

to metals. Many challenging problems exist, e.g. handling of thinned and fragile wafers, wafer-level bonding to achieve interlayer connections and so on (will be discussed in Section 1.2.2 and Section 1.2.3). This is a foundry-only solution.

Figure 1.4 Poly-Si TSV process proposed by Kawano *et al*. [5]. (a) Design rules for poly-Si TSVs and plan views before poly-Si CVD. (b) Poly-Si TSV cross sections at several process steps.

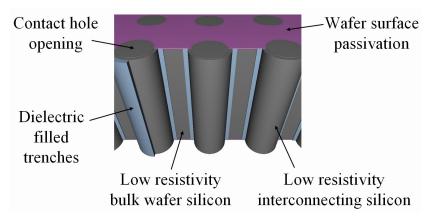

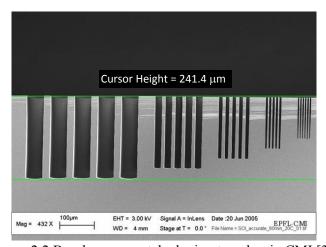

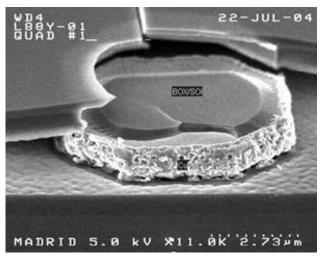

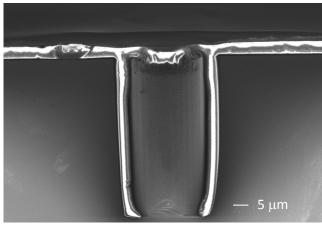

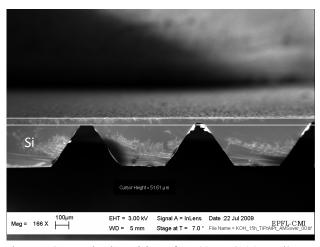

From a MEMS processing perspective, the "via-first" approach is by all means preferred in most cases since completed delicate MEMS structures will not benefit from additional wafer level post processing and handling. In 2007, Bauer presented a unique via-first process for low-frequency 3D MEMS applications (Fig. 1.5) [6]. The process began with the formation of  $10 - 15 \, \mu m$  wide ring trenches using DRIE process, achieving the necessary high aspect ratio features up to  $600 \, \mu m$  thick low-resistivity silicon substrate. Then the wafer was subject to a high temperature filling of the trenches by a dielectric material. Finally, a chemical mechanical polishing (CMP) process was applied to the backside of the wafer until the via plugs were isolated from the bulk of the wafer. Typical resistance in a standard via connection of  $100 \, \mu m$  diameter in a  $400 \, \mu m$  thick substrate is on the order of  $1 \, \Omega$  and such a resistance will constitute an unacceptable loss in most RF designs.

Figure 1.5 Schematic cross section of the TSV structure proposed by Bauer [6].

#### BEOL TSV or Via-Last Approach

Most research institutes and companies went for BEOL solutions. In this via-last approach, TSVs are fabricated after the device integration and the BEOL metal processes. The thermal budget is thus constrained by BEOL metal process that must be kept below 450 °C. Even

temperatures lower than 300 °C are preferred. If the chip is exposed to temperatures greater than 450 °C, CMOS metallization will start diffusing significantly into silicon, resulting in non-functional circuits [7, 8].

Post-processing might also induce device damages. Technologies such as e-beam evaporation generate X-ray radiation that might cause threshold voltage shifts in transistors and deteriorates the circuits [8], so that should be avoided. Reactive Ion Etch (RIE) and Deep Reactive Ion Etch (DRIE) processes used to fabricate TSV holes may also cause some radiation-induced damages in CMOS circuits due to charging from high energy UV photons, ions or electrons [9]. Moreover, plasma processing might cause dielectric breakdown of gate dielectrics [9]. To minimize the potential damages to CMOS devices, BEOL TSVs are better processed from the back-side of the wafer or chip. This is called "backside TSV". Conversely, "frontside TSV" exists as well.

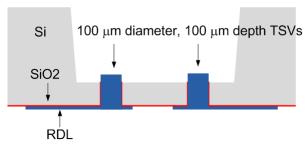

Early developed BEOL TSVs were etched through the full thickness of the wafer. The diameters ranged from about 100  $\mu$ m to more than 200  $\mu$ m, mainly depending on the etching technology used, either KOH or DRIE.

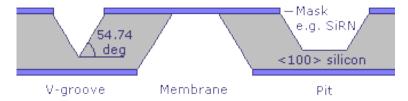

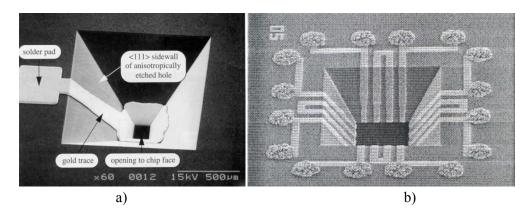

KOH-etched TSVs have to be quite large because of the etching mechanism (Fig. 1.6). In 1994, Linder *et al.* presented the first results of vias fabricated by partial metallization of KOH-etched wafer through-holes [10]. The process was based on photolithography in the KOH etch pit using photosensitive polyimide and subsequent electroplating of Au into the polyimide mould. The resistance of the vias was around 20 m $\Omega$  and their capacitance in the range of 2 pF to 5 pF. In 1996 Linder presented an improved via process in which electrodeposited photoresist was employed for patterning the via metallization [11]. A via fabricated according to this process is shown in Fig. 1.7-a. This via has a resistance of 10 m $\Omega$  only and a parasitic capacitance in the range of 2 pF to 5 pF. In 1996, Burger *et al.* fabricated multiple via Al metal connections using KOH-etched through-holes with a shadow mask. The via resistance was reported to be below 5 m $\Omega$  and the parasitic capacitance less than 1 pF. Finally, in 1998/1999, Heschel *et al.* proposed a process based on electrodeposition of photoresist used as a mould for electroplating of copper via metal from evaporated Ti/Au seed layer [12, 13, 14]. Parasitic capacitance and resistance of these vias were further reduced to 0.7 pF and in the range of 700 m $\Omega$ . This is shown in Fig. 1.7-b.

Figure 1.6 KOH etching mechanism.

Figure 1.7 TSV technologies presented by (a) Linder et al. [11] and (b) Heschel et al. [13].

In the continuous effort to increase the via density, DRIE producing smaller and straight TSVs was adopted. With the same wafer thickness, the via aspect ratio was increased which rendered even more difficult the problem of sidewall isolation and metallization. Conventional physical vapor deposition (PVD) methods were not able to achieve highly conformal deposition on the via sidewall.

In 2003, Rasmussen *et al.* presented a hallow TSV structure using Parylene as dielectric isolation. Highly conformal deposition of TiN/Cu by MetalOrganic Chemical Vapor Deposition (MOCVD) was employed to metallize parylene. A 100  $\mu$ m wide and 380  $\mu$ m deep through-wafer TSVs with 5  $\mu$ m thick parylene for isolation and 1  $\mu$ m thick Cu layer for conduction was fabricated. The via resistance and capacitance were 161 m $\Omega$  - 177 m $\Omega$  and 1.7 pF [16].

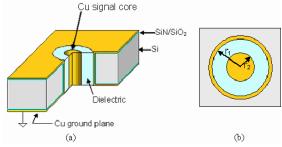

The benefit coming with TSV shrinkage is reduced TSV parasitics and thus improved electrical performance. An example of coaxial shield TSV structure is illustrated in Fig. 1.8. This was proposed by Ho *et al.* [16] in 2006 for high frequency application. The process consists in: 1) 300 µm diameter through wafer (250 µm thick) via-hole etching; 2) 1 µm SiO<sub>2</sub> and 1000 Å silicon nitride insulation liner deposition; 3) 1 µm thick Cu ground plane deposition along the via and the substrate; 4) screen-printing of 112 µm thick SU8 into the via holes for the dielectrics; 5) removing core centers in the SU8-filled via holes by photolithography; 6) bottom-up electroplating to fill the center cores with Cu. With this proposed coaxial shield via structure, the TSVs fabricated in low-resistivity silicon substrate achieved a minimum RF signal transmission loss under 40 GHz. It also provides an elegant method to achieve thick dielectrics along the via sidewall.

Figure 1.8 Coaxial shield TSV structure [16].

Although these TSV densities and their number were quite limited because of their large size, 3D demonstrators had already shown a great reduction of form factor, thus making this technology commercially competitive. An early attempt of commercial application of vias

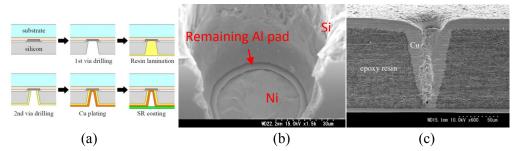

was in a MEMS microphone consisting of stacked chips electrically interconnected by vias [12, 17]. In 2008, Toshiba produced the first commercial 3D CMOS image sensor with a cheap and streamlined TSV (they call "Through Chip Via (TCV)") process [3]. For instance, the CMOS image sensor wafer was attached to a handling glass wafer by patterned adhesives and thinned by backside grinding and polishing. A first via was drilled by a pad-stop (stop at Ni plated above the Al pads) laser ablation technique from the wafer backside with backside alignment to the pads. A resin was laminated using vacuum lamination equipment to completely fill the via holes. A second via drilling was performed at the center of the first via. Subtractive or semi-additive PCB electroplating processes was employed to pattern the 10  $\mu$ m Cu plate on the back of the wafer and inside the vias. Typical via diameter was 60  $\mu$ m at the top and 30  $\mu$ m at the bottom. The process flow and the cross-section of Cu plated via are shown in Fig. 1.9 [19, 20].

To optimize the area and get better electrical characteristics of the TSVs in order to use them for more advanced 3D applications, an effort was done to develop smaller TSVs with higher density. Wafers were thinned down to less than  $100~\mu m$ , mostly  $50~\mu m$ , and sometimes even  $15~\mu m$ . Trade-offs exist. Thicker wafers can be easily handled and thinned, so a tall TSV is preferred. Then, In order to keep the via density, higher aspect ratios are necessary. But the aspect ratio is constrained by many processing steps, such as etching, deposition and electroplating.

Figure 1.9 Toshiba TSV technology. (a) Via process flow used in Toshiba 3D image sensor. (b) First via drilling. (c) Cross-section of Cu-plated via.

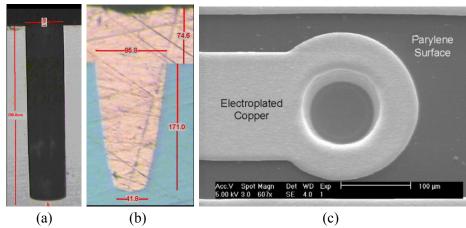

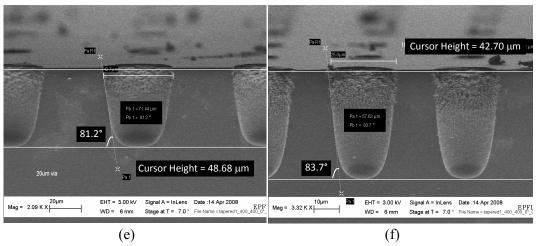

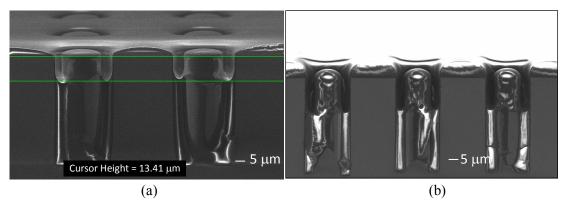

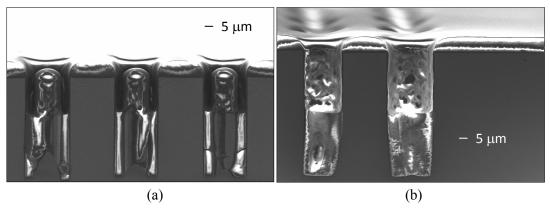

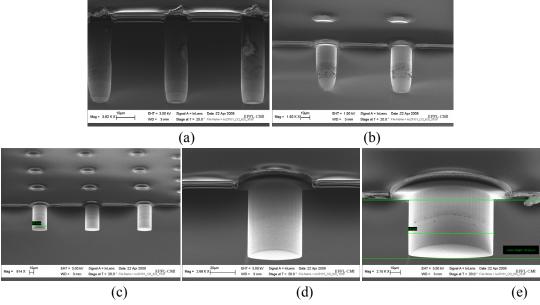

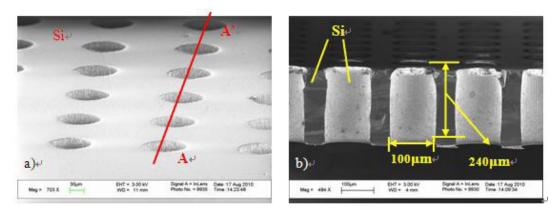

Nagarajan *et al.* proposed a tapered TSV process in 2006 [21]. 200  $\mu$ m-deep 100  $\mu$ m-wide 80°-tapered via holes were etched by a dual-etch process (DRIE followed by continuous silicon etch) and later completely filled with copper by a DC plating process with equal ON/OFF time of 20 ms. The optical images of the via cross-sections in different process steps are shown in Fig. 1. 10-a and Fig. 1. 10-b. No electrical characteristic has been reported.

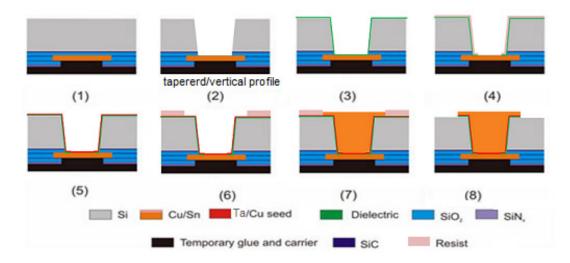

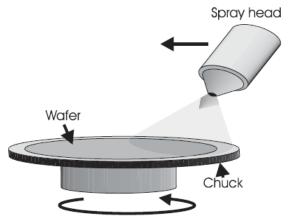

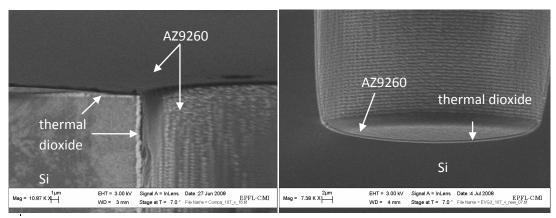

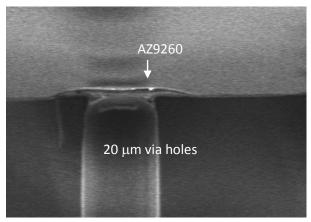

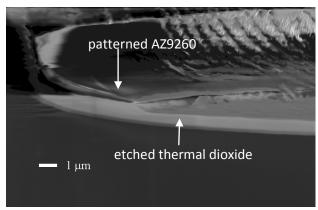

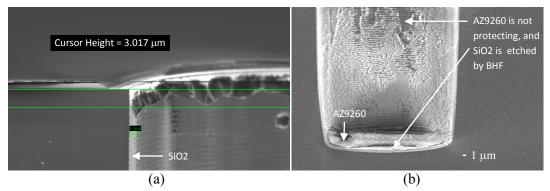

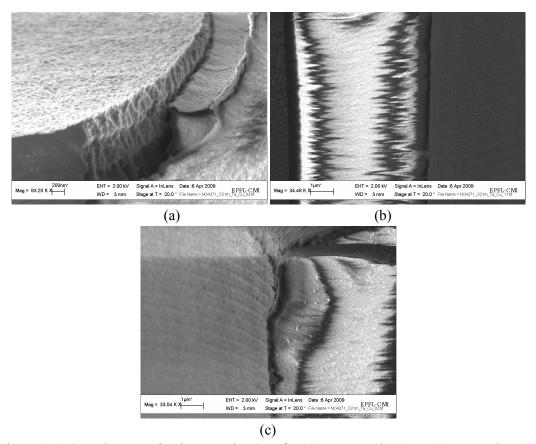

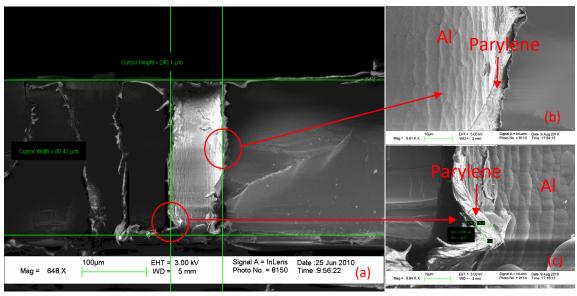

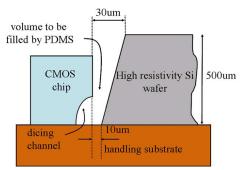

Another sloped TSV process for 3D wafer-level packaging was presented by Tezcan *et al.* in 2007 [22]. A silicon wafer was glued on a carrier pyrex wafer and thinned down to 100  $\mu$ m. Then 50 - 100  $\mu$ m wide 80 °-tapered vias were etched until the landing Al pads, and covered with parylene for isolation. Subsequently, the insulator material at the bottom of the via was removed in order to reach the metal contact. The related photolithography step was done through spray resist coating technique. Finally a seed layer was sputtered, followed by Cu plating. With 140  $\mu$ m top diameter, 100  $\mu$ m bottom diameter, 100  $\mu$ m height, 1 - 2  $\mu$ m thick parylene as dielectric isolation and 5 - 20  $\mu$ m thick copper electroplated on the via sidewall for current conduction. A via resistance in the range of 20 - 30 m $\Omega$  was reported. A cross-section view of such a via is shown in Fig. 1.10-c.

Figure 1.10 TSV technology proposed by Nagarajan *et al.* [21] and Tezcan *et al.* [22]. (a) Via hole after 1st DRIE in [21]. (b) Via hole after 2nd etch in [21] and filled with copper. (c) Via cross section view in [22].

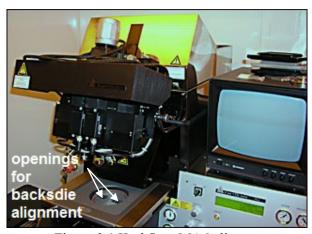

Next, in 2007, Benkart *et al.* presented a 5 µm-long and 10 µm-tall square TSV process with a thermal budget below 300 °C [23]. The wafer was prepared in a unique way for thinning which includes markers definition for backside alignment and epitaxial overgrowth with a high boron doped etch stop layer in the silicon wafers before CMOS fabrication. Mechanical grinding was performed on the backside of the wafer which was glued to a carrier wafer, followed by chemical etching down to the etch stop layer. By adding a step of anodic oxidation at < 50 °C to the low temperature CVD of SiO<sub>2</sub>, leakage current between the signal lines or into the substrate was decreased, so the isolation was enhanced. The vias were filled with Cu electroplating. As it was a through-hole TSV technology, metal redistribution was required to get the connection between the TSV and the circuitry.

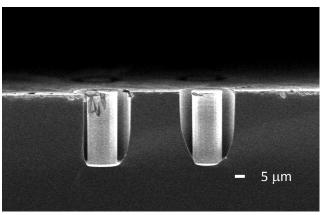

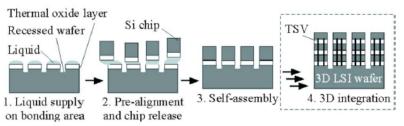

Very recently in 2011, Ohara *et al.* reported their development of 5  $\mu$ m-diameter backside TSV technology [24]. The chip was supported on a glass or silicon carrier wafer and thinned down to 15  $\mu$ m by grinding and CMP. Then, about 1  $\mu$ m SiO<sub>2</sub> was deposited as an isolation layer / hard mask . The TSVs were created with Bosch process and then lined with SiO<sub>2</sub> (500 nm). The bottoms of the insulated TSVs were opened by anisotropic SiO<sub>2</sub> etching using the thicker backside oxide layer as partially sacrificial mask for the etching. This is a much cheaper and simpler method to achieve TSV contact comparing to the afore-mentioned way Tezcan *et al.* applied in 2007 [ ].

The above TSVs are all based on plated copper as the conducting material. To further decrease the TSV dimension, plating is not sufficient to get a uniform coverage on very high aspect ratio structures. Instead, CVD has to be used.

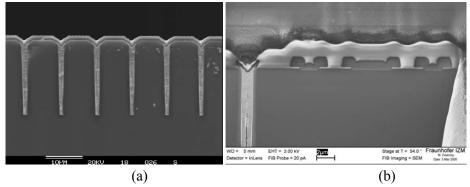

In 2005, a 1.2  $\mu$ m-diameter, 25  $\mu$ m-tall TSV technology was demonstrated by Wieland *et al.* [25] (Fig. 1.11). The dielectric layer deposited by sub atmospheric chemical vapor deposition (SACVD) was highly conformal O<sub>3</sub>/TEOS oxide. The vias were then filled with W using Metal Organic Chemical Vapor Deposition (MOCVD). See [26] for details.

Figure 1.11 TSV technology proposed by Wieland *et al.* [25]. (a) Test wafer with W-filled Inter Chip Vias (ICVs) and interconnect metallization. (b) FIB image of a metal gate NMOS transistor (w/l = 20/2) with W-filled ICV near active area.

As shown above, the fabrication of many TSV sizes have been demonstrated so far. Keeping in mind that the semiconductor industry is constrained by the cost, the main focus now is improving each process step in order to achieve higher throughput. Hereafter are some technological trends to achieve this goal.

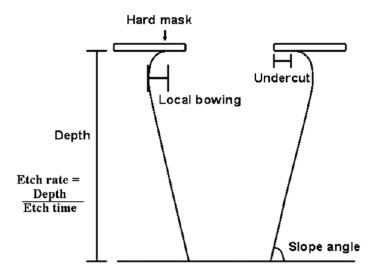

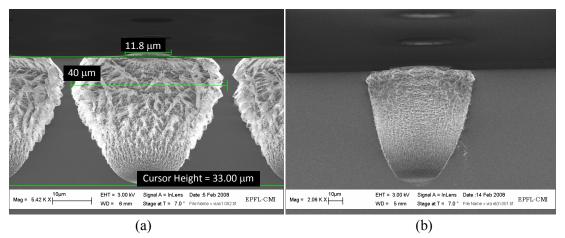

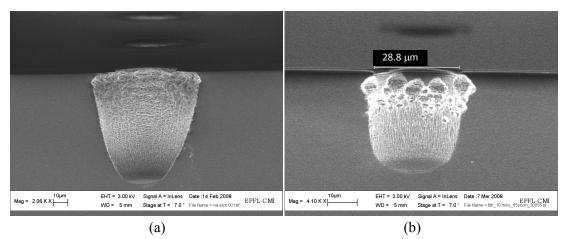

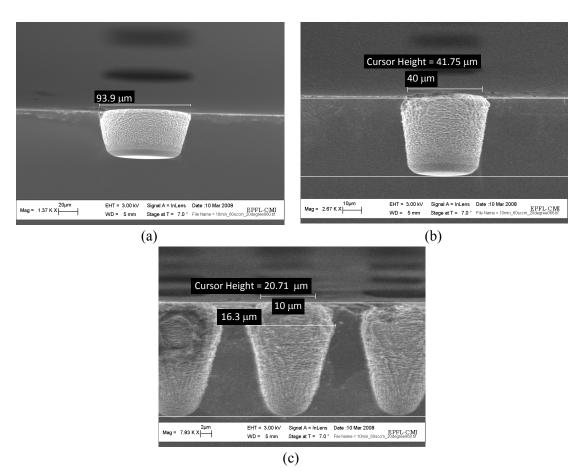

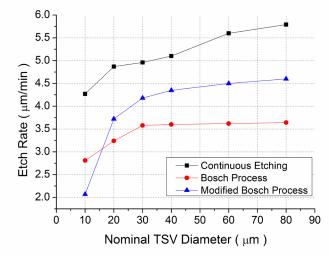

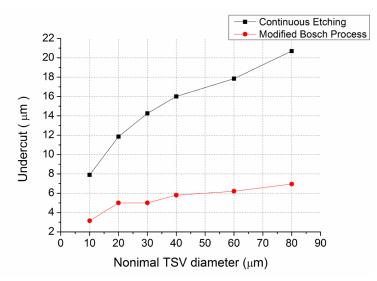

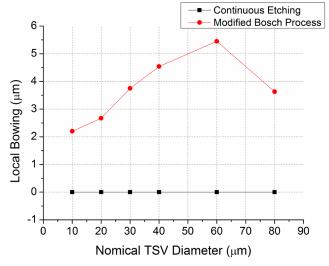

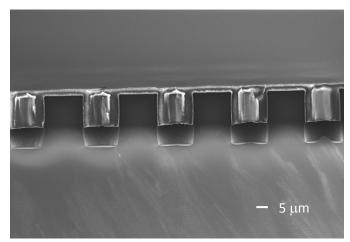

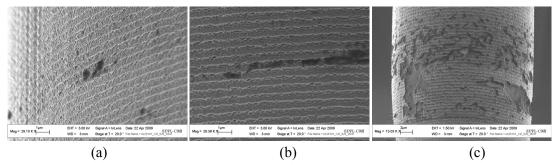

DRIE processes providing higher etch rate, smaller scallop, smoother via sidewall, higher selectivity of silicon to mask, and higher aspect ratio have been demonstrated [27, 28].

MOCVD and Atomic Layer Deposition (ALD) are relatively high-cost processes. Less expensive physical vapor deposition (PVD) methods have been demonstrated with good results on high AR structures. Weichart *et al.* presented a High Power Impulse Magnetron Sputtering (HPIMS) technique which achieved continuous layers of Ti and Cu inside TSVs with an AR of 10 [29]. Ionized Metal Plasma (IMP) Sputtering has been demonstrated to achieve conformal seed layer on the via sidewalls [30]. IMP sputtering is a magnetron sputtering system coupled with an inductively coupled plasma (ICP; RF 13.56 MHz) which ionizes gas atoms and a substrate bias (RF 27 MHz) that accelerates the ionized atoms towards the substrate. RF copper deposition with re-sputter technology is also able to improve copper step coverage, as demonstrated by Wu *et al.* [31]. TaN is deposited prior to sputter etch. So, after sputter etch, Ta sputtering will achieve a better coverage on the sidewall. This helps to improve the copper RF sputtering coverage.

Furthermore, completely filling the vias without void is timely. Less timing-consuming electroplating is being worked at to lower the cost. Some solutions have been proposed [32, 33, 34].

Electrografting has been demonstrated by Alchimer® to provide extremely uniform film coating stacks (isolation, barrier and fill layers) on TSVs with aspect ratios of 10:1 or 20:1 [35]. This fluid-based process eliminates voids, opens, and shorts, enables higher yields while also saves cost substantially.

#### MEOL TSV or Via-Middle Approach

BEOL TSV is a matter of supply chain issue. Processing TSVs on a chip fabricated somewhere else is not welcome since every house and foundry wants to make responsibility clear. So an intermediate approach known as "middle end of line (MEOL) TSV process" is the actual preferred solution. This approach leverages existing IC foundry infrastructure to fabricate TSVs after the FEOL processing and prior to BEOL processing. So after the chips are achieved, TSV structures are already fabricated inside. Later the wafers are to be thinned to expose TSVs from the wafer backside. After dicing, known good dies (KGDs) are to be stacked to the 3D stacks.

One advantage of MEOL TSV process over the via-last approach is the larger process temperature window. Here, the temperature can be as high as the BEOL metal process (450 °C). This is a foundry-level solution as well.

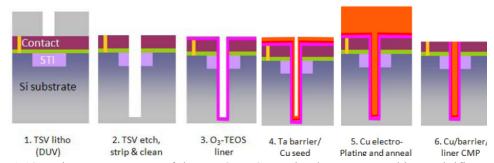

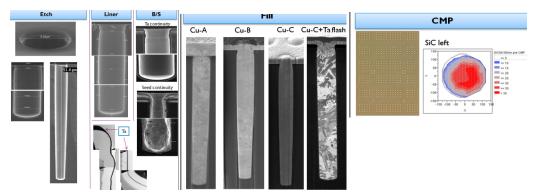

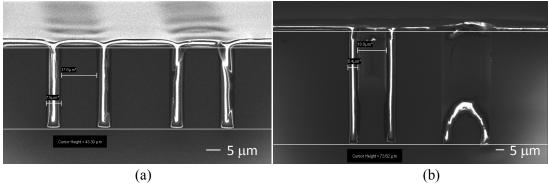

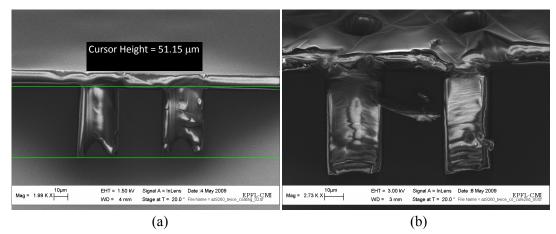

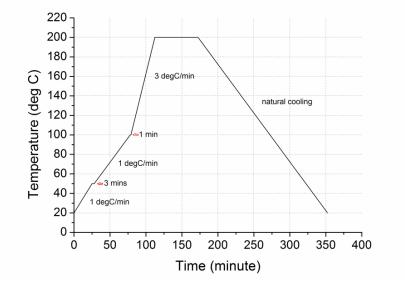

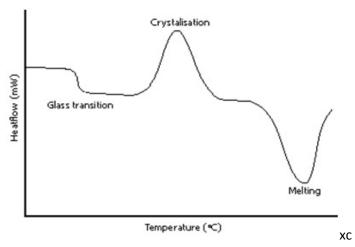

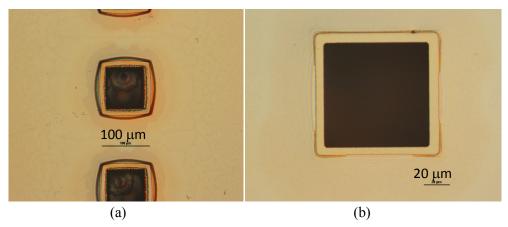

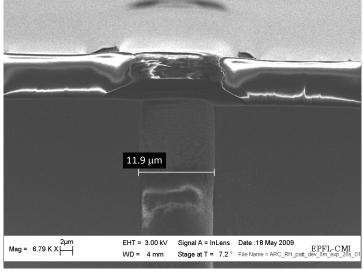

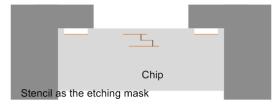

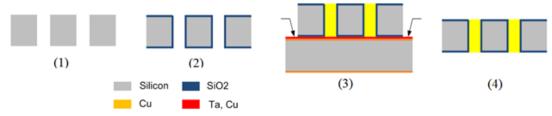

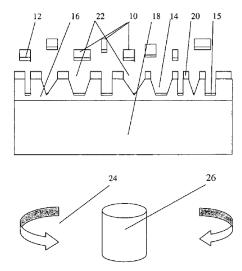

In 2011, Redolfi *et al.* presented a 300 mm industry-compliant via-middle TSV module, integrated with an advanced high k/metal gate CMOS process platform [36]. TSVs were fabricated following the Bosch process after contact definition and before the first metal layer. The target for the copper diameter was 5µm and the via depth in the silicon substrate was 50 µm. Dense structures had a pitch of 10µm. The vias were filled with TEOS/O3 oxide to reduce via-to-substrate capacitance and leakage and a Ta layer was used as the Cudiffusion barrier. The via was finally filled with electroplated copper. Copper was thermally treated before CMP to minimize copper pumping effects (Fig. 2.21). The processing (Fig. 1.12 and Fig. 1.13) was integrated as part of a 65 nm node CMOS fabrication module and validated with regular monitoring of physical parameters. The module was tested and integrated to a thinning and backside passivation flow. However, the electrical characteristics of these TSVs were not presented.

Figure 1.12 Major process steps of the MEOL TSV technology proposed by Redolfi et al. [36].

Figure 1.13 Results of the major process steps in the MEOL TSV technology proposed by Redolfi *et al.* [36].

Bringing 3-D devices based on through-silicon via (TSV) is taking longer than expected. It is only in this year (2011) that a breakthrough has been achieved by Samsung. A 1-Gbit DRAM with a 512-pin wide I/O interface intended for mobile applications such as smartphones and tablet computers was announced [37]. The chip was implemented in a manufacturing process technology somewhere between 50 nm and 59 nm. It was based on a MEOL TSV technology and housed in a 3-D package. Shipments are targeted for 2013. The fabricated TSVs (Fig. 1.14) were 7.5  $\mu$ m in diameter, and exhibited a resistance of 0.22 - 0.24  $\Omega$  and a capacitance of 47.4 fF.

Figure 1.14 TSV technology proposed by Samsung [37].

#### BEOL TSV or Via-Last TSV Processed after Bonding

Another option is to fabricate TSVs after chip-to-wafer (C-to-W) or wafer-to-wafer (W-to-W) bonding. The detailed introduction to bonding techniques can be found in the next section.

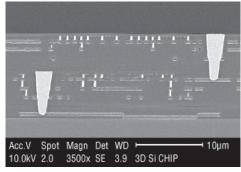

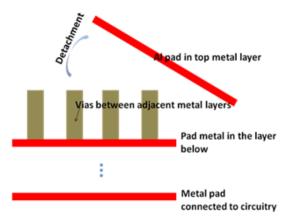

In this approach, TSVs are etched through the silicon substrate and the bonding interface landing at the expected metal pad made during BEOL metal process. The thermal budget depends on the bonding and BEOL metal process, so it can be the lowest among the four solutions discussed so far. Lincoln lab SOI TSV process can be viewed as such a process (Fig. 1.15). Basically, a SOI wafer with integrated CMOS devices is face-to-face bonded to the bottom carrier wafer. The buried SiO<sub>2</sub> layer in the upper SOI wafer is then etched away, leaving the thin upper part of the SOI wafer. TSVs are then etched through the thin upper wafer and the dielectric layer of the bottom wafer, finally landing on targeted metal pads [38].

Figure 1.15 TSV technology proposed by Lincoln Lab [38].

#### Summary of TSV Technologies

As explained in this section, different technologies have been developed and tested to integrate TSVs into the standard CMOS process flow. The preferred via size is now less than 30  $\mu$ m; eventually, it will go down to 5  $\mu$ m for memory-on-logic stacks and  $\leq$  2  $\mu$ m for heterogeneous 3D integration (Fig. 1.1). The drives to get via size as small as possible from a technology point of view are: 1) less thermal expansion mismatch between Si (2.5e-6/°C) and Cu (17.5e-6/°C); 2) lower cost using less Cu plating time to fill the vias; 3) higher throughput; 4) more space for routing. From an electrical performance point of view, smaller vias are with less parasitic capacitance meaning potential shorter delay and less power consumption.

#### 1.2.2 Thinning

Thinning or wafer thinning is one of the enabling technologies for 3D integration at the point of enabling TSV shrinking. Generally, the silicon wafer to be thinned is temporarily glued to a carrier wafer and then thinned from the backside to less than 50  $\mu$ m. A summary of thinned silicon wafer thickness for 200 mm or 300 mm wafers is shown in Table 1.1. For general

products, the minimum thickness of thinned wafer will maintain at 30 µm. For ultra-thin package, the minimum thickness of thinned wafer achieved was 20 µm, and will eventually go down to 10 µm. Whether going further down to 5 µm is still doubtful. Anyhow, transistors require a certain bulk thickness to ensure the expected performance. And the technological difficulties in the process itself need to be solved. The loading could damage the devices.

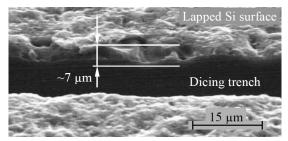

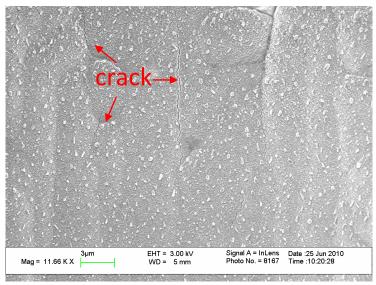

The thinning process usually starts from lapping or grinding the wafer down to a certain thickness which is thicker than the target. Then, polishing is used to refine the rough surface (Fig. 1.16) and to remove the stress concentrated at the cracks caused by the rough grinding. Other techniques to further relieve this stress can be processed after the polishing. For example, CMP and DRIE. As reported by Chen et al. [39], the chip strength can be enhanced after DRIE thinning.

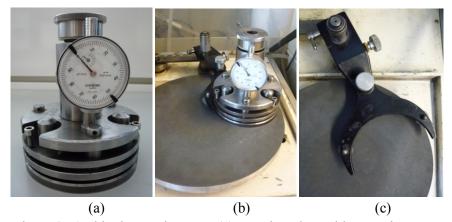

A critical issue for successful thinning is temporary gluing/bonding of the silicon wafer with the carrier or handling wafer. Without a good solution, delamination (Fig. 1.17-a), bubble (Fig.1.17-b) and wafer chipping (Fig.1.17-a) could happen. Thickness uniformity is important as well (Fig. 1.17-c). To settle these problems, many techniques have been proposed [42, 43] and many materials have been tested [42, 43, 45, 46].

The time to perform thinning is related to the TSV fabrication approach adopted (Section 1.2.1). Finally, a wafer thinned to less than 50 µm is of good flexibility (Fig. 1.18).

Figure 1.16 Surface after lapping and defect depth of a Si sample lapped with 3 μm Al<sub>2</sub>O<sub>3</sub> abrasive particles. Pits as deep as 7 µm have been found in SEM micrographs [44].

Table 1.1 Thinned Silicon Wafer Thickness 200 mm / 300 mm [40, 41].

|                    | Voor of                       | Min. Thickness (microns)      | Min. Thickness (microns) |

|--------------------|-------------------------------|-------------------------------|--------------------------|

| Year of Production | For General Products, Such As | For Ultra-Thin Packages, Such |                          |

|                    | Image Sensors                 | As Smart Card                 |                          |

|                    | 2007                          | 70                            | 20                       |

| Year of Production | Time Time Kilebb (Ilinerolib) | Titin. Timetimess (imerons)   |

|--------------------|-------------------------------|-------------------------------|

|                    | For General Products, Such As | For Ultra-Thin Packages, Such |

|                    | Image Sensors                 | As Smart Card                 |

| 2007               | 50                            | 20                            |

| 2008               | 50                            | 20                            |

| 2009               | 50                            | 15                            |

| 2010               | 50                            | 15                            |

| 2011               | 40                            | 10                            |

| 2012               | 40                            | 10                            |

| 2013               | 30                            | 10                            |

| 2014               | 30                            | 10                            |

| 2015               | 30                            | 5                             |

| 2016               | 20                            | 5                             |

Manufacturable solutions are known. Interim solutions are known.

Figure 1.17 Main problems caused by thinning. (a) Thickness nonuniformity and warpage. (b) Thin wafer delamination and breakage. (c) Chipping at the wafer edge.

Figure 1.18 50 μm-thick 200 mm silicon wafer showing flexibility [42].

#### **1.2.3 Bonding**

As another key enabling technology for 3D integration, bonding plays an important role to achieve the final stack.

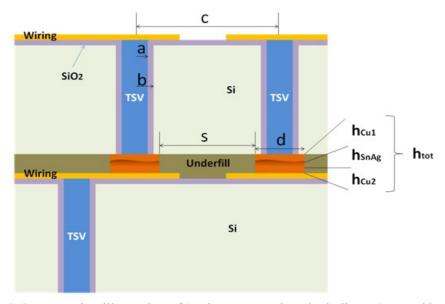

Many bonding techniques have been studied for 3D integration, among which we will highlight direct oxide bonding [47], polymer bonding [48], Cu-Cu thermal compression bonding [49], and Cu/Sn/Cu eutectic bonding [50, 51]. The first three techniques are wafer-level processes, while the last one mainly works at chip level and depends on flip chip technology.

For wafer-level bonding processes, the electrical connections between the stack are usually achieved through metal or oxide fusion under very high pressure and usually high temperatures (> 350 °C). The surface cleanliness and roughness are the key factors deciding the bonding quality. Surface pretreatment to remove oxidation is very complicated and the surface roughness requires < 1.0 nm Root-Mean-Square (RMS). The great advantage is that they can achieve very small TSV dimensions (< 5  $\mu$ m) and very high TSV densities (pitch < 10  $\mu$ m). From the research point of view, direct oxide bonding and polymer bonding should work with the BEOL TSV after bonding (Section 1.2.1, Part 4), while Cu-Cu thermal compression bonding should be proceeded after TSVs are fabricated (Section 1.2.1, Part 2 and 3). The cost of wafer-bonding processes is still very high, so it is not widely adopted as the chip-level bonding process nowadays.

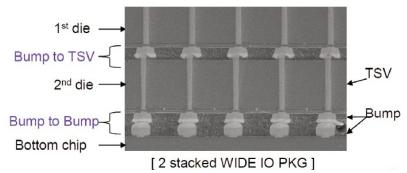

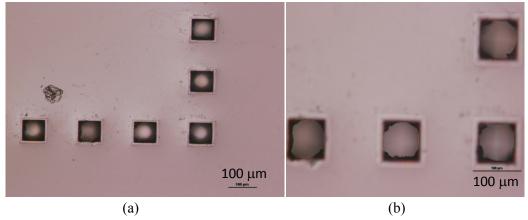

In the chip-level eutectic bonding processes, the connections are achieved by thermal compression on the eutectic solder bumps or balls. Thus, the bonding temperatures required are usually lower than the wafer-level processes, and the requirements on surface pretreatment are moderate. The cost is also low. But the bump size and density are limited. The dimension varies from minimum of about 8 µm to several tens of micrometers.

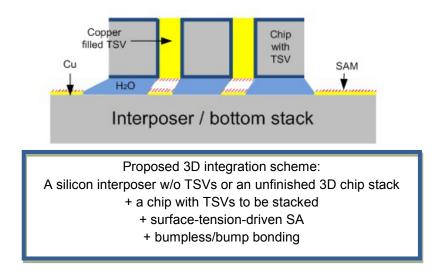

#### 1.2.4 3D Integration Schemes

Bonding technologies lead to a separation of 3D integration schemes into two main streams, which are named by Lau as "3D silicon integration" and "3D chip integration" [52]. Along this thesis, our work will cover many aspects of the 3D chip integration technology.

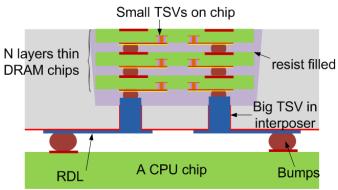

For 3D silicon integration, stacking is processed at the wafer level. Because the wafer-level bonding processes, e.g. direct oxide bonding, polymer bonding and Cu-Cu thermal compression bonding, are directly connecting two pads, no bump is required and so the footprint of inter-layer connections (TSV plus bonding/landing pad) can be decreased. Thus, tiny TSV dimensions as small as a few microns are achievable in this scheme. As mentioned in Section 1.2.3, wafer-level bonding technologies are costly and technologically challenging. Not only so, it also lacks of EDA design tools and is waiting for the whole product chain support.

For 3D chip integration, TSVs are fabricated on the wafers, mostly using the via-middle approach. Then, the chips with TSVs and bonding bumps are diced and bonded to the bottom chip stack or wafer using flip chip technology. As the dimension of the bumps is limited by the technology, the footprint of the inter-layer connection cannot be as small as that in 3D silicon integration. Today, 30  $\mu$ m-diameter TSV is used for 3D chip integration; eventually, it is expected to go down to 5 - 10  $\mu$ m.

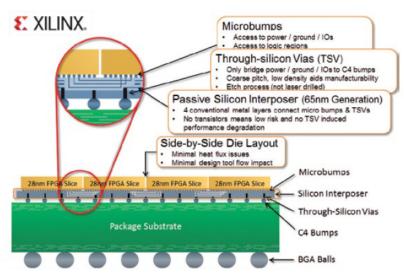

The concept of interposer, no matter it is a 2.5 interposer or 3D interposer, is popular in 3D chip integration. The difference between 2.5D and 3D is just whether dies are stacked on one side or both sides to the interposer. ("2.5D" means that TSVs might not be needed if one flip chip bonding is performed for the stacking). Interposers are also categorized in passive and active ones, depending on whether or not active devices are fabricated. If not, the TSV process will benefit from a wider temperature process window.

Some successful interposers are already on the market, such as Xilinx [53, 54, 55] and Toshiba [3], and more are on the way. Actually many vendors are picturing 3D products with interposers in the near future. Section 1.3 will talk about it more.

The wide adaptation of interposers is motivated by the inadequacy of EDA tools, testing schemes and industrial standardization. First, the commercial EDA tools do not support 3D design and simulation with TSVs. Then, splitting the inter-layer connection components from the circuit is the safest choice: signal integrity (SI) on the chip is ensured by circuit designers, while the TSVs in the interposer are analyzed separately to ensure the SI. Moreover, chips fabricated with standard technologies ask for a signal redistribution layer (RDL) to match the I/Os designed according to different industrial standards. Moreover, fabricating the RDL and TSVs in the interposers instead of in the chips can minimize the risk of chip damages and increase the yield. The benefit from the increased yield outweighs the additional costs brought by the additional wafer as interposer and the interposer fabrication.

To summarize this section, we have completed an overview of the existing 3D fabrication technologies. In this perspective, our work will cover the key technologies, i.e. TSV, bonding and thinning. But it should be noted that there are still many aspects not mentioned, e.g. metrology and testing. In the next section, we will mainly look at the existing 3D applications.

#### 1.3 3D Applications

Actually all the commercial 3D products are based on interposers, either glass or silicon. Until 2010, in the 3D interposer market [56], logic stacking (logic on logic and logic on memory) solutions are still lacking because small TSV dimensions (5 µm in diameter) and large TSVs density are required.

Xilinx presented their 3D FPGA work in 2010 as the first 3D stacking using an advanced logic technology (28 nm Virtex-7 LX2000T multi die FPGA) (Fig. 1.19) [53, 54, 55]. In this

approach, four dies were communicating through the metal stacks fabricated in the silicon interposer and they were at the same time connected to the package substrate through TSVs. However, it is still not stacking logic dies vertically on each other.

#### 1.4 3D Circuit Design and System Architecture

In the past 10 years, many aspects concerning 3D circuit design techniques have been studied, e.g. placement and partitioning, EDA, testing schemes, thermal and power analysis and so on [57, 58, 59, 60, 61, 62]. System architects mainly optimized computing systems by focusing on memory and/or logic stacking. Many interesting works have been presented but only a few are provided here [63, 64, 65, 66, 67, 68].

In these studies, great benefits have been demonstrated after using TSVs. One of the popular topics these days is the wide I/O (bandwidth) interface gained with TSVs. Less power consumption with greatly increased bandwidth has been demonstrated in the recent Samsung memory stacking [37].

A close and plain examination of TSV as a connection itself could be helpful to achieve further benefits. Firstly, TSVs can work at very high frequencies over 60 GHz [69]. In 3D digital systems, this inborn high bandwidth has not been exploited and is wasted on the slow data transmission rate. Secondly, many works were dedicated to improve the performance through novel inter-layer bus or routers ( for Network on Chip (NoC)) designs. But for system architects, the physical dimension is usually merged in the study, so TSVs' real physical dimension is ignored in many cases and thus its influence on circuits and systems has not been explored.

In all, to address these two issues requires a well-understanding of both technology feasibility and system requirements.

Figure 1.19 Xilinx introduced 3D silicon interposers with TSVs for wide I/O interface in FPGA products [53]. Courtesy of Xilinx.

#### 1.5 Outline of This Thesis

This thesis work started in September 2007 when controversies of 3D technologies widely existed both in academy and industry.

The general aim was to develop a die-level 3D stacking scheme at EPFL. So, the work had to cover all the aspects of the key 3D technologies in order to provide a well-balanced and workable solution. The existing works mainly adopted BEOL TSV approach at the wafer

level. However, in the context of a university project, our resource was limited at diced standard chips fabricated in the foundry. To post-processing TSVs on these singulated dies was of a greater challenge. Firstly, the way to handle and align the dies was a big problem. Secondly, we were facing many technology constraints, such as lacking of necessary instruments for 3D integration, e.g. a wafer grinding and polishing machine for wafer thinning and the die bonding machine.

Our work to tackle these technology problems will be presented in Chapters 2, 3 and 4.

In **Chapter 2**, a thorough study of the TSV fabrication feasibility based on the clean room facilities in Center of MicroNanotechnology, EPFL (hereafter referred to as CMI) will be performed. All the four TSV processes replying on wafer-level processes will be detailed in that chapter.

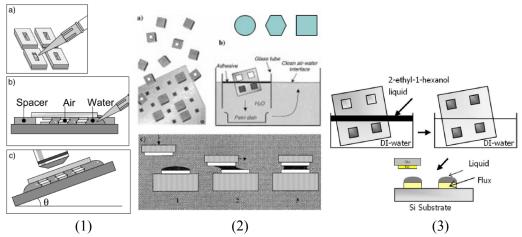

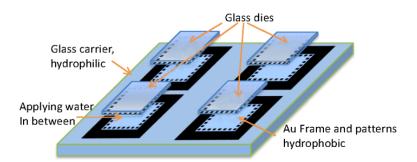

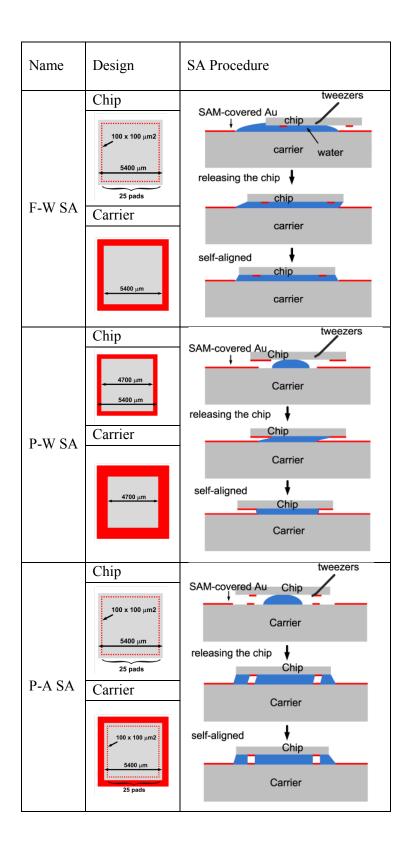

In **Chapter 3**, the feasibility of precise chip attachment to a carrier wafer with the available materials and technologies will be studied first. This is the prerequisite of the dielevel TSV post-processing. Seeing the limitations, self-alignment (SA) techniques were studied for a better alignment and a workable process. Four SA techniques, namely "gravitational SA", "hydrophobic SA", "electrostatic SA" and "magnetic SA", will be well studied, while the most successfully one, the hydrophobic SA will receive special attention in **Chapter 4**. SA techniques will be demonstrated as good solutions to achieve the final chip stacking as well as temporary die attachment and alignment techniques to post-process TSVs on dies.

Our work in the first four chapters will well-establish a 3D chip integration platform based on die-level post-processing. These studies will lead to a more realistic and practical study in the following chapters.

In **Chapter 5**, we will continue with a discussion of TSV characteristics, from silicon area cost to electrical performance and power consumption. These will clarify the key reasons of going for 3D. As TSVs' area is actually not negligible, and TSVs support very high bandwidths, exploiting this high bandwidth through inter-layer serialization could be a good method to save the precious silicon area consumed by the TSVs. We will discuss about the circuit implementation of the inter-layer serial links and provide a theoretical analysis of the future of this technique with smaller TSVs.

In **Chapter 6**, the serial links will be applied into 3D memory-on-core system simulators to evaluate the system performance. The TSV dimensions assumed in the simulation are practical numbers from the 3D chip integration technology.

In **Chapter 7**, we will conclude the thesis with an outlook on future developments.

#### Reference

- 1. W. Shockley, "Semiconductive Wafer and Method of Making the Same," United States Patent 3,044,909, July 17, 1962.

- 2. Y. Akasaka, "Three-Dimensional IC trends," *Proceedings of IEEE*, Vol. 74, No. 12, 1986, pp 1703.

- 3. Iwate Toshiba Electronics, Product name: Chip Scale Camera Module: CSCM, <a href="http://www.toshiba-iwashiba.co.jp/eng/product/cscm.htm">http://www.toshiba-iwashiba.co.jp/eng/product/cscm.htm</a>.

- 4. 3D-IC & TSV Interconnects 2010 Reports, Yole Development.

- 5. E. M. Chow, A. Partridge, C. G. Quate, and T. W. Kenny. "Through-Wafer Electrical Interconnects Compatible with Standard Semiconductor Processing." *Processings of Solid-State Sensor and Actuator Workshop*, pages 343-346, Hilton Head Island, SC, USA, June 4-8, 2000.

- 6. M. Kawano, N. Takahashi, Y. Kurita, K. Soejima, M. Komuro, and S. Matsui, "Three-Dimensional Packaging Technology for Stacked DRAM With 3-Gb/s Data Transfer", *IEEE Transactions on Electron Devices*, Vol. 55, No. 7, July 2008.

- 7. T. Bauer, "High Density Through Wafer Via Technology," *NSTI-Nanotech* 2007, www.nsti.org, ISBN 1420061844, Vol. 3, 2007

- 8. H. Baltes, O. Paul, and O. Brand, "Micromachined Thermally Based CMOS Microsensors," *Proceedings of the IEEE*, Vol. 86, No. 8, pp. 1660-1678, 1998.

- A. D. Yalçinkaya, "Micromechanical Resonators for Low-Power, Low-Voltage Systems," PhD thesis, Mikroelektronik Centret (MIC), Technical University of Denmark, June, 2003.

- L. L. Lauer, J. L. Shohet, and R. W. Hansen, "Measuring Vacuum Ultraviolet Radiation-Induced Damage," *Journal of Vacuum Science Technology A*, 21 (4): 1253-1259, July/August 2003.

- 11. S. Linder, H. Baltes, F. Gnaedinger, and E. Doering, Fabrication Technology for Wafer Through-Hole Interconnections and Three-Dimensional Stacks of Chips and Wafers, pp. 349-354, 1994.

- 12. S. Linder, "Chip Stacks for Memory Applications," PhD Thesis, Physical Electronics Laboratory, ETH Zürich, 1996.

- 13. M. Heschel, J. F. Kuhmann, S. Bouwstra, and M. Amskov, "Stacking Technology for a Space Constrained Microsystem," *Proceedings of the 11th IEEE International Conference on Micro Electro Mechanical Systems (MEMS ' 98)*, pages 312–317, Heidelberg, Germany, January 26–30, 1998.

- M. Heschel, "Multiple Through-Wafer Interconnects for Stacking of Microelectromechanical Devices," PhD thesis, Mikroelektronik Centret (MIC), Technical University of Denmark, June, 1999.

- 15. M. Heschel and S. Bouwstra," Conformal Coating by Photoresist of Sharp Corners of Anisotropically Etched Through-Holes in Silicon," *Sensors and Actuators A: Physical*, Vol. 70, 1998.

- 16. F. E. Rasmussen, "Electrical Interconnections Through CMOS Wafers," PhD Thesis, the Technical University of Denmark, 2003.

- 17. S. W. Ho, V. S. Rao, O. Kalandar, N. Khan, S. U. Yoon, V. Kripesh, "Development of Coaxial Shield Via in Silicon Carrier for High Frequency Application," *EPTC*, 2007.

- 18. Sonion MEMS A/S, Product Description: 3 mm<sup>3</sup> Smart Silicon Microphone. http://www.soionmems.dk, 2002.

- 19. K. Takahashi and M. Sekiguchi, "Through Silicon Via and 3-D Wafer/Chip Stacking Technology," *Symposium on VLSI Circuits Digest of Technical Papers*, 2006.

- 20. M. Sekiguchi, H. Numata, N. Sato, T. Shirakawa, M. Matsuo, H. Yoshikawa, M. Yanagida, H. Nakayoshi and K. Takahashi, "Novel Low Cost Integration of Through Chip Interconnection and Application to CMOS Image Sensor," 56th Electronic Components and Technology Conference, 2006

- 21. R. Nagarajan, L. Ebin, L. Dayong, S. C. Seng, K. Prasad and N. Balasubramanian, "Development of a Novel Deep Silicon Tapered Via Etch Process for Through-Silicon Interconnection in 3-D Integrated Systems," *56th Electronic Components and Technology Conference*, pp. 383 387, 2006.

- 22. D. S. Tezcan, N. Pham, B. Majeed, P. De Moor, W. Ruythooren and K. Baert, "Sloped Through Wafer Vias for 3D Wafer-Level Packaging," *57th Electronic Components and Technology Conference*, pp. 643 647, 2007.

- 23. P. Benkart, A. Munding, A. Kaiser, E. Kohn, A. Heittmann, H. Huebner, U. Ramacher, "Three-Dimensional Integration Scheme with a Thermal Budget Below 300 °C," *Sensors and Actuators A*, Vol. 139, pp. 350-355, 2007.

- 24. Y. Ohara, Y. Watanabe, K. Lee, T. Fukushima, M. Koyanagi, T. Tanaka, "Development of 5 μm Diameter Backside Cu TSV Technology for 3D LSI," *The International Conference on Electronics Packaging (ICEP)*, 2011.

- 25. R. Wieland, D. Bonfert, A. Klumpp, R. Merkel, L. Nebrich, J. Weber, P. Ramm, "3D Integration of CMOS Transistors with ICV-SLID Technology," *Microelectronic Engineering*, Vol. 82, pp. 529–533, 2005.

- 26. A. Klumpp, P. Ramm and R. Wieland, "3D-Integration of Silicon Devices: A Key Technology for Sophisticated Products," *Proceeding of Design, Automation and Test in Europe*, pp.1678 1683, 2010.

- 27. W. H. Teh, R. Caramto, T. Chidambaram, W. Wang, S. R. Arkalgud, T. Saito, K. Maruyama, and K. Maekawa,"300-mm Production-Worthy Magnetically Enhanced Non-Bosch Through-Si-Via Etch for 3-D Logic Integration," *IEEE Transactions on Semiconductor Manufacturing*, Vol. 23, No. 2, May 2010.

- 28. D. Haynes, "Advances in the Etching of TSVs for IC Packaging Applications," *SEMICON*, 2008.

- 29. J. Weichart, M. Elghazzali, S. Kadlec, and A. P. Ehiasarian, "PVD Processes in High Aspect Ratio Features by HIPIMS," *Proceedings of the 52nd Annual Technical Conference of Society of Vacuum Coaters*, Albuquerque, NM 87122-1914, United States, May 9-14, 2009 Santa Clara, (CA), 201 (2009).

- 30. B.-H. Cho, J.-J. Yun, and W.-J. Lee, "Filling of Very Fine Via Holes for Three-Dimensional Packaging by Using Ionized Metal Plasma Sputtering and Electroplating," *Japanese Journal of Applied Physics*, Vol.46, pp. 1135-1137, 2007.

- 31. H.-J. Wu, R. Shaviv, M. Sriram, W. Wu, A. Pradhan, K. J. Park, J. O'loughlin, K. Chattopadhyay, T. Mountsier and G. Dixit, "Improving Interconnect Reliability via Optimized Barrier/Seed," *Semiconductor International*, Vol. 31, No. 11, Oct. 1, 2008.

- 32. H. Y. Li, E. Liao, X. F. Pang, H. Yu, X. X. Yu, J. Y. Sun, "Fast Electroplating TSV Process Development for the Via-Last Approach," 60th Electronic Components and Technology Conference, 2010.

- 33. A. Keigler, Z. Liu, J. Chiu, J. Drexler, "Sematech 3D Equipment Challenges: 300 mm Copper Plating," Sematech Workshop on Equipment challenges for 3D Interconnect, San Francisco, CA, July 2008.

- 34. I. Teelinck, "Electrochemical Copper Deposition in IC Manufacturing," PhD thesis, University of Gent, 2002.

- 35. Electrografting, http://www.alchimer.com/electrografting#.

- 36. A. Redolfi, D. Velenis, S. Thangaraju, P. Nolmans, P. Jaenen, M. Kostermans, U. Baier, E. Van Besien, H. Dekkers, T. Witters, N. Jourdan, A. Van Ammel, K. Vandersmissen, S. Rodet, H.G.G. Philipsen, A. Radisic, N. Heylen, Y. Travaly, B. Swinnen, E. Beyne, "Implementation of an Industry Compliant, 5×50 μm, Via-Middle TSV Technology on 300 mm Wafers," *61th Electronic Components and Technology Conference*, pp. 1384 1388, 2011.

- 37. J.-S. Kim, C. S. Oh, H. Lee, D. Lee, H.-R. Hwang, S. Hwang, B. Na, J. Moon, J.-G. Kim, H. Park, J.-W. Ryu, K. Park, S.-K. Kang, S.-Y. Kim, H. Kim, J.-M. Bang, H. Cho, M. Jang, C. Han, J.-B. Lee, K. Kyung, J.-S. Choi, Y.-H. Jun, "A 1.2V 12.8GB/s 2Gb Mobile Wide-I/O DRAM with 4×128 I/Os Using TSV-Based Stacking," *ISSCC*, 2011.

- 38. J. A. Burns, B. F. Aull, C. K. Chen, C.-L. Chen, C. L. Keast, J. M. Knecht, V. Suntharalingam, K. Warner, P. W. Wyatt, and D.-R. W. Yost, "A Wafer-Scale 3-D Circuit Integration Technology," *IEEE Transactions on Electron Devices*, Vol. 53, No. 10, October 2006.

- 39. S. Chen, T.-Y. Kuo, H.-T. Hu, J.-R. Lin, and S.-P. Yu, "The Evaluation of Wafer Thinning and Singulating Processes to Enhance Chip Strength," *55th Electronic Components and Technology Conference*, 2005.

- 40. International Technology Roadmap for Semiconductors, 2009.

- 41. International Technology Roadmap for Semiconductors, 20011.

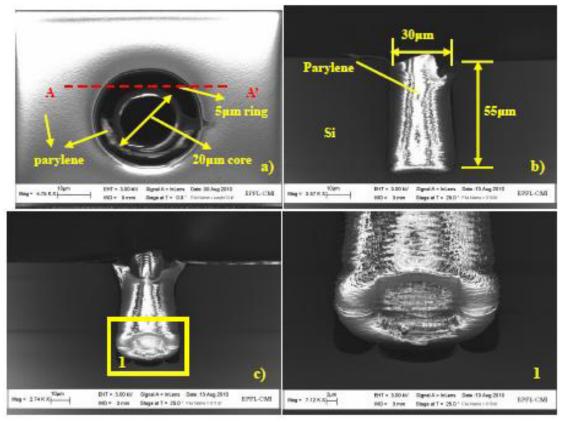

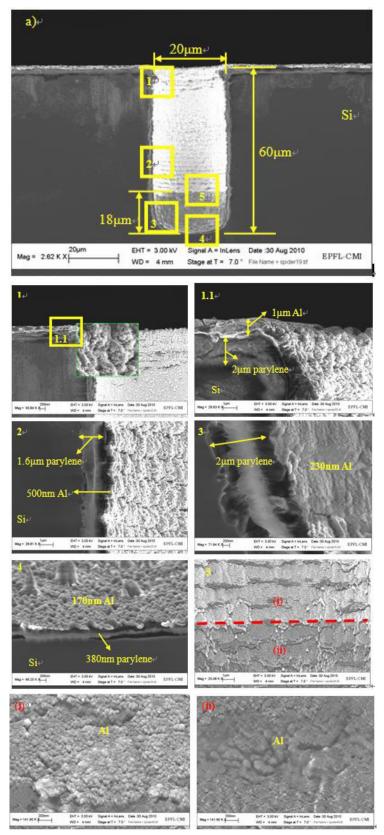

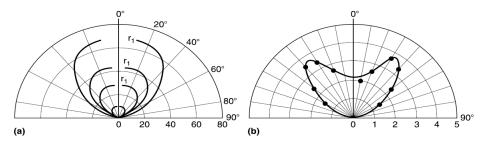

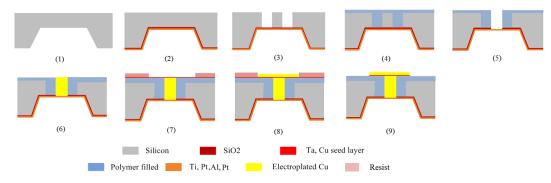

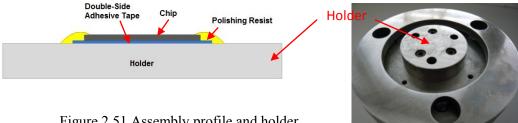

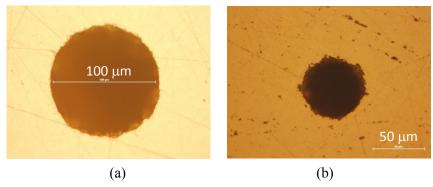

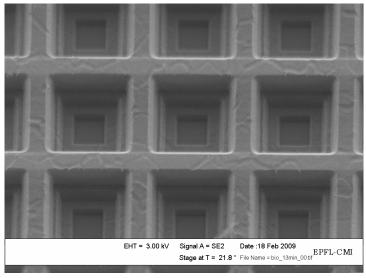

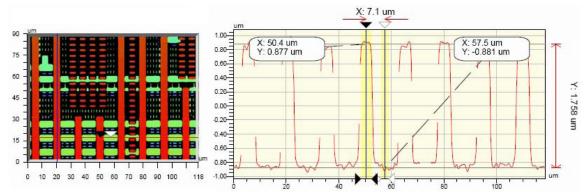

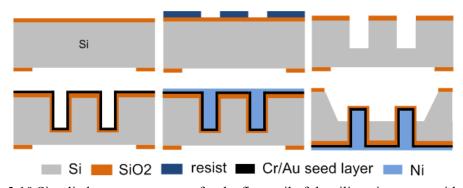

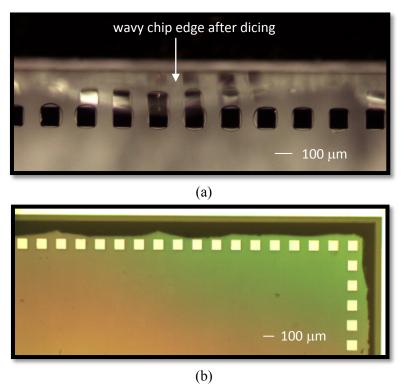

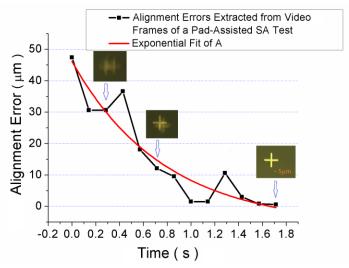

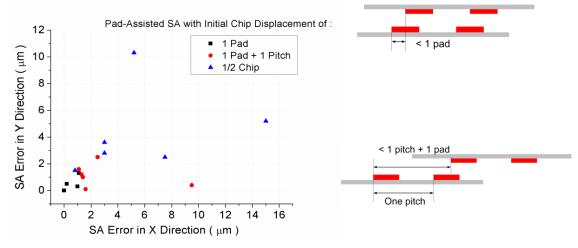

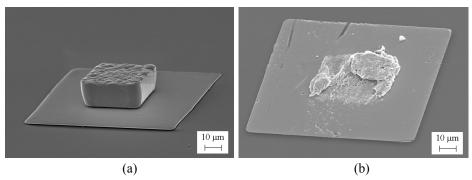

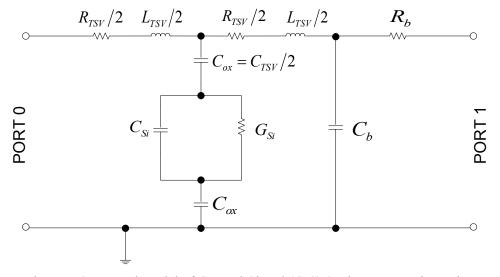

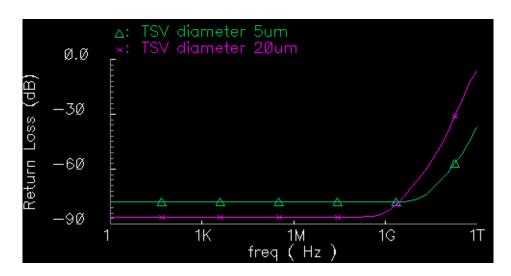

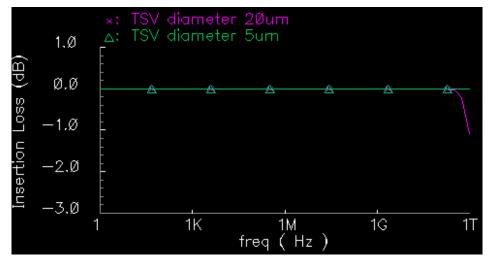

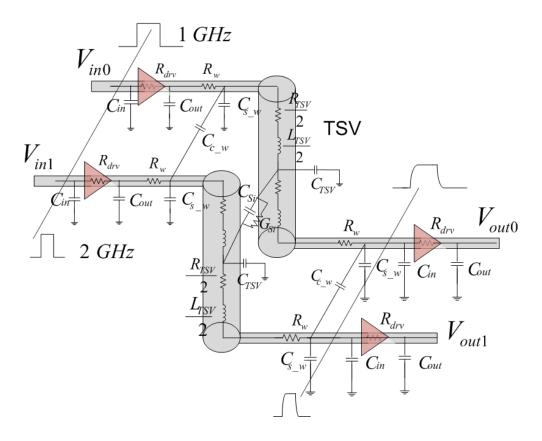

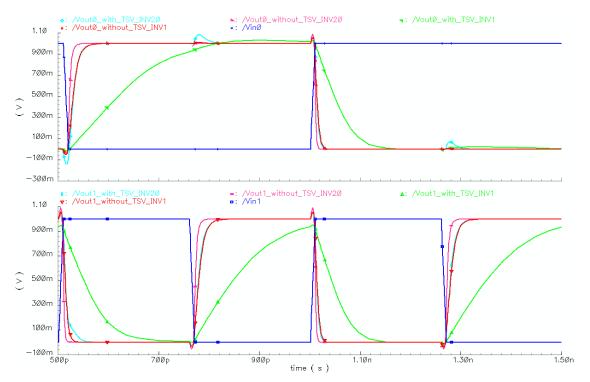

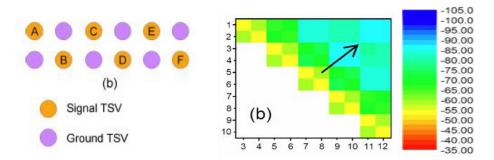

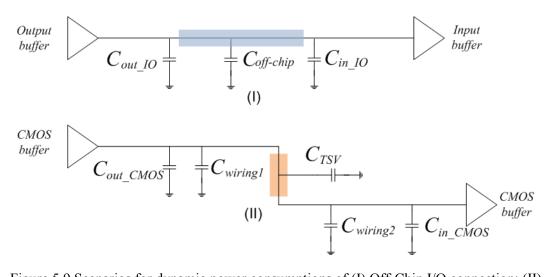

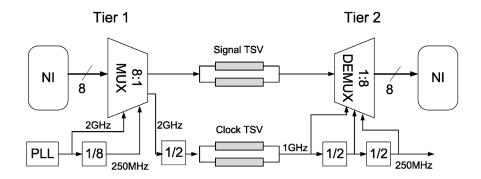

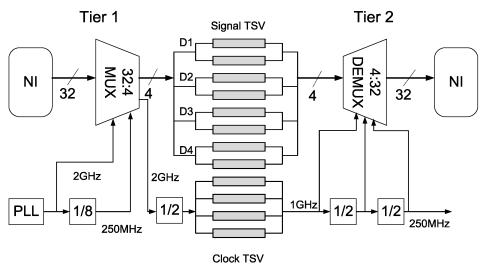

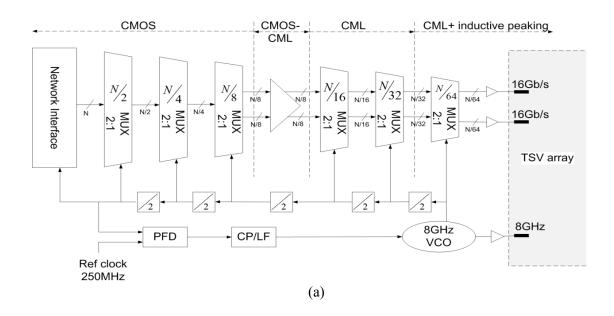

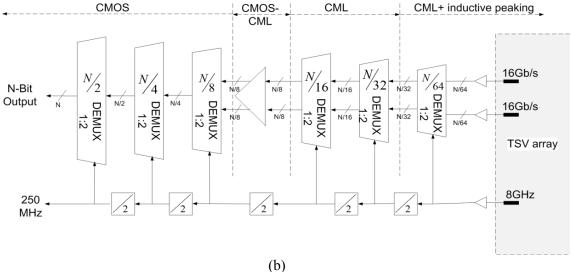

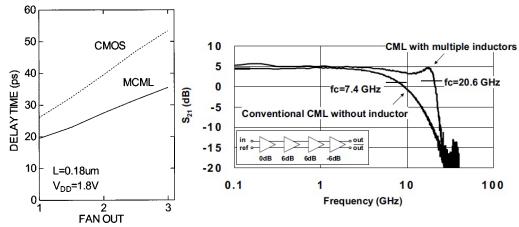

- 42. K. De Munck, "Generic Building Blocks for 3D Integration and Their Application on Hybrid CMOS Image Sensors," PhD thesis, Katholieke Universiteit Leuven, 2008.