### Single-Photon Techniques for Standard CMOS Digital ICs

### THÈSE Nº 4954 (2011)

PRÉSENTÉE LE 13 AVRIL 2011

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

GROUPE CHARBON

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Claudio FAVI

acceptée sur proposition du jury:

Prof. G. De Micheli, président du jury Prof. E. Charbon, directeur de thèse Dr P. Jarron, rapporteur Dr M. Mattavelli, rapporteur Dr L. Wang, rapporteur

# **CONTENTS**

| Ré | Ésumé  | 5        |                                       | 1   |

|----|--------|----------|---------------------------------------|-----|

| Al | ostrac | et       |                                       | vii |

| 1  | Intr   | oductio  | n                                     | 1   |

| 2  | Sing   | gle-Phot | on Detection and Generation           | 5   |

|    | 2.1    | Single   | -Photon Detection                     | 5   |

|    |        | 2.1.1    | Single-Photon Avalanche Diode         | 7   |

|    | 2.2    | Photor   | Generation                            | 15  |

|    | 2.3    | Photor   | Transport and Modulation              | 17  |

| 3  | Sing   | gle-Phot | on Communication                      | 21  |

|    | 3.1    | Buildi   | ng Blocks                             | 25  |

|    | 3.2    | Theory   | y and Limits                          | 27  |

|    |        | 3.2.1    | Time Resolution Limits                | 27  |

|    |        | 3.2.2    | Channel Capacity                      | 28  |

|    | 3.3    | Time o   | discrimination                        | 36  |

|    |        | 3.3.1    | Architecture                          | 40  |

|    |        | 3.3.2    | Digital Calibration                   | 45  |

|    |        | 3.3.3    | Results                               | 49  |

|    |        | 3.3.4    | Discussion                            | 62  |

|    |        | 3.3.5    | 130 nm FPGA TDC implementation        | 64  |

|    | 3.4    | Conclu   | usions                                | 66  |

| 4  | Sing   | le-Phot  | on Processing and Readout             | 67  |

|    | 4.1    | Proces   | ssing Techniques                      | 67  |

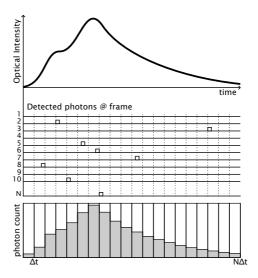

|    |        | 4.1.1    | Time-Uncorrelated Techniques          | 67  |

|    |        | 4.1.2    | Time-Correlated Techniques            | 68  |

|    |        | 4.1.3    | Spatio-Temporal Correlated Techniques | 70  |

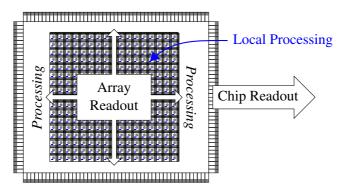

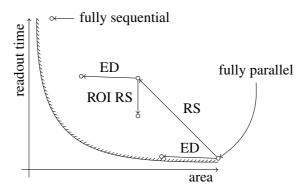

|    | 4 2    | Reado    | ut Strategies                         | 71  |

|    |                  | 4.2.1   | Array Readout                       | 73  |  |  |

|----|------------------|---------|-------------------------------------|-----|--|--|

|    |                  | 4.2.2   | Chip Readout                        | 79  |  |  |

|    | 4.3              | Case s  | tudies                              | 79  |  |  |

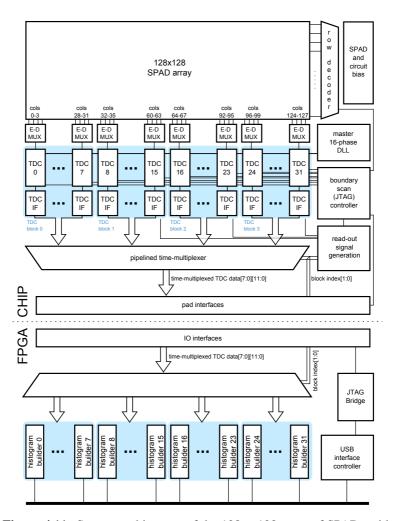

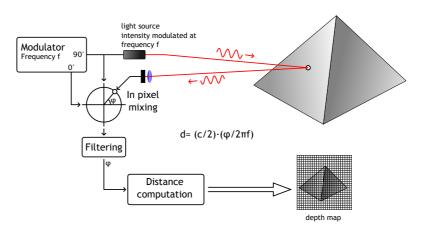

|    |                  | 4.3.1   | Case study 1: LASP 3D camera        | 80  |  |  |

|    |                  | 4.3.2   | Case study 2: SPSD 3D camera        | 87  |  |  |

|    | 4.4              | Conclu  | asion                               | 88  |  |  |

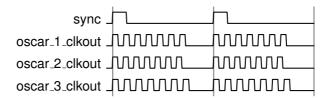

| 5  | Sing             | le-Phot | on Clocking                         | 89  |  |  |

|    | 5.1              | Motiva  | ation                               | 89  |  |  |

|    | 5.2              | Archite | ecture                              | 94  |  |  |

|    |                  | 5.2.1   | Fixed Frequency Oscar               | 95  |  |  |

|    |                  | 5.2.2   | Variable Frequency Oscar            | 97  |  |  |

|    |                  | 5.2.3   | Metastability                       | 99  |  |  |

|    |                  | 5.2.4   | Skew and Jitter                     | 100 |  |  |

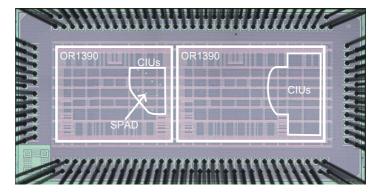

|    | 5.3              | Practic | cal implementation of Oscar in VLSI | 100 |  |  |

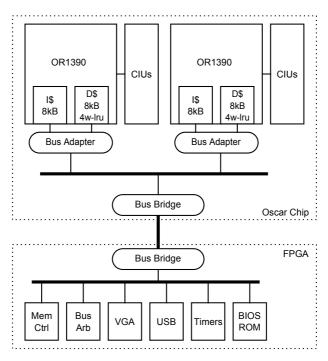

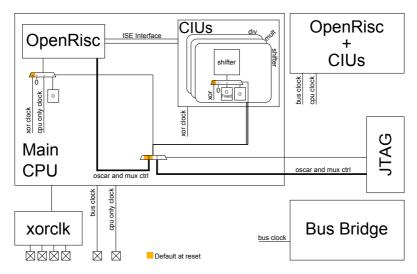

|    |                  | 5.3.1   | Processor and Custom Instructions   | 104 |  |  |

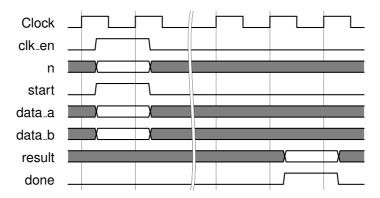

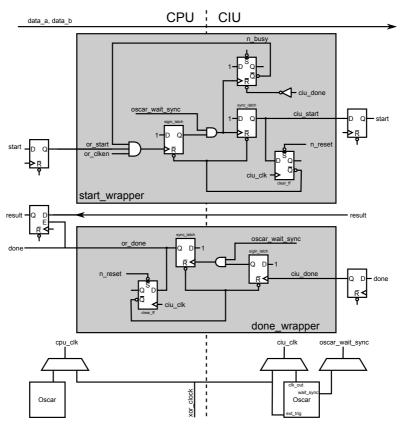

|    |                  | 5.3.2   | Custom Instruction Units and Oscar  | 105 |  |  |

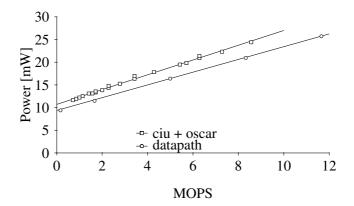

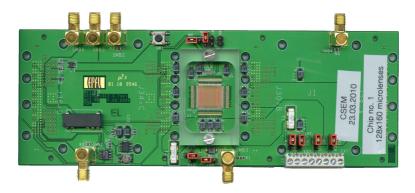

|    | 5.4              | Results | S                                   | 107 |  |  |

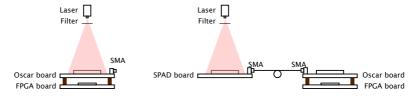

|    |                  | 5.4.1   | System Pre-validation               | 107 |  |  |

|    |                  | 5.4.2   | Test setup and methodology          | 107 |  |  |

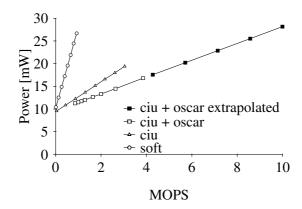

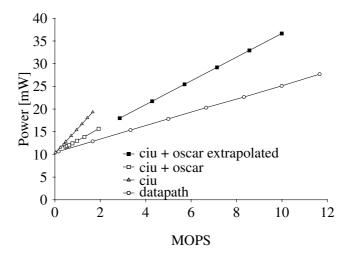

|    |                  | 5.4.3   | Measurements                        | 111 |  |  |

|    | 5.5              |         | sion                                | 114 |  |  |

|    | 5.6              | Conclu  | asion                               | 116 |  |  |

| 6  | Out              | look    |                                     | 119 |  |  |

| Li | List of acronyms |         |                                     |     |  |  |

| Re | eferen           | ces     |                                     | 129 |  |  |

| Al | out t            | he Auth | or                                  | 151 |  |  |

| Ρı | ıblica           | tions   |                                     | 153 |  |  |

### RÉSUMÉ

L'arrivée des photodétecteurs à photons individuels connus sous l'acronyme de SPAD (Single-Photon Avalanche Diode) dans un procédé de fabrication CMOS standard, a ouvert de nouvelles perspectives dans l'intégration de ces capteurs ultra-sensibles avec de la logique digitale.

La lumière a des propriétés intéressantes qui attirent les chercheurs en informatique et électronique depuis longtemps. Sa nature ondulatoire et donc sans masse fait d'elle une candidate idéale pour remplacer les électrons lorsque cela n'est pas déjà le cas. Ceci est notamment le cas pour les transferts de données à longue distance. Cependant une nouvelle tendance peut être observée. Les chercheurs se tournent vers la photonique, la science de la lumière, pour communiquer également à courte distance. Une des raisons de cette tendance est l'efficacité accrue en consommation énergétique. En effet, les photons, les particules élémentaires de la lumière, à l'instar des électrons, ne subissent pas d'effets résistifs, capacitifs ou inductifs. La nature ondulatoire de la lumière permet aussi aux concepteurs de se libérer de problèmes tels que le *cross-talk* et l'injection de bruit tout en tirant meilleur parti des phénomènes d'interférence. Cependant, la photonique n'est pas encore la panacée et nous ne pensons pas qu'elle remplacera entièrement un jour l'électronique traditionnelle. Une combinaison des deux sera très certainement adoptée afin de profiter au mieux des deux mondes.

La conception de circuits intégrés digitaux en technologie CMOS fait face à de nombreux obstacles et il n'est pas clair si la technologie sera encore capable, dans le futur, de fournir des réductions de taille, des performances accrues et des consommations réduites. Dans ce travail, nous présentons trois investigations où la photoniques à base de SPADs est intégrée avec la technologie digitale CMOS.

Les trois contributions principales de cette thèse sont: des paradigmes de communication à base de photons individuels, des techniques de traitement et de lecture de capteurs à photons individuels, et des méthodes de distribution d'horloge et de synchronisation basées sur les SPADs. La communication à base de photons individuels est proposée en combinant des SPADs avec des

TDCs ultra-rapides avec une modulation dédiée. Dans ce contexte, les limites théoriques de la capacité du canal en présence de bruit et d'autres sources de non-uniformité liées aux SPADs ont été dérivées; un TDC d'une résolution de 17 ps a été démontré sur une plateforme FPGA. A ce jour et au mieux de nos connaissances, ceci est la plus haute résolution reportée pour ce type de TDC. Le traitement et la lecture de capteurs à photons individuels ont été démontrés dans plusieurs technologies, et en particulier avec des systèmes d'imagerie à photons individuels où des architectures massivement parallèles ont été étudiées et implémentées en CMOS. Des méthodes de distribution d'horloge et de synchronisation pouvant potentiellement éliminer le problème de *skew* indépendamment de la taille d'un chip ont été démontrées. Les avantages en termes d'efficacité de cette approche sont particulièrement intéressants dans les systèmes embarqués avec extension du jeu d'instructions.

Cette thèse emploie la technologie des SPADs en CMOS pour plusieurs applications en créant ainsi un pont entre la conception de systèmes digitaux et la photonique à haute performance. A notre connaissance, ceci est la première tentative dans cette direction visant la technologie CMOS.

**Mots clés:** Single-Photon Avalanche Diode (SPAD), digital CMOS, single-photon communication, photon channel capacity, Time-to-Digital Converter (TDC), single-photon imaging, photon processing, Time-Uncorrelated Photon Counting (TUPC), Time-Correlated Single-Photon Counting (TC-SPC), sensor array readout strategies, single-photon clocking, clock distribution, clock networks.

### ABSTRACT

The advent of single-photon detectors known as Single-Photon Avalanche Diodes in standard CMOS technology opened the way to new perspectives in integrating these ultra sensitive light sensors with digital logic.

Light has some interesting properties that attracted researchers in computer and electronics for a long time. Its weightlessness nature makes it a candidate to replace electrons when it didn't already do so. This is particularly true for long distance data transfers. However a new trend can be observed. Researchers are looking into photonics, the science of light, for short distance communications as well. Power efficiency is one of the reasons of this trend. In fact, photons, the elementary particles of light, don't suffer of resistive, capacitive, or inductive effects like electrons do. The wavelike nature of light can also free designers from problems such as cross-talk and side-channel noise injection while taking advantage of interference. However photonics is still not the panacea and we don't believe it will ever completely replace electronics. Most certainly a combination of the two will be adopted to take advantage of both worlds.

CMOS digital Integrated Circuit (IC) design faces many challenges and it is not clear whether technology will still provide small footprints, high performance, and low power in the future. Photonics with SPADs can answer some of these questions. In this work, we present three investigations where SPAD photonics is integrated within digital CMOS technology.

The main contributions of this thesis are threefold: single-photon CMOS communication paradigms, single-photon processing and readout techniques, single-photon clocking and synchronization methods. Single-photon communication was achieved using a combination of SPADs and ultra-fast TDCs in a pulse position modulation scheme. In this context, theoretical channel capacity limits in the presence of noise and other non-idealities typical of SPADs were derived; a TDC with a resolution of 17 ps was demonstrated in a standard FPGA fabric. To the best of our knowledge, at the time of this writing, this is the highest reported resolution for a TDC of this kind. Single-photon processing and readout was achieved in several technologies, focusing on im-

age sensor design, whereby massive parallel architectures were studied and implemented in CMOS. Single-photon clocking and synchronization was demonstrated allowing potentially zero skew systems irrespective of the chip area. The power benefits of this approach in embedded systems with instruction set extensions are particularly interesting.

The thesis makes use of SPAD technology implemented in CMOS for a number of applications creating a bridge between digital design and high performance photonics. We believe that this is the first attempt in this direction focused on CMOS technology.

**Keywords:** Single-Photon Avalanche Diode (SPAD), digital CMOS, single-photon communication, photon channel capacity, Time-to-Digital Converter (TDC), single-photon imaging, photon processing, Time-Uncorrelated Photon Counting (TUPC), Time-Correlated Single-Photon Counting (TC-SPC), sensor array readout strategies, single-photon clocking, clock distribution, clock networks.

# 1 Introduction

OMPUTING has become the most pervasive resource of our daily lives. Computing devices have become more and more powerful while size and electrical consumption have shrunk. The most shocking comparison is perhaps that of our mobile phones that pack, in a few squared centimeters, more processing power than supercomputers only a few decades ago, at a fraction of the power. The chips that power our devices are the fruit of cunningly tailored trade-offs between performance, power, and diesize (i.e. cost). Very Large Scale Integration (VLSI) was a widely employed keyword a few years ago. Today, almost every electronic device produced can be labeled as a highly integrated technology.

High integration is a key factor in mobile applications such as mobile phones, laptops, and more recently, tablet computers. Small footprint devices also spawned from the need of higher inter-chip bandwidth, which is generally limited by capacitive and inductive effects. Specialized devices, such as MEMs, flash memories, or optical stacks, that require specific fabrication technology have also become integrated in systems known as Systems-on-Chip (SoC). Scaling in size of the electrical interface of integrated circuits, also known as pads, has not followed the transistors' trend. In fact, wirebonding and flip chip techniques are limiting the pads' size reduction.

Low power operation is not restricted to mobile devices; power budgets and, more specifically, thermal extraction limits are real constraints even in high-performance applications. For example, data centers packed with racks of commodity or high-end computing platforms have enormous power requirements for normal operation and air conditioning. While the cost of operation can be

reduced for the customer, the eco-friendly arguments is also becoming a non-negligible incentive.

High performance, at the risk of stating the obvious, is pursued to enable evermore computing/networking intensive applications. Performance can be characterized in terms of throughput, bandwidth, latency, and availability, to name a few usual metrics. When raw performance cannot be achieved by mere scaling of technology and clock frequency, parallelism is employed at the cost of silicon area. In fact, the area of chips keeps growing as more cores are integrated and heterogeneous systems created.

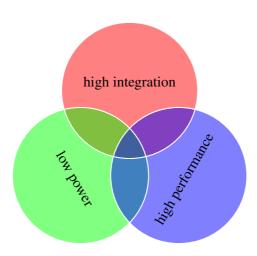

These three aforementioned contradictory requirements (high integration, low power, and high performance) are inevitably present in today's devices design. Technology scaling has helped pushing these limits, nonetheless, researchers are investigating alternative methods in order to expand beyond the current limitations.

Figure 1.1: Tradeoff in current chip design

2

One alternative method is to use photons, the elementary particle and fundamental unit of light. Photonics has already been exploited in the past for long distance communication. For a long time and still to date sensors have been made in custom processes that are generally not compatible with the standard logic process widely used and known as Complementary Metal-Oxide Semiconductor (CMOS) technology. In 2003, the horizon changed dramatically when Rochas *et al.* presented the first single-photon detector fabricated in CMOS technology [1]. In fact, starting around the beginning of the 21<sup>st</sup> century, a major focus of photonics has been on silicon. Silicon being the element used as substrate in CMOS technology, the integration of single-photon sensors in CMOS opened new applications where light sensing and digital data processing are combined.

Silicon photonics research at Intel [2] and IBM [3] for example, are now focusing on building light emitting devices, modulating devices, and receivers for chip-to-chip communication in the scope of high performance computing at first. In board-to-board and cabinet level interconnect, optical communication is the *de facto* standard. These research programs are pushing the boundary to the chip level and they are also addressing board level optical transmission [4].

The scope of this thesis is to propose an optical approach where the electrical one falls short and, by no means, promote an alloptical solution. Also the single-photon techniques presented do not necessarily imply that only a single photon is used but rather that a single detected photon is sufficient to trigger the desired effect. In fact, for practical reasons but to some extent, many photons can be used.

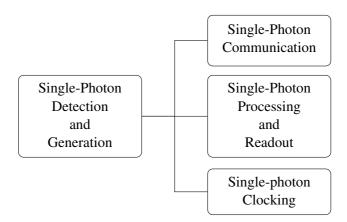

After a review of the existing state of the art in CMOS based photon detection, generation, and transport in chapter 2, the thesis is organized in three main sections. First, single-photon communication amenable for inter- and intra-chip communication is discussed

Figure 1.2: Structure of the thesis.

in chapter 3. A time-to-digital converter implementation and evaluation is particularly detailed in this chapter. Second, chapter 4 discusses single-photon processing, focusing on single-photon detection and readout integration in CMOS, as well as its applications. Third, a system for optical clock distribution is presented in chapter 5. The concluding chapter 6 describes future work and other possible applications. The main contributions of this work are also summarized in chapter 6.

# 2

# SINGLE-PHOTON DETECTION AND GENERATION

PHOTONICS is the science of light. From generation to detection, it covers amongst others transmission, modulation, and amplification of light. Photons, the elementary particles of light, present the particular duality of being both particles and waves. Although we will focus on the corpuscular aspect mainly, the wave-like aspects should be kept in mind.

Silicon photonics is a sub-class of photonics in which the light interacts with the most widely used semiconductor in industry: silicon. The semiconductor industry has grown and refined processes to fabricate larger and larger chips on purified crystalline silicon dies with very well controlled yield. High integration again is the motive that drives research of photonics with silicon. The major players, Intel and IBM, have silicon photonics research programmes [2, 3] that have produced very interesting results these recent years.

This chapter is meant as a review of the state of the art in silicon photonics with a certain bias on detectors. However we will shortly review light generation devices in section 2.2, and photons transport and modulation techniques in silicon in section 2.3.

## 2.1 Single-Photon Detection

Originally, detection of single-photon events has been and is still performed with Photomultiplier Tubes (PMTs). These vacuum tube devices, generally bulky by construction, provide detection in a wide spectrum with low noise but with high time response and jitter in the order of nanoseconds. Multichannel or Microchannel

Plates (MCPs), while still relatively large, can also provide optoelectric conversion and amplification with multiple channels that can be used for example in event position detection. Multichannel Plates (MCPs) may reach picosecond timing resolutions.

Avalanche Photodiodes (APDs) are solid state devices in which photon-induced electron-hole pairs are accelerated by an electric field. These accelerated carriers may produce secondary electronhole pairs by impact ionization. This process is known as avalanche multiplication. APDs have been built in GaAs, SiGe, and Si substrates. The first appearing APDs, also known as reach-through APDs (RAPDs), are thick devices built "vertically" in which a large region of absorption ( $\pi$  region) is layered on top of a p-n multiplication region. RAPDs have high breakdown voltage, high sensitivity in the visible and IR spectrum, large active area, and relatively poor timing resolution. A second category of APDs, which are the subject of interest of this thesis, are thin devices that present a reduced active area, low photon detection but excellent timing resolution are built with planar technology. Moreover, another advantage of the planar technology is that it suits well to high densitiv integration and quenching circuitry when required for normal operation.

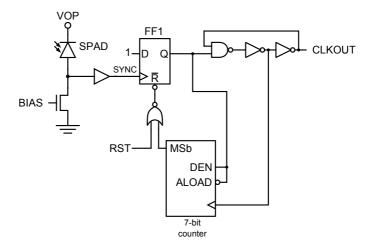

A Single-Photon Avalanche Diode (SPAD) is an APD operated above breakdown voltage, in the so-called Geiger mode. In Geiger mode of operation, SPADs exhibit a virtually infinite optical gain, however a mechanism must be provided to quench the avalanche.

SPADs and APDs in general have been built in custom and rather expensive processes until Rochas *et al.* presented the first SPAD built in standard CMOS technology, in 2003 [1, 5]. The breakthrough opened the way to large integrated arrays of SPADs [6] with an extremely low fabrication cost due to the use of a standard process. Many efforts have been made to port SPADs from sub-micron technology to deep sub-micron technology, such as [7] for 0.35 µm, [8–10] for 180 nm, [11–13] for 130 nm, and [14] for

90 nm technology. Generally speaking SPADs show excellent timing response and good quantum efficiency at the expense of long dead time and hard-to-control noise rate figures.

### 2.1.1 Single-Photon Avalanche Diode

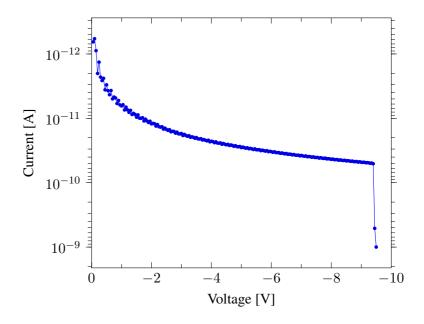

The SPAD active region or depletion region is a p-n junction that forms the diode. Biasing the diode near or above breakdown voltage induces a high electric field in the depletion region enabling the avalanche multiplication process. A typical I-V curve of a SPAD is shown in figure 2.1, the breakdown voltage for this device is 9.4 V.

**Figure 2.1:** I-V curve of a 130 nm SPAD [12, 13].

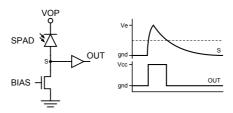

**Figure 2.2:** The SPAD and surrounding buffering and quenching circuitry.

The operating voltage  $V_{\rm op}$  is generally described in terms of the breakdown voltage  $V_{\rm bd}$  of the device and the excess bias  $V_{\rm e}$ :

$$V_{\rm op} = |V_{\rm bd}| + V_{\rm e}$$

.

The device requires quenching circuitry in order to stop the avalanche-induced current. Failure to do so would damage the device. There exist several techniques to accomplish quenching, classified in active and passive quenching. The simplest approach to passive quenching is to use a ballast resistance. The avalanche current causes the diode reverse bias voltage to drop below breakdown, thus pushing the junction to linear avalanching and even pure accumulation mode. Active quenching generally consists of a feedbackforced voltage drop below breakdown with the same effects as passive quenching. After quenching, the device requires a certain recovery or recharge time, to return to the initial state. Recharge can also be active or passive depending whether the bias of the diode is forced or not forced above breakdown. The quenching and recovery times are collectively known as dead time. Figure 2.2 shows a passive quenching and passive recharge scheme.

Hereafter will be discussed several figures of merit of SPADs such as DCR, PDP, jitter, dead time, and afterpulsing. A comparison of several devices will be also given toward the end of this section. Knowing the fundamental limitations of these devices yields

to several applications that can take advantage of the technology while avoiding their drawbacks.

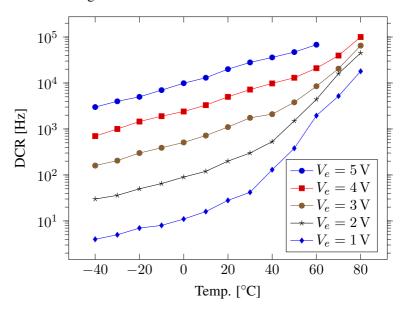

**Figure 2.3:** Example of dark count rate versus temperature with a 130 nm SPAD. Source: [13].

SPADs noise measured as Dark Count Rate (DCR) is the mean frequency of spurious pulses. Spurious pulses are mainly due to tunneling and thermal generation. Tunneling in SPADs is a stochastic phenomenon where a particle crosses the bandgap. The tunneling probability highly increases with the electric field and becomes dominant for field values in excess of 10<sup>6</sup> V/cm. Thermal generation can cause an electron in the valence band to transition to the conduction band. The presence of *traps*, intermediate energy levels in the bandgap, accentuate both tunneling and thermal generation. Figure 2.3 shows an example of DCR variation as a function of tem-

perature for a 130 nm CMOS implementation. Also shown in the figure, the DCR also increases as  $V_{\rm e}$  increases. Note that different devices may show different DCR behaviors depending on whether tunneling or thermal effects are dominant. For the case depicted in figure 2.3, we can see that for temperatures above 40 °C thermally generated free carriers are the main contributors, while tunnelling dominates at room temperature and below.

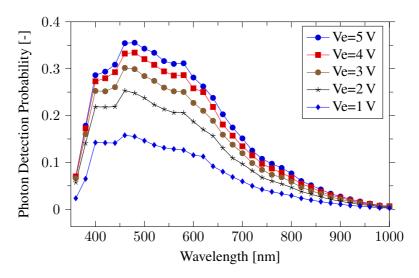

**Figure 2.4:** Illustration of Photon Detection Probability curves at different excess bias. Source: [12, 13].

Photon Detection Probability (PDP) is defined as the probability that a photon of wavelength  $\lambda$  generates a pulse at the output of the SPAD. For CMOS SPADs there are two factors that affect PDP. First, the photons need to reach the silicon and be absorbed. Depending the optical stack, photons are reflected, refracted, or absorbed before reaching the substrate. Second, photons that reach

the substrate must generate an electron-hole pair for an avalanche build-up to be triggered. For this to happen, the generated free carriers must lie in the depletion region of the SPAD (as carriers generated in a region with a low electric field will very likely recombine). Therefore the depth of the depletion region and the excess bias play an important role in PDP figures. Figure 2.4 shows PDP curves for a 130 nm CMOS SPAD. Note that increasing excess bias  $V_{\rm e}$  does not always increase PDP as at some point DCR will dominate hence PDP decreases. Note that CMOS SPADs have a peak in PDP between 400 nm and 600 nm.

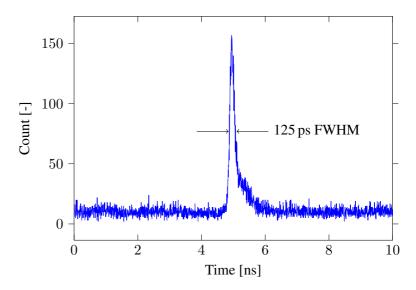

**Figure 2.5:** Histogram of the timing of pulses generated by SPAD illuminated with a fixed frequency picosecond laser source [12, 13].

Timing resolution or *jitter* is crucial for application where the exact arrival time of photons (and the event they represent) is required. The timing resolution in SPADs is influenced by the avalan-

che build-up process, parasitic capacitance, and the noise threshold of the output buffer. The avalanche steepness is dependent on the electrical field, while the capacitance and the threshold noise are dependent of the geometry and the technology. SPADs jitter is characterized by illuminating the active region with a fixed-frequency low-jitter laser source and controlling the intensity so as to prevent pileup effects. An histogram of the arrival time of SPAD's pulses with respect to the laser trigger is constructed. The full-width-athalf-maximum value is taken as timing jitter. Figure 2.5 shows an example of histogram built with a 40 MHz laser diode. Note that the measurement taken also accounts for jitter in the laser source and the measurement instrument both of which are relatively small (a few picoseconds) compared to the measured jitter.

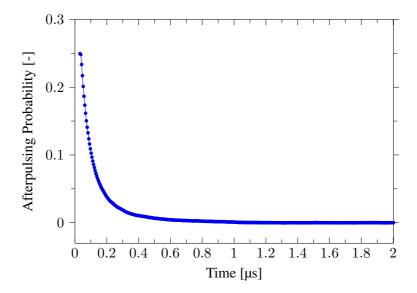

**Figure 2.6:** Afterpulsing probability at nominal dead-time (40 ns) for a 0.35 µm SPAD.

The dead time is defined as the minimum time between two photons that the sensor can unambiguously detect. For SPADs, the dead time is highly dependent on the quenching and, if present, recharging circuitry. The dead time is a design parameter, when building a SPAD with the surrounding circuitry (also known as SPAD ensemble), that affects the Afterpulsing Probability (APP). Afterpulses are avalanche breakdowns that occur when carriers from previous avalanches get trapped in the multiplication region. Afterpulsing effects can be reduced by either limiting the number of carriers an avalanche builds or allowing trapped carriers to evacuate the multiplication region before the SPAD is recharged to the operational state. Carrier limitation is done by reducing the parasitic capacitances. In CMOS, the integrated quenching and read-out circuitry intrinsically limit parasitic capacitances. Slowing down the recharge time, hence increasing the dead time, contributes to lower the APP. Figure 2.6 shows a typical APP curve.

Table 2.1 presents a comparison of CMOS SPADs from the first 0.8 µm device presented by Rochas *et al.* [1] to the latest 90 nm SPAD by Karami [14, 15]. The trend of the decreasing breakdown voltage (from the older to the newer devices) is due to increasing doping levels and increased tunneling effects [16]. The DCR increase is also mainly due to tunneling. The large timing jitter of [15] can be attributed to the large active area combined with the diffusion of minority carriers, generated by photons absorbed deeper than the depletion region, back into the multiplication region. The depletion region being shallower in this technology due to a higher electric field.

| Performance measure           | [15] | [13]                    | [11]       | [10]               | [6]       | [8]             | [7]        | [9]        | [1]        | Unit                 |

|-------------------------------|------|-------------------------|------------|--------------------|-----------|-----------------|------------|------------|------------|----------------------|

| Technology                    | 06   | 130                     | 130        | 180                | 180       | 180             | 350        | 800        | 800        | uu                   |

| Max. PDP                      | 12   | 18 a                    | 34 a       | N.A.               | $2.5^{a}$ | 14 <sup>a</sup> | 40 a       | 26 a       | 28 a       | %                    |

| Max. PDP                      | N.A. | $30_{p}$                | $41^{\ b}$ | N.A.               | $5.5^b$   | N.A.            | $35^{b}$   | N.A.       | $33^{\ b}$ | %                    |

| Typ. DCR                      | 16   | <sub>p</sub> 06         | 95 a       | N.A.               | 70 a      | $0.1^a$         | N.A.       | $0.35^{a}$ | $0.9^a$    | kHz                  |

| Typ. DCR                      | N.A. | $^{q}$ 0/29             | $^{9}$ 056 | $\sim \! 1000  ^b$ | N.A.      | N.A.            | $0.75^{b}$ | N.A.       | 4 <i>b</i> | kHz                  |

| Active area                   | 50   | 58                      | 78         | 3.1                | ~11       | 78              | 10         | 38         | 38         | $\mu$ m <sup>2</sup> |

| Timing jitter (FWHM)          | 398  | 125                     | 144        | N.A.               | N.A.      | N.A.            | 80         | 115        | 09         | sd                   |

| Afterpuling probability       | 32   | $\stackrel{\sim}{\sim}$ | N.A.       | N.A.               | N.A.      | N.A.            | 23         | N.A.       | 8          | %                    |

| Dead time                     | N.A. | 180                     | N.A.       | N.A.               | 30        | N.A.            | 40         | 40         | 75         | us                   |

| Breakdown voltage             | 10.4 | 9.4                     | 6.6        | 11                 | 10.2      | 10              | 17.7       | 25.5       | 25.25      | >                    |

| <sup>a</sup> Excess Bias (Ve) | 0.15 | _                       | 1.7        | N.A                | 0.5       | 0.5             | 3.3        | S          | 5          | >                    |

| $^b$ Excess Bias (Ve)         | N.A. | 2                       | 2.7        | 2.5                | 2         | N.A.            | 4          | N.A.       | 10         | >                    |

Table 2.1: Performance comparison of SPAD implementations.

### 2.2 Photon Generation

Light generation can be categorized in many ways: incadescence for light emission of hot body, chemiluminescence for light emission in chemical reactions, electroluminescence for light emission in response to an electric current, mechanoluminescence for light emission by solid under mechanical stress, etc. We are interested in electroluminescence as it can be conveniently controlled electrically, however the principles of light emission are similar in many other cases. Two fundamental photon emission cases are known: spontaneous emission and stimulated emission.

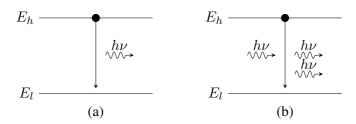

In the first case, an electron in an excited state at energy level  $E_h$  may transition to a lower level  $E_l$ . While doing so, it emits a photon with energy  $h\nu=E_h-E_l$ , where  $\nu$  is the frequency and h Planck's constant (fig. 2.7a). Spontaneous emission is fundamental process behind the incandescent light bulbs, light-emitting diodes, cathodic or plasma displays to cite a few.

In stimulated emission, photons with energy  $h\nu$  are generated by the transition of an electron from an excited level to a ground level similar to spontaneous emission. However, the transition is triggered by another photon of energy  $h\nu$  (fig. 2.7b). Note also that the newly generated photon's phase, frequency, polarization, and direction are the same as the triggering photon. The process of stimulated emission is used principally in lasers.

The integration of spontaneous and stimulated emission devices is a highly researched area. Because of the indirect bandgap of silicon, highly integrated spontaneous emission devices often use III-V nitride direct bandgap semiconductors processed on top sapphire substrates [17–21] that can be bump-bonded to CMOS drivers for instance [22]. Efficient silicon LEDs were demonstrated by using dislocation loops [23] or one- and two-photon assisted sub-bandgap light emission [24]. Experiments in fluorescence life-time imag-

**Figure 2.7:** Spontaneous photon emission (a) when an electron a excited state  $E_h$  transits to a lower lever energy state. In stimulated emission (b) the transition is triggered by a existing photon, the newly emitted photon has the same phase, frequency, polarization, and direction as the triggering photon.

ing (FLIM) are good examples of use of integrated micro-LEDs arrays [22] while optical stack considerations are shown in [20]. SPADs also present spontaneous emission of photons during avalanche breakdown although the intensity is rather limited and the timing not yet well controlled [13].

Lasers are stimulated emission devices that are known since the 1960s. Semiconductor lasers are today the most produced laser found in many consumer electronic apparatuses. Similarly to LEDs, silicon integrated lasers were only first demonstrated in 2004 [25] and are still an active subject of research [26, 27], the main limitation of these devices being their large size and require external optical pumping. Hybrid lasers such as [28] address theses issues by incorporating III-V elements in the amplification region and coupling light in an SOI cavity.

## 2.3 Photon Transport and Modulation

Free air transport of photons can be the first approach to moving light from point A to point B. However, scattering, reflections, and refractions might render an optical setup difficult to control. Confinement of light can be done efficiently with optical waveguides. By taking advantage of total internal reflection between two material of different refractive index, light is confined and generally can be channeled in a given direction with low attenuation. Optical fibers generally made of silica (SiO<sub>2</sub>) use this property for long distance communication.

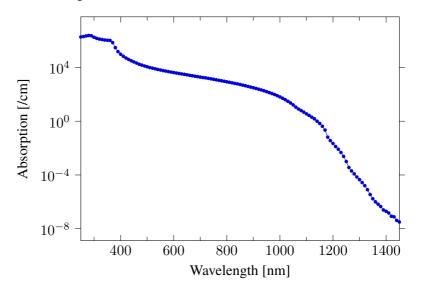

Low attenuation is dependent on the wavelength and the material used. For example, the absorption coefficients of silicon are shown in figure 2.8.

Figure 2.8: Silicon absorption coefficients. Source: [29]

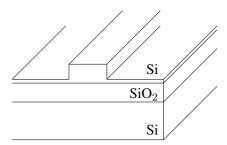

Waveguides have been implemented in silicon and with the advent of Silicon-on-Insulator (SOI) technology highly integrated in a CMOS compliant substrate [30–32]. For example, figure 2.9 shows the cross section on a waveguide on an SOI wafer.

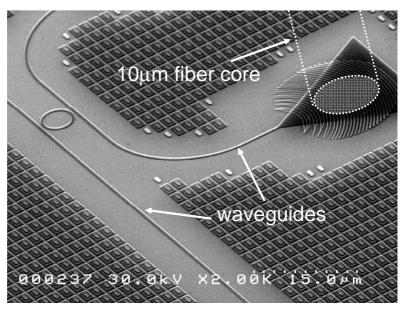

Silicon modulators built early in the 1990s by Treyz *et al.* [34] where leading the way to integrated light modulation. Since then, several SOI based modulators have been built [35–41]. The modulators use free-carrier absorption effects in p-i-n diodes combined with Mach-Zehnder interferometry. Recent modulators such those in [37–41] show modulation bandwidths in excess of 10 Gbps. An example of how light can be effectively coupled from a fiber into an SOI waveguide is shown in figure 2.10.

**Figure 2.9:** Cross section of a SOI based waveguide. For reference, the top silicon layer thickness can range from 12 nm to  $100 \mu \text{m}$ , and the buried oxide layer thickness 10 nm to  $3 \mu \text{m}$ . Source: [33].

**Figure 2.10:** Example of fiber coupled into SOI waveguide with a holographic lens. Source: [37]

3 SINGLE-PHOTON COMMUNICATION

HIP designers are developing increasingly complex integrated systems that require more and more die space for high throughput I/O pads. As a result, inter- and intra-chip communication is becoming one of the largest sources of noise and power dissipation on chip and also the bottleneck for performance. While transistor count has followed Moore's law; I/O pads have not evolved at the same pace. Moreover, due to bonding inductance, very high bit rates are possible at a cost of prohibitively high currents. Parallelism has often been used, but at a cost of large silicon area.

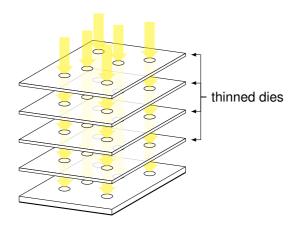

Traditional alternatives have been flip-chip and chip-level via technology [42]. However, reliability, cost, and flexibility are still open issues, especially when it comes to large inter-chip buses when more than two chips are involved. This is becoming an especially pressing problem with the emergence of densely packaged multi-processor and multi-core systems. For this reason, 3D and system-in-package (SiP) techniques have been conceived to enable stacks of inter-bonded dies (see figure 3.1). The problem with this approach is however the limitation of speed imposed by bonding wires and the power dissipation of drivers.

To overcome these limitations, researchers have turned to wireless solutions based on capacitive, inductive, and optical methods [37, 43, 44]. While capacitive and inductive methods are effective in reducing power and ensuring high speed, they are only appropriate for pairs of chips. Hence, they are ineffective for broadcast and multi-chip systems.

Optical interconnects for inter-chip communication have been proposed decades ago. Their slow adoption is due mainly to the

**Figure 3.1:** System-in-package wirebonding.

complexity of receivers whose output needs to be amplified, converted to a digital signal, and synchronized. These functions require area and may dissipate significant power. The lack of compact, low power optical sources has also been an issue. Commercial solutions for cabinet-level interconnect are actively developed by IBM, Intel, and Luxtera to name a few [2,3,45]. The current devices, generally built in CMOS SOI technology with Germanium deposited or flipchip APDs, are not yet easily integrable into single-chip or multichip formats due to size and complex building processes although recent progress seem to address these issues [46].

In this chapter a new approach to optical communication is proposed that can be integrated in standard CMOS technologies utilizing a fraction of the area and power of a pad. The proposed approach is amenable to optical broadcasting, optical clock distribution, and optical buses (both vertical and horizontal). The core of the optical interconnect channel is a CMOS SPAD. Thanks to its digital output it requires no amplification, no A/D conversion, nor any other type of signal processing. However, in SPADs the detection cycle can be as high as a few tens of nanoseconds. Thus, a simple digital modulation scheme must be added to achieve throughputs of several gigabit-per-second.

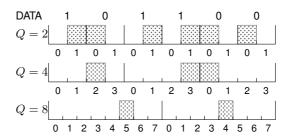

**Figure 3.2:** PPM modulation. The data to be modulated is shown at the top of the diagram. Q represents the length of the modulation slot. The position of the pulse in a slot represents the data.

We selected Pulse Position Modulation (PPM), a scheme that encodes K bits into  $Q=2^K$  time slots in the total allotted range  $R=Q\Delta T$  (see fig. 3.2). PPM was selected to minimize the effects of SPAD dead time. In fact SPAD dead time in the order of a few tens of nanosecond, would limit On-Off Keying (OOK) modulation throughput to a few megabit per second. With PPM, we take advantage of the SPAD's photon-to-avalanche timing response whose jitter can be reduced to a few picoseconds. In fact, note that R should be higher than the detection cycle to ensure proper operation of the communication link.

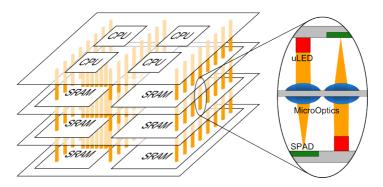

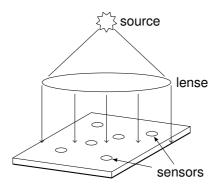

A highly integrated application of the proposed system is depicted in figure 3.3. Optical data signals are generated, for example, in an integrated CPU by a micro LED similar to [18]. A subnanosecond optical pulse was demonstrated for this device using CMOS drivers that occupy a fraction of the area of a pad. Light is focused on the active region of a SPAD by micro lenses. Note also that optical chip-to-board and optical chip-to-chip communications could also benefit from this approach replacing optical channels with conventional fibers or waveguides for example.

**Figure 3.3:** Inter-chip communication with LEDs, micro-lenses, and SPADs.

The detecting section of the channel is represented by a SPAD and integrated PPM decoder. The optical channel may be using integrated micro-optics that can be integrated on chip as a standard issue in most CMOS technologies. Multi-chip vertical buses can be obtained in this way by stacking dies that have been thinned. Optical transmission is ensured by low absorption coefficients of silicon in the visible spectrum.

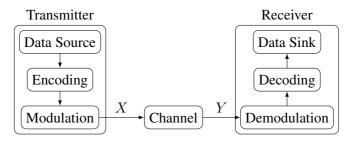

Figure 3.4: Point-to-point communication model.

## 3.1 Building Blocks

A traditional point-to-point communication system comprises the following elements: data source, encoder, modulator, channel, demodulator, decoder, and data sink. Figure 3.4 shows the chain relation between these elements. Several layers of protocol can be added on top of the data source/sink to provide reliability and flow-control. However, we will focus particularly on the modulation and demodulation part.

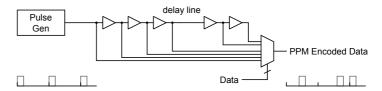

Figure 3.5: Simplified PPM modulation scheme.

Modulation of the data pulse in the proposed scheme can be implemented in several ways. Figure 3.5 presents a simplistic schematic of a modulator. The most critical issue in any modulator is to output pulses at a precise timing with a resolution  $\Delta T$  that pushes the limits of the technology. The use of one or several delay lines (whether electrical or optical) seems a natural choice. Performing PPM modulation requires precise and fast timing control of light emission. Laser emission is generally best controlled in either constant emission or pulsed at fixed frequency. Shutter-based techniques combined with constant light source were proposed in [47] but bandwidth is limited by the shutter speed. A similar approach is to use interferometry as means of shutter to expand the bandwidth [40]. Pulse emission at a fixed frequency can be modulated with several delay lines multiplexed at the transmission rate [48–50]. Integrated light emitting diode such as [18,22,51,52]

seem also good candidates for direct modulation. In particular, references [22, 51, 52] show sub-nanosecond optical pulses with an array of micro-LEDs.

Starting from the principle that optical to electrical conversion is available, demodulation of PPM signaling requires timing differentiation. The approach taken in [53] is to delay the integrated signal in Q delay lines, a pair-wise comparison of all signals is performed and fed into a "greatest of" receiver to recover the data. Shalaby in [48] counts photons in each interval  $\Delta T$  and the interval with the maximum count is selected. Shalaby also proposes parallel sampling of the Q timeslots. Note that using SPADs it is difficult to count photons in an interval  $\Delta T$  when  $\Delta T$  approaches or is smaller of the SPADs dead time. However we can use the fast timing response of the SPAD to retreive the position of the first pulse in a frame. In this work, similar to [54], we propose to use a time discriminator such as a Time-to-Digital Converter (TDC) to retrieve the timing of the first pulse, hence the data. A TDC implementation is presented in section 3.3 with experimental results.

Figure 3.6: Example of PPM demodulation scheme.

Source coding is used to provide error detection and correction. Furthermore, it can be used to approach channel capacity [55]. Reed-Solomon codes and Turbo Codes are widely used for this purpose [56, 57]. Both are of particular interest when used with optical PPM communication as shown in [58, 59] for the former and in [49, 50] for the latter.

# 3.2 Theory and Limits

Optical communication channels have been extensively studied from early in the 70s to well after the 90s [47–50,53,58–66]. In this section, the results found in literature are re-derived with the SPAD peculiarities in mind.

### 3.2.1 Time Resolution Limits

Theoritical limits on the time resolution in an optical communication system were pointed out by Butman *et al.* in [62]. The fundamental limit is imposed by the quantum mechanics energy-time uncertainty principle:

$$\Delta E \Delta T \ge h,$$

(3.1)

where  $\Delta E$  is the energy change in the system. The time resolution with which we can measure this change is represented by  $\Delta T$  and h is Planck's constant. In other words, the time of the arrival of an energy changing event cannot be measured with arbitrary high precision. In the case of photons, the energy of a photon at frequency  $\nu$  is  $h\nu$  and equation 3.1 leads to

$$\Delta T \ge \frac{1}{\nu}.\tag{3.2}$$

At visible frequencies the resolution approaches  $1 \times 10^{-15}$  s or 1 fs. Note that while we detect photo-induced electrons and that timing of these events could be performed with arbitrarily high precision, the actual limitation comes from the photo-optical processing [62].

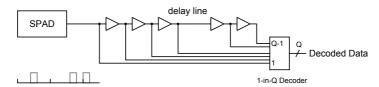

### 3.2.2 Channel Capacity

Butman in [62] already derived the bandwidth limitations in the case of a noiseless PPM-encoded optical channel. As also described in [63], the capacity of such channel can be made infinite, by decreasing  $\Delta T$ . However, as derived in section 3.2.1,  $\Delta T$  is ultimately limited by the quantum mechanic uncertainty principle. We will therefore derive the channel capacity by varying  $\Delta T$  down to the 1 fs limit. In this section, we will first derive the channel capacity in the ideal case. We will then introduce SPAD's non-idealities and derive the channel capacity again.

The traditional idea of a point-to-point communication channel comprises a transmitter, a channel, and a receiver (figures 3.4 and 3.7). X and Y are random variables representing the transmitted codes before and after the channel respectively. The modulation proposed, PPM, uses Q time slots of  $\Delta T$  seconds to encode Q source codes. A pulse present in time slot  $t_n$  represents the  $n^{\text{th}}$  code.

$$Tx$$

Channel  $Y$   $Rx$

Figure 3.7: Point-to-point communication model.

The channel is modeled in the context of PPM modulation as a Q-ary erasure channel. In this model, a code is either received (not-erased) with probability  $1-\epsilon$  or not received (erased) with probability  $\epsilon$ . The channel capacity as defined by information theory is determined by

$$C = \max_{P_Y} I(X;Y), \tag{3.3}$$

where the mutual information I(X;Y) = H(X) - H(X|Y). The

Figure 3.8: Q-ary erasure channel.

conditional entropy of X given Y is defined by:

$$H(X|Y) = \sum_{y} P(y)H(X|Y=y).$$

(3.4)

In the case of Q-ary erasure channel, the only non-zero term of the sum in eq. 3.4 is when y=?. In fact when y={1..Q}, knowing y completely determines x. The entropy

$$H(X|Y = ?) = H(X)$$

because knowing y does not give any information on x. From equations 3.3 and 3.4 the channel capacity:

$$C = \max_{P_X} (H(X) - \epsilon H(X))$$

$$= \max_{P_X} (1 - \epsilon)H(X).$$

(3.5)

The entropy H(X) is maximized when X is uniform i.e.

$$H(x) = -\sum_{y} P(y) \log_2 P(y)$$

$$= Q \times \frac{1}{Q} \log_2 Q$$

$$= \log_2 Q.$$

(3.6)

Therefore the channel capacity of a PPM encoded optical channel is

$$C_{\rm ch} = (1 - \epsilon) \log_2 Q$$

bits/channel use. (3.7)

A channel use takes  $Q\Delta T$  seconds therefore the capacity is

$$C = \frac{(1 - \epsilon)}{\Delta T} \frac{\log_2 Q}{Q} \qquad \text{bits/s.}$$

(3.8)

In the noiseless case the erasure probability  $\epsilon$  derives from the stochastic nature of light. Let us take a time interval  $\Delta T$  and a light source of intensity  $\Phi_{\rm s}$  photons per second. The probability that n photons are generated in a time period of  $\Delta T$  seconds is Poissonian with  $\lambda = \Phi_{\rm s} \Delta T$ , hence:

$$P(n \text{ photons generated}) = \frac{(\Phi_{s} \Delta T)^n e^{-\Phi_{s} \Delta T}}{n!}.$$

(3.9)

The erasure probability  $\epsilon$  is the probability that no photons are generated during period  $\Delta T$  therefore

$$\epsilon_{\text{ideal}} = P(\text{no photons generated}) = e^{-\Phi_{\text{s}}\Delta T}.$$

(3.10)

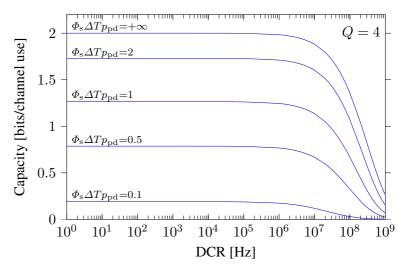

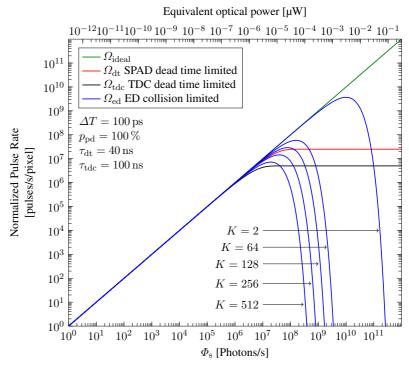

The ideal channel capacity is plotted in figure 3.9 varying Q and  $\Delta T$ . We note that 1 Gbps could already be achieved at a resolution of  $\Delta T = 100$  ps.

Figure 3.9: Ideal channel capacity with  $\Phi_{\rm s} \Delta T = 1$ .

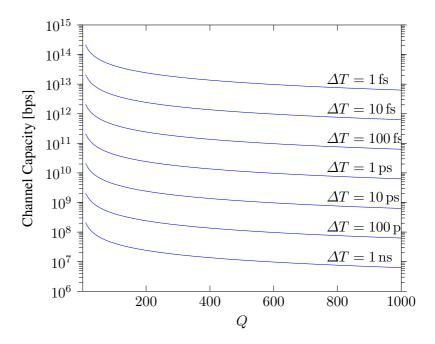

When we take into account SPADs photon detection probability  $p_{\rm pd}$ , the channel model described in the preceding paragraphs still holds. For simplicity we assume that the photon detection nonideality of the SPAD is in the channel and the receiver is ideal. We compute the erasure probability  $\epsilon_{\rm pdp}$  as the cumulated probability that no photons are detected assuming that photon detections in SPAD are independent and that the photon detection process is independent of the photon generation process.

$$\epsilon_{\rm pdp} = \sum_{k=0}^{\infty} P(k \text{ photons generated}) (1 - p_{\rm pd})^k$$

(3.11)

$$= e^{-\Phi_{\rm s}\Delta T} \sum_{k=0}^{\infty} \frac{(\Phi_{\rm s}\Delta T (1 - p_{\rm pd}))^k}{k!}$$

(3.12)

$$= e^{-\Phi_{\rm s}\Delta T} e^{\Phi_{\rm s}\Delta T(1-p_{\rm pd})} \tag{3.13}$$

$$=e^{-\Phi_{\rm s}\Delta T p_{\rm pd}}. (3.14)$$

Equation 3.11 is equivalent to saying that the probability of erasure is the sum of the probabilities that for the period of time  $\Delta T$ , zero photons are generated, one photon is generated and one photon is not detected, two photons are generated and two photons are not detected, etc. In (3.12) we use the well known series expansion  $e^x = \sum_{k=0}^{\infty} x^k/k!$ . In figure 3.10 the channel capacity is plotted against PDP given  $\Phi_s \Delta T = 1$  and  $Q = 2^{\dagger}$ . A PDP of 10 % yields a drop in channel capacity of one order of magnitude.

<sup>&</sup>lt;sup>†</sup>For such low value of Q and  $\Delta T$ , a very low SPAD dead time is required for proper operation.

Figure 3.10: Channel capacity variation according to photon detection probability.  $\Phi_{\rm s} \Delta T = 1, \, Q = 2.$

In order to derive the capacity in presence of noise, we need to change the channel model. Figure 3.11 shows the mapping of the chosen Q-ary noisy erasure channel. The conditional distribution P(X|Y) completely defines the channel transition probabilities hence the capacity. The decoding strategy, which influences P(X|Y), is defined as follow. For each period  $Q\Delta T$ , the timing of the first pulse defines the code. The noise is modeled as a Poisson process with rate  $\lambda_N$ . We define N to be the time of arrival of the first noise pulse (we assume noise pulses are not erased). The random variable N has an exponential distribution with rate  $\lambda_N$ . The conditional distribution P(X|Y) for the Q-ary noisy erasure channel is

$$P(Y = j | X = i) = \begin{cases} \epsilon_{j} - \epsilon_{j+1} & j < i \\ \epsilon_{j} (1 - \epsilon_{\text{pdp}}) + (\epsilon_{j} - \epsilon_{j+1}) \epsilon_{\text{pdp}} & j = i \\ (\epsilon_{j} - \epsilon_{j+1}) \epsilon_{\text{pdp}} & j > i \\ \epsilon_{Q} \epsilon_{\text{pdp}} & j = ? \end{cases}$$

(3.15)

where  $\epsilon_i = P(N > i\Delta T) = e^{-\lambda_N i\Delta T}$ .

**Figure 3.11:** *Q*-ary noisy erasure channel.

The solution of equation 3.3 in the general case requires to find the distribution of X that maximizes the mutual information I(X;Y). Equation 3.3 can be rewritten as

$$C = \max_{p(x)} I(X;Y)$$

$$= \max_{p(x)} \sum_{x} \sum_{y} p(x)p(y|x) \log \frac{p(x|y)}{p(x)}.$$

(3.16)

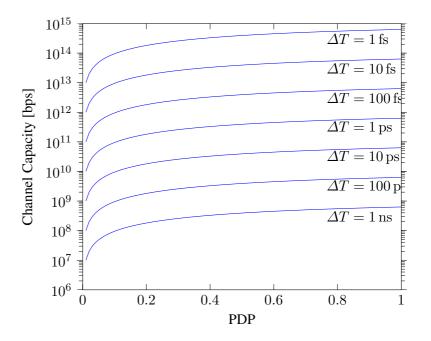

While equation 3.16 can be solved algebraically in several cases, we chose to use Arimoto-Blahut algorithm [67, 68] to solve it numerically with p(y|x) given by equation 3.15. The capacity per channel use was computed with noise ranging from a few herzt to one gigahertz. The results in figure 3.12 show that even in the case of noise as high as a few kilohertz, channel capacity is very close to the noiseless case.

**Figure 3.12:** Capacity per channel use in presence of noise and erasure. Q=4.

SPAD's dead time and afterpulsing should also be addressed. The effects of dead time can be mitigated in several ways. Let  $\tau_{\rm dt}$  denote the dead time. Imposing  $\Delta T > \tau_{\rm dt}$  would be very limiting in bandwidth unless  $\tau_{\rm dt}$  can be made arbitrarily small. Relaxing the requirement to  $Q\Delta T > \tau_{\rm dt}$  enables large channel capacity but, as the channel looses its memoryless property, state-dependent coding must be performed. Afterpulsing is highly linked with dead time. It can be seen as data-correlated noise which further reduce channel capacity. Source coding, such as block length coding, could be used to alleviate some of the these effects, however, we didn't yet expand our research in this area beyond the following paragraph.

Although we derived the channel capacity as a function of several system design variables, care should be taken in analyzing the numbers. As channel capacity is an upper limit to the transmission rate achievable, the practical limits are actually that of the source coding schemes implemented. We will not discuss source coding besides the fact that well known coding schemes such as Turbo Codes and Low Density Parity Check (LDPC) codes have shown performance approaching channel capacity. Area, power, and performance of such a system need to be analyzed in a prototype in order to finish this discussion. A first step toward this goal is presented in the next section, where we review time discrimination.

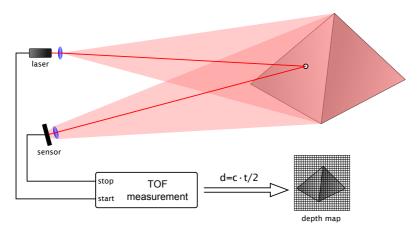

# 3.3 Time discrimination

This section is devoted to the measurement of time, that can be applied, but not limited to, PPM demodulation. In many applications, the precise measurement of the time difference between two signals spaced in time is important, especially when digital pulses are used relating to different physical measurements. Examples of such applications include time-of-flight sensors, optical correla-

tion spectroscopes, positron emission tomography instruments, and pulse position demodulators [69–71]. High time resolution, typically 100 ps, is key to achieving the desired performance, while high throughput is often required as well. For instance, in metrological applications, high throughput has the effect of achieving the wanted accuracy in a shorter time, thus improving the speed of a measurement or making it possible to achieve unprecedented accuracies whenever a phenomenon is fast occurring. Similarly, apparatuses, such as LIDARs, LADARs, and RADARs, as well as techniques using time-resolved imaging can benefit from this functionality [72,73].

We look to implement time measurement with Field Programmable Gate Array (FPGA) devices. However some of this discussion also apply to custom ASIC designs. Several techniques exist to measure a time difference; the simplest is based on a counter. In principle, the clock frequency of the counter determines the resolution. Thus, if metastability effects are ignored, to achieve 100 ps of resolution, a 10 GHz clock is required. Due to bandwidth limitations, it is generally not feasible to achieve such clock speeds in most commercial FPGAs. Alternatively, a time-to-amplitude converter (TAC) can be used. TACs enable detection of extremely short time differences by translating time onto voltage that can then be measured with high precision. However, this approach requires high-speed analog switches, high-precision current sources, and, in most cases, high-resolution A/D converters, components generally not available in conventional FPGAs.

An alternative is the use of a time-to-digital converter (TDC). TDCs are digital components that can be implemented in a fully-digital design style either as an ASIC or an FPGA. The literature on this type of devices is quite extensive, however, to our knowledge, none of them have implemented simultaneously in FPGA sub-nanosecond resolution *and* high throughput [74–85]. High time

resolution and high throughput are often contradictory specifications, however by proper use of design techniques and heavy use of pipelining, it is generally possible to achieve a good compromise. In the design proposed in [86] for example, a 3-stage pipelined TDC was used to achieve 10 MS/s with a resolution of 97 ps. However, the TDC was designed in full-custom style and it occupied a surface of approximately 0.4 mm<sup>2</sup>. In addition, the design was highly optimized, so as to achieve Process, Voltage and/or Temperature (PVT) variability control via a built-in feedback loop.

This section develops the FPGA-based TDC architecture presented in [83, 87, 88]. Two implementations of the architecture are presented. For the purpose of clarity, the latest implementation in a 65 nm FPGA is presented and the 130 nm FPGA implementation is shortly discussed in section 3.3.5. The 65 nm Virtex 5 implementations achieves an overall resolution of 17 ps over a range of temperatures. The TDC requires only 1208 slices while the throughput is 20 MS/s in normal operating mode and 300 MS/s in Turbo mode. The TDC exploits several design techniques to best utilize the available technology while maintaining high utilization efficiency. A repetitive fabric of CLBs is thus utilized to minimize clock net distribution mismatches while limiting skew. In addition, two calibration techniques are proposed for countering PVT variations albeit focusing mainly on temperature compensation.

The PVT variability control can be achieved either via a power supply control feedback on board or using an entirely digital scheme. The latter technique is based on the use of a periodical measurement of the fine delay of the TDC's built-in delay line. In case of temperature variations, each delay element will change its propagation delay, thus the number of delay elements will be adjusted. To maintain virtually the same resolution, the raw codes are mapped to the correct time difference using an appropriate table, while inter-value interpolations may be used. The same technique can be used when

migrating the TDC configuration from one FPGA to another and from one power supply to another, so as to achieve PVT independence.

### 3.3.1 Architecture

### **General Considerations**

Several time resolution methods are usually used in order to extend the range of measurement of time-to-digital converters. The Nutt interpolation technique splits the measurement between a coarse and fine (figure 3.13). At the coarsest level, a counter is usually employed, achieving nanosecond resolutions. At finer levels, the two most used approaches are

- 1. The Vernier method: it reaches its finest resolutions by harnessing the difference of propagation delays of the elements used. Generally two oscillators slightly out of tune [89,90] or two tapped delay lines with slightly different delay [91,92] are used.

- 2. The tapped delay line method: the method uses compensated [86, 93–96] or non-compensated [76–78] tapped delay lines. The resolution here is inherent to the delay element used.

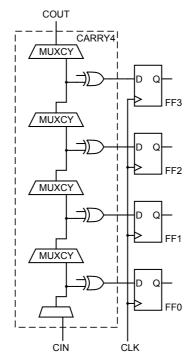

These techniques have been mapped to FPGA with relative ease. References [74–76, 81] use the Vernier method with mismatched delay lines while [80,85] use ring oscillators. In [77–79,82,83], like in this thesis the tapped delay line method based on carry propagation lines is employed. Dedicated carry lines present nowadays in all FPGA fabrics are usually employed in adder logic and therefore each adder's bit has a flip-flop nearby. For example, the Virtex-5 slices carry logic is shown in figure 3.14.

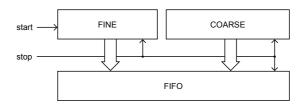

**Figure 3.13:** The global architecture of the TDC uses the Nutt interpolation technique whereby the measurement is split between coarse and fine.

**Figure 3.14:** Xilinx Virtex-5 slice (partial) with carry logic and sequential logic. CIN and COUT are inter-slice carry signal ports from the slice below and to the slice above respectively.

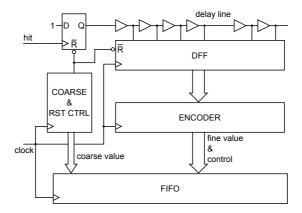

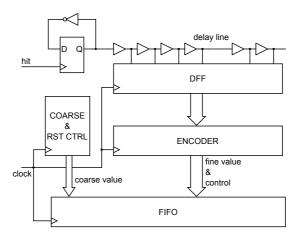

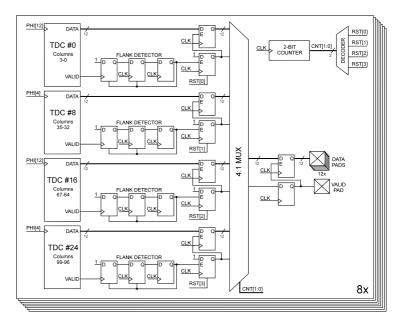

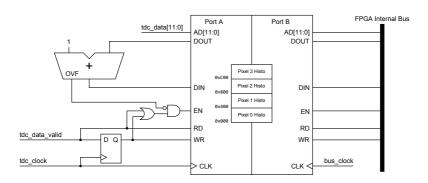

The architecture of the presented TDC, as shown in figure 3.15, consists of a free running coarse counter, a tapped delay line implemented in a carry chain, an input signal filter, an encoder, reset logic, and readout logic. The principle of operation is the following. Time is split in frames of 16 coarse clock cycles. The state of the delay line is latched at every clock cycle. A three-stage synchronizer is used to minimize metastability effects. Whenever the hit signal arrives, it propagates in the delay line. The detection and measurement is then performed by detecting transition in the first bits of the line. The thermometer encoded value in the line is converted to binary. Finally, the coarse and fine values are read out through a FIFO. A clock cycle is reserved for resetting the state of the delay line and filter, therefore one single measurement may be performed per frame.

**Figure 3.15:** Normal mode architecture of the TDC. The hit signal is fed to the delay line through a filter flipflop. The state of the delay line is latched at the rising edge of the clock which acts as stop signal. The reset circuitry, coarse counter, encoder, and FIFO are in the same synchronous domain.

Setup time or hold time of the fine chain latches are sometimes violated in the normal operation of the TDC. The value of violating latches will eventually resolve into a one or a zero. However, this can produce *bubbles* in the code, even when assuming a perfectly unskewed clock distribution. In the presence of clock skew, this phenomenon also occurs. A bubble-tolerant thermometer-to-binary encoder is required to limit the effect of bubbles on the output codes.

The design was implemented in VHDL with a completely automatic place and route procedure. Constraints were used to place the delay chain in the desired locations and no manual routing was performed.

### **Reducing Dead Time**

The hit signal propagates from the filtering flipflop to the fine delay line. Assuming an all-ones reset state of the line, zeros propagate from the beginning of the line toward the end. Since the line is sampled at each clock cycle, the resulting succession of *fine states* could be (bits flowing right to left):

| coarse | fine line                               |

|--------|-----------------------------------------|

| 0      | 1111111111111111111111                  |

| 1      | 11111111111111100000                    |

| 2      | 1110000000000000000000                  |

| 3      | 000000000000000000000000000000000000000 |

|        |                                         |

| 14     | 000000000000000000000000000000000000000 |

| 15     | 1111111111111111111111                  |

The measurement is armed at cycle 1 while cycle 15 resets the line to start a new measurement. The *dead time* is defined as the minimum time between the end of a measurement and the start of

the next one. For the architecture shown in figure 3.15, the dead time is one clock cycle. To reduce it, we propose to make use of propagation of ones and zeros alternatively with a toggling filter (fig. 3.16). With this architecture, the dead time is reduced to the minimum toggling time of the input filter flip-flop (<500 ps).

**Figure 3.16:** Turbo mode architecture. The two main differences from the normal mode architecture are: 1. the hit signal is filtered with a toggling flip-flop, hence '0's and '1's propagate through the delay line alternatively. 2. The filter and the line state latches are not reset anymore.

This architecture, referred to in the remainder of this chapter as Turbo mode, has the advantage of increased readout speed and the ability to handle multiple hits per frame. There are three main limitations of this design. First, the high-to-low and low-to-high transitions formed by the traveling hit signal have different propagation delays in the delay line. This yields an asymmetry in the measurement. Second, the metastability of the delay line latches is higher than in the normal architecture. The latches and input filter are never reset, therefore a metastable state can persist depending

on the clock frequency used. Third, the complexity of the encoder increases if detection of multi hits per clock cycle is required. Note however that our encoder can only encode a single measurement per clock cycle.

# 3.3.2 Digital Calibration

As traditional compensation techniques are not readily available in FPGAs, we need to rely on digital techniques to calibrate PVT variability. A method for mapping code to real-time value is necessary and of particular importance is the range of elements used in the fine line from which is derived the resolution. Several techniques to address these issues are presented in this section.

## Interpolation

Let  $N_{max}$  be the total number of elements in the chain. The interpolation process is the procedure by which a code c is converted from its natural interval (]0, N], with  $N < N_{max}$ ) to an output interval  $(]0, 2^b]$ ). Linear interpolation as the simplest approximation is defined:

$$c' = \left\lceil \frac{c \cdot 2^b}{N} \right\rceil$$

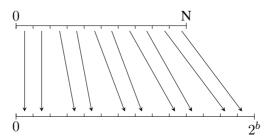

Linear interpolation can be conveniently implemented through mapping. The map information stored in a RAM block can be generated on-the-fly whenever the range changes. A single RAM lookup can output the interpolation result. As shown in figure 3.17, some codes may never appear in the output of the mapping if  $2^b > N$  and two or more input codes can be mapped to the same output code if  $2^b < N$ .

The real bin width of the fine elements can be estimated through a statistical code density test [97]. The interpolation process can be

**Figure 3.17:** With linear interpolation, output codes are skipped so that the N input codes are mapped into the  $[0, 2^b]$  range.

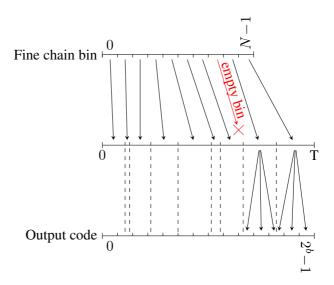

improved with this knowledge. If the output code space is chosen such that  $2^b > N$ , then there exists a source bin (a *large* bin) that is mapped to several destination bins. A pseudorandom distribution of original bin values to the corresponding output bins can be performed. For example, in figure 3.18, given the statistical code density test result, we can build an intermediate representation of the binning interval. This interval is the real-value time interval of one clock cycle where each bin has its size set according the density test. The interval is quantized into  $2^b$  slots. A given bin will then map to the corresponding slots to the extent of the bin coverage. For example the last bin in figure 3.18 will map to output codes  $2^b - 1$  and  $2^b - 2$  with likelihood of 40 % each and to  $2^b - 3$ with likelihood of 20 %. This non-deterministic mapping can be implemented on FPGA with a pseudorandom number generator or as a post-processing step. We call this method pseudorandom bin dithering in the remainder of this chapter.

### Automatic Range Adjustment (ARA)

Let N(x) be the number of propagated bits in the fine delay line latched at cycle x. Measurement N(x) is valid if N(x)>0 and

**Figure 3.18:** Pseudorandom bin dithering based on statistical code density test results. The statistical code density test is used to infer the real bin width of the fine chain bins. Each bin is first mapped to the real-value time interval spanning one clock cycle. Then, for each output code a probability density function is computed. In the example, the fine chain bin N-3 was found empty after the code density test, hence not output code space is allocated.

N(x-1)=0. Measurement N(x+1) is a range measurement if N(x) is valid and  $N(x+1) \neq N_{max}$ . The average resolution of the fine delay line r or 1 LSB is defined by

$$r = \frac{T}{N(x+1) - N(x)}$$

where T is the clock period. In the example of table 3.1, x+1 is a range measurement and therefore r=T/10.

| coarse | fine line              | N(x) |

|--------|------------------------|------|

| x-1    | 111111111111111111111  | 0    |

| x      | 11111111111111000000   | 6    |

| x + 1  | 1111000000000000000000 | 16   |

|        |                        |      |

**Table 3.1:** Automatic Range Adjustment Example: measurement at cycle x is valid. measurement at cycle x+1 is a range measurement. The resolution r=T/10

This method has the advantage of enabling to adjust the range on-the-fly while measurements are performed. A running mean of the range value can be kept and the interpolation process can be adapted consequently. However, this method can only adapt to relatively slow changing variations in PVT (in the order of several hundred clock cycles) and requires that some of the measurements yield a range measurement. This last requirement might never happen, therefore a simple range calibration scheduling can be put in place in order to gather these periodically.

## **Downsampling**

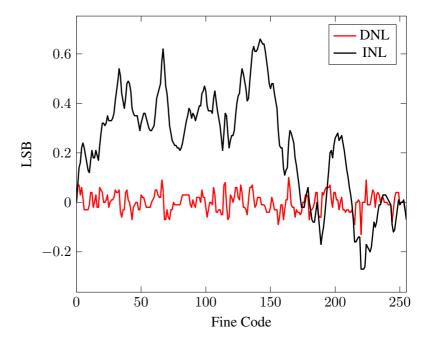

The inter-slice routing delays are expected to be relatively large compared to those inside a slice. Better uniformity can be obtained by implementing only 1 tap per slice at the cost of reduced resolution. While we decided to use the maximum resolution the fine line can offer by implementing 4 taps per slice (see Fig. 3.14), some results of the downsampling technique are presented in section 3.3.3.

### 3.3.3 Results

### **Test Setup**

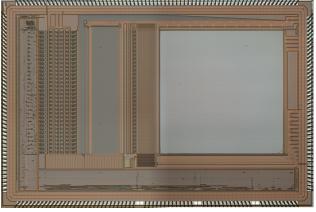

A Xilinx ML505 board was used to perform our experiments. The on-board Virtex-5 device is fabricated in 1 V, 65 nm triple-oxide process. High frequency SMA connectors were employed to feed the *hit* signal to the FPGA clock inputs. A custom USB interface board is used to transfer measurements to a computer. All reference measurements, such as input clock jitter, cable time delay, and time distribution of the random input signal, were performed on a LeCroy WaveMaster 8600A digitizing oscilloscope.

The clock (*stop* signal) of our design is generated on board by a low jitter frequency synthesizer. The differential output of the synthesizer after on-board buffering and an FPGA pass-through connection shows a measured jitter of less than 12 ps at 300 MHz. The coarse counter is free running at this frequency and shows an integral linearity error below 0.03 coarse LSBs. Our focus for the remainder of this section will be on the fine interpolation technique.

Three types of measurement were performed: linearity characterization, ARA validation, and precision evaluation.

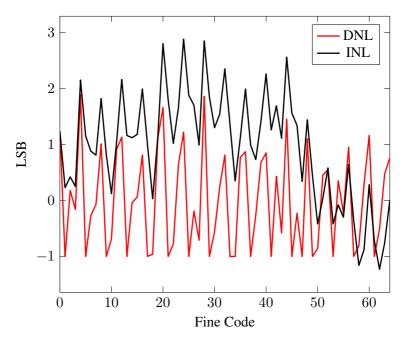

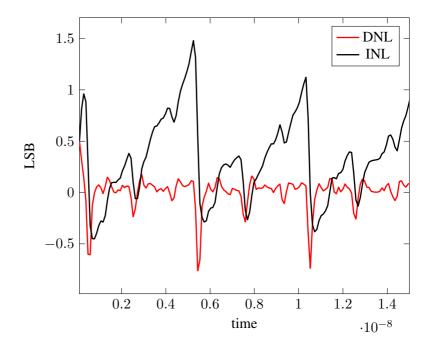

The linearity of the TDC can be characterized in several ways. A precise variable delay generator such as a tapped mechanical rail can be used to cover all of the fine TDC measurement range and derive the linearity. This yields stair shaped graphs such as those found in [74,79,98–101]. Another commonly used method is the statistical code density test [74]. The idea is to generate a large number N of pulses randomly distributed in time, and to collect the result of the TDC interpolation into a histogram. In the ideal case the histogram has C code bins containing  $\overline{n} = N/C$  counts each. In reality there is a differential non-linearity DNL<sub>c</sub> and for each

code  $c \in [1, C]$ ,  $n_c \neq N/C$ ,  $n_c$  representing the depth of bin c.

$$DNL_{c} = \frac{n_{c}}{\overline{n}} - 1.$$

The cumulative sum of  $DNL_c$  yields the integral non-linearity  $INL_c$

$$INL_c = \sum_{i=1}^c DNL_i.$$

INL and DNL values refer to the 1-bin unit hence are expressed in LSB units. Note also that, in practice, a random pulse generator is not required as a non-stabilized oscillator suffice as long as the output is not correlated with the TDC's main clock.

The automatic range adjustment values are gathered whenever available. All the values are collected into a histogram, and we derive the mean bin width of the fine codes.

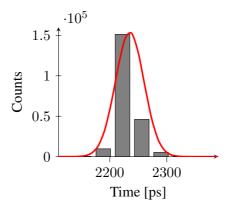

To measure the standard uncertainty or random error, we inject a delayed version of a clock synchronous signal into the fine delay line. Several fixed length cables are used to generate delays. Several hundred thousand measurements are taken and the worst standard deviation of the resulting codes is reported.

The pseudorandom bin dithering technique described in section 3.3.2 has also been evaluated. While its implementation in FPGA is conceivable, we post-processed gathered traces to produce the DNL and INL graphs shown.

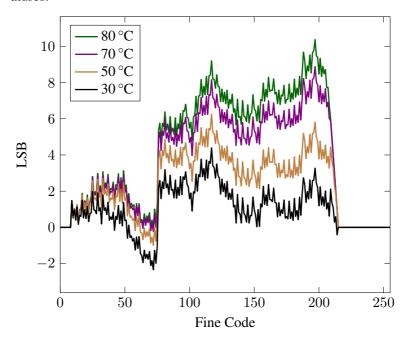

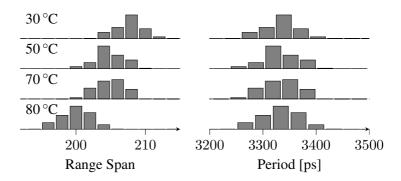

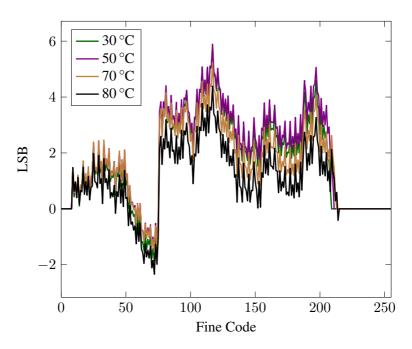

Temperature measurements were performed to validate ARA and to evaluate the variability in temperature. The temperature was set from  $30\,^{\circ}\text{C}$  to  $80\,^{\circ}\text{C}$  in a kiln. The measurement were taken after a stabilization period of up to 15 minutes. Both ARA and INL variations are reported.

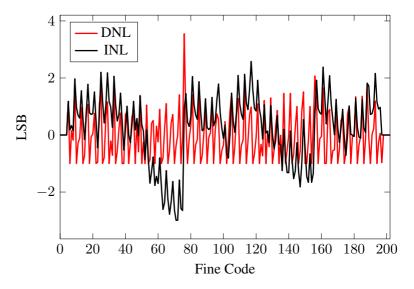

### Measurements

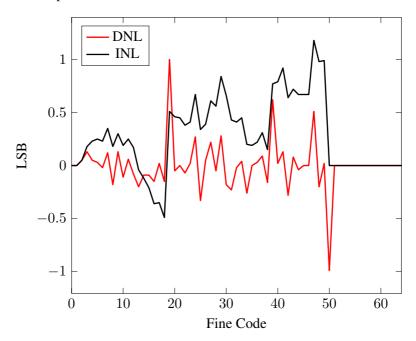

The statistical code density tests were performed with a photodetector exposed to ambient light. The sensor based on a single photon avalanche diode (SPAD) [5] displays a uniform distribution of pulses separated by at least 30 nanoseconds. Note that the same test can also be performed with an oscillator non-correlated with the system clock. In fact, the phase variations, between the oscillator signal and the system clock, due to non-tuned frequencies and PVT noise can ensure uniform coverage of the time interval. Such oscillator could also be implemented directly in FPGA, allowing *in situ* calibration. Figure 3.19 shows the INL and DNL of the fine line. The obtained DNL varies between -1 and +3.55 LSB. The INL lies in [-3, +2.58] LSB range.

**Figure 3.19:** Performance of the fine measurement. Differential and Integral Nonlinearity.

The large variations of DNL in figure 3.19 around bin 76 are due to the clock skew between slices. The clock signal travels from the differential input clock pads to a global clock buffer (BUFG) and is then distributed through regional buffers to each slice. The delay from the BUFG to some slice is reported in table 3.2. Note that the difference between slice X28Y39 and X28Y40 is 57 ps (=3.3 LSB).

| Slice  | Delay   | Fine position |

|--------|---------|---------------|

| X28Y21 | 1.614ns | 3             |

| X28Y22 | 1.612ns | 7             |

| X28Y23 | 1.609ns | 11            |

|        |         |               |

| X28Y37 | 1.613ns | 67            |

| X28Y38 | 1.615ns | 71            |

| X28Y39 | 1.617ns | 75            |

| X28Y40 | 1.560ns | 79            |

| X28Y41 | 1.558ns | 83            |

| X28Y42 | 1.556ns | 87            |

| X28Y43 | 1.553ns | 91            |

| X28Y44 | 1.549ns | 95            |

| X28Y45 | 1.544ns | 99            |

Table 3.2: Clock distribution delays for fine TDC line.

The results of our statistical code density tests show that inside each slice there is a disparity between the four latches (fig. 3.14). Besides the fact that the distribution across the four latches is not uniform, the second latch in every slice never becomes the most significant propagation bit. This systematic error can be explained by the combination of two factors. First, the propagation delay inside the CARRY4 structure is not uniform. The simulation results shown in table 3.3 display a delay for bin 2 that is substantially

smaller. Second, the clock skew between the latches is similar to the inter-slice clock skew problem of the previous paragraph. These phenomena contribute to the creation of bubbles.

| Point | Delay [ps] | Diff [ps] |  |

|-------|------------|-----------|--|

| CIN   | 0          | 0         |  |

| FF0_D | 33         | 33        |  |

| FF1_D | 47         | 14        |  |

| FF2_D | 81         | 34        |  |

| FF3_D | 104        | 23        |  |

**Table 3.3:** Carry4 structure delay from CIN to FF (from simulation).

Several placements of the delay chain were tested and this nonlinearity was found in all the designs. With further inspection we noticed that the anomaly arises when the chain crosses the middle of the device from slice X\*Y39 to slice X\*Y40. Since our design needs at least 50 slices (200+ bins) to cover a clock period, this non-linearity cannot be mitigated with chain placement. The clock skew variability underlying this problem was described in detail in [102]. To be able to remove the problem without changing device, we propose two solutions. The first solution is to compensate the clock skew by generating delayed versions of the clock for each problematic region. This can be done either with DCM or IODE-LAY elements. Note however that DCMs inject significant jitter (see section 3.3.4). The second solution is thus recommended to shorten the fine line and place it in such a way to avoid the particularly bad spots. To reduce the delay line, either the clock frequency needs to be increased or the line must be split in two; it thus operates on both clock edges. This has to be done in order to always have a complete clock cycle covered.

Downsampling by 4 (1 bin per slice) leads to improved INL as shown in figure 3.20. Here the INL's range is [-0.49, +1.18] LSB. The drawback of this approach is the loss of resolution. In this context, for about the same resolution as [78], the INL of our system [-0.49, +1.18] LSB is narrower than in [78] [-2.003, +1.855] LSB. While the clock skew problem was also reported in that work, note that the device used (Virtex II) is fabricated in a 130 nm, 1.5 V CMOS process.

**Figure 3.20:** DNL and INL of the fine delay line after downsampling by 4 (1 tap per slice).

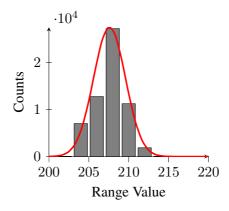

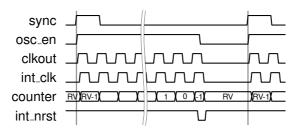

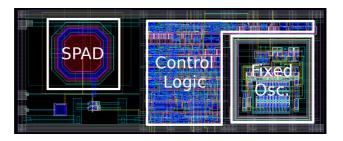

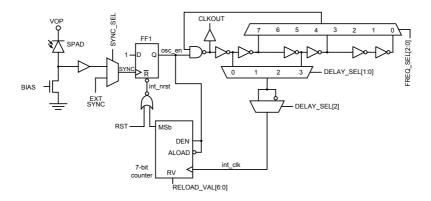

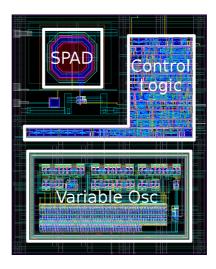

The collected values for the automatic range adjustment are shown in figure 3.21. The histogram of the values taken at  $30\,^{\circ}$ C, yields to the conclusion that, on average, 207 elements are used to cover a clock cycle of 3.3 ns. The bin width is therefore, on average, 16.1 picoseconds. The standard deviation of the histogram is of about 2 bins.