## Organic Pentacene Thin Film Transistors on Flexible Substrates Fabricated by Stencil Lithography

## THÈSE N° 4854 (2010)

PRÉSENTÉE LE 3 DÉCEMBRE 2010

À LA FACULTÉ SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

LABORATOIRE DE MICROSYSTÈMES 1

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

### Katrin SIDLER ARNET

acceptée sur proposition du jury:

Prof. Ph. Renaud, président du jury Prof. J. Brugger, directeur de thèse Prof. A. Boisen, rapporteur Dr S. Lacour, rapporteur Prof. L. Zuppiroli, rapporteur

Microsystems Laboratory (LMIS1), Ecole Polytecnique Fédérale de Lausanne (EPFL)

Thesis Director:

Prof. Dr. Jürgen Brugger

## **Abstract**

This thesis presents the fabrication and characterization of organic thin film transistors (TFTs) on flexible polymer substrates and the development of compliant stencil lithography to significantly improve the patterning resolution on full-wafer scale.

Polymers and organic semiconductors have gained increasing attention during the last years. Today, organic semiconductors are envisioned as a viable alternative to traditional TFTs based on inorganic materials. Organic TFTs can be a solution for device flexibility, cost-efficient fabrication, low-temperature processing and large area patterning. However, up to now they cannot keep up with the performance of TFTs based on single-crystalline inorganic semiconductors because of their low switching speeds. Due to the sensitivity of polymers and organic semiconductors to solvents and high temperatures, stencil lithography is a promising patterning technique for such materials.

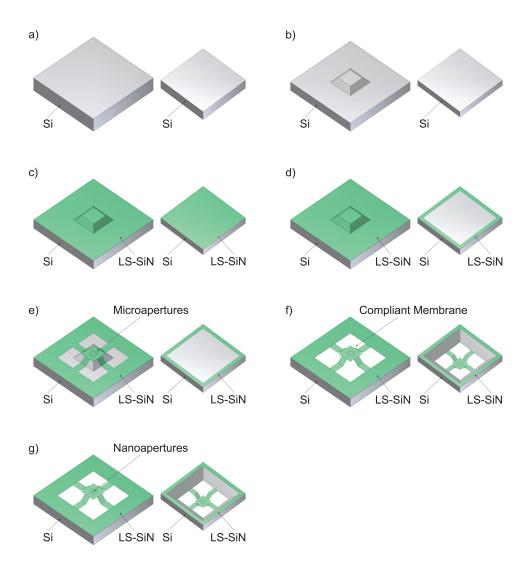

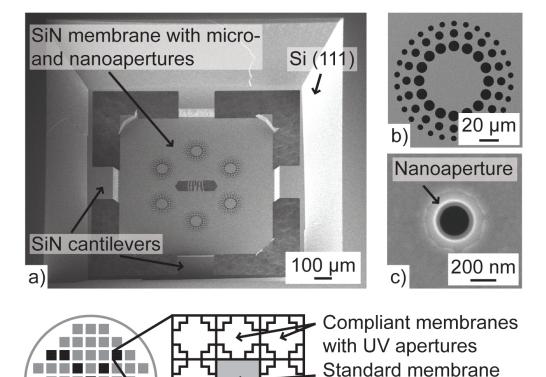

Stencil lithography is based on the principle of the shadow mask technique, which is a parallel process with high spatial resolution down to submicrometer scale. It is a solvent-free patterning method without need of elevated temperatures. The stencil is aligned and clamped to the substrate and the required material is deposited through the stencil. Finally the stencil is removed, resulting in a patterned substrate. A typical stencil is made of low-stress silicon nitride (SiN) membranes supported by bulk silicon (Si). The membranes are released by combined dry and wet etching and contain design-specific micro- and nanoapertures.

Stencil lithography was used to pattern titanium-gold (Ti-Au) wires on flexible polymer substrates. The wire resistivity was analyzed by 2-point and 4-point measurements and was found to be comparable with the resistivity of a Ti-Au thin film on a Si wafer.

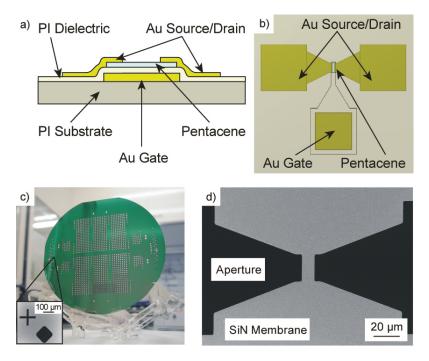

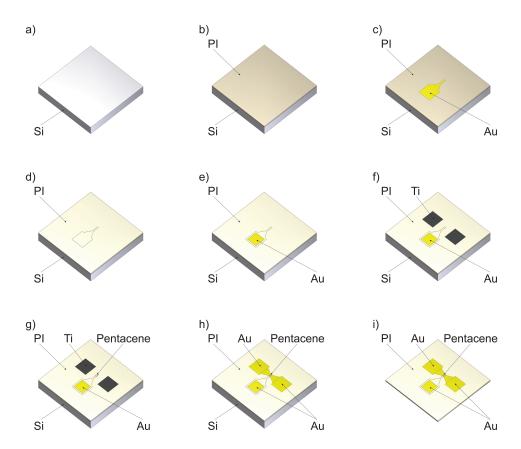

Stencil lithography was also applied to fabricate organic TFTs on a rigid Si sub-

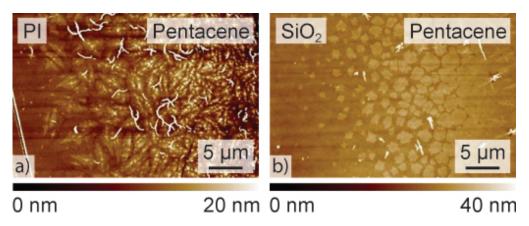

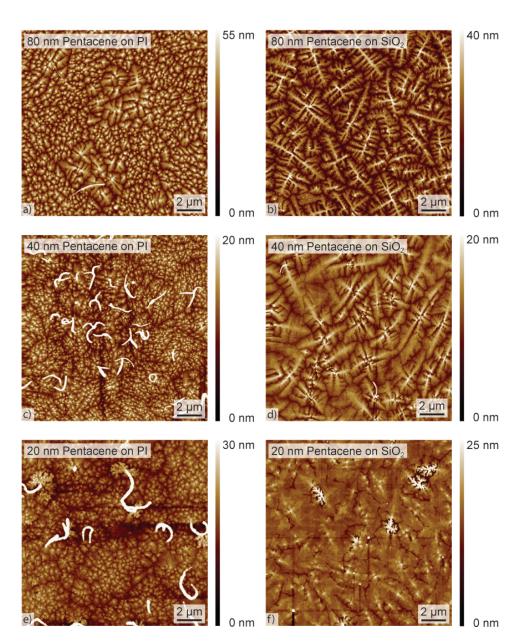

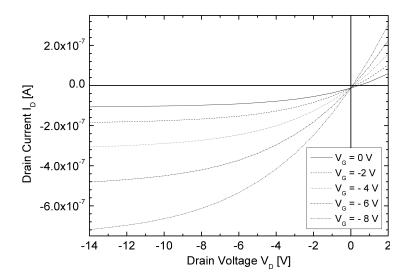

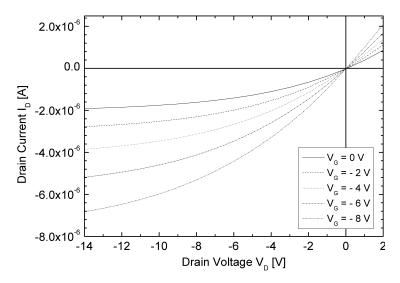

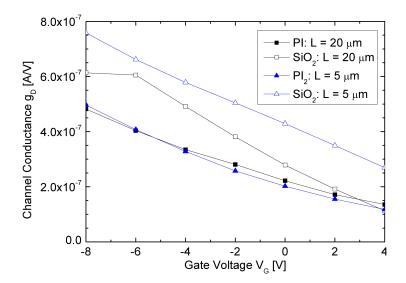

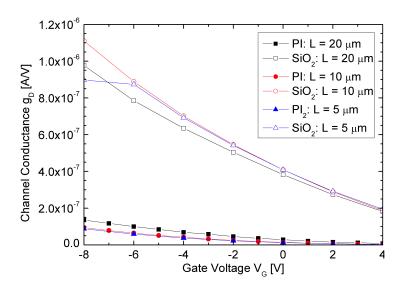

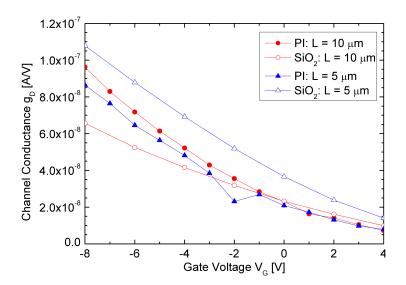

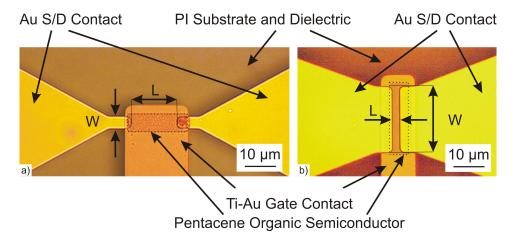

strate as the back gate contact. Polyimide (PI) or silicon dioxide (SiO<sub>2</sub>) was used as the dielectric layer while pentacene was tested as the organic semiconductor. Source-drain (S/D) Au top contacts were patterned by stencil lithography defining transistor channel lengths down to  $5 \,\mu m$ . Pentacene TFTs with different film thicknesses were characterized on both dielectrics. The organic TFT fabrication on rigid Si substrates was used to evaluate pentacene films deposited on a PI dielectric. They have shown continuous pentacene films and similar characteristics compared to SiO<sub>2</sub> as the dielectric layer.

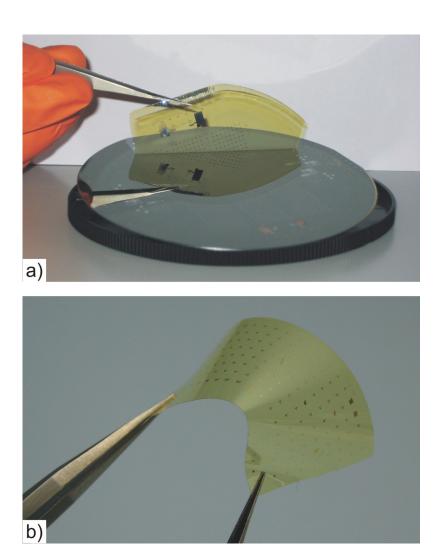

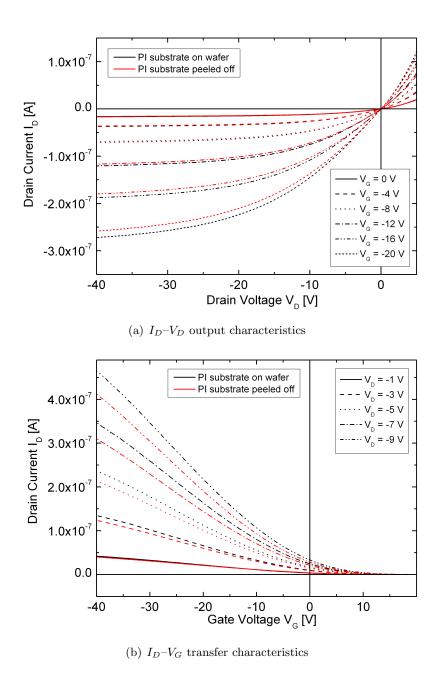

In a next step pentacene TFTs on a flexible 12  $\mu$ m thin PI substrate were fabricated on full-wafer scale using a Si wafer as a rigid support. The gate contacts were patterned locally and PI was used as the dielectric material. Pentacene and S/D Au contacts were patterned by applying aligned full-wafer stencil lithography for channel lengths down to 2.5  $\mu$ m. The yield of 72 pentacene TFTs was as high as 91.5 % and the average apparent mobility  $\mu$  was  $(5.0 \pm 0.7) \cdot 10^{-2}$  cm<sup>2</sup>/Vs. The pentacene TFTs have been characterized both before and after peeling the flexible PI film off the rigid Si support, showing a to  $(83 \pm 4)$  % reduced apparent mobility  $\mu$ .

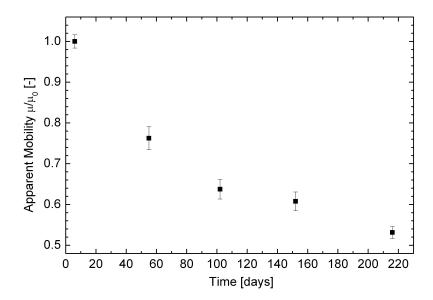

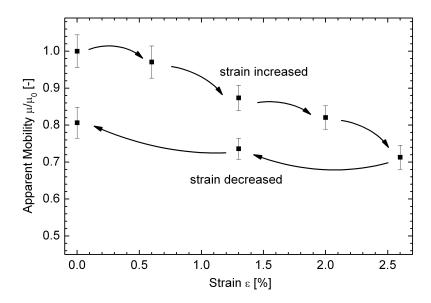

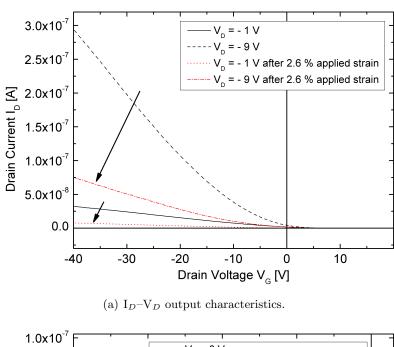

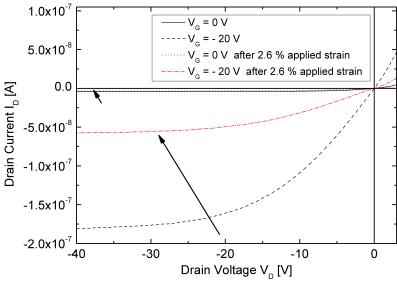

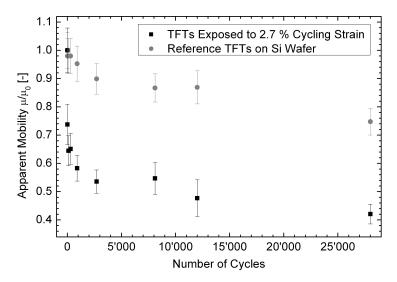

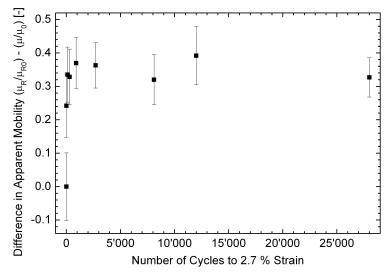

Pentacene TFTs were also characterized during and after exposing the PI substrate to tensile stress. It was found that uniaxial stretching experiments reduced the apparent mobility  $\mu$  to  $(71 \pm 3)$  % when the applied strain  $\epsilon$  was increased to 2.6 %. After releasing the applied strain  $\epsilon$  the apparent mobility  $\mu$  recovered partially to  $(81 \pm 4)$  % of its initial value. Cycling strain applied to the PI substrate changed the apparent mobility  $\mu$  distinctively within the first 1000 cycles compared to the reference TFTs. Further stretching cycles decreased the performance of stretched pentacene TFTs similar as the reference TFTs. After 28'000 cycles of 2.7 % applied strain  $\epsilon$  the apparent mobility  $\mu$  was reduced to  $(42 \pm 3)$  %. In parallel to the mentioned experiment, a degradation of the pentacene film over time was monitored. The apparent mobility  $\mu$  was significantly reduced to  $(61 \pm 2)$  % of its initial value.

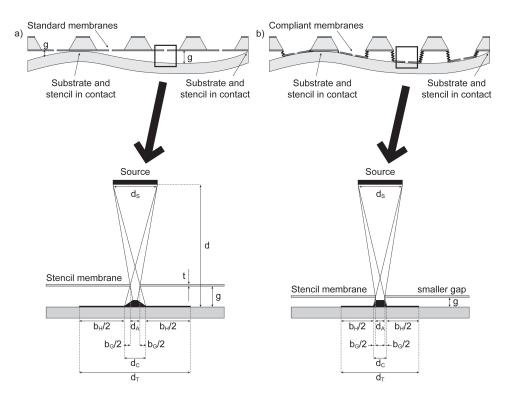

A known drawback in stencil lithography is the so-called blurring, which is the loss of resolution during the pattern transfer. The main cause of the blurring is the gap between the stencil membrane and the substrate surface. The origin of the gap has several reasons such as the non-planarity of the substrate or different curvatures

of stencil and substrate on full-wafer scale. The variation of the wafer curvature due to unsymmetrical patterning of front- and backside of the wafer was monitored during stencil fabrication. One of the major finding is that an increased curvature of the stencil results in an increased gap and therefore reduces the resolution of stencil lithography.

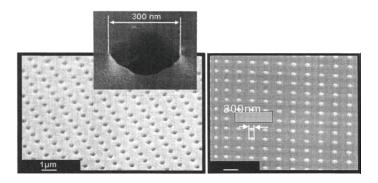

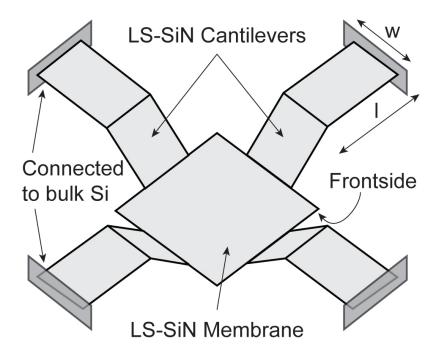

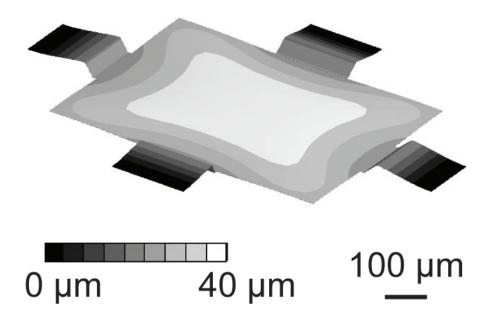

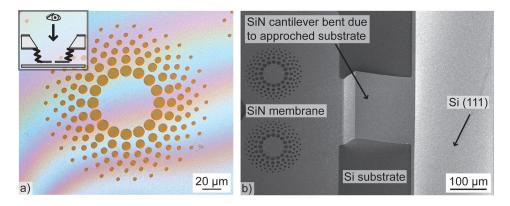

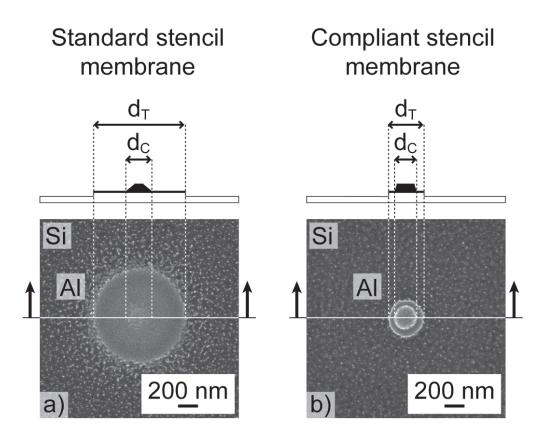

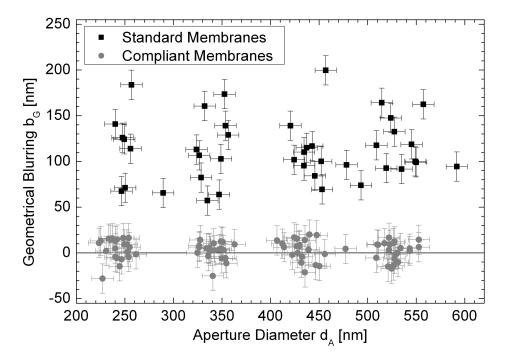

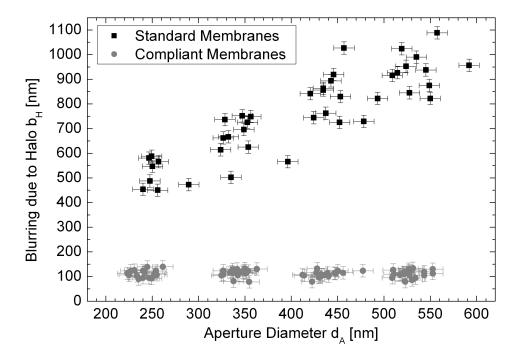

Therefore, a more sophisticated stencil based on compliant membranes is proposed in order to minimize the gap and improve the resolution of pattern transfer on full-wafer scale. Compliant membranes are mechanically decoupled from a rigid Si frame by means of four non-planar cantilevers. Compliant membranes are protruding parts, which adapt to the surface independently in order to reduce the gap between a membrane and its substrate. Finite element method (FEM) simulations have shown that compliant membranes can vertically deflect 40 µm, which is a typical maximal gap that can occur between stencil membrane and substrate. Microapertures were defined using ultraviolet (UV) lithography and nanoapertures, down to 200 nm in diameter, using focused ion beam (FIB). An aluminum (Al) layer was evaporated through compliant and non-compliant membranes on a Si wafer. Subsequent scanning electron microscopy (SEM) characterizations have shown that the use of a compliant stencil improves significantly the resolution on large area. The geometrical blurring was 95 % and the halo more than 75 % smaller compared to standard (i.e. non-compliant) full-wafer stencil lithography.

The results of this thesis demonstrate stencil lithography as a reliable fabrication method for metallic microstructures and organic pentacene TFTs on flexible PI substrates and represent a breakthrough towards improved resolution in full-wafer compliant stencil lithography.

**Keywords** Stencil lithography, flexible substrate, polyimide (PI), organic thin film transistor (OTFT), organic semiconductor, pentacene, flexible electronics, compliant stencil lithography

## Résumé

Ce travail de thèse présente la fabrication et la caractérisation de transistors organiques à couche mince (TFT<sup>1</sup>) sur des substrats polymériques flexibles et le développement de la lithographie par stencil adaptable afin d'améliorer la résolution sur tout un wafer.

Les polymères et les semi-conducteurs organiques ont gagné un intérêt croissant depuis plusieurs années. Aujourd'hui les semi-conducteurs organiques sont considérés comme une alternative prometteuse aux TFTs traditionnels à base inorganique. Les TFTs organiques pourraient être une solution pour des unités flexibles, une fabrication à coûts réduits, des procédés à basse température et la structuration de grandes surfaces. Ils ne peuvent cependant pas rivaliser avec les performances des TFTs à base inorganique à cause de leurs basses vitesses de couplage. En raison de la sensibilité des polymères et des semi-conducteurs organiques aux solvants et aux hautes températures, la lithographie par stencil est une technique prometteuse pour de tels matériaux.

La lithographie par stencil est basée sur le principe de masques durs qui est un procédé parallèle, ayant une résolution au dessous du micromètre. C'est une technique sans solvants et qui ne nécessite pas de températures élevées. Le stencil est aligné et fixé sur le substrat et le matériau nécessaire est déposé à travers. Finalement, le stencil est retiré, laissant le substrat structuré. Un stencil typique se compose de membranes de nitrure de silicium (SiN) à faible stress tenues par un cadre de silicium (Si). Les membranes du stencil, qui contiennent les micro et nano ouvertures, sont ensuite libérées par une combinaison de gravure sèche et humide.

La lithographie par stencil a été utilisée pour structurer des fils de titan-or (Ti-Au) sur des substrats polymériques flexibles. La résistivité des fils a été analysée

<sup>&</sup>lt;sup>1</sup>l'acronyme anglais du transistors à couche mince est selon thin film transistor TFT

par des mesures à 2-pointes et à 4-pointes et correlée avec la résistivité d'une couche mince de Ti-Au sur wafer de Si.

La lithographie par stencil a aussi permis la fabrication de TFTs organiques sur substrats rigides de Si servant de grille arrière. Le polyimide (PI) ainsi que l'oxyde de silicium (SiO<sub>2</sub>) ont servi de diélectrique pendant que le pentacène a été testé comme semi-conducteur organique. Les contacts de la source et du drain (S/D) on été structurés par lithographie par stencil définissant des longueurs de canaux de transistors descendant jusqu'à 5 µm. Des TFTs avec différentes couches de pentacène ont été caractérisés sur les deux diélectriques. La fabrication des TFTs organiques sur substrat rigide de Si a été utilisée pour l'évaluation des couches de pentacène sur PI. Ses performances électriques ont été comparées avec SiO<sub>2</sub>; comme diélectrique.

Par la suite, des TFTs de pentacène sur substrat flexible de PI ont été fabriqués sur un wafer de Si complèt, en l'utilisant comme support rigide. Les contacts de la grille ont été structurés localement et le PI utilisé comme diélectrique. Le pentacène et les contacts S/D ont été structurés sur tout le wafer en utilisant la lithographie par stencil avec alignement pour définir des canaux de transistors descendants jusqu'à  $2.5 \,\mu\text{m}$ . Le rendement de 72 TFTs de pentacène a atteint les 91.5 % et la mobilité apparente  $\mu$  moyenne les  $(5.0 \pm 0.7) \cdot 10^{-2} \, \text{cm}^2/\text{Vs}$ . Les TFTs de pentacène ont été caractérisés avant et après leur détachement du wafer de Si. La mobilité apparente à été réduite à  $(83 \pm 4) \,\%$ .

Les TFTs de pentacène ont aussi été caractérisés pendant et après l'application d'une tension mécanique. Une tension uniaxiale de 2.6 % a réduit la mobilité apparente  $\mu$  à  $(71 \pm 3)$  % de sa valeur initiale. Revenant en position de repos, la mobilité apparente  $\mu$  est remontée jusqu'à  $(81 \pm 4)$  %. La tension appliquée cycliquement a largement diminué la mobilité apparente  $\mu$  pendent les 1000 premiers cycles. Les cycles suivants ont diminué la performance des TFTs de pentacène de la même manière que les TFTs de référence. Après 28'000 cycles d'une tension de 2.7 %, la mobilité apparente  $\mu$  a été réduite à  $(42 \pm 3)$  %. En parallèle des expériences mentionnées, la dégradation d'une couche de pentacène a été analysée. La mobilité apparente  $\mu$  a été réduite à  $(61 \pm 2)$  %.

Le désavantage principal de la lithographie par stencil est le blurring; élargissement des structures déposées. La cause principale du blurring est l'espace entre la membrane et le substrat. L'origine de cet espace est la mauvaise planéité du wafer ou des diverses courbures du stencil et du substrat. Les variations de courbure d'un wafer à cause de la structuration asymétrique des faces avant et arrière ont été analysées. Une augmentation de la courbure du substrat induit un espace plus large entre le substrat et le stencil et diminue la résolution de la lithographie.

Un stencil plus sophistiqué, basé sur des membranes adaptables est proposé pour diminuer l'espace et améliorer la résolution sur le wafer complèt. Les membranes adaptables sont découplées du cadre de Si avec quatre leviers hors-plan. Les membranes dépassent le cadre de Si et s'adaptent à la surface du substrat. La méthode des éléments finis (FEM²) a montré que les membranes adaptables peuvent se déplacer de 40 µm, ce qui est typiquement l'espace maximum entre la membrane et le substrat. Les ouvertures micrométriques sont structurées par photolithographie et les ouvertures nanométriques, jusqu'à 200 nm, par sonde ionique focalisée (FIB³). Une couche d'aluminium (Al) a été évaporée à travers les membranes adaptables et standardes. La microscopie électronique à balayage (SEM⁴) a montré que la résolution est alors nettement améliorée. Le blurring causé par la géométrie est réduit de 95 % et le blurring causé par le halo est diminué d'au moins 75 % par rapport à la lithographie par stencil standard.

Les résultats de cette thèse montrent que la lithographie par stencil est une méthode intéressante pour la structuration des métaux et des TFTs organiques de pentacène sur substrats de PI flexibles. De plus, la lithographie par stencil adaptable apporte une amélioration considérable sur la résolution sur tout le wafer.

**Mots-clefs** Lithographie par stencil, substrat flexible, polyimide, transistor organique à couche mince (OTFT), semi-conducteur organique, pentacène, électronique flexible, lithographie par stencil adaptable

<sup>&</sup>lt;sup>2</sup>l'acronyme anglais de la méthode des éléments finis est selon finite element method FEM

<sup>&</sup>lt;sup>3</sup>l'acronyme anglais de la sonde ionique focalisée est selon focused ion beam FIB

<sup>&</sup>lt;sup>4</sup>l'acronyme anglais de la microscopie électronique à balayage est selon scanning electron microscopie SEM

## **Preface**

This thesis is an assignment to obtain the degree of "Docteur ès Sciences" at the Swiss Federal Institute of Technology Lausanne (EPFL). Since May 2006, I am working as a PhD student in the group of Microsystems Laboratory (LMIS1) at EPFL, Switzerland. Many people supported me immensely for the realization of this work.

I would like to thank my thesis supervisor Prof. Dr. Jürgen Brugger for offering me a position in his cheerful group and giving me much freedom to realize my ideas.

I thank the jury of my oral thesis examination Prof. Dr. Anja Boisen, Dr. Stéphanie Lacour, Prof. Dr. Libero Zuppiroli and the jury president Prof. Dr. Philippe Renaud for having kindly accepted my request.

I acknowledge the Swiss National Science Foundation (SNSF) for the financial support of my thesis. The presented results were realized within the projects "Radio on Paper" and "Flexible Radios".

Both SNSF projects were carried out in collaboration with Nanolab at EPFL. I would like to thank Prof. Dr. Adrian Ionescu for being the project initiator and his scientific support. Many thanks to Nenad Cvetkovic and Dr. Dimitrios Tsamados for the diverse explanations about thin film transistors.

A part of this thesis was done in collaboration with the Laboratory of Optoelectronics of Molecular Materials (LOMM) at EPFL. Sincere thanks to its leader Prof. Dr. Libero Zuppiroli for introducing me to his group and their meetings. Special thanks go to Franziska Fleischli for the excellent teamwork and to Michel Schär for assisting me in their laboratory. I would also like to thank Paul Ivaldi, Dr. Stéphane Suarez, Michel Longchamp, Philippe Bugnon and Dr. Adrian von Mühlenen for their help and advices. I always felt welcome.

The fabrication of the presented samples and devices within this thesis was mainly

carried out at the Center of Micro and Nanotechnology (CMI) at EPFL. I would like to thank Dr. Philippe Flückiger and his team for their effort and friendly support. I enjoyed very much to work in this professionally run clean room laboratory.

Ilona Modoux and Marie Halm supported me within the administration at EPFL. Thank you very much for your patience and the information you provided me.

I specially thank to Dr. Guillermo Villanueva for his unconditional support and his open door for any questions and concerns. Big thanks to Dr. Oscar Vazquez Mena for patterning hundreds of FIB apertures in my membranes, continuously discussing my results and keeping me up to date with latest publications. Thanks to Dr. Victor Cadarso, Dr. Veronica Savu, Dr. Schahrazède Mouaziz, Dr. Nao Takano, Dr. Thomas Kiefer, Dr. Vaida Auzelyte and Dr. Maurizio Gullo for their kind assistance in writing scientific reports. Many thanks go to Jonas Grossenbacher and Loïc Jacot-Descombes who contributed to the French translation of the abstract.

Within this thesis I assisted four students during a project. I thank Nicolas Ferrier, Alexandre Michalis, Jean-Baptiste Lincelles and Camille Chaumien for the excellent results.

Many thanks go to my former and present colleagues of LMIS1, Mattia Marelli, Kristopher Pataky, Jonas Henriksson, Shenqi Xie, Dr. Songmei Wu, Mona Klein, Dr. Bastien Rachet, Dr. Peter Vettiger, Dr. Cristina Martín, Dr. Joo Yeon Kim, Dr. Christian Santschi, Dr. Vahid Fakhfouri, Dr. Marc van den Boogaart, Dr. Chan Woo Park, Dr. Yun Luo, Dr. Jeroen Steen, Dr. Sivashankar Krishnamoorthy. Big thanks to all my friends in and close to the BM building for all the jokes, dinners, bike-to-work participations, swimming sessions, parties, discussions, lunch and coffee breaks.

I specially thank my parents Hanna and Heinz, my sisters Esther and Astrid and my husband Paul for their encouragement and enormous support for so many years.

> Katrin Sidler Lausanne, October 8, 2010

# Glossary

## Symbols

| A              | Cross section                     | $[m^2]$                |

|----------------|-----------------------------------|------------------------|

| $\mathbf{b}_G$ | Geometrical blurring              | [m]                    |

| $\mathbf{b}_H$ | Blurring due to halo              | [m]                    |

| c              | Capacitance of dielectric layer   | $[F/m^2]$              |

| d              | Distance from source to substrate | [m]                    |

| $d_A$          | Aperture diameter                 | [m]                    |

| $\mathrm{d}_C$ | Diameter of center part           | [m]                    |

| $\mathrm{d}_S$ | Source diameter                   | [m]                    |

| $\mathrm{d}_T$ | Total diameter                    | [m]                    |

| E              | Young's modulus                   | [Pa]                   |

| g              | Gap                               | [m]                    |

| $g_D$          | Channel conductance               | [S] or $[\Omega^{-1}]$ |

| $g_m$          | Transconductance                  | [S] or $[\Omega^{-1}]$ |

| $I_D$          | Drain current                     | [A]                    |

| $I_{on}$       | On current                        | [A]                    |

| $I_{off}$      | Off current                       | [A]                    |

| 1              | Length                            | [m]                    |

| L              | TFT channel length                | [m]                    |

| r              | Bending radius of a wafer         | [m]                    |

| $r_0$          | Initial wafer bending radius      | [m]                    |

| R              | Electrical resistance             | $[\Omega]$             |

| t              | Thickness                         | [m]                    |

| $V_D$          | Drain voltage                     | [V]                    |

|                |                                   |                        |

| $V_G$            | Gate voltage                         | [V]                          |

|------------------|--------------------------------------|------------------------------|

| $V_T$            | Threshold voltage                    | [V]                          |

| w                | Width                                | [m]                          |

| W                | TFT channel width                    | [m]                          |

| $\epsilon$       | Strain                               | [-] or $[%]$                 |

| $\kappa$         | Wafer curvature                      | [1/m]                        |

| $\kappa_0$       | Initial wafer curvature              | [1/m]                        |

| $\mu$            | Apparent mobility                    | $[\mathrm{m}^2/\mathrm{Vs}]$ |

| $\mu_0$          | Initial apparent mobility            | $[\mathrm{m}^2/\mathrm{Vs}]$ |

| $\mu_R$          | Reference apparent mobility          | $[\mathrm{m}^2/\mathrm{Vs}]$ |

| $\mu/\mu_0$      | Relative apparent mobility           | [-] or $[%]$                 |

| $\mu_R/\mu_{R0}$ | Reference relative apparent mobility | [-] or $[%]$                 |

| ho               | Electrical resistivity               | $[\Omega \mathrm{m}]$        |

| $\sigma$         | Stress                               | [Pa]                         |

| $\#\mathrm{sq}$  | Number of squares                    | [-]                          |

|                  |                                      |                              |

### **Acronyms**

AFM Atomic force microscopy

Al Aluminum

Ar Argon

Au Gold

${\rm Cr}$   ${\rm Chromium}$   ${\rm CH_3COOH}$   ${\rm Acetic\ acid}$

CMOS Complementary metal-oxide-semiconductor

CVD Chemical vapor deposition

D Drain

DC Direct current

DIBL Drain-induced barrier lowering

e-beam Electron beam

FEM Finite element method FET Field-effect transistor FIB Focused ion beam

G Gate

Ge Germanium

H<sub>2</sub>O Water

H<sub>3</sub>PO<sub>4</sub> Phosphoric acid HF Hydrofluoric acid

HNO<sub>3</sub> Nitric acid

$I_2$  Iodine

KI Potassium iodideKOH Potassium hydroxideLCD Liquid crystal display

LPCVD Low-pressure chemical vapor deposition

LS-SiN Low-stress silicon nitride MIM Metal-insulator-metal

MOSFET Metal-oxide semiconductor field-effect transistor

N<sub>2</sub> Nitrogen

NMP N-methyl-2-pyrrolidone

O<sub>2</sub> Oxygen

PDMS Polydimethylsiloxane

PECVD Plasma enhanced chemical vapor deposition

PEN Polyethylene naphthalate PET Polyethylene terephthalate

PI Polyimide

Pt Platinum

S Source

S/D Source-drain

SEM Scanning electron microscopy

Si Silicon

$\begin{array}{ll} {\rm SiN} & {\rm Silicon~nitride} \\ {\rm SiO}_2 & {\rm Silicon~dioxide} \end{array}$

SOI Silicon-on-insulator

Ti Titanium

TFT Thin film transistor

UV Ultraviolet

# **Contents**

| 1 | Intr                    | oduction                                                | 1  |  |  |  |  |

|---|-------------------------|---------------------------------------------------------|----|--|--|--|--|

|   | 1.1                     | Motivation                                              | 1  |  |  |  |  |

|   | 1.2                     | Flexible Electronics                                    | 2  |  |  |  |  |

|   |                         | 1.2.1 Conducting Wires on Flexible Substrates           | 2  |  |  |  |  |

|   |                         | 1.2.2 Inorganic and Organic TFTs on Flexible Substrates | 3  |  |  |  |  |

|   |                         | 1.2.3 Applications of Flexible Electronics              | 6  |  |  |  |  |

|   | 1.3 Organic Electronics |                                                         |    |  |  |  |  |

|   |                         | 1.3.1 Organic TFT Design                                | 8  |  |  |  |  |

|   |                         | 1.3.2 Acenes-Based Organic Semiconductors               | 9  |  |  |  |  |

|   |                         | 1.3.3 TFT Applications with Organic Semiconductors      | 11 |  |  |  |  |

|   | 1.4                     | Stencil Lithography                                     | 13 |  |  |  |  |

|   | 1.5                     | Objectives                                              | 19 |  |  |  |  |

|   | 1.6                     | Thesis Outline                                          | 19 |  |  |  |  |

| 2 | Ste                     | ncil Design and Fabrication                             | 21 |  |  |  |  |

|   | 2.1                     | Stencil Fabrication Methods                             | 21 |  |  |  |  |

|   |                         | 2.1.1 Aperture Patterning                               | 22 |  |  |  |  |

|   |                         | 2.1.2 Membrane Release by Wet Etching                   | 23 |  |  |  |  |

|   |                         | 2.1.3 Membrane Release by Combined Dry and Wet Etching  | 24 |  |  |  |  |

|   | 2.2                     | Wafer Curvature Variations during Stencil Fabrication   | 24 |  |  |  |  |

|   | 2.3                     | Conclusion                                              | 28 |  |  |  |  |

| 3 | Met                     | al Wires on Polymer Substrates                          | 29 |  |  |  |  |

|   | 3.1                     | Stencil Design                                          | 29 |  |  |  |  |

|   | 3.2                     | Polymer Substrates                                      | 30 |  |  |  |  |

|   | 3.3 | Patter  | rning by Chip-Size Stencil Lithography                                    | 31 |

|---|-----|---------|---------------------------------------------------------------------------|----|

|   | 3.4 | Chara   | cterization                                                               | 33 |

|   |     | 3.4.1   | 2-Point Measurements                                                      | 34 |

|   |     | 3.4.2   | 4-Point Measurements                                                      | 35 |

|   |     | 3.4.3   | Ti-Au Thin Film                                                           | 36 |

|   | 3.5 | Concl   | usion                                                                     | 37 |

| 4 | Org | anic Pe | entacene Thin Film Transistors                                            | 39 |

|   | 4.1 | Electr  | ical Characterization of TFTs                                             | 39 |

|   | 4.2 | Penta   | cene TFTs with a PI or SiO <sub>2</sub> Dielectric and S/D Top Contacts   | 43 |

|   |     | 4.2.1   | Pentacene Top Contact TFT Fabrication                                     | 43 |

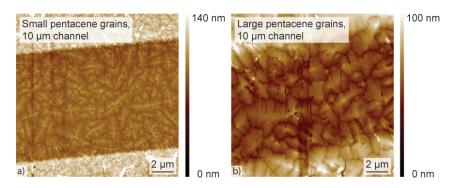

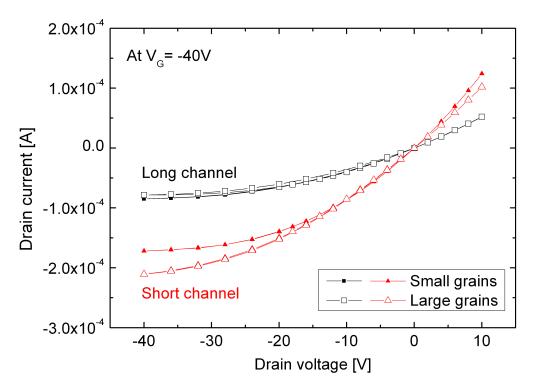

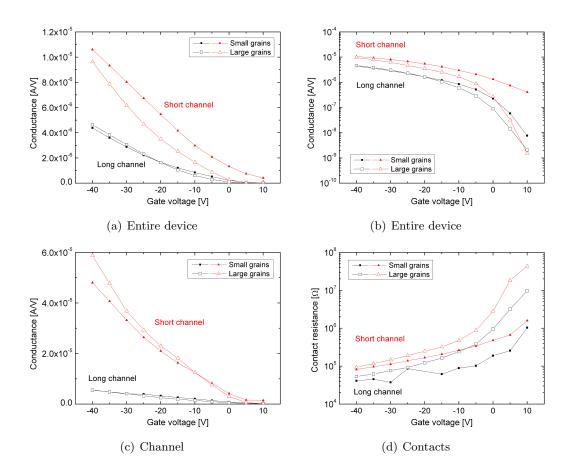

|   |     | 4.2.2   | $\operatorname{AFM}$ and Electrical Characterization of Pentacene TFTs $$ | 44 |

|   |     | 4.2.3   | Analysis of Pentacene Films on PI and $SiO_2$ Dielectrics                 | 51 |

|   | 4.3 | Penta   | cene TFTs on a Flexible Substrate                                         | 53 |

|   |     | 4.3.1   | Pentacene TFT Fabrication on Flexible PI Substrates                       | 53 |

|   |     | 4.3.2   | Electrical Pentacene TFT Characterization                                 | 55 |

|   |     | 4.3.3   | Discussion                                                                | 61 |

|   |     | 4.3.4   | Conclusion                                                                | 64 |

|   | 4.4 | Penta   | cene TFTs on a Flexible Substrate Exposed to Tensile Strain .             | 65 |

|   |     | 4.4.1   | Pentacene TFT Fabrication for Tensile Stress Experiments $$ .             | 65 |

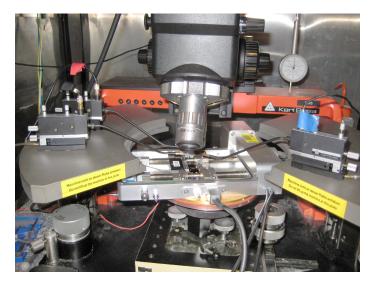

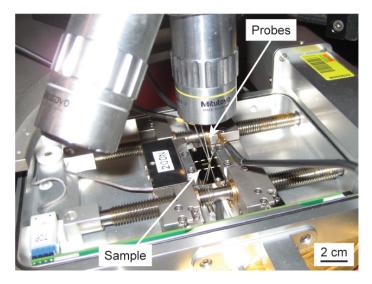

|   |     | 4.4.2   | Stretching Setup                                                          | 65 |

|   |     | 4.4.3   | Tensile and Electrical Characterization of Pentacene TFTs $$ .            | 68 |

|   |     | 4.4.4   | Discussion                                                                | 76 |

|   |     | 4.4.5   | Conclusion                                                                | 80 |

|   | 4.5 | Concl   | usion on Pentacene TFTs                                                   | 82 |

| 5 | Con | npliant | Stencil Lithography                                                       | 85 |

|   | 5.1 | Princi  | ple of Compliant Stencil Lithography                                      | 85 |

|   | 5.2 | FEM     | Simulation on the Displacement of a Compliant Membrane                    | 87 |

|   | 5.3 | Fabric  | eation Process                                                            | 89 |

|   | 5.4 | Setup   | for Compliant Stencil Lithography                                         | 90 |

|   | 5.5 | Chara   | cterization of the Resolution in Compliant Stencil Lithography            | 93 |

|    | 5.6          | Discussion                                | 96  |  |  |  |  |  |

|----|--------------|-------------------------------------------|-----|--|--|--|--|--|

|    | 5.7          | Conclusion                                | 99  |  |  |  |  |  |

| 6  | Sun          | nmary, Conclusion and Outlook             | 101 |  |  |  |  |  |

|    | 6.1          | Summary                                   | 101 |  |  |  |  |  |

|    | 6.2          | Conclusion                                | 103 |  |  |  |  |  |

|    | 6.3          | Outlook                                   | 104 |  |  |  |  |  |

| Α  | Maı          | nuscript Submitted to Organic Electronics | 109 |  |  |  |  |  |

| Bi | Bibliography |                                           |     |  |  |  |  |  |

# List of Figures

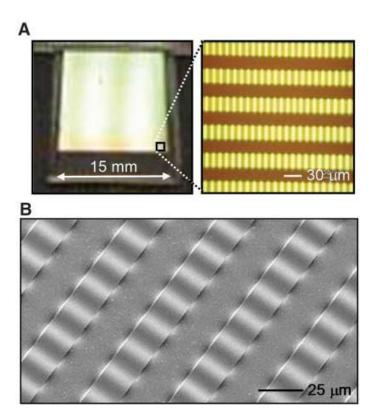

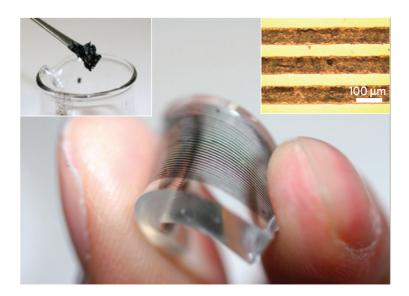

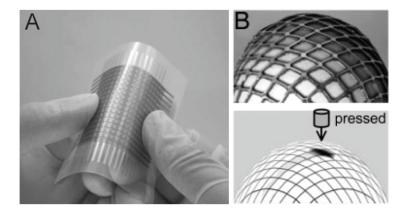

| 1.1  | Si ribbons on an elastomeric substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

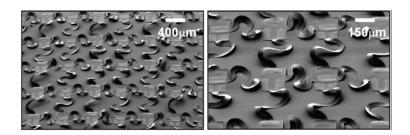

| 1.2  | Stretchable serpentine shaped bridges between CMOS inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5  |

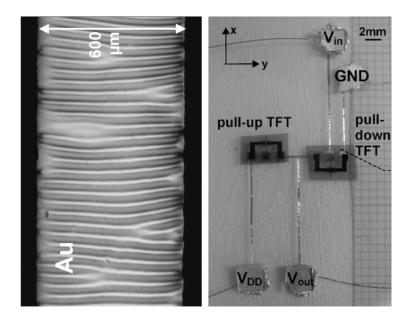

| 1.3  | Stretchable interconnects of an inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5  |

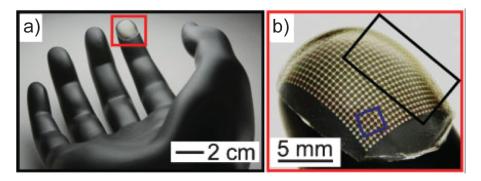

| 1.4  | Mesh circuit on a plastic substrate mounted onto the tip of a human                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | finger model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7  |

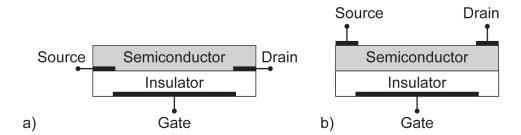

| 1.5  | Bottom contact and top contact configuration of an organic TFT $$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8  |

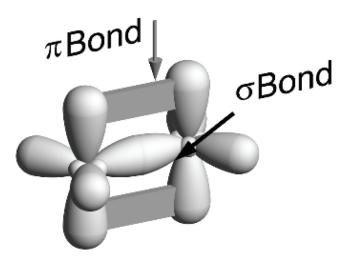

| 1.6  | Schematic orbital illustration of a double carbon bond $\ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9  |

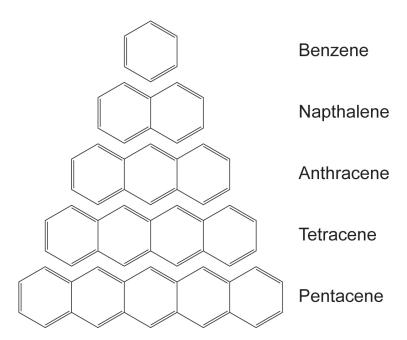

| 1.7  | Schematic illustration of acenes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

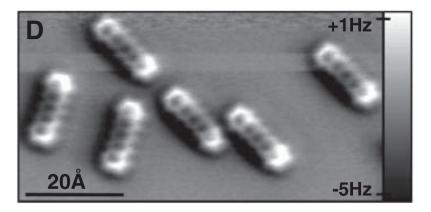

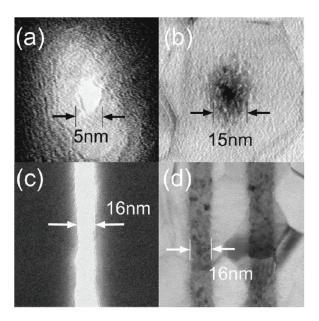

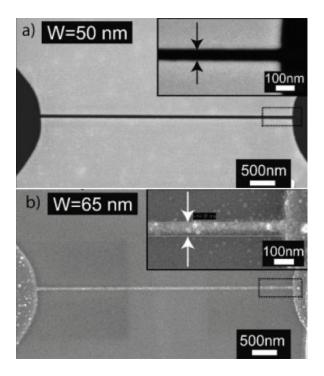

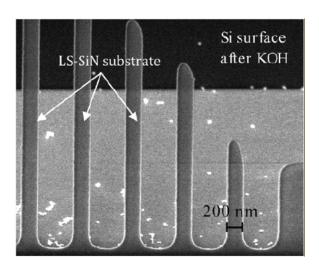

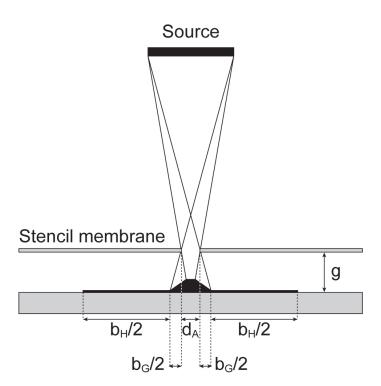

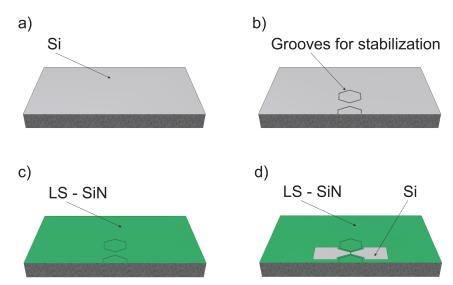

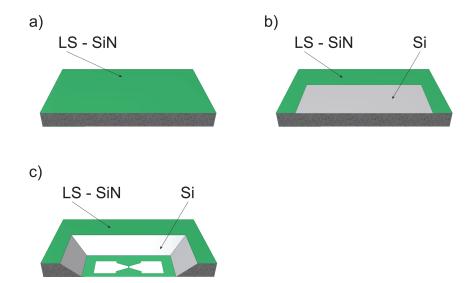

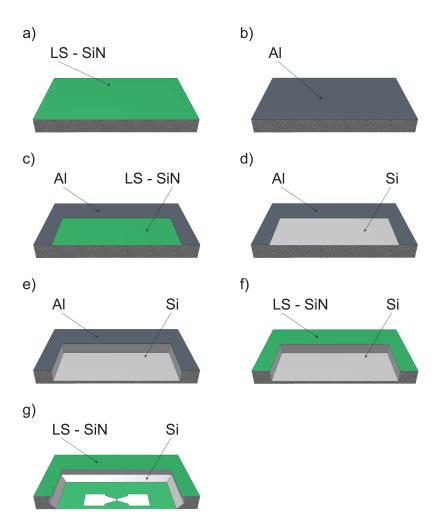

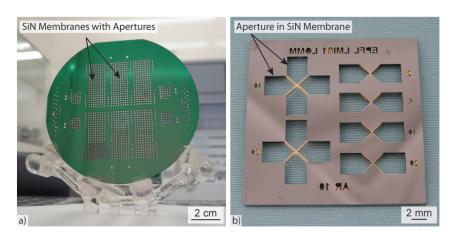

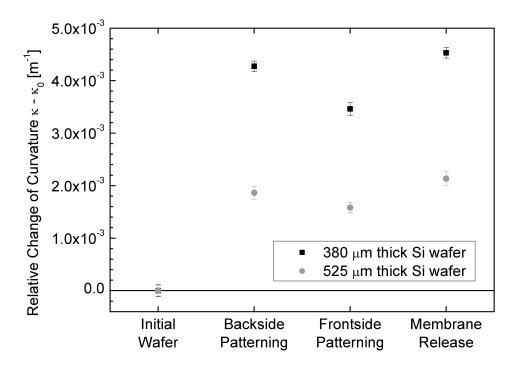

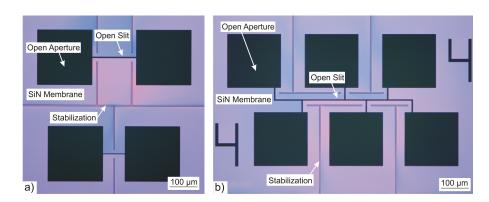

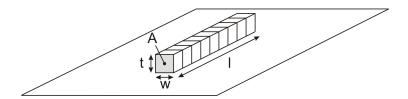

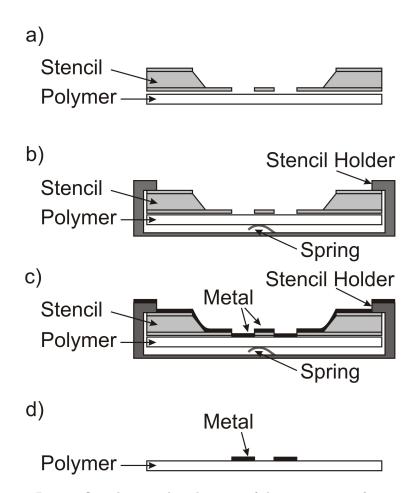

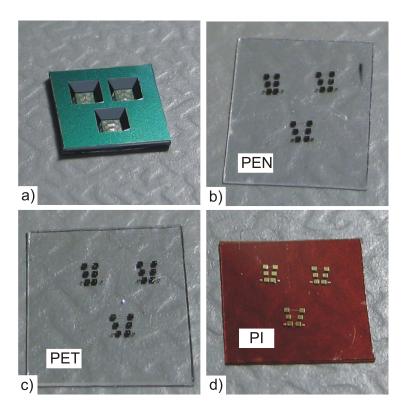

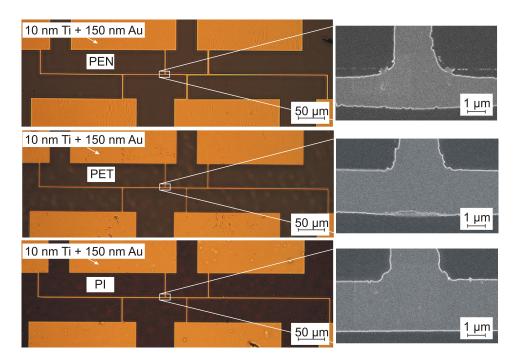

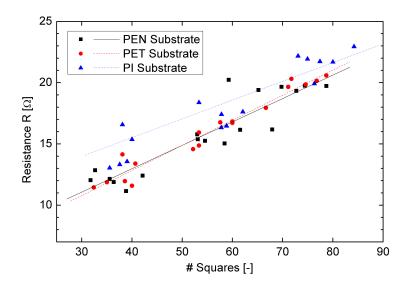

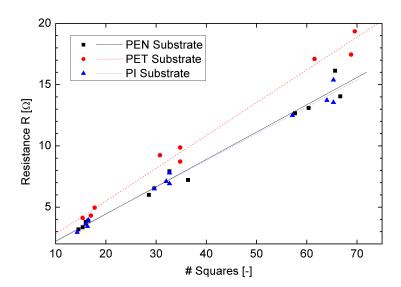

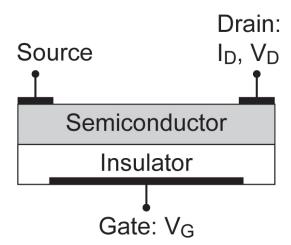

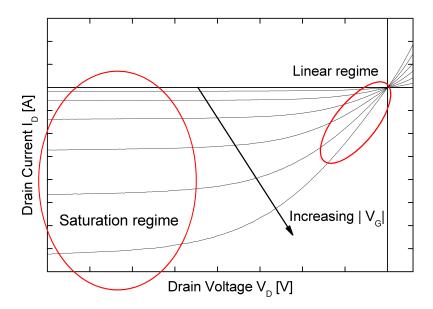

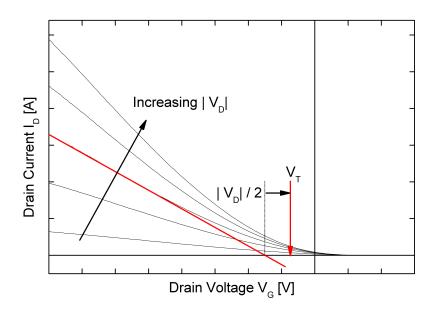

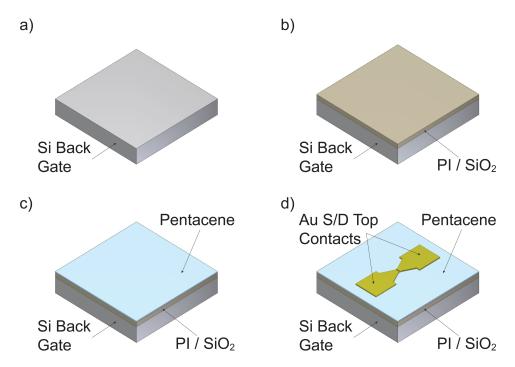

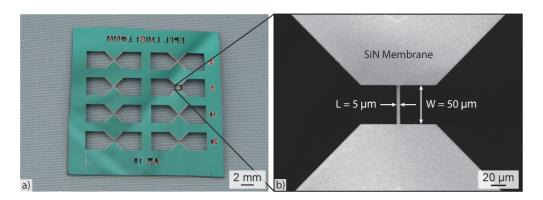

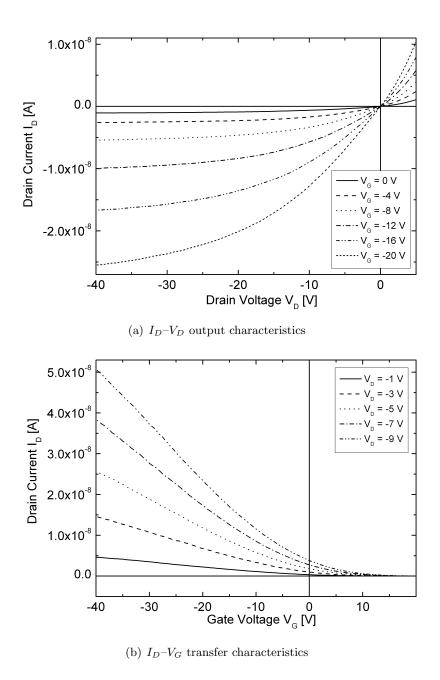

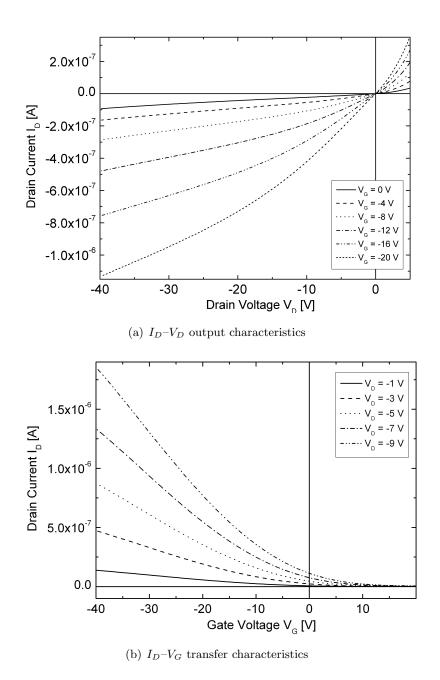

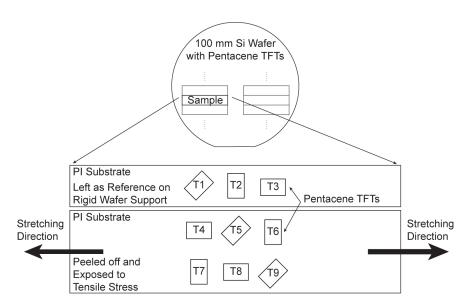

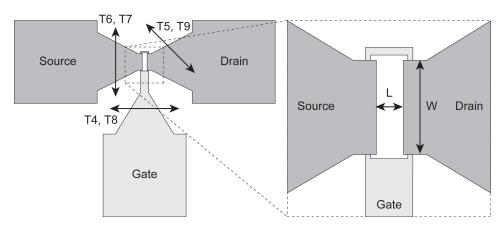

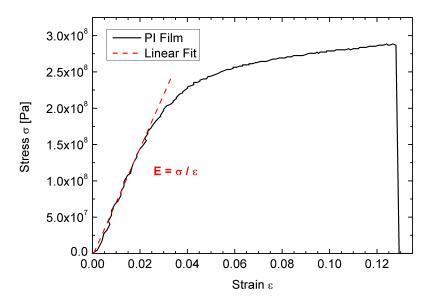

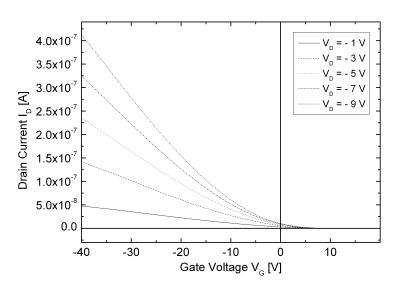

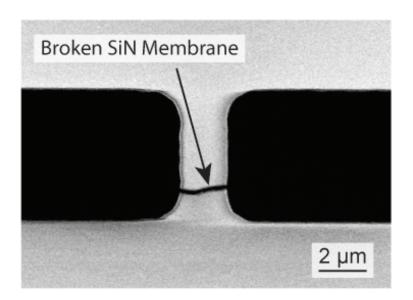

| 1.8  | Pentacene molecules imaged by AFM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11 |