## New Approach for SOI Pixel Sensor, Analysis and Implementation

THÈSE Nº 4440 (2009)

PRÉSENTÉE LE 2 OCTOBRE 2009 À LA FACULTÉ SCIENCES ET TECHNIQUES DE L'INGÉNIEUR INSTITUT DE GÉNIE ÉLECTRIQUE ET ÉLECTRONIQUE - GROUPE KAYAL PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Louis HARIK

acceptée sur proposition du jury:

Prof. M. A. Ionescu, président du jury Prof. M. Kayal, Dr J.-M. Sallèse, directeurs de thèse T. Baechler, rapporteur Prof. P. Fazan, rapporteur Prof. C. Lallement, rapporteur

# Acknowledgment

ERE I am at the finish line of a long term project, where I have come to interact with people from all around the globe. It is time to express my gratitude for all those with whom I have not only worked with but also have shared a part of my life for the past six years. I would like first of all to thank my thesis advisors Maher KAYAL and Jean-Michel SALLESE for their guidance that helped me to put back on track the project after inevitable derailings, things we encounter very often in any research work. I would like also to thank them for their trust in me as well as their support at many instances of the work.

I would like to thank the office mates with whom I have shared not only an office but also some thoughts (philosophical for many of them), jokes, comments, lunches, stress and difficult moments. I will go chronologically, Marija BLAGOJEVIC, Danica STEFANOVIC, Sergio PESENTI, Ira NAGEL and Laurent FABRE.

My thanks go also to Marija BLAGOJEVIC and Sergio PESENTI for their support during my very first year in the lab, where I have been working on independent projects with them. Their expertise helped me develop a better view in a field that was new to me.

In addition to the research work, we had assistantship work we share among the group. This too allowed interactions with the lab people. Under this category I would like to thank especially Danica STEFANOVIC and Ira NAGEL whose passion for education and perfection will always amaze me.

Also rememberable are the lunch breaks with Didier BOUVET and Patrice BEAUD and later on with Daniel GROGG, Dimitris TSAMADOS and Pierre-Yves PFIRTER especially when we tackled world wide financial and political issues. Nor shall I forget the discussions and the exchange of recipes with the italian group in the lab, especially with Donatello ACQUAVIVA and Giovanni SLAVATORE.

Without the little chit chat here and there and the moments of comics spent with the people around in the lab, the work environment would become unbearable. For these moments I would like to thank in the order of appearance during my typical day at the lab, Andrea AJBL, Cédric MEINEN, Laurent FABRE, Fabrizio LOCONTE, Diana CIRESSAN then at the coffee break at 9:30 sharp Adil KOUKAB, Marc PASTRE, Paulo DAL FABBRO, then comes after the coffee throughout the day Sylvain MARECHAL, Imre KOVACS, Raymond SUTTER, François KRUMME-NACHER, Nicolas PILLIN, Luca DE MICHIELIS, Livio LATTANZIO, Anupama ARUN, Matthieu BOPP, Nenad CVETKOVIC and Montserrat FER- NANDEZ. My special thanks go for the secretaries Marie HALM, Isabelle BUZZI and Karin BELLARDINELLI-BORCARD not only for the perfect administrative work they do, but also for the organization of the social events of the lab. Also to remember the discussions we have numerous times made at the early coffee break.

Special thanks goes to Roland JAQUES and Joseph GUZZARDI for the continuous technical support at any time of the day and sometimes from remote places!

I would like to thank my friend and associate Jari CURTY for his patience and understanding especially during the last phase of the thesis.

Last but not least I would like to thank my parents and brother for their love and the trust they have put in me and the help they provided me to nurture my curiosity all the way through.

To my mom Marie, my father Bahige and my brother François.

# وقل لمنديدّعري فري العلم فلسفةً حفظت شيئاً وغابت عنـك أشرياء أبوالنوّاس

iv

# Abstract

SILICON on Insulator (SOI) is an interesting alternative to bulk silicon for the fabrication of integrated circuits due to its advantages with respect to the junction leakage, low switching noise coupling, high temperature immunity, low voltage and low power applications. Recently, SOI transistors have also been used in high speed CPU's due to their high switching performances and their reduced power consumption. Another application where high performances and even higher densities are needed are dynamic memories (DRAM) where floating body SOI MOSFETS were used as an 1T memory node. Using the floating body as a charge storage reduces the unit cell size and drastically increases the bit density and the storage capacity.

However, despite technical advances in SOI technology, it has rarely been exploited in optical sensing and imagery. The main reasons are the expected low optical conversion efficiency due to the relatively thin silicon film thicknesses, well below 1  $\mu m$  and the slow time constants due to slow recombinations at the junctions. In addition, the slim active region reduces the optical bandwidth of such sensors as longer wavelengths are absorbed deeper (and in the case of SOI probably in the buried oxide layer).

Despite these major handicaps, it was shown recently that an SOI MOS-FET based phototransistor could detect light intensities as low as  $5mW/m^2$ . However, previous work addressed only low light intensities neglecting the slow transients drawbacks. Moreover, as for most fully and partially depleted SOI MOSFET's based photodetectors, it is the drain current variation due to light absorption that was used as a measure of photon densities (for instance the  $5mW/m^2$  generates 50 fA of photocurrent). Such variations are hard to measure with the needed resolution as such currents are close to the noise levels of any amplifier.

This research project proposes a new measurement technique that does not rely on direct quantification of the photocurrent and hence overcomes the problems inherent to noise and low current variations. In addition to that, this novel technique solves the problem of slow drain current recovery time inherent to the slow recombinations at the junctions.

This technique relies on the transient charge pumping used to remove continuously photogenerated charges from the electrically insulated body of the MOSFET. Then, since the transistor is always maintained in equilibrium conditions, this approach will get rid of any transient effect occuring in the partially depleted SOI MOSFET.

Also presented in this work is an extension of this technique to any float-

ing body MOSFET. We presented also measurement of bulk P-MOSFET whose n-well was left floating and showed that the behaviour was similar to that of a floating body SOI MOSFET. Still using the transient charge pumping to remove extra charge from the floating n-well.

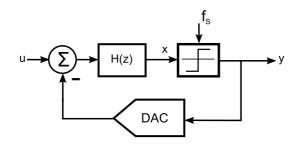

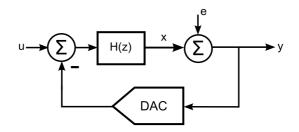

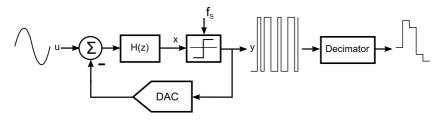

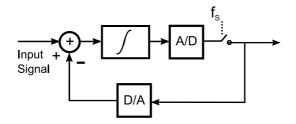

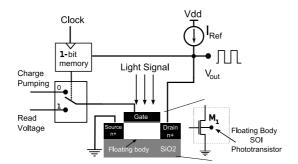

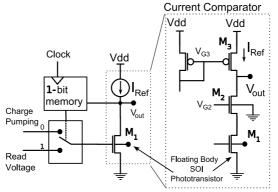

Finally, An SOI cicruit implementation of this technique was presented. This circuit takes advantage of some of the properties of the floating body SOI MOSFET to implement a first order delta sigma modulator at the pixel level without subtantially reducing the fill factor. The first order delta sigma modulator in each pixel, can improve the resolution and offer a direct digital output without the need of an ADC.

**Keywords:** Silicon on insulator (SOI), phototransistor, partially depleted, charge pumping, delta-sigma modulation, digital pixel sensor (DPS), active pixel sensor (APS), floating body, floating N-well, photogeneration, recombination, photon shot noise, charge pumping noise.

# Résumé

S ILICON on Insulator (SOI), littéralement "silicium sur isolant", représente une alternative à la technologie silicium classique dite "bulk" pour la fabrication de circuits intégrés. Les avantages du SOI se situent dans les faibles courants de fuites des jonctions, les bruits de découplage ainsi que l'immunité aux hautes température. La technologie SOI est davantage utilisée dans des applications faible tension et faible consomation et à haute fréquence, comme c'est le cas pour les unités centrale (CPU). Une autre application intéressante concerne les memoires vives appelées DRAM où l'on utilise le transistor à substrat flottant comme capacité de charge à la place d'un condensateur, ce qui permet d'atteindre des densités d'intégration plus élevées.

Malgrés les progrès technologiques de la SOI, on trouve très rarement des détecteurs optiques de haute performance. Les chercheurs sont decouragés non seulement par la faible efficacité optique, qui est essentiellement dûe à la faible épaisseur du film de silicium inférieur au  $1\mu m$ , mais aussi par des constantes de temps relativement longues qui sont dûes aux faibles taux de recombinaisons dans les jonctions source-body et drain-body. De plus, l'épaisseur du film de silicium réduit l'efficacité pour les plus longues longueur d'onde qui sont principalement absorbées dans l'oxide enterré.

Ces limitations techniques n'ont pas empêché l'avancement dans ce domaine. Un détecteur optique basé sur un phototransistor SOI a également pu détecter des faibles intensités lumineuses allant jusqu'à  $5mW/m^2$ . Cependant, la problématique de la constante de temps subsiste encore: le temps de réaction du dispositif reste inacceptable pour la plupart des applications. Toutes les solutions qui ont amélioré l'efficacité optique des phototransistors SOI, partiellement ou totalement déplétés, mesurent un photocourant (une variation du courant du drain) pour évaluer la densité de photons qui a été absorbée (une illumination de  $5mW/m^2$  génère un courant de 50 fA seulement). Cette faible variation de l'amplitude est difficilement mesurable par un circuit intégré car elle est proche du niveau du bruit d'entrée du circuit d'amplification.

Dans ce contexte, ce projet de recherche propose une nouvelle technique de mesure qui ne repose pas sur la quantification exacte de la variation du courant de drain (le photocourant) mais plutôt sur le maintient d'une valeur fixe de celui-ci.

Cette technique de mesure utilise le "transient charge pumping" pour recombiner continuellement les charges photogénerées dans le "body" flottant du MOSFET. Comme le transistor est constamment maintenu dans un état d'équilibre, cette approche s'affranchit des effets transitoires qui ont lieu dans un MOSFET SOI partiellement déplété. Ainsi, cette solution s'affranchit des problèmes dûs aux bruits de circuit d'amplification ainsi que de la constante de temps qui sont des facteurs limitatifs.

Egalement, cette approche peut être étendue à tous les types de MOS-FETs dont le substrat est flottant. Des mesures réalisées sur un PMOS-FET de type bulk dont le caisson N est laissé flottant révèle un comportement identique à celui du MOSFET SOI avec "body" flottant. En effet, il a été démontré que la technique du "transient charge pumping" est également applicable à un tel dispositif pour recombiner les charges en excès existant dans le caisson.

Finallement, l'implementation d'un circuit utilisant la technologie SOI a été présentée. Ce circuit utilise les propriétés du transistor SOI à "body" flottant et implémente un modulateur delta sigma du premier ordre au niveau du pixel, occupant une surface negligeable par rapport à celle du phototransistor. Avec un modulateur delta sigma dans chaque pixel, la résolution du signal à la sortie a été accrue. De plus un modulateur delta sigma présente une sortie qui, par nature, est numérique, ce qui évite d'avoir à réaliser un convertiseur analogique numérique à la sortie du système.

Ainsi, à travers ce travail de thèse, nous avons pu démontrer que la technologie SOI associé à une technique de mesures innovante devenait une alternative intérressante à la technologie CMOS-bluk pour les capteurs optiques.

**Mots-clés:** Silicon on insulator (SOI), phototransistor, partiellement déplété, charge pumping, modulation delta-sigma, digital pixel sensor (DPS), active pixel sensor (APS), body flottant, N-well flottant, photogeneration, recombinaison, photon shot noise, bruit de "charge pumping".

# Contents

| C        | onter | nts     |                                                                                                | ix |

|----------|-------|---------|------------------------------------------------------------------------------------------------|----|

| 1        | Intr  | oducti  | ion                                                                                            | 1  |

|          | 1.1   | Silicor | n on Insulator                                                                                 | 1  |

|          |       | 1.1.1   | The Bulk MOS                                                                                   | 3  |

|          |       | 1.1.2   | The SOI MOS                                                                                    | 6  |

|          |       | 1.1.3   | Body Tied SOI MOSFET                                                                           | 9  |

|          |       | 1.1.4   | Floating Body MOS                                                                              | 13 |

|          | 1.2   | Photo   | sensors                                                                                        | 16 |

|          |       | 1.2.1   | Photodiodes the State of the Art                                                               | 17 |

|          |       | 1.2.2   | Phototransistors: the State of the Art                                                         | 23 |

|          |       | 1.2.3   | Techniques                                                                                     | 26 |

|          | 1.3   | SOI P   | hotosensors                                                                                    | 27 |

|          |       | 1.3.1   | State of the Art                                                                               | 27 |

|          |       | 1.3.2   | Our Phototransistor                                                                            | 28 |

|          | 1.4   | Concl   | usion                                                                                          | 30 |

| <b>2</b> | Dev   | vice Pr | inciples                                                                                       | 31 |

|          | 2.1   | Introd  | luction                                                                                        | 31 |

|          | 2.2   | The E   | ffect of Light on a Partially Depleted Floating Body                                           |    |

|          |       | SOI M   | IOSFET                                                                                         | 32 |

|          |       | 2.2.1   | The Effect of Light on Electrical Characteristics $% \left( {{{\bf{F}}_{{\rm{E}}}}} \right)$ . | 33 |

|          |       | 2.2.2   | Impact of the Gate Voltage on Charge Separation                                                | 34 |

|          | 2.3   | Charg   | e Pumping                                                                                      | 39 |

|          | 2.4   | Stand   | ard Charge Pumping in Bulk MOS                                                                 | 39 |

|          | 2.5   | Transi  | ient Charge Pumping in Floating Body SOI MOSFET                                                | 41 |

|          | 2.6   |         | Transient Charge Pumping as a New Light Sensing       ique         ique                        | 46 |

|          |       |         | T                                                                                              |    |

|   |      | 2.6.1  | Transient Charge Pumping and Optical IntensityMeasurement46                                                           |

|---|------|--------|-----------------------------------------------------------------------------------------------------------------------|

|   |      | 2.6.2  | Calibration of the CP                                                                                                 |

|   |      | 2.6.3  | Optical Intensity Measurement                                                                                         |

|   | 2.7  | The E  | Effect of Light on a Photo-MOSFET                                                                                     |

|   |      | 2.7.1  | Principle                                                                                                             |

|   |      | 2.7.2  | Light Measurement Technique                                                                                           |

|   |      | 2.7.3  | Measurements Results                                                                                                  |

|   | 2.8  | Discus | ssion $\ldots \ldots 56$                 |

|   | 2.9  | Concl  | usion                                                                                                                 |

| 3 | Circ | cuit P | rinciples 61                                                                                                          |

|   | 3.1  | Introd | luction $\ldots \ldots 61$ |

|   | 3.2  | Delta  | Sigma Theory 62                                                                                                       |

|   |      | 3.2.1  | In General                                                                                                            |

|   |      | 3.2.2  | First Order Delta Sigma                                                                                               |

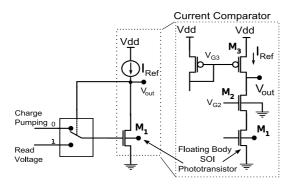

|   | 3.3  | Prope  | sed Circuits                                                                                                          |

|   |      | 3.3.1  | Model and Simulations                                                                                                 |

|   |      | 3.3.2  | Synchronous Pixel                                                                                                     |

|   |      | 3.3.3  | Asynchronous Pixel                                                                                                    |

|   |      | 3.3.4  | Current Comparator Transistor Sizing 75                                                                               |

|   | 3.4  | Circui | it Measurements $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 77$                                   |

|   |      | 3.4.1  | Principles                                                                                                            |

|   |      | 3.4.2  | Performances                                                                                                          |

|   |      | 3.4.3  | Comparison Sync-Async                                                                                                 |

|   |      | 3.4.4  | Discussion                                                                                                            |

|   | 3.5  | Impro  | vements and Outlook                                                                                                   |

|   |      | 3.5.1  | Leakage                                                                                                               |

|   |      | 3.5.2  | Optical Efficiency                                                                                                    |

|   | 3.6  | Matri  | x                                                                                                                     |

|   |      | 3.6.1  | Reading Algorithm                                                                                                     |

|   |      | 3.6.2  | The Reference Current Source                                                                                          |

|   |      | 3.6.3  | Voltage Sense Amplifier                                                                                               |

|   | 3.7  | Concl  | usion                                                                                                                 |

| 4  | Noi            | se Sou  | rces                                                                                     | 99  |

|----|----------------|---------|------------------------------------------------------------------------------------------|-----|

|    | 4.1            | Introd  | uction                                                                                   | 99  |

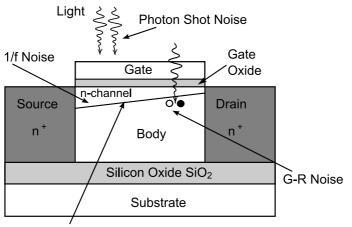

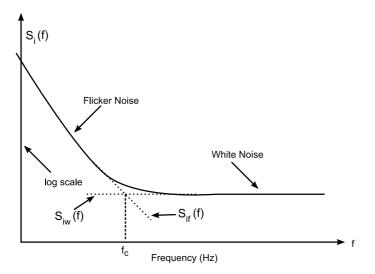

|    | 4.2            | All the | e Noise Sources                                                                          | 99  |

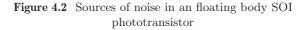

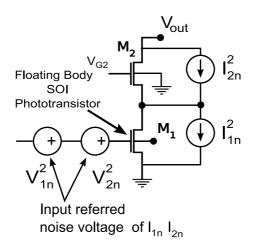

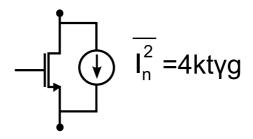

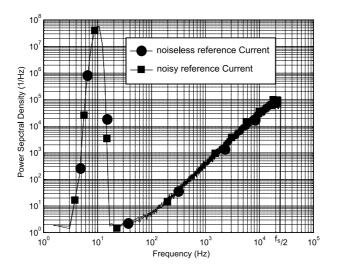

|    |                | 4.2.1   | White and Flicker Noise of the Reference Current                                         | 100 |

|    |                | 4.2.2   | Cascode Noises                                                                           | 102 |

|    |                | 4.2.3   | Flicker Noise                                                                            | 103 |

|    |                | 4.2.4   | White Noise                                                                              | 104 |

|    |                | 4.2.5   | Charge Pumping Noise                                                                     | 105 |

|    |                | 4.2.6   | Photon Shot Noise                                                                        | 106 |

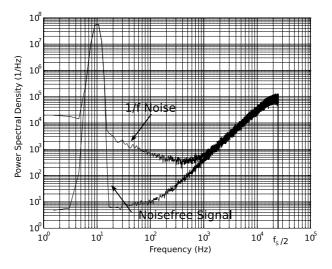

|    | 4.3            | Noise   | Simulations                                                                              | 106 |

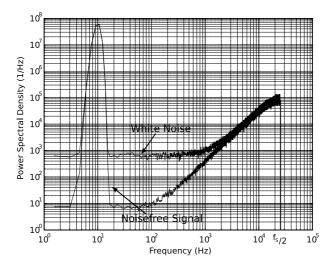

|    |                | 4.3.1   | Current Reference Noise Soures Simulation Results                                        | 106 |

|    |                | 4.3.2   | Phototransistor Flicker Noise Simulation Results .                                       | 107 |

|    |                | 4.3.3   | $\label{eq:phototransistor} \mbox{ Phototransistor White Noise Simulation Results } \ .$ | 107 |

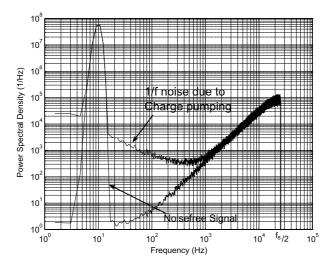

|    |                | 4.3.4   | Charge Pumping Noise Simulation Results $\ \ . \ . \ .$                                  | 108 |

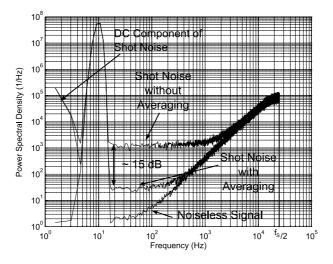

|    |                | 4.3.5   | Photon Shot Noise Simulation Results $\ . \ . \ .$ .                                     | 108 |

|    | 4.4            | Discus  | sion                                                                                     | 110 |

|    |                | 4.4.1   | Noises Filtered by the Delta Sigma Modulator $~$                                         | 110 |

|    |                | 4.4.2   | Unfiltered Noises $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 111 |

|    | 4.5            | Conclu  | usion                                                                                    | 111 |

| 5  | Con            | clusio  | n                                                                                        | 113 |

|    | 5.1            | Thesis  | Outlook                                                                                  | 113 |

|    | 5.2            | Main (  | Contributions                                                                            | 114 |

|    | 5.3            | Future  | Work                                                                                     | 114 |

| A  | App            | oendix  |                                                                                          | 117 |

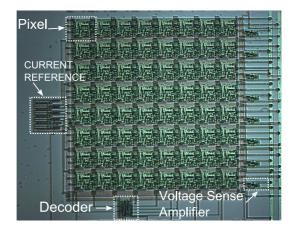

|    | A.1            | Matrix  | c Layout                                                                                 | 117 |

| Bi | bliog          | graphy  |                                                                                          | 119 |

| In | $\mathbf{dex}$ |         |                                                                                          | 133 |

#### CHAPTER 1

# Introduction

### 1.1 Silicon on Insulator

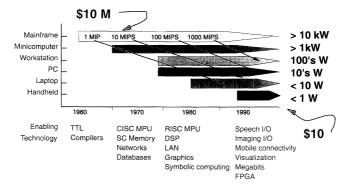

SILICON On Insulator CMOS is becoming a major player in existing VLSI systems. Designers are attracted to this technology because of its suitability for low power applications using low supply voltage. Along with the progress in CMOS processing technology, the CMOS device has been scaled down serving two purposes, low voltage supply and higher densities. Allowing to achieve a computing power similar to that achievable 25 years ago with 10,000 times less power consumed. (figure 1.1 adapted from [44]). This trend is continuing according to Semiconductor Industries Association (SIA) leading to smaller and smaller geometries for the transistor and forcing circuit designer to design with lower voltages.

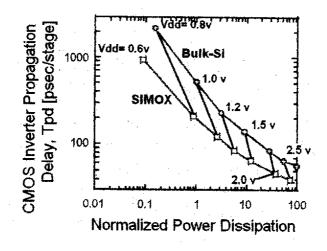

Owing to the oxide layer underneath the structure, SOI devices have lower current leakage, less parasitic capacitances which results in higher speed performance of the SOI CMOS compared to the bulk counterpart. Figure 1.2 (adapted from [2]) shows a comparison between an SOI and a bulk CMOS inverter using a 0.35  $\mu$ m transistors. As we lower the supply voltage the power dissipated in the inverter drops in both cases as well as the delay performances; however, the SOI CMOS is less affected by the scale down of the voltage, implying that SOI technologies are better suited for low voltage circuits.

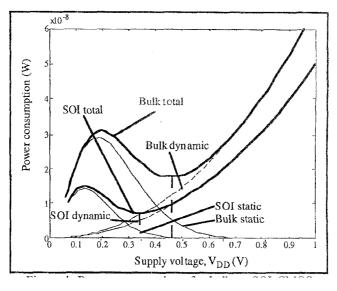

Generally, SOI CMOS outperforms the bulk CMOS by about 25% in speed performance at a reduced power consumption. Along with the improved speed performance, circuit designers would like to keep power consumption down too. Figure 1.3 (adapted from [10]) shows that the

Figure 1.1 Trend on Power Consumptions during the past 40 years

Figure 1.2 Propagation delay versus normalized power consumption

Figure 1.3 Power consumption versus supply voltage

SOI CMOS has a lower static power consumption as well as a lower dynamic power consumption and the latter is because of the smaller parasitic capacitances of the SOI CMOS. All of these factors show that for the future trends SOI technology is a good candidate to replace the bulk especially that the SOI CMOS technology is similar to the bulk CMOS counterpart except for the starting silicon wafer. There are essentially two major of techniques: Separation by Implantation of Oxygen (SIMOX) and the wafer bonding methods.

### 1.1.1 The Bulk MOS

#### **Basic Structure**

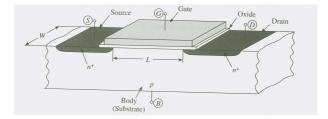

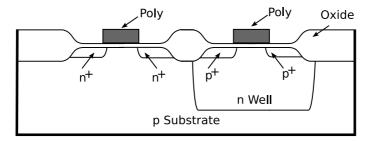

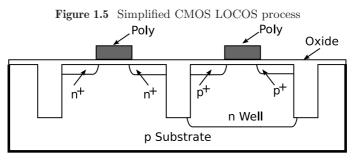

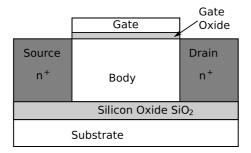

The basic idea of the MOS transistor dates back to the early 1930's with the patent of J.E. Lilienfeld. However, the MOS did not become popular until the early sixties when techniques of reliably growing oxide were developed and the basic theories of operation were established. The simplified structure of an n-channel MOS transistor is shown in Figure 1.4. The transistor is formed on a p-type silicon called the body or substrate which is lightly doped typical concentrations range between  $10^{16}$  and  $10^{18}cm^{-3}$ . At the center of the structure a thin layer of silicon dioxide (sometimes simply called oxide) is grown with thicknesses varying from 1 to 10 nm. On top of this oxide a low resistivity electrode called the gate is added. Usually the gate is made by a polycrystalline silicon also

Figure 1.4 Simplified structure of an n-channel MOS transistor

called polysilicon or simply poly. The two  $n^+$  regions on the sides of the gate are what we call drain and source of the transistor. The gate is acting as a mask against the implant that dope the drain and source region, which makes a self aligned doping to the gate. The depth of these regions are between 0.04  $\mu$ m and 0.2  $\mu$ m. Due to the heavy doping of these regions some diffusion takes place and we can see some diffuses laterally under the gate. The region between the drain and the source is called the channel and is characterized by W and L which are the width and length respectively. These values varies largely from transistor to another depending on circuit design needs. Often the n-channel and p-channel MOSFET transistors are called nMOS and pMOS transistors respectively. Using CMOS (complementary MOS) technology both nMOS and pMOS can coexist on the same chip, this is possible thanks to a technique called LOCOS (Local oxidation of silicon). With this a gradual increase of the silicon dioxide thickness is possible, resulting in the so-called "bird's beak" shape as shown in figure 1.5. The thick layer of oxide is used to prevent the accidental formation of a parasitic channel underneath it in case a metal line was passing above it. In addition to this heavily doped "channel stops" are made under this thick oxide. As we can see in figure 1.5 all the nMOS transistors will share the same p substrate, the pn junction formed by the source and the drain on one side and the p substrate on the other side is kept in reverse bias mode by connecting the p substrate to the lowest potential in the circuit. The pMos transistors are formed in a separate n-well as shown in figure 1.5. This n-well is connected to the highest potential in the circuit to keep the pn junction formed by the n-well and the p substrate in reverse bias. An oxide layer called passivation layer is put on top of all the devices to protect them from their environment. In figure 1.6 we see a technique which is becoming prevalent to isolate nMOS from pMOS transistor and is called the *shallow-trenchisolation*(STI). A "'trench" filled with oxide separates devices from one another without compromising performance. The advantage of this technique is that the devices can be packed closer

$\begin{array}{c} \mbox{Figure 1.6} & \mbox{Simplified CMOS shallow-trench isolation} \\ & \mbox{process} \end{array}$

together without causing any latch up problem.

### Qualitative description of operation

In this section and for the sake of example we will take the n-channel shown in figure 1.4. If sufficiently high positive voltage is applied at the gate, the holes are repelled from the surface and electrons are attracted to the surface. These electrons can easily enter either or both of the  $n^+$ . This situation is called *inversion* as the p-type, which is naturally abundant with holes, has now more electrons. Now when a potential  $V_{ds}$ is applied across the channel, the electrons will be accelerated as they enter from the source and they leave through the drain. This corresponds to a current flowing from the drain toward the source. In the next subsection we will show how this current behaves as a function of the gate and the drain voltages.

#### **MOS** transistor characteristics

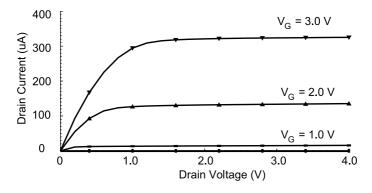

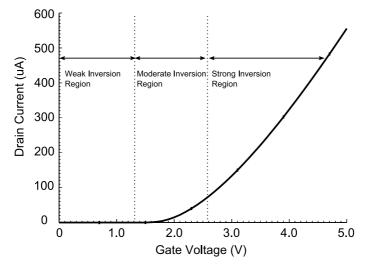

Let's take a look at the main characteristics of a MOS transistor. This is summarized by figure 1.7 where the drain current is plotted versus  $V_{ds}$  with  $V_{qs}$  as a parameter and in figure 1.8 where the drain current

Figure 1.7  $I_D$ - $V_{DS}$  characteristics with  $V_{GS}$  as parameter for a specific device

is plotted versus  $V_{gs}$ . The inversion of the channel can be seen in figure 1.8 where the different inversions have been marked in terms of  $V_{gs}$ . The weak inversion region can be seen in the graph for gate voltages much lower than the threshold voltage  $V_{th}$ . This mode of operation is becoming more and more attractive as circuit designer are more confronted with Low power and low voltage applications. In this mode of operation the current is mainly due to diffusion of carriers, while in the strong inversion case the drift of carriers is the major contributor to the current. The moderate inversion is a mixture of both where both drift and diffusion of carriers contribute to the current.

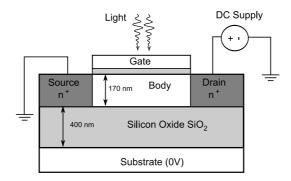

#### 1.1.2 The SOI MOS

As stated in section 1.1.1, it was said that the MOS was originally invented in the early 1930's. The patent filed of Lilienfield stated that a piece of semiconductor which constituted the active part of the device was a thin film deposited on an insulator. Some consider this MOSFET as Semiconductor on insulator device (SOI) and thus SOI dates back to the first MOSFET ever built. Figure 1.9 depicts a simplified view of an SOI MOSFET.

The fabrication process of SOI CMOS is similar to that of the bulk CMOS, except at the wafer fabrication stage, where the silicon oxide layer has to be incorporated to the wafer. We can differentiate two main methods of wafer fabrication: the Separation by Implantation of Oxygen (SIMOX) and Wafer-Bonding.

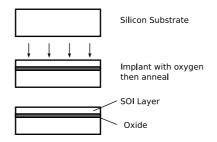

The Separation by Implantation of Oxygen (SIMOX) is the process that creates SOI through implantation, most of which use the oxygen implantation. This implantation takes place before the CMOS processing.

Figure 1.8  $I_D$ - $V_{GS}$  characteristics

Figure 1.9 Simplified view of an SOI MOSFET

Figure 1.10 Preparation of SOI using SIMOX process

High energy oxygen is sent deep below the silicon wafer surface, the doses used are about 200 times higher than those used for ion implantation doping. The second step is annealing which takes place at 1300C for 6 hours. During this stage the silicon dioxide is formed and recrystalization of the damaged epitaxial layer due to high energy implantation takes place. Typical thicknesses of the oxide layer ranges from 50 to 500 nm with a uniformity of  $\pm 2.5$ nm. The thickness of the silicon film above this dioxide layer is 40 to 70 nm for a fully depleted material and 100 to 200 nm for the partially depleted material. Figure 1.10 shows an SOI wafer made using the SIMOX process.

Wafer-bonding methods for preparing SOI wafers have basically the same process sequence. The active wafer is bonded to a handle wafer. In most of the cases both are oxidized, this is followed by an annealing to strengthen the bonds between the two wafers. Finally comes the thinning process which ranges from grinding to chemical etching going through plasma assisted chemical etching, selective etch and implantenhanced wafer splitting.

#### Physical Thinning and etch back

This is the most mature process for SOI wafer bonding, however this is the least economical in terms of raw material. As for most wafer bonding processes, 2 wafers one called the active and the second the handle, are bonded after oxidizing both of them. The active side which is used for the circuitry, is ground and thinned down to the desired thickness. However the uniformity is rather poor making it only useful for thick Silicon films. Figure 1.11

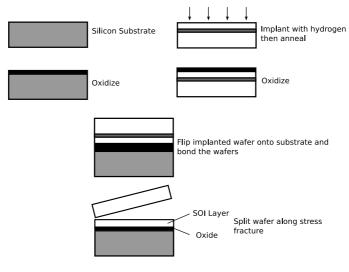

#### Smart Cut

Smart Cut was developed by SOITEC as a variant of the bonding technique. However with this method the active wafer is implanted with hydrogen protons at the depth of  $1\mu m$ . When annealed this creates a stress fracture. Afterward the active and handle wafer are bonded and the active wafer is split along the stress fracture. The unused portion of the active wafer can be reused, resulting in reduced costs over the

Figure 1.11 Etch-back process for creating SOI material

ground back described before. Figure 1.12

#### 1.1.3 Body Tied SOI MOSFET

The body of an SOI MOS as opposed to the bulk MOS is deposited on a thicklayer of  $SiO_2$  called the BOX which effectively isolates the body of the MOS from the substrate and hence two configurations are possible: Either the body is left unconnected to any potential and the transistor is called floating body transistor or the body has a contact which can be connected to a known potential, which is called body tied. In this section we will examine the partially depleted MOS with the body tied to a known potential through a contact. We will also see the different body ties currently used.

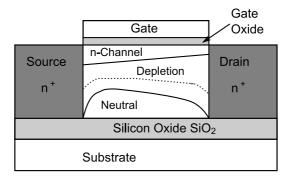

#### Partially Depleted

An SOI MOS is said to be partially depleted when there is a neutral region below the gate, the thickness of the silicon film is larger than the depletion region, as shown in figure 1.13. For thicknesses smaller than the depletion the transistor is said to be fully depleted which we will discuss in the next sections. The behavior of partially depleted MOS is very similar to their bulk counter part, the neutral zone in SOI also called body corresponds to the local well in bulk. The differences are more important when the body is left floating, whose different effect will be discussed in section 1.1.4. These effects are undesirable especially for analog circuits. Adding a body contact to a partially depleted SOI

Figure 1.12 SOI wafer produced using the SmartCut®process

MOSFET eliminates these undesirable effects and makes it behave like a bulk MOSFET.

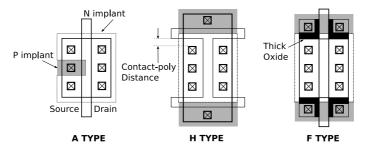

**Type A.** This type of contact is made up by a P implant in the active area of the source, this creates an ohmic contact with the channel of the transistor. It is necessary to have a metallic line connecting the N diffusion to the P hence the body potential is forcefully the same as that of the source. It is not noting that such topology is not adapted to the design of pass gates or analog switches because the MOSFET structure

Figure 1.13 Neutral, depletion and the channel regions in a partially depleted SOI MOSFET

Figure 1.14 Different layouts of body contacts

loses its symmetry (Figure 1.14). If the body is connected to the source then for the case of nMOS, the switch would be on even if the control voltage is low at the gate and the input voltage is high at the source. This is because the body-drain junction is forward biased.

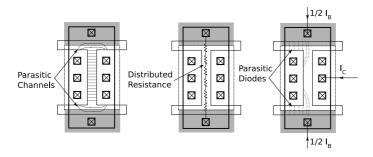

**Type H.** This contact, unlike type A, does not break the symmetry of the MOS. However, due to layout rules for the minimum distances between polysilicon and contact, minimum widths cannot be achieved. Yet small widths can be achieved with this type of contact. The effective width of the channel is better controlled than in the case of the A contact. Few parasitic elements are due to this contact like the parasitic channel and diodes shown in figure 1.15; furthermore, the efficiency of the contact is reduced due to the distributed resistance created between the substrate contact. This was circumvented by setting a maximum W/L ratio to 6. Throughout this thesis work the H type of contact was used for all analog circuits as it has the best control over the potential in the body of the transistor. In addition to that, the foundry had the most suitable model for this type of contacts (Figure 1.14).

**Type F.** This type of contact uses the thick oxide normally used for high voltage MOS. This oxide is most of time doped in  $P^+$  to reduce the resistivity of the contact. This type does not suffer from parasitic channel (as the oxide of the gate gets thicker in the contact regions). However, their main disadvantage is their rather high leakage current at the reverse biased drain-body junction (Figure 1.14).

The phototransistors used in the proposed pixels are called floating body SOI MOSFETs, this is because their body is floating, in addition to this, those MOSFETs had no contacts at all. Whereas, the digital gates used were taken from the digital library provided by the foundry where the transistors have a body contact of type A.

The Partially depleted SOI MOSFET behaves like a bulk MOSFET when its body contact is connected to ground, if this contact was left electri-

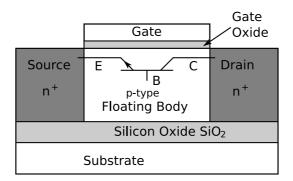

Figure 1.15 Parasitic elements of the H type contact

Figure 1.16 The parasitic bipolar device of PD-nMOS

cally floating then the partially depleted SOI MOSFET would still behave like a bulk MOSFET with the exception of two parasitic effects [11]: one called the Kink effect which we will detail in section 1.1.4 and the second is the presence of a parasitic open-base NPN bipolar transistor as shown in figure 1.16. The base is left open however, capacitive switching as well as leakage effects will combine to increase the body voltage and turn on the MOSFET. A typical example is that of a transmission gate where for instance the source and the drain were at a high potential so will the body drift to that potential too. Now suppose that the gate was low then the n-MOSFET should be off; however, when the source goes low the base-emitter diode will be forward biased therefore turning on the NPN transistor and causing a current to flow from the drain to the source. This can take few picoseconds to few milliseconds, until all carriers are swept from base region. This behavior can seriously impact the performance of both digital and analog circuits hence the need to use of body contact to connect the body to a fixed know potential.

#### 1.1.4 Floating Body MOS

We have seen in the previous section the effect of the different types of body contact on the behavior of the partially depleted SOI MOSFET and the importance of tying the body to a know potential for the use of the transistor in analog and digital circuits. In this section we will see the effects of leaving this body floating electrically for both the partially and fully depleted SOI MOSFETs.

#### Partially Depleted

#### Kink Effect

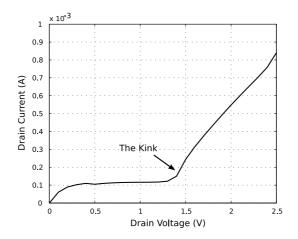

The effect of impact ionization in a floating body SOI MOSFET is much more important than that of bulk CMOS device [18]. In the case of a partially depleted because there is a neutral zone in the body and the potential barrier at the source body junction is high, holes generated by the impact ionization are not evacuated from the body. For the case of an nMOS this increases the body potential, thus decreases the threshold voltage. As a consequence the drain current shoots up; however, this phenomenon is not unbound, as the body potential increases the potential barrier at the source body junction decrease and holes created by the impact ionization flow from body to source, allowing the body potential to reach a steady state. The impact ionization takes place when the lateral field in the channel created by the potential  $V_{ds}$  is large enough and normally this takes place near the drain junction when the transistor is in the saturation region. Figure 1.17 shows an example of the kink effect on a floating body SOI MOSFET. The kink effect is reinforced by the parasitic NPN bipolar transistor shown in figure 1.16. This kink effect is mainly visible for nMOS; however, pMOS are usually free of kink effect. This behavior is suppressed as the frequency increases [37], implying that it could be beneficial when designing RF circuits for SOI applications [47]. However, other suggested the use of source to body connection to minimize the effect of the parasitic bipolar transistor. However, for many analog circuits like operational amplifiers and analogto-digital converters and many others the kink effect should be suppressed. In addition to this, it is a phenomenon that cannot be easily modeled and implemented in circuit simulators [52]. Numerous methods are used to suppress this undesirable behavior. This can be done either by process optimization by minimizing the gain of the parasitic

bipolar transistor or by body ties. The different body ties that were discussed in section 1.1.3 could apply. However, we have to keep in mind that those body ties are not perfect and that they exhibit parasitic resis-

Figure 1.17 The kink effect in 100/1 PD-nMOS

tances, many found ries set a maximum  $\rm W/L$  ratio to keep the parasitic resistance to minimum.

#### Light Effect

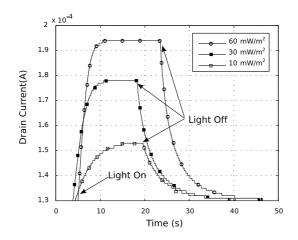

When Biased appropriately (in order not to cause any kink), a floating body SOI MOSFET exposed to light will increase its drain current by decreasing the threshold voltage due to accumulation of some photogenerated majority carriers inside the floating body this behavior was shown by [60]. When a floating body SOI MOSFET is actually illuminated by light some of the photons generate electron-hole pairs inside the body. These pairs get separated by the electric field in the depletion layer and at the source and drain junction, the electrons are evacuated through the channel while the holes will accumulate in the body (as it is electrically isolated) until the junctions body-source and body-channel become forward biased [40]). Figure 1.18 (adapted from [20]) shows the drain current variation for different light intensities. This figure shows also the slow decay of the drain current that is due to the slow recombination at the reverse biased source-body junctions. We recognize also another problem, the rather slow generation rate which is also a function of the illuminating light intensity and which is due to the rather low efficiency of the thin Si film of the floating body.

From this simple experiment we can foresee two major limitations to the utilization of the SOI phototransistor: the first is the low efficiency and the second is the slow decay of the photocurrent.

Figure 1.18 Drain current of a floating body SOI MOS when subject to a light pulse

#### **Fully Depleted**

In the fully depleted SOI MOSFET, the SOI film is far thinner than the depletion region width. The width of the silicon film is typically between few nanometers to few tens of nanometers. Thus there is no body region of the MOSFET to be charged and as a consequence no floating body effects like the kink effect, light effect and the history effect [8].

As a matter of fact, the fully depleted was designed as an effort to suppress the floating body effects. It may be assumed that the fully depleted SOI MOSFET are more suited for analog circuits implementation, as they have no kink effect and no history effect. The fully depleted SOI MOSFET have a steep sub-threshold slope and low parasitic capacitances making them suitable for low voltage, low power applications. An important advantage of the fully depleted SOI circuits is that, for the same bandwidth, they consume only about half the power of their bulk counter part.

However, because they do not have kink effects and are almost insensitive to light, the fully depleted SOI MOSFETs are not attractive for our specific (light sensing) application and therefore, only partially depleted SOI MOSFETs will be used throughout this project. Table 1.1 summarizes a comparison between the fully depleted and the partially depleted SOI MOSFET

|                          | Partially<br>Depleted SOI | Fully Depleted<br>SOI |

|--------------------------|---------------------------|-----------------------|

| Floating Body            | yes                       | no*                   |

| Active Silicon Thickness | $>0.15 \ \mu m$           | $< 0.1 \mu m$         |

| Kink Effect              | yes**                     | no                    |

| History Effect           | yes                       | no                    |

| Source/Drain resistance  | moderate                  | high                  |

| Manufacturing            | reasonable                | difficult             |

| Power                    | low                       | very low              |

Table 1.1

Comparison between partially depleted SOI and the fully depleted SOI

\* Floating body is not present in the saturation region of operation

\*\* Kink effect is suppressed in some operational states

### 1.2 Photosensors

Optical absorption is the fundamental process which is exploited when converting optical energy into electrical one. Photosensors are the devices that implement this conversion. Thanks to the work done by Max Plank and Albert Einstein, we can describe the light by a quantummechanical particle formalism. The smallest unit of light intensity is a quantum-mechanical particle called a *photon*. Photons are used to characterize electromagnetic radiation in the optical range from infrared to ultraviolet spectrum.

Photons are characterized by their energy E, itself dependent on the wavelength .

$$E = h\nu = \frac{hc}{\lambda} = \frac{hc_0}{\lambda_0}.$$

(1.1)

Where h is Planck's constant, E is expressed in electron-volt (eV),  $c_0$  is the speed of light in m/s and  $\lambda_0$  is the wavelength in nm both in vaccum. Whereas c is the speed of light in a medium with index of refraction  $\bar{n}$  and  $\lambda$  is the wavelength in the same medium. A useful relation to get the energy of a photon at a certain wavelength is:

$$E = \frac{1240}{h} \tag{1.2}$$

Where 1240 is the result of the product  $c_0h$ .

We define the flux density as the number of photons incident per time unit on a unit area. The optical power  $P_{opt}$  incident on a detector with an active area A, can be determined by the photon energy and the flux density:

$$P_{opt} = E\phi A = h\nu\phi A. \tag{1.3}$$

It is important to know the energy of a photon as it determines if it can be transferred to an electron allowing to pass from the valence band to the conduction band of a semiconductor. Indeed, an incident photon with energy larger than that of the bandgap  $(E_g)$  generates an electron-hole pair and the photon is absorbed. Photons with energies lower than  $E_g$  cannot be absorbed and the semiconductor is transparent for wavelengths longer than  $\lambda = \frac{hc_0}{E_g}$ . Another important parameter for photodetectors is the optical absorption coefficient  $\alpha$ . This coefficient, which depends on the semiconductor, affects the efficiency of the generation of electron-hole pairs and thus the photocurrent. The absorption coefficient determines the penetration depth  $1/\alpha$  of the light in the semiconductor material according to Lambert-Beer's law:

$$I(\bar{y}) = I_0 exp(-\alpha \bar{y}). \tag{1.4}$$

The optical absorption coefficient is strongly dependent on the wavelength of the incident light, for wavelengths shorter than  $\lambda_c$  which corresponds to the bandgap energy ( $\lambda = \frac{hc_0}{E_g}$ ) the absorption coefficient increase steeply according to the so-called *fundamental absorption*. Table 1.2 summarizes the absorption coefficient and intensity factors of silicon as a function of the most important wavelengths for a constant flux density of  $\phi = I_0/\alpha = 1.58 \times 10^{18}$  photons/ $cm^2$ .(ehp/ $cm^3$  is the electron-hole pairs/ $cm^3$ )

Although Silicon is not the optimal semiconductor regarding the optical absorption, it is widely used due to economical reasons.

#### 1.2.1 Photodiodes the State of the Art

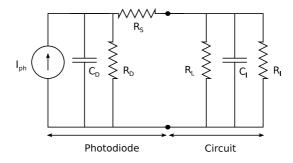

Typically, a photosensor consists of a photodiode and an amplifier with an input capacitance  $C_I$  and with an input resistance  $R_I$ . The equivalent circuit of a photodiode is shown in figure 1.19 together with the parasitic elements of the amplifier. These two elements define in general the major parameters of the photosensor like its speed, sensitivity and dynamic range.  $C_D$  is the space-charge region capacitance of the photodiode,  $I_{ph}$  current source is the photocurrent,  $R_D$  models the reverse bias leakage of the photodiode (also known as the dark current). The resistance  $R_L$  is a load resistance ;whereas, the series resistance

| Wavelength | $\alpha$       | $I_0$              |

|------------|----------------|--------------------|

| (nm)       | $(\mu m^{-1})$ | $(ehp/cm^3)$       |

| 980        | 0.0065         | $1.03 \ge 10^{20}$ |

| 850        | 0.06           | $9.5 \ge 10^{20}$  |

| 780        | 0.12           | $1.89 \ge 10^{21}$ |

| 680        | 0.24           | $3.79 \ge 10^{21}$ |

| 635        | 0.38           | $6.00 \ge 10^{21}$ |

| 565        | 0.73           | $1.16 \ge 10^{22}$ |

| 465        | 3.6            | $5.72 \ge 10^{22}$ |

| 430        | 5.7            | $9.00 \ge 10^{22}$ |

Table 1.2Absorption coefficient  $\alpha$  of silicon and intensity<br/>factors  $I_0$

$R_S$  cannot be neglected when the photocurrent has to flow through low doped regions, this is not the case for PIN photodiodes where the P and N regions are highly doped. Based on this model, we can determine the -3dB frequency

$$f_{3dB} = \frac{1}{2\pi (R_L//R_I)(C_D + C_I)}$$

(1.5)

for amplifiers with MOSFET input  ${\cal R}_I$  is very large and can be neglected.

Then  $f_{3dB}$  can be rewritten as

$$f_{3dB} = \frac{1}{2\pi R_L (C_D + C_I)}.$$

(1.6)

The capacitance of the photodiode can be approximated for the case of a reverse biased abrupt PN junction as follows:

$$C_D = A \sqrt{\frac{q\varepsilon_r \varepsilon_0 N_{A/D}}{2} \frac{1}{\sqrt{U_D - U - (2k_B T/q)}}}$$

(1.7)

where

$$U_D = \frac{K_B T}{q} \frac{N_A N_D}{n_i^2} \tag{1.8}$$

For the case of a PiN photodiode, the capacitance is approximated to that of a plate capacitor (neglecting the boundary capacitance):

$$C_D = A \frac{\varepsilon_r \varepsilon_0}{d_I} \tag{1.9}$$

Figure 1.19 Small-signal equivalent of a photodiode with parasitic element of the amplifier

where  $d_I$  is the thickness of the intrinsic region and A is the area of the photodiode.  $N_{A/D}$  is the doping concentration of the low doped side of a PN junction.

In the next subsection we will be interested only in CMOS integrated photodiodes.

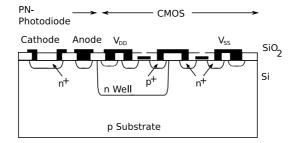

#### **CMOS** Integrated Photodiodes

**PN Photodiodes.** A PN junction in the CMOS process is the simplest way to build a photodiode using the source/drain-substrate or the source/drain-well or even well-substrate junctions. The main disadvantage of such photodiode is the absence of an electric field in certain regions. In such regions, the slow diffusion of photogenerated charges determines the -3dB frequency of such photodiode. The source/drain-well junction are suitable for short wavelength (shorter than 600 nm)as they are shallow junctions and the short wavelengths have limited penetration capabilities as shown in table 1.2. On the other side the junction well-substrate is suitable for longer wavelengths (780-850 nm). Figure 1.20, shows an  $N^+/P$ -substrate photodiode. Besides the slow diffusion, the series resistance of the anode contact limits the speed of such photodiodes.

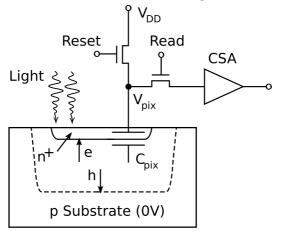

The parasitic capacity of the PN photodiode can be used as a storage to integrate and store photogenerated charges. This stored charge can be read later on to determine the intensity of the incident light. For this purpose in an initial phase, (also called the reset phase) the photodiode capacitor is charged to  $V_{DD}$ , then the diode is left floating. Exposure to light will discharge it gradually at a rate dependent on the intensity of incident light. This phase is commonly known as the integration phase. Next is the reading phase, the photodiode is connected to a charge sen-

Figure 1.20 Cross section of a PN photodiode integrated in a one-well CMOS chip

Figure 1.21 A PN photodiode in a pixel working in discharge mode

sitive amplifier which converts the charge into a voltage level that is converted to a digital value by an analog to digital converter (usually not associated to the pixel but rather to a complete column of pixels). Figure 1.21 shows the setup of a photodiode being used as a charge collector, specifically in discharge mode. This mode is advantageous as it allows the use of the electric field that build up during the reset phase.

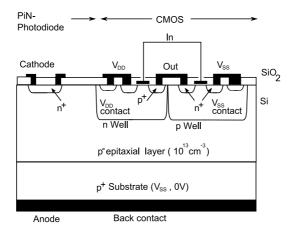

**PiN Photodiodes**, A PiN photodiode is a photodiode with a intrinsic region between the N and the P regions (hence the name PiN). The incident photons are absorbed in the intrinsic region which is a lightly doped or undoped Si region.

Compared to the PN photodiode, a PiN photodiode has a thicker depletion region allowing it to collect more photogenerated charges and hence PiN photodiodes have higher quantum efficiency. The thicker de-

Figure 1.22 A cross section of a PiN photodiode in a CMOS process

pletion region leads also to a lower parasitic capacitance, thus this kind of photodiodes has a large bandwidth typically in the order of few tens of gigahertz. Those photodiodes are sensitive along the visible spectrum and the infrared as it is based on Silicon. Having these specifications this photodiode is ideal for high speed communication systems.

Figure 1.22 shows how a PiN photodiode can be integrated on the same die with MOSFET transistors using a CMOS process.

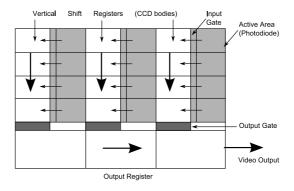

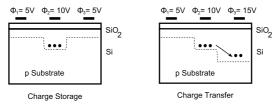

**Charge-Coupled-Device**, are basically closely spaced MOS capacitors whose capacity can be stored below one with the appropriate biasing for the gate under which the charges are stored as well as the surrounding gates. To transfer the charges from one gate to the other, one only needs to alter the biasing of the gates accordingly. An example of biasing for the storage and transferring the charges is given in figure 1.24. The light sensing part is always a photodiode which is the source of photogenerated charges that are transferred through the MOS capacitor. Figure 1.23 shows a typical array structure of CCD pixels, the charge is first transferred from the active area to the input gates, then a column wise transfers the charges to the output registers.

It is worth mentioning that 2 phase CCD's are also possible, these need an additional doping structure for generating an internal lateral electric field.

Active Pixel Sensor, the need to miniaturize has driven circuit designers to try to integrate the whole camera on chip. This means, we will need to have have both the optical sensor and the signal process-

Figure 1.24 An example of biasing for charge storage and charge transfer in a charge-coupled device

ing circuits integrated on the same die (and specifically using the same CMOS process). The Active Pixel Sensor (APS) represents many advantages over the CCD the most important of them are the following:

(i) random access

(ii) nondestructive readout

(iii) ease of integration with on chip electronics

Although CCD can be integrated with the electronics, some compromises will have to be made which will degrade the performance of the circuits. We can distinguish two types of active pixel sensors the photo-gate and the photodiode.

Figure 1.25 shows a block diagram of an array of APS pixels, showing the ease of access randomly to any of the pixel as opposed to the architecture of an array of CCD cells.

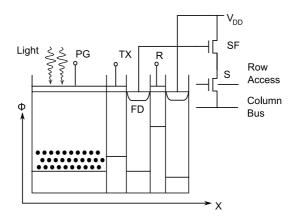

Photo-gate, with this kind of APS a charge transfer is needed from the photogate toward the storage region FD (figure 1.26). The pixel is selected by enabling the transistor S connecting the output of the source follower to column bus. The reset is done by enabling the transistor R. After the reset the charges generated by light at the photogate are transferred to the storage node FD. This creates a change of potential at the gate of the source follower which outputs the signal of the pixel

Figure 1.25 The block diagram of an array of APS pixels

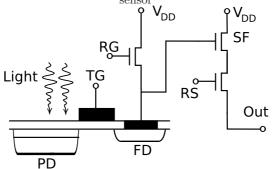

*Photodiode*, with this kind of APS, the photodiode acts as a charge integrator too. This charge is then transferred to the charge storage through the transfer gate TG (figure 1.27), the rest of the circuit is similar to that of the photogate.

A quick comparison of both types of APS shows that the photogate type has a lower quantum efficiency, it also needs a larger area due to the additional transfer switch. Its advantages are lower noise and higher conversion gain due to a smaller floating node capacitance [6].

## 1.2.2 Phototransistors: the State of the Art

For applications with weak optical signal the use of photodetectors with built in amplifications are used, these photodetectors are called phototransistors. These can be divided in two groups the *bipolar phototransistor* and the *MOSFET phototransistor*.

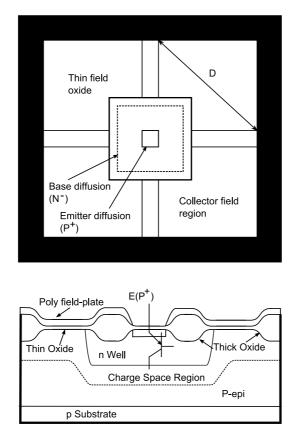

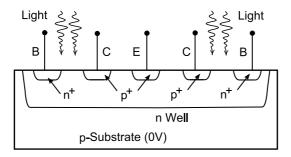

**Bipolar phototransistor**, are usually done on a CMOS process without substantial modifications through the use of a floating well as a floating base of a PNP transistor, the  $P^+$  of the source or the drain diffusions as the emitter and the substrate as the collector (figure 1.28). These phototransistors are used as common collector as the collector (the substrate in this case) is connected to ground.

The limitations of such a phototransistor are mainly :

(i) low sensitivity to short and medium wavelengths due to the depth of the N-well P substrate junction

(ii) a rather large base-collector capacitance due to the large base area.

Figure 1.26 Pixel circuit of a photogate APS image sensor

$Figure \ 1.27 \quad {\rm Pixel \ circuit \ of \ a \ photodiode \ APS \ image}$

Figure 1.28 A cross section of a vertical bipolar phototransistor in a CMOS process

Figure 1.29 Cross section and layout of a PNP phototransistor with reduced Base-Collector capacitance

These disadvantages were overcome by the use of a polysilicon field-plate structure (shown in figure 1.29). This allows the reduction of the N-well base area, whereby the space-charge region below the plate and carrier diffusion in the areas not covered by the polysilicon are used for the collection of photogenerated charges. ([53])

As mentioned before the vertical bipolar (shown in figure 1.28) can only be used in a common-collector topology, however a lateral bipolar (shown in figure 1.30) can be freely used. These are also readily available in a standard CMOS process without modifications. However, they suffer from low current gain and lower collector efficiency than their vertical counterpart. [42] proposed modification to the structure to improve the performances of this lateral bipolar phototransistor.

Figure 1.30 A cross section of a lateral bipolar phototransistor in a CMOS process

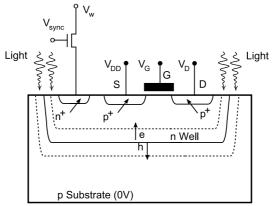

Figure 1.31 A cross section of a MOSFET phototransistor

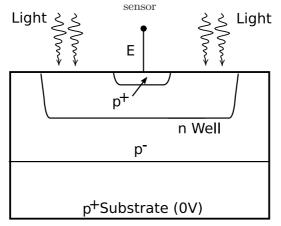

**MOSFET phototransistor**, is a usual transistor, with the N-well left floating as is shown in figure 1.31. The incident light will generate electron-hole pairs that get separated by the electric field at N-well P substrate junction. The N-well will become charged negatively as the free electrons will drift to the N-well. This will change the threshold voltage and hence modulate the drain current. Some of the drawbacks of this phototransistor is that the dark current is also amplified with the signal, slow response due to space charge that extends some 1-2  $\mu m$  away from the N-well which causes slow charge diffusion.

#### 1.2.3 Techniques

Based on the electrical model of the photodiode, we can see that all the techniques of measurements are done by measuring and quantifying

Figure 1.32 A schematic cross section of an illuminated SOI nMOS ([58])

the photocurrent that is a change in the current (or conversely in the voltage of a charged capacitor) and then amplify it.

The challenges are to design an amplifier with the lowest input noise that would not mask the photocurrent or create the greater voltage change by minimizing the value of the integrating capacitor (and also taking care of the  $\frac{KT}{CP}$  noise due to switching the integrating capacitor).

## **1.3 SOI Photosensors**

SOI photosensors range from the classical photodiodes to phototransistors just like in the bulk case, in the following section we will review the recent studies and researches in this field.

### 1.3.1 State of the Art

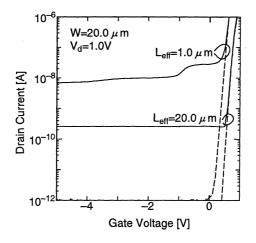

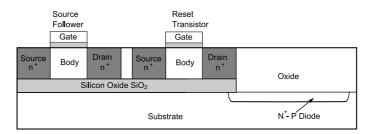

Lateral bipolar transistor in the floating body SOI. This was shown in [58]. In the setup shown in Figure 1.32 the sample is illuminated from the gate side. This creates electron hole pairs in the body. The electrons are evacuated through the positively biased drain, while the holes remain in the floating body. The positively charged holes in the body are responsible for the base current of the lateral bipolar which amplifies the drain current by a factor  $\beta$ . Note that the base which is nothing but the body is floating, and hence is not biased that's why the author named this topology as *self biased*. The base width of this parasitic bipolar transistor is the channel length of the SOI MOSFET. Figure 1.33 shows the current gain that is due to illumination for two channel lengths.(figure taken from [58]).

Figure 1.33 Current gain due to illumination for channel lengths  $1\mu m$  and  $20\mu m$ . ([58])

| Dark Current  | Diode<br>Responsivity | Conversion<br>Gain | Output Swing | Dynamic<br>Range |

|---------------|-----------------------|--------------------|--------------|------------------|

| $< 50 nAcm^2$ | 500  mA/w             | $1\mu V/e$         | > 0.5V       | 74dB             |

Table 1.3 Summary of performance of the hybrid APS

The authors in [57], have opted for a hybrid solution where the circuits are in SOI MOSFETs while the photodiode was built on the handle substrate. Figure 1.34 shows the structure adopted by the author to build an APS using both bulk and SOI on the same die. The performances of such an APS are summarized in the table 1.3

### 1.3.2 Our Phototransistor

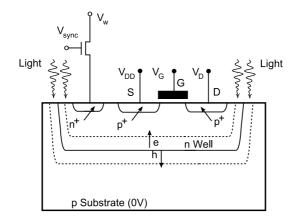

The phototransistor we have used throughout the whole project, is a partially depleted floating body SOI MOSFET. The need for a partially depleted is motivated by the use of the neutral region to store the photogenerated holes that are responsible for the drain current increase through the change in the threshold voltage. The floating body is needed to store the charges otherwise they will be sunk through the source, for instance, for a body connected to the source. And finally the use of SOI is actually related to the above mentioned characteristics which cannot be found in a bulk process. The photogenerated charges will remain in the body even when light is switched off. As we can see in figure 1.18 the decay of the current is slow (time constant is in the order of sec-

Figure 1.34 A schematic structure of the hybrid bulk/SOI CMOS APS( [57])

Figure 1.35 The photogeneration and storage in a PD floating gate SOI MOSFET

onds), and is due to the recombination of the holes at the reverse biased source-body and drain-body junctions.

In figure 1.35 we show how the electron-hole pairs are generated and how these photogenerated charges get stored in the floating body.

It is worth mentioning that the partially depleted SOI MOSFETs used in this research are devices optimized for mixed mode applications from the Xi10 of XFAB and not optically optimized for imaging applications. The specifications of such devices are shown in table 1.4. As shown in figure 1.35 the device performances were measured when it was illuminated from the front gate side, it is known that illuminating from the backside greatly improves the optical efficient by at least a factor of 2 [43].

| Parameters        | $\mathbf{Symbol}$ | Units             | N-type | P-type |

|-------------------|-------------------|-------------------|--------|--------|

| Gate Oxide        | $t_{oxf}$         | nm                | 25     | 25     |

| Silicon Film      | $t_{si}$          | nm                | 250    | 250    |

| Buried Oxide      | $t_{box}$         | nm                | 1000   | 1000   |

| Channel Doping    | N                 | $10^{16} cm^{-3}$ | 16     | 4      |

| Mobility          | $\mu$             | $m^2/Vs$          | 510    | 180    |

| Body Factor       | $\mu C_{ox}$      | $\mu A/V^2$       | 82     | 32     |

| Threshold Voltage | $V_{T0}$          | V                 | 1.7    | -1.3   |

| Body Factor Slope | n                 |                   | 2.3    | 1.5    |

| Supply Voltage    |                   | V                 | 5      | 5      |

| Table 1.4      | XFAB's partially depleted SOI MOSFET |  |  |  |  |

|----------------|--------------------------------------|--|--|--|--|

| specifications |                                      |  |  |  |  |

## 1.4 Conclusion

In this chapter we had a general review of what is being used currently in image sensing using both the bulk CMOS process as well as the SOI process. We have also seen the limitations that an SOI image sensor has, due mainly to the thin Si film to collect the incident photons. We have exposed the characteristic of the partially depleted floating body SOI MOSFET as well as the problems in having it used as a phototransistor.

The following chapters will discuss the technique used to overcome the two major limitations of the SOI phototransistor: the low optical efficiency and the slow decay due to the charged body.

### Chapter 2

# **Device Principles**

## 2.1 Introduction

S ILICON On Insulator, as we have seen in chapter 1, is being widely used in the fabrication of integrated circuits due to its advantages with respect to the low junction leakage, low switching noise coupling, high temperature immunity, low voltage and low power applications. More recently, SOI transistors have also been used in high speed CPU's [25] due to their high switching performances and their reduced power consumption. Another application where high performances are needed are dynamic memories (DRAM) where floating SOI MOSFETS were used as an 1T memory node. That drastically increased the density of unit cells and hence the storage capacity [34].

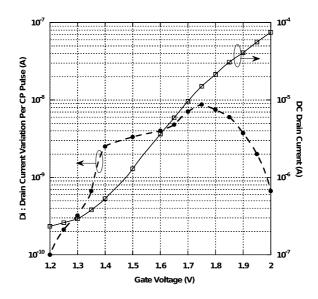

However, despite the technical advances in SOI technology, it has rarely been exploited in optical sensing and imagery [13], the main reasons being the expected low optical conversion efficiency due to the relatively thin silicon film thicknesses, well below 1  $\mu m$  and the slow time constants due to slow recombinations at the junctions. This slim active region reduces the optical bandwidth of such sensors as longer wavelengths are absorbed deeper (and in the case of SOI probably in the buried oxide layer). Even with such a handicap it was shown recently that an SOI MOSFET based phototransistor could detect light intensities as low as  $5mW/m^2$  [12]. However, in this work, as it is the case for most of the works done on fully and partially depleted SOI MOSFET's based photodetectors, it is the drain current variation due to light absorption that was used as a measure of photon densities [15, 42, 58, 59, 35, 36, 43] (for instance in [12] the  $5mW/m^2$  generates 50 fA of photocurrent). Such variations are hard to measure with the needed resolution as such currents are close to the noise levels of any amplifier.

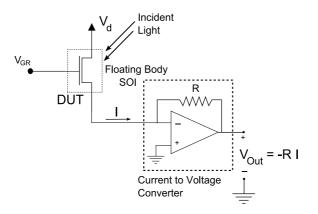

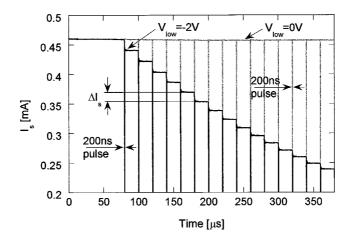

In this chapter, we present a new measurement technique for low light intensity overcoming the problems inherent to noise and low current variations, and the problems of slow drain current recovery due to slow recombinations at the junctions in a floating body partially depleted MOSFET. In addition, an extension of this technique to any floating well bulk MOSFET is presented. Measurement results proved that a bulk PMOS with a floating N-well have the same behaviour as the floating body SOI MSOFET.

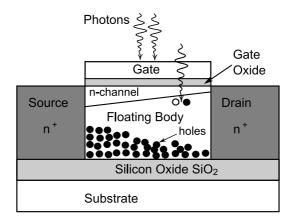

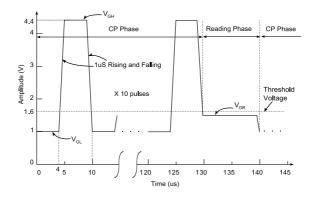

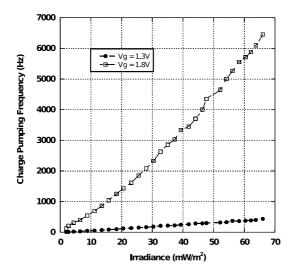

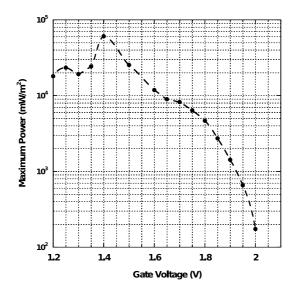

Essentially, when a floating body SOI MOSFET is exposed to light, some of the incident photons will be absorbed, generating electron-hole pairs inside the body. A fraction of these electron-hole pairs will get separated by the electric field in the depletion layers, i.e. below the channel, and at the junctions. Considering an N-channel device, electrons will drift to the drain whereas holes will remain in the body and will accumulate until the body-source and/or body-channel junctions start to be forward biased. Being electrically insulated, holes remaining in the body will decrease the threshold voltage that in turn will increase the drain current. This phenomena is very similar to the well known kink effect taking place in floating body SOI MOSFET's when relatively high drain to source voltages is applied [55, 28]. Usually in standard approaches the drain current magnitude is representative of the light intensity. However, here we intend to propose a new method based on the transient charge pumping technique [31]. This method consists in maintaining the drain current to a nominal value by removing the excess of photogenerated holes from the body. This can be achieved by recombining holes with electrons trapped on defects located near the  $Si/SiO_2$  interface using the transient charge pumping. In the following sections, this new approach will be analyzed showing its effectiveness to measure light intensity from practical application and its main advantages in terms of speed, dynamic range and sensitivity.

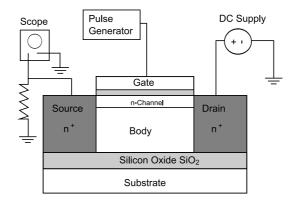

## 2.2 The Effect of Light on a Partially Depleted Floating Body SOI MOSFET

We propose to analyze the effect of light on the drain current of a floating body SOI MOSFET. In particular, we will study the impact of the gate voltage on the electron-hole pair collect efficiency, which, to our knowledge, was never reported so far. Without loss of generality, we propose to investigate an N type floating body partially depleted SOI MOSFET. The silicon film thickness is 250 nm and is doped at about  $10^{17}cm^{-3}$  and the gate oxide is 25 nm thick. The threshold voltage was measured and found to be close to 1.6V. In our experiment, the phototransistor was illuminated from the 'top' with different wavelengths and the optical power density was measured using a calibrated photodiode. This configuration is obviously not optimized since incident light had then to cross all the passive layers and the gate contact before reaching the active body. Neither was the device itself as it was fabricated in a quite old technology (1  $\mu m$  minimum channel length). Measurements circuits were not integrated on the chip and data acquisition was done through external circuits. In order to reduce the measurement time constants, we intentionally used a relatively large device with width and length of  $100\mu m$  and  $1\mu m$  respectively (nevertheless, the pixel active area is still equivalent to that of a  $10/10\mu m$  device).

### 2.2.1 The Effect of Light on Electrical Characteristics

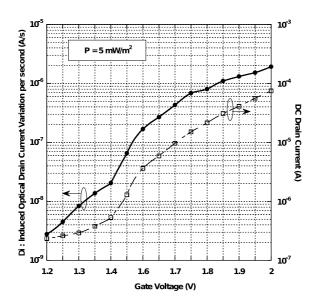

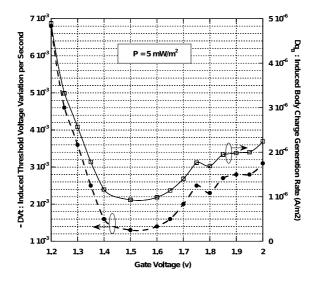

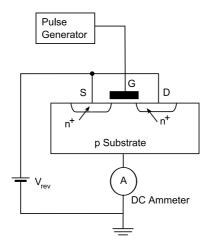

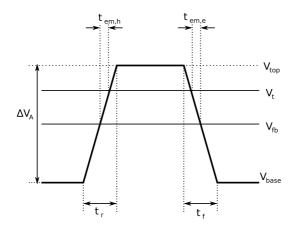

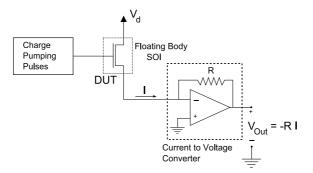

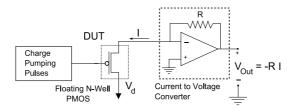

As already reported in previous works [60], illuminating a PD SOI MOSFET will increase the drain current by decreasing the threshold voltage due to accumulation of some photogenerated majority carriers inside of the body. Electrons will drift to the channel and will be collected by the drain whereas holes will stay inside the body. Some of these electrons will leak through the body-source and body-channel junctions [60]. For a given wavelength (for instance with a green LED), we intend to evaluate the photogeneration rate (optical efficiency) of the SOI MOSFET by measuring the drain current drift with respect to time for a given light irradiance  $(mW/m^2)$ . In order to avoid non linear effects, the photogeneration rate was extracted through the drain current variation at the onset of illumination ensuring that the operating point is almost constant. This was further confirmed in our experiments through the evaluation of the induced body potential variations. The gate voltage was in the range of 1.2 V to 2.0V and the drain potential was set to 0.3V in order to avoid electron-hole pair generation by impact ionization [55, 28]. An external low-noise high-gain current to voltage converter was connected to the source of the transistor, as shown in figure 2.12. This setup was used both to decrease the time response of the overall circuit and, due to the high gain of the amplifier, to set the source potential to zero volt (according to figure 2.1, a simple relation exists between the output voltage and the input current).

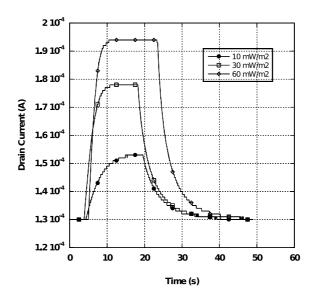

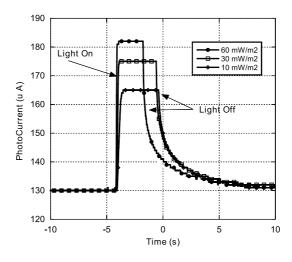

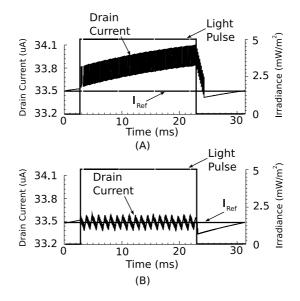

Figure 2.2 shows a typical dependence of the drain current  $(I_D)$  versus time when the device is illuminated with different light intensities. Under illumination the drain current increases until it reaches a 'steady state' value. This can be explained by a competition between (optically induced) hole generation and hole recombination rates at the junctions

Figure 2.1 Circuit topology used in the light generation experiment

(mainly between body/source [55, 28] and body/channel [40]).

Indeed, accumulation of holes inside the electrically insulated body will increase the body potential. Conversely, increase in the body potential will induce recombination of these holes at the forward biased junctions. Since recombination rate of hole inside the junctions varies exponentially with the body potential, an equilibrium state will be reached after a given time depending on the light intensity. Now, after switchingoff the light, the transistor is in non-equilibrium and the excess of holes will then recombine through junction leakage. This will reduce the body potential and hence the drain current, giving rise to the slow transient decay on figure 2.2. In our case, the switch off time constant could exceed 10 seconds, which is obviously not acceptable for practical applications (the reason for slow decay comes from the vanishingly small recombination rate for low values of the body potential. It is worth noticing that the apparent fast decay observed in [58] was due to the fact that the authors did not wait long enough to recover a true steady state. In our case this would lead to unacceptable errors especially when low intensities are measured).

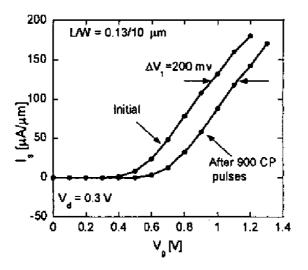

### 2.2.2 Impact of the Gate Voltage on Charge Separation

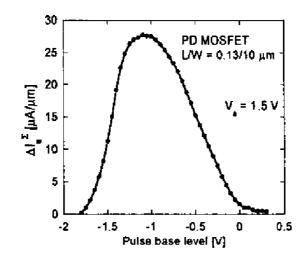

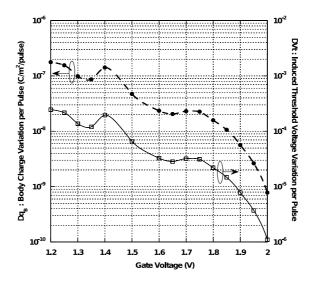

Since electron hole pairs separation is governed by the built-in electric fields in the depletion regions, we expect that the gate voltage will have an impact on the collect efficiency of holes by affecting the depletion layer below the channel. We measured the effect of the gate voltage on the photo-induced drain current variation by illuminating the transistor with a green light ( $\lambda = 550nm$ ), with an incident power of  $5mW/m^2$ .

Figure 2.2 Time dependence of the drain current of a floating body partially depleted SOI MOSFET when subjected to a light pulse

Then, we computed the current slopes evaluated at the onset of illumination for different gate voltages from 1.2V to 2.0V, while keeping  $V_{DS}$ at 0.3 volt. Figure 2.2 shows both the dark drain current and the drain current variation due to the illumination of the transistor with a light irradiance of  $5mW/m^2$ . Apparently, for a given illumination intensity, the current variation always increases with the gate voltage. However, since the relation between current and body charge density depends on the inversion level of the channel, we have to convert the current into body charges.

Based on the EKV formalism [41, 39] and provided gate, source and drain potentials are maintained constant with respect to an external reference, we can explicit the relations that govern the relation between the body charge density and induced drain current variations in a floating body partially depleted SOI MOSFET.

Let's first normalize the currents and charges to  $2n\mu C_{ox}U_t^2$  and  $-2nC_{ox}U_t$  respectively with n varying between 1.1 and 1.7 from strong to weak inversion and normalizing potentials to the thermal voltage [39], we obtain:

$$i = (q_S^2 + q_S) - (q_D^2 + q_D)$$

(2.1)

Where i,  $q_S$  and  $q_D$  represent the normalized current and normalized source and drain charges. In addition, normalized charges and potentials

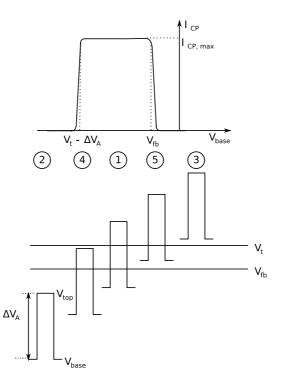

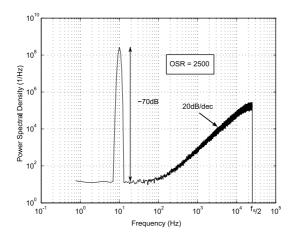

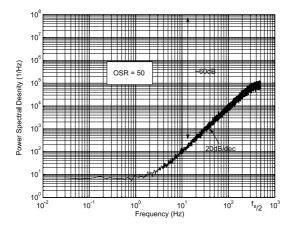

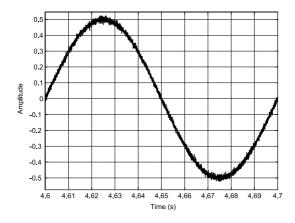

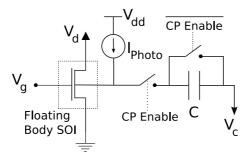

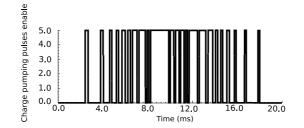

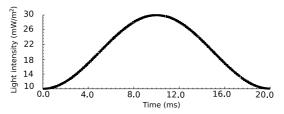

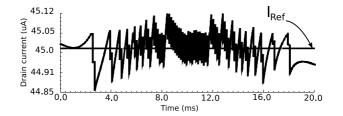

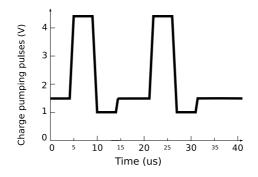

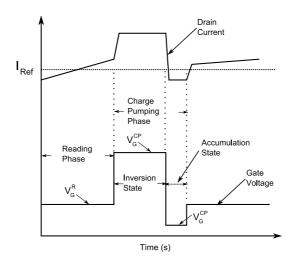

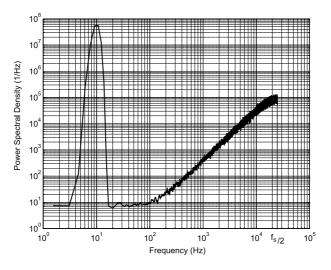

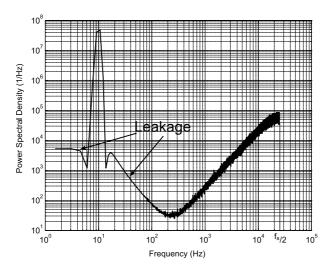

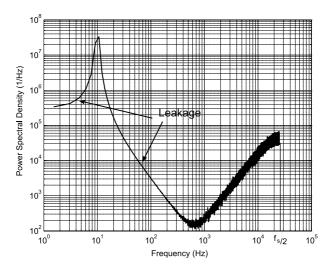

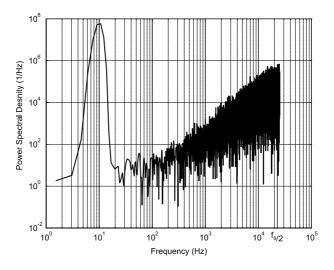

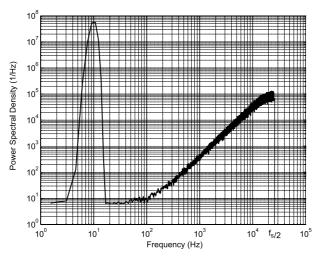

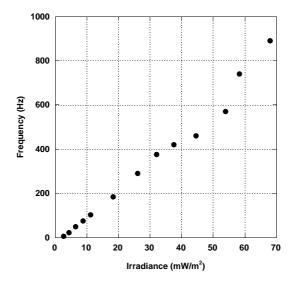

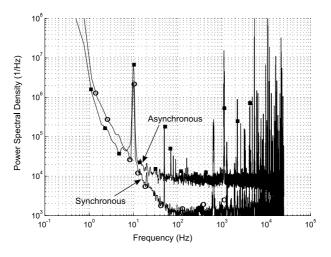

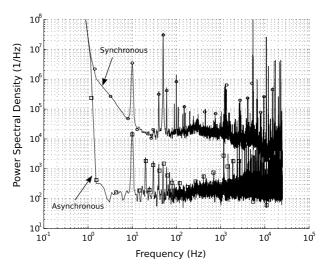

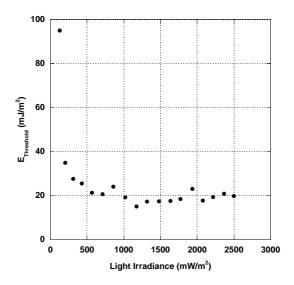

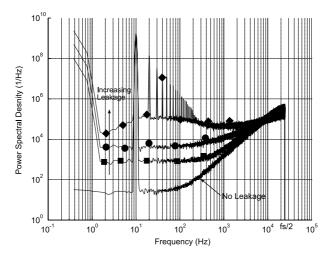

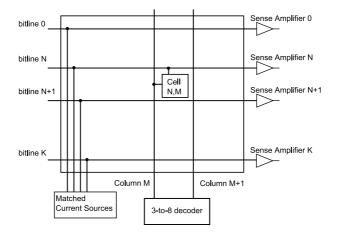

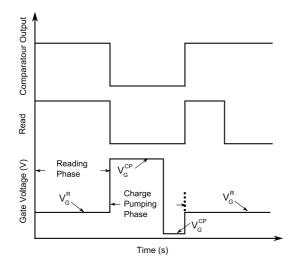

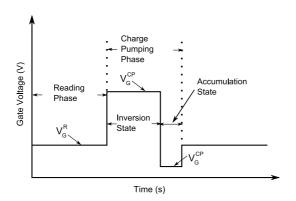

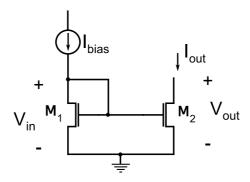

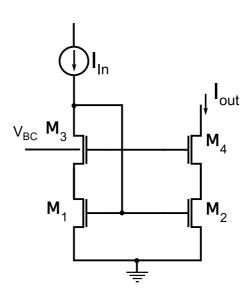

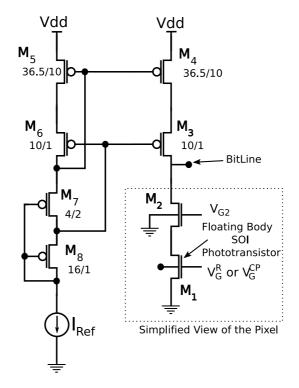

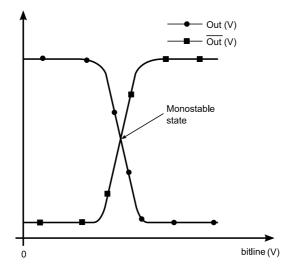

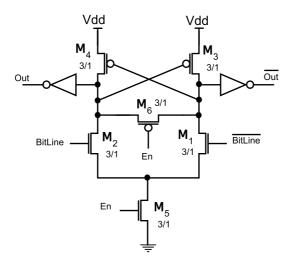

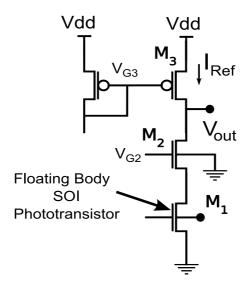

are also linked by [41]: