# Controlled synthesis of silicon nanocrystals into a thin SiO<sub>2</sub> layer synthesized by stencil-masked ultra-low energy ion implantation

Dumas C.<sup>a,b</sup>, <u>Grisolia J.<sup>a</sup></u>, BenAssayag G.<sup>b</sup>, Bonafos C.<sup>b</sup>, Schamm S.<sup>b</sup>, Arbouet A.<sup>b</sup>, Paillard V.<sup>b</sup>, Van den Boogaart M.A.F.<sup>c</sup>, Brugger J.<sup>c</sup>, Normand P.<sup>d</sup>

<sup>a</sup> LPCNO, INSA, 135 avenue de Rangueil, 31077 Toulouse, France, Jeremie.grisolia@insa-toulouse.fr

<sup>b</sup> CEMES-CNRS, 29 rue Jeanne Marvig, 31055 Toulouse, France

<sup>c</sup> Ecole Polytechnique Fédérale de Lausanne (EPFL), Laboratoire de Microsystèmes, CH-1015 Lausanne, Switzerland

<sup>d</sup> Institute of Microelectronics, NCSR 'Demokritos', 15310 Aghia Praskevi, Greece

#### **Abstract**

We have synthesized Si Nps rich submicron area within a thin  $SiO_2$  layer using a new method called "stencil-masked ion implantation". It consists in implanting silicon ions at ultra-low energy through windows (from 50nm to 2 $\mu$ m) opened in a stencil mask containing. After thermal annealing the implanted regions perfectly mimic the mask geometry. Energy-filtered transmission electron microscopy images and PL measurement reveal that smaller nanocrystals are formed near the edges of the implanted areas due to a dose edge effect.

# 1. INTRODUCTION

Nanocrystal (nc) based memory technology is one of the identified routes which fulfil the stringent requirements of non-volatile memory cell downscaling [1-3]. More devices exploiting new effects such as Coulomb blockade and quantized charging effects at room temperature [4-5] should be fabricated and MOS cells with nanometer-sized nanocrystals are good candidates if the number of Ncs is small [6-7]. It has been previously demonstrated that ultra low energy ion implantation (1keV) into an ultra thin SiO<sub>2</sub> layer (7nm), followed by annealing can produce 2D arrays of Si ncs [8-9]. In order to control simultaneously the size, the number and the localization of synthesized ncs we propose in this work a new approach combining stencil lithography and ultra low energy ion implantation ("stencil mask ion implantation process").

#### 2. EXPERIMENTAL DETAILS

The stencil masks are fabricated using a combination of deep ultraviolet (DUV) exposure and a standard micro-electromechanical processing [10].

They are made of four  $500\mu\text{m}\times500\mu\text{m}$  membranes bored with a window array defined on a DUV resist and then transferred into the SiN layer by anisotropic etching. The thickness of these SiN membranes ranges from 100nm to 500nm. The apertures made by DUV have a size varying from 220nm to  $4\mu\text{m}$ , and a pitch ranging from  $1\mu\text{m}$  to  $10\mu\text{m}$ .

A 7nm thick dry silicon dioxide layer is thermally grown on an 8-in. *p*-type (100)-oriented Si wafer. The stencil mask is attached directly on the silica surface and maintained by double sided adhesive tape. The implantation dose and the ion energy are respectively  $1 \times 10^{16}$  Si<sup>+</sup>/cm<sup>2</sup> and 1keV. After stencil mask removal the sample is annealed for various duration ranging from 30mn to 240mn, at 1050°C under N<sub>2</sub> ambient. During the annealing process a phase separation between the excess silicon and the oxide occurs and ncs are formed.

After annealing, the implanted areas are observed by Scanning Electron Microscope (SEM) using a Zeiss 1540XB CrossBeam. To extract the size, the density and the surface coverage on implanted and non-implanted regions Energy-Filtered Transmission-Electron Microscopy (EFTEM) is performed. PL spectroscopy is used for optical studies.

## 3. RESULTS AND DISCUSSION

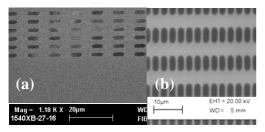

Figure 1a shows a SEM picture of the stencil mask containing micrometric patterns (5µm long, 1.5µm wide with a 3µm pitch). Figure 1b is a SEM image of a sample implanted through the stencil mask. It clearly shows the Si implanted regions (dark areas) that reproduce the stencil mask patterns. These observations prove that implantation through a stencil

Figure 1: SEM images (a) Stencil Mask (b) NCs area in locally implanted regions.

mask creates nanocrystals in well-localized regions of the oxide.

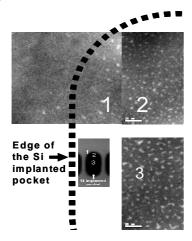

Figure 2: TEM plane view of an implanted area.

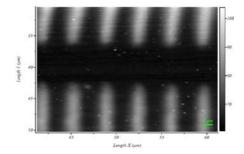

EFTEM images shown in Figure 2 reveal three pertinent regions of an implanted pocket: (1) near the left edge, (2) in the upper part and (3) in the center. In region (1), ncs are generated only inside the implanted area. In region (2) and (3), a dense array of ncs was detected showing two morphology types: (a) a connected array of elongated particles of 2.1nm in length and with a surface density of 3.4x10<sup>12</sup>cm<sup>-2</sup>, corresponding to 11.3% in terms of surface coverage (region (3)) and (b) a dense array of isolated spherical particles (3.4nm in diameter), with a surface density of  $2x10^{12}$ cm<sup>-2</sup>, i.e. 11.7% of surface coverage (region (2)). Edge effects are evidenced with smaller nanocrystals detected near the window edges which reduce the effective implanted dose and reduce the NC mean size. Fig. 3 shows a typical large scale PL image taken in large apertures (micron size) which was recorded using the 0.9 NA objectives and using a 0.2 micron step. A line drawn along the Y axis exhibits a succession of

dark (i.e. weak PL intensity) and white (i.e. high PL

Figure 3: PL cartography of implanted/non implanted area

intensity) zones corresponding respectively to nonimplanted and Si implanted regions. This PL spectrum again proves that the Si ncs region mimics the mask pattern. The maximum PL intensity and the energy position of the implanted pockets are in good agreement with a previous study performed on implanted bare wafers [11].

## 4. CONCLUSIONS

In conclusion, we have presented an original technique called "stencil masked ion implantation process" to synthesize a localized and controlled number of Si ncs by implanting silicon ions through apertures made in a stencil mask. SEM, EFTEM and PL reveal a perfect matching between the detected implanted areas and the stencil mask patterns. This number could be reduced to one for 30 nm windows in the stencil mask.

## REFERENCES

[1] S. Tiwari, F. Rana, H. I. Hanafi, A. Hartstein, E. F. Crabbé, and K. Chan, Appl. Phys. Lett. **68**, 1377 (1996).

[2] H. I. Hanafi, S. Tiwari, and I. Khan, IEEE Trans. Electron Devices **ED43**, 1553, (1996).

[3] J. De Blauwe, IEEE Trans. Nanotechnol. 1, 72 (2002).

[4] E. Kapetanakis, P. Normand, D. Tsoukalas, and K. Beltsios, Appl. Phys. Lett. **80**, 2794 (2002).

[5] S. Huang, S. Banerjee, R. T. Tung, and S. Oda, J. Appl. Phys. 93, 576, (2003).

[6] G. Molas, B. De Salvo, D. Mariolle, G. Ghibaudo, A. Toffoli, N. Buffet, and S. Deleonibus, Solid-State Electron. 47, 1645 (2003).

[7] M. Shalchian, J. Grisolia, G. Ben Assayag, H. Coffin, S.M. Atarodi, A. Claverie, Solid-State Electron. 49, 1198–1205, 2005

[8] C. Bonafos, M. Carrada, N. Cherkashin, H. Coffin, D. Chassaing, G. Ben Assayag, A. Claverie, T. Müller K. H. Heinig, M. Perego, M. Fanciulli, P. Dimitrakis, and P. Normand, J. Appl. Phys. **95**, 5696 (2004).

[9] P. Normand, P. Dimitrakis, E. Kapetanakis, D. Skarlatos, K. Beltsios, D.Tsoukalas, C. Bonafos, H. Coffin, G. Benassayag, A. Claverie, V. Soncini, A. Agarwal, Ch. Sohl, and M. Ameen, Microelectron. Eng. **73–74**, 730, (2004).

[10] M.A.F.Van Den Boogaart, G.M.Kim, R.Pellens, J.-P.Vand Den Heuvel, J.Brugger, Journ.Vac.Sci.Technol.B, **22**, 6 (2004).

[11] M.Carrada, A.Wellner, V.Paillard, C.Bonafos, H.Coffin, A.Claverie, Appl. Phys. Lett. 87, 251911(2005).