## Performance Prediction and Race Detection in Message-Passing Parallel Applications

### THÈSE N° 4274 (2009)

PRÉSENTÉE LE 6 FÉVRIER 2009

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE DE SYSTÈMES PÉRIPHÉRIQUES

PROGRAMME DOCTORAL EN INFORMATIQUE, COMMUNICATIONS ET INFORMATION

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Basile SCHÄLI

acceptée sur proposition du jury:

Prof. R. Guerraoui, président du jury Prof. R. Hersch, directeur de thèse Dr R. Gruber, rapporteur Prof. P. Kropf, rapporteur Dr S. Ur, rapporteur

## **Abstract**

The combination of low cost clusters and multicore processors lowers the barrier for accessing massive amounts of computing power. As computational sciences advance, the use of *in silico* simulations to complement *in vivo* experiments promises parallel programming a bright future in multiple scientific fields. It is therefore increasingly important to develop tools helping developers to write efficient and bug-free parallel applications.

This thesis focuses on performance prediction and advanced testing tools for distributed memory message-passing parallel applications. The tools have been implemented within the Dynamic Parallel Schedules (DPS) parallelization framework. They have also been partly adapted to applications written using the Message Passing Interface (MPI) standard.

The first part presents a parallel application simulator which has been integrated into the DPS framework. We identified a small set of processing and networking parameters that characterize the hardware platform on which the application is running. After parameterizing the hardware platform, the running time of parallel applications can be predicted using direct execution without requiring any change to the application source code. We propose a partial direct execution technique that reduces the execution time and memory consumption of the simulation. Using partial direct execution, the simulation is no longer tied to the platform to be simulated. Simulations may thus run on a desktop computer rather than on the target parallel machine. The proposed parameterization of the application and of the hardware properties enable using the simulator to study the sensitivity of a parallel application to various operating conditions such as the data subdivision granularity, the adopted parallelization strategy and the underlying hardware platform properties. The proposed simulator helps developers identifying the factors having the largest impact on their application's performance, and determining the most suitable cluster hardware configuration.

Speed should not come at the expense of correctness. Since improving parallelization efficiency often requires loosening synchronizations or implementing more complex communication patterns, developers need to ensure that their changes do not introduce potential message races or deadlocks. Deadlocks and message races are common sources of problems in parallel applications and stem from the fact that the delivery of messages from different sources is not deterministically ordered. This non-determinism makes such synchronization errors hard to reproduce and debug.

The second part of the thesis presents methods for uncovering potential deadlocks and message races by taking advantage of the flow graph structures and checkpointing capabilities of DPS. We developed a debugger for DPS applications that displays an instantaneous graphical view of the global computation state and is able to control the ordering of message delivery in order to explicitly test specific orderings. The number of possible orderings explodes when the number of messages sent by the application increases. Manual testing can only cover a tiny fraction of possible executions. Therefore, we use the simulator's ability to control the execution of a parallel application, in order to automatically detect deadlocks and message races. A first method for reducing the number of orderings to be tested relies on a partial-order reduction of the search space and on the decomposition of the application execution into independently testable subparts. This method relies on a static analysis of an execution trace of the application, and can therefore only be applied to parallel applications that produce a fixed set of messages, i.e. applications producing the same messages for all delivery orderings. In order to overcome this limitation, we propose an approach relying on the dynamic construction of a state graph expressing possible executions. Both methods reduce the testing costs by several orders of magnitude, and can be combined to further improve the results. Nevertheless, testing durations may remain prohibitive for longer running applications. We therefore also define algorithms generating subsets of possible orderings that are likely to reveal erroneous executions.

In the recent years, the MPI standard has emerged as the *de facto* standard for writing message-passing parallel applications. The final part of this thesis therefore focuses on adapting the aforementioned parallel application testing concepts to MPI applications. We first describe the extension of our work on visualizing the execution of parallel applications. We then discuss the limits and the benefits of using partial-order execution graphs to describe MPI application executions, and show that our dynamic message-passing state graph construction approach can be successfully applied.

**Keywords:** Message-passing parallel applications, performance prediction, message race, testing, partial-order reduction, debugging, Dynamic Parallel Schedules, Message Passing Interface

## Résumé

La combinaison de clusters à bas coûts et de processeurs multicoeurs expose un public de plus en plus large à une puissance de calcul considérable. Avec l'avance des sciences computationnelles, l'utilisation de simulations *in silico* pour compléter les expériences *in vivo* promettent à la programmation parallèle un futur radieux dans un nombre croissants de domaines scientifiques. Il est donc de plus en plus important de développer des outils pour aider les développeurs à écrire des applications parallèles efficaces et correctes.

Cette thèse se concentre sur la prédiction de performance et sur des outils de tests avancés pour les applications parallèles à mémoire distribuée communiquant par envoi de messages. Ces outils ont été implémentés dans la framework de programmation parallèle Dynamic Parallel Schedules (DPS). Ils ont aussi été partiellement adaptés aux applications utilisant le standard Message Passing Interface (MPI).

La première partie présente un simulateur d'applications parallèles intégré dans DPS. Nous avons identifié un petit ensemble de paramètres caractérisant les performances de calcul et de communication de la plateforme matérielle sur laquelle tourne l'application. Après avoir paramétrisé le matériel, le temps d'exécution des applications parallèles peut être prédit sans modifier le code de l'application en utilisant de l'exécution directe. Nous proposons une technique d'exécution directe partielle réduisant la durée de la simulation et sa consommation mémoire. En utilisant l'exécution directe partielle, la simulation n'est plus liée à la plateforme devant être simulée. Les simulations peuvent donc être effectuées sur un ordinateur de bureau plutôt que sur la machine parallèle cible. La paramétrisation de l'application et des caractéristiques matérielles permettent d'utiliser le simulateur pour étudier la sensibilité d'une application parallèle aux différentes conditions d'opérations, telles que la granularité de subdivision, la stratégie de parallélisation et la vitesse des calculs ou des communications. Le simulateur proposé peut donc aider les développeurs à identifier les facteurs ayant le plus d'impact sur les performances de leur application, et à déterminer quelle machine parallèle est la plus appropriée.

L'amélioration de la vitesse d'exécution ne doit pas induire des erreurs dans le programme.

L'efficacité de la parallélisation est souvent améliorée en relâchant certaines synchronizations ou en implémentant des patterns de communications plus complexes. Les développeurs doivent donc s'assurer que leurs changements n'introduisent pas des interblockages (deadlocks) ou des situations de compétitions (message races). Ces deux problèmes sont fréquents dans les programmes parallèles et sont dûs au fait que des messages provenant de différentes sources n'arrivent pas dans un ordre déterministe. Ce non-déterminisme rend ces erreurs de synchronizations difficiles à reproduire et à corriger.

La deuxième partie de cette thèse présente des méthodes provoquant et détectant les deadlocks et message races potentiels en tirant parti du graphe de flux et des capacités de checkpointing des applications DPS. Nous présentons un débuggeur capable de représenter graphiquement l'état d'avancement de l'exécution d'une application DPS. Un contrôle sur l'ordonnancement des messages permet de tester spécifiquement certaines exécutions. Comme le nombre d'ordonnancements possibles explose lorsque le nombre de messages envoyés par l'application croît, des tests manuels ne peuvent explorer qu'une fraction des exécutions possibles. Nous utilisons la capacité du simulateur à contrôler l'exécution d'une application pour détecter automatiquement les deadlocks et les message races. Une première méthode pour réduire le nombre d'ordonnancements à tester utilise une réduction partielle d'ordre de l'espace de recherche et décompose l'exécution de l'application en sous-parties pouvant être testée indépendamment les unes des autres. Cette méthode s'appuie sur l'analyse statique de la trace d'une exécution de l'application et ne s'applique ainsi qu'aux applications produisant un ensemble fixe de messages, i.e. produisant les mêmes messages quel que soit l'ordre dans lequel ils sont traités par l'application. Nous supprimons cette limitation à l'aide d'une approche construisant dynamiquement un graphe d'état représentant les exécutions possibles. Les deux méthodes réduisent de plusieurs ordres de magnitude le coût d'un test, et leur combinaison améliore encore les résultats. Malgré tout, le temps nécessaire à tester un application reste prohibitif pour des applications plus compexes. Nous proposons donc aussi des algorithmes générant des sous-ensembles d'ordonnancements de messages révélant les erreurs de synchronization avec une probabilité élevée.

Ces dernière années, MPI s'est imposé comme le standard *de facto* pour écrire des applications parallèles à mémoire distribuée. La dernière partie de cette thèse décrit donc l'adaptation des techniques décrites ci-dessus pour tester des applications MPI. Nous décrivons d'abord l'extension de nos résultats sur la visualisation de l'exécution d'applications parallèles. Nous discutons ensuite les limites et les bénéfices liés à l'utilisation de graphes d'ordonnancements partiels d'exécutions pour décrire l'exécution d'applications MPI, et montrons comment des

graphes d'états peuvent être construits dynamiquement.

**Mots-clés :** Applications parallèles à envoi de messages, prédiction de performance, message race, test, réduction partielle d'ordre, débogage, Dynamic Parallel Schedules, Message Passing Interface

## **Acknowledgments**

I would first like to thank my thesis advisor, Roger Hersch for his support and guidance, and for letting me choose my way. Having the opportunity to lecture and teach various courses, describing the lab's Visible Human project to young children or presenting parallel programming to Master students was something I particularly enjoyed.

I am also greatly indebted to Sebastian Gerlach, and not only because he wrote the DPS framework on which most of this thesis is built. In addition to being a living encyclopedia of all things technical, Sebastian is also an entertaining and passionate communicator. Sharing an office for three years with him therefore widely broadened and deepened my knowledge on many subjects.

Somewhat further on the EPFL campus, I had the pleasure of meeting Ralf Gruber and Vincent Keller, who introduced me to the "practical" side of HPC. They were instrumental in making me realize the existing gap between a large part of the research being performed on parallel computing and the actual problems faced by the users. If this thesis tries to throw a few ropes between these two sides, it is thanks to them.

I also had a great time with the former and current members of the lab, Emin Gabrielyan, Fabienne Allaire, Mathieu Brichon, Thomas Bugnon, Romain Rossier, Fabrice Rousselle, Mathieu Hébert, Isaac Amidror, and Maria Anitua. Smart and friendly people also exist outside of the LSP, and I was privileged to meet a few of them. Julien Pilet, Roman Schmidt, David Leroux, Ron Levy and Jean Berney, thanks to all of you. A special thank goes of course to my friend, former flatmate and passionate researcher Ruben Merz, who was always ready for a late hour chat.

I had the pleasure of supervising a few semester and Master projects. In order of appearance: Pascal Jermini, Pierre Dumas, Noël Jobé, Selim Arsever, Samuel Robyr, Ali Al-Shabibi and Mamy Fetiarison. Thank you for your ideas, energy and contributions.

Finally, I would not have reached this point without the support of my family and, last but not least, of Ochélio. You changed my life for the better.

## **Contents**

| Al | Abstract                                 |                |                                     |     |  |  |  |

|----|------------------------------------------|----------------|-------------------------------------|-----|--|--|--|

| R  | ésumé                                    | į              |                                     | iii |  |  |  |

| A  | cknov                                    | ledgme         | ents                                | vi  |  |  |  |

| 1  | Intr                                     | oductio        | on                                  | 1   |  |  |  |

|    | 1.1                                      | Motiva         | ations                              | 1   |  |  |  |

|    | 1.2                                      | Paralle        | el programming paradigms            | 2   |  |  |  |

|    | 1.3                                      | Scope          |                                     | 3   |  |  |  |

|    | 1.4                                      | Disser         | rtation outline                     | 4   |  |  |  |

|    | 1.5                                      | Contri         | ibutions                            | 5   |  |  |  |

| 2  | The Dynamic Parallel Schedules Framework |                |                                     |     |  |  |  |

|    | 2.1                                      | 1 Introduction |                                     |     |  |  |  |

|    | 2.2                                      | The flo        | ow graph                            | 8   |  |  |  |

|    |                                          | 2.2.1          | Basic Operation Types               | 8   |  |  |  |

|    |                                          | 2.2.2          | Flow Graph Composition              | 10  |  |  |  |

|    |                                          | 2.2.3          | Loops                               | 10  |  |  |  |

|    | 2.3                                      | Threac         | ds and thread collections           | 12  |  |  |  |

|    |                                          | 2.3.1          | Thread local storage                | 14  |  |  |  |

|    |                                          | 2.3.2          | Routing functions                   | 14  |  |  |  |

|    | 2.4                                      | A prac         | ctical example                      | 15  |  |  |  |

|    |                                          | 2.4.1          | Messages                            | 16  |  |  |  |

|    |                                          | 2.4.2          | Operations                          | 16  |  |  |  |

|    |                                          | 2.4.3          | Routing function                    | 19  |  |  |  |

|    |                                          | 2.4.4          | Building and running the flow graph | 19  |  |  |  |

|                  |     | 2.4.5   | Using local thread storage                 |

|------------------|-----|---------|--------------------------------------------|

|                  |     | 2.4.6   | Execution highlights                       |

|                  | 2.5 | Runtin  | ne behavior of parallel schedules          |

|                  |     | 2.5.1   | Message identifiers                        |

|                  |     | 2.5.2   | Execution model                            |

|                  | 2.6 | Split-n | nerge interactions                         |

|                  |     | 2.6.1   | Notify split and notify merge messages     |

|                  |     | 2.6.2   | Flow control                               |

|                  |     | 2.6.3   | Load balancing                             |

|                  | 2.7 | Seriali | zable objects                              |

|                  |     | 2.7.1   | Serializable objects                       |

|                  |     | 2.7.2   | Checkpointable threads                     |

|                  |     | 2.7.3   | Checkpointing operations                   |

|                  |     | 2.7.4   | Types of serialization                     |

|                  |     | 2.7.5   | Comparing serializable objects             |

|                  | 2.8 | Applic  | eation deployment                          |

|                  |     | 2.8.1   | Thread mapping                             |

|                  |     | 2.8.2   | TCP network layer                          |

|                  |     | 2.8.3   | MPI network layer                          |

|                  | 2.9 | Conclu  | asion                                      |

| 3                | Sim | ulation | and Performance Prediction 43              |

| 3.1 Introduction |     |         | action                                     |

|                  |     | 3.1.1   | The need for optimizations                 |

|                  |     | 3.1.2   | Related work                               |

|                  |     | 3.1.3   | Our approach                               |

|                  | 3.2 | Structu | are of the simulation system               |

|                  | 3.3 | The sin | mulator's system model and its assumptions |

|                  |     | 3.3.1   | Internal implementation                    |

|                  |     | 3.3.2   | Computing the network bandwidth allocation |

|                  | 3.4 | Practic | cal considerations                         |

|                  |     | 3.4.1   | Direct execution simulation                |

|                  |     | 3.4.2   | Partial direct execution simulation        |

|                  |     | 3.4.3   | Avoiding memory allocations                |

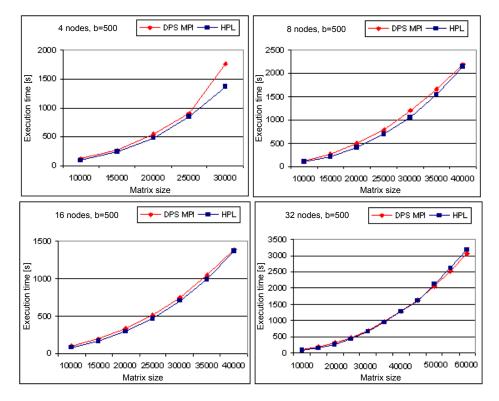

|   | 3.5  | First te                            | est application: LU factorization                                         |  |  |  |  |

|---|------|-------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

|   |      | 3.5.1                               | Implementation                                                            |  |  |  |  |

|   |      | 3.5.2                               | Variants                                                                  |  |  |  |  |

|   |      | 3.5.3                               | Validation                                                                |  |  |  |  |

|   | 3.6  | Second                              | d test application: Traveling Salesman                                    |  |  |  |  |

|   |      | 3.6.1                               | Implementation and validation                                             |  |  |  |  |

|   | 3.7  | Improv                              | ving simulation times and portability through partial direct execution 72 |  |  |  |  |

|   |      | 3.7.1                               | Preparing the LU application                                              |  |  |  |  |

|   |      | 3.7.2                               | Results                                                                   |  |  |  |  |

|   | 3.8  | Simula                              | ations for application analysis                                           |  |  |  |  |

|   |      | 3.8.1                               | Randomizing atomic steps durations                                        |  |  |  |  |

|   | 3.9  | Limita                              | tions and possible improvements                                           |  |  |  |  |

|   |      | 3.9.1                               | Internal DPS delays                                                       |  |  |  |  |

|   |      | 3.9.2                               | Clusters of heterogeneous computers                                       |  |  |  |  |

|   |      | 3.9.3                               | Multicores and accelerators                                               |  |  |  |  |

|   |      | 3.9.4                               | Network topologies                                                        |  |  |  |  |

|   |      | 3.9.5                               | Multi-application simulations                                             |  |  |  |  |

|   | 3.10 | Conclu                              | asions and future work                                                    |  |  |  |  |

| 4 | Mes  | Message Race and Deadlock Detection |                                                                           |  |  |  |  |

|   | 4.1  | Introdu                             | uction                                                                    |  |  |  |  |

|   |      | 4.1.1                               | Underlying concepts and assumptions                                       |  |  |  |  |

|   |      | 4.1.2                               | Related work                                                              |  |  |  |  |

|   | 4.2  | Synchi                              | ronization errors in DPS applications                                     |  |  |  |  |

|   | 4.3  | Interac                             | etive testing of DPS applications                                         |  |  |  |  |

|   |      | 4.3.1                               | Interaction between the debugger and the parallel application 93          |  |  |  |  |

|   |      | 4.3.2                               | Features and functionality                                                |  |  |  |  |

|   |      | 4.3.3                               | Influencing the application execution                                     |  |  |  |  |

|   |      | 4.3.4                               | Debugging example                                                         |  |  |  |  |

|   |      | 4.3.5                               | Scalability issues                                                        |  |  |  |  |

|   | 4.4  | Autom                               | nated testing through static decomposition                                |  |  |  |  |

|   |      | 4.4.1                               | Building a Partial Order Execution Graph                                  |  |  |  |  |

|   |      | 4.4.2                               | Partitioning the POEG                                                     |  |  |  |  |

|   |      | 4.4.3                               | Partial-Order Reductions                                                  |  |  |  |  |

|   |                                        | 4.4.4          | Generating a subset of possible orderings                    |

|---|----------------------------------------|----------------|--------------------------------------------------------------|

|   |                                        | 4.4.5          | Implementation                                               |

|   |                                        | 4.4.6          | Results                                                      |

|   |                                        | 4.4.7          | Limitations                                                  |

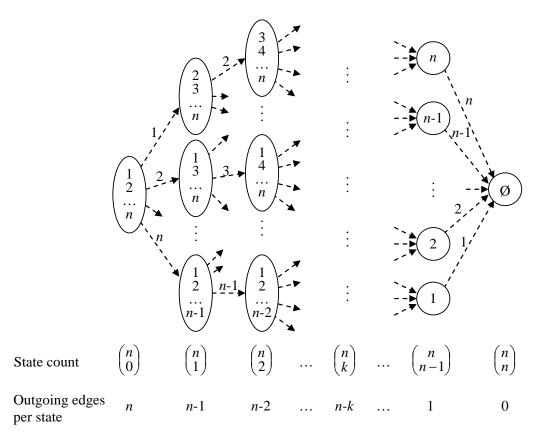

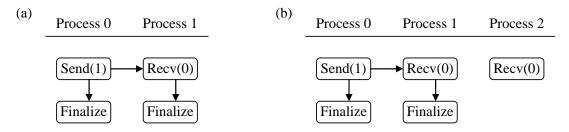

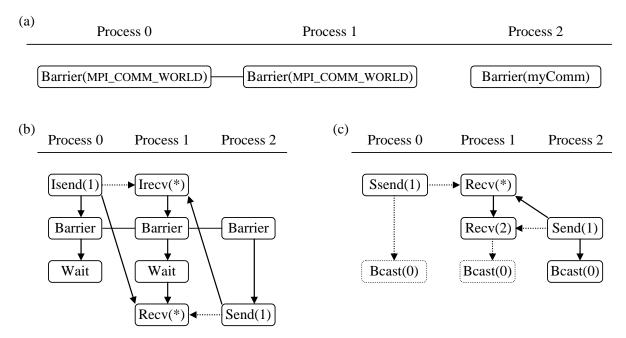

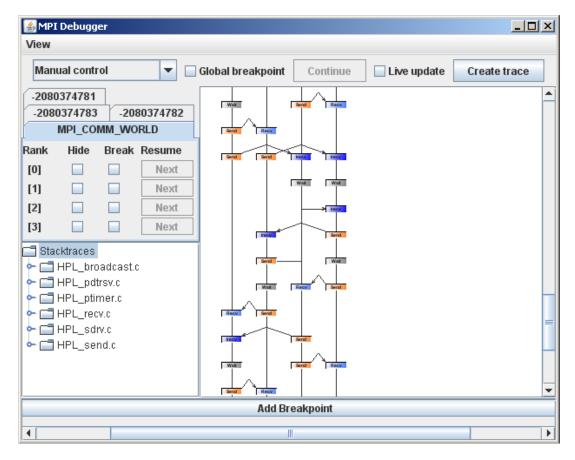

|   | 4.5                                    | Dynan          | nic testing                                                  |

|   |                                        | 4.5.1          | Reducing the number of visited states                        |

|   |                                        | 4.5.2          | Implementation                                               |

|   |                                        | 4.5.3          | Results                                                      |

|   |                                        | 4.5.4          | Scalability issues                                           |

|   |                                        | 4.5.5          | Testing a subset of orderings                                |

|   | 4.6                                    | Compa          | aring the automated testing approaches                       |

|   | 4.7                                    | Apply          | ing dynamic exploration to the static POEG decomposition     |

|   | 4.8                                    | Potent         | ial improvements                                             |

|   |                                        | 4.8.1          | Optimizing operation scheduling                              |

|   |                                        | 4.8.2          | Using checkpoints with manual testing                        |

|   |                                        | 4.8.3          | Combining execution visualization and POEG decomposition 133 |

|   |                                        | 4.8.4          | A note on non-deterministic computations                     |

|   | 4.9                                    | Conclu         | usion                                                        |

| 5 | Llain                                  | a MDI          | 137                                                          |

| 3 | 5.1                                    | ig MPI         | uction                                                       |

|   |                                        |                |                                                              |

|   | 5.2 MPI: the Message Passing Interface |                |                                                              |

|   |                                        | 5.2.1          | Point-to-point communications                                |

|   |                                        | 5.2.2          | Collective communications                                    |

|   |                                        | 5.2.3<br>5.2.4 | The MPI profiling interface                                  |

|   | 5.2                                    |                | Sending and receiving complex C++ objects                    |

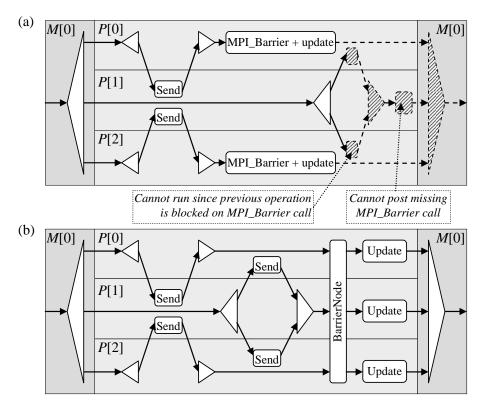

| • |                                        | •              | ronization errors in MPI applications                        |

|   | 5.4                                    |                | etive testing of MPI applications                            |

|   |                                        | 5.4.1          | Architecture                                                 |

|   |                                        | 5.4.2          | Controlling the application execution                        |

|   |                                        | 5.4.3          | Debugging example                                            |

|   |                                        | 5 1 1          | Immost an amiliations                                        |

|   |                                        | 5.4.4          | Impact on applications                                       |

|   |                                        | 5.4.5          | Impact on applications                                       |

|                                       | 5.5             | Autom     | ated error detection and testing of MPI applications                |     | 164 |  |

|---------------------------------------|-----------------|-----------|---------------------------------------------------------------------|-----|-----|--|

|                                       |                 | 5.5.1     | Detecting deadlocks in MPI programs                                 |     | 165 |  |

|                                       |                 | 5.5.2     | Partial-order execution graphs for wildcard-free MPI applications . |     | 170 |  |

|                                       |                 | 5.5.3     | Generalized partial-order execution graphs                          |     | 172 |  |

|                                       |                 | 5.5.4     | Detecting potential performance optimizations                       |     | 176 |  |

|                                       |                 | 5.5.5     | Applying message-passing state graphs to MPI applications           |     | 178 |  |

|                                       |                 | 5.5.6     | Related work                                                        |     | 181 |  |

|                                       | 5.6             | Conclu    | sion                                                                |     | 183 |  |

| 6                                     | Con             | clusion   |                                                                     |     | 185 |  |

| A                                     | Sim             | ulator to | ools                                                                |     | 189 |  |

|                                       | A.1             | Cluster   | parameterization                                                    |     | 189 |  |

|                                       | A.2             | Autom     | ated benchmarking                                                   |     | 190 |  |

|                                       |                 | A.2.1     | Collecting measurements                                             |     | 190 |  |

|                                       |                 | A.2.2     | Reusing measurements                                                |     | 190 |  |

|                                       | A.3             | Instrun   | nentation example                                                   |     | 191 |  |

|                                       |                 | A.3.1     | Avoiding memory allocations                                         |     | 193 |  |

| Aŗ                                    | pend            | ix        |                                                                     |     |     |  |

| В                                     | Auto            | oserial p | performance                                                         |     | 195 |  |

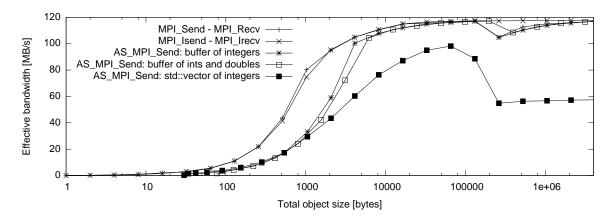

|                                       | B.1             | Experi    | ment                                                                |     | 195 |  |

|                                       | B.2             | Results   | 8                                                                   |     | 196 |  |

|                                       |                 | B.2.1     | AS_MPI_Send vs.MPI_Send                                             |     | 197 |  |

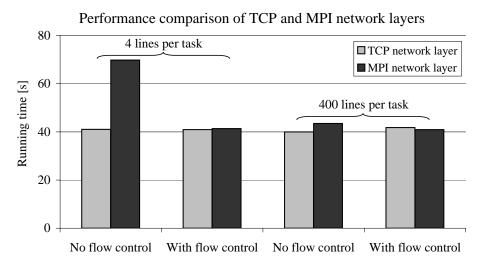

| C                                     | DPS             | over M    | PI                                                                  |     | 199 |  |

|                                       | C.1             | Introdu   | action                                                              |     | 199 |  |

|                                       | C.2             | Implen    | nentation overview                                                  |     | 199 |  |

|                                       | C.3             | Enablin   | ng new capabilities                                                 |     | 202 |  |

|                                       |                 | C.3.1     | Implementation examples                                             |     | 204 |  |

| Bibliography                          |                 |           |                                                                     |     | 207 |  |

| Lists of figures, tables and listings |                 |           |                                                                     | 220 |     |  |

| Cı                                    | Curriculum Vitæ |           |                                                                     |     |     |  |

"Tell us, if there were one thing we could do for your village, what would it be?"

"With all respect, Sahib, you have little to teach us in strength and toughness. And we don't envy you your restless spirits. Perhaps we are happier than you? But we would like our children to go to school. Of all the things you have, learning is the one we most desire for our children."

- Conversation between Sir Edmund Hillary and Urkien Sherpa, from Schoolhouse in the Clouds.

## **Chapter 1**

## Introduction

### 1.1 Motivations

Parallel computers are spreading through our everyday life. This change has been mostly driven by the dropping costs of computer hardware. While the first parallel machines were expensive and produced by a few specialized companies, falling costs of commodity hardware made processing power affordable to smaller institutions and companies, and broadened the range of scientific disciplines that could take advantage of it. Some of the newcomers in the area of scientific computing such as life sciences and biology have become heavy users and now contribute to the stride towards more powerful computers.

More recently, processor manufacturers stopped aiming for ever higher clock rates. The performance increase is now mainly coming from adding multiple processing units within a single processor chip. These *multicore* processors are now present in nearly every new desktop and laptop computer. This shift has a strong impact on the program developers, who can no longer assume that their sequential programs will automatically run faster on the next hardware generation. Rather, clock frequencies are reduced to avoid heat dissipation issues caused by densely packed cores. The performance of individual cores therefore tends to decrease, and codes must be parallelized in order to take advantage of the additional processing units.

A third push toward a wider use of parallel processing may come from the raising prices of energy. The Green500 project (green500.org [102]) was specifically started to rank supercomputers taking their total electrical power consumption into account. The list ranks systems according to the number of floating-point operations performed per second for every unit of energy consumed (MFLOPS/Watt ratio [102]). It illustrates the benefits of swapping a few

high-frequency processors by many lower frequency ones: among the most power efficient systems, IBM's BlueGene/P systems [52] contain densely packed processors clocked at only 850 MHz.

These developments imply that an increasing number of developers are being exposed to parallel programming. As with any technology, the average level of expertise of its users decreases as the popularity of the technology increases. It is therefore crucial to provide easy to use tools to help developers write efficient and correct parallel applications.

## 1.2 Parallel programming paradigms

Modern operating systems provide two levels of concurrent tasks execution: *processes* and *threads*. A *process* has access to a private address space, and cannot read or modify the address space of another process. This segregation is enforced by the operating system. Within a single process, a developer may use *threads* to perform concurrent computations. Multiple threads share a single address space<sup>1</sup>. These two concepts provide different parallelization paradigms.

In *shared memory*, *multithreaded* applications, a single process uses multiple threads. These threads share information by reading and writing common memory locations. This paradigm, once reserved for expensive multiprocessor machines such as the SGI Altix, is gaining in popularity due to multicore processors and to the availability of standardized APIs. POSIX threads [82] provide a portable interface for creating and managing threads on all major operating systems. OpenMP [12] is a more recent industry standard developed for facilitating the development of shared memory parallel scientific applications. Unlike POSIX threads, OpenMP frees the developer from managing the creation and destruction of threads, and provides easy to use and high-level synchronization functions. However, it mostly provides parallel for loops and therefore cannot implement arbitrary parallelization patterns.

In *distributed memory*, *message-passing* applications, multiple processes exchange data by sending messages to each other. The message-passing model has several advantages that explain its popularity for writing scientific applications. Firstly, multiple processes can run on a single multicore machine as well as on multiple machines. The same application can therefore run on a wider range of hardware. The same paradigm can be used whether messages are sent over a network or using shared memory. Secondly, message-passing applications enable the

<sup>&</sup>lt;sup>1</sup>The terms of *heavy* and *light* threads are sometimes found in the literature. Some operating systems may also have more subtle mechanisms for sharing memory between processes. Nevertheless, these definitions are broadly accepted and are sufficient for our purpose.

SCOPE 3

developer to better control the distribution of the data among the participating processes. He may thus ensure that each piece of data is stored close to the process that uses it, which is beneficial to the application performance.

The current *de facto* standard for writing message-passing parallel applications is MPI (Message-Passing Interface [77]). MPI provides a portable interface for sending and receiving messages that abstracts the details of the underlying operating system and networking layer.

The shared and distributed memory parallel programming models are not mutually exclusive. For example, the availability of multicore processors makes the combination of OpenMP and MPI more common: MPI handles the inter-node parallelism, while OpenMP is used for intra-node parallelism.

The work presented in this thesis only considers distributed, message-passing parallel applications. Most of it relies on the Dynamic Parallel Schedules (DPS) parallelization library, which was developed at EPFL. Its distinguishing feature is the use of a *flow graph* to describe the application parallelism. This representation enables the DPS runtime to provide a number of features that would need to be implemented manually under MPI. The flow graph also provides a graphical representation that makes it easier to understand parallel programs and to communicate among developers.

## 1.3 Scope

While many problems can be parallelized easily in principle, naive parallelizations often have poor performance. The challenge is therefore to write parallel programs that efficiently use the available processing units. Among the factors that improve that efficiency are the choice of an appropriate problem decomposition granularity to minimize the amount of communications between processes, the overlap of the remaining communications with computations, and the reduction in the number of synchronizations between processes. Indeed, synchronizing a set of processes requires these processes to wait for the slowest process in the set. Synchronizations become increasingly prohibitive as the number of processes involved grows.

On the other hand, optimized implementations are complex and error prone. For instance, removing too many synchronizations may lead to errors that are specific to parallel applications: deadlocks occur when conflicts over the use of resources prevent one or several processes from moving forward, and message races occur when changes in the delivery order of messages change the computation outcome. Such errors are particularly difficult to foresee *a priori*, and to understand *a posteriori*. They are sometimes called *heisenbugs*: trying to study them

changes the ordering of events in the application and makes the bugs disappear. Their transient nature, due to their appearance in specific and rare circumstances, adds an additional difficulty.

Application developers must therefore satisfy two objectives: produce parallel programs that are both efficient and correct. In this thesis, we present solutions for both sides of the problem. Simulation and performance prediction capabilities help identifying and setting the parameters leading to a good performance, and testing tools automatically detect potential synchronization errors.

One of the main considerations that guided the present work was the ease of use of the proposed solutions. In addition to the rising number of programmers exposed to parallel programming, many of the current computational science application developers do not have a computer science background. Rather, they are for instance chemists, physicists, biologists or mechanical engineers. All these users often prefer to focus on their main field of interest instead of spending time optimizing and testing code. For them, ease of use is a key element for the acceptance and use of tools facilitating the development of parallel applications.

### 1.4 Dissertation outline

We begin by describing the Dynamic Parallel Schedules parallelization framework. Chapter 2 presents the elements of DPS needed for understanding the subsequent chapters, and describes a few extensions implemented during the course of this thesis.

Chapter 3 then discusses the integration of simulation capabilities within the DPS framework, which can be used for any DPS application. We propose a partial direct execution technique that prevents the need to use a parallel machine to run simulations and at the same time reduces the running time and memory consumption of simulations.

Testing the application for the absence of deadlocks and message races requires executing an application in many different configurations. Unfortunately, the number of possible executions explodes as the size and complexity of the application grows. In Chapter 4, we describe methods that greatly reduce the number of tests needed to exhaustively cover all possible executions and detect existing errors. For cases where the testing costs remain prohibitive, we present heuristics that test a subset of executions that are likely to produce errors.

The following chapter, Chapter 5, briefly describes the Message Passing Interface (MPI) standard, which is the most popular API for writing distributed memory parallel applications. We then show how the testing techniques developed in the context of DPS in Chapter 4 can be adapted to MPI applications.

CONTRIBUTIONS 5

Finally, Chapter 6 summarizes our results and the possible paths for future research.

### 1.5 Contributions

The detailed list of contributions is as follows:

• We present an efficient simulation framework for predicting the performance of adaptive parallel applications.

- We describe a simple parameterization of cluster hardware that enables accurate prediction of parallel application running times on clusters of single-processor nodes.

- For parallel applications that can be described using a static Partial-Order Execution Graph, we propose an efficient decomposition algorithm for reducing the number of ordering to be tested for detecting races within DPS applications.

- We describe a dynamic approach for testing parallel applications whose dependencies cannot be statically expressed.

- These two approaches provide a significant reduction in number of orderings to be tested. However, their scalability is limited with respect to the increase in the number of nodes and in the communication complexity. We therefore describe heuristics that test a subset of possible orderings that have a high probability of producing existing message races.

- We generalize the use of the Partial-Order Execution Graph and of the dynamic testing approach to detect message races within MPI parallel applications.

- For both DPS and MPI applications, we describe debuggers that provide a graphical representation of the execution. In both cases, the tools have the ability to reorder events in order to test for the presence of message races.

## **Chapter 2**

# The Dynamic Parallel Schedules Framework

### 2.1 Introduction

The Dynamic Parallel Schedules (DPS) framework is a high-level framework for developing distributed memory parallel applications on clusters of workstations. It has been developed at the Peripheral Systems Laboratory of the Ecole Polytechnique Fédérale de Lausanne (EPFL). While its general concepts were developed in the late 90's, its implementation reached its final form in 2005. The various incarnations of DPS have been used to teach parallel programming to Master students, who have successfully compiled and run their parallel applications on a wide range of compilers, operating systems and hardware platforms. DPS therefore provides a stable and cross-platform library for writing parallel applications.

An application using DPS is expressed as a directed acyclic graph of sequential operations, called a *flow graph*. Individual operations are fully customizable, and sections of distinct flow graphs can be composed together, enabling the reuse of existing code. The graphs and the mapping of operations to processing nodes are specified dynamically at runtime. DPS applications are pipelined and multithreaded by construction, ensuring a maximal overlap of computations and communications.

This chapter presents the concepts and features of DPS that are required to fully understand the topics presented in the following chapters. In particular, it leaves out many practical implementation details about how to write DPS applications. This information can be found on the DPS website [37], which provides tutorials, sample code and the API documentation. We

also do not detail the internal implementation of the framework, and ignore several advanced features offered by DPS. These can be read in [35].

### 2.2 The flow graph

DPS applications are described by their *flow graph*. The nodes on the graph are the operations that are executed. Its edges specify how messages may flow from one operation to the next, thereby describing the admissible sequences of operations. Each operation in the graph takes one or several message as input, and produces one or several messages as output.

The flow graph only specifies the dependencies between the various operations that compose an application, and not the actual application deployment. The allocation of operations onto processing nodes will be described in Section 2.8.

### 2.2.1 Basic Operation Types

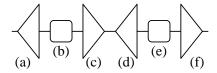

DPS provides four basic operation types, which differ in the number of messages that they may receive or send. The basic operations are the following:

- *Split* operations take exactly one message as input, and can produce any number of messages as output. At least one message must be sent to avoid halting the data flow in the flow graph. Outputs typically represent subtasks that may be performed in parallel.

- *Leaf* operations take exactly one message as input, and produce exactly one message as output. They are typically used to perform computations using data provided in the input message, and send the results within the output message.

- *Merge* operations take any number of messages as input, and produce exactly one message as output once all messages have been received. These operations are used to merge partial results into a single result. In a flow graph, every merge operation must match a single split operation. The number of input messages of a merge corresponds to the number of messages sent by the matching split operation.

- *Stream* operations combine the functionalities of a merge and a split operation by allowing any number of both input and output messages. Every stream must therefore match a split or another stream operation that precedes it in the flow graph, as well as a successor merge or stream operation.

THE FLOW GRAPH 9

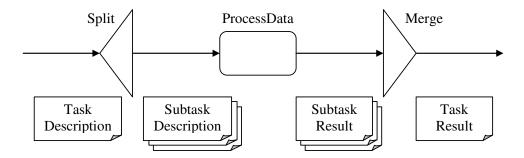

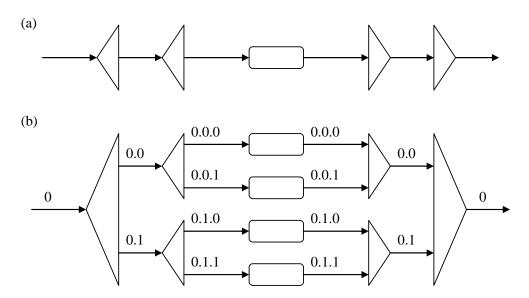

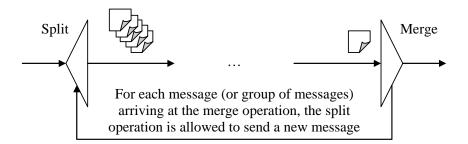

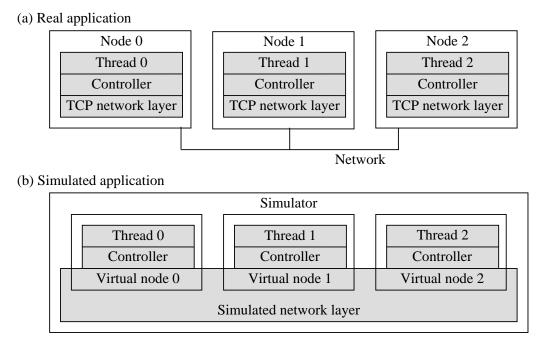

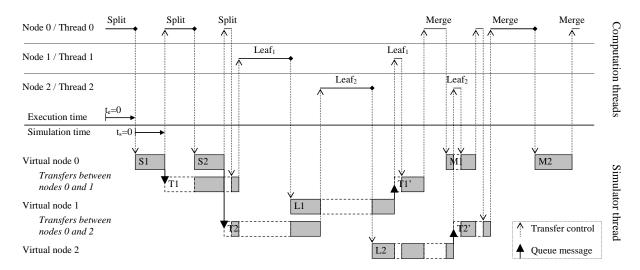

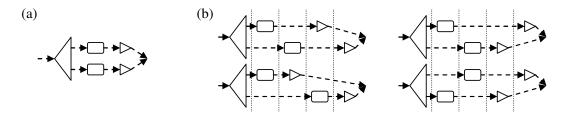

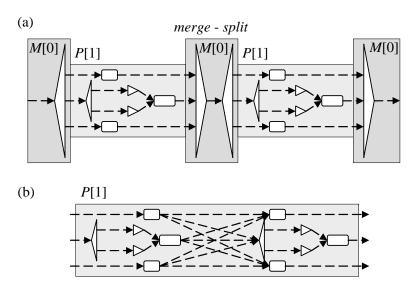

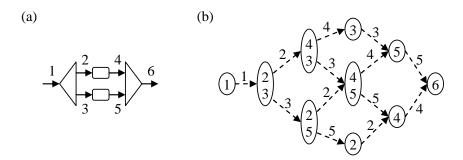

**Figure 2.1:** A simple parallel application using a split-leaf-merge flow graph.

In order to build a parallel application, a developer writes custom operations of the desired type and composes them into a flow graph. Figure 2.1 displays the basic building block of parallel applications written using DPS. The split-leaf-merge construct forms a simple flow graph suitable for many types of embarrassingly parallel applications. The split and merge operations contain customized code to control exactly how the work and the data is distributed in subtasks, and how the computed sub-results are combined into the final output result. The code of the leaf operation processes the output messages of the split operation and sends a message to the merge operation.

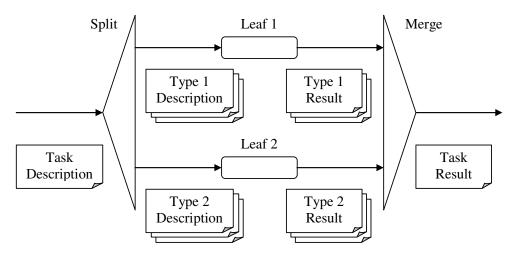

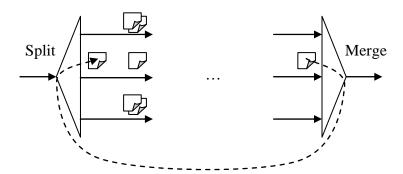

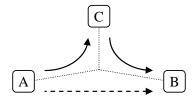

The basic split-leaf-merge construct may have multiple parallel branches when different outputs of a single split or stream operation are processed by different operations, as shown in Figure 2.2.

**Figure 2.2:** Parallel branches enclosed by a split and a merge operation pair. The two branches perform different functions.

### 2.2.2 Flow Graph Composition

Operations may be composed together provided that every split operation is matched by a single merge operation. Since streams combine the functionality of both splits and merges, the left side of a stream must match a split or another stream, and its right side must match a merge or another stream.

From the perspective of the flow graph, a sequence of two leaf operations is equivalent to a single leaf operation, since for each input message, there is exactly one output message. This equivalence property also applies to the simple split-leaf-merge block: for every input of the split operation, the matching merge produces exactly one output message.

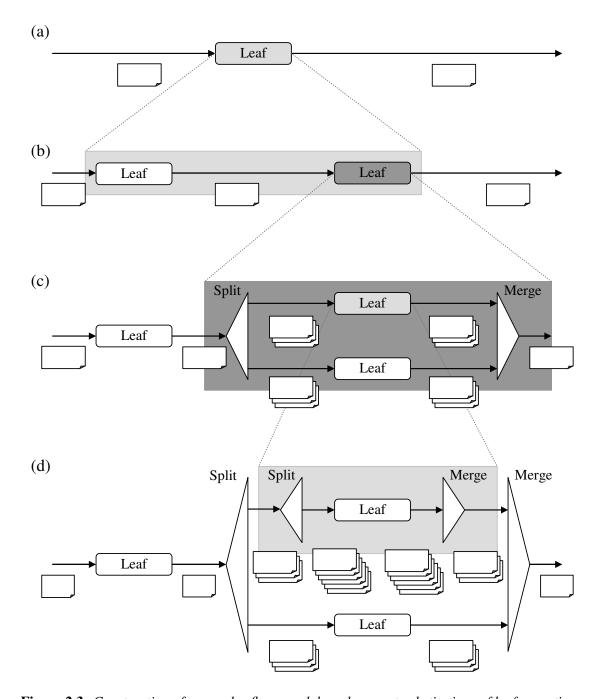

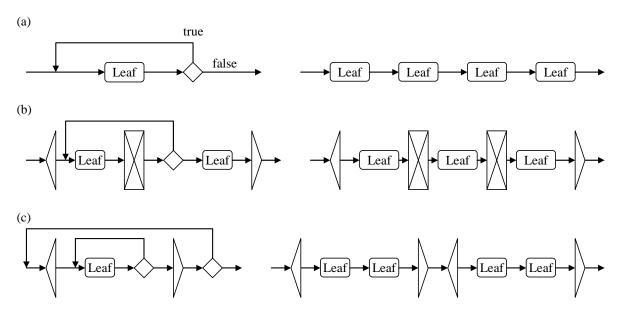

Admissible flow graphs may therefore be built by substituting leaf operations by sequences of leafs or by split-leaf-merge blocks. Starting from a single leaf operation, one may produce flow graphs of arbitrary complexity by iteratively performing operation substitutions (Figure 2.3).

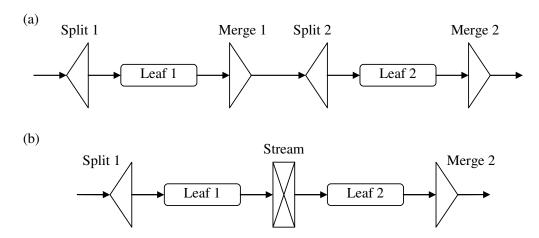

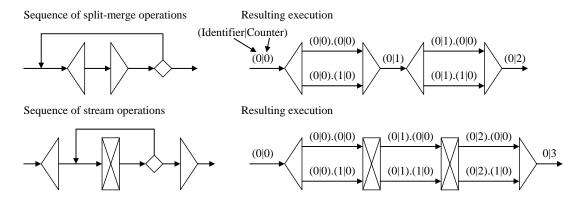

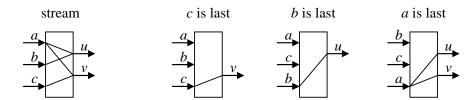

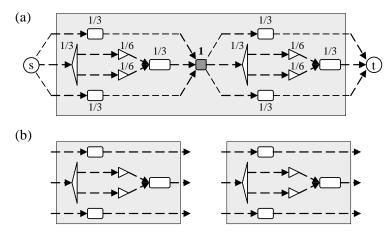

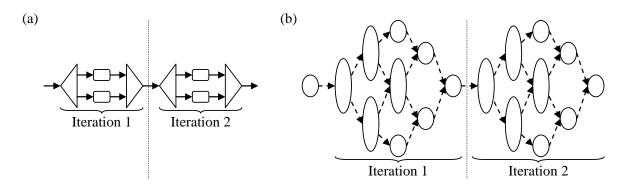

Multiple computations steps can be performed by using consecutive split-leaf-merge sequences, as illustrated in Figure 2.4a. Since the merge operation does not send any message before all incoming messages have been received, it guarantees that all previous computations are over before starting the next operation in the flow graph. In some cases however, this synchronization model is too strict and negatively impacts the application performance. This happens when not all the results of the computations preceding the merge are required in order to perform parts of subsequent computations. In these cases, it is desirable to already split out these parts of the second computation before the first computation is complete in order to ensure proper pipelining of the application. The stream operation was designed to accomplish this objective, by combining the functionality of a merge operation and a split operation in a single operation. The stream operation can output data objects at any time within the merge process. From the perspective of the flow graph, any merge-split sequence can be replaced by a stream operation, as illustrated in Figure 2.4b.

### 2.2.3 **Loops**

The actual number of messages sent by a split or stream operation depends on the implementation of the operation, and is therefore known only during the execution of the flow graph. However, the flow graph itself cannot be modified once its execution started. Although flow graphs of arbitrary lengths can be created statically, in many cases applications do not know in advance how many operations will have to be executed. For instance, iterative linear solvers

THE FLOW GRAPH 11

**Figure 2.3:** Construction of a complex flow graph by subsequent substitutions of leaf operations.

**Figure 2.4:** (a) Two computations with intermediate barrier synchronization, and (b) relaxed synchronization using a stream operation

iteratively compute an approximate solution x' of a linear system Ax = b. Each iteration improves the approximation of the solution and the execution stops once the approximation error ||Ax' - b|| is smaller than some predefined  $\epsilon$ . In such cases, the number of iterations to be performed cannot be determined a priori given A.

Within a flow graph, this type of execution pattern can be expressed using a loop, a specialized type of operation that encloses any sequence of operations and evaluates a condition on the output message of the last operation of the sequence. As long as the condition is true, the encapsulated sequence of operations is executed again on the output message.

The loop operation does not create a cycle within the flow graph; it produces a pipelined sequence of operations, the length of which is determined at runtime based on the loop condition. Flow graphs are therefore always acyclic, since none of the allowed patterns enables the construction of cycles. The acyclic property ensures that unless an operation does not generate any output message an execution is always free of deadlocks.

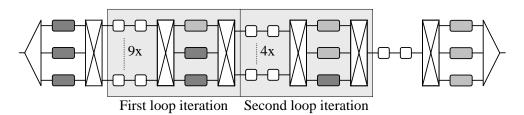

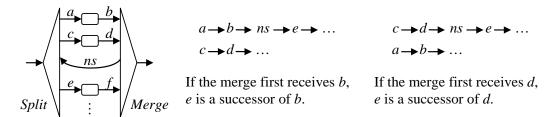

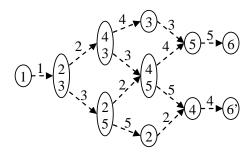

Figure 2.5 illustrates some flow graph constructions that can be achieved using loop constructs. When inserting loop constructs, the only constraint is to ensure that the flow graph preserves the symmetry between split and merge operations: for each split operation within the flow graph, a corresponding merge operation needs to exist within the flow graph.

### 2.3 Threads and thread collections

Flow graphs provide a simple and efficient mechanism for describing program flow. We now need to indicate in which context the various operations on the flow graph should be executed.

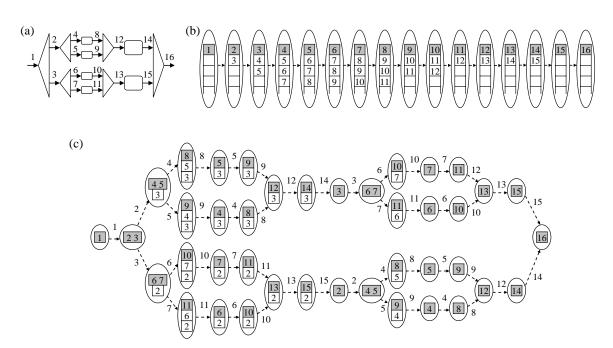

**Figure 2.5:** Left: examples of use of the loop construct; right: resulting runtime flow graph. (a) Loop around a leaf operation, returns false at fourth iteration; (b) deep pipeline using stream operations, loop returns false at second iteration; (c) nested loops, both return false at second iteration.

Operations are assigned to *threads* that are mapped onto the processing nodes. A thread within the parallel schedules concept provides a context within which operations can be executed. A thread executes only one operation at a time. The threads are grouped within *thread collections*. Multiple threads (whether from the same or from different thread collections) may be mapped onto the same compute node, in which case they execute operations concurrently and independently of each other.

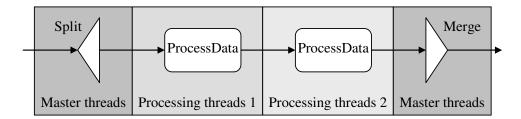

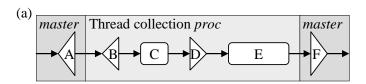

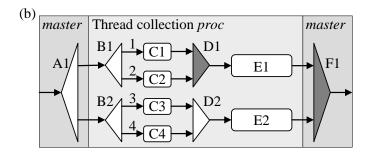

Each operation within the flow graph must be attached to one thread collection. A single thread collection may support multiple operations. Let us for instance consider a simple compute farm application, where a master node distributes tasks to a set of processing nodes, and later collects the results of the processing. For such an application, two thread collections would be created. The first is used for all the master tasks, and we attach the split and merge operations to it. The second thread collection is used for all the processing tasks, and runs the leaf operations. Figure 2.6 displays an example where the same operation is executed twice in a pipeline, and each operation runs on a different collection of threads. In this example, the master thread collection would contain only a single thread, whereas processing thread collections would typically contain one thread for each participating CPU.

The thread collections provide a logical description of the execution environment of the application. Their assignment to operations is invariant for a given flow graph. On the other hand, the actual number of threads within a thread collection, as well as the their distribution

**Figure 2.6:** Assignment of thread collections to operations within the flow graph. The ProcessData operation is executed twice in a pipeline on two different thread collections.

onto compute nodes, can be chosen arbitrarily at runtime and may potentially change during the parallel schedule execution (Section 2.8.1).

### 2.3.1 Thread local storage

Parallel schedule threads can provide local storage to the operations that execute within their context. The storage is provided as an instance of a user-defined data structure. The *type* of storage is the same for all threads of a same thread collection. However, the *storage* itself is specific to individual threads, and two threads of the same type located on the same processing node cannot access each other's data.

This local storage is preserved within the thread state, and persists from one operation to the next. Data-parallel applications can use this thread local storage to store distributed data structures. For example, an application performing matrix computations could store matrix blocks within its threads.

Since local storage provides a private memory location to each thread, the programming model of DPS can be seen as being strictly distributed memory, even though multiple operations may be executing simultaneously in the same process<sup>1</sup>.

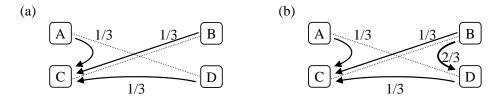

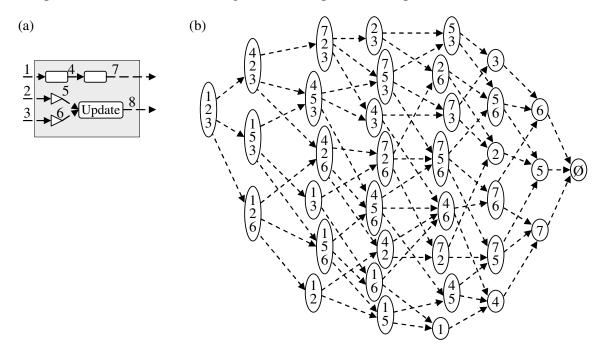

### 2.3.2 Routing functions

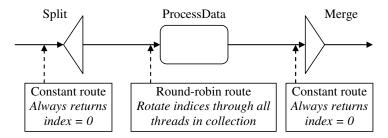

When an operation outputs a message, the DPS runtime identifies the recipient operation and therefore the destination thread collection using information from the flow graph. However, it must still determine which thread within the collection should be used as the execution context for running the operation.

In the data-driven computation model of DPS, the destination thread of each message is

<sup>&</sup>lt;sup>1</sup>Developers may technically use global variables to share information between threads. This practice is however discouraged, among other reasons because it prevents threads from migrating between processes (Section 2.8.1).

A PRACTICAL EXAMPLE 15

computed using a routing function. Routing functions are attached to operations during the construction of the flow graph, and are applied to each one of their input messages. Since a routing function may access the content of messages to determine their destination, its behavior is very flexible: it can provide simple mechanisms such as constant routing or round-robin routing, data-dependent routing using the message content, or even automatic load-balancing (Section 2.6.3).

**Figure 2.7:** Routing functions are attached to operations, and are used to compute the destination thread of incoming messages.

## 2.4 A practical example

The previous sections described the basic concepts of DPS. We now present the implementation of a simple parallel application so as to provide a better understanding of the behavior of DPS applications. This section illustrates only the most important elements presented so far, and we refer the interested reader to the documentation provided on the DPS website [37] for further information.

All the elements that compose flow graphs such as operations or routing functions are implemented as C++ classes. These statically defined components are assembled at any time during execution to build one or several flow graphs. A same component may be used multiple times within a single flow graphs and can be reused in multiple flow graphs. A same flow graph can then be used to spawn multiple parallel schedules.

The chosen example is a basic parallel merge sort application. The parallelization is expressed using a split-leaf-merge flow graph similar to the one displayed in Figure 2.1. First, the *SplitVector* operation receives a vector of integers as input, and splits it into subvectors containing 100 elements. The leaf operation, *Sort*, then receives a subvector and sorts it. The *MergeVector* then aggregates all the sorted subvectors into a single sorted vector. The implementation focuses on brevity rather than on performance, enabling the complete source code to be provided.

### 2.4.1 Messages

The messages transiting through the flow graph are also C++ objects. Our merge sort application uses only a single type of message. The message contains two fields, a vector provided by the C++ standard library that contains the data to be sorted, and an integer to be used by the routing function to determine the destination thread of the message.

The C++ language provides no reflection and serialization capabilities. DPS therefore provides its own mechanism that is able to automatically serialize regular C++ objects. It requires only a few macros to be added by the application developer, and will be described in more details in Section 2.7. Listing 2.1 displays the declaration of a serializable *VectorData* class that contains the required members: one integer, *target*, to be used by the routing function and one standard library vector, *v*, to store the data.

Listing 2.1: Serializable object declaration

```

#include <dps/dps.h>

3 class VectorData : public dps::AutoSerial

4

CLASSDEF (VectorData)

// Class name

5

MEMBERS

6

7

8

CLASSEND;

11 public:

// Default constructor

12

VectorData() { target = 0; }

13

14 };

```

### 2.4.2 Operations

Operations constitute the nodes of the flow graph, and encapsulate all of the application's functionality. Within DPS, all operation types (leaf, split, merge and stream) share a common syntax and programming model. The body of an operation is composed of standard sequential C++ code that performs the operation's tasks. Operations are further characterized by two additional parameters specifying the type of input messages and the type of output messages.

Listing 2.2 shows the code of the *SplitVector* operation. The type (split, merge, leaf, stream) of each operation is determined by its base class. The *SplitVector* class derives from the *dps::SplitOperation* class, and specifies the types of the input and output messages as tem-

A PRACTICAL EXAMPLE 17

**Listing 2.2:** Declaration of SplitVector operation

```

// Splits input vector into 100 element subvectors

class SplitVector

: public dps::SplitOperation<VectorData, VectorData>

17

18

IDENTIFY(SplitVector)

19

public:

20

21

void execute(VectorData *in)

22

int counter = 0;

23

std::vector<int>::const_iterator it = in->v.begin();

24

while(it != in->v.end())

25

26

VectorData *out = new VectorData();

27

out->target=counter;

28

for(int i=0; i<100 && it!=in->v.end(); ++i)

29

out->v.push_back(*it++);

30

postDataObject(out);

31

counter++;

32

33

}

}

34

};

35

```

plate parameters<sup>2</sup> (line 17). An *IDENTIFY* macro adds code that registers the type of the object within a *class factory* in the DPS library. When a message arrives, the DPS runtime is therefore able to instantiate the operation that will process the message.

The entry point of an operation is its *execute* method, which takes the received message as a parameter. The developer must provide his own code to process the incoming message and create and send new messages. In our example, the *SplitVector::execute* method creates new messages containing 100 elements from the original vector. The local variable *counter* keeps track of the number of messages already created and is used to set the *target* field (line 28), thereby numbering every message. Once a message is instantiated and initialized, it is sent to the next operation using the *postDataObject* method. Once all messages have been sent, the *execute* method returns and the operation terminates.

The leaf operation *Sort* is created in the same fashion (Listing 2.3). It derives from the *dps::LeafOperation* base class and specifies *VectorData* as the type of its input and output messages (line 38). Its *execute* method first creates a copy of the input message. It then sorts the vector of the message copy, and sends it.

The MergeVector operation (Listing 2.4) derives from the dps::MergeOperation base class.

<sup>&</sup>lt;sup>2</sup>Multiple input and output types can be specified using type vectors [37].

### **Listing 2.3:** *Declaration of* Sort *operation*

```

// Sort subvector

class Sort

: public dps::LeafOperation<VectorData, VectorData>

38

39

IDENTIFY(Sort);

40

41

public:

void execute (VectorData *in)

42

43

VectorData *vd = new VectorData(*in); // Copy message

44

std::sort(vd->v.begin(), vd->v.end()); // Sort vector

45

// Send result

postDataObject(vd);

46

}

47

} ;

48

```

#### **Listing 2.4:** Declaration of MergeVector operation

```

// Merge parts back

class MergeVector

50

: public dps::MergeOperation<VectorData, VectorData>

51

52

IDENTIFY (MergeVector)

53

public:

54

void execute(VectorData *in)

55

56

VectorData *out = new VectorData();

57

do

58

{

59

std::vector<int> tmp;

60

tmp.swap(out->v); // Exchange content of tmp and out->v

std::vector<int>::const_iterator it1 = in->v.begin(),

62

it2 = tmp.begin();

63

while (it1!=in->v.end() || it2!=tmp.end())

64

65

if (((*it1)<(*it2) && (it1!=in->v.end()))

66

| | it2 = tmp.end())

67

out->v.push_back(*it1++);

68

else

69

out->v.push back(*it2++);

70

}

71

72

while((in=(VectorData*)waitForNextDataObject()) != NULL);

73

postDataObject(out);

75

76

}

77

} ;

```

A PRACTICAL EXAMPLE 19

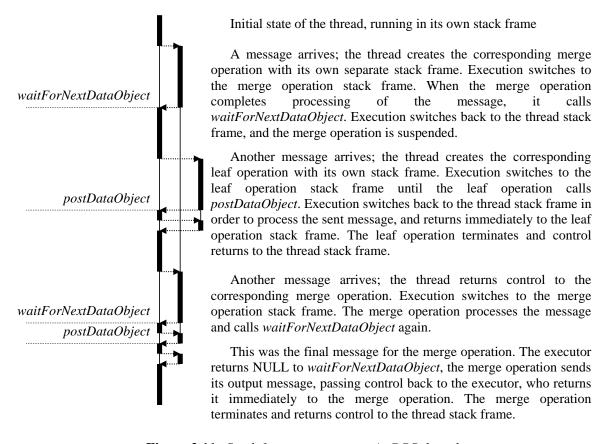

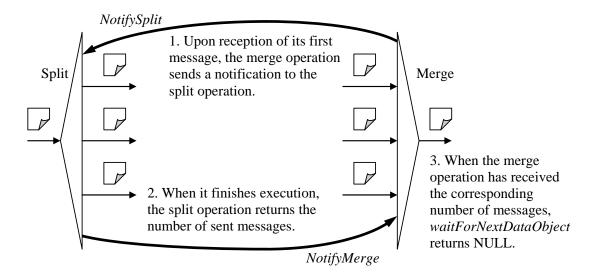

The operation starts by creating the output message into which sorted subvectors will be merged. While the first message is received as a parameter of the *execute* operation, subsequent messages are received by calling the *waitForNextDataObject* method (line 73). Calling this method suspends the execution of the operation until the next message arrives. For each input message, we create a temporary *tmp* vector to store the elements already accumulated in the output message (line 61; following the swap, *out->v* is empty and *tmp* contains the values previously in *out->v*). The content of *tmp* and of the input message *in* are then merged into the output message. When all messages have been received, *waitForNextDataObject* returns *NULL*, and the operation sends its output message (line 75).

## 2.4.3 Routing function

The routing functions used to determine the destination thread of messages are also defined as C++ classes. They derive from the *dps::Route* base class, and specify the type of routed messages as a template parameter. The message to be routed is delivered as a parameter of the *route* member function, which is responsible for computing the index of the destination thread of the message. The body of that function may do so using any computations, possibly using member variables of the routed message. In our case, we use the *target* field modulo the number of threads in the thread collection to which the next operation is attached (Listing 2.5).

**Listing 2.5:** Routing function declaration

```

// Routing function

class TargetRoute : public dps::Route<VectorData>

{

IDENTIFY(TargetRoute)

public:

Size route(VectorData *in)

{

return in->target%threadCount();

}

};

```

## 2.4.4 Building and running the flow graph

The building blocks of our merge sort application have now been declared. In order to build a flow graph and execute a parallel schedule, we must define an application class that derives from *dps::Application*. The main method within that class is *start*, and parallel schedules must be started from within that method.

**Listing 2.6:** Build and execute flow graph

```

//! Application class

class MergeSortApp : public dps::Application

IDENTIFY (MergeSortApp)

91

public:

92

//! Startup function

93

virtual void start()

94

95

// Create thread collections

96

dps::StatelessThreadCollection mainThreads =

97

getController()->createStatelessThreadCollection("main");

dps::StatelessThreadCollection processThreads =

99

getController()->createStatelessThreadCollection("process");

100

// Create threads on processing nodes

102

mainThreads.addThread("host1");

103

processThreads.addThread("host1 host2 host3");

104

// Declare flow graph nodes with operation, routing function,

// and thread collection

107

dps::FlowgraphNode<SplitVector, TargetRoute> split(mainThreads);

108

dps::FlowgraphNode<Sort, TargetRoute> sort(processThreads);

109

dps::FlowgraphNode<MergeVector, TargetRoute> merge(mainThreads);

110

// Build flow graph

112

dps::FlowgraphBuilder builder = split >> sort >> merge;

113

dps::Flowgraph sortGraph =

getController()->createFlowgraph("mergeSortGraph", builder);

115

// Create initial message with 10000 random elements

117

VectorData *in = new VectorData();

118

for (int i=0; i<10000; ++i)</pre>

119

in->v.push_back(rand()%10000);

120

// Execute parallel schedule

VectorData *result =

123

(VectorData*)getController()->callSchedule(sortGraph, in);

124

// 'result' is the output message of the MergeVector

126

// operation and contains the sorted vector

127

delete result;

130

131

} ;

```

A PRACTICAL EXAMPLE 21

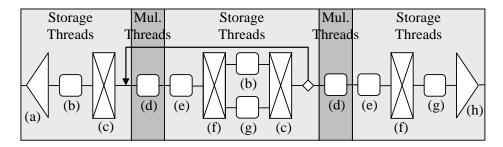

We first create the thread collections onto which the flow graph will execute. In our case, we create stateless thread collections, i.e. collections where threads have no attached local storage (lines 97–100). We then add threads to each collection using their *addThread* member function. The parameter is a string that typically contains the hostnames or IP addresses of the processing nodes onto which the application will execute.

The flow graph is built by combining *flow graph nodes*. Constructing a flow graph node requires three parameters. The first two specify the type of the operation and the type of the routing function used to route the input messages of the operation, and appear as template parameters. The thread collection providing the execution context to the operation is specified as a constructor parameter (lines 108–110). DPS performs type validation in order to ensure that the operations will be executed on threads of the appropriate type, and that the routing functions use the correct message type in order to select the target threads. However, operations that do not perform any processing on a locally stored thread state can be attached to a thread collection containing threads of any type.

The flow graph nodes may then be connected to each other to form a flow graph (line 113). The resulting sequence of operations is validated at compile time to ensure that the input type of an operation matches the output type of the preceding operation. Once the flow graph has been built, a parallel schedule can be started with the *callSchedule* method. The two parameters indicate the flow graph to be started, as well as its input message, i.e. the message that will be delivered to the first operation of the flow graph (line 124).

Finally, one must instantiate and start the application itself. The application object is instantiated explicitly by the developer and may therefore be set up as needed. The *dps::dpsMain* function then takes care of initializing internal data structures of the DPS runtime, and calls the application *start* method. This is done in Listing 2.7 at line 135.

Listing 2.7: Start application

```

//! Starts up application

int main(int argc, char *argv[])

134 {

135    return dps::dpsMain(argc, argv, new MergeSortApp());

136 }

```

## 2.4.5 Using local thread storage

Local thread states are expressed as standard C++ classes, and may therefore contain any number of fields to store data. While operations are destroyed after execution, threads are created once. They therefore preserve their variables, which can be used by multiple operations that run on the same thread. Such variables may be initialized by adding a constructor without any parameters to the thread state class. This constructor is called when the thread is created by DPS. Within an operation, the local storage can then be accessed by calling the *getThread* member function.

Let us assume that the *Sort* operation wants to store the sorted vector for future use. One would first need to declare a class able to store the vector (Listing 2.8). We must then add a template parameter to the *Sort* operation that indicates the type of thread it has access to (line 9). The operation may then access the local thread state via the *getThread* method (line 18). The type of the thread storage class must finally be added as a template parameter during the

**Listing 2.8:** Declaration of local thread storage and access from operation

```

// Declare VectorThread thread storage

2 class VectorThread

3

{

4 public: std::vector<int> threadVector;

} ;

// Sort subvector and store it within local thread state

class Sort

: public dps::LeafOperation<VectorData, VectorData, VectorThread>

9

10

IDENTIFY(Sort);

11

public:

12

13

void execute(VectorData *in)

14

VectorData *vd = new VectorData(*in);

15

std::sort(vd->v.begin(), vd->v.end());

16

// Store sorted vector locally

17

getThread()->threadVector = vd->v;

18

postDataObject(vd);

19

20

};

21

// In the start() method of the application class

dps::ThreadCollection<VectorThread> processThreads =

getController() ->createThreadCollection<VectorThread>("process");

```

A PRACTICAL EXAMPLE 23

declaration of the thread collection within the *start* method of the application: this tells DPS which storage must be created upon creation of the threads of the collection.

## 2.4.6 Execution highlights

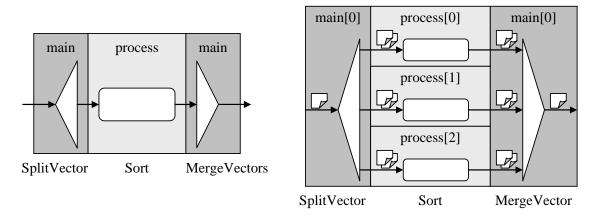

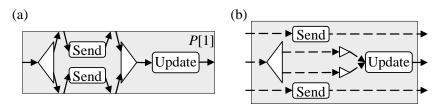

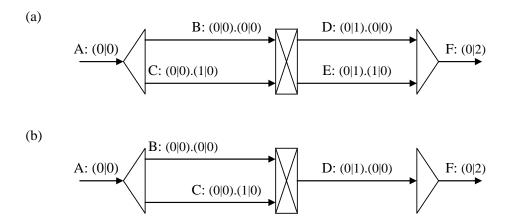

The execution of DPS application can be represented graphically by drawing its *unfolded* flow graph. Such a view better represents the parallelism within the computation by displaying the distribution of operations onto threads. However, in order to keep the representation compact, it does not tell how many times a single operation is executed on a given thread (Figure 2.8).

**Figure 2.8:** (a) The flow graph computing the parallel merge sort and (b) its unfolded representation when the processing thread collection contains three threads. Although DPS instantiates one Sort operation for every output message of SplitVector, we only display a single operation per thread to keep the graph readable.

After the call to the *callSchedule* method, the input message of the flow graph first goes through *TargetRoute*, which is the routing function associated to the first operation of the flow graph. Since the value of *target* is 0 (as set by the default constructor of *VectorData*), the message is routed to the thread 0 of the thread collection "main". Upon reception of the message, the thread instantiates a new *SplitVector* operation and calls its *execute* method with the received message as parameter. All the output messages of the *SplitVector* operation are then routed by *TargetRoute*. Since the value of *target* in successive messages are consecutive integers, the routing functions effectively distributes the messages to the threads of the "process" thread collection in a round-robin fashion. The outputs of the *Sort* operations are then routed back to thread 0 of the "main" thread collection where they are collected by the *MergeVector* operation. (The thread collection "main" contains a single thread, so *TargetRoute::route* always returns 0). Since the merge operation is the last operation in the flow graph, its output message is sent back to the caller of the parallel schedule. The result is then available for further

processing within the *start* method of the application.

## 2.5 Runtime behavior of parallel schedules

DPS implements a data-driven execution model, where all communications between DPS operations are performed asynchronously. Each thread stores incoming messages within a queue until it can process them. As soon as a message is available within a thread's pending message queue, that thread immediately starts processing by executing the appropriate operation. When the execution of the operation completes, the next message within the queue is retrieved for processing. Similarly, messages are sent to the target thread as soon as they are created by an operation. This behavior allows the overlapping of computations and communications and hides at least partially the latencies and transfer times related to communications.

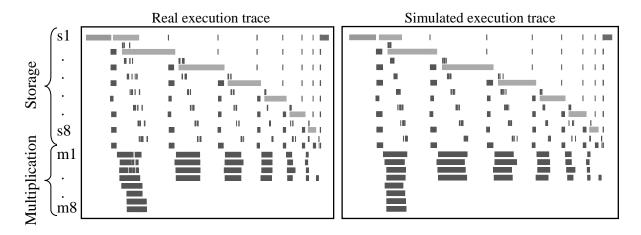

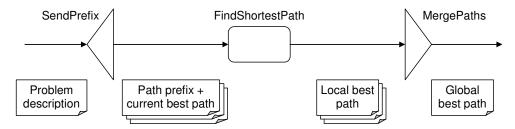

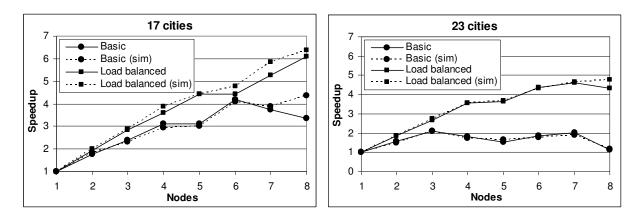

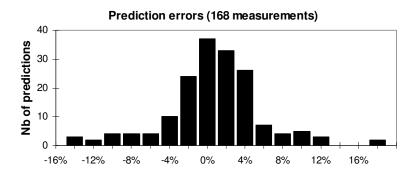

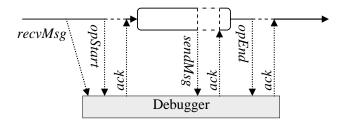

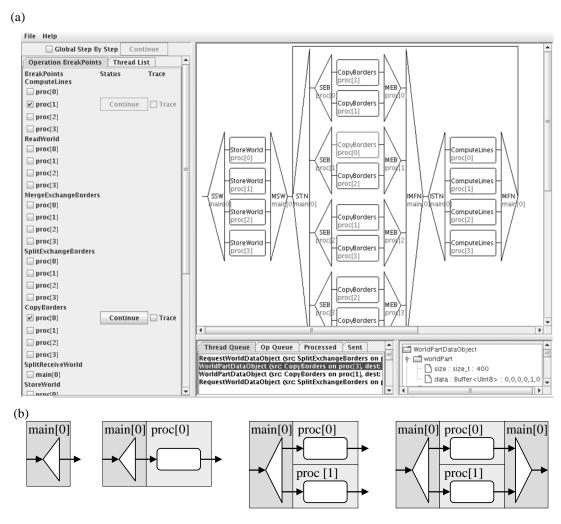

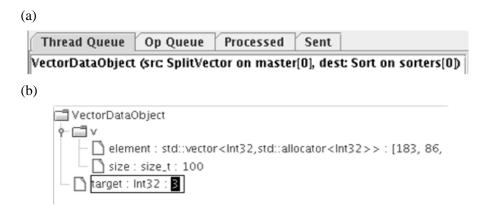

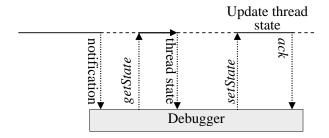

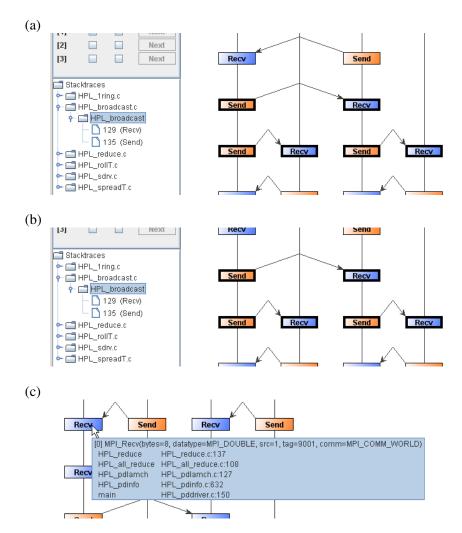

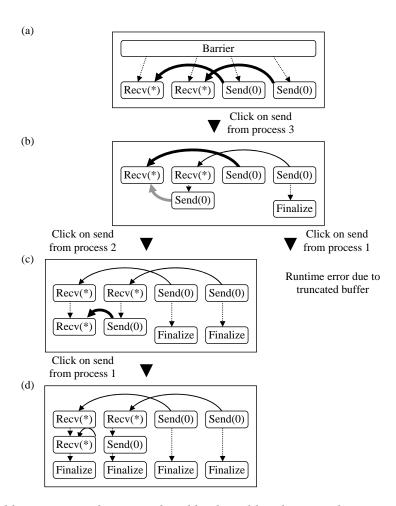

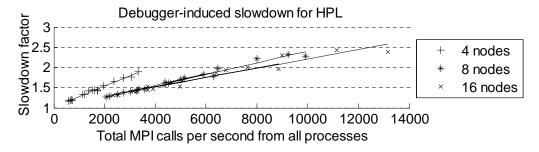

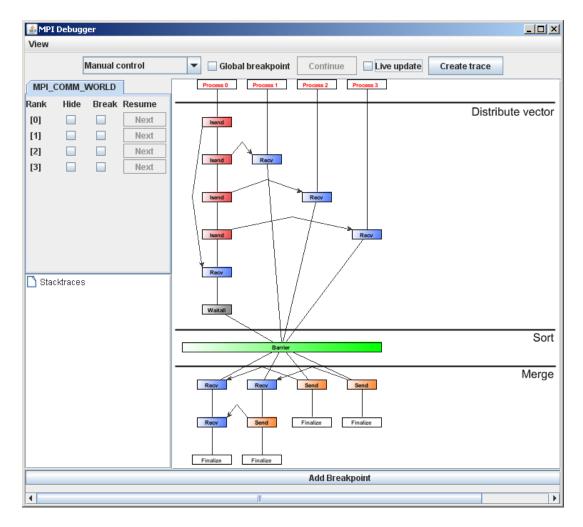

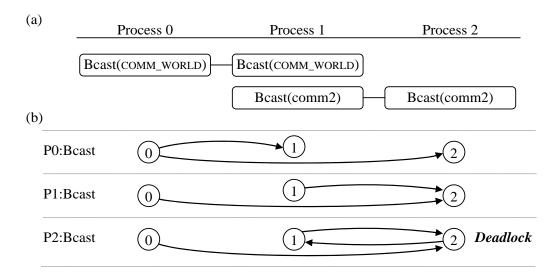

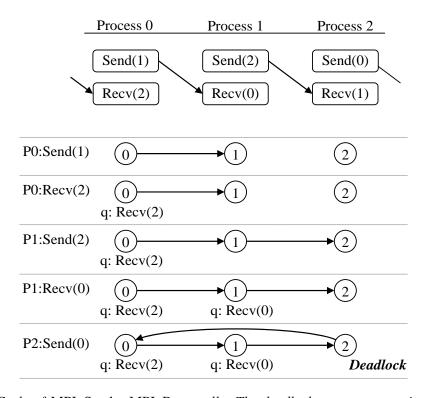

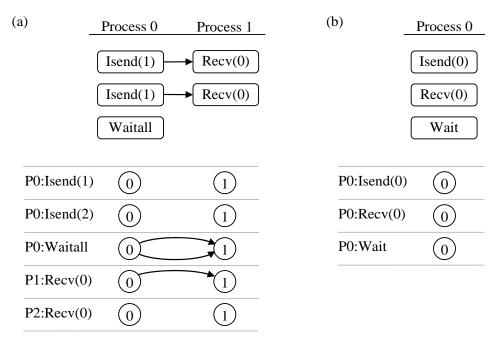

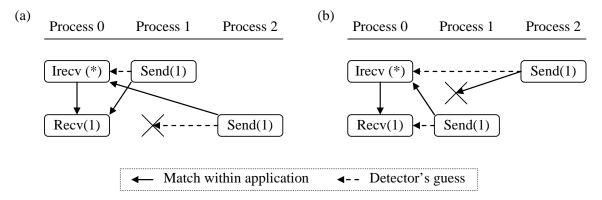

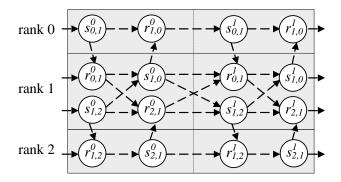

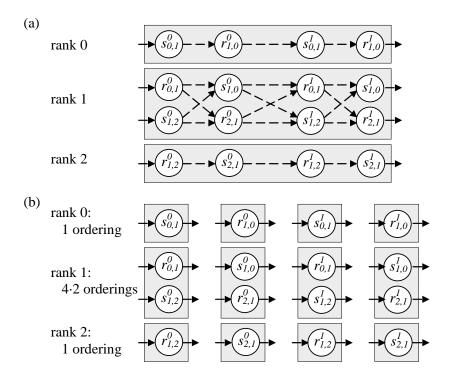

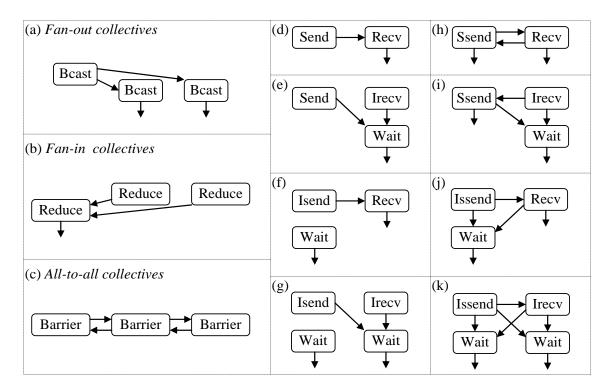

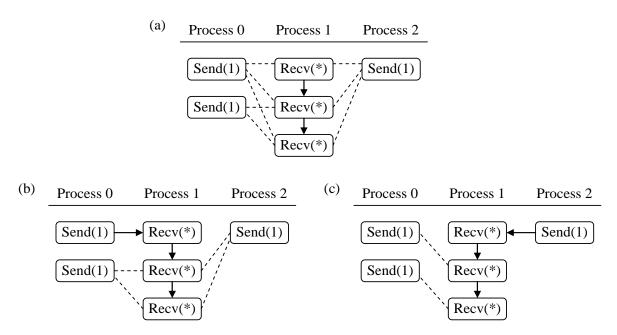

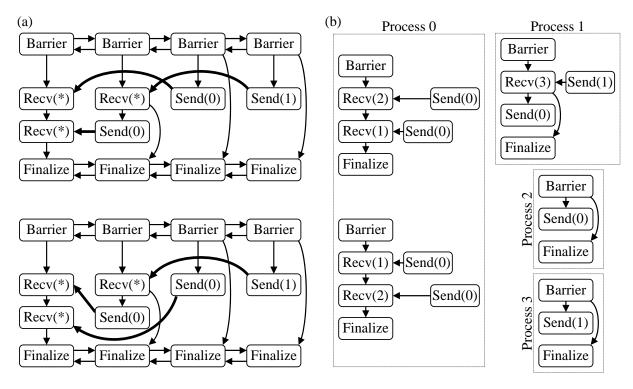

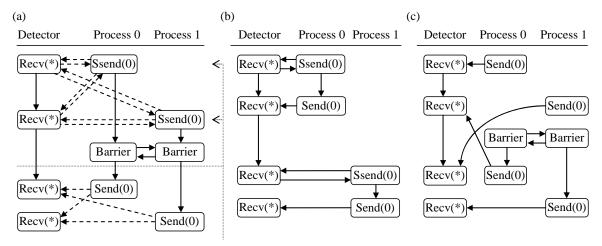

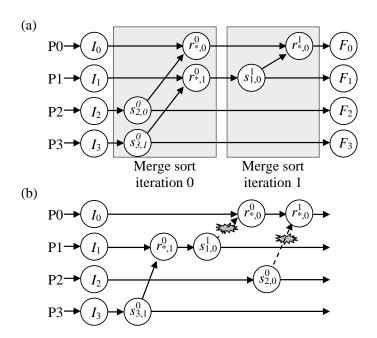

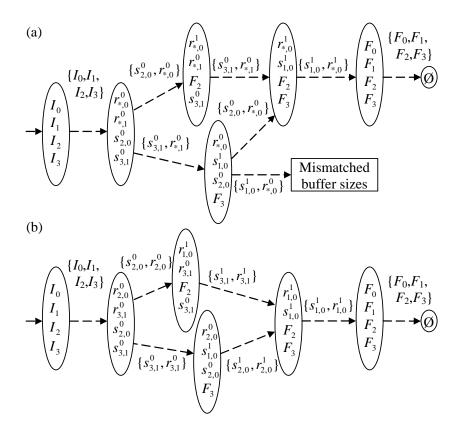

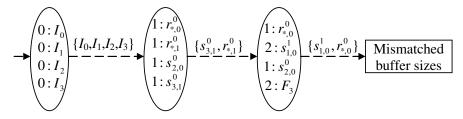

## 2.5.1 Message identifiers