# **COMPACT MODELING OF HIGH VOLTAGE MOSFETs**

THÈSE Nº 3915 (2007)

PRÉSENTÉE LE 17 DÉCEMBRE 2007 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE D'ÉLECTRONIQUE GÉNÉRALE 1 PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

# Yogesh Singh CHAUHAN

M.Tech. in electrical engineering, Indian Institute of Technology Kanpur, Inde et de nationalité indienne

acceptée sur proposition du jury:

Prof. Y. Leblebici, président du jury Prof. M. Declercq, Prof. M. A. Ionescu, directeurs de thèse M. H. Casier, rapporteur Dr A. Schmid, rapporteur Prof. M. Östling, rapporteur

# Acknowledgements

I would like to gratefully acknowledge Prof. Adrian Mihai Ionescu for the support, confidence and academic freedom, he has provided me to carry out the research work here. It was an honor and pleasure to work with him, who taught me several things other than academics.

I wish to express my gratitude to Prof. Michel Declercq for the enthusiastic supervision during this work.

My deepest appreciation goes to Dr. Francois Krummenacher, for his contribution to this work. I admire his way to share the knowledge of device modeling with others. His knowledge and experience in this field has always helped me to understand the basics of microelectronics.

I wish to thanks all the members of the jury for their participation and constructive comments.

I wish to thank all my colleagues and staff from the laboratory for their help in technical and nontechnical areas. I wish to specially acknowledge Dr. Ananda Sankar Roy for sharing the knowledge of device physics.

I would like to thank all the participants of the ROBUSPIC project, especially Dr. Renaud Gillon, Dr. Christian Maier and Mr. Andre Baguenier Desormeaux for their contribution in this work.

I am grateful to all my friends from EPFL especially Saugata Bandyopadhyay, Santanu Mahapatra and Prakash Tiwary for their continuous moral support during my good and bad days.

I wish to thank my parents, brother, sisters and wife for their support and love.

### Abstract

In the automotive industry, there is a strong trend that has increased the electronics in cars for various functions like fuel injection, electric control of doors and windows, electric chair adjustment, air conditioning etc. The 12V battery used in the present cars will not be sufficient for the increasing number of functions, as a consequence, a change towards 42V batteries will be necessary. For these automotive systems, so called smart power ICs must be used. These are the chips in which the power functionality e.g. control of motor is integrated with logic control. There is also a trend towards operation at high voltages and integrating more intelligence using a microcontroller's RAM/ROM memory and several other sensors and interfaces. The final goal is the integration of a complete system on a single chip, so called power system on chip (SoC).

The interest in accurate modeling of high voltage transistors has increased in recent years due to the compatibility of these devices with standard CMOS technology. However, existing LDMOS models are not accurate enough for this task and SPICE models are specially weak for AC performance. The limitation of these models lies in their lack of capability to physically model some of the characteristic phenomena observed in high voltage devices. The increased difficulty is related to complex 2D effects specific to asymmetric high voltage device architectures.

This thesis presents the compact modeling of high voltage devices. First, a highly scalable general high voltage MOSFET model, for the first time, is presented, which can be used for any high voltage MOSFET with extended drift region. This model includes physical effects like the quasi-saturation, impact-ionization and self-heating, and a new general model for drift resistance. The model is validated on the measured characteristics of two widely used high voltage devices in the industry i.e. LDMOS and VDMOS devices, and implemented in Verilog-A code and tested on commercial circuit simulators like SABER (Synopsys), ELDO (Mentor Graphics), Spectre (Cadence) and UltraSim (Cadence). The model exhibits excellent scalability with transistor width, drift length, number of fingers and temperature. Second, the compact modeling of lateral non-uniform doping is presented, which has great impact on the AC behavior. Third, the invalidity of Ward-Dutton charge partitioning scheme for lateral non-uniformly doped MOSFET is explained. A novel partitioning scheme is then developed and validated on the device simulation. For the first time, noise modeling of lateral non-uniformly doped MOSFET is carried out and validated on the device simulation.

Keywords: High Voltage MOSFET, DMOS, LDMOS, VDMOS, DEMOS, LAC, LAMOS, Drift, Model, DC, AC, Capacitance, EKV, HV-EKV, Partitioning, Noise, Lateral Non-uniform Doping, Scaling

# Résumé

L'industrie automobile a alimenté une forte tendance d'intégrer de plus en plus de composants électroniques dans les voitures afin d'accomplir des fonctions diverses telles que le contrle de l'injection de carburant, des vitres électriques, des siges automatiques ou de la climatisation. Les batteries de 12V utilisées dans les véhicules actuels seront bientt insuffisantes pour toutes les fonctions envisagées et par conséquent l'utilisation des sources de 42V est nécessaire. Un nouveau type de circuit intégré de puissance, appelé " smart power " IC en anglais, doit tre utilisé dans lequel la fonctionnalité du contrle de la puissance sera intégrée avec celle de la logique, par exemple pour la gestion du moteur. Il existe, d'ailleurs, une tendance vers des dispositifs haute tension avec la co-intégration d'intelligence accrue, en utilisant la mémoire RAM/ROM de microcontrleurs, en parallle avec des capteurs et d'autres interfaces. Finalement, le but sera la fabrication d'un systme complet sur puce, le systme de puissance sur puce (SoC, " System on Chip ").

La compatibilité de ces composants avec la technologie standard CMOS a récemment augmenté l'intért pour une modélisation précise des transistors haute tension. Toutefois, les modles existants LDMOS ne sont pas suffisamment précis et les models SPICE s'avrent particulirement faibles quant la performance AC. La limitation des modles mentionnés se situe dans leur incapacité de modéliser physiquement des phénomnes caractéristiques observés dans les dispositifs haute tension. La difficulté principale est liée des effets bidimensionnels spécifiques aux architectures asymétriques de ces composants.

Ce travail de thse est consacré la modélisation compacte de dispositifs haute tension. Tout d'abord, un modle MOSFET général de scalabilité accrue est présenté pour la premire fois et qui peut tre utilisé pour tous les MOSFET haute tension avec une région de "drift" étendue. Le modle en question prend en compte des phénomnes physiques tels que la quasisaturation, l'ionisation par impact, l'autoéchauffement et il introduit une nouvelle description pour la résistance de "drift". Par ailleurs, le modle a été validé sur des caractéristiques mesurées de deux types de composants, largement répandus dans l'industrie comme le LDMOS et le VD-MOS, mis en uvre en code Verilog-A et testé sur des simulateurs commerciaux comme SABER (Synopsys), ELDO (Mentor Graphics), Spectre (Cadence) et UltraSim (Cadence). D'une part, le modle présente une scalabilité excellente avec la largeur du transistor, la longueur de "drift", le nombre d'électrodes interdigitées et la température. D'autre part, la modélisation compacte du dopage non-uniforme latéral est présentée, qui a un impact considérable sur le comportement AC. En outre, l'invalidité de la théorie de Ward-Dutton sur la répartition des charges dans les MOSFET dopage uniforme est expliquée. Une nouvelle théorie sur cette répartition a été développée et validée par simulation numérique. Finalement, pour la premire fois, la modélisation du bruit des MOSFET dopage latéral non-uniforme a été élaborée et vérifiée par simulation numérique.

Keywords: High Voltage MOSFET, DMOS, LDMOS, VDMOS, DEMOS, LAC, LAMOS, Drift, Model, DC, AC, Capacitance, EKV, HV-EKV, Partitioning, Noise, Lateral Non-uniform Doping, Scaling

# Contents

| Acknowledgements i |                                               |                                                       |          |  |  |  |

|--------------------|-----------------------------------------------|-------------------------------------------------------|----------|--|--|--|

| Ał                 | ostrac                                        | t                                                     | iii      |  |  |  |

| Ré                 | ésumé                                         | e of content                                          | <b>v</b> |  |  |  |

|                    | Table                                         |                                                       | viii     |  |  |  |

| 1                  | Intr                                          | roduction                                             | 1        |  |  |  |

|                    | 1.1                                           | Background                                            | 1        |  |  |  |

|                    | 1.2                                           | High Voltage MOSFET models                            | 3        |  |  |  |

|                    | 1.3                                           | Thesis Structure                                      | 5        |  |  |  |

| 2                  | DC and AC behavior of High-Voltage MOSFETs 11 |                                                       |          |  |  |  |

|                    | 2.1                                           | High Voltage MOSFET architectures                     | 11       |  |  |  |

|                    |                                               | 2.1.1 Drain-Extended MOSFET (DEMOS)                   | 11       |  |  |  |

|                    |                                               | 2.1.2 Lateral double-Diffused MOSFET (LDMOS)          | 12       |  |  |  |

|                    |                                               | 2.1.3 Vertical double-Diffused MOSFET (VDMOS)         | 13       |  |  |  |

|                    | 2.2                                           | DC behavior of HV-MOSFETs                             | 14       |  |  |  |

|                    |                                               | 2.2.1 Quasi-Saturation Effect                         | 14       |  |  |  |

|                    |                                               | 2.2.2 Self-Heating Effect                             | 15       |  |  |  |

|                    |                                               | 2.2.3 Impact Ionization Effect                        | 16       |  |  |  |

|                    | 2.3                                           | AC behavior of HV-MOSFETs                             | 18       |  |  |  |

|                    |                                               | 2.3.1 Effect of Lateral Non-uniform doping            | 18       |  |  |  |

|                    |                                               | 2.3.2 Effect of drift region                          | 24       |  |  |  |

|                    | 2.4                                           | Conclusion                                            | 27       |  |  |  |

| 3                  | EKV                                           | /-based Scalable High Voltage MOSFET Model            | 35       |  |  |  |

|                    | 3.1                                           | Behavior of surface potential in the drift region     | 36       |  |  |  |

|                    | 3.2                                           | GENERAL DRIFT RESISTANCE MODEL                        | 37       |  |  |  |

|                    | 3.3                                           | CHARGE EVALUATION based on EKV MODEL                  | 40       |  |  |  |

|                    | 3.4                                           | Modeling of Quasi-Saturation and Self-Heating Effects | 43       |  |  |  |

|                    |                                               | 3.4.1 Quasi-Saturation Effect                         | 43       |  |  |  |

|                    |                                               | 3.4.2 Self-Heating Effect                             | 43       |  |  |  |

|                    |                                               | 3.4.3 Impact Ionization Effect                        | 44       |  |  |  |

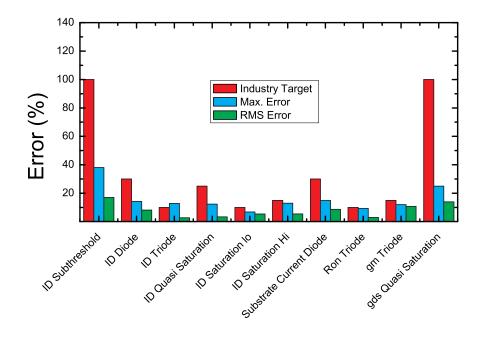

|                    | 3.5                                           | MODEL VALIDATION and RESULTS                          | 44       |  |  |  |

|                    |                                               | 3.5.1 Case Study 1: VDMOS Transistor                  | 45       |  |  |  |

|                    |                                               |                                                       |          |  |  |  |

| С |            | riculum Vitae<br>of Publications                                                                                                    | 121<br>123 |

|---|------------|-------------------------------------------------------------------------------------------------------------------------------------|------------|

| B |            | e Modeling of LAMOS                                                                                                                 | 115        |

|   |            | Evaluation of $q (= q_s \text{ or } q_d) \dots \dots$ |            |

| A | A.1        | tions of transcendental equations of $\psi_p$ , $q_s$ and $q_d$<br>Evaluation of $\psi_p$                                           |            |

| 6 | Con        | clusion                                                                                                                             | 111        |

|   | 5.6        | Conclusion                                                                                                                          |            |

|   |            | <ul><li>5.5.1 Development of the noise model</li></ul>                                                                              | 100<br>101 |

|   | 5.5        | Noise Modeling in the Lateral Non-uniformly doped MOSFET                                                                            | 100        |

|   | 5.4        | Discussion and Results                                                                                                              | 95         |

|   |            | 5.3.3 Partitioning of Gate Tunnelling Noise                                                                                         | 94         |

|   |            | 5.3.2 Partitioning of Gate Tunnelling Current                                                                                       | 94         |

|   | 5.3        | APPLICATION of small signal partitioning                                                                                            | 91<br>91   |

|   | 5.2        | Partitioning Scheme                                                                                                                 | 88         |

|   | 5.1        | Introduction                                                                                                                        | 87         |

| 5 | Part       | itioning Scheme and Noise Modeling in LAMOS                                                                                         | 87         |

|   | 4.4        | Conclusion                                                                                                                          | 81         |

|   |            | 4.3.2 Model validation on the measured data of VDMOS and LDMOS                                                                      | 72         |

|   | т.Ј        | 4.3.1 Validation of the LAMOS model on numerical device simulation                                                                  | 69         |

|   | 4.2<br>4.3 | Modeling of Lateral Non-uniform doping                                                                                              | 64<br>69   |

|   | 4.1        | Introduction                                                                                                                        | 63         |

| 4 |            | pact Modeling of Lateral Non-uniform doping                                                                                         | 63         |

|   | 3.7        | Conclusion                                                                                                                          | 58         |

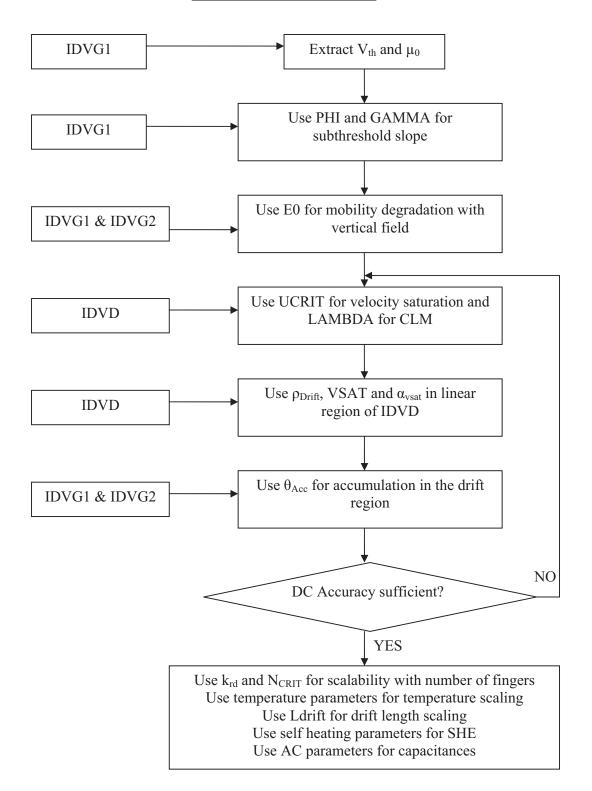

|   | 3.6        | Parameter Extraction and Model Calibration                                                                                          | 54         |

|   |            | 3.5.3 Case Study 3: SOI - LDMOS device                                                                                              | 53         |

|   |            | 3.5.2 Case Study 2: LDMOS Transistor                                                                                                | 50         |

# Chapter 1

# Introduction

# 1.1 Background

The transistor and subsequently the integrated circuits certainly qualify as two of the greatest inventions of the twentieth century. In a certain sense, all of solid-state electronics goes back to the invention by Ferdinand Braun of the solid-state rectifier in 1874 [1, 2]. That was a full 73 years before the discovery of the transistor. His work centered around the solid-state rectifier using a point contact based on lead sulfide. Of course, this configuration made for a very unstable device. In fact, after the invention of the vacuum tube, later in the century, this device very quickly became obsolete. But, later when people wanted to go to very high frequencies, and vacuum tubes would not work at the frequencies desired, the idea of the point contact rectifier made a comeback.

The theoretical development of quantum mechanics during the 1920s also played an important role in driving solid-state electronics. Without quantum mechanics, there would never have been any comprehensive understanding of solids. The understanding of the differences between metals, insulators, and semiconductors was quickly developed. The concept of electronic band structure, due to quantum mechanics, was the key to that insight. Following these advances, was the development of the quantum theory of solids led by Peierls, Wilson, Mott, Franck, and others, largely in England. These researchers added much to the understanding about electron conductivity in metals. Those days were truly the beginnings of establishing a picture of the electronic structure of metals. Metallic sodium is the simplest of all metals from an electronics point of view and was often studied in that era. A simple theory of Schottky barriers led to a crude understanding of the rectifiers discussed above, but the theory did not work quantitatively. These dedicated researchers brought the understanding forward, but semiconductors sat in the middle between the metal and the insulator, and in those days semiconductors were still a puzzle.

The continued efforts extended toward the discovery of new devices. For example, in 1926, Lilienfeld invented the concept of a field effect transistor (FET) [3]. He believed that applying a voltage to a poorly conducting material would change its conductivity and thereby achieve amplification. He patented this concept in 1926, but no one was able to do anything with it until much later.

By the late 1930s, it was beginning to be more widely accepted that there may be opportunities to create some form of solid-state devices. At this time Mervin Kelly, at Bell Labs, decided in 1936 that he should start a solid-state device group. He challenged a number of people, Bill Shockley, Russell Ohl, Jack Scaff, and others, to begin work on solid-state devices. Kelly had a feeling that the vacuum tube was not going to be the ultimate answer to electronics. Its reliability and size were such that something needed to be done, besides making more efficient and smaller vacuum tubes. It is interesting to note that by 1938, two Germans (Pohl and Hilsch) described a solid amplifier made using potassium bromide that had three metal leads. However, this device turned out to have too low operating frequency. Also, it was not a device that could be used in any true sense for electronics. That such a device came along about the same time that Kelly created the Bell Labs solid-state group shows that other engineers were thinking along the same lines. By 1940, Russell Ohl had done a great deal of work, along with others at Bell Labs, in an attempt to understand silicon crystals. Ohl learned that depending on how you prepared single crystals of silicon, you could get either n- or p-type silicon. What was meant by n or p type back in those days was whether it was a positive or negative rectifier. That was where the notation n or p came from. It was a question of which direction the rectification occurred; they defined these terms by that criterion. It is also interesting that a little later on, Ohl actually was able to make a sample in which the top part was a p-type region and the bottom was n type, and he found that when light was shone on it, it actually developed a voltage [4].

This was the status of solid-state electronics near the beginning of WWII, and it really did not change all that much during the war except in technology areas influenced by the work on radar. Radar requirements produced a very strong desire to fine-tune solid-state rectifiers, and this resulted in some effort to try to improve silicon and germanium materials. In this era, there was a lot of solid-state detector work done, mostly by trial and error. After WWII, the discovery of point contact transistor by Berdeen and Brattain in 1947 and the theory of the bipolar junction transistor by Shockley [5] at the Bell Telephone Laboratories [6] changed the future of microelectronics. By April 1950, Shockley et al. actually succeeded in growing the first junction npn device [7]. In fact, the device behaved essentially as predicted by Shockleys theory. Progress was supported by a series of important inventions that led to better and better devices. In fact, Shockley wrote a book titled Electrons and Holes in Semiconductors. Still it took several years before the first  $Si/SiO_2$  MOSFET, which is now so widely used, was demonstrated by Kahng and Atalla [8, 9]. But, this turned out to be a pretty poor device. It took until the early 1970s, 15 years before planar FETs came into common use. The first integrated circuits (IC) were developed by Noyce at Fairchild Semiconductor and by Kilby at Texas Instruments. Kilby's circuits consisted of transistors fabricated using the mesa technique, where the collector contact is made to the backside of the wafer, and bonded gold wire is used for interconnect. Noyce's ICs more closely resembled present day chips because they used a planar fabrication technique developed by Hoerni at Fairchild, where oxide masking and diffusion were used to form the transistor [10].

The initial circuits were oscillators and simple digital flip-flops using two or three active devices along with passive elements, but by 1971, the technology had advanced to the stage, where the first microprocessor (Intel 4004) was fabricated with 2300 transistors. In 1965, Moore published a paper on the state of the semiconductor industry, which predicted that the number of devices in an integrated circuit would double each year [11, 12]. This prediction became the famous "Moore's Law". Today the density of transistors in a chip has crossed the billion mark.

# **1.2 High Voltage MOSFET models**

The interest in the high voltage (HV) MOS devices has dramatically increased as these devices were integrated with the low power modules in MOS technology. Today, HV-MOS devices are extensively used in all kinds of integrated power circuits, like switch-mode power supplies and power amplifiers. In addition, Lateral double-Diffused MOSFET (LDMOS) devices processed in thin-film silicon-on-insulator (SOI) provides a new and attractive technology for smart power integrated circuits in consumer and automotive applications [13]. Optimal design of these power circuits requires HV-MOS models for circuit simulation, which describe the device characteristics accurately over a wide range of biases.

The accurate compact modeling of high voltage MOS transistors has always been a challenge in the device modeling community. This is due to the fact that the charges and field associated with the drift region and intrinsic MOS have very complex dependence on the external terminal biases owing to the asymmetric device architecture. Though many groups around the world have attempted to model the different architectures of HV-MOS transistors using different approaches, most of these are sub-circuit or macro-models. Acceptable simulation accuracy is obtained by the use of these macro-models based on conventional low voltage modules [14, 15], but these macro-models are not physical and do not take into account the special phenomena of HV devices.

The LDMOS macro model proposed by Frere et al. [15], which is being used in AMI Semiconductor (AMIS), is based on BSIM3v3.2. The model uses an adapted JFET to model the drift region and shorted PMOS transistors to model the capacitance behavior of the drift region. The drift region modeling using JFET is carried out by equations based on Schichman & Hodges [16]. The equations were implemented in Verilog-A module. The gate voltage of the JFET was tied to the intrinsic drain potential of intrinsic MOS, which provided variable threshold voltage of JFET. Two shorted PMOS transistors were used to model the gate overlap over thin and thick oxide, respectively. Even though this LDMOS model provides good behavior for both DC and AC operations, the scalability of model especially for drift length was never demonstrated.

Some other compact models have also been reported in the literature with better accuracy [17, 18, 19, 20, 21, 22, 23, 24]. Other models reported in the literature show reasonable accuracy in DC operation [17, 18, 19, 20, 22], but do not show model validity for AC operation under different biasing conditions. Although the physical LDMOS model developed by Anghel et al. demonstrated good accuracy in DC regions, it was very difficult to implement and use it for industrial purposes because of the convergence problems in the simulator. There has also been some work in the development of DMOS models using neural network based approach [25, 26]. This approach provides excellent results with speed, provided the model is trained on wide range of measurement data. The major weakness of neural network based models is that they are not scalable and can be used only for the particular device structure for which it has been trained.

The MOS model 20 (MM20) [23, 24] from NXP (earlier Philips Semiconductor) is the famous LDMOS compact model. This model has shown capability to model both DC and AC operations including quasi-saturation and self-heating effects. MM20 is a surface potential based model, whose intrinsic MOS model is similar to the MM11 or PSP [27, 28], while drift region is modeled using MM31 or MM40 [27]. MM20 model has several variations for different LDMOS structures. One model is for LDMOS with thin gate oxide all over the drift region.

Another variation of this model is for the partial gate overlap in the drift region and uses a resistance to described the non-overlapped drift region. Then there is different model for drift region with both thin and thick gate oxides. Even though all of these models have demonstrated good results for different LDMOS devices, one has to choose different model for different devices. Also none of these models take into account the lateral non-uniform doping in the intrinsic MOS, which may result in poor accuracy in the transient operations [29, 30].

Recently Hiroshima University has developed an HiSim-LDMOS model [31, 32]. This LDMOS model is the modular extension of HiSim model, which is a surface potential based model. There has been no publication of this LDMOS model yet.

Although efforts mentioned have been successful in solving some modeling problems in high voltage devices, still there are several open challenges. Following are some of the key challenges in this field, which are also the must have features of any standard high voltage model by compact modeling council (CMC):

► Accurate modeling of DC/AC behavior as well as the derivatives of terminal currents and node charges with respect to node voltages for all working modes (off, linear, saturation regions and reverse modes).

➤ Charge model has to be charge conservative, and intrinsic charge model has to take into account the effects of voltage drop across the source and drain resistances.

► Accurate modeling of drain extension (drift) region resistance including velocity saturation.

► Accurate modeling of gate/drain overlap region bias dependent capacitance and resistance.

Accurate modeling of parasitic effects (gate, source and drain, and substrate resistances, and source/drain-body junction diodes)

► Accurate modeling of the 1/f, thermal, and gate induced noise.

$\blacktriangleright$  Capable of modeling accurately with power supplies up to 200 volts and temperature ranges from -50 °C to 200 °C.

➤ Capable of modeling self-heating effects accurately and efficiently, which requires scalable temperature-dependence modeling.

➤ Capable of modeling accurately quasi-saturation effects and  $g_m$  fall-off in the saturation region, namely, the channel current compressions at higher  $V_{GS}$  when  $V_{DS}$  is greater than  $V_{dsat}$ . ➤ Capable of modeling accurately  $C_{GD}$  drop at higher external  $V_{GS}$  biases.

$\blacktriangleright$  Capable of accurate modeling of the true asymmetry of the source and drain resistances and the source and drain junctions in I - V and C - V.

➤ Capable of modeling substrate current behavior correctly including the impact ionization taking place in the drain drift extension regions.

➤ Capable of handling scalability over a wide range of geometries, biases, and temperatures with one set of global model parameter set to cover the entire device matrix provided for model extraction. Provides drain drift region length as an instance parameter.

Capable of covering reverse working mode for both symmetric and asymmetric structure ( i.e. when  $V_{DS} < 0$  )

► Capable of handling of p-type devices as well as n-type devices.

► Good convergence in reasonable scale circuit simulation.

➤ Capable of modeling accurately a wide array of HV-MOSFET process technologies and device structures, which would include LDMOS and EDMOS (Extended Drain), both symmetrical and asymmetrical, and other drain drift extension structures including, but not limited to, those of various RESURF flavors.

#### **1.3 Thesis Structure**

➤ Capable of modeling layout dependent characteristics including multi-finger device structures that have separate, merged, and shared source and drain connections, and point and wide source/drain contacts.

► Capable of modeling body bias dependency of DC and AC characteristics.

Capable of providing optional temperature node for thermal electrical coupling simulation.

► Capable of modeling parasitic BJT effects.

In this thesis, a detailed analysis and modeling of high voltage MOSFETs will be presented. Some of the key challenges mentioned above will be addressed here.

# **1.3 Thesis Structure**

This section briefly outlines the contents of the chapters.

#### • Chapter 2: DC and AC behavior of High-Voltage MOSFETs

A basic overview of the architectures of high voltage MOSFETs is presented. Impact of lateral non-uniform doping and drift region on both the DC and AC behavior is analyzed which paves the way to develop an accurate HV-MOS model [33].

#### • Chapter 3: EKV-based Scalable General High Voltage MOSFET Model

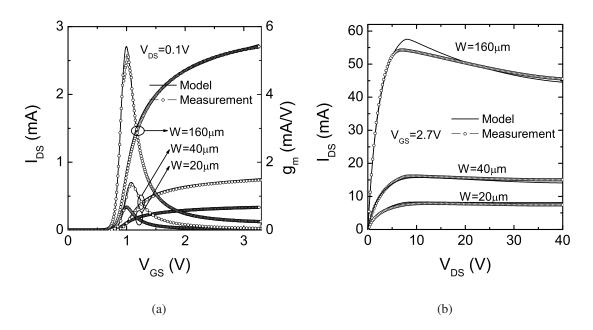

A new high voltage MOSFET model is developed in this chapter. The model uses charge based EKV model for the modeling of intrinsic MOS channel while drift region is modeled using bias dependent drift resistance. The model is validated on the AMIS I2T100 and I3T50 technologies. The scaling of the model is tested for different temperatures, drift length and number of fingers [34, 35, 36, 37].

### • Chapter 4: Compact Modeling of Lateral Non-uniform doping

For the first time, true compact modeling of lateral non-uniform doping is presented. The impact of this model is emphasized on the capacitance behavior of high voltage MOSFETs. The model is validated on the AMIS I2T100 and I3T50 technologies especially for the AC behavior [29, 38, 39, 30].

# • Chapter 5: Partitioning Scheme and Noise Modeling in the Lateral Non-Uniformly doped MOSFET

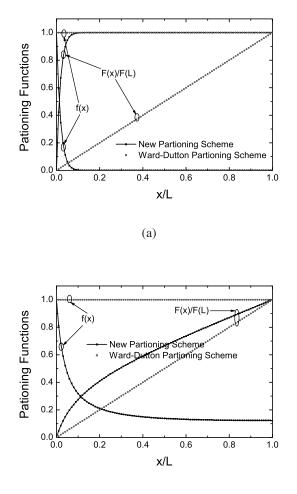

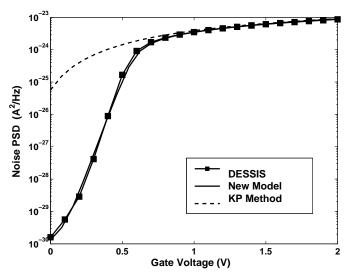

The invalidity of Ward-Dutton charge partitioning scheme for lateral non-uniformly doped MOSFET is explained. A novel partitioning scheme is then developed and validated on the device simulation [40, 41, 42]. For the first time, noise modeling of lateral non-uniformly doped MOSFET is carried out and validated on the device simulation [43].

# **Bibliography**

- [1] E. Braun and S. Macdonald, "Revolution in Miniature." Cambridge University Press, 1982.

- [2] W. Brinkman, D. Haggan, and W. Troutman, "A history of the invention of the transistor and where it will lead us," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 1858– 1865, Dec. 1997.

- [3] J. E. Lilienfield, "," US Patent 1745175, 1926.

- [4] J. H. Scaff, H. C. Theuerer, and E. E. Schumacher, "P-type and N-type silicon and the formation of the photovoltaic barriers in silicon ingots," *Trans. A.I.M.E.*, vol. 185, p. 383388, June 1949.

- [5] W. Shockley, "The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors," *Bell Syst. Tech. Journal*, vol. 28, pp. 435–489, 1949.

- [6] J. Bardeen and W. H. Brattain, "The transistor, a semi-conductor triode," *Phys. Rev.*, vol. 74, no. 2, pp. 230–231, Jul 1948.

- [7] M. S. W. Shockley and G. K. Teal, "P-N junction transistors," *Phys. Rev.*, vol. 83, p. 151162, 1951.

- [8] D. Kahng and M. M. Atalla, "Silicon-silicon dioxide field induced surface device," in *Solid State Device Research Conf.*, June 1960.

- [9] D. Kahng, "A Historical Perspective on the Development of MOS Transistors and Related Devices," *IEEE Transactions on Electron Devices*, vol. 23, pp. 655–657, July 1976.

- [10] G. Moore, "The Role of Fairchild in Silicon Technology in the Early days of 'Silicon Valley'," *Proceedings of the IEEE*, vol. 86, pp. 53–62, Jan 1998.

- [11] —, "Cramming More Components Onto Integrated Circuits," *Proceedings of the IEEE*, vol. 86, no. 1, pp. 82–85, Jan 1998.

- [12] —, "No exponential is forever: but 'Forever' can be delayed! [semiconductor industry]," in *IEEE International Solid-State Circuits Conference*, 2003, pp. 20–23.

- [13] J. A. van der Pol, A. Ludikhuize, H. Huizing, B. van Velzen, R. Hueting, J. Mom, G. van Lijnschoten, G. Hessels, E. Hooghoudt, R. van Huizen, M. Swanenberg, J. Egbers, F. van den Elshout, J. Koning, H. Schligtenhorst, and J. Soeteman, "A-BCD: An

economic 100 V RESURF silicon-on-insulator BCD technology for consumer and automotive applications," in *IEEE International Symposium on Power Semiconductor Devices and ICs*, June 2000, p. 327330.

- [14] A. Canepari, G. Bertrand, A. Giry, M. Minondo, F. Blanchet, H. Jaouen, B. Reynard, N. Jourdan, and J.-P. Chante, "LDMOS modeling for analog and RF circuit design," in *IEEE European Solid-State Device Research Conference (ESSDERC)*, Sept. 2005, pp. 469 – 472.

- [15] S. Frere, P. Moens, B. Desoete, D. Wojciechowski, and A. Walton, "An improved LDMOS transistor model that accurately predicts capacitance for all bias conditions," in *Proceedings of the 2005 International Conference on Microelectronic Test Structures (ICMTS)*, April 2005, pp. 75 – 79.

- [16] "Affirma spectre circuit simulator reference, product version 4.4.6," June 2000.

- [17] J. Victory, J. Sanchez, T. DeMassa, and B. Welfert, "A static, physical VDMOS model based on the charge-sheet model," *IEEE Transactions Electron Devices*, vol. 43, no. 1, pp. 157 – 164, Jan. 1996.

- [18] C.-Y. Tsai, D. E. Burk, and K. D. T. Ngo, "Physical Modeling of the Power VDMOST for Computer-Aided Design of Integrated Circuit," *IEEE Transactions Electron Devices*, vol. 44, no. 3, pp. 472 – 480, March 1997.

- [19] N. Hefyene, C. Anghel, A. Ionescu, S. Frere, R. Gillon, M. Vermandel, B. Bakeroot, and J. Doutreloigne, "An experimental approach for bias-dependent drain series resistances evaluation in asymmetric HV MOSFETs," in *IEEE European Solid-State Device Research Conference (ESSDERC)*, Sept. 2001, pp. 403 – 406.

- [20] C. Anghel, "High voltage devices for standard MOS technologies : characterisation and modelling," Ph.D. dissertation, EPFL, 2004, thesis No. 3116.

- [21] N. D'Halleweyn, J. Benson, W. Redman-White, K. Mistry, and M. Swanenberg, "MOOSE: a physically based compact DC model of SOI LD MOSFETs for analogue circuit simulation," *IEEE Transactions Computer-Aided Design of Integrated Circuits and Systems*, vol. 23, no. 10, pp. 1399–1410, Oct. 2004.

- [22] N. Hefyene, "Electrical characterization and modelling of lateral DMOS transistor : investigation of capacitances and hot-carrier impact," Ph.D. dissertation, EPFL, 2005, thesis No. 3200.

- [23] A. Aarts, N. D'Halleweyn, and R. van Langevelde, "A surface-potential-based high-voltage compact LDMOS transistor model," *IEEE Transactions Electron Devices*, vol. 52, no. 5, pp. 999 1007, May 2005.

- [24] A. Aarts and W. Kloosterman, "Compact modeling of high-voltage LDMOS devices including quasi-saturation," *IEEE Transactions Electron Devices*, vol. 53, no. 4, pp. 897 – 902, April 2006.

#### **BIBLIOGRAPHY**

- [25] S. Frere, B. Desoete, J. Rhayem, M. Anser, and A. Walton, "A neural-network-based local inverse mapping technique for building statistical DMOS models," in *IEEE European Solid-State Device Research Conference (ESSDERC)*, Sept. 2003, pp. 331–334.

- [26] R. Gillon, "Aspects of robust mixed-signal design in smart-power IC processes," in *IEEE International Symposium on Industrial Electronics (ISIE)*, vol. 2, June 2005, pp. 485–488.

- [27] "High voltage models,", http://www.nxp.com/models.

- [28] G. Gildenblat, X. Li, W. Wu, H. Wang, A. Jha, R. V. Langevelde, G. Smit, A. Scholten, and D. Klaassen, "Psp: An advanced surface-potential-based mosfet model for circuit simulation," *IEEE Transactions Electron Devices*, vol. 53, no. 9, pp. 1979 – 1993, Sept. 2006.

- [29] Y. S. Chauhan, F. Krummenacher, C. Anghel, R. Gillon, B. Bakeroot, M. Declercq, and A. M. Ionescu, "Analysis and Modeling of Lateral Non-Uniform Doping in High-Voltage MOSFETs," in *IEEE International Electron Devices Meeting*, Dec. 2006, pp. 8.3.1 – 8.3.4.

- [30] Y. S. Chauhan, F. Krummenacher, R. Gillon, B. Bakeroot, M. Declercq, and A. M. Ionescu, "Compact Modeling of Lateral Non-uniform doping in High-Voltage MOS-FETs," *IEEE Transactions on Electron Devices*, vol. 54, no. 6, pp. 1527–1539, June 2007.

- [31] "Hisim-ldmos model,", http://home.hiroshima-u.ac.jp/usdl/HiSIM.html, 2006.

- [32] "Model features of hisim-ldmos,", http://www.eigroup.org/cmc/minutes, 2006.

- [33] Y. S. Chauhan, R. Gillon, M. Declercq, and A. M. Ionescu, "Impact of Lateral Nonuniform doping and hot carrier degradation on Capacitance behavior of High Voltage MOSFETs," in *IEEE European Solid-State Device Research Conference (ESSDERC)*, Sept. 2007.

- [34] Y. S. Chauhan, C. Anghel, F. Krummenacher, R. Gillon, A. Baguenier, B. Desoete, S. Frere, A. M. Ionescu, and M. Declercq, "A Compact DC and AC Model for Circuit Simulation of High Voltage VDMOS Transistor," in *IEEE International Symposium on Quality Electronic Design (ISQED)*, March 2006, pp. 109–114.

- [35] Y. S. Chauhan, C. Anghel, F. Krummenacher, A. M. Ionescu, M. Declercq, R. Gillon, S. Frere, and B. Desoete, "A Highly Scalable High Voltage MOSFET Model," in *IEEE European Solid-State Device Research Conference (ESSDERC)*, Sept. 2006, pp. 270 – 273.

- [36] Y. S. Chauhan, C. Anghel, F. Krummenacher, C. Maier, R. Gillon, B. Bakeroot, B. Desoete, S. Frere, A. B. Desormeaux, A. Sharma, M. Declercq, and A. M. Ionescu, "Scalable General High Voltage MOSFET Model including Quasi-Saturation and self-heating effect," *Solid State Electronics*, vol. 50, no. 11-12, pp. 1801–1813, 2006.

- [37] Y. S. Chauhan, R. Gillon, B. Bakeroot, F. Krummenacher, M. Declercq, and A. M. Ionescu, "An EKV-based High Voltage MOSFET Model with improved mobility and drift model," *Solid State Electronics*, 2007.

- [38] Y. S. Chauhan, F. Krummenacher, R. Gillon, B. Bakeroot, M. Declercq, and A. M. Ionescu, "A New Charge based Compact Model for Lateral Asymmetric MOSFET and its application to High Voltage MOSFET Modeling," in *IEEE International Conference on VLSI Design and International Conference on Embedded Systems*, Jan. 2007, pp. 177 182.

- [39] C. Anghel, Y. S. Chauhan, N. Hefyene, and A. Ionescu, "A physical analysis of HV MOS-FET capacitance behaviour," in *IEEE International Symposium on Industrial Electronics* (*ISIE*), vol. 2, June 2005, pp. 473 – 477.

- [40] A. Aarts, R. van der Hout, J. Paasschens, A. Scholten, M. Willemsen, and D. Klaassen, "New fundamental insights into capacitance modeling of laterally nonuniform MOS devices," *IEEE Transactions Electron Devices*, vol. 53, no. 2, pp. 270 – 278, Feb. 2006.

- [41] A. S. Roy, Y. S. Chauhan, C. Enz, J.-M. Sallese, A. M. Ionescu, and M. Declercq, "Partitioning Scheme in Lateral Asymmetric MOST," in *IEEE European Solid-State Device Research Conference*, Sept. 2006, pp. 307–310.

- [42] A. S. Roy, C. C. Enz, and J.-M. Sallese, "Drain-Source Partitioning in MOSFET," *IEEE Transactions on Electron Devices*, June 2007.

- [43] A. S. Roy, Y. S. Chauhan, C. Enz, and J.-M. Sallese, "Noise modeling in lateral asymmetric MOSFET," in *IEEE International Electron Devices Meeting (IEDM)*, Dec. 2006, pp. 191–194.

# Chapter 2

# **DC and AC behavior of High-Voltage MOSFETs**

The interest in the high-voltage (HV) MOS devices has dramatically increased as these devices were integrated with the low power modules in MOS technology [1, 2, 3, 4, 5]. Today, HV-MOS devices are extensively used in all kinds of integrated power circuits, like switch-mode power supplies, motor drivers and, power amplifiers. In addition, LDMOS devices processed in thin-film silicon-on-insulator (SOI) provide a new and attractive technology for smart power integrated circuits in consumer and automotive applications [6]. The discussion in this chapter will be focused on different HV-MOS architectures and special effects occurring in these devices.

# 2.1 High Voltage MOSFET architectures

There are three different types of high-voltage devices, normally used with CMOS technology. These are Drain-Extended MOSFET [4, 5, 7, 8], Lateral double-diffused MOSFET [9, 10, 11] and Vertical double-diffused MOSFET [12, 13]. Only N-channel devices are considered here but all of them have their P-channel counterparts.

### 2.1.1 Drain-Extended MOSFET (DEMOS)

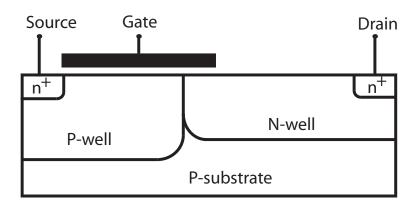

Modern digital VLSI circuits are presently operating at the voltage levels of 1.8 V and below. However, circuit requirements often call for design and interface with other circuits operating at 3.3/5.0 V or even higher. Example circuits are input/output interface circuits with various offchip system components, such as power management switches that regulate power from battery or system supplies, analog input circuits conditioning transducer signals, or output analog drive functions for speakers or other actuators. System designers increasingly want all of these functions in a monolithic IC to decrease system size and increase reliability. One solution to this problem of two voltage levels on an integrated circuit is to use two gate oxides and two sets of lightly-doped drain (LDD) implants [4], but this method increases the process complexity and cost. The alternate solution is to use drain extended (DE) MOS transistors [7, 8] that can operate at much higher drain voltages without significant loss of performance and without added

Figure 2.1: Schematic representation of the Drain-Extended MOSFET (DEMOS).

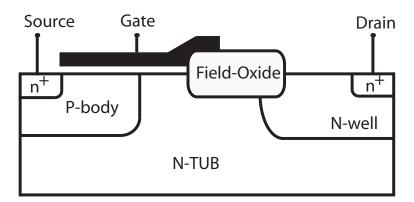

Figure 2.2: Schematic representation of the Lateral double-Diffused MOSFET (LDMOS).

process complexity. Another solution to this problem of two voltage levels on an integrated circuit that is widely used is circuit techniques such as cascading low-voltage transistors. This approach adds considerable circuit complexity and uses more power to maintain intermediate voltages for the gate drive. The use of DEMOS instead of cascaded circuits or other circuit methods offers significant die size area and power savings. It is well known that a LDD extension increases the drain breakdown voltage by reducing the electric field under the gate at the drain end of the transistor. The difficulty here has to do with achieving the goal with a higher than the very thin 4 nm oxides can normally withstand, without the luxury of a LOCOS oxide used in conventional DE style devices for the poly to terminate on. A typical twin well CMOS process, that uses p-substrate wafers, allows DE MOS transistors to be built with the n-well as the NMOS drain extension. Fig. 2.1 shows the schematic representation of N-type DEMOS device. These devices are generally used for 5V operation range especially as in input/output interfaces.

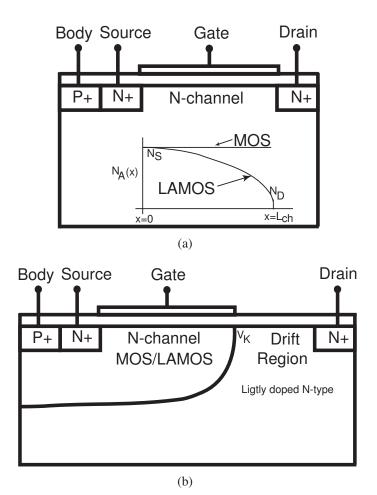

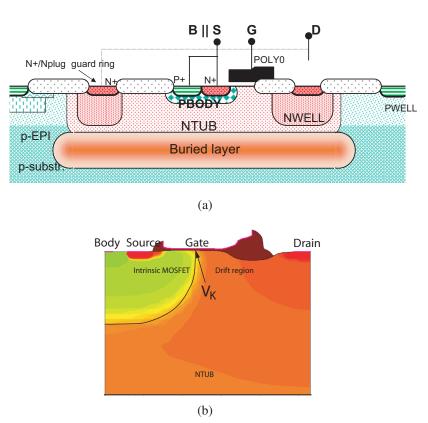

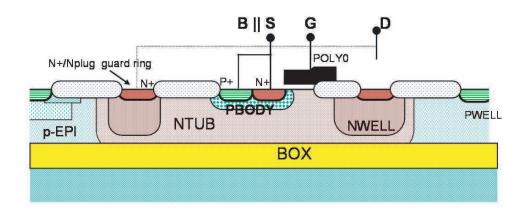

### 2.1.2 Lateral double-Diffused MOSFET (LDMOS)

Due to the inherent limitations of CMOS technology, DEMOS device characteristics, especially avalanche breakdown and on-resistance, are highly dependent on the n-well doping profile and surface concentration. As CMOS technology is maturing in deep-submicron lithography, other approaches were investigated in order to make available high voltage devices with improved characteristics. The LDMOS device architecture, which actually originated from DEMOS/LDD-MOS, has much higher breakdown voltage than DEMOS architectures. Fig. 2.2 shows the schematic representation of N-type LDMOS device. The LDMOS devices are useful in high-voltage switching because of their switching speeds and relative simplicity in processing [14]. There are many variations of LDMOS devices [9, 10, 11, 15]. The device shown in Fig. 2.2 is generally used for 20-100V application e.g switch-mode power supplies and power amplifiers etc. The channel in the device is created using double diffused process and thus it has lateral non-uniform doping. The effective gate length is shorter than the physical length of the gate electrode. The drift region is lightly doped N-type whose length varies with increasing voltage blocking capability in the drain side. The maximum drain-source voltage, that can be applied, is determined by the breakdown voltage of the p-n junction, which is limited by the n layer doping, thickness and field crowding at the junction edge.

The electric field in the LDMOS near the silicon surface is considerably lower than in the conventional MOS or DEMOS. However, the maximum field still remains on the surface and avalanche breakdown may occur there [16]. The surface electric field can be reduced significantly by the use of thick oxide (as shown in Fig. 2.2) or field plate as the maximum field is now located inside the bulk. To reduce the on-resistance in LDMOS (with field plate), the length of the field plate should be as small as possible. The effect of field plate on LDMOS characteristics e.g. breakdown voltage, quasi-saturation effect has been studied in the literature in detail [17, 18, 19, 20, 21, 22]. The on-resistance of the LDMOS can also be decreased by using the ion-implantation in the drift region [23]. The field plate also shields the gate from the drain potential, thus minimizing the feedback (drain-to-gate) capacitance, which means improvement of RF signal gain. The p-n junction and the field plate form a fairly uniform field between gate and the drain, thus giving better breakdown voltage.

The LDMOS transistors fare much better at higher frequencies compared to their vertical counterpart (VDMOS) devices. The LDMOS transistors with frequencies more than 2.7GHz are already available in the market. Freescale has recently announced 3.8GHz high power LDMOS for coming WIMAX applications [24]. Since in the LDMOS design, the gate, source and drain are all on the top surface, chip size grows rapidly for high voltage handling capability above 200V.

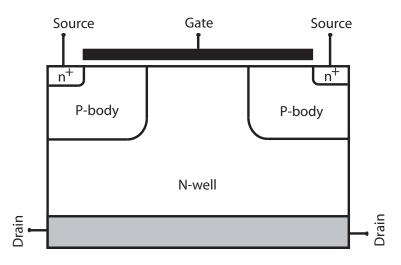

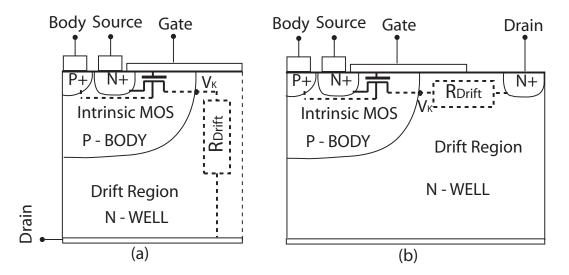

### **2.1.3** Vertical double-Diffused MOSFET (VDMOS)

The growing chip size problem for higher operating voltages is addressed by the VDMOS transistor technology [25]. Fig. 2.3 shows the schematic representation of N-type VDMOS device [12, 13]. Since these devices have the drain at the back surface, a variety of junction edge termination schemes can be utilized at the perimeter of the die. However, the channel region itself is on the top surface and thus the current flow is lateral through the channel and vertical through the lightly doped drift. The channel in the device is created using double diffused process and thus it has lateral non-uniform doping. The effect of lateral non-uniform doping and lightly doped drift region on device characteristics is explained in the next section. The VDMOS design sacrifices speed for lower on-resistance and denser high-voltage layout due to large gate/drift overlap. A lower on-resistance than VDMOS is produced in VVMOS devices, on the other hand, minimize gate-drain overlap at the cost of an on-resistance increase [26].

Figure 2.3: Schematic representation of the Vertical double-Diffused MOSFET (VDMOS).

# 2.2 DC behavior of HV-MOSFETs

The high voltage devices show some special effects due to high electric field inside the device e.g. self-heating, quasi-saturation and impact ionization effects. In fact, some of these effects (self-heating and impact ionization) are also visible in low voltage MOSFETs as electric field in these devices also becomes quite high as channel length is decreased. Even though above mentioned effects arise due to high electric fields in the device, some other special effects are also observed due to different device processes in these devices compared to conventional MOS-FETs. One of the major difference in terms of device process is the lateral non-uniform doping in the channel and drift region in the drain side of HV devices. Here we will discuss the physical origin of these effects and their impact on device characteristics.

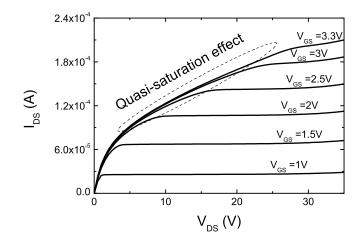

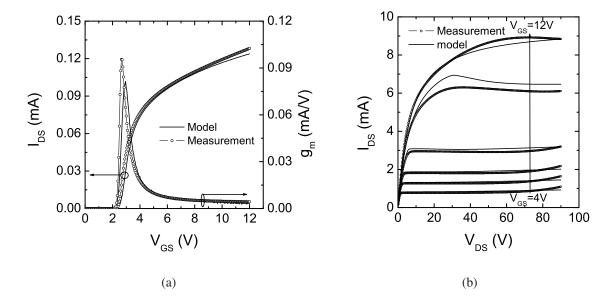

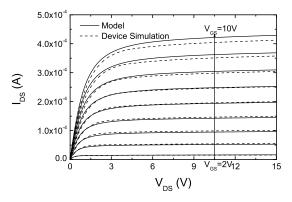

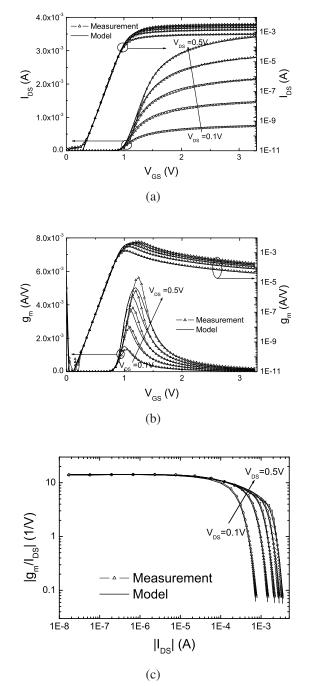

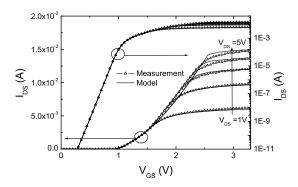

### 2.2.1 Quasi-Saturation Effect

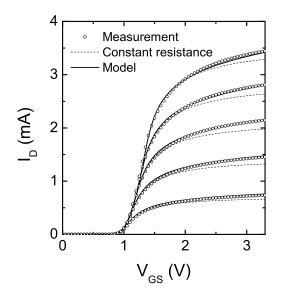

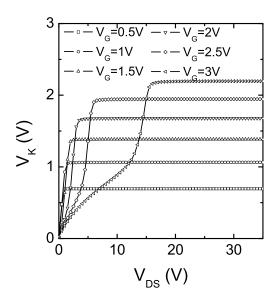

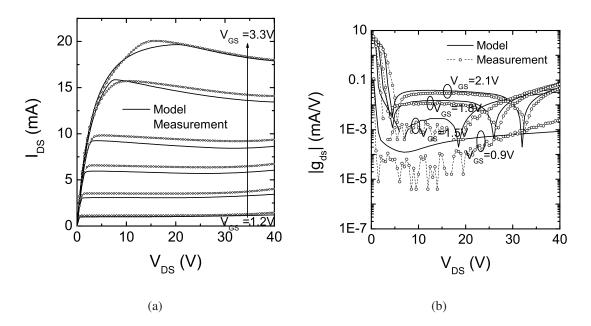

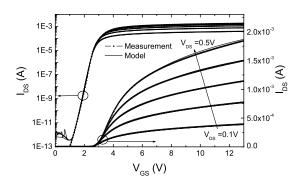

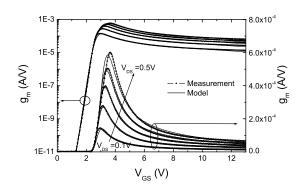

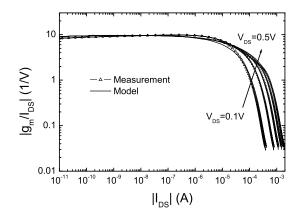

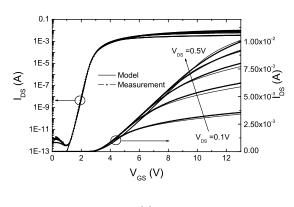

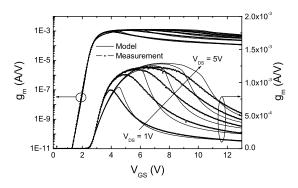

The quasi-saturation effect [27, 28, 29, 30, 31] is one of the unique effect observed in HV devices other than bipolar devices [32, 33, 34, 35, 36, 37]. To explain the quasi-saturation effect, first let's discuss the saturation mechanisms in HV devices [38] using output characteristics of VDMOS transistor shown in Fig. 2.4. The current saturation on  $I_{DS} - V_{DS}$  characteristics can occur due to following three mechanisms:

(a) Pinch-off in the channel: For a fixed gate voltage, if drain voltage is increased, the channel gets depleted and current saturates. This effect is called pinch-off and it is also the normal saturation mechanism in long channel MOSFETs. In HV devices, the channel pinch-off is generally observed at low  $V_{GS}$  (see  $V_{GS} = 1V$  curve in Fig. 2.4).

(b) Velocity saturation in the channel: If the lateral electric field in the channel is more than certain limit called as critical field, the velocity of the electrons get saturated and thus there will be no further increase in the current for any further increase in the drain voltage. This effect is called velocity saturation, which is quite common phenomenon in short channel MOSFETs. In HV devices, this effect is generally observed for medium to high  $V_{GS}$  (see  $I_{DS} - V_{DS}$  curves for  $V_{GS} = 1.5, 2, 2.5, 3V$  at  $V_{DS}$ =30V in Fig. 2.4). A simple way to see this effect is that when intrinsic MOS is velocity saturated, the output characteristics become equidistant for equal

Figure 2.4:  $I_{DS}$  vs.  $V_{DS}$  from device simulation of 50V VDMOS transistor. The quasisaturation effect is evident at higher  $V_{GS}$  for this device.

increase in  $V_{GS}$ .

(c) Velocity saturation in the drift region: Another saturation mechanism can occur due to velocity saturation in the drift while intrinsic MOS is still not saturated. Actually this cannot be called saturation as current does not get saturated. If drift is velocity saturated and intrinsic MOS is in linear region, the increase in  $V_{GS}$  does not increase current level significantly and gate bias has no or little effect (see  $V_{GS} = 2, 2.5, 3, 3.3V$  in Fig. 2.4). This effect is called quasi-saturation, which is generally observed at high  $V_{GS}$ .

Note that all or any two of the three effects described above may superimpose with each other and, sometimes, they may not be separable from each other.

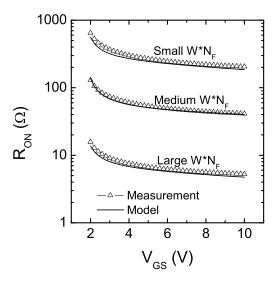

The quasi-saturation effect can be reduced by reducing the resistivity of the drift region and parasitic JFET in VDMOS transistor [27]. The reduction in the quasi-saturation effect increases the current carrying capability of the devices and decreases the on-resistance. One possible method of achieving this is to exploit the trench technology [39], which allows the gate to be extended down into the intercell region. Even though it reduces the quasi-saturation effect, it introduces a corner in the trench which affects the blocking capability of the device. Another method is to use the ion-implantation into the JFET structure of VDMOS, which reduces the quasi-saturation effect with little change in the blocking capability [27].

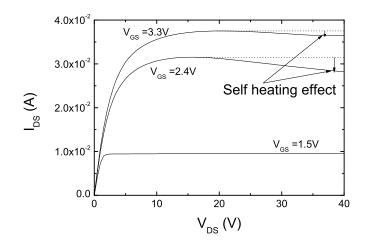

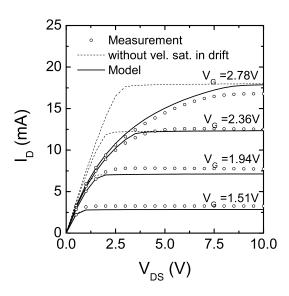

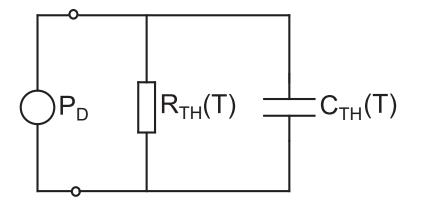

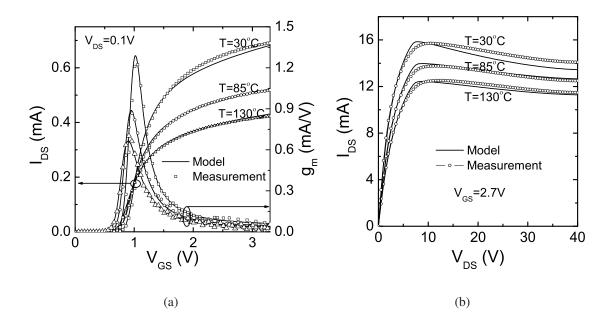

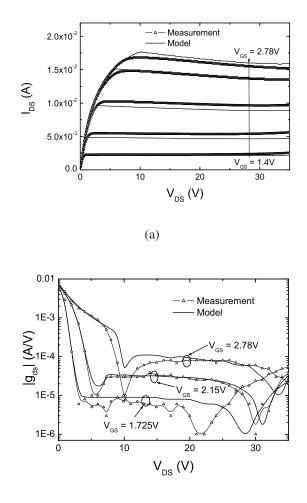

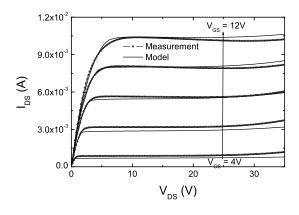

### 2.2.2 Self-Heating Effect

The self-heating effect (SHE) [40, 41, 42, 43, 44, 45, 46, 47] represents the heating of the device due to its internal power dissipation. This effect appears, when high levels of power are attained in the device. The dissipated heat leads to an increase in the internal temperature of the device and modifies the I - V characteristics. Fig. 2.5 shows the  $I_{DS} - V_{DS}$  characteristics of a 40V LDMOS transistor. The decrease in the current with increasing  $V_{DS}$  is caused by the self heating effect. As  $V_{DS}$  increases, the current starts rising. The increase in the current ( $I_{DS}$ ) as well as voltage across the device ( $V_{DS}$ ) increase the power dissipation ( $I_{DS}V_{DS}$ ) inside the device. As

Figure 2.5: Measured  $I_{DS}$  vs.  $V_{DS}$  of 40V LDMOS transistor. The decrease in the current with increasing  $V_{DS}$  is due to self heating effect.

discussed above, the increase in power dissipation increases temperature which affects other transistor parameters (e.g. mobility, threshold voltage etc.). The rise in temperature decreases mobility due to scattering which in turn decreases the current showing negative resistance on output characteristics.

The internal temperature increase due to self heating effect influences the device characteristics mainly by affecting the mobility, threshold voltage and velocity saturation. In the literature, this effect was mainly studied on the SOI devices and the proposed models for SHE are distributed or non-distributed models. As expected, better accuracy is obtained from distributed models, which offer a larger flexibility for the current simulation. Still, the clear advantage of the non-distributed models over the distributed ones is the parameter extraction procedure, as non-distributed approach offers a simple and efficient representation of the problem. The detailed discussion of self-heating effect and its modeling has been covered in [47] and also in section 3.4.2 of chapter 3.

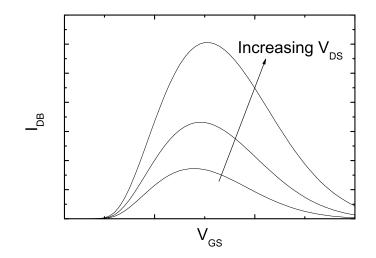

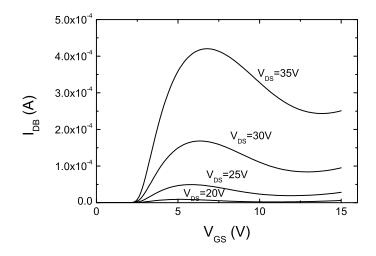

#### 2.2.3 Impact Ionization Effect

Before discussing the impact ionization effect is HVMOS, lets review this effect for conventional low voltage MOSFETs [48].

The increase in the  $V_{DS}$  in the MOSFET increases the longitudinal electric field in the channel increasing from source to drain. For abrupt source and drain junctions, the peak field is at the drain-to-channel junction, and its value depends on  $V_{DS}$  and channel length L. When carriers move in the fields that exceed the value of the onset of velocity saturation, they continue to acquire kinetic energy from the field but their velocity is randomized by the excessive collisions such that their velocity along the field direction no longer increases but their kinetic energy does. Depending on the statistics of scattering, a small fraction of the overall carrier population acquires a significant amount of energy, and these are called hot carriers. Clearly, the higher the field, the higher the proportion of hot carriers. Generally, in MOSFETs, the high

Figure 2.6: Substrate current vs. gate-source voltage, with drain-source voltage as a parameter.

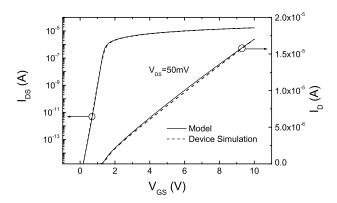

fields are encountered in saturation in the pinchoff region. For large longitudinal electric field, the cool electrons are coming into the pinchoff region and are heated by the field. Some of them acquire enough energy to create impact ionization of silicon atoms, whereby new electrons and holes are created; this effect is also referred to as weak avalanche. The new electrons join the stream of channel electrons and move toward the drain. The normal depletion field in the channel pushes the holes into the substrate, where they give rise to drain-to-substrate current  $(I_{DB})$ . This current is proportional to the number of electrons available per unit time, which in turn is proportional to  $I_{DS}$ . Also, according to above discussion,  $I_{DB}$  is an increasing function of the maximum field at the drain; this field is, in turn, a function of the excess drain voltage  $(V'_{DS})$ . Fig. 2.6 shows the typical  $I_{DB} - V_{GS}$  curve for MOSFET. For a given  $V_{DS}$ , when  $V_{GS}$  is increased starting from low values,  $I_{DS}$  increases, and thus  $I_{DB}$  increases too, according to above discussion. Further increase in  $V_{GS}$  increases the saturation voltage significantly, causing a strong decrease in  $V_{DS} - V'_{DS}$ , and thus in the maximum field at the drain. The maximum  $I_{DB}$  is observed, roughly, at  $V_{GS} = V_{DS}/2$ .

The impact ionization in the HVMOS device has the contributions from both the channel region and the drift region. Fig. 2.7 shows the  $I_{DB} - V_{GS}$  curve for LDMOS transistor. At low current, the hot carriers are generated near the channel while at high current levels, hot carriers are generated near the drain end in the drift region. This is why there is an increase in the  $I_{DB}$  at higher  $V_{GS}$ . The impact ionization in the drift can be reduced with the field plate configuration [49]. The step drift region or deep drift design proposed in the literature also helps in the reduction of hot carriers in the drift region [49].

Figure 2.7: Measured substrate current vs. gate-source voltage for 40V LDMOS transistor.

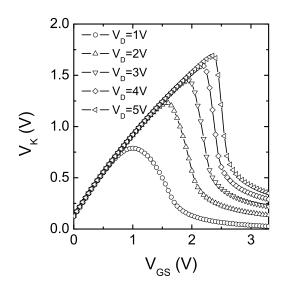

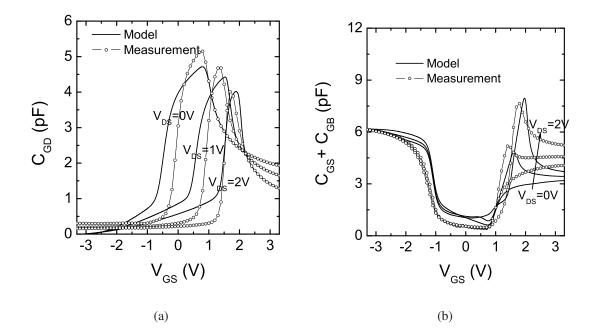

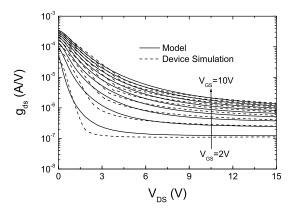

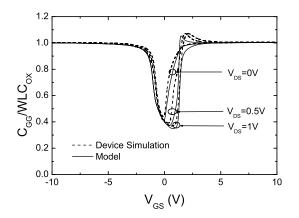

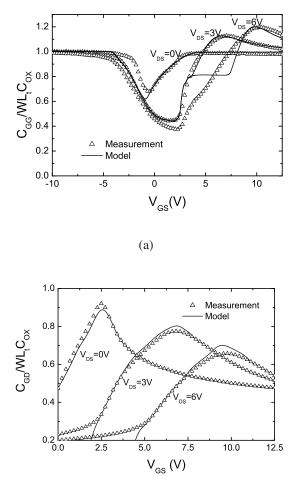

### 2.3 AC behavior of HV-MOSFETs

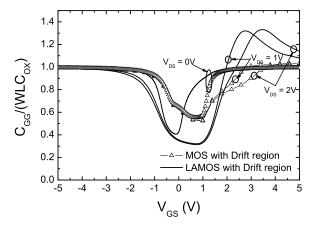

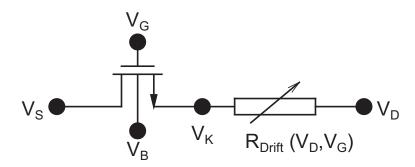

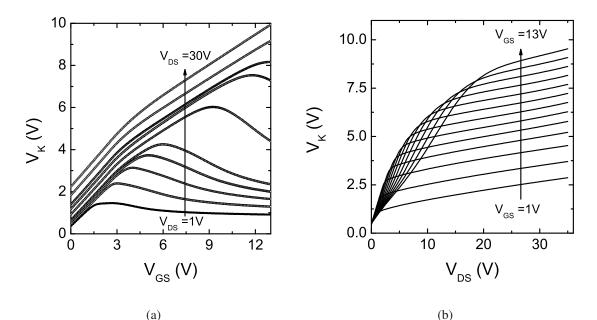

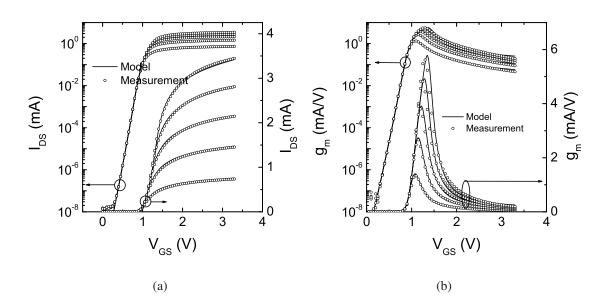

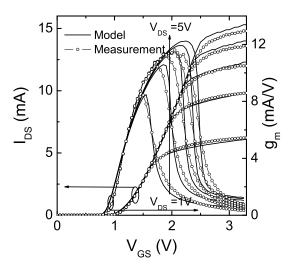

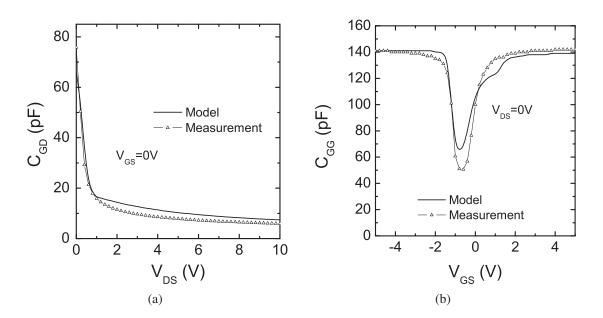

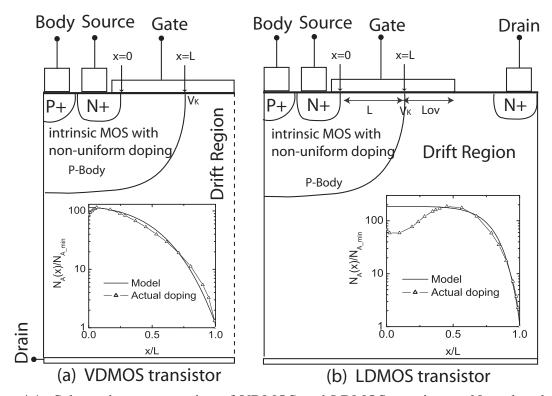

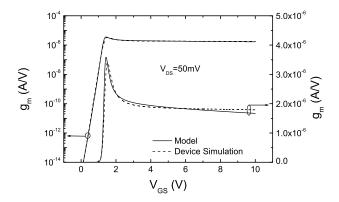

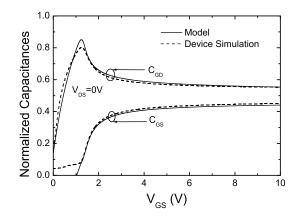

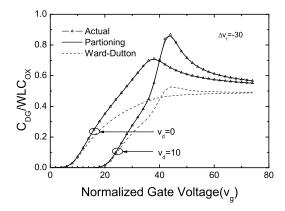

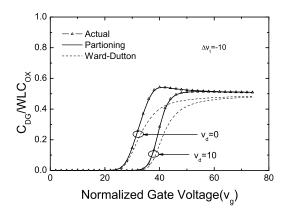

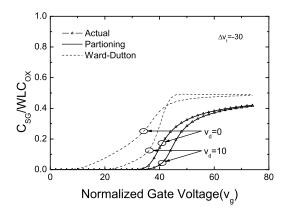

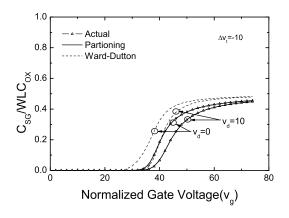

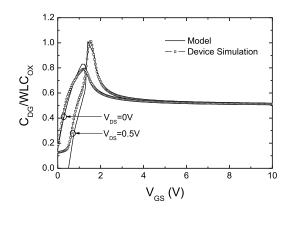

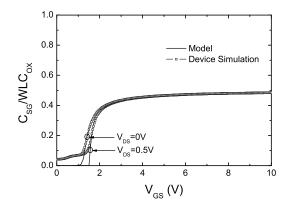

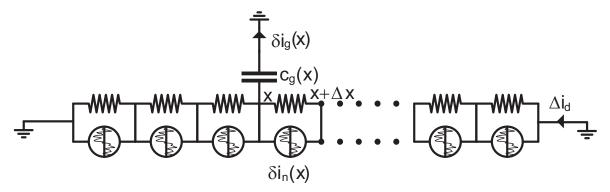

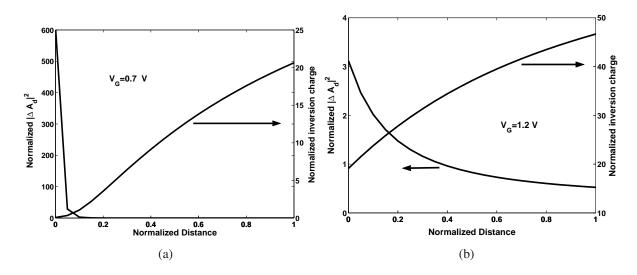

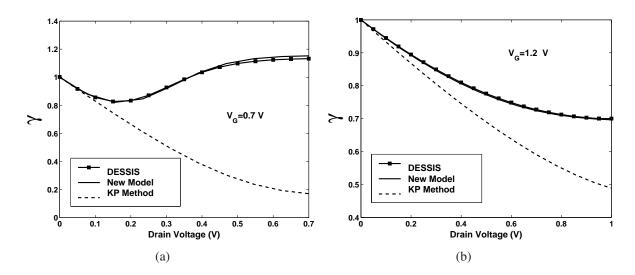

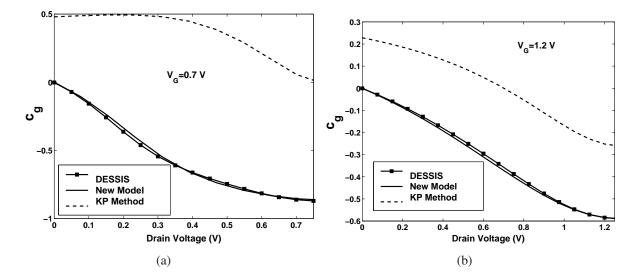

The special behavior of HV-MOS e.g. LDMOS, VDMOS capacitances has been under study in research community for many years [50, 51, 52, 53, 54, 55]. In literature, generally the HV-MOS capacitances have been studied together with drift region [52, 53], which makes it difficult to separately understand and analyze the impact of lateral non-uniform doping and drift region. The unique capacitance characteristics of HV-MOS originates from the device architecture of HV-MOS. The major difference between HV-MOS and conventional MOS is the lateral nonuniform doping in the channel and the drift region, which affects the capacitances depending on the bias regime. The unique behavior of  $C_{GD}$  in high voltage devices has been analyzed in detail in the literature [50, 51, 53]. Frére et al. [50] showed that the peaks in  $C_{GD}$  are actually originating from LAMOS. Liu et al. [53] reproduced the peaks in  $C_{GD}$  of VDMOS transistor using small signal analysis. Here, the effect of lateral non-uniform doping and drift region on capacitance characteristics of HV-MOS will be separately analyzed and compared with conventional MOS characteristics [56]. To analyze the capacitance behavior of HV-MOS, we will divide the analysis in two parts - Impact of lateral non-uniform doping and drift region. For this we will have four cases as shown in Fig. 2.8: (1) Conventional MOS with uniform doping in the channel and (2) Lateral Non-uniformly doped or Lateral Asymmetric MOS (LAMOS) with lateral doping gradient in the channel, (3) Conventional MOS with uniform doping in the channel and a drift region to sustain high voltage, and (4) LAMOS with a drift region to sustain high voltage. The intrinsic drain potential in Fig. 2.8(b) will be called  $V_K$ , which is the point where channel meets the drift region.

### 2.3.1 Effect of Lateral Non-uniform doping

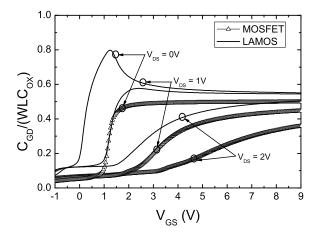

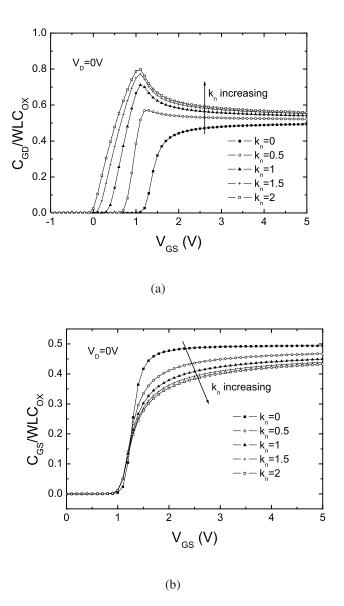

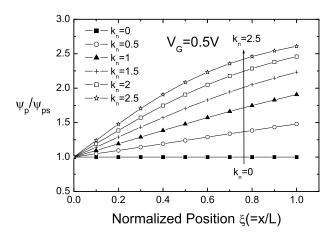

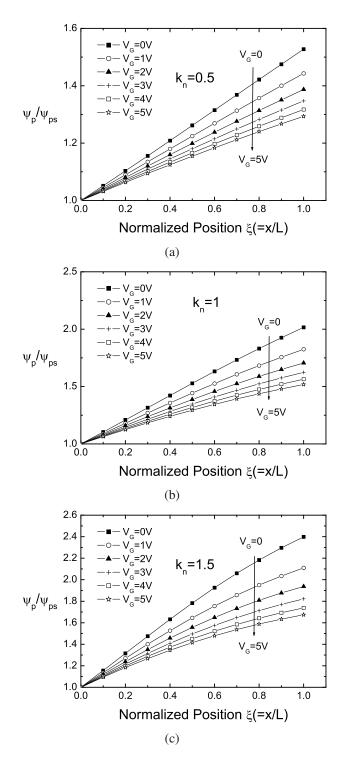

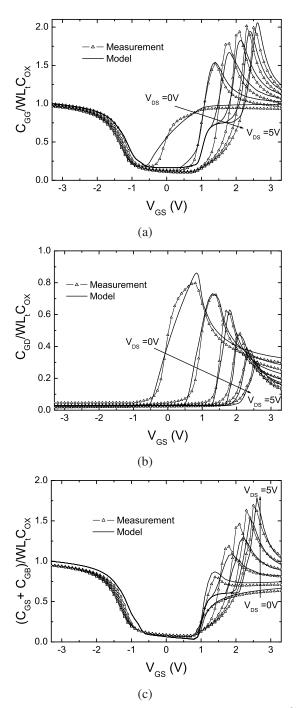

Here we will explain, how lateral non-uniform doping affects the small signal capacitance behavior of high-voltage MOSFETs. Fig. 2.8(a) shows the device architecture under study. To see the impact of lateral non-uniform doping on capacitances, let's start with  $C_{GD}$  capacitance. Fig.

Figure 2.8: Device architectures of  $(L_{ch}=2\mu m)$ : (a) Conventional MOSFET with uniform doping and LAMOS with lateral doping gradient in the channel. The lateral doping gradient is approximated by the complementary error function  $N_A(x) = N_S.erfc[k_n(\xi)]$  [57, 58, 59], where  $\xi = \frac{x}{L_{ch}}$  is the normalized position along the channel,  $k_n$  is a parameter representing the doping gradient. The doping level at the source side of the channel  $(N_S)$  is highest and decreases towards the drain in the channel region. Higher  $k_n$  means sharp decrease in the doping level from source to drain and vice-versa. (b) Conventional MOSFET with uniform doping and LAMOS with lateral doping gradient in the channel and a drift region to sustain high voltage.

2.9 shows the  $C_{GD}$  vs.  $V_{GS}$  using device simulation for different drain voltages. As expected, the  $C_{GD}$  at  $V_{DS} = 0$  for conventional MOS stays low values for  $V_{GS} < V_T$  (threshold voltage). As  $V_{GS}$  starts to increase beyond  $V_T$ , the  $C_{GD}$  increases sharply and saturates to  $\frac{1}{2}WLC_{OX}$ . The situation is completely different for LAMOS. Due to lateral non-uniform doping, the  $C_{GD}$ starts increasing as soon as  $V_{GS}$  is more than the surface inversion potential at drain side. It means that the inversion at the drain side starts at lower values of  $V_{GS}$  than source side because of the lower doping at the drain end compared to source end. As  $V_{GS}$  keeps on increasing, the inversion in the channel propagates from drain towards source and  $C_{GD}$  keeps on rising. Once  $V_{GS}$  is greater than the surface inversion potential at source side (or  $V_T$  of LAMOS), the  $C_{GD}$ starts to fall [51]. This can be explained by the fact the rise in inversion charge is exponential for  $V_{GS} < V_T$  and after that rise gets slower ultimately becoming linear function of  $V_{GS}$ . In strong

Figure 2.9: The gate-to-drain capacitance  $C_{GD}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The lateral non-uniform doping in LAMOS produces peaks in  $C_{GD}$  capacitances at low drain bias.

Figure 2.10: The gate-to-source capacitance  $C_{GS}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The lateral non-uniform doping in LAMOS produces peaks in  $C_{GS}$  capacitances around  $V_{GS} = V_T$ .

inversion ( $V_{GS} >> V_T$ ), the  $C_{GD}$  saturates to some value equal to or higher than  $\frac{1}{2}WLC_{OX}$  depending on the doping gradient in the channel [58, 59]. The impact of different doping gradients on capacitances will be explained later in this section. Increasing drain voltage reduces the peak due to depletion at drain side. For sufficiently high values of drain voltages, there may not exist any peak in  $C_{GD}$  (e.g.  $V_{DS} \ge 2V$  in Fig. 2.9).

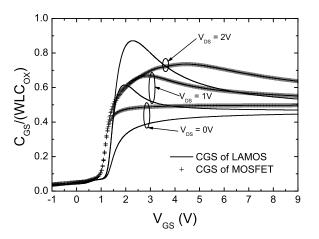

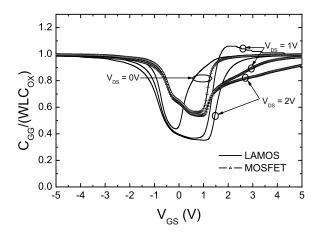

Another interesting property of LAMOS capacitances is seen on  $C_{GS}$  and  $C_{GG}$  behavior as shown in Fig. 2.10 and Fig. 2.11. The  $C_{GS}$  at  $V_{DS} = 0$  is similar to MOSFET (except lower values due to low doping in the drain side), where the increase in  $C_{GS}$  occurs when channel gets inverted ( $V_{GS} \ge V_T$ ). The situation is quite different for  $V_{DS} > 0$ . For  $V_{DS} < V_{GS} - V_{TD}$ (threshold voltage corresponding to the doping at drain), the  $C_{GS}$  is slightly higher than its value at  $V_{DS} = 0$  and behaves similar to the MOS capacitance. But if  $V_{DS} > V_{GS} - V_{TD}$ , the

Figure 2.11: The gate-to-gate capacitance  $C_{GG}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The lateral nonuniform doping in LAMOS produces peaks in  $C_{GG}$  capacitances, when  $V_{GS}$  is around threshold voltage for small nonzero  $V_{DS}$ .

drain end is depleted. For these drain voltages, as  $V_{GS}$  increases, there will be small increase in the channel charge from drain side until  $V_{GS} < V_T$ . At  $V_{GS} = V_T$ , there is sudden flow of large amount of charges from source end (the small signal resistance seen from any point in the channel towards the drain will be higher than towards the source and charges choose the least resistive path, which is source side in this case) and whole of the channel gets filled up by these charges. This sudden rise in the charge from source side gives rise to increased peaks in  $C_{GS}$ for higher drain voltages as shown in Fig. 2.10.

It is interesting to note that  $C_{GG}$  also has small peaks for  $V_{DS} = 1$  V as shown in Fig. 2.11, which was also shown in [60] for nonzero small  $V_{DS}$ . These peaks in  $C_{GG}$  can be explained by the fact that for  $V_{GS} \leq V_T$ , the source end of the channel is still in weak inversion while drain end is in depletion. Once  $V_{GS}$  reaches close the  $V_T$ , there will be sudden flow of charge from source side giving sharp increase in  $C_{GG}$ . This is not the case with the  $C_{GG}$  of conventional MOS, where continuous supply of charge is maintained from source side due to uniform doping. Also note that for low drain voltages, there will be large supply in the charge from drain end also once it comes out of depletion which again helps in increasing the total channel charge. Note that the peak vanishes as  $V_{GS}$  increases significantly above threshold voltage as now inversion charge is being supplied from both source and drain, and now gate charge is a linear function of gate voltage. For high values of drain voltages, no peak is observed, as charges entering from source end also contributes in removing the depletion at the drain side. Hence, the peak in  $C_{GG}$  occurs for small nonzero values of  $V_{DS}$ , when  $V_{GS}$  is around threshold voltage (source end entering into strong inversion from weak/moderate inversion). Another note on the  $C_{GG}$  of LAMOS is that the dip (lowest value) is lower compared to  $C_{GG}$  of MOS. This is due to the lower doping in the drain side which produces sharper and lower dip on  $C_{GG}$ . This can also be analyzed using segmentation approach, where LAMOS channel can be divided in several smaller channel length MOS with uniform doping in each channel but varying across different MOS giving equivalent non-uniform doping also called graded channel approach [60, 61].

Figure 2.12: The drain-to-gate capacitance  $C_{DG}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The lateral non-uniform doping in LAMOS produces peaks in  $C_{DG}$  capacitances. The peaks in the  $C_{DG}$  can be higher than  $WLC_{OX}$  depending on the doping profile and drain voltage [58]. The bias dependent partitioning scheme [62, 63] also explain these peaks.

The behavior of  $C_{DG}$  capacitances is also quite different for LAMOS [60, 64, 62, 63] as shown in Fig. 2.12. Similar to other capacitances of LAMOS, peaks are also observed on  $C_{DG}$ . The peak in  $C_{DG}$  at  $V_{DS} = 0$  can be explained similar to the peak in  $C_{GD}$  at  $V_{DS} = 0$ . As gate voltage increases, the drain end of the channel gets inverted and  $C_{DG}$  starts increasing till source end get inverted and after that it decreases and saturates. In fact  $C_{GD}$  and  $C_{DG}$  are exactly same for  $V_{DS} = 0$ . But for nonzero drain voltages,  $C_{DG}$  has totally different behavior than  $C_{GD}$ . At  $V_{DS} = 1V$ , note that the peak increases because a change in gate voltage induces a change in the channel potential (the perturbed channel potential becomes negative), which in turn causes a change in charge distribution and the combined effect increases the peak [62, 63]. To understand why perturbed channel potential can become negative to increase the small signal charge, consider the situation, when the source end is weakly inverted and drain end is strongly inverted. In this case the transistor can be thought of a series combination of two transistors with different threshold voltages, where the one near the source is weakly inverted and near the drain end is strongly inverted. Now let  $Q_S$  and  $Q_D$  be the charge at the source and drain end of the strongly inverted transistor. The current flowing through the transistor is proportional to  $Q_S^2 - Q_D^2$  [62, 63, 65, 66]. The weakly inverted transistor in series forces current to be very small, therefore  $Q_S^2 \approx Q_D^2$ . Now as gate voltage increases both  $Q_S$  and QD will change and we have  $\delta Q_S \cdot Q_S \approx \delta Q_D \cdot Q_D$ . As drain end is kept at a fixed channel potential and is in strong inversion  $\delta Q_D \approx C_{OX} \delta V_{GS}$ . So we have  $\delta Q_S / \delta V_{GS} = (Q_D / Q_S) C_{OX}$ . As  $Q_D > Q_S$ in this situation (because the drain end has lower doping), we have  $\delta Q_S / \delta V_{GS} > C_{OX}$ , which is only possible if the channel potential goes negative and aids the gate voltage. Depending on the doping profile in the channel and drain voltage, the peak in  $C_{DG}$  may even increase above  $WLC_{OX}$  in presence of a gate voltage [62, 58].

The above analysis was made using single value of doping gradient  $(k_n)$  in the channel of LAMOS. If the value of doping gradient  $(k_n)$  is increased giving sharper doping profile

Figure 2.13: Effect of different doping gradients  $(k_n)$  on LAMOS: (a) Normalized  $C_{GD}$  and (b) normalized  $C_{GS}$  at  $V_{DS}$ =0. Note that the peak in  $C_{GD}$  increases, while  $C_{GS}$  in strong inversion decreases with increase in doping gradient. The  $k_n$ =0 corresponds to uniformly doped MOSFET.

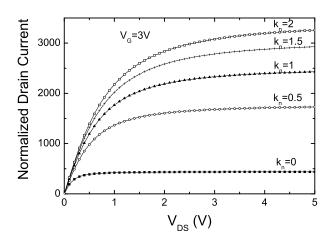

in the channel, the peaks on  $C_{GD}$  increases and value of  $C_{GS}$  decreases in strong inversion, while the rising slope on both capacitances decreases [58] as shown in Fig. 2.13(a) and (b). The lateral doping gradient in the channel also affects DC characteristics of LAMOS. Higher doping gradient increases the saturation voltage and saturation current on the output characteristics as shown in Fig. 2.14. The prolonged linear region in the output characteristics and peaks/slopes on capacitances can be explained by the fact that doping gradient changes the surface potential required for the inversion across the channel decreasing from source to drain.

Figure 2.14: Effect of different doping gradients  $(k_n)$  on LAMOS: Normalized drain current  $\frac{I_D}{2n_q\mu_0}\frac{W}{L}C_{OX}U_T^2$  at  $V_{GS}$ =3V (strong inversion). Note that the linear region extends, current as well as saturation voltage increases and  $R_{ON}$  decreases with increase in doping gradient. The  $k_n$ =0 corresponds to uniformly doped MOSFET.

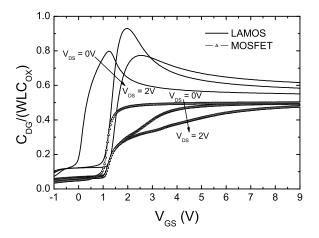

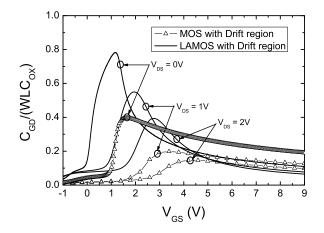

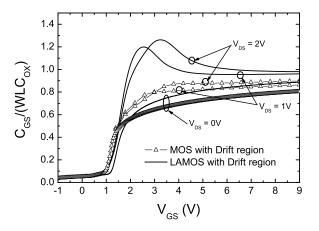

### 2.3.2 Effect of drift region

Fig. 2.8(b) shows the device architecture under study. The effect of the drift region (without any gate overlap) is to lower the  $C_{GD}$  capacitance value in strong inversion (see LAMOS with drift region in Fig. 2.15). It is interesting to note that the  $C_{GD}$  for a conventional MOS with drift (e.g. DEMOS or LDD-MOS transistor) also shows decrease of capacitance at higher gate bias, but it should not be confused as peak in capacitance because it is always less than or equal to  $\frac{1}{2}WLC_{OX}$  (see MOS with drift in Fig. 2.15). The rising part of  $C_{GD}$  is mainly given by lateral asymmetry in the channel as explained above, while the fall in  $C_{GD}$  is heavily affected by the drift region also demonstrated in Fig. 2.15. As mentioned earlier, the lateral non-uniform doping produces peaks in  $C_{GG}$  and  $C_{GS}$  around threshold voltage. The drift region gives higher peaks and also shifts the position of peaks as shown in Fig. 2.16 and Fig. 2.17 for nonzero  $V_{DS}$ . To understand it better, we can write the normalized  $C_{GG}$  expression as,

$$C_{GG} = \frac{dQ_G(V_G, V_K, V_S, V_B)}{dV_{GS}}$$

=  $\frac{\partial Q_G(V_G, V_K, V_S, V_B)}{\partial V_G} + \frac{\partial Q_G(V_{GS}, V_K, V_S, V_B)}{\partial V_K} \frac{dV_K}{dV_G}$  (2.1)

=  $C_{GG(LAMOS)} - C_{GD(LAMOS)} \frac{dV_K}{dV_G}$

Here  $V_K$  is the intrinsic drain potential (the point where LAMOS meets drift region in high voltage devices) as shown in Fig. 2.8. If there is no drift region, then  $V_K = V_D$  and second term in (4.26) vanishes as  $\frac{dV_K}{dV_G} = 0$ . In the presence of the drift region,  $V_K$  is not fixed and will vary to maintain a constant current from drain to source. If there is a slight positive change  $\partial V_G$  in  $V_G$ , the LAMOS current will increase. Now to increase the current in the drift region to the level of LAMOS,  $V_K$  should decrease as  $V_D$  is fixed. Larger the drift resistance, larger

Figure 2.15: The gate-to-drain capacitance  $C_{GD}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The value of  $C_{GD}$  is lowered due to drift region. Higher the value of drift resistance (quasi-saturation or current crowding effect), sharper will be the decrease in  $C_{GD}$  capacitance.

should be the drop in  $V_K$ . Thus  $\frac{dV_K}{dV_G}$  will be negative for positive values of  $\partial V_G$  and from (4.26), it is evident that  $C_{GG}$  of any high voltage device would be larger than  $C_{GG(LAMOS)}$  and will increase with higher drift resistance for nonzero  $V_{DS}$ . From modeling point of view, a good model for HV-MOS needs both excellent modeling of intrinsic MOS channel (which provides  $C_{GG(LAMOS)}$ ) and drift region (which dictates derivative of  $V_K$ ) [58, 54, 67].

Similarly  $C_{GS}$  can be expressed as,

$$C_{GS} = -\frac{Q_G(V_G, V_K, V_S, V_B)}{dV_S}$$

=  $-\frac{\partial Q_G(V_G, V_K, V_S, V_B)}{\partial V_S} - \frac{\partial Q_G(V_G, V_K, V_S, V_B)}{\partial V_K} \frac{dV_K}{dV_S}$  (2.2)

=  $C_{GS(LAMOS)} + C_{GD(LAMOS)} \frac{dV_K}{dV_S}$

If there is a slight positive change  $\partial V_S$  in  $V_S$ , the LAMOS current will decrease. Now to decrease the current in the drift region to the level of LAMOS,  $V_K$  should increase as  $V_D$  is fixed. Larger the drift resistance, larger should be the increase in  $V_K$ . Thus  $\frac{dV_K}{dV_{GS}}$  will be positive for positive values of  $\partial V_S$  and from (2.2), it is evident that  $C_{GS}$  of any high voltage device would be larger than  $C_{GS(LAMOS)}$  and will increase with higher drift resistance for nonzero  $V_{DS}$ .

Above analysis of capacitances did not include the drift region with gate overlap. The effect of gate overlap in the drift region is to increase the capacitances as the total gate charge increases due to the accumulation of electrons in the overlap region for positive gate voltages or vice-versa. There is also diffusion of charges from gate overlapped drift region into LAMOS in HV-MOS, which again helps in increasing the total gate charge [52].

Figure 2.16: The gate-to-source capacitance  $C_{GS}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The peak and value of  $C_{GS}$  is increased due to drift region. Higher the value of drift resistance (quasi-saturation or current crowding effect), sharper will be the increase in  $C_{GS}$  capacitance.

Figure 2.17: The gate-to-gate capacitance  $C_{GS}$  vs.  $V_{GS}$  for  $V_{DS} = 0,1$  and 2V. The peaks in  $C_{GG}$  is increased due to drift region. Higher the value of drift resistance (quasi-saturation or current crowding effect), sharper will be thepeaks in  $C_{GG}$  capacitance.

### 2.4 Conclusion

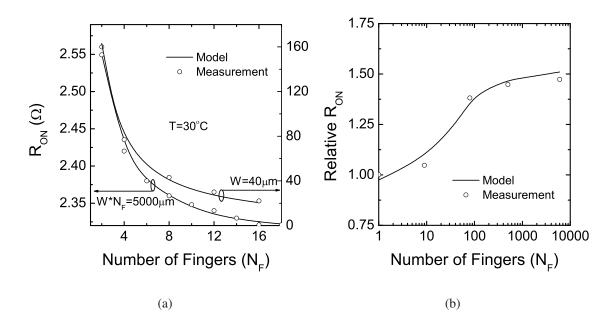

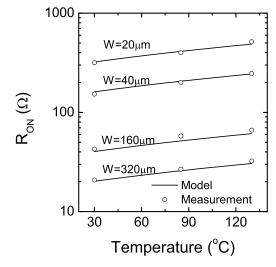

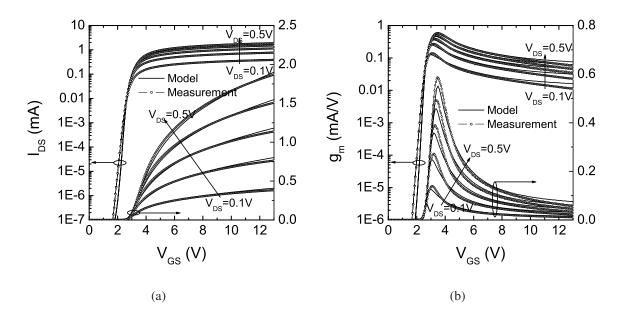

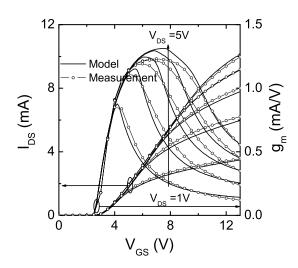

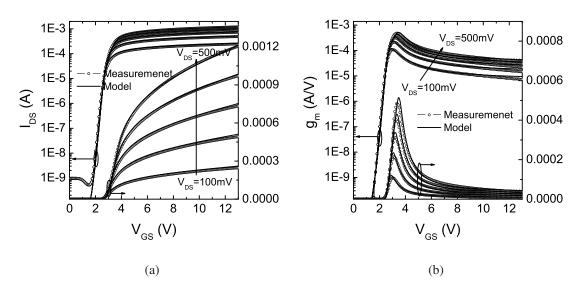

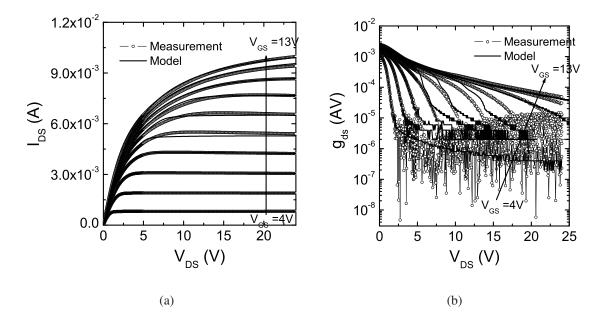

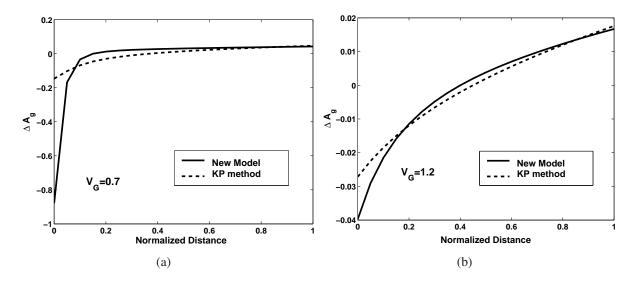

In this chapter, an overview of high voltage MOSFET architecture was presented. Three main device architectures of high-voltage devices, Drain-Extended MOSFET, Lateral double-diffused MOSFET and Vertical double-diffused MOSFET, normally used with CMOS technology, were discussed. Several advantages and disadvantages of these architectures were also pointed out. Due to several different types of asymmetric architectures, there has been no single model for these devices.