## COPPER/LOW-K TECHNOLOGICAL PLATFORM FOR THE FABRICATION OF HIGH QUALITY FACTOR ABOVE-IC PASSIVE DEVICES

## THÈSE N° 3831 (2007)

PRÉSENTÉE LE 22 JUIN 2007

PRÉSENTÉE À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR

Laboratoire d'électronique générale 2

SECTION DE GÉNIE ÉLECTRIQUE ET ÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

### Marcelo Bento PISANI

M.Sc. in Electrical Engineering, University of São Paulo, Brésil et de nationalité brésilienne

acceptée sur proposition du jury:

Dr J.-M. Sallèse, président du jury Prof. M. A. Ionescu, Dr C. Hibert, directeurs de thèse Dr X. Gagnard, rapporteur Prof. G. Piazza, rapporteur Prof. R. Popovic, rapporteur

Copyright © 2007 by Marcelo B. Pisani

Ainda bem que você veio comigo, Porque senão, o que seria da vida? Nos dias frios... (Vanessa da Mata)

Esta tese é dedicada à minha esposa Roberta Maria.

# **Table of Contents**

| Abstract                                                      | ix   |  |

|---------------------------------------------------------------|------|--|

| Version abrégée                                               | xi   |  |

| List of abbreviations and acronyms                            | xiii |  |

| List of symbols and units                                     | Xvii |  |

|                                                               |      |  |

| Chapter 1. Introduction                                       | 1    |  |

| 1.1. Organization of the thesis                               | 2    |  |

| 1.2. MEMS and RF MEMS passive devices                         | 3    |  |

| 1.3. Motivation and objectives                                | 6    |  |

| 1.4. State-of-the-art on RF MEMS                              | 8    |  |

| 1.5. Quality factor enhancement techniques                    | 11   |  |

| Chapter 2. Integrated inductors                               | 18   |  |

| 2.1. Inductors and inductance                                 | 18   |  |

| 2.2. Quality factor and self-resonant frequency               | 19   |  |

| 2.3. Inductance calculation                                   | 22   |  |

| 2.3.1. Inductance of a system of conductors                   | 23   |  |

| 2.3.2. Elementary inductance calculations                     | 24   |  |

| 2.3.3. Mutual inductance between current filaments            | 25   |  |

| 2.4. Spiral inductors                                         | 27   |  |

| 2.5. Other types of integrated inductors                      | 30   |  |

| 2.6. Simplified physical model of integrated spiral inductors | 31   |  |

| Summary                                                       | 36   |  |

| Chapter 3. Copper / polyimide fabrication process             | 37   |  |

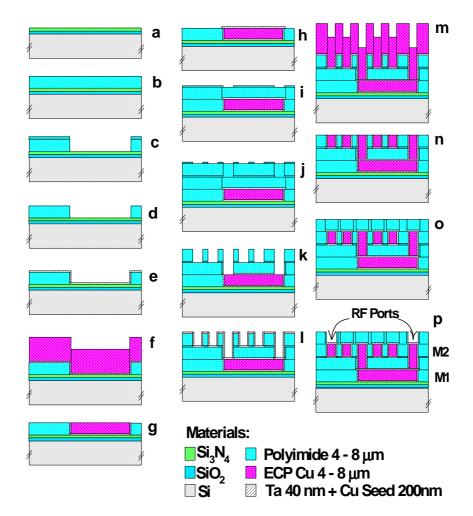

| 3.1. Proposed process flow                                    | 37   |  |

| 3.2. Development of the process flow                          | 39   |  |

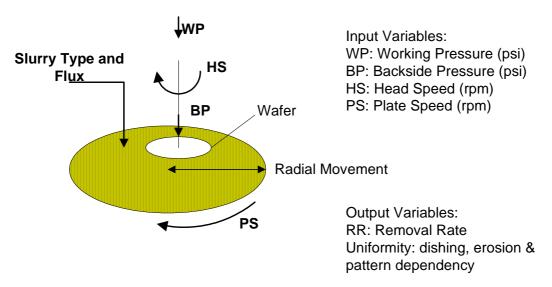

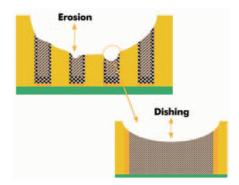

| 3.3. Copper CMP process                                       | 41   |  |

| 3.4. Adhesion and diffusion issues                            | 44   |  |

| 3.5. Fabrication results                                      | 45   |  |

| 3.5.1. Substrates used                                        | 45   |  |

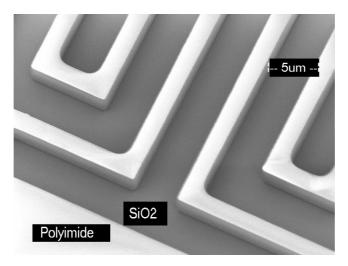

| 3.5 2. Wafer insulation                                       | 46   |  |

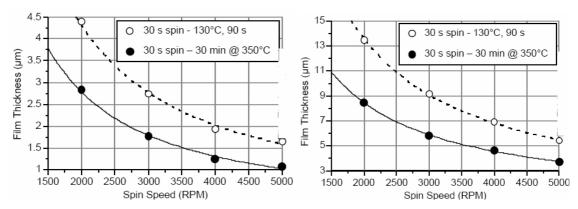

| 3.5.3. Polyimide deposition                                   | 46   |  |

| 3.5.4. Polyimide hard mask deposition                         | 49   |  |

|   | 3.5.5. Lithography                                                          | 49 |

|---|-----------------------------------------------------------------------------|----|

|   | 3.5.6. Hard mask definition                                                 | 50 |

|   | 3.5.7. Polyimide etch                                                       | 50 |

|   | 3.5.8. Hard mask removal                                                    | 51 |

|   | 3.5.9. Seed layer deposition                                                | 51 |

|   | 3.5.10. Copper electroplating                                               | 52 |

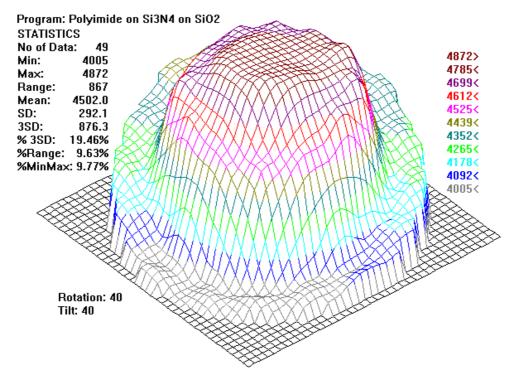

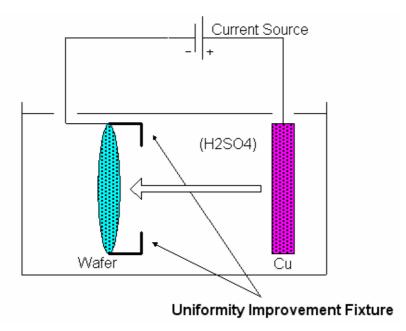

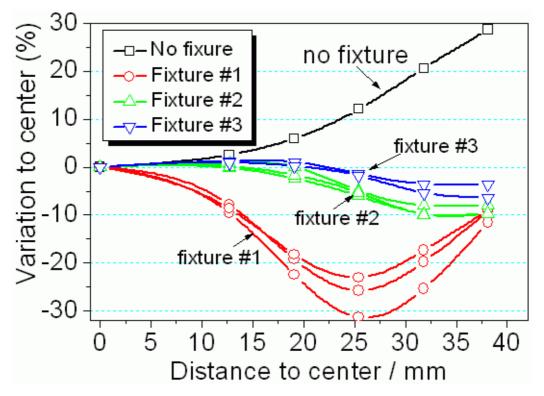

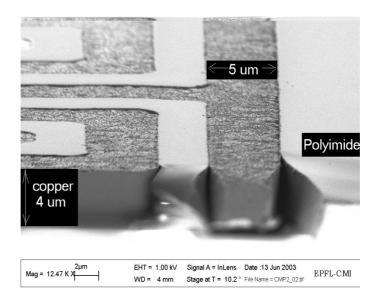

|   | 3.5.11. Electroplating uniformity optimization                              | 53 |

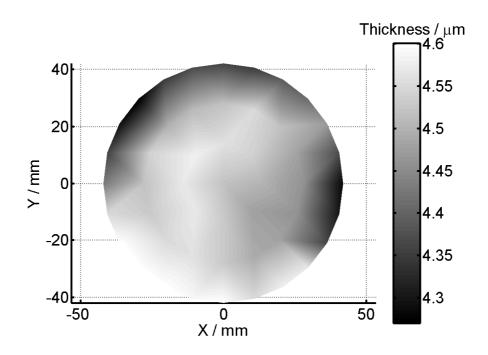

|   | 3.5.12. Copper CMP                                                          | 56 |

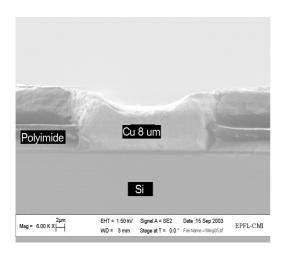

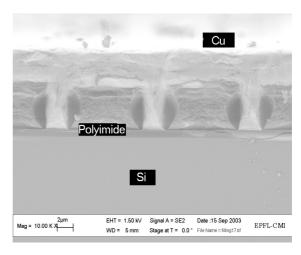

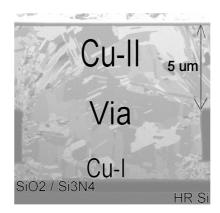

|   | 3.5.13. Two metal level process                                             | 57 |

|   | 3.6. Process characterization test structures                               | 59 |

|   | 3.6.1. Copper resistivity                                                   | 59 |

|   | 3.6.2. Via contact resistance                                               | 60 |

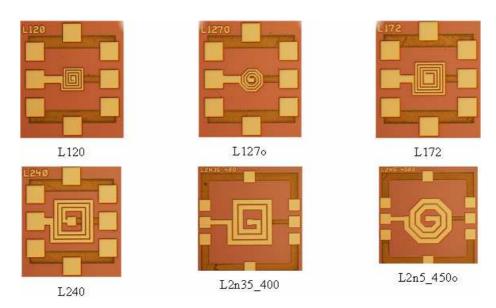

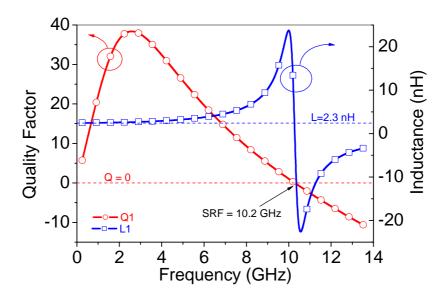

|   | 3.7. Fabricated devices and RF performances                                 | 63 |

|   | 3.8. Other process developments based on this process module                | 69 |

|   | 3.9. Filter applications using high Q passive devices                       | 70 |

|   | Summary                                                                     | 75 |

| C | hapter 4. High $f Q$ inductors and $f RF$ packaging using quartz substrates | 77 |

|   | 4.1. Fabrication process                                                    | 78 |

|   | 4.2. Fabrication results                                                    | 79 |

|   | 4.3. RF performance results                                                 | 80 |

|   | 4.4. Functionalized quartz packaging                                        | 83 |

|   | 4.5. Wafer-level packaging process                                          | 84 |

|   | 4.6. SU-8 photolithography                                                  | 85 |

|   | 4.7. Bonding process                                                        | 87 |

|   | 4.8. Packaging characterization                                             | 88 |

|   | 4.9. Bond strength and adhesion                                             | 89 |

|   | 4.10. Wettability                                                           | 89 |

|   | Summary                                                                     | 90 |

| C | hapter 5. Simulation, characterization, modeling and optimization of spiral | 93 |

|   | inductors                                                                   |    |

|   | 5.1. RF passive simulation tools                                            | 95 |

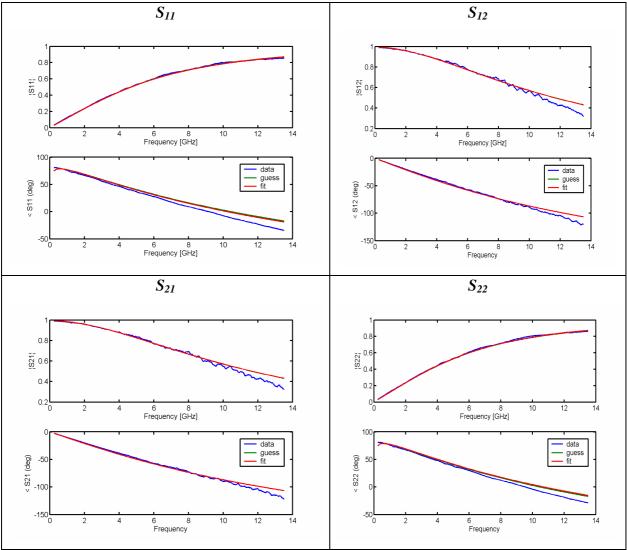

|   | 5.2. Measurement-based models                                               | 95 |

|   | 5.3. Simulation-based models                                                | 96 |

| 5.4. Analytical models                                                         | 96  |

|--------------------------------------------------------------------------------|-----|

| 5.5. ADS Momentum simulations                                                  | 98  |

| 5.6. HFSS simulation for a 2.5 nH inductor                                     | 100 |

| 5.7. Geometric parameter definitions                                           | 102 |

| 5.8. Inductor design space                                                     | 104 |

| 5.9. Influence of the RF pads and ground rings on the RF performance of spiral | 105 |

| inductors                                                                      |     |

| 5.10. Effect of metallization thickness and substrate resistivity              | 108 |

| 5.11. Physics based model for spiral inductors                                 | 109 |

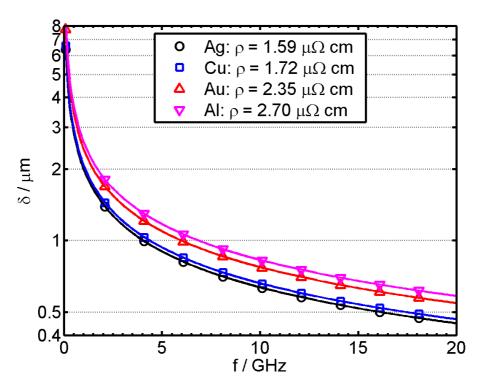

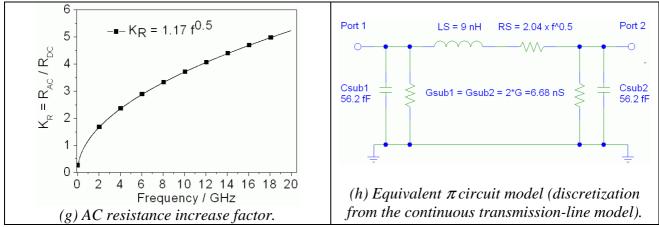

| 5.11.1. Spiral losses                                                          | 109 |

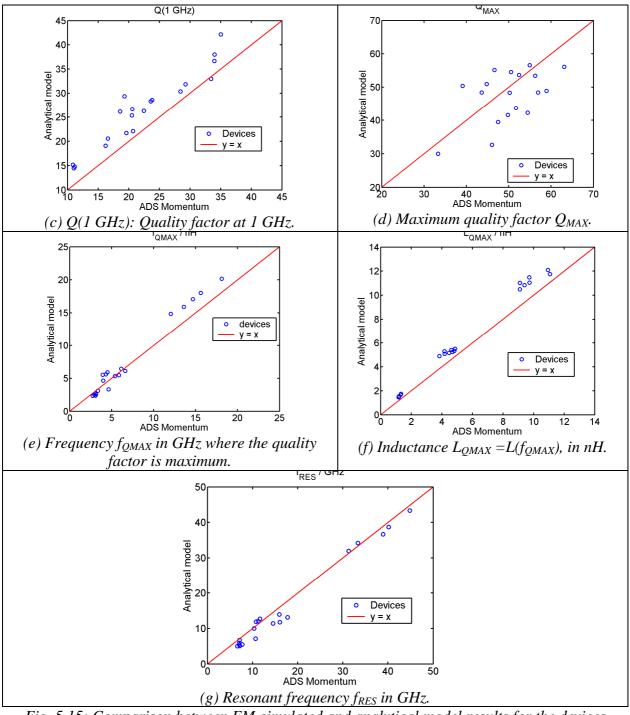

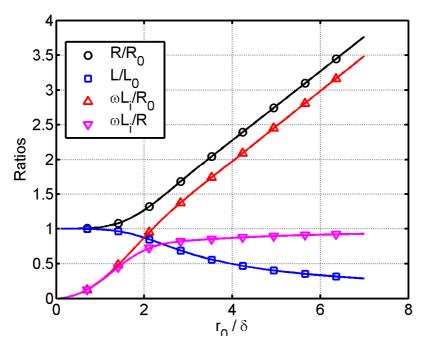

| 5.11.2. Current crowding effect                                                | 112 |

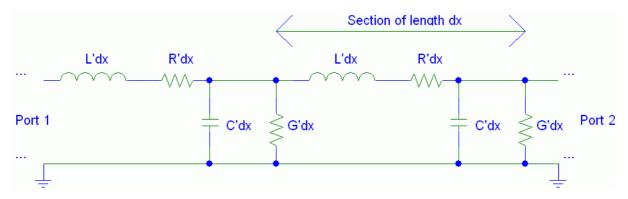

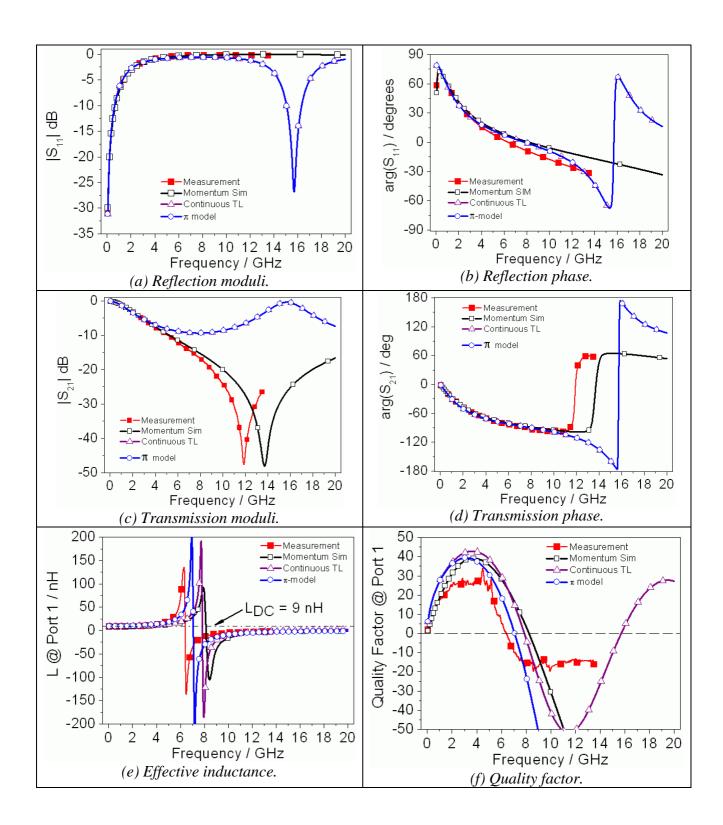

| 5.11.3. Coupled strip line model for spiral inductors                          | 114 |

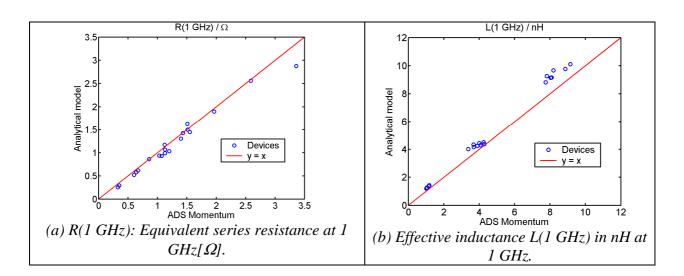

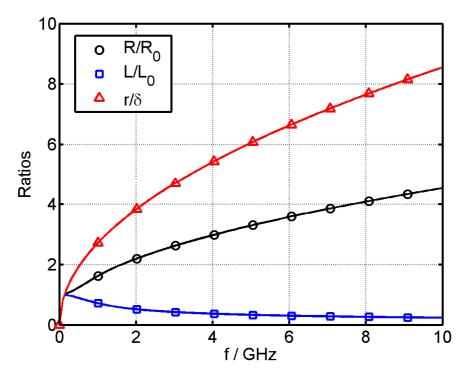

| 5.11.4. Comparison between the analytical model and EM simulations             | 123 |

| 5.11.5. Numeric optimization of inductor devices                               | 127 |

| Summary                                                                        | 129 |

| Chapter 6. Conclusions and perspectives                                        | 131 |

| 6.1. General conclusions                                                       | 131 |

| 6.2. Perspectives for future research                                          | 133 |

| Appendix A: Skin effect in conductors                                          | 135 |

| A.1. Cylindrical wire                                                          | 135 |

| A.2. Infinitely long and wide rectangular stripline with finite thickness      | 139 |

| A.3. Rectangular stripline                                                     | 141 |

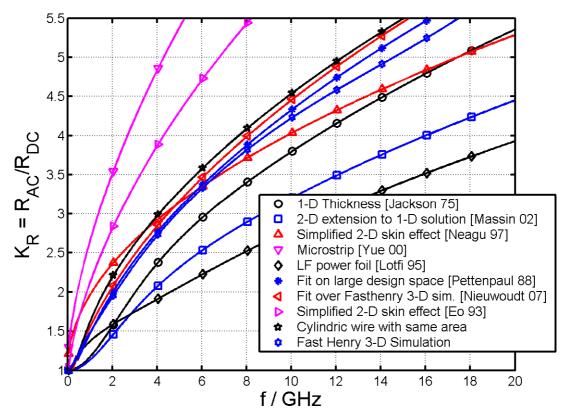

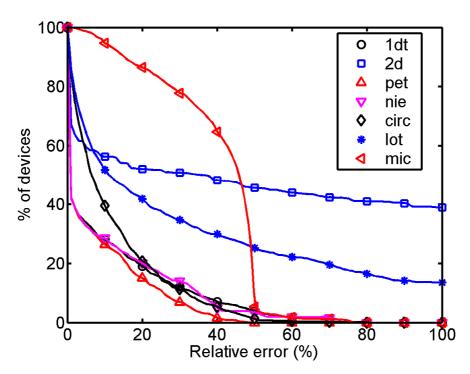

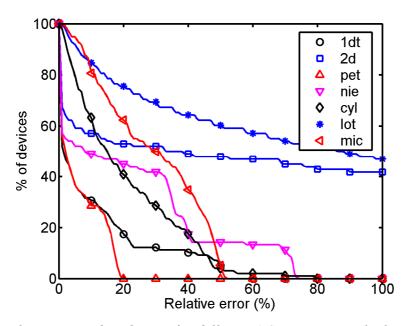

| A.4. Fasthenry simulations and comparison between AC resistance calculation    | 146 |

| models                                                                         |     |

| Bibliography                                                                   | 153 |

| Acknowledgments                                                                | 169 |

| Vitae                                                                          | 171 |

### **Abstract**

Modern communication devices demand challenging specifications in terms of miniaturization, performance, power consumption and cost. Every new generation of radio frequency integrated circuits (RF-ICs) offer better functionality at reduced size, power consumption and cost per device and per integrated function. Passive devices (resistors, inductors, capacitors, antennas and transmission lines) represent an important part of the cost and size of RF circuits. These components have not evolved at the same level of the transistor devices, especially because their performance is strongly degenerated when they scale down in size. The low resistivity silicon used to build the transistors also imposes prohibitive levels of RF losses to these passive devices. Radio frequency microelectromechanical systems (RF MEMS) are enabling technologies capable to bring significant improvement in the electrical performances and expressive size and cost reduction of these functions, with unparallel introduction of new functionalities, unimaginable to attain when using bulky, externally connected discrete components.

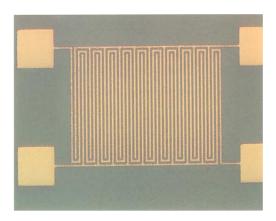

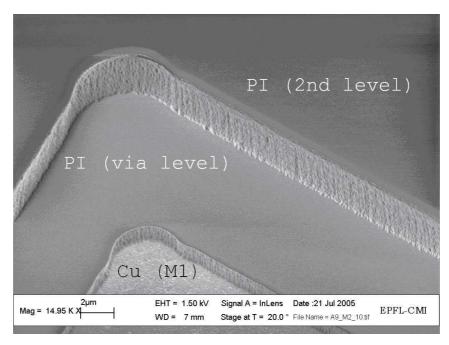

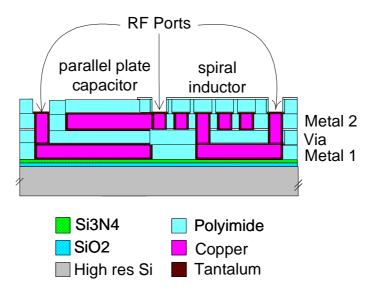

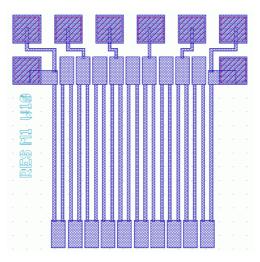

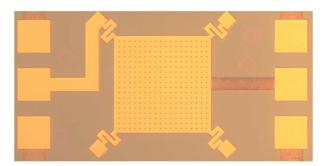

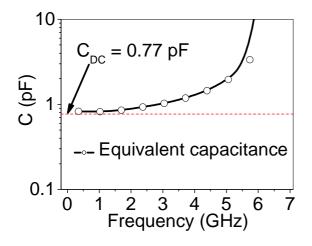

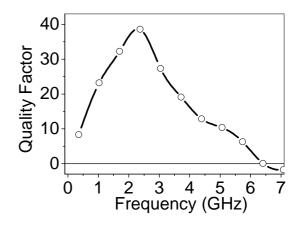

High quality factor (Q) inductors are amongst ones of the most needed components in RF circuits and at the same time ones that are most affected by thin metallization and substrate related losses, demanding considerable research effort. This thesis presents a contribution toward the development of thick metal fabrication technologies, covering also the design, modeling and characterization of high quality factor and high self-resonant frequency (SRF) RF MEMS passive devices, with a special emphasis on spiral inductors. A new approach using damascene-like interconnect fabrication steps associated to low  $\kappa$  dielectrics (polyimide), highly-conductive thick copper electroplating, chemical mechanical polishing (CMP) and tailored substrate properties delivered quality factors in excess of 40 and self resonant frequencies in excess of 10 GHz, performances in the current state-of-the-art for integrated spiral inductors built on top of silicon wafers. Furthermore, the developed process steps are compatible with back-end processing used to fabricate modern IC interconnects and have a low thermal budget (< 250 °C), what makes it a good choice to build above-IC passives without degenerating the performance of passivated RF-CMOS circuits.

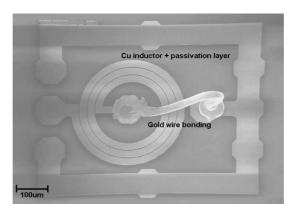

Deep reactive ion etching (DRIE) of quartz substrates was also studied for the fabrication of spiral inductors, offering excellent RF performances (Q exceeding 40 and SRF exceeding 7

GHz). A new doubly-functional quartz packaging concept for RF MEMS devices was developed. This technique process both sides of the packaging wafer: the top is used to embed high quality factor copper inductors while the bottom is thermo-mechanically bonded to another RF MEMS wafer, offering a semi-hermetic SU-8 epoxy-based seal. The bonding process was optimized for high yield, to be compatible with SF<sub>6</sub>-plasma-released MEMS and to present low level of RF losses.

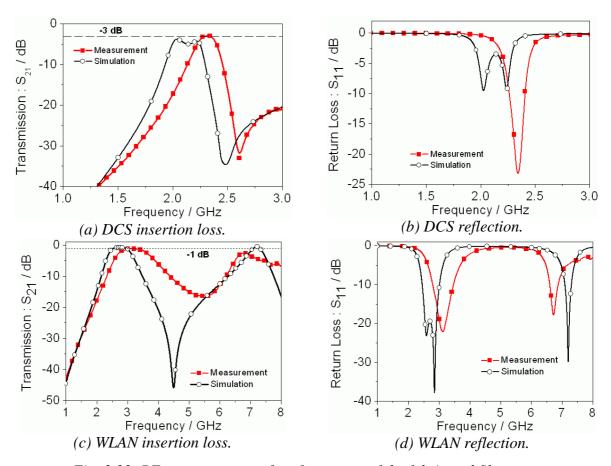

Band pass filters for the GSM (1.8 GHz) and WLAN (5.2 GHz) standards were fabricated and characterized by RF measurements and full wave electromagnetic simulations. Although further development is need in order to predict the frequency response accurately, insertion losses as low as 1.2 dB were demonstrated, levels that cannot be usually attained using onchip passives.

Systematic analysis, RF measurements, electromagnetic simulations and equivalent circuit extraction were used to model the behavior of the fabricated devices and establish a methodology to deliver optimum performances for a given technological profile and specified performance targets (quality factor, inductance and frequency bandwidth). A simple yet accurate physics-based analytical model for spiral inductors was developed and proved to be accurate in terms of loss estimation for thick metal layers. This model is capable to accurately describe the frequency-dependent behavior of the device below its first resonant frequency over a large device design space. The model was validated by both measurements and full wave electromagnetic simulations and is well suited to perform numeric optimization of designs. The proposed models were also systematized in a Matlab® toolbox.

<u>Keywords</u>: radio frequency micro electromechanical systems (RF MEMS), high quality RF passive devices, above-IC integration, copper / low  $\kappa$  technology, RF passive modeling and characterization.

## Version Abrégée

Les dispositifs de communication modernes ont des spécifications agressives en termes de miniaturisation, de performance, de consommation d'énergie et de coût. Chaque nouvelle génération des circuits intégrés radio (RF-ICs) offre de meilleures fonctionnalités à une petite taille, avec une faible consommation d'énergie et un coût réduit par fonction implémentée. Les dispositifs passifs (les résistances, les bobines, les condensateurs, les antennes et les lignes de transmission) représentent une partie importante du coût et de la taille des circuits RF. Ces composants n'ont pas évolués dans le même rythme des transisteurs, principalement car leur performance est fortement dégradée quand ils diminuent de taille. La faible résistivité du silicium utilisé dans la fabrication des transistors impose de forts nivaux de pertes RF aux dispositifs passifs. Les dispositifs micro électromécaniques pour la radio fréquence (RF MEMS) sont de nouvelles technologies qui ouvrent la voie pour avoir une amélioration significative de performance, avec l'introduction de nouvelles fonctionnalités inimaginables de s'obtenir par l'utilisation des composants discrets et encombrants.

Les bobines à fort facteur de qualité (Q) sont parmi les composants les plus attendus au même temps qu'elles sont une des plus affectées par les pertes associées aux couches métalliques minces et aux pertes RF du substrat. Cette thèse apporte des contributions vers le développement des procédés de fabrication de couches métalliques épaisses, aussi bien que pour le dessin, la modélisation et la caractérisation des dispositifs RF MEMS à fort facteur de qualité et à forte fréquence de résonance. Une attention spéciale est dédiée aux bobines en spirale.

Une approche originale utilisant la méthode damascène pour la fabrication d'interconnexions a été proposée. Le polissage chimique mécanique (CMP), l'utilisation des polymères à faible constant diélectrique (polyimide) associés aux couches épaisses en cuivre à faible résistivité et au contrôle des propriétés du substrat ont permis d'avoir des facteurs de qualité plus forts que 40 et des fréquences de résonance plus fortes que 10 GHz. Ces performances sont dans l'état de l'art pour les bobines fabriquées sur des wafers en silicium. Le procédé développé est compatible avec d'autres utilisés dans la fabrication "back-end" des interconnexions pour les CIs d'actualité, avec un petit budget thermique (< 250 °C) ce qui fait de cette technique un

bon choix pour la fabrication "above-IC" des passifs sans une dégradation de la performance des circuits RF CMOS.

La gravure profonde (DRIE) des substrats en quartz a été utilisée comme technique de fabrication alternative pour les bobines en spirale, présentant d'excellents résultats pour la performance RF (*Q* plus fort que 40 et SRF plus forte que 7 GHz).

Un nouveau procédé d'encapsulation avec double fonction pour le wafer quartz appliqué pour les RF MEMS a été développé. Cette technique s'utilise des deux cotés du wafer : le dessus pour la fabrication de bobines et le dessous pour l'encapsulation au nivaux du wafer pour des plaquettes RF MEMS avec une protection semi hermétique basée sur la résine époxy SU-8. Le procédé de soudage a été optimisé pour avoir un rendement élevé, pour être compatible avec des dispositifs libérés par la gravure sèche basée sur le SF<sub>6</sub> et pour présenter des faibles pertes en RF.

Des filtres passe bande GSM (1.8 GHz) et WLAN (5.2 GHz) ont été fabriqués et caractérisés par des mesures RF et des simulations électromagnétiques. Même si une maîtrise de la réponse en fréquence est encore envisageable, des pertes d'insertion aussi faibles que 1.2 dB on été démontrées, des valeurs particulierment difficiles à obtenir pour des filtres conçus à partir des composants passifs sur silicium.

L'analyse systématique, des mesures RF et des simulations électromagnétiques et par circuit électrique équivalents ont été utilisés pour modéliser le comportement des composants fabriqués et pour établir une méthodologie afin avoir la performance désiré en fonction des paramètres de dessin (le facteur de qualité, l'inductance et la bande de fréquence de travail). Un modèle physique simple et précis pour les bobines en spirale a été développé et validé par des mesures RF et par des simulations électromagnétiques. Les modèles proposés ont été systématisés dans une librairie de calcul pour Matlab®.

<u>Mots-clés</u>: systèmes microélectromécaniques pour la radio fréquence (RF MEMS), composants passifs à fort facteur de qualité, intégration "above-IC", technologie cuivre / diélectriques à faible constante diélectrique, modélisation et caractérisation de composants RF passifs.

### List of abbreviations and acronyms

1-D one-dimensional

2-D bi-dimensional

3-D tri-dimensional

AC alternate current

ADS advanced design system (simulation program from Agilent)

Amicom European Research Project IST-2003-507352: "European Network of

Excellence on RF MEMS and RF Microsystems"

ASCII American Standard Code for Information Interchange

ASITIC analysis and simulation of inductors and transformers for integrated circuits

BCB benzocyclobutene (low  $\kappa$  polymer)

BiCMOS bipolar / complementary metal oxide semiconductor technology

BioMEMS biological microelectromechanical systems

Bluetooth short-range, low-data rate, low-cost, wireless personal area network

communication standard (IEEE 802.15.1 standard, operates in the 2.4 GHz

ISM frequency band)

BTA benzotriazole (C<sub>6</sub>H<sub>5</sub>N<sub>3</sub>)

CAD computer aided design

CMI Center of Micro and Nanotechnology (École Polytechnique Fédérale de

Lausanne)

CMOS complementary metal-oxide-semiconductor technology

CMP chemical-mechanical polishing

CPS coupled parallel striplines

CPW coplanar waveguide

DC direct current

DECT digital enhanced (formerly European) cordless telecommunications (1880 -

1900 MHz in Europe, 1920 – 1930 MHz in the USA)

DMTL distributed MEMS transmission line

DOE design of experiments

DRIE deep reactive ion etching

EM electromagnetic

EPFL École Polytechnique Fédérale de Lausanne (also Swiss Federal Institute of

Technology Lausanne)

EU European Union

FIB focused ion beam

GaAs gallium arsenide

GND ground

GPIB general propose interface bus

GPRS general packet radio service (GSM data transfer and internet access service)

GPS global positioning system (L1 frequency = 1575.42 MHz, L2 frequency =

1227.60 MHz)

GSG ground, signal, ground (RF port configuration)

GSM global system for mobile communications (0.8, 0.9 and 1.8 GHz)

HFSS high frequency structure simulator (electromagnetic simulation tool from

**Ansoft Corporation**)

HMDS hexamethyldisilazane (photoresist adhesion promoter)

HR high resistivity

HR-Si high resistivity silicon (8 k $\Omega$  cm in this work)

IC integrated circuit

ICP inductively coupled plasma

IEEE Institute of Electrical and Electronics Engineers

IMT National Institute for Research and Development in Microtechnologies

(Bucharest, Romania)

IPA inductance per unit area [H/m<sup>2</sup>]

IPA isopropyl alcohol

ISM Industrial, Scientific and Medical (various unlicensed RF frequencies, mainly

in the 2400 – 2480 MHz range and its harmonics)

ISS impedance standard substrate

IST Information Society Technologies (EU research funded projects)

LC inductance / capacitance

LIGA Roentgen Litographie Galvanik Abformung (X-ray lithography,

electrodeposition and molding)

LNA low noise amplifier

LR low resistivity (0.3  $\Omega$  cm in this work)

LTCC low temperature co-fired ceramic

Matlab® matrix laboratory (trademark of Mathworks Inc.)

MCM-D multichip module deposition

MCLIN microstrip coupled lines (ADS Libra)

MEMS microelectromechanical systems

MIC microwave integrated circuit

MIM metal, insulator, metal

Mimosa European Research project IST-2002-507045: "Microsystems platform for

Mobile Services and Applications"

MLIN microstrip line (ADS Libra)

MMIC monolithic microwave integrated circuit

MOEMS microoptoelectromechanical systems

OPS oxidized porous silicon

PA power amplifier

PC personal computer

PECVD plasma enhanced chemical vapor deposition

PEEC partial element equivalent circuit

PGMEA propylene glycol monomethyl ether acetate (SU-8 developer)

PGS patterned ground shield

PS porous silicon

PVC polyvinyl chloride (also polychloroethene)

PVD physical vapor deposition

RAM random access memory

RCL resistance, capacitance and inductance

RCLK resistance, capacitance, inductance and mutual inductance

RF radio frequency (GHz-range in this work)

RF MEMS radio frequency microelectromechanical system

RIE reactive ion etching

RLGC resistance, inductance, conductance and capacitance

Si silicon

SI Système International (International System of Units)

SOI silicon on insulator

SOLT short, open, load and through

SPIE Society of Photo-Optical Instrumentation Engineers

SPICE simulation program with integrated circuit emphasis (University of California

Berkeley, USA)

sq square (sheet resistance measurement)

SU-8 brand name of an epoxy-based negative resist

TEM transversal electromagnetic

TMN tuning matching network

UMTS universal mobile telecommunications system (2.2 GHz)

UV ultraviolet light

UWB ultra-wideband (bandwidth > 500 MHz or 20% of the center frequency)

VLSI very-large scale of integration

VNA vector network analyzer

VTTDL variable true-time delay line

Wide-RF European Research Project IST-2001-33286: "Innovative MEMS devices for

Wideband reconfigurable RF Microsystems"

WLAN wireless local area network (2.4 and 5.2 GHz)

WLP wafer-level packaging

### List of symbols and units

A area [m<sup>2</sup>]

A arbitrary constant

ABCD ABCD parameter matrix  $[1, \Omega; S, 1]$

A<sub>SPI</sub> spiral area [m<sup>2</sup>]

B magnetic flux density [T]

B arbitrary constant

BP back pressure [Pa or psi]

BW frequency bandwidth [Hz]

$c_n$  current sheet inductance calculation coefficients [non dimensional]

C capacitance [F]

$C^*$  complex (lossy) capacitance [F] C' capacitance per unit length [F/m] C'' capacitance per unit area [F/m<sup>2</sup>]

$C_{INS}$  insulator capacitance [F]

$C_{INS}$ '' insulator capacitance per unit area [F/m<sup>2</sup>]

$C_P$  parallel capacitance [F]  $C_S$  spiral capacitance [F]  $C_{SUB}$  substrate capacitance [F]

$C_{SUB}$ '' substrate capacitance per unit area [F/m<sup>2</sup>]

d center to center distance between parallel conductors [m]

D diameter [m]

$D_{CENTER}$  track center-to-center diameter of a spiral [m]

$D_{IN}$  internal diameter [m]  $D_{OUT}$  external diameter [m]

E electric field [V/m = N/C]

$E_0$  electric field at the surface of a conductor [V/m]

e natural logarithm basis ( $e \approx 2.718\ 281\ 828\ 459\ 045\ 5...$ )

f frequency [Hz]

$f_{CRIT}$  critical frequency [Hz]

$f_{OMAX}$  frequency where  $Q_{MAX}$  occurs [Hz]

$f_{RES}$  resonance frequency, the same as SRF [Hz]

*FMI* factor of merit of an inductor [Hz/m<sup>2</sup>]

G conductance [S]

G'' conductance per unit area [S/m<sup>2</sup>]

GMD geometrical mean distance [m]

$GMD_{PAR}$  geometrical mean distance of parallel rectangular strips [m]

$G_{SUB}$ '' substrate conductance per unit area [S/m<sup>2</sup>]

H magnetic field intensity [A/m]

$H_0^{(1)}$  0-th order, 1<sup>st</sup> kind Henkel function:  $H_{\nu}^{(1)} = J_{\nu}(z) + jN_{\nu}(z)$

HF high frequency regime (characteristic dimensions  $r_0$ , w,  $t >> \delta$ )

HF hydrofluoric acid

HS head speed [rpm]

h conductor thickness (in Fasthenry simulations) [m]

I electrical current [A]IL insertion loss [dB]

*Im* imaginary part of a complex number

IPA inductance per unit area [H/m<sup>2</sup>]

J current density [A/m<sup>2</sup>]

J<sub>0</sub> 0-th order Bessel function:  $J_{\nu}(z) = \sum_{m=0}^{\infty} \frac{(-1)^m (z/2)^{\nu+2m}}{m! \Gamma(\nu+m+1)}$

$J_S$  linear current density [A/m]

*j* imaginary unit  $(j = \sqrt{-1})$

k alternative typographic form for the dielectric constant  $\kappa$  [non dimensional]

k magnetic coupling coefficient [non dimensional]

k argument of the complete elliptic integral K [non dimensional]

k' complementary argument of the complete elliptic integral K [non dimensional]

K(k) first kind complete elliptic integral,  $K(k) = \int_{0}^{\pi/2} \frac{d\varphi}{\sqrt{1 - k^2 \sin^2 \varphi}}$

K'(k) complementary first kind complete elliptic integral, K'(k) = K(k'), with

$k' = \sqrt{1 - k^2}$

L inductance [H]

$L^*$  complex (lossy) inductance [H]

L' inductance per unit length [H/m]

LF low frequency regime (characteristic dimensions  $r_0$ , w,  $t << \delta$ )

$L_{SERIES}$  series inductance [H]

$L_{SHUNT}$  shunt inductance [H]

$L_{RECT}$  inductance of a rectangular stripline [H]

$L_{SPI}$  inductance of a spiral [H]

l length [m]

$l_{\text{CIRC}}$  length of a circular spiral [m]

$l_G$  length of spiral gap [m]

*l*<sub>POLY</sub> length of a polygonal spiral [m]

ln natural logarithmlog10 base 10 logarithm

$l_{SO}$  length of a square spiral [m]

m segment length [m]

*M* mutual inductance [H]

$M_{INC}$  mutual inductance between 2 inclined segments [H]  $M_{PAR}$  mutual inductance between 2 parallel segments [H]

N integer number

$N_{\nu}(z)$  Neumann function of order v:  $N_{\nu}(z) = \frac{\cos \nu \pi J_{\nu}(z) - J_{-\nu}(z)}{\sin \nu \pi}$

*n* integer number

n number of turns of a spiral inductor

*nwinc* number of meshing cells along the width (Fasthenry)

nhinc number of meshing cells along the thickness (Fasthenry)

$N_S$  number of sides per turn (polygonal spiral)

P power [W] or [dBm]

*PS* plate speed [rpm]

p normalized frequency:  $p = \sqrt{2f\sigma\mu wt} = \frac{1}{\delta}\sqrt{\frac{2wt}{\pi}}$  [non dimensional]

Q quality factor [non dimensional]

$Q_{EFF}$  effective quality factor [non dimensional]

$Q_{MAX}$  maximum quality factor (peak value) [non dimensional]

$Q_P$  parallel quality factor (capacitor) [non dimensional]

$Q_S$  series quality factor (inductor) [non dimensional]

*R* resistance  $[\Omega]$

R spiral radius [m]

$R_{CROWD}$  AC resistance due to current crowding [ $\Omega$ ]

*Re* real part of a complex number

$R_F$  frequency-dependent surface resistance  $R_F = \sqrt{\pi f \rho \mu} = \rho/\delta [\Omega]$

RR removal rate [µm/min]

$R_S$  series resistance  $[\Omega]$

$R_{SH}$  sheet resistance  $[\Omega / \text{sq} = \Omega]$

$R_{SUB}$  substrate resistance  $[\Omega]$

r cylindrical radial coordinate [m]

r rectangular conductor aspect ratio (= t/w or w/t) [non dimensional]

$r_0$  cylindrical wire radius [m]

rw meshing increasing ratio along the width (non dimensional, Fasthenry)

rh meshing increasing ratio along the thickness (non dimensional, Fasthenry)

S S-parameter matrix [non dimensional]

s track spacing [m]

SRF self-resonant frequency, the same as  $f_{RES}$  [Hz]

S scattering parameter matrix [non dimensional]

$S_{11}$  S<sub>11</sub>-parameter data (reflection at port 1) [non dimensional]

S<sub>21</sub> – parameter data (forward port 1-2 transmission or insertion loss) [non

dimensional]

$S_{12}$  S<sub>12</sub>-parameter data (reverse port 1-2 transmission) [non dimensional]

$S_{22}$   $S_{22}$ -parameter data (reflection at port 2) [non dimensional]

T Bessel equation parameter:  $T = \sqrt{-j\omega\mu\sigma} = (1-j)/\delta$  [m<sup>-1</sup>]

*TCC* temperature coefficient of capacitance [K<sup>-1</sup>] or [°C<sup>-1</sup>]

TCR temperature coefficient of resistance  $[K^{-1}]$  or  $[{}^{\circ}C^{-1}]$

t thickness [m]

tan  $\delta$  loss tangent (also known as loss factor) [non dimensional]

$t_{INS}$  insulator thickness [m]

$t_{INS,M1}$  thickness of the insulator between the underpass and the first level of metal

[m]

thickness normalized by the skin depth:  $t_N = t / \delta$  [non dimensional]

$t_{SUB}$  substrate thickness [m]

w track width [m]

$w_N$  track width normalized by the skin depth:  $w_N = w / \delta$  [non dimensional]

WP working pressure [Pa or psi]

X reactance  $[\Omega]$

Y conductance matrix (moduli in [S])

y<sub>xx</sub> conductance matrix coefficient (moduli in [S])

Z complex impedance (moduli in  $[\Omega]$ )

Z' impedance per unit length  $[\Omega/m]$

$Z_i'$  internal impedance per unit length of a conductor  $[\Omega/m]$

$Z_0$  real characteristic impedance  $[\Omega]$

$Z_0^*$  complex characteristic impedance (moduli in  $[\Omega]$ )

$\alpha$  attenuation coefficient [Np/m] or [dB/m]

α angle between segments [rad]

β phase constant of a transmission line: [rad/m] or [ $^{0}$ /m]

$\Gamma$  reflection coefficient (also  $S_{11}$  or  $S_{22}$ ) [non dimensional]

$$\Gamma(x)$$

gamma function:  $\Gamma(x) = \int_{0}^{\infty} t^{x-1} e^{-t} dt$

$\gamma \qquad \qquad \text{complex propagation constant} = \alpha + j \; \beta \; [\text{m}^{\text{-}1}]$

$$δ$$

skin depth [m] =  $\sqrt{\frac{\rho}{m\mu}} = \sqrt{\frac{2}{\omega\mu\sigma}}$

δ parallel segment overlap length (for mutual inductance calculation) [m]

ε dielectric constant [F/m]

$\varepsilon^*$  complex (lossy) dielectric constant =  $\varepsilon$  - i tan  $\delta$

$\epsilon_0$  vacuum dielectric constant =  $1/\mu_0 c_0^2 \approx 8.854 \ 188 \cdot 10^{-12} \ \text{F/m}$

$\varepsilon_{INS}$  insulator dielectric constant [F/m]

$\varepsilon_{R}$  relative dielectric constant ( $\varepsilon / \varepsilon_{0}$ , non dimensional)

$\varepsilon_{R.EFF}$  effective relative dielectric constant (non dimensional)

$\varepsilon_{SUB}$  substrate dielectric constant [F/m]

$\kappa$  dielectric constant (alternative name to  $\varepsilon_R$ )

$\lambda$  wavelength = c/f [m]

$\lambda_0$  free space wavelength =  $c_0/f$  [m]

$\mu_0$  vacuum magnetic permeability =  $4 \pi 10^{-7}$  H/m

μ magnetic permeability [H/m]

$\mu_R$  relative magnetic permeability:  $\mu_R = \mu / \mu_0$  [non dimensional]

$\xi$  spiral geometric filling factor [non dimensional]

$\pi$  constant  $\cong$  3.141 592 653 589 793 1...

$\Sigma$  summation

σ electrical conductivity [S/m]

$\sigma_{SUB}$  substrate conductance conductivity [S/m]

Φ magnetic flux [Wb]

$\Phi_{ij}$  magnetic flux induced in the circuit loop j by the current in loop i [Wb]

ω angular frequency =  $2 \cdot \pi \cdot f$  [rad/s]

## International System of units (SI)

A ampere – electrical current [base unit = C/s]

C coulomb – electric charge [A·s]

dB decibel – amplitude or power ratio defined as  $20 \cdot log_{10}(U/U_{REF})$  for voltages or

$10 \cdot log_{10}(P/P_{REF})$  for power

dBm power in dB referenced to 1 mW:  $P(dBm) = 10 \cdot log_{10}(P / 1 \text{ mW})$

F farad – capacitance  $[C/V = m^{-2} \cdot kg^{-1} \cdot s^4 \cdot A^2]$

GB gigabyte – information capacity equal to  $1.0 \cdot 10^6$  bytes

H henry – inductance [Wb/A =  $m^2 \cdot kg \cdot s^{-2} \cdot A^{-2}$ ]

Hz hertz – frequency [s<sup>-1</sup>]

kg kilogram – mass [base unit]

m meter – length [base unit]

mol mol – quantity of matter  $[6.022 \ 141 \ 5 \cdot 10^{23} \ particles]$

Np neper – amplitude ratio: 1 Np =  $e = 20 \text{ dB} / ln(10) \cong 8.6859 \text{ dB}$

Pa pascal – pressure  $[N/m^2 = m^{-1} \cdot kg \cdot s^{-2}]$

rad radian – angle [non dimensional]

s second – time [base unit]

S siemens – electrical conductivity  $[A/V = \Omega^{-1} = m^{-2} \cdot kg^{-1} \cdot s^3 \cdot A^2]$

T tesla – magnetic flux density  $[Wb/m^2 = V \cdot s/m^2 = kg \cdot s^{-2} \cdot A^{-1}]$

V volt – electric potential  $[J/C = m^2 \cdot kg \cdot s^{-3} \cdot A^{-1}]$

W watt – power  $[J/s = m^2 \cdot kg \cdot s^{-3}]$

Wb weber – magnetic induction flux  $[V \cdot s = m^2 \cdot kg \cdot s^{-2} \cdot A^{-1}]$

Ω ohm - electrical resistance [V/A = m<sup>2</sup>·kg·s<sup>-3</sup>·A<sup>-2</sup>]

#### Non-SI units used in this work

in length in inches: 1 in = 2.54 cm

mbar pressure in mbar: 1 mbar = 100 Pa

psi pressure in pounds per square inch:  $1 \text{ psi} = 1 \text{ lbf} / \text{in}^2 = 6 894.757 29 \text{ Pa}$

rpm angular velocity in revolutions per minute: 1 rpm =  $2 \pi \text{ rad} / \text{min}$

sccm flow rate in standard cubic centimeters per minute (measured at 1 atm and

$0^{\circ}$ C): 1 sccm = 1 atm · cm<sup>3</sup>/min @  $0^{\circ}$ C = 7.4358 ·  $10^{-7}$  mol/s = 4.4780 ·  $10^{17}$

particles / s

Torr pressure in Torr: 1 Torr = 133.322 Pa

## **Physical constants**

vacuum speed of light (exactly  $2.99792458 \cdot 10^8$  m/s  $\approx 3.0 \cdot 10^8$  m/s)

$\epsilon_0$  vacuum dielectric constant = 1 /  $(\mu_0 c_0) = 8.85418781762 \cdot 10^{-12} \text{ F/m}$

$μ_0$  vacuum magnetic permeability (exactly  $4·π·10^{-7}$  H/m  $≅ 1.2566 · 10^{-6}$  H/m)

$η_0$  vacuum characteristic impedance =  $\sqrt{\frac{\mu_0}{\varepsilon_0}}$  = 376.73...  $Ω \cong 120 π Ω$

$d_{CU}$  copper density = 8.920 g/cm<sup>3</sup>

$ρ_{CU}$  copper resistivity (bulk value = 1.72 μΩ cm, thin film value = 2.00 μΩ cm)

$\rho_{AG} \qquad \qquad \text{silver resistivity (bulk value} = 1.62 \ \mu\Omega \ \text{cm)}$

$\rho_{AU} \qquad \qquad \text{gold resistivity (bulk value} = 2.44 \ \mu\Omega \ \text{cm)}$

$ρ_{AL}$  aluminum resistivity (bulk value = 2.62 μΩ cm, thin film value = 3.30 μΩ cm)

$\epsilon_{R,OX}$  relative dielectric constant of silicon dioxide (SiO<sub>2</sub>) = 3.9

$\epsilon_{R,PI}$  relative dielectric constant of polyimide = 2.9

$\varepsilon_{R,SI}$  relative dielectric constant of silicon (Si) = 11.9

# **Chapter 1**

## Introduction

Microelectronic devices are miniaturized electronic components generally built in a single piece of a monocrystaline semiconductor material like silicon (Si) or gallium arsenide (GaAs). The possibility to fabricate very small components enables the integration of complex circuit functionalities in a small piece of semiconductor material at minimum cost and energy consumption per device.

An intense increase in both the degree of miniaturization and in the performance of the electronic circuits has been observed since the establishment of the microelectronic fabrication industry. A consistent increase in the number of transistors per integrated circuit has been observed every year. For each new generation of integrated circuits new and more complex functions can be integrated in a single semiconductor chip. A trend known as Moore's law, observed in 1965 by one of the co-founders of Intel Corporation and still valid today, states that the number of transistors in complex integrated circuits approximately doubles every 2 years [Moore 1965, Moore 1995].

Passive devices (resistors, capacitors, inductors and transmission lines) have been traditionally built separately from the main integrated circuit transistor functions and attached to them using special interconnection techniques. These bulky components represent a large amount of the cost of the RF circuits and the external fabrication and interconnection of these devices is a factor that adds significant volume, parasitics, weight and cost to the RF products.

Co-integration of passive devices in the same silicon substrate is desirable in order to reduce the interconnect parasitics, reduce the size and cost of the units and increase the operating frequencies of the RF circuits. The challenges following this tendency are associated to the limited performance of these devices when built in miniaturized configurations and in proximity with high conductivity substrates. This framework introduces the need of using new materials and fabrication technologies in order to increase the electrical performance of these devices, while still keeping the process low-cost and compatible with the standard technologies used to fabricate RF CMOS circuits.

Moreover, the design of passive devices to attain a certain specification must trade-off many variables that determine the size and the performance of these devices. Careful electromagnetic optimization of the device geometry should be carried out in order to ensure that one can obtain the maximum performance that a given fabrication technology can deliver.

The aim of this thesis is to present a contribution to the study and development in the fabrication of high quality factor integrated passive devices. The development of a new fabrication technology based on the definition of thick copper layers embedded in low  $\kappa$  polyimide is proposed. A systematic study on the design and characterization of the fabricated devices was carried out, with special emphasis on integrated inductors used as a demonstration vehicle to probe the performance of the developed fabrication techniques.

#### 1.1. Organization of the thesis

This first chapter of the thesis presents a general introduction to the field of MEMS and RF MEMS and a brief description of the advantages and issues related to RF MEMS fabrication technologies. The motivations and objectives of this PhD project as well as a picture of the current state-of-the-art in the field are also presented.

The chapter 2 presents the basic underlining concepts, models and equations defining passive integrated inductors, with special attention to the definition of the inductance calculation formulae and merit factors used in this research.

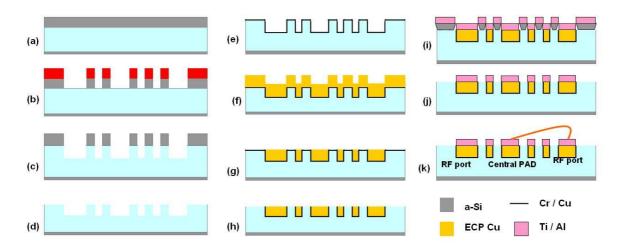

In the chapter 3, the fabrication technology developed in the frame of this thesis is presented in detail, describing the fabrication steps, the main issues involving the technological choices made and how they were addressed. This chapter will finally present the fabrication results obtained using the developed technology platform. An application of the high Q passive

devices developed in the frame of this thesis for the synthesis of high frequency bandpass filters is also presented.

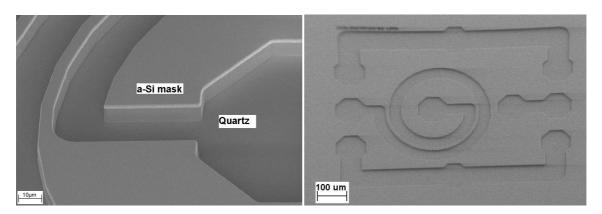

Chapter 4 presents an alternative fabrication process based on the direct deep reactive ionetching of insulating substrates filled with thick electroplated copper lines. An innovative double-functionalized RF packaging solution is also proposed. This solution can be used for both packaging and fabrication of high Q inductors by exploiting both sides of the capping wafer.

Chapter 5 presents the simulation tools and RF characterization methods used to predict and measure the performance of the fabricated devices. It presents and discusses the software tools used and especially developed to accomplish task. Finally, an accurate, physics-based model for spiral inductors is proposed and validated.

Finally, the chapter 6 draws up the general conclusions of this research project and point some research directions to be followed in order to continue the advancement in the field.

#### 1.2. MEMS and RF MEMS passive devices

Micro-electro mechanical systems (MEMS) are miniaturized devices having functionality related to both the mechanical and electrical domains, presenting in general both functionalities in a single device. The term emerged to describe a class of devices that can be fabricated using adapted technologies inherited mainly from integrated circuit fabrication techniques [Madou 1997].

MEMS devices can effectively incorporate integrated circuit functions and interface these circuits with a variety of domains like fluidics and biology (microchannels, micropumps, defining the so-called Bio-MEMS field), optics (micromirrors and optical switches, defining the so-called optical-MEMS or MOEMS field) and mechanical sensors and actuators (electrostatic, thermally or magnetically driven sensors and actuators).

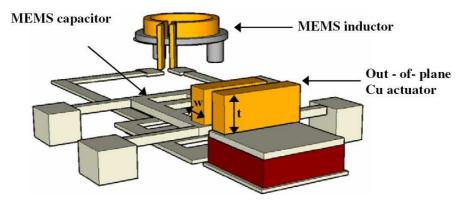

Radio frequency micro-electro mechanical systems (RF MEMS) is the term used to describe the emerging technology of fabricating and using MEMS devices that have functionality in radio communication circuits operating in the GHz frequency range [de los Santos 1999, de

los Santos 2002, Yao 2000, Nguyen 2002, Varadan 2003]. MEMS and microelectronic fabrication techniques are enabling technologies to fabricate high quality factor passive devices (capacitors and inductors), low-loss transmission lines, RF switches, microrelays and a number of application circuits obtained by combining these basic devices in functional blocks. Emerging RF applications demand a number of passive circuit functions, including high performance switches with low insertion losses and high isolation [Rebeiz 2001], large tuning range variable capacitors [Rijks 2004], tunable inductors [Fukushige 2003], tunable filters [Brank 2001], suspended transmission lines [Pham 2001], tuning matching networks [Unlu 2006], reconfigurable antennas [Erdil 2007], variable true-time delay lines (VTTDLs) [Hung 2004, Perruisseau-Carrier 2006], antenna phased arrays [Sagkol 2002], and electromechanical filters and resonators [Nguyen 1998, Dubois 2005, Piazza 2006] as basic passive network building blocks.

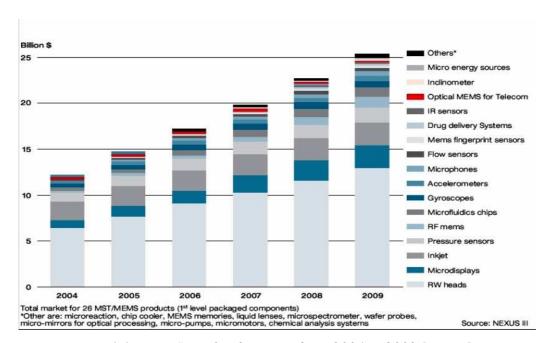

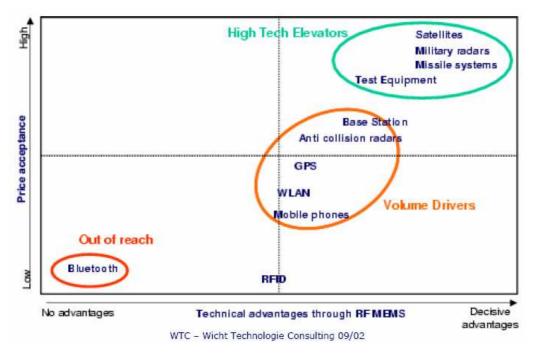

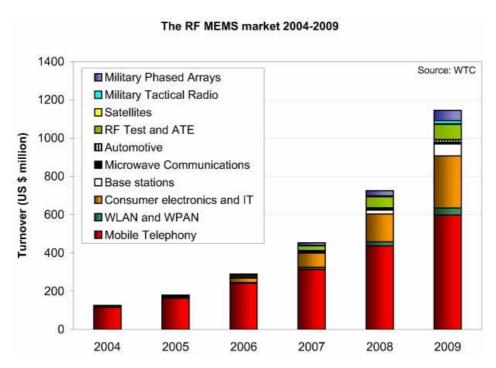

Figure 1.1 shows a MEMS market forecast shared between the various families of MEMS devices available to date. The predominant products are data read / write heads, followed by micro displays, inkjet printer heads, pressure sensors and RF MEMS occupying the 5<sup>th</sup> position. Figure 1.2 shows a forecast with the sharing of the RF MEMS market in different sub-areas. This projection predicts a U\$ 1.2 billion market for 2009 by having mobile telephony and consumer electronics as the major volume drivers, followed by other wireless applications. RF test and WLAN networks represent a significant percentage of this market, followed by other low volume, higher technology drivers like satellites and military applications (fig. 1.3).

These market projected figures are, of course, estimations based on the behavior and expectations of the market, and are dependent on a number of uncertain economical and technical issues that should be addressed.

From the technical point of view, the large-scale insertion of RF MEMS in mobile and consumer electronics is dependent on a number of key technological factors related to:

How low-cost the technology would be, including the packaging issues and how this

aspect impacts the cost and the performance of the devices. This topic should be

addressed by searching for solutions that should be compatible with the current CMOS

fabrication and packaging practices, using low bill of materials and simple and robust

fabrication methods.

- The added value that RF MEMS can provide for the products in terms of new functionality, performance and energy saving,

- The reliability and long-term stability of the electrical and mechanical characteristics of these devices, especially the ones having movable mechanical parts and electrical contacts like variable capacitors and switches.

Fig. 1.1: MEMS market forecasts from 2004 to 2009 [Nexus].

Fig. 1.2: RF MEMS technology drivers [WTC].

Fig. 1.3: Market forecasts for RF MEMS devices shared by different sub-applications [WTC].

#### 1.3. Motivation and objectives

High Q passive devices, especially inductors, are desirable in order to reduce the phase noise in voltage controlled oscillators (VCOs), reduce the losses in filter and tuning matching networks (TMN) and reduce the power consumption in oscillator and power amplifier circuits (PA) [Malba 1998, Rebeiz 2003]. Table 1.1 shows how the main circuit figures of merit scale as function of the inductor quality factor (supposing that all the other parameters are kept constant).

| Application       | Parameters                                                              | Assumptions                    | Scaling with Q |

|-------------------|-------------------------------------------------------------------------|--------------------------------|----------------|

|                   | Phase noise                                                             | LC-type resonator circuit      | $1/Q^2$        |

| Oscillators       | Power                                                                   | For a fixed phase noise level  | 1/Q            |

|                   | consumption                                                             |                                |                |

|                   | Gain                                                                    | Proportional to load impedance | Q              |

| Amplifiers        | Power                                                                   | Same gain with less            | 1/Q            |

| Ampiniers         | consumption                                                             | transconductance for the       |                |

|                   |                                                                         | transistor                     |                |

| Matching networks | <b>[atching networks</b> ] Insertion loss Unloaded resonator Q sets the |                                | 1/Q            |

| and filters       |                                                                         | loss                           |                |

Table 1.1: Scaling of RF circuit parameters as function of the inductor quality factor [Rebeiz 2003].

The use of MEMS devices in RF circuits is very appealing because at very high GHz frequency ranges semiconductor switches and transmission lines built on conventional silicon substrates become too lossy. Solid-state devices are also limited in terms of linearity and power handling capability, limitations that electromechanical devices are less subject to. On the other hand, there are off-chip high quality factor devices available today, but the cointegration of these devices with the IC functions is desirable in order to reduce the volume, costs and parasitics associated to the fact of having bulky components with long interconnecting lines going outside the RF circuitry core.

Additionally, the possibility of building high quality factor, tunable and switchable components will be key enabling factors for new emerging multi-GHz reconfigurable radio circuits and high performance / low power telecommunication modules by introducing new functionalities that the present day components cannot offer due to their high cost, size and impossibility of being fabricated in large numbers and co-integrated with transistors.

Passive devices have been largely studied and fabricated on GaAs and more recently on silicon-based RF technologies. RF performances on top of silicon substrates are poor in general, which poses severe limitations in the scalability and use of these technologies when co-integrated with CMOS technologies for the high GHz frequency ranges. The use of new technologies and materials associated to innovative and optimized RF designs are key points for what this thesis will propose contributions to continue the advancement in the RF silicon-based technologies.

The objective of this thesis is to contribute in the field of high quality factor RF MEMS by developing new CMOS-compatible fabrication technology platforms and by the systematic analysis on the performance limitation factors of these devices.

In order to explore all the potential of a given RF technology, numeric optimization, electromagnetic simulation and RF measurement-based models should be extensively exploited to give optimal designs in the sense that the best possible performance for a given technology profile can be delivered. This thesis make a contribution in this direction with the systematic use of modern RF simulation tools available to date, as well as applying and comparing the various models available in the literature and by extracting accurate equivalent circuit models based on S-parameter measurements.

The devices fabricated and studied in the frame of this thesis had also the objective of providing different RF MEMS related EU research projects with demonstrator prototypes. These research projects were: Wide-RF ("Innovative MEMS devices for Wideband reconfigurable RF Microsystems", project IST-2001-33286), Mimosa ("Microsystems platform for Mobile Services and Applications", project IST-2002-507045) and Amicom ("European Network of Excellence on RF MEMS and RF Microsystems", project IST-2003-507352).

#### 1.4. State-of-the-art on RF MEMS

Integrated passive devices have been fabricated and modeled initially on top of GaAs substrates [Cauton 1968, Greenhouse 1974, Pettenpaul 1988]. The fabrication and study of spiral inductors on top of low resistivity silicon wafers has been performed essentially in the past two decades [Nguyen 1990], and started to gain more interest in the past decade [Nguyen 1998]. The first devices that appeared in this direction showed very poor RF performances, with peak quality factors that do not exceed the range of 3-5 and self resonance frequencies in the 1-3 GHz range, imposing severe limitations to the practical application of these devices [Nguyen 1990, Yue 1996].

The availability of Cu / low  $\kappa$  advanced interconnects in the state-of-the-art high speed CMOS processes provided an enabling way to deliver devices with significant increase in both peak quality factor (around 10) and self-resonance frequencies (around 5 GHz) [Burghartz 1996, Burghartz 1997].

In 1996, Burghartz et al. proposed to shunt layers of metal in a multilevel metallization BiCMOS process by putting traces of metal in parallel by using many vias interconnecting them. Inductors in the range of 1 to 5 nH with quality factors in the range of 5 to 20 were obtained by using this technique [Burghartz 1996b].

The obtained increase in the RF performance by using high-speed interconnects is related to the reduction in the parasitics and increase in the conductivity of the interconnects, the same driving force that is pushing the IC local interconnects for the multi-GHz frequency range, but these performances did not showed to be enough to respond the demand for high Q devices

with resonant frequencies into the 6 - 10 GHz range expected for the new emerging RF application standards (GSM, WLAN for example).

These issues have been addressed by introducing new fabrication technologies and materials and by removing the limitations imposed the lossy silicon substrate. In 1993, Chang et al. demonstrated for the first time a suspended 100 nH inductor by etching a cavity underneath the inductor and improving both gain and bandwidth of a CMOS RF amplifier [Chang 1993]. In 2000, López-Villegas et al. proposed to etch the silicon on the backside of the designed spiral inductors, demonstrating an increase in the quality factor from 3 to 30, shifting the frequency  $f_{QMAX}$  from 1.5 to 5 GHz.

In 1997, Young et al. fabricated copper solenoid inductors with conductors wrapped around a 500- $\mu$ m-wide and 650- $\mu$ m-high alumina core [Young 1997, Malba 1998b]. A 4.8-nH inductor with Q=30 @ 1 GHz was demonstrated by this fabrication technique. Kim et al fabricated copper solenoid inductors with air-core instead of alumina, demonstrating inductors in the range of 1 to 20 nH with quality factors in the range of 7 to 60 [Kim 1998]. Chen et al. demonstrated in 2001 solenoid inductors made using thick SU-8 resist on top of CMOS circuits with  $Q_{MAX}=20$  @ 4.5 GHz and SRF > 10 GHz [Chen 2001].

In 1999, Yoon et al proposed to fabricate overhang inductor structures in order to reduce substrate related losses, placing the inductor 30  $\mu$ m to 50  $\mu$ m far away from the substrate [Yoon 1999]. A suspended inductor of 1.8-nH having a Q-factor of 50 at 7 GHz was demonstrated by using this technique. This same author proposed solenoid inductors fabricated on top of 10  $\Omega$  cm substrate. An inductor of 2.7 nH with a peak quality factor of 17 and self-resonant frequency of 2.4 GHz was demonstrated using this technique.

Another fabrication technique adopted in order to reduce substrate-related losses is to locally increase the resistivity of the silicon substrate underneath the inductor by providing a poor conductivity silicon material by modification of the substrate by proton ion bombardment or by the formation of porous silicon layer (PS). Hsu et al. demonstrated an increase on the peak quality factor from 8 to 18, with a shift in  $f_{QMAX}$  from 1.5 to 3.5 GHz by applying proton implantation treatment of the silicon underneath the inductors. A peak quality factor of 45 at 15 GHz with a resonant frequency of 22 GHz was demonstrated [Hsu 2002]. This process presents some issues related to the damage of the silicon by the high-energy particle

bombardment [Liao 2003]. Nam et al. demonstrated inductors fabricated on top of oxidized porous silicon (OPS): a 6.3-nH with peak Q-factor of 13.3 at 4.6 GHz and self-resonant frequency of 13.8 GHz was demonstrated [Nam 1997]. In 2003, Royet et al demonstrated  $Q_{MAX} = 45$  @ 1 GHz and SRF of 5 GHz by using also porous silicon formation technique [Royet 2003]. In 2007, Contopanagos et al. demonstrated inductors fabricated on top of porous silicon layer using copper conductor with  $Q_{MAX} = 30$  @ 3.5 GHz [Contopanagos 2007].

In 1999, Lee et al. as well as Kim et al. demonstrated the use of bondwires to fabricate solenoid-type inductor structures by closing large circuit loops [Lee 1999, Kim 1999]. Inductors between 2 to 6 nH with quality factors in the range of 30 to 60 were demonstrated using this fabrication technique. The problem with this approach is the difficulty to accurately control the form and size of the loops and so the final inductance value characteristics of the final device.

In 2002, Chomnawang et al. demonstrated high Q inductors using thick resist fabrication of solenoid-like inductors. A 1.8-nH inductor with Q=40 at 10 GHz was demonstrated [Chomnawang 2002].

The use of LIGA processing enables the fabrication of thick metal structures suitable to build high Q passive devices [Bacher 1995]. In 2003, Park et al. demonstrated high current handling (> 3A) devices using nickel-iron magnetic material for the inductor core, but with very low-frequency and low quality factor (Q = 4.5 @ 50 kHz) [Park 2003]. In 2007, Lu et al. demonstrated  $Q_{MAX}$  between 60 and 90 @ 2.5 GHz and SRF between 17 and 20 GHz using very thick out-of-plane solenoid structures fabricated using LIGA process. This process uses 100 and 200  $\mu$ m-thick vias [Lu 2007].

Active inductors are circuits made of a combination of transistors and other passive components to emulate the electrical behavior of passive inductors [Kaunisto 1995, Hara 1988, Hayashi 1996, Haslett 2001]. These circuits can present high Q and broadband frequency behavior at moderate to low on-wafer area consumption. The major drawback of these devices is their very poor performance in terms of phase noise and high power consumption [Craninckx 1995].

Variable inductors are highly needed to fabricate high-performance reconfigurable filters, and are probably the less developed RF MEMS device to date. The major issues associated in fabricating this kind of device is the difficulty to obtain in the same device a high inductance per area density, large range tunability, low actuation voltage or currents, high quality factor and high self-resonant frequency. No design to date can answer to all these issues simultaneously. Fukushige et al. presented an out-of-plane movable helical design with 3% of tuning range (demonstrated by the use of external actuator) and a quality factor of only 2 [Fukushige 2003]. Tassetti et al. proposed an electrostatically actuated actuator to operate the secondary of a transformer-like structure, with actuation voltages in the range of 100 V to 200 V and no reporting on the quality factor, expected to be inherently low in this kind of structure [Tassetti 2003, Tassetti 2004]. The most promising variable inductor solution proposed to date seems to associate high Q fixed devices with high-performance switches in order to build switchable banks of fixed devices, where the total inductance is defined by the series or parallel combination of individual high-performance devices. This configuration, in spite of requiring high-performance switches to be implemented, does not compromise the quality factor of the inductor in order to acquire the desired tunability. This approach also let the circuit designer free of the use of complicate feedback mechanisms or non-linear calibrations needed to precisely control the inductance value.

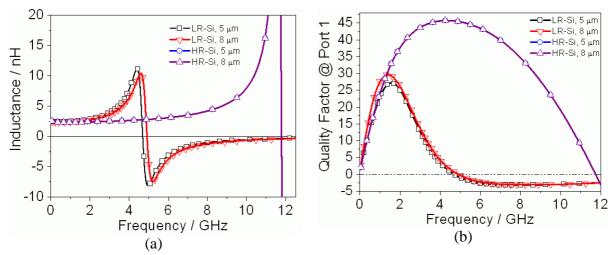

The current state-of-the-art results on CMOS-compatible integrated inductors has been obtained associating thick highly conductive metals, low  $\kappa$  polymers and high resistivity substrates, offering peak quality factors in the range of 20-60 and self-resonant frequency exceeding 6 GHz, reaching sometimes the range of 10-20 GHz [Carchon 2004].

The focus of this thesis is mainly put on spiral inductors, which are to date the devices suffering from the lower quality factor and higher substrate related losses. Finding good technological alternatives for the fabrication of inductors will set technological solutions enabling low insertion losses and high self-resonant frequencies that can be successfully applied for virtually any type of passive device.

#### 1.5. Quality factor enhancement techniques

Many techniques have been proposed and tested in the pursuit of higher quality factor integrated inductors. These techniques can be divided basically in two major groups: design-

related and technology-related. Design-related approaches try to extract the best performance that a given technology can offer by using adapted design methodologies in order to increase the performance of the device without changing radically the way it is fabricated. These methodologies are needed when a given mature technology must be used to fabricate the devices and the designer has no choice about this point. This approach is also necessary in order to obtain the best quality factor that a given technology can offer. Technology-related approaches propose new materials and fabrication technologies in order to provide better performance and functionality by overcoming the inherent limitations of the materials and processing steps used to fabricate the device, namely the thin metal layers and substrate-related losses.

From the design point of view, in spite of being geometrically simple, inductors present many trade-offs related to the choice of the geometrical parameters.

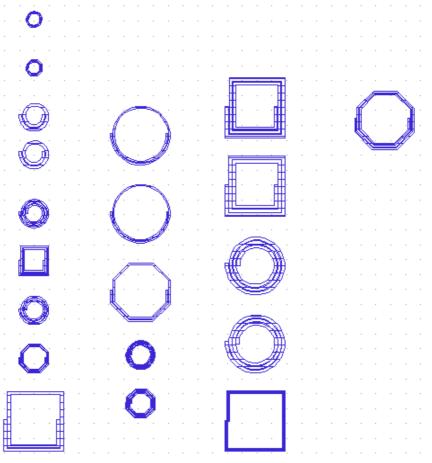

Amongst all polygonal forms, circular spirals present a better quality factor related to a better inductance / perimeter ratio [Chaki 1995, Park 1997, Lee 2001, Aguilera 2002]. The circular design is not available in general for all the mask fabrication processes. In that case, octagonal inductors are the best compromise for the number of sides per turn when only 45<sup>0</sup> lines are allowed by the design rules.

Craninckx demonstrated by electromagnetic simulation that the inner segments of the spiral inductors do not contribute effectively to the total inductance of the device due to their reduced length compared to the overall spiral one [Craninckx 1997]. On the other hand, the inner segments are prone to strong magnetic field influence generated by the outer segments, and present more AC resistance per unit length than the outer ones, contributing significantly to increase the losses of the device. The conclusion of this study is that it is advisable to design "hollow spirals" having the largest possible internal diameter. The drawback of this technique is the increased on-wafer area consumption and some increase on the parasitic capacitances that scale with the total device area. In this same way of thinking, tapered spirals having narrow widths for the inner segments were proposed [López-Villegas 2000, Lin 2002]. The narrow inner tracks are less prone to AC resistance increase due to the external magnetic field generated by the outer tracks, and have also more inductance per unit length. Both effects together can compensate for the increased resistance due to the reduction in the cross section area, and these inductors can have gains in the quality factor in the order of 10 to 20%

if correctly optimized. The major drawback of this technique is that an accurate modeling approach is needed in order to have the good balance with the tendency to increase the quality factor by having more resistive narrower inner tracks. For this kind of spiral, no simple rule for the track width decrease ratio as function of the geometry and inductance is clearly established. By the same way, no accurate closed-form inductance calculation formulae are available, making it difficult to build devices in an accurate predictive basis.

Differential excitation of spiral inductors showed to be less prone to substrate parasitic influence [Danesh 2002, Reiha 2003], due to the series association of parasitic capacitances when both sides of the device have potentials referenced to the ground. The result from this study suggest that moving for differential circuit architectures are beneficial and can offer up to 30% of improvement in the quality factor with respect to single ended devices build on top of low resistivity silicon substrates. A symmetrical spiral design can also help in order to flatten the frequency response of the device and have larger frequency bandwidth inductors, a feature desirable for multi standard RF circuit operation.

Transformer-like designs like the one proposed by Tiemeijer et al. [Tiemeijer 2001] basically put two or more spirals in parallel in order to decrease the total resistance of the inductor. This technique is effective only when the 2 spirals can be put in close proximity in order to have a high magnetic coupling coefficient that does not make the parallel inductance decrease by the same ratio of the resistance, presenting in the end a better inductance / resistance ratio and then a better quality factor. Another drawback of this type of design is that putting spirals in close proximity can increase the parasitic capacitance reducing the frequency response of the devices. The fabrication of spirals by stacking layers of metal in parallel can reduce the low frequency resistance of the spiral, presenting although a strong reduction in the self-resonant frequency due to the increase in parasitic capacitances [Koutsoyannopoulos 2000, Zolfaghari 2001].

When designing inductors on top of low resistivity substrates, the excessive losses of the substrate can be avoided by putting a conductive grid between the spiral and the substrate, made of highly-doped silicon or metal. The grid must be patterned with thin, non-closed paths in order to avoid induced losses due to eddy current and reduction of the inductance by the image currents that would be induced by a solid conductive structure. This technique is known as the patterned ground shield (PGS, fig. 1.4) [Mohan 1998, Yue 1998, Tan 2000, Ng

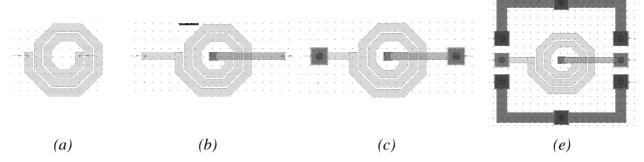

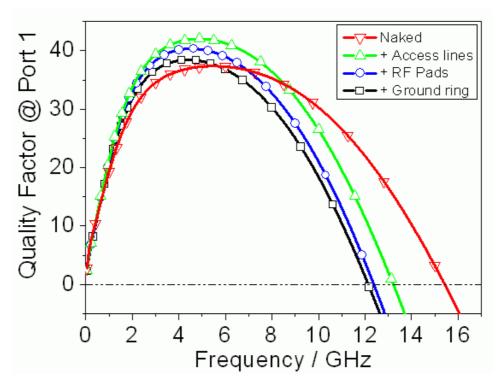

2001] and is effective when the resistivity of the substrate is in the order of 0.1  $\Omega$  cm or less. For higher resistivity substrates, this technique presents the drawback of increasing the parasitic coupling capacitance to the substrate, what reduces by consequence the resonant frequency of the device. Burghartz demonstrated in 1997 that the surrounding ground ring and the way it is electrically connected to the substrate also plays an important role in the quality factor of the inductors [Burghartz 1997b].

- (a) Highly diffused silicon and lateral contact vias.

- (b) Spiral build on metal with GSG lines contacting the underneath structure.

Fig. 1.4: The use of a patterned ground shied (a) underneath the spiral inductor (b) built on top of low resistivity substrate in order to avoid substrate eddy current losses.

Designing higher track widths reduces proportionally the low-frequency resistance of the device, but an optimum point is reach due to the decrease of inductance with the increase in the cross-sectional area as well as due to an increase of the parasitic capacitance to the substrate, proportional to the metal area. Designing with small track spacing s is usually beneficial due to the gain due to the increase of the mutual inductance term. This gain usually overcomes the drawback of having more track-to-track parasitic capacitance coupling that can potentially reduce the resonant frequency of the devices.

A summary of the studies and techniques performed to date in order design and fabricate high *Q* integrated inductors is schematically shown in tables 1.2 and 1.3.

| Strategy         | Advantages                         | Issues                                                    | References         |

|------------------|------------------------------------|-----------------------------------------------------------|--------------------|

| Use of circular  | Better quality                     | Not always available in the                               | [Chaki 1995, Park  |

| spirals          | factor than square                 | design kit (octagonal can be a                            | 1997, Lee 2001,    |

|                  | ones                               | good compromise)                                          | Aguilera 2002]     |

| Use of hollow    | Avoid using low                    | Use of more on-wafer                                      | [Craninckx 1997]   |

| spiral designs   | quality /                          | surface, increasing cost                                  |                    |

|                  | inductance in the                  |                                                           |                    |

|                  | inner part of the                  |                                                           |                    |

|                  | spiral                             |                                                           |                    |

| Tapered width    | Increase in $Q$ for                | Complicated design and                                    | [López-Villegas    |

| spirals          | the same area of                   | optimization, gain in Q is                                | 2000, Lin 2002]    |

|                  | other geometries                   | marginal if not properly                                  |                    |

|                  |                                    | designed                                                  | rmi u acci         |

| Symmetrical or   | Increase in Q                      | Needs high coupling (lower                                | [Tiemeijer 2001,   |

| transformer-like |                                    | spacing), via resistance limits                           | Danesh 2002]       |

| inductors        |                                    | the performance, needs                                    |                    |

| G                |                                    | differential excitation                                   | ID 11 20021        |

| Symmetrical      | Increase in $Q$ and                | Needs special circuit design                              | [Reiha 2003]       |

| excitation       | SRF due to less                    | (differential topology)                                   |                    |

|                  | substrate                          |                                                           |                    |

| Increase track   | influence Increase <i>Q</i> in low | Lamas substrate manasities and                            | [A avilana 2001]   |

| width            | frequencies                        | Large substrate parasitics and on-wafer area consumption, | [Aguilera 2001]    |

| wiath            | riequencies                        | reduce inductance                                         |                    |

| Reduce track     | Increase mutual                    | Needs tight fabrication                                   | [Aguilera 2001]    |

| spacing          | coupling, reduce                   | tolerances, increase of spiral                            | [Agunera 2001]     |

| spacing          | on-wafer area                      | capacitance                                               |                    |

| Overall          | Get best device                    | Needs accurate modeling                                   | [Crols 1996]       |

| optimization for | for the given                      | tools or a large library of                               | [ -1010 1 > 0 ]    |

| target           | inductance and                     | devices to produce                                        |                    |

| application      | frequency                          | measurement-based models                                  |                    |

| Reduce track     | Increase in                        | Large losses due to increased                             | -                  |

| width            | inductance, small                  | line resistance                                           |                    |

|                  | footprint                          |                                                           |                    |

| Stacked spirals  | Increase in                        | Large parasitics, decreased                               | [Koutsoyannopoulos |

| _                | inductance                         | SRF                                                       | 2000, Zolfaghari   |

|                  | density                            |                                                           | 2001, Lee 2007]    |

Table 1.2: Overview of design-related spiral inductor quality factor improvement strategies.

| Strategy         | Advantages                  | Issues                                                    | References            |

|------------------|-----------------------------|-----------------------------------------------------------|-----------------------|

| Increase the     | Reduce losses,              | Effective only at certain                                 | [Massin 2002]         |

| thickness of the | increasing $Q$              | frequencies (skin depth                                   |                       |

| metal            | _                           | limited), challenging etching                             |                       |

|                  |                             | steps or need of thick resist                             |                       |

|                  |                             | processing                                                |                       |

| High conductive  | Reduce losses,              | Needs new processing steps                                | [Bahl 2001, Zu        |

| metals           | increasing $Q$              | and materials (e.g. thick                                 | 1996, Ternent 1999,   |

|                  |                             | electroplating, advanced                                  | Carazzetti 2005]      |

|                  |                             | etching or CMP)                                           |                       |

| Low k polymers   | Decrease parasitic          | Need of new materials and                                 | [Burghartz 1997,      |

|                  | capacitances,               | processing steps (diffusion                               | Jeong 2003]           |

|                  | increase both Q             | barriers, adhesion                                        |                       |

|                  | and $f_{RES}$               | optimization)                                             |                       |

| Thick polymer    | Decouple spiral             | Delaminating, need of high-                               | [Arnold 1992,         |

| under the spiral | performance from            | quality vias or packaging-like                            | Baringer 1993,        |

| or use of        | substrate                   | technology to fabricate the                               | Beyne 1995,           |

| multichip        | resistivity, very           | devices                                                   | Shimoto 1995,         |

| module           | good RF                     |                                                           | Samber 1998,          |

| deposition       | performances                |                                                           | Pieters 1998, Pieters |

| (MCM-D)          |                             |                                                           | 2001, Carchon         |

| technology       |                             |                                                           | 2004]                 |

| High resistivity | Eliminate killing           | Makes the process less                                    | [Benaissa 2003,       |

| substrates       | substrate                   | compatible with standard                                  | Spirito 2005]         |

|                  | parasitics                  | CMOS                                                      | 1000                  |

| Backside etching | Eliminate killing           | Complicated fabrication                                   | [Ozgur 1999,          |

|                  | substrate                   | steps, stress related issues for                          | López-Villegas        |

|                  | parasitics using            | thick metals, fragile structures                          | 2000]                 |

|                  | low resistivity substrates  |                                                           |                       |

| Front side       |                             | Complicated fabrication                                   | II alzdawala 20021    |

|                  | Eliminate killing substrate | Complicated fabrication, stress related issues with thick | [Lakdawala 2002]      |

| etching          | parasitics when             | metals                                                    |                       |

|                  | using low                   | inetals                                                   |                       |

|                  | resistivity                 |                                                           |                       |

|                  | substrates                  |                                                           |                       |

| Free standing    | Less prone to               | Stress related issues, tunable                            | [Syms 1993, Yoon      |

| structures       | substrate losses,           | L has very low $Q$ and                                    | 1999, Jiang 2000,     |

| 201 40041 00     | enable the                  | bandwidth and usually need                                | Dahlmann 2001,        |

|                  | fabrication of              | very high actuation voltage                               | Dahlmann 2002,        |

|                  | tunable devices,            | , , , , , , , , , , , , , , , , , , ,                     | Zou 2003]             |

|                  | introducing new             |                                                           |                       |

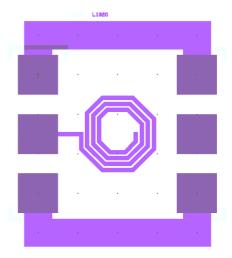

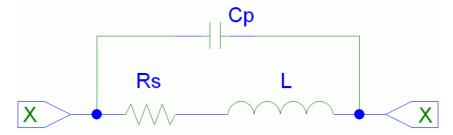

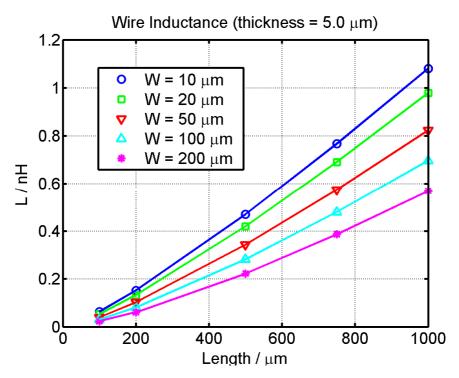

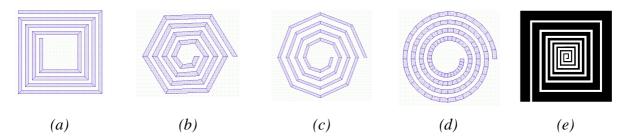

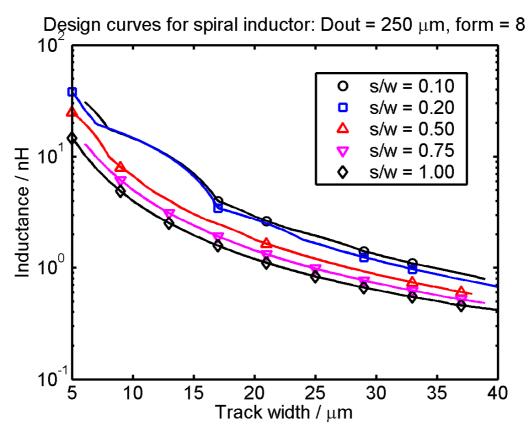

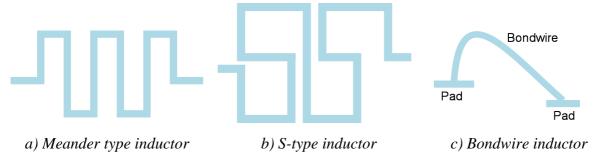

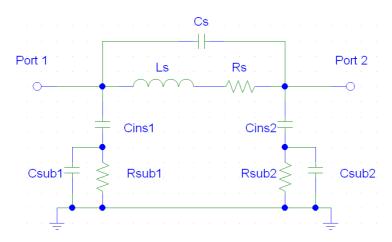

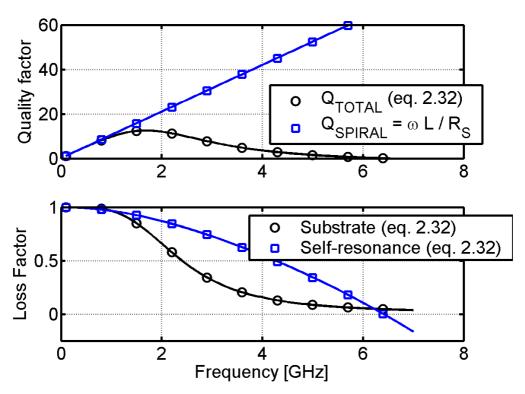

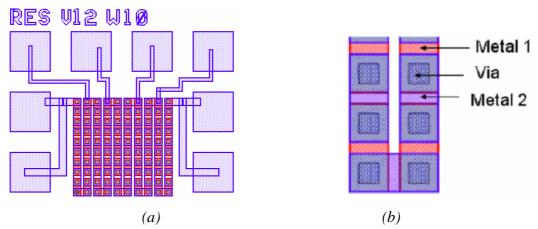

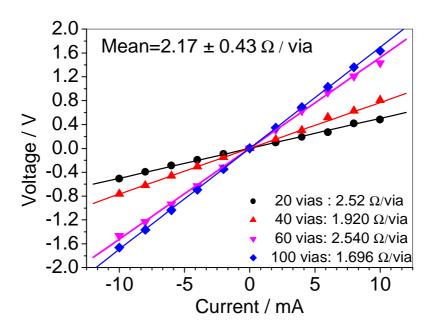

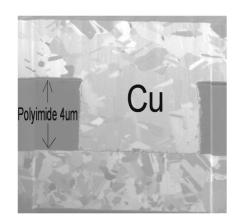

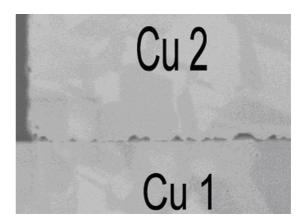

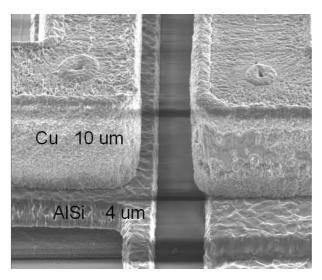

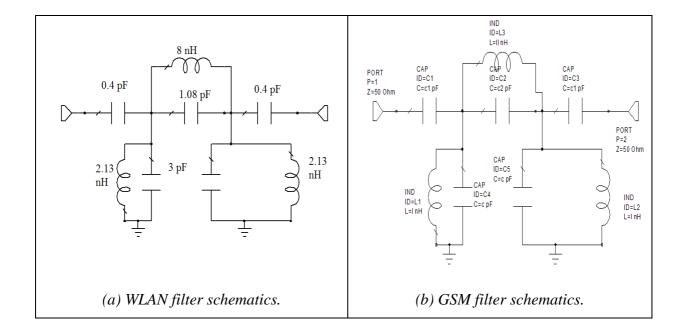

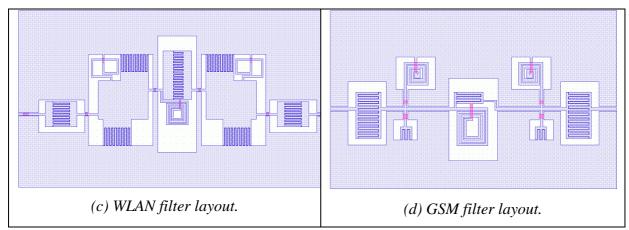

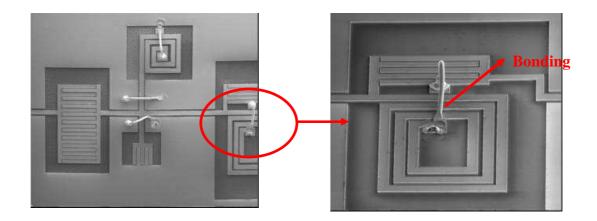

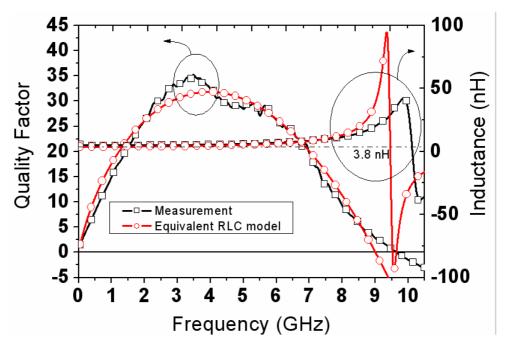

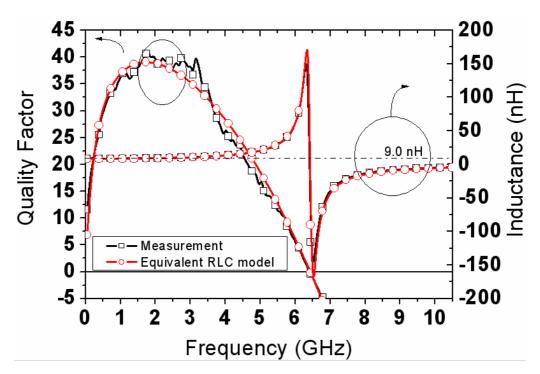

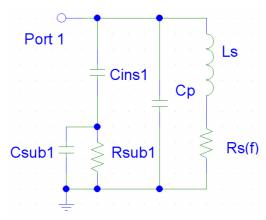

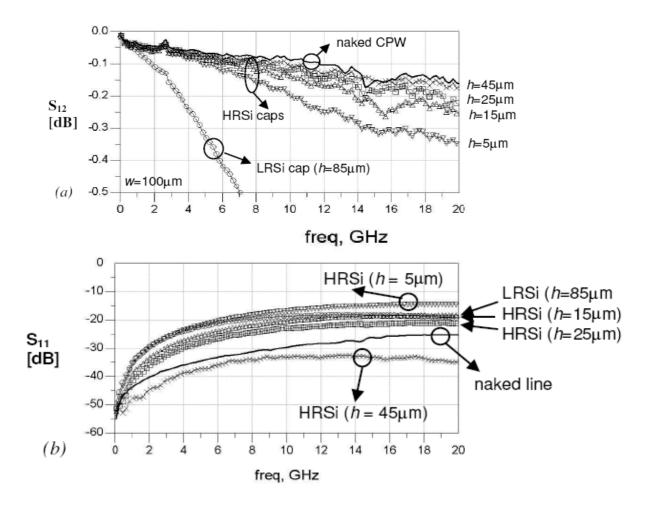

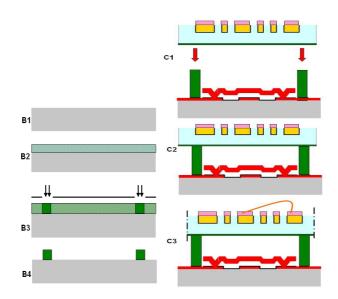

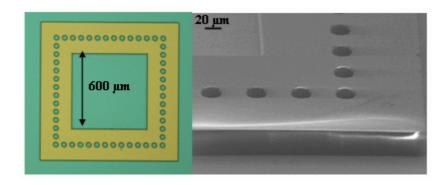

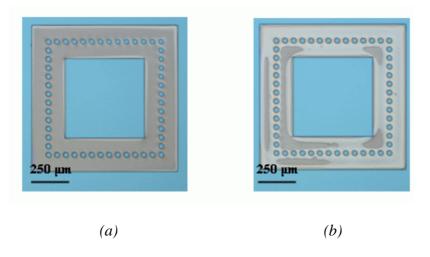

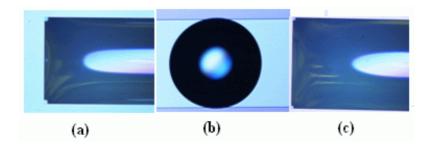

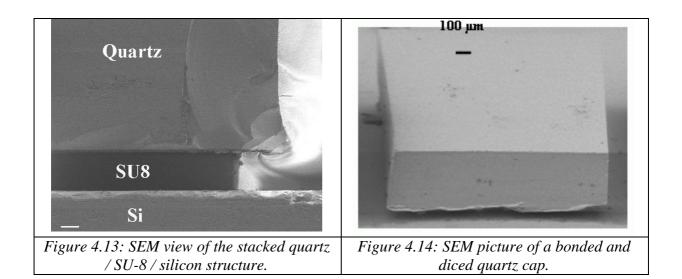

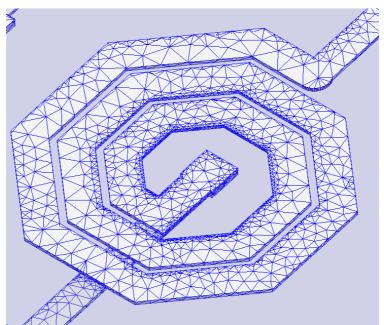

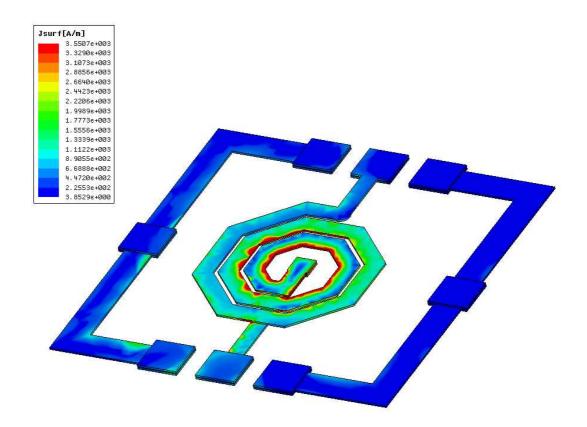

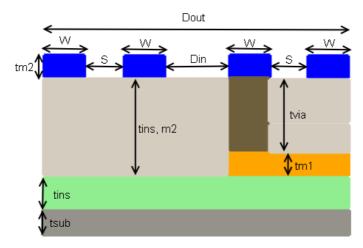

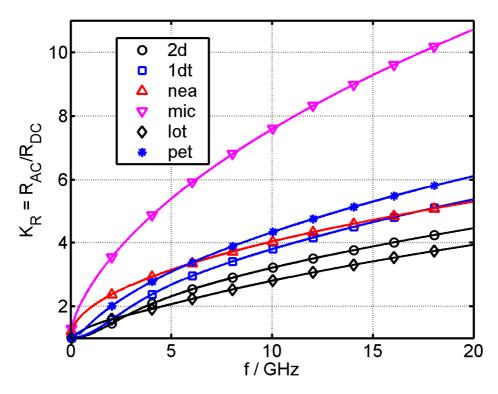

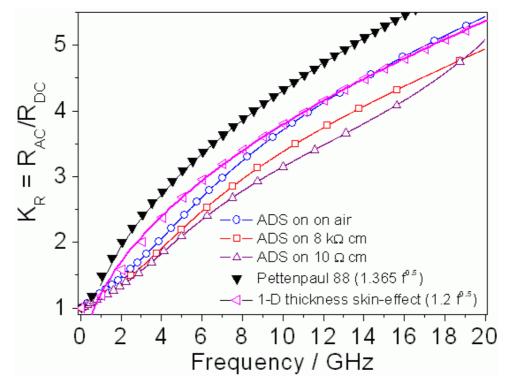

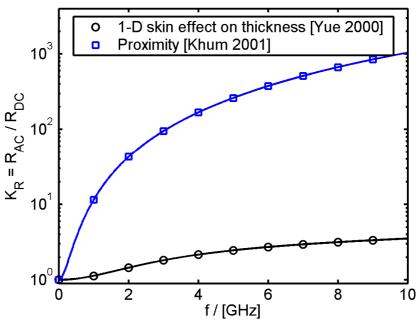

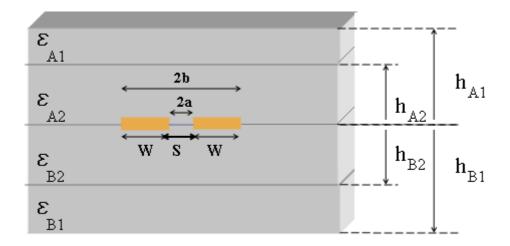

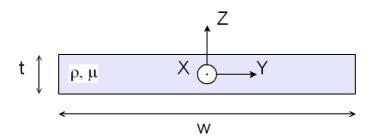

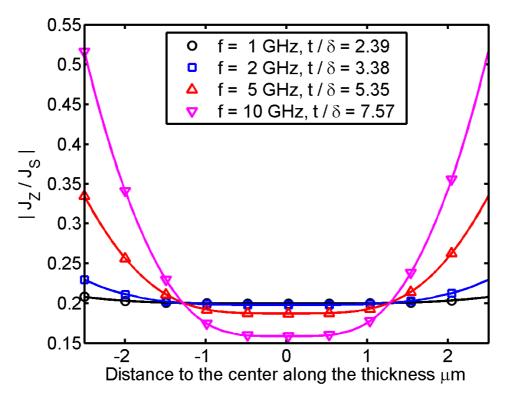

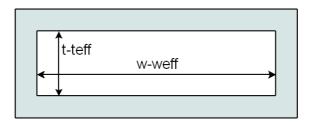

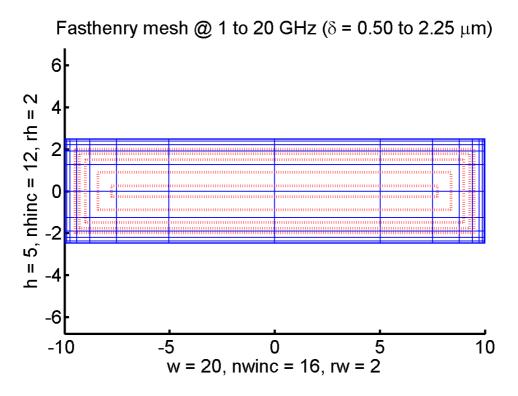

|                  | functionality               |                                                           |                       |