## Direct fabrication of thin layer MoS2 field-effect nanoscale transistors by oxidation scanning probe lithography

Francisco M. Espinosa, Yu K. Ryu, Kolyo Marinov, Dumitru Dumcenco, Andras Kis, and Ricardo Garcia

Citation: Applied Physics Letters 106, 103503 (2015); doi: 10.1063/1.4914349

View online: http://dx.doi.org/10.1063/1.4914349

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/106/10?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Synthesized multiwall MoS2 nanotube and nanoribbon field-effect transistors

Appl. Phys. Lett. 106, 022114 (2015); 10.1063/1.4906066

Selective chemical vapor sensing with few-layer MoS2 thin-film transistors: Comparison with graphene devices Appl. Phys. Lett. **106**, 023115 (2015); 10.1063/1.4905694

Growth-substrate induced performance degradation in chemically synthesized monolayer MoS2 field effect transistors

Appl. Phys. Lett. 104, 203506 (2014); 10.1063/1.4873680

Electrical performance of monolayer MoS2 field-effect transistors prepared by chemical vapor deposition Appl. Phys. Lett. **102**, 193107 (2013); 10.1063/1.4804546

Comparative study of chemically synthesized and exfoliated multilayer MoS2 field-effect transistors Appl. Phys. Lett. **102**, 043116 (2013); 10.1063/1.4789975

## Direct fabrication of thin layer MoS<sub>2</sub> field-effect nanoscale transistors by oxidation scanning probe lithography

Francisco M. Espinosa,  $^1$  Yu K. Ryu,  $^1$  Kolyo Marinov,  $^2$  Dumitru Dumcenco,  $^2$  Andras Kis,  $^2$  and Ricardo Garcia  $^{1,a)}$

(Received 4 December 2014; accepted 25 February 2015; published online 11 March 2015)

Thin layer  $MoS_2$ -based field effect transistors (FET) are emerging candidates to fabricate very fast and sensitive devices. Here, we demonstrate a method to fabricate very narrow transistor channel widths on a single layer  $MoS_2$  flake connected to gold electrodes. Oxidation scanning probe lithography is applied to pattern insulating barriers on the flake. The process narrows the electron path to about 200 nm. The output and transfer characteristics of the fabricated FET show a behavior that is consistent with the minimum channel width of the device. The method relies on the direct and local chemical modification of  $MoS_2$ . The straightforward character and the lack of specific requirements envisage the controlled patterning of sub-100 nm electron channels in  $MoS_2$  FETs. ©  $2015 \ AIP \ Publishing \ LLC$ . [http://dx.doi.org/10.1063/1.4914349]

Single layer  $MoS_2$  is a relevant two-dimensional semiconductor material with the potential to fabricate novel electronic and optical devices. <sup>1-4</sup> Field effect transistors based on  $MoS_2$  have been devised <sup>5-7</sup> and applied as label-free biosensors <sup>8-10</sup> or memory cells. <sup>11</sup> The integration of  $MoS_2$  electronics will be enhanced by the development of direct patterning methods with the capability to generate nanoscale features on  $MoS_2$ .

The optimization of the  $MoS_2$  nanoscale devices and the enhancement of their applications require the development of direct, reliable, and easy-to use nanopatterning methods. The positioning capabilities and patterning resolution of scanning probe lithography  $(SPL)^{12}$  make SPL a candidate to pattern  $MoS_2$  flakes at the nanoscale level. Different SPL methods have been applied to pattern graphene-like and other carbon-based materials.  $^{13-16}$

Oxidation scanning probe lithography (o-SPL) has been used to fabricate a variety of nanoscale devices on different materials such as nanowire FETs on silicon, <sup>17,18</sup> random access memories on gallium arsenide, <sup>19</sup> single photon detectors on niobium nitride, <sup>20</sup> or quantum dots on graphene. <sup>21</sup>

We report the development of o-SPL to directly change the chemical composition of selected regions of a  $MoS_2$  flake by applying a negative voltage pulse between the tip and the flake in the presence of ozone. The modification produces structures that protrude from the flake baseline. Those barriers effectively suppress the electron transport across them. The ability to control the size of the patterns is exploited to reduce the conduction channel of a  $MoS_2$  monolayer field-effect transistor from microns to hundreds of nanometers. The output curves of the FET before and after o-SPL demonstrate that the electrons are channeled through a 200 nm constriction. It also shows that the o-SPL process does not degrade the electrical properties of the unmodified  $MoS_2$  regions.

The MoS<sub>2</sub> layers were grown by means of chemical vapor deposition (CVD) on sapphire substrates based on the gas phase reaction of MoO<sub>3</sub> and sulfur at 700 °C.<sup>22</sup> Single triangular domains of single layer MoS2 are formed on the surface. Their orientation follows the underlying sapphire crystal structure. For the fabrication of field-effect transistors, the material was transferred to a Si substrate covered with 270 nm thermally grown SiO<sub>2</sub> using the wet transfer KOH method and 950PMMA A2 as support polymer. After transferring, PMMA is removed in acetone and residues are removed during annealing in Ar atmosphere at 350 °C for 5 h. Metallic contacts were defined by means of conventional electron beam lithography (EBL) followed by the deposition of 90 nm Au. Finally, contact annealing at 200 °C in Ar atmosphere was performed to reduce contact resistance and eliminate resist residues.

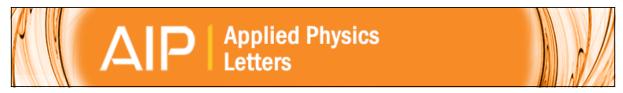

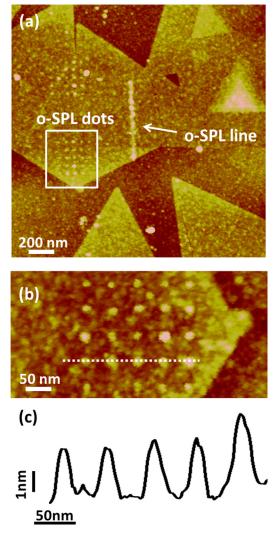

The atomic force microscope (AFM) and the sample are kept in a closed chamber to control the relative humidity and the temperature during the oxidation process. The o-SPL is performed by operating the AFM in the amplitude modulation mode<sup>23</sup> with a free amplitude in the 5–10 nm range and a set point amplitude/free amplitude ratio of about 0.9. We have used n<sup>+</sup>-doped silicon cantilevers (NCH-W, NanoWorld) with a force constant of about 40 N/m and a resonant frequency of about 300 kHz. The relative humidity is kept in 40%-60% range. Voltage pulses of 40-60 V and 0.5 ms were used. To enhance the oxidation of MoS2, we have enriched the SPL chamber with ozone.<sup>24</sup> The ozone was generated by illuminating the chamber with ultraviolet light for 30 min. Figure 1 shows a scheme of o-SPL applied to pattern MoS<sub>2</sub> flakes. Figure 3(a) shows several MoS<sub>2</sub> flakes transferred on a SiO<sub>2</sub> layer 270 nm thick. They are contacted with gold pads by EBL.5

The I–V curves were recorded before and after the lithography process to check the effect of the patterning on the device. The measurements were performed at room temperature in a probe station (Everbeing EB 06, Taiwan) with a semiconductor analyser (Keithley 4200).

<sup>&</sup>lt;sup>1</sup>Instituto de Ciencia de Materiales, CSIC, Sor Juana Inés de la Cruz 3, Madrid, Spain

<sup>&</sup>lt;sup>2</sup>École Polytechnique Fédérale de Lausanne, LANES, Station 17, Lausanne, Switzerland

a)r.garcia@csic.es

FIG. 1. (a) Scheme of the fabrication process of dielectric barriers on a  $MoS_2$  flake by o-SPL. An ozone enriched atmosphere enhances the oxidation rate of the surface. (b) Scheme of the final device. The dielectric barriers define the electron channel

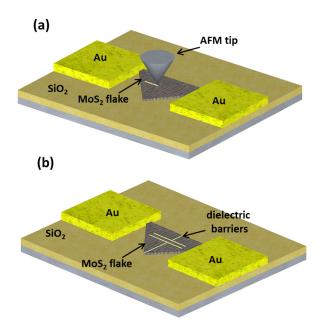

FIG. 2. (a) AFM topography image of some o-SPL nanostructures fabricated on a MoS<sub>2</sub> flake. (b) High resolution AFM topographic image of the array of o-SPL dots shown in (a). (c) AFM cross section along the line marked in (b).

Figure 2(a) shows several nanostructures fabricated by o-SPL. An array of dots and a line were fabricated with voltage pulse amplitude and duration, relative humidity and free amplitude of, respectively, 54 V and  $250 \,\mu\text{s}$ , 45% and  $5 \,\text{nm}$ . Figures 2(b) and 2(c) show, respectively, the AFM topographic image and cross section of one of the rows of dots represented in Figure 2(a). The structures protrude 2–5 nm from the  $\text{MoS}_2$  flake, and the widths—given at full width at half maximum (FWHM)—are between 40–50 nm (Fig.2(c)).

We propose that the application of high electric fields during o-SPL (about 10 V/nm) favors the formation of MoO<sub>3</sub>. Rolandi *et al.*<sup>25</sup> have applied o-SPL to transform selected regions of a molybdenum thin film into MoO<sub>3</sub>. The stoichiometry of the formed oxide (MoO<sub>3</sub>) was inferred because the patterns were soluble in water. In addition, Ross and Sussman<sup>26</sup> have described the reaction of MoS<sub>2</sub> surface in the presence of water vapor and a temperature of 85 °C as

$$2\text{MoS}_2 + 9\text{O}_2 + 4\text{H}_2\text{O} \rightarrow 2\text{MoO}_3 + 4\text{H}_2\text{SO}_4.$$

(1)

We propose that the electric field replaces the role of the temperature to facilitate the transformation of MoS<sub>2</sub> into MoO<sub>3</sub>. In fact, the patterns fabricated on MoS<sub>2</sub> by o-SPL are readily etched in water, which supports the formation of MoO<sub>3</sub> during the lithographic process.

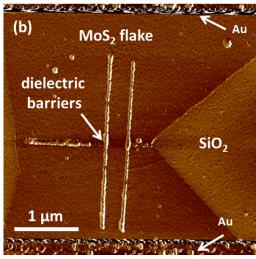

FIG. 3. (a) Optical image of several MoS $_2$  flakes deposited on a 270 nm thick SiO $_2$  layer. One of these flakes has been contacted with gold pads by electron beam lithography. (b) AFM phase image of a MoS $_2$  thin layer FET. The narrowest section of the channel is 200 nm wide. An additional dielectric barrier prevents the current flow outside the channel.

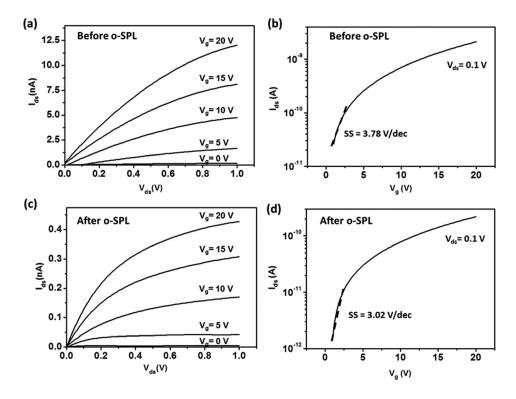

FIG. 4. Output and transfer characteristics of a MoS<sub>2</sub> FET. (a) Output and (b) transfer curves before the fabrication of dielectric barriers by o-SPL. (c) Output and (d) transfer curves of the nano-FET after o-SPL. The current ratio observed between the thin layer FET and the nano FET corresponds to the change in the ohmic resistance given by the width ratio between the channel and the unmodified flake. The curves were taken at room temperature. The dashed lines in (b) and (d) represent the section where the SS values have been calculated.

The process to fabricate a 200 nm channel constriction on a thin layer MoS2 FET starts from contacting a flake on SiO<sub>2</sub> layer with two gold microelectrodes (Fig. 3(a)). The optical image shows a flake derived from the coalescence of two triangular flakes bridging the electrodes. This system could already be operated as a FET having the silicon substrate as a third electrode (back gate) underneath the SiO<sub>2</sub>. Oxidation SPL is used to decrease the width of the FET channel. For this, we pattern two parallel lines running from source to drain gold electrodes. To avoid any damage in the Au electrodes, the patterning starts and ends about 100-200 nm from the Au electrodes. To direct the electron flow from the Au electrodes through the space defined by the oxide lines, we have also patterned a line running perpendicular to the oxide channel lines as it is shown in the AFM phase image (Fig. 3(b)). This line will act as a dielectric barrier to prevent the electron leakage outside the electron channel.

To illustrate the performance of the fabricated FET, we have compared the output and transfer curves before and after (nano-FET) the patterning process. Those curves were acquired by using the same values of source-to-drain and gate voltages. The device is an *n*-channel transistor because the current increases with the positive gate voltage. The output and transfer curves before the o-SPL patterning are shown in Fig. 4 (panels (a) and (b)). From the transfer curve, a subthreshold swing (SS) of 3.78 V/dec is obtained. The output and transfer characteristics of the nano-FET are depicted in Figs. 4(c) and 4(d). The output curves show a reduction of the current of about one order of magnitude. In the linear regime of the output curves ( $V_g = 20 \text{ V}$  and  $V_{ds} = 0.05 \text{ V}$ ), we obtain a current ratio between the original FET and the nano-FET of 12.4. This ratio is very close to the change in the ohmic resistance from the 2100 nm wide MoS<sub>2</sub> flake to the 200 nm wide channel constriction. We also observe that the saturation regime is reached at lower  $V_{ds}$  values in the nano-FET. The SS obtained from the transfer curve of the nano-FET is of 3.02 V/dec. This value is smaller than the one obtained before o-SPL. In any case, those values are higher than the ones obtained by using thicker  $MoS_2$  flakes. The high SS values obtained here are attributed to the use of ultra-thin  $MoS_2$  flakes and the type of dielectric  $(SiO_2)$ .

In short, we have demonstrated an o-SPL method to fabricate thin layer MoS<sub>2</sub> field effect transistors with a channel width of 200 nm. Oxidation SPL is applied to define the transistor channel across the source and drain electrodes by patterning dielectric barriers on the thin layer MoS<sub>2</sub> flake. The decrease of the electron conductance in the nano-FET with respect to the precursor MoS<sub>2</sub> FET scales linearly with the channel width ratio. This lithography process is direct and does not require any specific sample preparation. In addition, the dielectric barrier width (30 nm) envisages the fabrication of MoS<sub>2</sub> field effect transistors with sub-100 nm channel widths.

This work was funded by the European Union FP7/2007-2013 under Grant Agreement No. 318804 (SNM), the Ministerio de Economía y Competitividad (Spain) under Grant No. MAT2013-44858-R, the Marie Curie ITN network "MoWSeS" (Grant No. 317451) and the Swiss SNF Sinergia Grant No. 147607.

<sup>&</sup>lt;sup>1</sup>O. Lopez-Sanchez, D. Lembke, M. Kayci, A. Radenovic, and A. Kis, Nat. Nanotechnol. **8**, 497 (2013).

<sup>&</sup>lt;sup>2</sup>K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, Phys. Rev. Lett. **105**, 136805 (2010).

<sup>&</sup>lt;sup>3</sup>W. Zhang, J.-K. Huang, C.-H. Chen, Y.-H. Chang, Y.-J. Cheng, and L.-J. Li, Adv. Mater. **25**, 3456 (2013).

<sup>&</sup>lt;sup>4</sup>Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, and M. S. Strano, Nat. Nanotechnol. 7, 699 (2012).

<sup>&</sup>lt;sup>5</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nat. Nanotechnol. **6**, 147 (2011).

- <sup>6</sup>B. Radisavljevic and A. Kis, Nat. Mater. 12, 815 (2013).

- <sup>7</sup>Y. Zhang, J. Ye, Y. Matsuhashi, and Y. Iwasa, Nano Lett. **12**, 1136 (2012).

- <sup>8</sup>D. Sarkar, W. Liu, X. Xie, A. C. Anselmo, S. Mitragotri, and K. Banerjee, ACS Nano 8, 3992 (2014).

- <sup>9</sup>L. Wang, Y. Wang, J. I. Wong, T. Palacios, J. Kong, and H. Y. Yang, Small **10**, 1101 (2014).

- <sup>10</sup>K. Liu, J. Feng, A. Kis, and A. Radenovic, ACS Nano 8, 2504 (2014).

- <sup>11</sup>S. Bertolazzi, D. Krasnozhon, and A. Kis, ACS Nano 7, 3246 (2013).

- <sup>12</sup>R. Garcia, A. W. Knoll, and E. Riedo, Nat. Nanotechnol. 9, 577 (2014).

- <sup>13</sup>L. L. Cheong, P. Paul, F. Holzner, M. Despont, D. J. Coady, J. L. Hedrick, R. Allen, A. W. Knoll, and U. Duerig, Nano Lett. 13, 4485 (2013).

- <sup>14</sup>M. Kaestner, M. Hofer, and I. W. Rangelow, J. Micro/Nanolithogr. MEMS, MOEMS 12, 031111 (2013).

- <sup>15</sup>L. Oria, A. Ruiz de Luzuriaga, J. A. Alduncin, and F. Perez-Murano, Microelectron. Eng. 110, 234 (2013).

- <sup>16</sup>Z. Wei, D. Wang, S. Kim, S.-Y. Kim, Y. Hu, M. K. Yakes, A. R. Laracuente, Z. Dai, S. R. Marder, C. Berger, W. P. King, W. A. de Heer, P. E. Sheehan, and E. Riedo, Science 328, 1373 (2010).

- <sup>17</sup>M. Chiesa, P. P. Cárdenas, F. Otón, J. Martínez, M. Mas-Torrent, F. García, J. C. Alonso, C.Rovira, and R. Garcia, Nano Lett. 12, 1275 (2012).

- <sup>18</sup>J. Martínez, R. V. Martínez, and R. Garcia, Nano Lett. **8**, 3636 (2008).

- <sup>19</sup>J. T. H. Tsai, C. H. Hsu, C. Y. Hsu, and C. S. Yang, Electron. Lett. **49**, 554 (2013).

- <sup>20</sup>C. Delacour, B. Pannetier, J. C. Villegier, and V. Bouchiat, Nano Lett. 12, 3501 (2012).

- <sup>21</sup>R. K. Puddy, C. J. Chua, and M. R. Buitelaar, Appl. Phys. Lett. 103, 183117 (2013).

- <sup>22</sup>D. Dumcenco, D. Ovchinnikov, K. Marinov, O. Lopez-Sanchez, D. Krasnozhon, M.-W. Chen, P. Gillet, A. F. Morral, A. Radenovic, and A. Kis, preprint arXiv:1405.0129[cond-mat] (2014).

- <sup>23</sup>R. Garcia and A. San Paulo, Phys. Rev. B **60**, 4961 (1999).

- <sup>24</sup>F. M. Espinosa and R. Garcia, "Improved oxidation scanning probe lithography in ozone enriched environments" (unpublished).

- <sup>25</sup>M. Rolandi, C. F. Quate, and H. Dai, Adv. Mater. **14**, 191 (2002).

- <sup>26</sup>S. Ross and A. Sussman, J. Phys. Chem. **59**, 889 (1955).

- <sup>27</sup>S. Kim, A. Konar, W. S. Hwang, J. H. Lee, C. Jung, H. Kim, J. B. Yoo, J. Y. Choi, S. Y. Lee, D. Jena, W. Choi, and K. Kim, Nat. Commun. 3, 1011 (2012).