# MoS<sub>2</sub> Transistors Operating at Gigahertz Frequencies

Daria Krasnozhon, Dominik Lembke, Clemens Nyffeler, Yusuf Leblebici, and Andras Kis\*

Electrical Engineering Institute, Ecole Polytechnique Federale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland

Supporting Information

**ABSTRACT:** The presence of a direct band gap<sup>1-4</sup> and an ultrathin form factor<sup>5</sup> has caused a considerable interest in two-dimensional (2D) semiconductors from the transition metal dichalcogenides (TMD) family with molybdenum disulfide (MoS<sub>2</sub>) being the most studied representative of this family of materials. While diverse electronic elements, <sup>6,7</sup> logic circuits, <sup>8,9</sup> and optoelectronic devices <sup>12,13</sup> have been demonstrated using ultrathin MoS2, very little is known about their performance at high frequencies where commercial

devices are expected to function. Here, we report on top-gated MoS<sub>2</sub> transistors operating in the gigahertz range of frequencies. Our devices show cutoff frequencies reaching 6 GHz. The presence of a band gap also gives rise to current saturation, 10 allowing power and voltage gain, all in the gigahertz range. This shows that MoS<sub>2</sub> could be an interesting material for realizing high-speed amplifiers and logic circuits with device scaling expected to result in further improvement of performance. Our work represents the first step in the realization of high-frequency analog and digital circuits based on 2D semiconductors.

KEYWORDS: MoS<sub>2</sub>, 2D semiconductors, radio frequency, current gain, voltage gain, power gain

he operating frequency of semiconductor devices has increased remarkably since the invention of the first transistor. By reducing the transistor's critical dimensions, we can at the same time reduce the electron transit time and the gate capacitance that boosts the performance of transistors in the high-frequency range. The next challenging step is to reduce the device dimensions in the vertical direction to their ultimate limit. For this purpose, nanoscale materials such as carbon nanotubes (CNTs)<sup>11,12</sup> and graphene<sup>13–15</sup> have been suggested. Theory predicts that CNTs operating in the ballistic regime could provide a gain in the terahertz range. 16 However, their small size carries disadvantages, such as the large contact resistance resulting in high device impedance, making it difficult to measure and integrate CNT-based devices with a standard radio frequency (RF) setup.

Another candidate for future high-frequency devices is graphene. Graphene shows large carrier mobility<sup>17</sup> and saturation velocity.<sup>18</sup> Graphene field-effect transistors (GFETs) have lower impedance compared to CNT-FETs, making impedance matching a less sensitive issue in GFETs than in CNT-FETs. The other important advantage of graphene compared to CNTs lies in its two-dimensional (2D) nature and high mobility that results in large trans-conductance  $g_{\rm m}$  and intrinsic cutoff frequency  $f_{\rm T}$ ,  $^{13,19,20}$  the frequency at which current gain becomes unity.

Power and voltage amplification are also important transistor applications in electronic circuits. The maximum frequency of oscillation  $f_{\text{max}}$  is the frequency at which the power gain equals unity. In high-performance voltage and power amplifiers,  $f_{\text{max}}$ should be as high as possible. In the case of RF-GFETs,  $f_{max}$  still remains lower than the current gain cutoff frequency  $f_{\rm T}$ because it is relatively difficult to achieve saturation in graphene

FETs due to the absence of a band gap. In devices that lack saturation in drain current, this results in high values of drain conductance  $g_{\rm ds}$  and limited voltage gain  $A_{\rm v}=g_{\rm m}/g_{\rm ds}$ .

Other 2D materials such as for example molybdenum disulfide (MoS2) could be interesting for applications in RF electronics, especially in high-frequency digital electronics where voltage gain higher than 1 is desired. MoS2 is a semiconductor from the family of transition-metal dichalcogenide (TMD) materials with the common formula MX<sub>2</sub>, where M represents a transition metal (M = Mo,W, Nb, Ta, Ti, or Re) and X stands for either Se, S, or Te. MoS2 has a bandgap and unique valley<sup>21,22</sup> and spin properties as well as remarkable properties for new electronic and optoelectronic applications.<sup>23</sup> In contrast to graphene, which is a semimetal, MoS<sub>2</sub> is a 2D semiconductor with an electronic structure dependent on its thickness. 1-4 First, locally gated FETs based on monolayers of MoS<sub>2</sub><sup>24</sup> were shown to have room-temperature current on/off ratio higher than 108. Monolayer MoS<sub>2</sub> also shows voltage gain<sup>25</sup> larger than 10, due to its natural band gap, high intrinsic transconductance and drain-source current saturation. 10 The combination of all these properties makes MoS2 attractive for high-frequency applications. Self-consistent ballistic quantum transport simulations, independent of mobility values, show that cutoff frequencies well above 100 GHz could be possible for MoS $_2$  transistors with channel lengths of  $L_{\rm g}\sim 15$  nm, operating in the ballistic limit. In addition, large-area MoS $_2$ can be prepared using either liquid-phase exfoliation <sup>27</sup> or CVD growth. <sup>28–30</sup>

July 25, 2014 Received: Revised: September 10, 2014

Here, we characterize top-gated MoS $_2$  FETs in the high-frequency range. The current gain of MoS $_2$  FETs decreases with increasing frequency and shows the typical 1/f dependence for different thicknesses of 2D MoS $_2$  crystals. We realized MoS $_2$  FETs with a maximum transconductance  $g_{\rm m}=54~\mu{\rm S}/\mu{\rm m}$ , the highest transconductance in MoS $_2$  transistors reported up to date,  $^{10}$  and showing current saturation. The highest intrinsic cutoff frequency  $f_{\rm T}$  derived from the measured scattering parameters is 6 GHz and presents a strong dependence on the bias voltage, gate voltage, and material thickness. MoS $_2$  RF transistors also show a voltage gain higher than 1 and a maximum frequency of oscillation comparable to the cutoff frequency, reaching  $f_{\rm max}=8.2$  GHz, which makes MoS $_2$  interesting for high-frequency logic circuits and amplifiers.

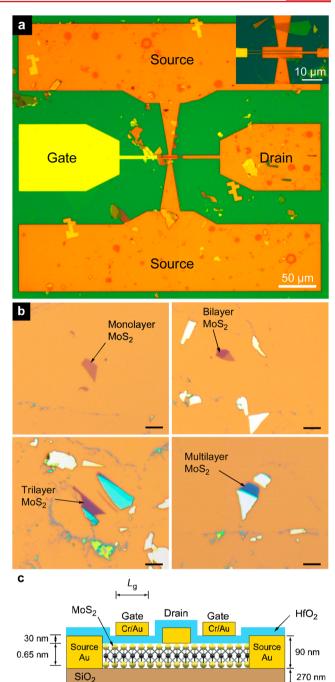

Our MoS<sub>2</sub> FETs are fabricated from MoS<sub>2</sub> exfoliated onto a highly resistive intrinsic Si substrate covered with 270 nm thick SiO<sub>2</sub>. 31 Figure 1 shows the device layout of a MoS<sub>2</sub> FET with probe pads in the ground-signal-ground configuration (GSG) designed for high-frequency measurements. We have fabricated RF transistors based on 1L-MoS<sub>2</sub>, 2L-MoS<sub>2</sub>, 3L-MoS<sub>2</sub>, and multilayer (5 nm thick) MoS<sub>2</sub> crystals shown in Figure 1b. Electrical contacts were patterned using electron-beam lithography and by depositing 90 nm thick gold electrodes. This was followed by an annealing step at 200 °C in order to remove resist residue and decrease the contact resistance. Atomic layer deposition (ALD) was used to deposit a 30 nm thick layer of high-k dielectric HfO2. Local top gates for controlling the current in the two branches were fabricated using another e-beam lithography step followed by evaporation of 10 nm/50 nm of Cr/Au. All of our devices had a gate length  $L_{\rm g}$  = 240 nm with the underlap region 50 nm long on both sides of the gate electrode. Channel widths are in the 9-21.5  $\mu$ m range due to the stochastic nature of the MoS<sub>2</sub> exfoliation

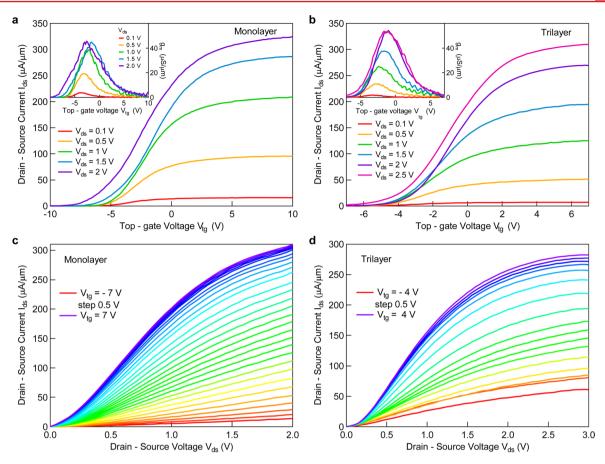

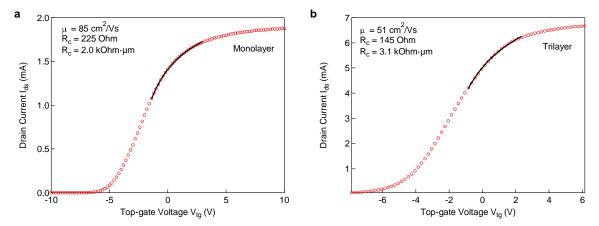

Transfer and output characteristics of 1L-MoS<sub>2</sub> and 3L-MoS<sub>2</sub> FETs are shown in Figure 2. All our devices show transconductance typical of n-type semiconductors with onstate current reaching ~300  $\mu$ A/ $\mu$ m for  $V_{\rm ds}=2$  V and gate voltage  $V_{\rm tg}=10$  V in the case of monolayer MoS<sub>2</sub>. The dielectric constant of 30 nm HfO<sub>2</sub> deposited at 200 °C is 14, probably due to surface impurities trapped between the HfO<sub>2</sub> and MoS<sub>2</sub> layer. From the  $I_{\rm ds}-V_{\rm tg}$  characteristic of our devices, we extract estimates for the field effect mobility and contact resistance  $\mu_{\rm FE}=85$  cm<sup>2</sup>/(V s) and  $R_{\rm c}=2.0$  k $\Omega\cdot\mu$ m for the case of the monolayer device and  $\mu_{\rm FE}=51$  cm<sup>2</sup>/(V s) and  $R_{\rm c}=3.1$  k $\Omega\cdot\mu$ m for the trilayer device (Figure S1 in Supporting Information).

One of the most important parameters affecting the high-frequency performance of transistors is the transconductance  $g_{\rm m}=dI_{\rm ds}/dV_{\rm tg}$ , shown in the insets of Figure 2a,b. The magnitude of  $g_{\rm m}$  drastically rises when increasing  $V_{\rm ds}$  in the range from 100 mV to 1.5 V for 1L-MoS<sub>2</sub> and from 100 mV to 2 V for 3L-MoS<sub>2</sub>, reaching a maximum of ~44  $\mu$ S/ $\mu$ m for the single-layer and ~54  $\mu$ S/ $\mu$ m for the trilayer device. These values are comparable to those reported for the first graphene RF devices <sup>13</sup> and are desirable for achieving high-frequency operation. Our devices can also easily achieve saturation. Figure 2c,d show the  $I_{\rm ds}$ - $V_{\rm ds}$  characteristics of two MoS<sub>2</sub> devices with a different number of layers. We measure very low values for the channel conductance  $g_{\rm ds}$ , reaching values as low as ~3  $\mu$ S/ $\mu$ m in the trilayer device at  $V_{\rm ds}$  = 3 V and  $V_{\rm tg}$  = 4 V.

Figure 1.  $MoS_2$ -based high-frequency transistors. (a) Optical image of the device layout with ground—signal—ground pads for the drain and the gate on intrinsic Si substrate covered with a 270 nm thick  $SiO_2$  layer. The inset shows the magnified optical image of the coplanar waveguide with the gate length  $L_g = 240$  nm. The total channel length is 340 nm. Underlap regions are 50 nm long. (b) Optical images of 1L- $MoS_2$ , 2L- $MoS_2$ , 3L- $MoS_2$ , and multilayer (5 nm thick)  $MoS_2$ . Transistors are fabricated on top of regions with uniform crystal thickness. Scale bar is 10  $\mu$ m long. (c) Schematic cross-sectional view of the RF- $MoS_2$  transistor.

intrinsic Si

One of the main figures of merit to estimate the performance of radio frequency devices is the cutoff frequency  $f_{\rm T}$ , the frequency at which the current gain becomes unity<sup>32</sup>

Figure 2. DC output characteristics of MoS<sub>2</sub> RF transistors. (a) Transfer characteristic for 1L-MoS<sub>2</sub> FET under the applied drain voltage in the range from  $V_{\rm ds} = 0.1-2$  V with a step of 0.5 V. (b) Transfer characteristic for 3L-MoS<sub>2</sub> FET under the applied drain voltage in the range from  $V_{\rm ds} = 0.1-2.5$  V with a step of 0.5 V. Insets in panels a and b show the transconductance of 1L-MoS<sub>2</sub> and 3L-MoS<sub>2</sub> derived from  $I_{\rm ds}-V_{\rm tg}$  characteristics. (c) The drain current  $I_{\rm ds}$  as a function of bias voltage  $V_{\rm ds}$  measured for different top-gate voltages in the case of a device based on single-layer MoS<sub>2</sub>. The top-gate voltage varies from -7 to 7 V with a step of 0.5 V. (d) The drain current  $I_{\rm ds}$  as a function of bias voltage  $V_{\rm ds}$  for the 3L-MoS<sub>2</sub> device, measured for different top-gate voltages. The gate voltage varies from -4 to 4 V with a step of 0.5 V.

$$\begin{split} f_{\rm T} &= \frac{g_{\rm m}}{2\pi} \\ &\times \frac{1}{(C_{\rm gs} + C_{\rm gd})[1 + g_{\rm ds}(R_{\rm s} + R_{\rm d})] + C_{\rm gd}g_{\rm m}(R_{\rm s} + R_{\rm d})} \end{split}$$

where  $g_{\rm m}$  is the intrinsic transconductance,  $C_{\rm gs}$  is the gate-source capacitance,  $C_{\rm gd}$  is the gate-drain capacitance,  $g_{\rm ds}$  is the drain conductance, and  $R_{\rm s}$  and  $R_{\rm d}$  are the source and drain series resistances, respectively.

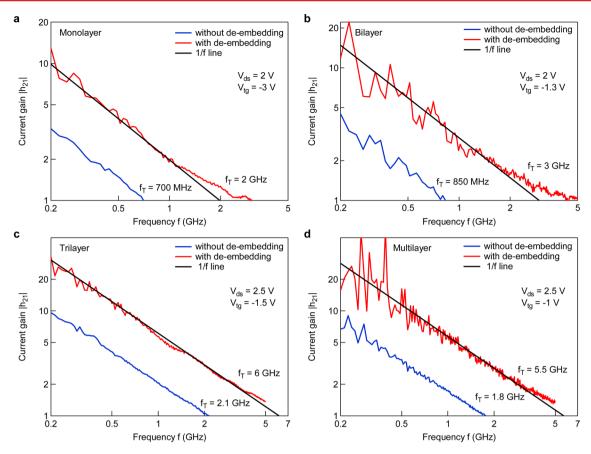

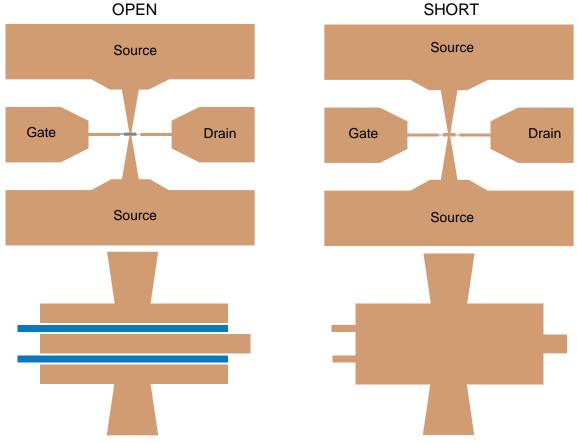

To probe the intrinsic performance of MoS<sub>2</sub> FETs in the RF range of operation, we measure the scattering S-parameters describing our devices using a vector network analyzer and perform standard calibration using dummy OPEN and SHORT structures<sup>33</sup> with the purpose of de-embedding the influence of the parasitic gate capacitance and resistance due to contact pads and device connections. These structures were fabricated with the same layout as the MoS<sub>2</sub> FETs and produced in the same fabrication run on intrinsic Si substrates, Supporting Information Figure S3. The intrinsic cutoff frequency obtained in this way is related to the carrier transit time between the source and drain terminals. We analyzed FETs based on 1L-MoS<sub>2</sub>, 2L-MoS<sub>2</sub>, and 3L-MoS<sub>2</sub> as well as multilayer MoS<sub>2</sub> stacks with thicknesses of ~5 nm. All the devices have a 240 nm gate length, total channel length of 340 nm, and a 30 nm thick layer of HfO2 acting as the gate dielectric.

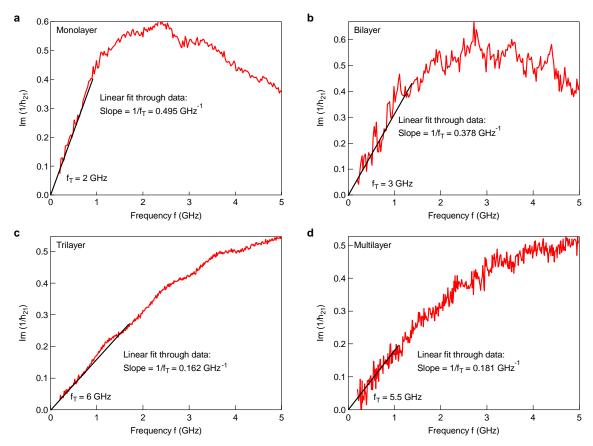

Figure 3 shows the short-circuit current gain (the ratio of small-signal drain and gate currents)  $h_{21}$  as a function of frequency for different thicknesses of exfoliated MoS<sub>2</sub>, before and after de-embedding. We operated our devices under bias and gate voltages  $V_{\rm ds}$  and  $V_{\rm tg}$  where they showed the highest intrinsic transconductance. We attribute the significant noise in the low-frequency characteristics to the large impedance mismatch between our devices and the test setup. The current gain  $H_{21}$  decreases with increasing frequency. All our devices showed  $f_T$  higher than 1 GHz after de-embedding. For 1L- $MoS_2$ , we obtain a cutoff frequency  $f_T = 2$  GHz for  $V_{ds} = 2$  V and  $V_{\rm tg}$  = -3 V. We record the highest cutoff frequency for trilayer MoS<sub>2</sub> with  $f_T = 6$  GHz for  $V_{ds} = 2.5$  V and  $V_{tg} = -1.5$  V. To estimate the value of  $f_T$  independently, we also used the Gummel's method<sup>34,35</sup> with results shown on Supporting Information Figure S2. The cutoff frequencies obtained from intercept of the 1/f dependence and Gummel's method are closely matched.

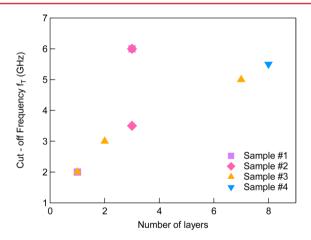

Figure 4 represents the behavior of the cutoff frequency as a function of the number of layers of MoS<sub>2</sub> FETs. We see a rise of the cutoff frequency with increasing number of layers from 1L-MoS<sub>2</sub> to 3L-MoS<sub>2</sub>, while the 5 nm thick multilayer MoS<sub>2</sub> devices shows no improvement in performance over the trilayer device. Possible reasons for this could include a lower contact resistance in the case of the trilayer device and longer collision-free paths for the trilayer device as indicated by the more

Figure 3. RF performance analysis for devices based on exfoliated MoS<sub>2</sub>. Small-signal current gain  $h_{21}$  as a function of frequency for devices based on 2D MoS<sub>2</sub> crystals with different thicknesses with and without deembedding. (a) Single-layer MoS<sub>2</sub> with the cutoff frequency  $f_{\rm T}=2$  GHz (b), bilayer MoS<sub>2</sub> with  $f_{\rm T}=3$  GHz at applied  $V_{\rm ds}=2$  V and  $V_{\rm tg}=-1.3$  V. (c) Trilayer MoS<sub>2</sub> with  $f_{\rm T}=6$  GHz and (d) multilayer MoS<sub>2</sub> with  $f_{\rm T}=5.5$  GHz at applied  $V_{\rm ds}=2.5$  V and  $V_{\rm tg}=-1$  V. The current gain  $h_{21}$  decreases with increasing frequency, following the -20 dB/dec slope expected for conventional FETs.

**Figure 4.** Summary of the RF performance of  $MoS_2$  devices. (a) Intrinsic cutoff frequency  $f_{\rm T}$  as a function of the number of layers of  $MoS_2$  transistors for four different samples with  $L_{\rm g}=200$  nm. Highest cutoff frequency is observed for the trilayer transistor.

pronounced saturation behavior in the trilayer device when compared to the monolayer device.

Because the intrinsic cutoff frequency is mostly determined by the minimum time required for charge carriers to travel across the channel, decreasing the length of the semiconducting channel and the gate length are expected to result in increased cutoff frequency of FETs as reported for RF GFET devices.  $^{13,35-37}$  Because the cutoff frequency  $f_{\rm T}$  is proportional to transconductance  $g_{\rm m}$ , which in turn is proportional to the field-effect mobility  $\mu_{\rm FE}$ , improving the mobility of the material by removing the adsorbates,  $^{38}$  removing intrinsic defects and reducing the temperature should result in further improvements to the cutoff frequency.

In addition to current gain, transistors for high-frequency logic circuits and amplifiers should also show voltage and power gains characterized by the maximum frequency of oscillation  $f_{\rm max}$ . This is the frequency at which the power gain is equal to 1. Just as  $f_{\rm T}$ ,  $f_{\rm max}$  can be expressed by following the equation for field-effect transistors<sup>39</sup>

$$f_{\text{max}} = \frac{f_{\text{T}}}{2\sqrt{g_{\text{ds}}(R_{\text{g}} + R_{\text{S}}) + 2\pi f_{\text{T}} C_{\text{g}} R_{\text{g}}}}$$

where  $g_{\rm ds}$  is the drain differential conductance,  $R_{\rm s}$  is the source resistance,  $C_{\rm gd}$  is the gate to drain capacitance, and  $R_{\rm g}$  is the gate resistance, which mainly depends on the gate thickness and area.

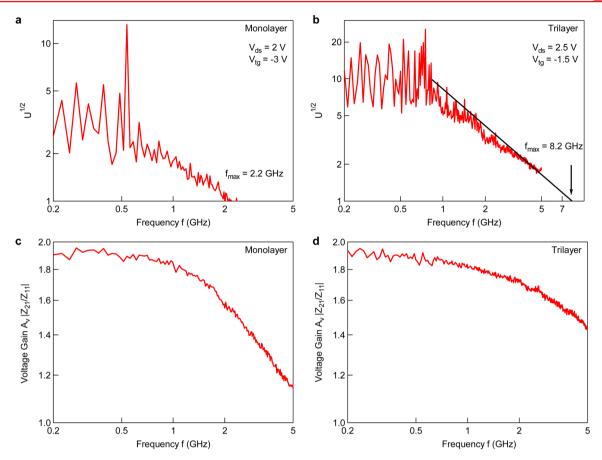

In Figure 5, we plot Mason's unilateral power gain U as a function of frequency for two  $\mathrm{MoS}_2$  devices. This figure of merit is useful for describing the quality of three-terminal devices and is the highest possible gain obtained by unilateralizing the two-port network with lossless feedback. For active devices, the quantity U is higher than 1 and  $f_{\mathrm{max}}$  corresponds to the frequency at which U=1 (U=0 dB). As

Figure 5. Power and voltage gain analysis for devices based on exfoliated MoS<sub>2</sub>. (a) Mason's unilateral gain U as a function of frequency for the monolayer MoS<sub>2</sub> device. Maximum frequency of oscillation  $f_{\text{max}} = 2.2$  GHz is extracted at the point where power gain reaches unity. (b) Same as in part a but for a trilayer device, resulting in  $f_{\text{max}} = 8.2$  GHz. (c) Voltage gain  $|Z_{21}/Z_{11}|$  as a function of frequency for the monolayer MoS<sub>2</sub> device showing gain higher than 1 up to 5 GHz. (d) Dependence of the voltage gain on frequency for the trilayer device.

shown in Figure 5a, we obtain  $f_{\rm max}$  = 2.2 GHz for single-layer MoS<sub>2</sub> with 240 nm gate length. For trilayer MoS<sub>2</sub>, we obtained  $f_{\text{max}}$  = 8.2 GHz, Figure 5b, similar to high-end RF FETs based on epitaxial graphene. 15 This result shows that MoS<sub>2</sub> could be interesting for high-frequency amplifiers. We also extract the intrinsic voltage gain  $A_v = g_m/g_{ds}$  for the same set of devices by converting the scattering S-parameters to impedance Z-parameters where  $A_{\rm v} = Z_{21}/Z_{11}$ . The results are presented in Figure 5c,d for our MoS2 FETs. At 200 MHz, Av is equal to 1.9 (5.5 dB) and is twice as high as in state-of-the-art RF-GFETs with equivalent gate oxide thickness and similar gate lengths.<sup>37</sup> Further device scaling is expected to improve all the operating parameters described here. Improvements in the voltage gain can be expected from decreasing the oxide thickness, resulting in better electrostatic control over the semiconducting channel. Reducing the gate length and improving the semiconducting channel mobility is expected to result in increased cutoff frequency  $f_T$ , while the maximum frequency of oscillation  $f_{\rm max}$  can be increased by reducing the parasitic effects due to the layout, capacitance, gate, and contact resistance.

In conclusion, we have characterized the high-frequency operation of top-gated  $MoS_2$  transistors with a 240 nm gate length. Our  $MoS_2$  RF-FETs show an intrinsic transconductance higher than 50  $\mu$ S/ $\mu$ m, saturation of drain-source current, and a voltage gain higher than 1. These features allow the operation of  $MoS_2$  transistors in the gigahertz range of frequencies. Our devices show cutoff frequencies as high as 6 GHz and are able

to not only amplify current in this frequency range but also power and voltage with the maximum frequency of oscillation  $f_{\rm max}=8.2$  GHz. These features show that  ${\rm MoS_2}$  and other 2D TMD semiconductors can be used to fabricate transistors that operate at gigahertz frequencies. Further improvements in device geometry and material processing are possible and will help realize the full potential of 2D semiconductors for low-cost and flexible high-frequency analog current and voltage amplifiers as well as high-frequency logic circuits.

Materials and Methods. Device characterization is performed at room temperature in an RF probe station (Cascade Microtech). Direct current (dc) and alternating current (ac) voltages are applied using bias tees connected to each probe head. The dc currents are measured using an Agilent B2912A parameter analyzer. The ac excitations and subsequent S-parameter measurements are performed using an Agilent N5224A vector-network analyzer (VNA). Highfrequency S-parameter characterization was carried out in the 0.2-5 GHz frequency range. The two VNA ports are connected to the sample's source and drain electrode via the bias-tees and probe heads. The probe system was calibrated before the measurements of the device under test (DUT) in order to take into account any spurious contribution of connectors, cables, and the electrical environment of the DUT and to subtract it from the measured signal. This is done first by means of a calibration pad and in the second step using a set of dummy structures. The system was calibrated using the linereflect-reflect-match method for the required frequency range

and at low input power (typically –27 dBm) using a standard CSR-8 substrate. On-chip OPEN and SHORT structures with exact design layout of the devices were used to de-embed the parasitic effects such as pad capacitance and interconnection resistance with the purpose to obtain the intrinsic RF performance. OPEN dummy structures are used to cancel the influence of the capacitive coupling between the electrodes. SHORT dummy structures are used to cancel the series resistance from the leads and contact resistance between probe tips and landing pads.

#### ASSOCIATED CONTENT

## S Supporting Information

Supplementary figures and discussion related to device fabrication, field-effect mobility and contact resistance extraction, cutoff frequency extraction using the Gummel's method, and layout of structures used for parameter de-embedding. This material is available free of charge via the Internet at http://pubs.acs.org.

### AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: andras.kis@epfl.ch.

#### **Notes**

The authors declare no competing financial interest.

### ACKNOWLEDGMENTS

The authors would like to thank W. Grabinski and O. Sanchez for useful discussions as well as A. Allain and S. Bertolazzi for technical help. Device fabrication was carried out in the EPFL Center for Micro/Nanotechnology (CMI). We thank Z. Benes (CMI) for technical support with e-beam lithography. This work was financially supported by Swiss SNF Grants 135046 and 144985 as well as ERC Grant 240076.

#### REFERENCES

- (1) Lebegue, S.; Eriksson, O. Electronic structure of two-dimensional crystals from ab initio theory. *Phys. Rev. B* **2009**, *79*, 115409.

- (2) Splendiani, A.; Sun, L.; Zhang, Y.; Li, T.; Kim, J.; Chim, C.-Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer MoS<sub>2</sub>. *Nano Lett.* **2010**, *10*, 1271–1275.

- (3) Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin  $MoS_2$ : A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* **2010**, 105, 136805.

- (4) Kuc, A.; Zibouche, N.; Heine, T. Influence of quantum confinement on the electronic structure of the transition metal sulfide TS<sub>2</sub>. *Phys. Rev. B* **2011**, *83*, 245213.

- (5) Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-dimensional atomic crystals. *Proc. Natl. Acad. Sci. U.S.A.* **2005**, *102*, 10451–10453.

- (6) Radisavljevic, B.; Whitwick, M. B.; Kis, A. Small-signal amplifier based on single-layer MoS<sub>2</sub>. Appl. Phys. Lett. **2012**, 101, 043103.

- (7) Bertolazzi, S.; Krasnozhon, D.; Kis, A. Nonvolatile Memory Cells Based on MoS<sub>2</sub>/Graphene Heterostructures. *ACS Nano* **2013**, *7*, 3246–3252.

- (8) Radisavljevic, B.; Whitwick, M. B.; Kis, A. Integrated circuits and logic operations based on single-layer MoS<sub>2</sub>. ACS Nano **2011**, 5, 9934–9938.

- (9) Wang, H.; et al. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

- (10) Lembke, D.; Kis, A. Breakdown of High-Performance Monolayer MoS<sub>2</sub> Transistors. ACS Nano 2012, 6, 10070–10075.

- (11) Avouris, P.; Chen, Z.; Perebeinos, V. Carbon-based electronics. *Nat. Nanotechnol.* **2007**, *2*, 605–615.

(12) Schroter, M.; Claus, M.; Sakalas, P.; Haferlach, M.; Dawei, W. Carbon Nanotube FET Technology for Radio-Frequency Electronics: State-of-the-Art Overview. *IEEE J. Electron Devices Soc.* **2013**, *1*, 9–20.

- (13) Lin, Y.-M.; Jenkins, K. A.; Valdes-Garcia, A.; Small, J. P.; Farmer, D. B.; Avouris, P. Operation of Graphene Transistors at Gigahertz Frequencies. *Nano Lett.* **2008**, *9*, 422–426.

- (14) Wei, P.; et al. Tuning the Dirac Point in CVD-Grown Graphene through Solution Processed n-Type Doping with 2-(2-Methoxyphen-yl)-1,3-dimethyl-2,3-dihydro-1H-benzoimidazole. *Nano Lett.* **2013**, *13*, 1890–1897.

- (15) Lin, Y.-M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H.-Y.; Grill, A.; Avouris, P. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. *Science* **2010**, 327, 662.

- (16) Castro, L. C.; John, D. L.; Pulfrey, D. L.; Pourfath, M.; Gehring, A.; Kosina, H. Method for predicting  $f_T$  for carbon nanotube FETs. *IEEE Trans. Nanotechnol.* **2005**, *4*, 699–704.

- (17) Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* **2004**, *306*, 666–669.

- (18) Barreiro, A.; Lazzeri, M.; Moser, J.; Mauri, F.; Bachtold, A. Transport Properties of Graphene in the High-Current Limit. *Phys. Rev. Lett.* **2009**, *103*, 076601.

- (19) Novoselov, K. S.; Falko, V. I.; Colombo, L.; Gellert, P. R.; Schwab, M. G.; Kim, K. A roadmap for graphene. *Nature* **2012**, 490, 192–200.

- (20) Guo, Z.; et al. Record Maximum Oscillation Frequency in C-Face Epitaxial Graphene Transistors. *Nano Lett.* **2013**, *13*, 942–947.

- (21) Zeng, H.; Dai, J.; Yao, W.; Xiao, D.; Cui, X. Valley polarization in MoS<sub>2</sub> monolayers by optical pumping. *Nat. Nanotechnol.* **2012**, *7*, 490–493, http://www.nature.com/nnano/journal/vaop/ncurrent/abs/nnano.2012.95.html#supplementary-information.

- (22) Mak, K. F.; He, K.; Shan, J.; Heinz, T. F. Control of valley polarization in monolayer MoS<sub>2</sub> by optical helicity. *Nat. Nanotechnol.* **2012**, *7*, 494–498.

- (23) Lopez-Sanchez, O.; Lembke, D.; Kayci, M.; Radenovic, A.; Kis, A. Ultrasensitive photodetectors based on monolayer MoS<sub>2</sub>. *Nat. Nanotechnol.* **2013**, *8*, 497–501.

- (24) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS<sub>2</sub> transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- (25) Radisavljevic, B.; Whitwick, M. B.; Kis, A. Small-signal amplifier based on single-layer MoS<sub>2</sub>. *Appl. Phys. Lett.* **2012**, *101*, 043103.

- (26) Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? *Nano Lett.* **2011**, *11*, 3768–3773.

- (27) Coleman, J. N.; et al. Two-Dimensional Nanosheets Produced by Liquid Exfoliation of Layered Materials. *Science* **2011**, *331*, 568–571.

- (28) Lee, Y.-H.; et al. Synthesis of Large-Area MoS<sub>2</sub> Atomic Layers with Chemical Vapor Deposition. *Adv. Mater.* **2012**, *24*, 2320–2325.

- (29) Najmaei, S.; et al. Vapour phase growth and grain boundary structure of molybdenum disulphide atomic layers. *Nat. Mater.* **2013**, 12, 754–759.

- (30) van der Zande, A. M.; et al. Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide. *Nat. Mater.* **2013**, *12*, 554–561.

- (31) Benameur, M. M.; Radisavljevic, B.; Heron, J. S.; Sahoo, S.; Berger, H.; Kis, A. Visibility of dichalcogenide nanolayers. *Nanotechnology* **2011**, *22*, 125706.

- (32) Schwierz, F. Graphene transistors. *Nat. Nanotechnol.* **2010**, *5*, 487–496.

- (33) Che, Y.; Lin, Y.-C.; Kim, P.; Zhou, C. T-Gate Aligned Nanotube Radio Frequency Transistors and Circuits with Superior Performance. *ACS Nano* **2013**, *7*, 4343–4350.

- (34) Gummel, H. K. On the definition of the cutoff frequency  $f_T$ . *Proc IEEE* **1969**, *57*, 2159–2159.

- (35) Wu, Y.; Lin, Y.-m.; Bol, A. A.; Jenkins, K. A.; Xia, F.; Farmer, D. B.; Zhu, Y.; Avouris, P. High-frequency, scaled graphene transistors on diamond-like carbon. *Nature* **2011**, 472, 74–78, DOI: 10.1038/nature09979.

(36) Zheng, J. Sub-10 nm Gate Length Graphene Transistors: Operating at Terahertz Frequencies with Current Saturation. Sci. Rep. **2013**, DOI: 10.1038/srep01314.

- (37) Wu, Y.; et al. State-of-the-Art Graphene High-Frequency

- Electronics. Nano Lett. 2012, 12, 3062–3067.

(38) Baugher, B.; Churchill, H. O. H.; Yang, Y.; Jarillo-Herrero, P. Intrinsic Electronic Transport Properties of High Quality Monolayer and Bilayer MoS<sub>2</sub>. Nano Lett. 2013, 13, 4212-4216.

- (39) Bahl, I. Fundamentals of RF and Microwave Transistor Amplifiers; John Wiley & Sons: New York, 2009.

# **Supplementary Information**

# for

# MoS<sub>2</sub> Transistors Operating at Gigahertz Frequencies

Daria Krasnozhon, Dominik Lembke, Clemens Nyffeler, Yusuf Leblebici, Andras Kis\*

Electrical Engineering Institute, Ecole Polytechnique Federale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland

\*Correspondence should be addressed to: Andras Kis, andras.kis@epfl.ch

## 1. Device fabrication

Top-gated MoS<sub>2</sub> transistors were fabricated starting with the adhesive-tape based micromechanical cleavage of commercially available, naturally occurring crystals of molybdenite using the method previously developed for graphene fabrication. The adhesive tape with ultrathin crystals is pressed against the surface of a substrate composed of intrinsic Si with 270 nm of SiO<sub>2</sub>. The substrate is imaged using an optical microscope (Olympus BX51M) equipped with a color camera. We have previously established the correlation between the optical contrast and thickness as measured by AFM for a number of dichalcogenide materials, including MoS<sub>2</sub>. We investigate the RF operation of MoS<sub>2</sub> in the GHz range for different thicknesses of the material.

## 2. Field-effect effective mobility and contact resistance

The particular contact geometry dictated by the need to interface RF transistors with the network analyzer and RF probes prohibits the fabrication of four or six contact devices, necessary to accurately measure the contact resistance and field-effect mobility in our devices. The presence of an underlap region is also expected to result in a relatively high value of the contact resistance which would dramatically underestimate the mobility extracted using the conventional two-contact field-effect mobility expression.

We can however, give an estimate of these quantities, based on a simple model where the source-drain current  $I_{ds}$  in a field-effect transistor is given by the following expression:

$$I_{ds} = \mu_{FE} C_{ox} \frac{W}{L_g} (V_{tg} - V_T) (V_{ds} - 2I_{ds} R_c)$$

(1)

Where of  $\mu_{FE}$  is the field-effect effective mobility,  $C_{ox}$  the gate capacitance, W the channel width,  $L_{g}$  the gate length,  $V_{tg}$  the top-gate voltage and  $V_{T}$  the threshold voltage.  $V_{ds}$  is the drain-source bias voltage while  $-2I_{ds}R_{c}$  is its reduction due to voltage drop on the contact resistance  $R_{c}$ . In this picture, the contact resistance corresponds to the inseries resistance of a single metal/MoS<sub>2</sub> junction and the ungated region of the MoS<sub>2</sub>

channel next to it. Because of the absence of a back-gate, we can neglect the variation of  $R_c$  with the gate voltage. We also neglect the variation of  $\mu_{FE}$  with the gate voltage.

We can rewrite equation (1) as:

$$I_{ds} = \frac{V_{ds}}{\frac{L_{g}}{\mu_{FE}C_{ox}W(V_{tg} - V_{T})} + 2R_{c}}$$

(2)

and fit the  $I_{\rm ds}$  -  $V_{\rm tg}$  curves as shown on Figure S1. We restrict the fit to regions of  $V_{\rm tg}$  where the curve shows a substantial deviation from a linear behavior, indicating a significant influence of the contact resistance. Previous measurements have shown that at these doping levels, the mobility of MoS<sub>2</sub> is not dependent on charge density.<sup>3</sup>

Fig. S1. Mobility and contact resistance extraction from the transfer characteristics of (a) monolayer and (b) trilayer  $MoS_2$  field-effect transistors. For both cases,  $V_{ds} = 0.1 \text{V}$ ,  $\kappa = 14$ , dielectric thickness is 30 nm and channel length  $L_g = 240$  nm. Channel width is W = 9  $\mu m$  for the monolayer and W = 21.5  $\mu m$  for the trilayer device.

Using this model, we extract estimates for the field effect mobility and contact resistance  $\mu_{FE} = 85 \text{ cm}^2/\text{Vs}$  and  $R_c = 2.0 \text{ k}\Omega \cdot \mu\text{m}$  for the case of the monolayer device and  $\mu_{FE} = 51 \text{ cm}^2/\text{Vs}$  and  $R_c = 3.1 \text{ k}\Omega \cdot \mu\text{m}$  for the trilayer device.

## 3. Cut-off frequency extraction using the Gummel's method

Gummel's method of extracting the cut-off frequency  $f_T$  offers a very useful verification of  $f_T$  values since it relies on lower frequency measurements. The method is based on the common-emitter current gain transfer function and the quasi-static definition for  $f_T$ :

$$h_{21}(f) = \frac{h_{21}(f=0)}{1 + jh_{21}(f=0)\frac{f}{f_T}}$$

(3)

Together with the realization that the best line-fit through  $Im[1/h_{21}(f)]$  for low values of f yields a slope equal to  $1/f_T$ . Figure S2 shows the results for our devices, resulting in  $f_T$  values in agreement with those presented in the main manuscript.

Fig. S2. Gummel's method. (a) The cut-off frequency for the monolayer  $MoS_2$  FET extracted using the Gummel's method is 2 GHz. (b) Gummel's method results in  $f_T$  = 3GHz for the bilayer device. (c) The cut-off frequency for trilayer  $MoS_2$  FET obtained using the Gummel's method is 6 GHz. (d) The cut-off frequency for multilayer  $MoS_2$  FET extracted with Gummel's method is 5.5 GHz.

## 4. Structures used for parameter de-embedding

In our work, we performed an OPEN/SHORT de-embedding procedure to remove the influence of gate capacitance and resistance due to contact pads and device connections. Figure S3 presents the OPEN and SHORT structures used for deembedding. They were fabricated together with the device under test (DUT) with the same geometry.

Fig. S3. Schematic images of OPEN and SHORT structures used for the de-embedding procedure. Lower panels: magnified view of the middle portion of the device. The de-embedding procedure subtracts the effect of the pads and reveals the intrinsic behavior of the device in the active area.

## References

- 1 Novoselov, K. S., Geim, A. K., Morozov, S. V., Jiang, D., Zhang, Y., Dubonos, S. V., Grigorieva, I. V. & Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 306, 666-669 (2004).

- 2 Benameur, M. M., Radisavljevic, B., Heron, J. S., Sahoo, S., Berger, H. & Kis, A. Visibility of dichalcogenide nanolayers. *Nanotechnology* **22**, 125706, doi:10.1088/0957-4484/22/12/125706 (2011).

- 3 Schmidt, H. *et al.* Transport Properties of Monolayer MoS<sub>2</sub> Grown by Chemical Vapor Deposition. *Nano Lett.*, doi:10.1021/nl4046922 (2014).

- 4 Gummel, H. K. On the definition of the cutoff frequency f<sub>T</sub>. *Proceedings of the IEEE* **57**, 2159-2159, doi:10.1109/proc.1969.7509 (1969).